Datasheet dsPIC33EP128GM304, dsPIC33EP128GM604, dsPIC33EP256GM304, dsPIC33EP256GM604, dsPIC33EP512GM304 Datasheet

...

dsPIC33EPXXXGM3XX/6XX/7XX

16-Bit Digital Signal Controllers with High-Speed PWM,

Op Amps and Advanced Analog Features

Operating Conditions

• 3.0V to 3.6V, -40°C to +85°C, up to 70 MIPS

• 3.0V to 3.6V, -40°C to +125°C, up to 60 MIPS

Core: 16-Bit dsPIC33E CPU

• Code-Efficient (C and Assembly) Architecture

• Two 40-Bit Wide Accumulators

• Single-Cycle (MAC/MPY) with Dual Data Fetch

• Single-Cycle Mixed-Sign MUL plus Hardware Divide

• 32-Bit Multiply Support

Clock Management

• Internal Fast FRC Oscillator with 1% Accuracy

• Programmable PLLs and Oscillator Clock Sources

• Fail-Safe Clock Monitor (FSCM)

• Independent Watchdog Timer (WDT)

• Fast Wake-up and Start-up

Power Management

• Low-Power Management modes (Sleep, Idle, Doze)

• Executing Optimized NOP String with Flash Fetch

• Integrated Power-on Reset and Brown-out Reset

• 0.6 mA/MHz Dynamic Current (typical)

•30 µA IPD Current (typical)

High-Speed PWM

• Up to 12 PWM Outputs (six generators)

• Primary Master Time Base Inputs allow Time Base

Synchronization from Internal/External Sources

• Dead Time for Rising and Falling Edges

• 7.14 ns PWM Resolution

• PWM Support for:

- DC/DC, AC/DC, Inverters, PFC, Lighting

- BLDC, PMSM, ACIM, SRM

• Programmable Fault Inputs

• Flexible Trigger Configurations for ADC Conversions

• Supports PWM Lock, PWM Output Chopping and

Dynamic Phase Shifting

Advanced Analog Features

• Two Independent ADC modules:

- Configurable as 10-bit, 1.1 Msps with

four S&H or 12-bit, 500 ksps with one S&H

- 11, 13, 18, 30 or 49 analog inputs

• Flexible and Independent ADC Trigger Sources

• Up to Four Op Amp/Comparators with Direct

Connection to the ADC module:

- Additional dedicated comparator

- Programmable references with 32 voltage points

- Programmable blanking and filtering

• Charge Time Measurement Unit (CTMU):

- Supports mTouch™ capacitive touch sensing

- Provides high-resolution time measurement (1 ns)

- On-chip temperature measurement

Timers/Output Compare/Input Capture

• 21 General Purpose Timers:

- Nine 16-bit and up to four 32-bit timers/counters

- Eight output capture modules configurable as

timers/counters

- PTG module with two configurable timers/counters

- Two 32-bit Quadrature Encoder Interface (QEI)

modules configurable as a timer/counter

• Eight Input Capture modules

• Peripheral Pin Select (PPS) to allow Function Remap

• Peripheral Trigger Generator (PTG) for Scheduling

Complex Sequences

Communication Interfaces

• Four Enhanced Addressable UART modules

(17.5 Mbps):

- With support for LIN/J2602 protocols and IrDA

• Three 3-Wire/4-Wire SPI modules (15 Mbps)

• 25 Mbps Data Rate for Dedicated SPI module

(with no PPS)

2

•Two I

• Two CAN modules (1 Mbps) with CAN 2.0B Support

• Programmable Cyclic Redundancy Check (CRC)

• Codec Interface module (DCI) with I

C™ modules (up to 1 Mbps) with SMBus Support

2

S Support

®

Direct Memory Access (DMA)

• 4-Channel DMA with User-Selectable Priority Arbitration

• Peripherals Supported by the DMA Controller include:

- UART, SPI, ADC, CAN and input capture

- Output compare and timers

Input/Output

• Sink/Source 15 mA or 10 mA, Pin-Specific for

Standard V

• 5V Tolerant Pins

• Selectable Open-Drain, Pull-ups and Pull-Downs

• Up to 5 mA Overvoltage Clamp Current

• Change Notice Interrupts on All I/O Pins

• PPS to allow Function Remap

OH/VOL

Qualification and Class B Support

• AEC-Q100 REVG (Grade 1, -40°C to +125°C) Planned

• AEC-Q100 REVG (Grade 0, -40°C to +150°C) Planned

• Class B Safety Library, IEC 60730

Debugger Development Support

• In-Circuit and In-Application Programming

• Three Complex and Five Simple Breakpoints

• IEEE 1149.2 Compatible (JTAG) Boundary Scan

• Trace and Run-Time Watch

2013-2014 Microchip Technology Inc. DS70000689D-page 1

dsPIC33EPXXXGM3XX/6XX/7XX

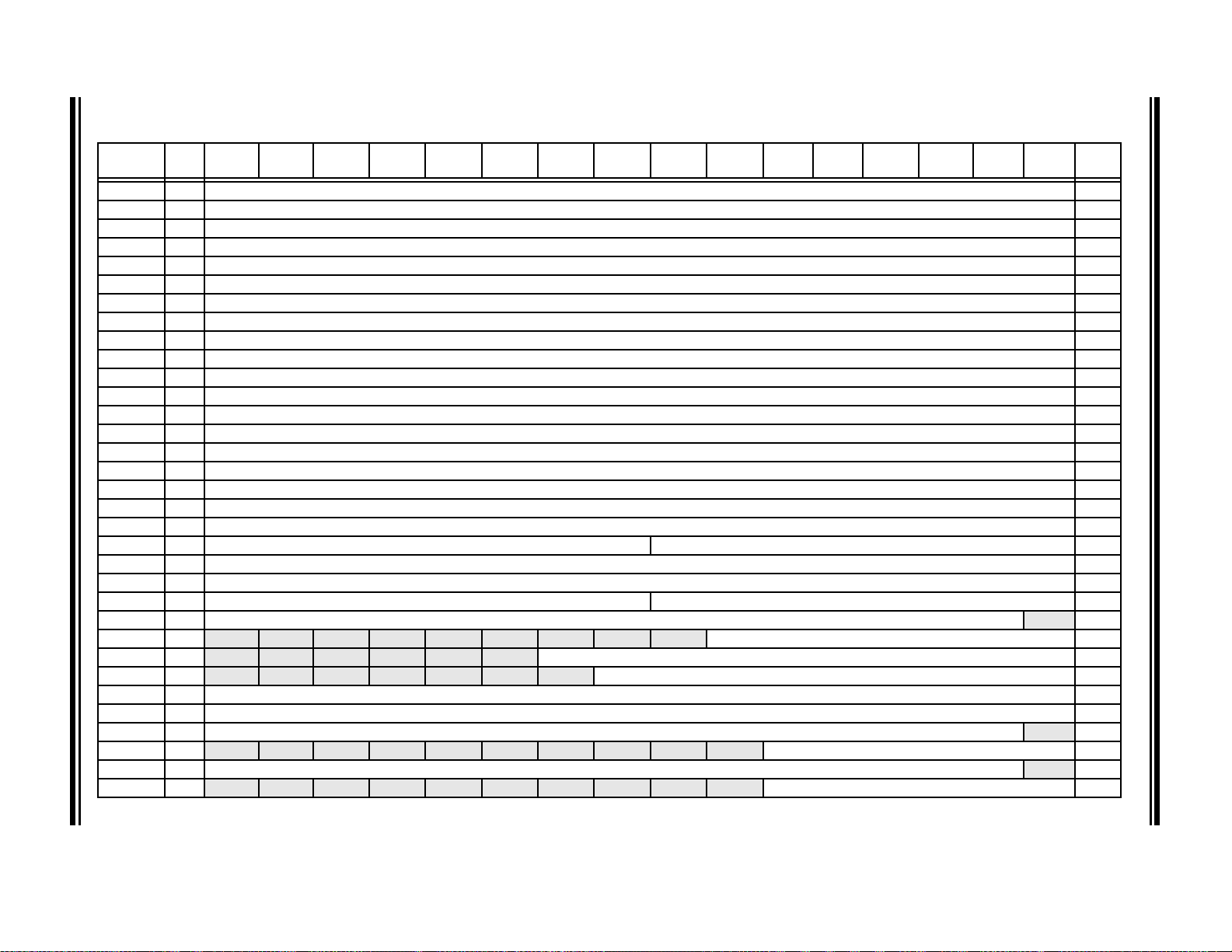

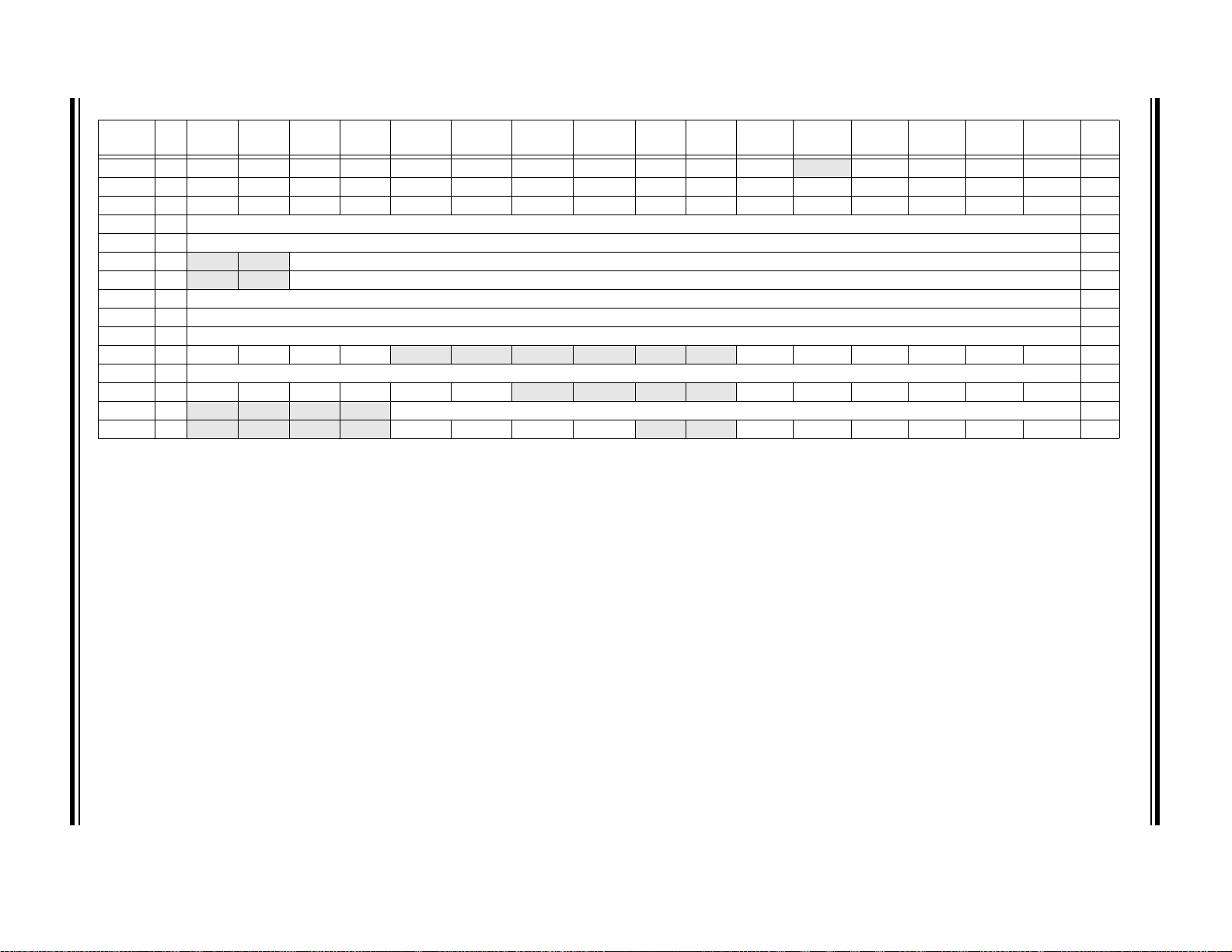

dsPIC33EPXXXGM3XX/6XX/7XX PRODUCT FAMILY

The device names, pin counts, memory sizes and

peripheral availability of each device are listed in

Table 1. Their pinout diagrams appear on the following

pages.

T A BL E 1: dsPIC33EPXXXGM3XX/ 6 XX/7X X FAM ILY DEVIC ES

Remappable Peripherals

(2)

Device

CAN

RAM (Kbytes)

Program Flash Memory (Kbytes)

dsPIC33EP128GM304

dsPIC33EP128GM604 2

dsPIC33EP256GM304

dsPIC33EP256GM604 2

dsPIC33EP512GM304

dsPIC33EP512GM604 2

dsPIC33EP128GM306

dsPIC33EP128GM706 2

dsPIC33EP256GM306

dsPIC33EP256GM706 2

dsPIC33EP512GM306

dsPIC33EP512GM706 2

dsPIC33EP128GM310

dsPIC33EP128GM710 2

dsPIC33EP256GM310

dsPIC33EP256GM710 2

dsPIC33EP512GM310

dsPIC33EP512GM710 2

Note 1: Only SPI2 and SPI3 are remappable.

2: INT0 is not remappable.

128 16

256 32

512 48

128 16

256 32

512 48

128 16

256 32

512 48

0

0

0

0

0

0

0

0

0

Input Capture

16-Bit/32-Bit Timers

9/4 8 8 12 2 4 3 1 5 2 1 2 18 4/5 1 Yes No No 35 44

9/4 8 8 12 2 4 3 1 5 2 1 2 30 4/5 1 Yes Yes Yes 53 64

9/48 8122 4 3 1 5 2 1 2494/5 1 YesYesYes85

DCI

C™

2

External I nt e r ru pts

ADC

I

CRC Generator

Op Amps/Comparators

10-Bit/12-Bit ADC (Channels)

PTG

PMP

CTMU

RTCC

Pins

I/O Pins

100/

121

Packages

TQFP,

QFN

TQFP,

QFN

TQFP,

TFBGA

(1)

QEI

SPI

UART

Output Compare

Motor Control PWM (Channels)

DS70000689D-page 2 2013-2014 Microchip Technology Inc.

Pin Diagrams

44-Pin TQFP

(1,2)

= Pins are up to 5V tolerant

4443424140393837363534

1

33

2

32

331

4

30

529

6

28

727

8

26

925

10 24

11 23

1213141516171819202122

TCK/AN26/CV

REF1O

/ASCL1/RP40/T4CK/RB8

TDO/PWM4H/RA10

RPI45/PWM2L/CTPLS/RB13

PGEC1/OA1IN+/AN4/C1IN3-/C1IN1+/C2IN3-/ RPI34/RB2

PGED1/OA1IN-/ AN5/C1IN1-/CTMUC/RP35/RB3

OA3OUT/AN6/C3IN 4-/C4IN4-/C4IN1+/RP48/OCFB/RC0

OA3IN-/AN7/C3IN1-/C4IN1-/RP49/RC1

OA4IN+/AN8/C3IN3-/C3IN1+/RPI50/U1RTS

/BCLK1/FLT3/RC2

V

DD

V

SS

AN32/OSC1/CLKI/RPI18/RA2

OSC2/CLKO/RPI19/RA3

SDA2/RPI24/RA8

FLT32/SCL2/RP36/RB4

TDI/PWM4L/RA7

RPI46/PWM1H/T3CK/T7CK/RB14

RPI47/PWM1L/T5CK/T6CK/RB15

AV

SS

AV

DD

MCLR

OA2OUT/AN0/C2I N4-/C5IN2-/C4IN3-/RPI16 /RA0

OA2IN+/AN1/C2IN1+/RPI17/RA1

PGED3/V

REF

-/OA2IN-/AN2/C2IN1-/ SS1/RPI32/CTED2/RB0

PGEC3/V

REF

+/CV

REF

+/OA1OUT/AN3/C1IN4-/C4IN2-/RPI33/CTED1/RB1

RPI44/PWM2H/ RB12

RP43/PWM3L/RB11

RP42/PWM3H/RB10

V

CAP

V

SS

RP57/PWM5L/RC9

RP56/PWM5H/RC8

RP55/PWM6L/RC7

RP54/PWM6H/RC6

TMS/OA5IN-/AN27/C5IN1-/RP41/RB9

OA5OUT/AN25/C5IN4-/RP39/INT0/RB7

PGEC2/ASCL2/RP38/RB6

PGED2/ASDA2/RP37/RB5

VDDVSSAN31/CV

REF2O

/SCL1/RPI53/RC5

AN30/SDA1/RPI52/RC4

AN29/SCK1/RPI51/RC3

AN28/ASDA1/SDI1/RPI25/ RA9

OA5IN+/AN24/C5IN3-/C5IN1+/SDO1/RP20/T1CK/RA4

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 “Peripheral

Pin Select (PPS)” for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O

Ports” for more information.

dsPIC33EPXXXGM304/604

dsPIC33EPXXXGM3XX/6XX/7XX

2013-2014 Microchip Technology Inc. DS70000689D-page 3

dsPIC33EPXXXGM3XX/6XX/7XX

44-Pin QFN

(1,2,3)

= Pins are up to 5V tolerant

44 43 42 41 40 39 38 37 36 35

12 13 14 15 16 17 18 19 20 21

3

30

29

28

27

26

25

24

23

4

5

7

8

9

10

11

1

2 32

31

6

22

33

34

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 “Peripheral

Pin Select (PPS)” for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O

Ports” for more information.

3: The metal pad at the bottom of the device is not connected to any pins and is recommended to be connected to

V

SS externally.

dsPIC33EPXXXGM304/604

TCK/AN26/CV

REF1O

/ASCL1/RP40/T4CK/RB8

TDO/PWM4H/RA10

RPI45/PWM2L/CTPLS/RB13 PGEC1/OA1IN+/AN4/C1IN3-/ C1IN1+/C2IN3-/RPI34/RB2

PGED1/OA1IN-/AN5/C1IN1-/CTMUC/RP35/RB3

OA3OUT/AN6/C3IN4-/C4IN4-/C4IN1+/RP48/OCFB/RC0

OA3IN-/AN7/C3IN1-/C4IN1-/RP49/RC1

OA3IN+/AN8/C3IN3-/C3IN1+/RPI50/U1RTS/BCLK1/FLT3/RC2

V

DD

V

SS

AN32/OSC1/CLKI/RPI18/RA2

OSC2/CLKO/RPI19/RA3

SDA2/RPI24/RA8

FLT32/SCL2/RP36/RB4

TDI/PWM4L/RA7

RPI46/PWM1H/T3CK/T7CK/RB14

RPI47/PWM1L/T5CK/T6CK/RB15

AV

SS

AV

DD

MCLR

OA2OUT/AN0/C2IN4-/C4IN3-/RPI16/RA0

OA2IN+/AN1/C2IN1+/RPI17/RA1

PGED3/V

REF

-/OA2IN-/AN2/C2IN1-/SS1/RPI32/CTED2/RB0

PGEC3/V

REF

+/CV

REF

+/OA1OUT/AN3/C1IN4-/C4IN2-/RPI33/CTED1/RB1

RPI44/PWM2H/RB12

RP43/PWM3L/RB11

RP42/PWM3H/RB10

V

CAP

V

SS

RP57/PWM5L/RC9

RP56/PWM5H/RC8

RP55/PWM6L/RC7

RP54/PWM6H/RC6

PGEC2/ASCL2/RP38/RB6

PGED2/ASDA2/RP37/RB5

VDDVSSAN30/SDA1/RPI52/RC4

AN29/SCK1/RPI51/RC3

AN28/ASDA1/SDI1/RPI25/RA9

OA5IN+/AN24/C5IN3-/C5IN1+/SDO1/RP20/T1CK/RA4

OA5OUT/AN25/C5IN4-/RP39/INT0/RB7

AN31/CV

REF2O

/SCL1/RPI53/RC5

TMS/OA5IN-/AN27/C5IN1-/RP41/RB9

Pin Diagrams (Continued)

DS70000689D-page 4 2013-2014 Microchip Technology Inc.

Pin Diagrams (Continued)

64-Pin TQFP

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 1 1.4 “Peripheral

Pin Select (PPS)” for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O

Ports” for more information.

3: This pin is not available as an input when OPMODE (CMxCON<10>) = 1.

dsPIC33EP128GM306/706

dsPIC33EP256GM306/706

dsPIC33EP512GM306/706

646362616059585756555453525150

49

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

171819202122232425262728293031

32

TDI/PWM4L/PMD5/RA7

RPI46/PWM1H/T3CK/T7CK/PM D6/RB14

RPI47/PWM 1L/T5CK/T 6CK/PMD7 /RB15

AN19/RP118/PMA5/RG6

AN18/ASCL1/RPI119/PMA4/RG7

AN17/ASDA1/RP120/PMA3/ RG8

MCLR

AN16/RPI121/PMA2/RG9

V

SS

V

DD

AN10/RPI28/RA12

AN9/RPI27/RA11

OA2OUT/AN0/C2IN4-/C4IN3-/RPI16/RA0

OA2IN+/A N1/C2IN1+/RPI17/RA1

PGED3/V

REF

-/OA2IN-/AN2/C2IN1-/SS1/RPI32/CT ED2/RB0

PGEC3/V

REF

+/CV

REF

+/OA1OUT/AN3/C1IN4-/C4IN2-/RPI33/CTED1/RB1

TDO/PWM4H/PMD4/RA10

RPI45/PWM2L/CTPLS/PMD3/RB13

RPI44/PWM2H/PMD2/RB12

RP43/PWM3L/PMD1/RB11

RP42/PWM3H/PMD0/RB10

RP97/RF1

RPI96/RF 0

VDDV

CAP

RP57/PWM5L/RC9

RP70/RD6

RP69/PMRD/RD5

RP56/PWM5H/PMWR/RC8

RP55/PWM6L/PMBE/RC7

RP54/PWM6H/RC6

TMS/OA5IN-/AN27/C5IN4-/RP41/RB9

TCK/AN26/CV

REF1O

/SOSCO/RP40/T4CK/RB8

SOSCI/RPI61/RC13

OA5OUT/AN25/C5IN4-/RP39/INT0/RB7

AN48/CV

REF2O

/RPI58/PMCS1/RC10

PGEC2/ASCL2/RP38/PMCS2/RB6

PGED2/ASDA2/RP37/RB5

RPI72/RD8

V

SS

OSC2/CLKO/RPI63/RC15

AN49/OSC1/CLKI/RPI60/RC12

V

DD

AN31/SCL 1/RPI53/RC5

AN30/SDA 1/RPI52/RC4

AN29/SCK 1/RPI51/RC3

AN28/SDI1/RPI25/RA9

OA5IN+/AN24/C5IN3-/C5IN1+/SDO1/RP20/T1CK/RA4

PGEC1/OA1IN+/AN4/C1IN3-/ C1IN1+/C2IN3-/RPI34/RB2

PGED1/O A1IN-/AN5/C1IN1-/(CTMUC)/ RP35/RTCC/RB3

AV

DD

AV

SS

OA3OUT/AN6/C3IN4-/C4IN1+/RP48/OCFB/RC0

OA3IN-/AN7/C3IN1-/C4IN1-/R P49/RC1

OA3IN+/AN8/C3IN3-/C3IN1+/RPI50/U1RTS/BCLK1/FLT3/RC2

AN11/C1IN2-/U1 CTS/FLT4/PMA12/RC11

V

SS

V

DD

AN12/C2IN2-/C5IN2-/U2RTS/BCLK2/FLT5/PMA11/RE12

AN13/C3IN2-/U2CTS/FLT6/PMA10/RE13

AN14/RPI94/FLT7/PMA1/RE14

AN15/RPI95/FLT8/PMA0/RE15

SDA2/RPI24/PMA9/RA8

FLT32/SCL2/RP36/PMA8/RB4

dsPIC33EPXXXGM3XX/6XX/7XX

2013-2014 Microchip Technology Inc. DS70000689D-page 5

dsPIC33EPXXXGM3XX/6XX/7XX

64-Pin QFN

(1,2,3,4)

= Pins are up to 5V tolerant

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 “Peripheral

Pin Select (PPS)” for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O

Ports” for more information.

3: This pin is not available as an input when OPMODE (CMxCON<10>) = 1.

4: The metal pad at the bottom of the device is not connected to any pins and is recommended to be connected to

V

SS externally.

dsPIC33EP128GM306/706

dsPIC33EP256GM306/706

dsPIC33EP512GM306/706

646362616059585756555453525150

49

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

171819202122232425262728293031

32

TDO/PWM4H/PMD4/RA10

RPI45/PWM2L/CTPLS/PMD3 /RB13

RPI44/PWM2H/PMD2/RB12

RP43/PWM3L/PM D1/RB11

RP42/PWM3H/P MD0/RB10

RP97/RF1

RPI96/RF0

VDDV

CAP

RP57/PWM5L/R C9

RP70/RD6

RP69/PMRD/RD5

RP56/PWM5H/P MWR/RC8

RP55/PWM6L/PM BE/RC7

RP54/PWM6H/RC6

TCK/AN26/CV

REF1O

/SOSCO/RP40/T4CK/RB8

SOSCI/RPI61/RC13

OA5OUT/AN25/ C5IN4-/RP39/INT0/RB7

AN48/CV

REF2O

/RPI58/PMCS 1/RC10

PGEC2/ASCL2/RP38/PMC S2/RB6

PGED2/ASDA2/RP37/RB5

RPI72/RD8

V

SS

OSC2/CLKO/RPI63/RC15

AN49/OSC1/CLKI/RPI60/RC12

V

DD

AN31/SCL1/RP I53/RC5

AN30/SDA1/RPI52/RC4

AN29/SCK1/RPI51/RC3

AN28/SDI1/RPI25/RA9

OA5IN+/AN24/C5IN3-/C5IN1+/SDO1/RP20/T1CK/RA4

PGEC1/OA1IN+/AN4/C1IN3-/C1IN1+/C2IN3-/RPI34/RB2

PGED1/OA1IN-/AN5/C1IN1-/(CTMUC)/RP35/RTCC/RB3

AV

DD

AV

SS

OA3OUT/AN6/C3IN4-/C4IN4-/C4IN1+/RP48/OCFB/RC0

OA3IN-/AN7 /C3IN1-/C4IN1-/RP49/RC1

OA3IN+/AN8/C 3IN3-/C3IN1+/R PI50/U1RTS

/BCLK1/FLT3/RC2

AN11/C1IN2-/U1CTS

/F LT4/ PM A1 2/ RC11

V

SS

V

DD

AN12/C2IN2-/C 5IN2-/U2RTS/BCLK2/FLT5/PMA11/RE12

AN13/C3IN2-/U 2CTS

/FLT6/PMA10/RE13

AN14/RPI94/F LT7/PMA1/RE14

AN15/RPI95/F LT8/PMA0/RE15

SDA2/RPI24/PMA9/RA8

FLT32/SCL2/RP36/PMA 8/RB4

TDI/PWM4L/P MD5/RA7

RPI46/PWM1H/T3CK/T7CK/PMD6/RB1 4

RPI47/PWM1L/T5CK/T6CK/PM D7/RB15

AN19/RP118/PMA5/RG 6

AN18/ASCL1/RPI119/PMA4/RG7

AN17/ASDA1/RP120/PMA3/RG 8

MCLR

AN16/RPI121 /PMA2/RG9

V

SS

V

DD

AN10/RPI28/RA12

AN9/RPI27/RA11

OA2OUT/AN0 /C2IN4-/C4IN3- /RPI16/RA0

OA2IN+/AN1/C2IN1+/RPI17/RA1

PGED3/V

REF

-/OA2IN-/AN2/C2IN1-/SS1/RPI32/CTED2/RB0

PGEC3/V

REF

+/CV

REF

+/OA1OUT/A N3/C1IN4-/C4IN 2-/RPI33/CTED1/RB1

TMS/OA5IN-/ AN27/C5IN1-/RP41/RB9

Pin Diagrams (Continued)

DS70000689D-page 6 2013-2014 Microchip Technology Inc.

Pin Diagrams (Continued)

100-Pin TQFP

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 “Peripheral

Pin Select (PPS)” for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O

Ports” for more information.

3: This pin is not available as an input when OPMODE (CMxCON<10>) = 1.

dsPIC33EP128GM310/710

dsPIC33EP256GM310/710

dsPIC33EP512GM310/710

75

100

1

26

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

2728293031323334353637383940414243444546474849

50

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

9998979695949392919089888786858483828180797877

76

PGEC1/OA1IN+/AN4/C1IN3-/C1IN1+/C2IN3-/RPI34/RB2

PGED1/OA1IN-/AN5/C1IN1-/CTMUC/RP35/RTCC/RB3

V

REF

-/AN33/PMA6/RF9

V

REF

+/AN34/PM A7/RF10

AV

DD

AV

SS

OA3OUT/AN6/C3IN4-/C4IN4-/C4IN1+/RP48/OCFB/RC0

OA3IN-/AN7/C3IN1-/C4IN1-/RP49/RC1

OA3IN+/AN8/C3IN3-/C3IN1+/RPI50/U1RTS

/BCLK1/FLT3/RC2

AN11/C1IN2-/U1CTS

/FLT4/PMA12/RC11

V

SS

V

DD

AN35/RG11

AN36/RF1 3

AN37/RF1 2

AN12/C2IN2-/C5IN2-/U2RTS

/BCLK2/FLT5/PMA11/RE12

AN13/C3IN2-/U2CTS

/FLT6/PMA10/ RE13

AN14/RPI94/FLT7/PMA1/RE14

AN15/RPI95/FLT8/PMA0/RE15

V

SS

V

DD

AN38/RD1 4

AN39/RD1 5

SDA2/RPI24/PMA9/RA8

FLT32/SCL2/RP36/PMA8/RB4

TDI/PWM4L/PMD5/RA7

RPI47/PWM1L/T5CK/T6CK/PMD7/RB15

AN19/RP118/PMA5/RG6

AN18/ASCL1/RPI119/PMA4/RG7

AN17/ASDA1/RP120/PMA3/RG8

MCLR

AN16/RPI121/PMA2/RG9

V

DD

AN10/RPI 28/RA12

AN9/RPI27/RA11

OA2OUT/AN0/C2IN4-/C4IN3-/RPI16/RA0

OA2IN+/AN1/C2IN1+/RPI17/RA1

PGED3/OA2IN-/AN2/C2IN1-/SS1

/RPI32/CTED2/RB0

PGEC3/CV

REF

+/OA1OUT/AN3/C1IN4-/C4IN2-/RPI33/CTED1/RB1

V

SS

RPI46/PWM1H/T3CK/T7CK/PMD6/RB14

V

DD

AN22/RG10

AN21/RE8

AN20/RE9

AN23/RP 127/RG15

PWM5L/RD1

PWM5H/RD2

PWM6L/T9CK/RD3

PWM6H/T8CK/RD4

V

SS

TCK/AN26/CV

REF1O

/SOSCO/RP 40/T4CK/RB8

SOSCI/RPI61/RC13

OA5OUT/AN25/C5IN4-/RP39/INT0/RB7

AN48/CV

REF2O

/RPI58/PMCS1/RC10

PGEC2/ASCL2/RP38/PMCS2/RB6

PGED2/ASDA2/RP37/RB5

RPI72/RD8

AN47/INT4/RA15

AN46/INT3/RA14

V

SS

OSC2/CLKO/RPI63/RC15

AN49/OSC1/CLKI/RPI60/RC12

V

DD

AN45/RF5

AN44/RF4

AN43/RG3

AN42/RG2

TDO/PWM4H/PMD4/RA10

RPI45/PWM2L/CTPLS/PMD3/RB13

RPI44/PWM2H/PMD2/RB12

RPI124/RG12

RP126/RG14

RP43/PWM3L/PMD1/RB11

RP42/PWM3H/PMD0/RB10

RF7

RF6

RPI112/RG0

RP113/RG1

RP97/RF1

RPI96/RF0

VDDV

CAP

RP57/RC9

RP70/RD6

RP69/PMRD/RD5

RP56/PMWR/RC8

RPI77/RD13

RPI76/RD12

RP55/PMBE/RC7

RP54/RC6

TMS/OA5IN-/AN27/C5IN1-/RP41/RB9

AN31/SCL1/RPI53/RC5

AN30/SDA1/RPI52/RC4

AN41/RP81/RE1

AN40/RPI80/RE0

OA5IN+/AN 24/C5IN3-/C5I N1+/SDO1/RP20/ T1CK/RA4

AN29/SCK1/RPI51/RC3

AN28/SDI1/RPI25/RA9

RP125/RG13

dsPIC33EPXXXGM3XX/6XX/7XX

2013-2014 Microchip Technology Inc. DS70000689D-page 7

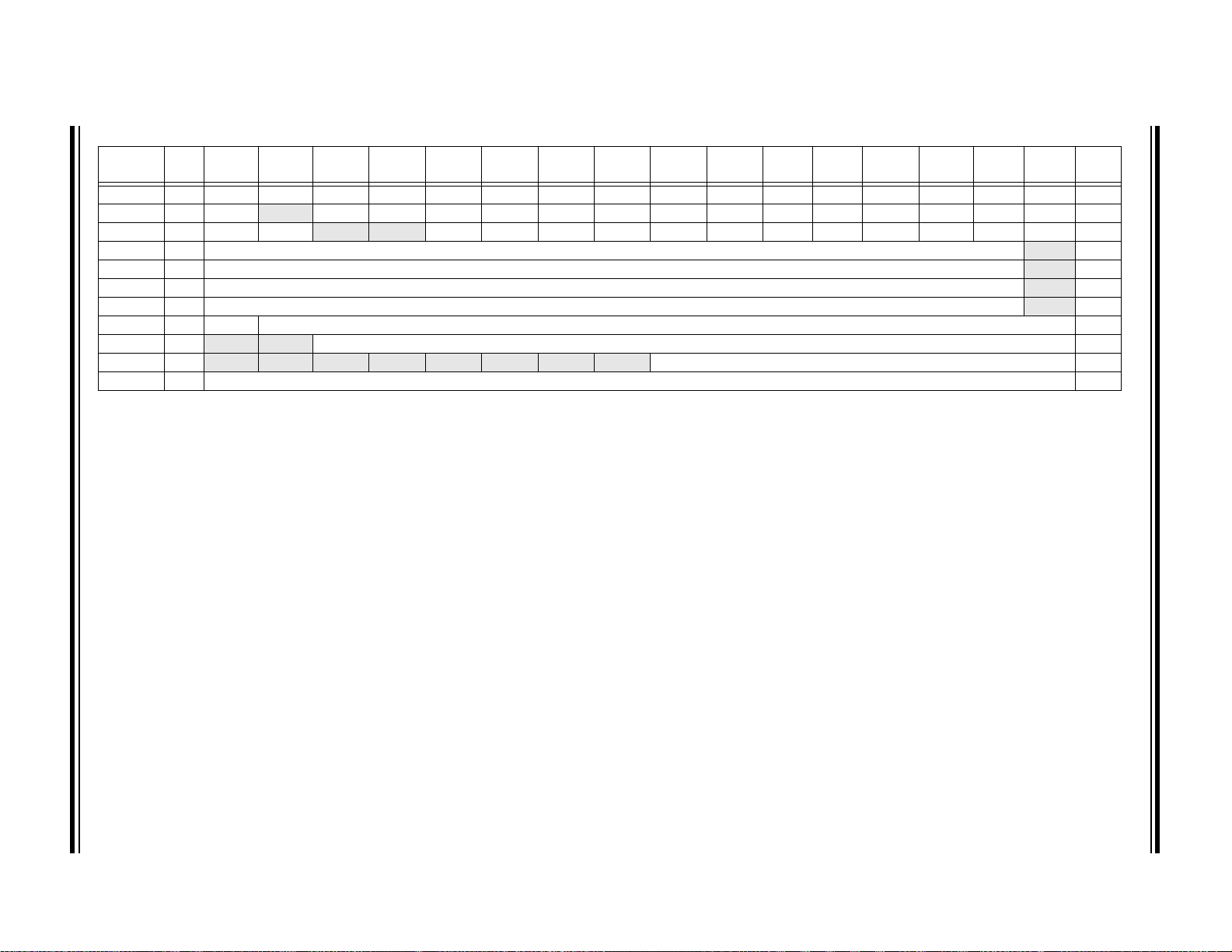

dsPIC33EPXXXGM3XX/6XX/7XX

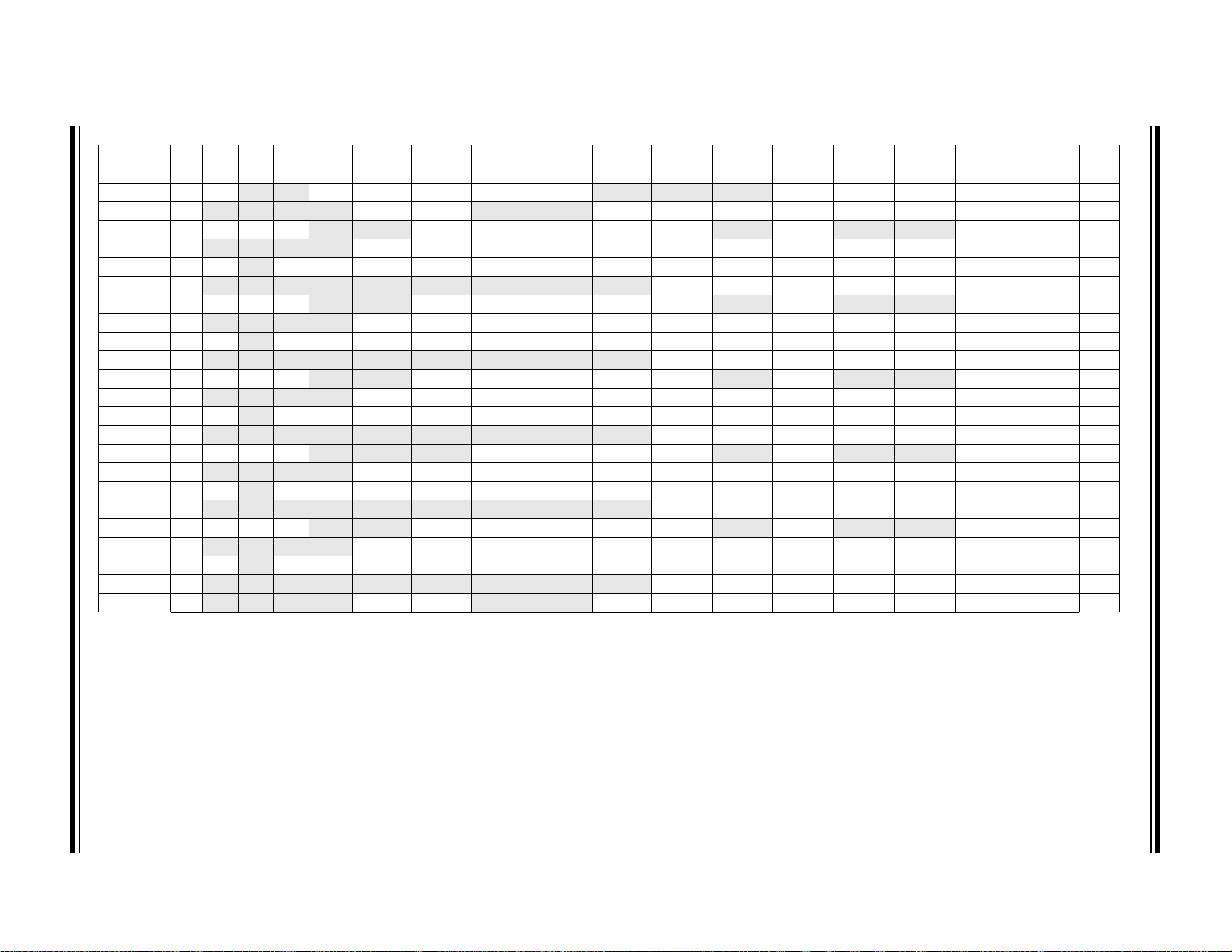

121-Pin TFBGA

(1)

= Pins are up to 5V tolerant

dsPIC33EP128GM310/710

dsPIC33EP256GM310/710

dsPIC33EP512GM310/710

Note 1: Refer to Table 2 for full pin names.

1234567891011

A

RA10 RB13 RG13 RB10 RG0 RF1 VDD NC RD12 RC6 RB9

B

NC RG15 RB12 RB11 RF7 RF0 VCAP RD5 RC7 VSS RB8

C

RB14 VDD RG12 RG14 RF6 NC RC9 RC8 NC RC13 RC10

D

RD1 RB15 RA7 NC NC NC RD6 RD13 RB7 NC RB6

E

RD4 RD3 RG6 RD2 NC RG1 NC RA15 RD8 RB5 RA14

F

MCLR RG8 RG9 RG7 VSS NC NC VDD RC12 VSS RC15

G

RE8 RE9 RG10 NC VDD VSS VSS NC RF5 RG3 RF4

H

RA12 RA11 NC NC NC VDD NC RA9 RC3 RC5 RG2

J

RA0 RA1 RB3 AVDD RC11 RG11 RE12 NC NC RE1 RC4

K

RB0 RB1 RF10 RC0 NC RF12 RE14 VDD RD15 RA4 RE0

L

RB2 RF9 AVSS RC1 RC2 RF13 RE13 RE15 RD14 RA8 RB4

Pin Diagrams (Continued)

DS70000689D-page 8 2013-2014 Microchip Technology Inc.

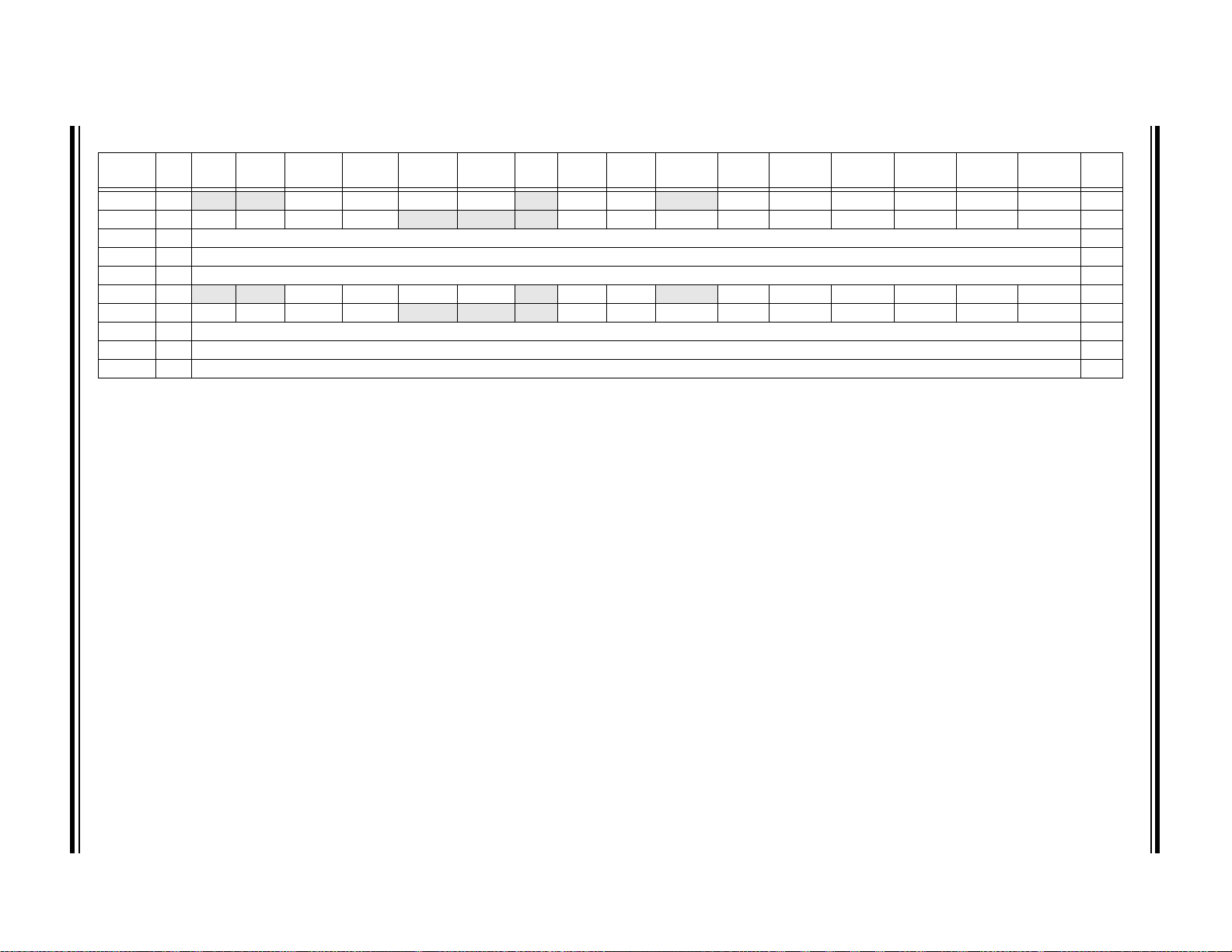

dsPIC33EPXXXGM3XX/6XX/7XX

T ABLE 2: PIN NAMES: dsPIC33EP128/256/512GM310/710 DEVICES

Pin # Full Pin Name Pin # Full Pin Name

A1 TDO/PWM4H/PMD4/RA10 E8 AN47/INT4/RA15

A2 RPI45/PWM2L/CTPLS/PMD3/RB13 E9 RPI72/RD8

A3 RP125/RG13 E10 PGED2/ASDA2/RP37/RB5

A4 RP42/PWM3H/PMD0/RB10 E11 AN46/INT3/RA14

A5 RPI112/RG0 F1 MCLR

A6 RP97/RF1 F2 AN17/ASDA1/RP120/PMA3/RG8

A7 V

A8 No Connect F4 AN18/ASCL1/RPI119/PMA4/RG7

A9 RPI76/RD12 F5 V

A10 RP54/RC6 F6 No Connect

A11 TMS/OA5IN-/AN27/C5IN1-/RP41/RB9 F7 No Connect

B1 No Connect F8 V

B2 AN23/RP127/RG15 F9 AN49/OSC1/CLKI/RPI60/RC12

B3 RPI44/PWM2H/PMD2/RB12 F10 V

B4 RP43/PWM3L/PMD1/RB11 F11 OSC2/CLKO/RPI63/RC15

B5 RF7 G1 AN21/RE8

B6 RPI96/RF0 G2 AN20/RE9

B7 V

B8 RP69/PMRD/RD5 G4 No Connect

B9 RP55/PMBE/RC7 G5 V

B10 VSS G6 VSS

B11 TCK/AN26/CVREF1O/SOSCO/RP40/T4CK/RB8 G7 VSS

C1 RPI46/PWM1H/T3CK/T7CK/PMD6/RB14 G8 No Connect

C2 V

C3 RPI124/RG12 G10 AN43/RG3

C4 RP126/RG14 G11 AN44/RF4

C5 RF6 H1 AN10/RPI28/RA12

C6 No Connect H2 AN9/RPI27/RA11

C7 RP57/RC9 H3 No Connect

C8 RP56/PMWR/RC8 H4 No Connect

C9 No Connect H5 No Connect

C10 SOSCI/RPI61/RC13 H6 V

C11 AN48/CVREF2O/RPI58/PMCS1/RC10 H7 No Connect

D1 PWM5L/RD1 H8 AN28/SDI1/RPI25/RA9

D2 RPI47/PWM1L/T5CK/T6CK/PMD7/RB15 H9 AN29/SCK1/RPI51/RC3

D3 TDI/PWM4L/PMD5/RA7 H10 AN31/SCL1/RPI53/RC5

D4 No Connect H11 AN42/RG2

D5 No Connect J1 OA2OUT/AN0/C2IN4-/C4IN3-/RPI16/RA0

D6 No Connect J2 OA2IN+/AN1/C2IN3-/C2IN1+/RPI17/RA1

D7 RP70/RD6 J3 PGED1/OA1IN-/AN5/C1IN1-/CTMUC/RP35/RTCC/RB3

D8 RPI77/RD13 J4 AV

D9 OA5OUT/AN25/C5IN4-/RP39/INT0/RB7 J5 AN11/C1IN2-/U1CTS/FLT4/PMA12/RC11

D10 No Connect J6 AN35/RG11

D11 PGEC2/ASCL2/RP38/PMCS2/RB6 J7 AN12/C2IN2-/C5IN2-/U2RTS

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 “Peripheral Pin Select (PPS)” for

DD F3 AN16/RPI121/PMA2/RG9

SS

DD

SS

CAP G3 AN22/RG10

DD

DD G9 AN45/RF5

DD

DD

available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O Ports” for more information.

3: The availability of I

ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 30.0 “Special Features” for more information.

2

C™ interfaces varies by device. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits,

(1,2,3)

/BCLK2/FLT5/PMA11/RE12

2013-2014 Microchip Technology Inc. DS70000689D-page 9

dsPIC33EPXXXGM3XX/6XX/7XX

TABLE 2: PIN NAMES: dsPIC33EP128/256/512GM310/710 DEVICES

Pin # Full Pin Name Pin # Full Pin Name

E1 PWM6H/T8CK/RD4 J8 No Connect

E2 PWM6L/T9CK/RD3 J9 No Connect

E3 AN19/RP118/PMA5/RG6 J10 AN41/RP81/RE1

E4 PWM5H/RD2 J11 AN30/SDA1/RPI52/RC4

E5 No Connect K1 PGED3/OA2IN-/AN2/C2IN1-/SS1

E6 RP113/RG1 K2 PGEC3/CV

E7 No Connect K3 V

K4 OA3OUT/AN6/C3IN4-/C4IN4-/C4IN1+/RP48/OCFB/RC0 L3 AV

K5 No Connect L4 OA3IN-/AN7/C3IN1-/C4IN1-/RP49/RC1

K6 AN37/RF12 L5 OA3IN+/AN8/C3IN3-/C3IN1+/RPI50/U1RTS

K7 AN14/RPI94/FLT7/PMA1/RE14 L6 AN36/RF13

K8 V

K9 AN39/RD15 L8 AN15/RPI95/FLT8/PMA0/RE15

K10 OA5IN+/AN24/C5IN3-/C5IN1+/SDO1/RP20/T1CK/RA4 L9 AN38/RD14

K11 AN40/RPI80/RE0 L10 SDA2/RPI24/PMA9/RA8

L1 PGEC1/OA1IN+/AN4/C1IN3-/C1IN1+/C2IN3-/RPI34/RB2 L11 FLT32/SCL2/RP36/PMA8/RB4

L2 V

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 “Peripheral Pin Select (PPS)” for

DD L7 AN13/C3IN2-/U2CTS/FLT6/PMA10/RE13

REF-/AN33/PMA6/RF9

available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 “I/O Ports” for more information.

3: The availability of I

ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 30.0 “Special Features” for more information.

2

C™ interfaces varies by device. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits,

CTED1/RB1

REF+/AN34/PMA7/RF10

SS

PMA13/RC2

(1,2,3)

(CONTINUED)

/RPI32/CTED2/RB0

REF+/OA1OUT/AN3/C1IN4-/C4IN2-/RPI33/

/BCLK1/FLT3/

DS70000689D-page 10 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

Table of Contents

dsPIC33EPXXXGM3XX/6XX/7XX Product Family ................................................................................................................................ 2

1.0 Device Overview ........................................................................................................................................................................ 15

2.0 Guidelines for Getting Started with 16-Bit Digital Signal Controllers.......................................................................................... 21

3.0 CPU............................................................................................................................................................................................ 27

4.0 Memory Organization................................................................................................................................................................. 37

5.0 Flash Program Memory............................................................................................................................................................ 103

6.0 Resets ..................................................................................................................................................................................... 111

7.0 Interrupt Controller ................................................................................................................................................................... 115

8.0 Direct Memory Access (DMA) .................................................................................................................................................. 129

9.0 Oscillator Configuration ............................................................................................................................................................ 143

10.0 Power-Saving Features............................................................................................................................................................ 153

11.0 I/O Ports ................................................................................................................................................................................... 163

12.0 Timer1 ...................................................................................................................................................................................... 211

13.0 Timer2/3, Timer4/5, Timer6/7 and Timer8/9 ............................................................................................................................ 213

14.0 Input Capture............................................................................................................................................................................ 219

15.0 Output Compare....................................................................................................................................................................... 223

16.0 High-Speed PWM Module ........................................................................................................................................................ 229

17.0 Quadrature Encoder Interface (QEI) Module ........................................................................................................................... 257

18.0 Serial Peripheral Interface (SPI)............................................................................................................................................... 273

19.0 Inter-Integrated Circuit™ (I

20.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 289

21.0 Controller Area Network (CAN) Module (dsPIC33EPXXXGM6XX/7XX Devices Only) ........................................................... 295

22.0 Charge Time Measurement Unit (CTMU) ............................................................................................................................... 321

23.0 10-Bit/12-Bit Analog-to-Digital Converter (ADC) ...................................................................................................................... 327

24.0 Data Converter Interface (DCI) Module.................................................................................................................................... 343

25.0 Peripheral Trigger Generator (PTG) Module............................................................................................................................ 349

26.0 Op Amp/Comparator Module ................................................................................................................................................... 365

27.0 Real-Time Clock and Calendar (RTCC) .................................................................................................................................. 383

28.0 Parallel Master Port (PMP)....................................................................................................................................................... 395

29.0 Programmable Cyclic Redundancy Check (CRC) Generator .................................................................................................. 405

30.0 Special Features ...................................................................................................................................................................... 411

31.0 Instruction Set Summary.......................................................................................................................................................... 419

32.0 Development Support............................................................................................................................................................... 429

33.0 Electrical Characteristics.......................................................................................................................................................... 433

34.0 High-Temperature Electrical Characteristics............................................................................................................................ 499

35.0 Packaging Information.............................................................................................................................................................. 507

Appendix A: Revision History............................................................................................................................................................. 527

Index ................................................................................................................................................................................................. 529

The Microchip Web Site..................................................................................................................................................................... 537

Customer Change Notification Service .............................................................................................................................................. 537

Customer Support .............................................................................................................................................................................. 537

Product Identification System ............................................................................................................................................................ 539

2

C™).............................................................................................................................................. 281

2013-2014 Microchip Technology Inc. DS70000689D-page 11

dsPIC33EPXXXGM3XX/6XX/7XX

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS70000689D-page 12 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

Referenced Sources

This device data sheet is based on the following

individual chapters of the “dsPIC33/PIC24 Family Ref-

erence Manual”, which are available from the Microchip

web site (www.microchip.com). These documents

should be considered as the general reference for the

operation of a particular module or device feature.

• “Introduction” (DS70573)

• “CPU” (DS70359)

• “Data Memory” (DS70595)

• “Program Memory” (DS70613)

• “Flash Programming” (DS70609)

• “Interrupts” (DS70000600)

• “Oscillator” (DS70580)

• “Reset” (DS70602)

• “Watchdog Timer and Power-Saving Modes” (DS70615)

• “I/O Ports” (DS70000598)

• “Timers” (DS70362)

• “Input Capture” (DS70000352)

• “Output Compa r e” (DS70005157)

• “High-Speed PWM” (DS70645)

• “Quadrature Encoder Interface (QEI)” (DS70601)

• “Analog-to-Digital Converter (ADC)” (DS70621)

• “Universal Asynchronous Receiver Transmitter (UART)” (DS70000582)

• “Serial Peripheral Interface (SPI)” (DS70005185)

• “Inter-Integrated Circuit™ (I

• “Data Converter Interface (DCI) Module” (DS70356)

• “Enhanced Controller Area Network (ECAN™)” (DS70353)

• “Direct Memory Access (DMA)” (DS70348)

• “Programming and Diagnostics” (DS70608)

• “Op Amp/Comparator” (DS70000357)

• “32-Bit Programmable Cyclic Redundancy Check (CRC)” (DS70346)

• “Parallel Master Port (PMP)” (DS70576)

• “Device Configuration” (DS70000618)

• “Peripheral Trigger Generator (PTG)” (DS70669)

• “Charge Time Measurement Unit (CTMU)” (DS70661)

2

C™)” (DS70000195)

2013-2014 Microchip Technology Inc. DS70000689D-page 13

dsPIC33EPXXXGM3XX/6XX/7XX

NOTES:

DS70000689D-page 14 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

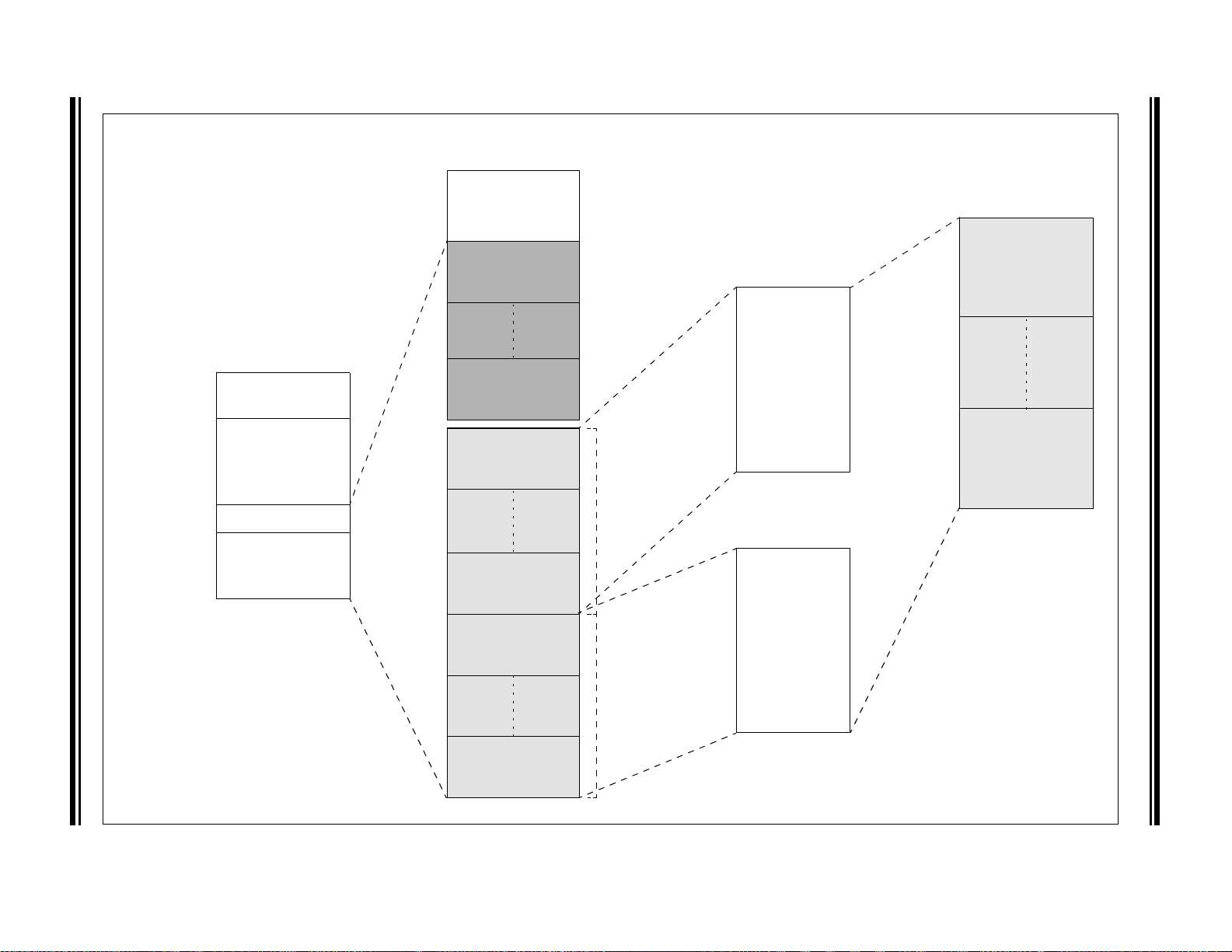

PORTA

Power-up

Timer

Oscillator

Star t-up

OSC1/CLKI

MCLR

VDD, VSS

UART1/2/3/4

Timing

Generation

CAN1/2

(1)

I2C1/2

ADC

Timers

Input

Capture

Output

Compare

AV

DD, AVSS

SPI1/2/3

Watchdog

Timer

POR/BOR

CRC

QEI1/2

PWM

Remappable

Pins

Note 1: This feature or peripheral is only available on dsPIC33EPXXXGM6XX/7XX devices.

Op Amp/

Comparator

CTMU

PTG

CPU

Refer to Figure 3-1 for CPU diagram details.

16

16

PORTB

PORTC

PORTD

PORTE

PORTF

PORTG

PORTS

Peripheral Modules

Timer

1.0 DEVICE OVERVIEW

This document contains device-specific information for

the dsPIC33EPXXXGM3XX/6XX/7XX Digital Signal

Note 1: This data sheet summarizes the features

of the dsPIC33EPXXXGM3XX/6XX/7XX

family of devices. It is not intended to be

a comprehensive resource. To complement the information in this data sheet,

refer to the related section of the

“dsPIC33/PIC24 Family Reference

Manual”, which is available from the

Controller (DSC) devices.

dsPIC33EPXXXGM3XX/6XX/7XX devices contain

extensive Digital Signal Processor (DSP) functionality

with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core

and peripheral modules. Table 1-1 lists the functions of

the various pins shown in the pinout diagrams.

Microchip web site (www.microchip.com)

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

FIGURE 1-1: dsPIC33EPXXXGM3XX/6XX/7XX BLOCK DIAGRAM

2013-2014 Microchip Technology Inc. DS70000689D-page 15

dsPIC33EPXXXGM3XX/6XX/7XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS

Pin

Pin Name

AN0-AN49 I Analog No Analog Input Channels 0-49.

CLKI

CLKO

OSC1

OSC2

SOSCI

SOSCO

IC1-IC8 I ST Yes Input Capture Inputs 1 through 8.

OCFA

OCFB

OC1-OC8

INT0

INT1

INT2

INT3

INT4

RA0-RA4, RA7-RA12,

RA14-RA15

RB0-RB15 I/O ST Yes PORTB is a bidirectional I/O port.

RC0-RC13, RC15 I/O ST Yes PORTC is a bidirectional I/O port.

RD1-RD6, RD8,

RD12-RD15

RE0-RE1, RE8-RE9,

RE12-RE15

RF0-RF1, RF4-RF7,

RF9-RF10,

RF12-RF13

RG0-RG3,

RG6-RG15

T1CK

T2CK

T3CK

T4CK

T5CK

T6CK

T7CK

T8CK

T9CK

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

PPS = Peripheral Pin Select TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the “Pin Diagrams” section for pin

availability.

DD must be connected at all times.

2: AV

Buffer

Type

Type

I

CMOS

O

I

CMOS

I/O

I

CMOS

O

I

I

O

I

I

I

I

I

I/O ST Yes PORTA is a bidirectional I/O port.

I/O ST Yes PORTD is a bidirectional I/O port.

I/O ST Yes PORTE is a bidirectional I/O port.

I/O ST No PORTF is a bidirectional I/O port.

I/O ST Yes PORTG is a bidirectional I/O port.

I

I

I

I

I

I

I

I

I

PPS Description

ST/

ST/

ST/

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

NoNoExternal clock source input. Always associated with OSC1 pin function.

—

—

—

—

Oscillator crystal output. Connects to crystal or resonator in Crystal

Oscillator mode. Optionally functions as CLKO in RC and EC modes.

Always associated with OSC2 pin function.

NoNoOscillator crystal input. ST buffer when configured in RC mode; CMOS

otherwise.

Oscillator crystal output. Connects to crystal or resonator in Crystal

Oscillator mode. Optionally functions as CLKO in RC and EC modes.

NoNo32.768 kHz low-power oscillator crystal input; CMOS otherwise.

32.768 kHz low-power oscillator crystal output.

Yes

Output Compare Fault A input (for compare channels).

No

Output Compare Fault B input (for compare channels).

Yes

Output Compare 1 through 8.

No

External Interrupt 0.

Yes

External Interrupt 1.

Yes

External Interrupt 2.

No

External Interrupt 3.

No

External Interrupt 4.

No

Timer1 external clock input.

Yes

Timer2 external clock input.

No

Timer3 external clock input.

No

Timer4 external clock input.

No

Timer5 external clock input.

No

Timer6 external clock input.

No

Timer7 external clock input.

No

Timer8 external clock input.

No

Timer9 external clock input.

DS70000689D-page 16 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin

Pin Name

U1CTS

U1RTS

U1RX

U1TX

U2CTS

U2RTS

U2RX

U2TX

U3CTS

U3RTS

U3RX

U3TX

U4CTS

U4RTS

U4RX

U4TX

SCK1

SDI1

SDO1

SS1

SCK2

SDI2

SDO2

SS2

SCK3

SDI3

SDO3

SS3

SCL1

SDA1

ASCL1

ASDA1

SCL2

SDA2

ASCL2

ASDA2

TMS

TCK

TDI

TDO

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

PPS = Peripheral Pin Select TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the “Pin Diagrams” section for pin

availability.

2: AV

DD must be connected at all times.

Type

I

O

I

O

I

O

I

O

I

O

I

O

I

O

I

O

I/O

I

O

I/O

I/O

I

O

I/O

I/O

I

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

O

Buffer

Type

ST

—

ST

—

ST

—

ST

—

ST

—

ST

—

ST

—

ST

—

ST

ST

—

ST

ST

ST

—

ST

ST

ST

—

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

—

PPS Description

Yes

UART1 Clear-to-Send.

Yes

UART1 Ready-to-Send.

Yes

UART1 receive.

Yes

UART1 transmit.

Yes

UART2 Clear-to-Send.

Yes

UART2 Ready-to-Send.

Yes

UART2 receive.

Yes

UART2 transmit.

Yes

UART3 Clear-to-Send.

Yes

UART3 Ready-to-Send.

Yes

UART3 receive.

Yes

UART3 transmit.

Yes

UART4 Clear-to-Send.

Yes

UART4 Ready-to-Send.

Yes

UART4 receive.

Yes

UART4 transmit.

No

Synchronous serial clock input/output for SPI1.

No

SPI1 data in.

No

SPI1 data out.

No

SPI1 slave synchronization or frame pulse I/O.

Yes

Synchronous serial clock input/output for SPI2.

Yes

SPI2 data in.

Yes

SPI2 data out.

Yes

SPI2 slave synchronization or frame pulse I/O.

Yes

Synchronous serial clock input/output for SPI3.

Yes

SPI3 data in.

Yes

SPI3 data out.

Yes

SPI3 slave synchronization or frame pulse I/O.

No

Synchronous serial clock input/output for I2C1.

No

Synchronous serial data input/output for I2C1.

No

Alternate synchronous serial clock input/output for I2C1.

No

Alternate synchronous serial data input/output for I2C1.

No

Synchronous serial clock input/output for I2C2.

No

Synchronous serial data input/output for I2C2.

No

Alternate synchronous serial clock input/output for I2C2.

No

Alternate synchronous serial data input/output for I2C2.

No

JTAG Test mode select pin.

No

JTAG test clock input pin.

No

JTAG test data input pin.

No

JTAG test data output pin.

2013-2014 Microchip Technology Inc. DS70000689D-page 17

dsPIC33EPXXXGM3XX/6XX/7XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin

Pin Name

(1)

INDX1

HOME1

QEA1

QEB1

CNTCMP1

INDX2

HOME2

QEA2

QEB2

CNTCMP2

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

COFS

CSCK

CSDI

CSDO

C1RX

C1TX

C2RX

C2TX

RTCC O — No Real-Time Clock and Calendar alarm output.

REF O Analog No Comparator Voltage Reference output.

CV

C1IN1+, C1IN2-,

C1IN1-, C1IN3-

C1OUT

C2IN1+, C2IN2-,

C2IN1-, C2IN3C2OUT

C3IN1+, C3IN2-,

C2IN1-, C3IN3C3OUT

C4IN1+, C4IN2-,

C4IN1-, C4IN3C4OUT

C5IN1-, C5IN2-,

C5IN3-, C5IN4-,

C5IN1+

C5OUT

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

PPS = Peripheral Pin Select TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the “Pin Diagrams” section for pin

availability.

DD must be connected at all times.

2: AV

Buffer

Type

O

O

I/O

I/O

O

I

I

I

I

I

I

I

I

I

I

Type

ST

ST

ST

ST

—

ST

ST

ST

ST

—

ST

ST

ST

—

ST—Yes

O

I

ST—Yes

O

IOAnalog—No

IOAnalog—No

IOAnalog—No

IOAnalog—No

IOAnalog—No

PPS Description

Yes

Quadrature Encoder Index1 pulse input.

Yes

Quadrature Encoder Home1 pulse input.

Yes

Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer

external clock input in Timer mode.

Yes

Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer

external gate input in Timer mode.

Yes

Quadrature Encoder Compare Output 1.

Yes

Quadrature Encoder Index2 Pulse input.

Yes

Quadrature Encoder Home2 Pulse input.

Yes

Quadrature Encoder Phase A input in QEI2 mode. Auxiliary timer

external clock input in Timer mode.

Yes

Quadrature Encoder Phase B input in QEI2 mode. Auxiliary timer

external gate input in Timer mode.

Yes

Quadrature Encoder Compare Output 2.

Yes

Data Converter Interface frame synchronization pin.

Yes

Data Converter Interface serial clock input/output pin.

Yes

Data Converter Interface serial data input pin.

Yes

Data Converter Interface serial data output pin.

CAN1 bus receive pin.

Yes

CAN1 bus transmit pin

CAN2 bus receive pin.

Yes

CAN2 bus transmit pin

Comparator 1 inputs.

Yes

Comparator 1 output.

Comparator 2 inputs.

Yes

Comparator 2 output.

Comparator 3 inputs.

Yes

Comparator 3 output.

Comparator 4 inputs.

Yes

Comparator 4 output.

Comparator 5 inputs.

Yes

Comparator 5 output.

DS70000689D-page 18 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin

Pin Name

Type

Buffer

Type

PPS Description

PMA0

I/O

TTL/ST

No

Parallel Master Port Address Bit 0 input (Buffered Slave modes) and

output (Master modes).

PMA1

I/O

TTL/ST

No

Parallel Master Port Address Bit 1 input (Buffered Slave modes) and

output (Master modes).

PMA2-PMA13

PMBE

PMCS1, PMCS2

PMD0-PMD7

O

O

O

I/O

—

—

—

TTL/ST

No

Parallel Master Port Address Bits 2-13 (Demultiplexed Master modes).

No

Parallel Master Port Byte Enable strobe.

No

Parallel Master Port Chip Select 1 and 2 strobe.

No

Parallel Master Port Data (Demultiplexed Master mode) or

Address/Data (Multiplexed Master modes).

PMRD

PMWR

FLT1-FLT2

FLT3-FLT8

(1)

(1)

FLT32

DTCMP1-DTCMP6

PWM1L-PWM6L

PWM1H-PWM6H

SYNCI1

(1)

(1)

(1)

, SYNCI2

SYNCO1, SYNCO2

PGED1

PGEC1

PGED2

PGEC2

PGED3

PGEC3

MCLR

O

—

No

Parallel Master Port Read strobe.

O

—

No

Parallel Master Port Write strobe.

I

ST

Yes

PWMx Fault Inputs 1 through 2.

I

(1)

(1)

(1)

O

O

O

I/O

I/O

I/O

ST

I

ST

I

ST

I

ST

ST

I

ST

ST

I

ST

ST

I

ST

—

—

—

No

PWMx Fault Inputs 3 through 8

No

PWMx Fault Input 32

Yes

PWMx Dead-Time Compensation Inputs 1 through 6.

No

PWMx Low Outputs 1 through 7.

No

PWMx High Outputs 1 through 7.

Yes

PWMx Synchronization Input 1.

Yes

PWMx Synchronization Outputs 1 and 2.

No

Data I/O pin for Programming/Debugging Communication Channel 1.

No

Clock input pin for Programming/Debugging Communication Channel 1.

No

Data I/O pin for Programming/Debugging Communication Channel 2.

No

Clock input pin for Programming/Debugging Communication Channel 2.

No

Data I/O pin for Programming/Debugging Communication Channel 3.

No

Clock input pin for Programming/Debugging Communication Channel 3.

I/P ST No Master Clear (Reset) input. This pin is an active-low Reset to the

device.

(2)

AV

DD

P P No Positive supply for analog modules. This pin must be connected at all

times.

SS P P No Ground reference for analog modules.

AV

DD P — No Positive supply for peripheral logic and I/O pins.

V

VCAP P — No CPU logic filter capacitor connection.

VSS P — No Ground reference for logic and I/O pins.

REF+ I Analog No Analog voltage reference (high) input.

V

VREF- I Analog No Analog voltage reference (low) input.

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

PPS = Peripheral Pin Select TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the “Pin Diagrams” section for pin

availability.

DD must be connected at all times.

2: AV

2013-2014 Microchip Technology Inc. DS70000689D-page 19

dsPIC33EPXXXGM3XX/6XX/7XX

NOTES:

DS70000689D-page 20 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

Note 1: This data sheet summarizes the features

of the dsPIC33EPXXXGM3XX/6XX/7XX

family of devices. It is not intended to be

a comprehensive reference source. To

complement the information in this data

sheet, refer to the related section of the

“dsPIC33/PIC24 Family Reference

Manual”, which is available from the

Microchip web site (www.microchip.com)

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGM3XX/6XX/7XX

family requires attention to a minimal set of device pin

connections before proceeding with development. The

following is a list of pin names, which must always be

connected:

DD and VSS pins

•All V

(see Section 2.2 “Decoupling Capacitors”)

•All AV

•V

•MCLR

• PGECx/PGEDx pins used for In-Circuit Serial

• OSC1 and OSC2 pins when external oscillator

Additionally, the following pins may be required:

•V

DD and AVSS pins (regardless if ADC module

is not used)

(see Section 2.2 “Decoupling Capacitors”)

CAP

(see Section 2.3 “CPU Logic Filter Capacitor

Connection (VCAP)”)

pin

(see Section 2.4 “Master Clear (MCLR) Pin”)

Programming™ (ICSP™) and debugging purposes

(see Section 2.5 “ICSP Pins”)

source is used

(see Section 2.6 “External Oscillator Pins”)

REF+/VREF- pins are used when external voltage

reference for ADC module is implemented

Note: The AV

connected independent of the ADC

voltage reference source.

DD and AVSS pins must be

2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of

power supply pins, such as V

SS is required.

AV

Consider the following criteria when using decoupling

capacitors:

• Va lue and type of cap a citor: Recommendation

of 0.1 µF (100 nF), 10-20V. This capacitor should

be a low-ESR and have resonance frequency in

the range of 20 MHz and higher. It is

recommended to use ceramic capacitors.

• Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within

one-quarter inch (6 mm) in length.

• Handling high-frequency noise: If the board is

experiencing high-frequency noise, above tens of

MHz, add a second ceramic-type capacitor in

parallel to the above described decoupling

capacitor. The value of the second capacitor can

be in the range of 0.01 µF to 0.001 µF. Place this

second capacitor next to the primary decoupling

capacitor. In high-speed circuit designs, consider

implementing a decade pair of capacitances as

close to the power and ground pins as possible.

For example, 0.1 µF in parallel with 0.001 µF.

• Maximizing performance: On the board layout

from the power supply circuit, run the power and

return traces to the decoupling capacitors first,

and then to the device pins. This ensures that the

decoupling capacitors are first in the power chain.

Equally important is to keep the trace length

between the capacitor and the power pins to a

minimum, thereby reducing PCB track

inductance.

DD, VSS, AVDD and

2013-2014 Microchip Technology Inc. DS70000689D-page 21

dsPIC33EPXXXGM3XX/6XX/7XX

dsPIC33EP

VDD

VSS

VDD

VSS

VSS

VDD

AVDD

AVSS

VDD

VSS

0.1 µF

Ceramic

0.1 µF

Ceramic

0.1 µF

Ceramic

0.1 µF

Ceramic

C

R

V

DD

MCLR

0.1 µF

Ceramic

VCAP

L1

(1)

R1

10 µF

Tantalum

Note 1: As an option, instead of a hard-wired connection, an

inductor (L1) can be substituted between V

DD and

AV

DD to improve ADC noise rejection. The inductor

impedance should be less than 1 and the inductor

capacity greater than 10 mA.

Where:

f

FCNV

2

------------- -=

f

1

2 LC

-----------------------=

L

1

2fC

--------------------- -

2

=

(i.e., ADC Conversion Rate/2)

Note 1: R 10 k is recommended. A suggested

starting value is 10 k. Ensure that the

MCLR

pin VIH and VIL specifications are met.

2: R1 470 will limit any current flowing into

MCLR

from the external capacitor, C, in the

event of MCLR

pin breakdown due to

Electrostatic Discharge (ESD) or Electrical

Overstress (EOS). Ensure that the MCLR

pin

V

IH and VIL specifications are met.

C

R1

(2)

R

(1)

VDD

MCLR

dsPIC33EP

JP

FIGURE 2-1: RECOMMENDED

MINIMUM CONNECTION

The placement of this capacitor should be close to the

CAP pin. It is recommended that the trace length not

V

exceeds one-quarter inch (6 mm). See Section 30.3

“On-Chip Voltage Regulator” for details.

2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device

functions:

• Device Reset

• Device Programming and Debugging.

During device programming and debugging, the

resistance and capacitance that can be added to the

pin must be considered. Device programmers and

debuggers drive the MCLR

specific voltage levels (V

transitions must not be adversely affected. Therefore,

specific values of R and C will need to be adjusted

based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is

recommended that the capacitor, C, be isolated from

the MCLR

pin during programming and debugging

operations.

Place the components as shown in Figure 2-2 within

one-quarter inch (6 mm) from the MCLR

pin. Consequently,

IH and VIL) and fast signal

pin.

CAP)

CAP pin must not be

2.2.1 TANK CAPACITORS

On boards with power traces running longer than six

inches in length, it is suggested to use a tank capacitor

for integrated circuits including DSCs to supply a local

power source. The value of the tank capacitor should

be determined based on the trace resistance that connects the power supply source to the device, and the

maximum current drawn by the device in the application. In other words, select the tank capacitor so that it

meets the acceptable voltage sag at the device. Typical

values range from 4.7 µF to 47 µF.

2.3 CPU Logic Filter Capacitor

A low-ESR (< 1 Ohms) capacitor is required on the

CAP pin, which is used to stabilize the voltage

V

regulator output voltage. The V

connected to V

than 4.7 µF (10 µF is recommended), 16V connected

to ground. The type can be ceramic or tantalum. See

Section 33.0 “Electrical Characteristics” for

additional information.

DS70000689D-page 22 2013-2014 Microchip Technology Inc.

Connection (V

DD, and must have a capacitor greater

FIGURE 2-2: EXAMPLE OF MCLR PIN

CONNECTIONS

dsPIC33EPXXXGM3XX/6XX/7XX

Main Oscillator

Guard Ring

Guard Trace

Oscillator Pins

2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and

debugging purposes. It is recommended to keep the

trace length between the ICSP connector and the ICSP

pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a

series resistor is recommended, with the value in the

range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the

PGECx and PGEDx pins are not recommended as they

will interfere with the programmer/debugger communications to the device. If such discrete components are

an application requirement, they should be removed

from the circuit during programming and debugging.

Alternatively, refer to the AC/DC characteristics and

timing requirements information in the respective

device Flash programming specification for information

on capacitive loading limits and pin Voltage Input High

IH) and Voltage Input Low (VIL) requirements.

(V

Ensure that the “Communication Channel Select” (i.e.,

PGECx/PGEDx pins) programmed into the device

matches the physical connections for the ICSP to

MPLAB

ICE™.

For more information on MPLAB ICD 2, ICD 3 and

REAL ICE connection requirements, refer to the

following documents that are available on the

Microchip web site:

• “Using MPLAB

• “MPLAB® ICD 3 Design Advisory” DS51764

• “MPLAB® REAL ICE™ In-Circuit Emulator User’s

• “Using MPLAB

®

PICkit™ 3, MPLAB ICD 3, or MPLAB REAL

®

ICD 3” (poster) DS51765

Guide” DS51616

®

REAL ICE™ In-Circuit Emulator”

(poster) DS51749

2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a

high-frequency primary oscillator and a low-frequency

secondary oscillator. For details, see Section 9.0

“Oscillator Configuration” for details.

The oscillator circuit should be placed on the same

side of the board as the device. Also, place the

oscillator circuit close to the respective oscillator pins,

not exceeding one-half inch (12 mm) distance

between them. The load capacitors should be placed

next to the oscillator itself, on the same side of the

board. Use a grounded copper pour around the

oscillator circuit to isolate them from surrounding

circuits. The grounded copper pour should be routed

directly to the MCU ground. Do not run any signal

traces or power traces inside the ground pour. Also, if

using a two-sided board, avoid any traces on the

other side of the board where the crystal is placed. A

suggested layout is shown in Figure 2-3.

FIGURE 2-3: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

2013-2014 Microchip Technology Inc. DS70000689D-page 23

dsPIC33EPXXXGM3XX/6XX/7XX

IPFC

VOUTPUT

ADC Channel

ADC Channel

PWM

k

1

k

2

k

3

FET

dsPIC33EP

VINPUT

Op Amp/

Output

Driver

Comparator

2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and

configured for the device start-up oscillator, the

maximum oscillator source frequency must be limited

to 5 MHz < F

IN < 13.6 MHz to comply with device PLL

start-up conditions. This means that if the external

oscillator frequency is outside this range, the

application must start up in the FRC mode first. The

default PLL settings after a POR with an oscillator

frequency outside this range will violate the device

operating speed.

Once the device powers up, the application firmware

can initialize the PLL SFRs, CLKDIV and PLLDBF to a

suitable value, and then perform a clock switch to the

Oscillator + PLL clock source. Note that clock switching

must be enabled in the device Configuration Word.

2.8 Unused I/Os

Unused I/O pins should be configured as outputs and

driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between V

and unused pins, and drive the output to logic low.

SS

2.9 Application Examples

• Induction heating

• Uninterruptable Power Supplies (UPS)

• DC/AC inverters

• Compressor motor control

• Washing machine 3-phase motor control

• BLDC motor control

• Automotive HVAC, cooling fans, fuel pumps

• Stepper motor control

• Audio and fluid sensor monitoring

• Camera lens focus and stability control

• Speech (playback, hands-free kits, answering

machines, VoIP)

• Consumer audio

• Industrial and building control (security systems

and access control)

• Barcode reading

• Networking: LAN switches, gateways

• Data storage device management

• Smart cards and smart card readers

• Dual motor control

Examples of typical application connections are shown

in Figure 2-4 through Figure 2-8.

FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

DS70000689D-page 24 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

k

1

Op Amp/

k

2

k

7

PWM

PWM

ADC

Channel

ADC

Channel

5V Output

I

5V

12V Input

FET

Driver

dsPIC33EP

Comparator

k

5

k

4

k

3

k

7

Op Amp/Comparator

Op Amp/Comparator

ADC Channel

Op Amp/Comparator

ADC

Channel

PWM

PWM

PWM

PWM

PWM

PWM

3.3V Output

12V Input

FET

Driver

FET

Driver

FET

Driver

dsPIC33EP

k

6

FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

FIGURE 2-6: MULTIPHASE SYNCHRONOUS BUCK CONVERTER

2013-2014 Microchip Technology Inc. DS70000689D-page 25

dsPIC33EPXXXGM3XX/6XX/7XX

VAC

VOUT+

Op Amp/Comparator

PWM

ADC

PWM

|VAC|

k

4

k

3

FET

dsPIC33EP

Driver

V

OUT-

ADC Channel

FET

Driver

k

1

k

2

Op Amp/

Channel

Op Amp/

Comparator

Comparator

3-Phase

Inverter

PWM3H

PWM3L

PWM2H

PWM2L

PWM1H

PWM1L

FLTx

Fault

BLDC

dsPIC33EP

AN3

AN4

AN5

AN2

Demand

Phase Terminal Voltage Feedback

R49 R41 R34

R36

R44

R52

FIGURE 2-7: INTERLEAVED PFC

FIGURE 2-8: BEMF VOLTAGE MEASURED USING THE ADC MODULE

DS70000689D-page 26 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

3.0 CPU

Note 1: This data sheet summarizes the features

of the dsPIC33EPXXXGM3XX/6XX/7XX

family of devices. It is not intended to be a

comprehensive reference source. To complement the information in this data sheet,

refer to the “dsPIC33/PIC24 Family Refer-

ence Manual”, “CPU” (DS70359), which

is available from the Microchip web site

(www.microchip.com).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including

significant support for digital signal processing. The

CPU has a 24-bit instruction word, with a variable

length opcode field. The Program Counter (PC) is

23 bits wide and addresses up to 4M x 24 bits of user

program memory space.

An instruction prefetch mechanism helps maintain

throughput and provides predictable execution. Most

instructions execute in a single-cycle, effective execution rate, with the exception of instructions that change

the program flow, the double-word move (MOV.D)

instruction, PSV accesses and the table instructions.

Overhead-free program loop constructs are supported

using the DO and REPEAT instructions, both of which

are interruptible at any point.

3.1 Registers

The dsPIC33EPXXXGM3XX/6XX/7XX devices have

sixteen 16-bit Working registers in the programmer’s

model. Each of the Working registers can act as a data,

address or address offset register. The 16th Working

register (W15) operates as a Software Stack Pointer for

interrupts and calls.

3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class

of instructions. These two instruction classes are

seamlessly integrated into the architecture and execute from a single execution unit. The instruction set

includes many addressing modes and was designed

for optimum C compiler efficiency.

3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words

or 8 Kbytes and is split into two blocks, referred to as X

and Y data memory. Each memory block has its own

independent Address Generation Unit (AGU). The

MCU class of instructions operate solely through the X

memory AGU, which accesses the entire memory map

as one linear Data Space. On dsPIC33EP devices,

certain DSP instructions operate through the X and Y

AGUs to support dual operand reads, which splits the

data address space into two parts. The X and Y Data

Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map

can optionally be mapped into Program Space at any

16K program word boundary. The program-to-Data

Space mapping feature, known as Program Space

Visibility (PSV), lets any instruction access Program

Space as if it were Data Space. Moreover, the Base

Data Space address is used in conjunction with a Data

Space Read or Write Page register (DSRPAG or

DSWPAG) to form an Extended Data Space (EDS)

address. The EDS can be addressed as 8M words or

16 Mbytes. Refer to “Data Memory” (DS70595) and

“Program Memory” (DS70613) in the “dsPIC33/

PIC24 Family Reference Manual” for more details on

EDS, PSV and table accesses.

On dsPIC33EP devices, overhead-free circular buffers

(Modulo Addressing) are supported in both X and Y

address spaces. The Modulo Addressing removes the

software boundary checking overhead for DSP

algorithms. The X AGU circular addressing can be

used with any of the MCU class of instructions. The X

AGU also supports Bit-Reversed Addressing to greatly

simplify input or output data reordering for radix-2 FFT

algorithms.

3.4 Addressing Modes

The CPU supports these addressing modes:

• Inherent (no operand)

• Relative

•Literal

• Memory Direct

• Register Direct

• Register Indirect

Each instruction is associated with a predefined

addressing mode group, depending upon its functional

requirements. As many as six addressing modes are

supported for each instruction.

2013-2014 Microchip Technology Inc. DS70000689D-page 27

dsPIC33EPXXXGM3XX/6XX/7XX

Instruction

Decode and

Control

16

PCH

16

Program Counter

16-Bit ALU

24

24

24

24

X Data Bus

PCU

16

16

16

Divide

Support

Engine

DSP

ROM Latch

16

Y Data Bus

EA MUX

X RAGU

X WAGU

Y AGU

16

24

16

16

16

16

16

16

16

8

Interrupt

Controller

PSV and Table

Data Access

Control Block

Stack

Control

Logic

Loop

Control

Logic

Data LatchData Latch

Y Data

RAM

X Data

RAM

Address

Latch

Address

Latch

16

Data Latch

16

16

16

X Address Bus

Y Address Bus

24

Literal Data

Program Memory

Address Latch

Power, Reset

and Oscillator

Control Signals

to Various Blocks

Ports

Peripheral

Modules

Modules

PCL

16 x 16

W Register Array

IR

FIGURE 3-1: dsPIC33EPXXXGM3XX/6XX/7XX CPU BLOCK DIAGRAM

DS70000689D-page 28 2013-2014 Microchip Technology Inc.

dsPIC33EPXXXGM3XX/6XX/7XX

3.5 Programmer’s Model

The programmer’s model for the dsPIC33EPXXXGM3XX/

6XX/7XX devices is shown in Figure 3-2. All registers in

the programmer’s model are memory-mapped and can be

manipulated directly by instructions. Table 3-1 lists a

description of each register.

In addition to the registers contained in the

programmer’s model, the dsPIC33EPXXXGM3XX/

6XX/7XX devices contain control registers for Modulo

Addressing and Bit-Reversed Addressing, and

interrupts. These registers are described in subsequent

sections of this document.

All registers associated with the programmer’s model

are memory-mapped, as shown in Table 4-1.

TABLE 3-1: PROGRAMMER’S MODEL REGISTER DESCRIPTIONS

Register(s) Name Description

W0 through W15 Working Register Array

ACCA, ACCB 40-Bit DSP Accumulators

PC 23-Bit Program Counter

SR ALU and DSP Engine Status register

SPLIM Stack Pointer Limit Value register

TBLPAG Table Memory Page Address register

DSRPAG Extended Data Space (EDS) Read Page register

DSWPAG Extended Data Space (EDS) Write Page register

RCOUNT REPEAT Loop Count register

DCOUNT DO Loop Count register

(1)

DOSTARTH

DOENDH, DOENDL DO Loop End Address register (High and Low)

CORCON Contains DSP Engine, DO Loop Control and Trap Status bits

Note 1: The DOSTARTH and DOSTARTL registers are read-only.

, DOSTARTL

(1)

DO Loop Start Address register (High and Low)

2013-2014 Microchip Technology Inc. DS70000689D-page 29

dsPIC33EPXXXGM3XX/6XX/7XX

NOVZ C

TBLPAG

PC23

PC0

7

0

D0D15

Program Counter

Data Table Page Address

STATUS Register

Working/Address

Registers

DSP Operand

Registers

W0 (WREG)

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12

W13

Frame Pointer/W14

Stack Pointer/W15

DSP Address

Registers

AD39 AD0

AD31

DSP

Accumulators

(1)

ACCA

ACCB

DSRPAG

9

0

RA

0

OA

(1)OB(1)SA(1)SB(1)

RCOUNT

15

0

REPEAT Loop Counter

15 0

DO Loop Counter and Stack

DOSTART

23 0

DO Loop Start Address and Stack

0

DOEND

DO Loop End Address and Stack

IPL2 IPL1

SPLIM

Stack Pointer Limit

AD15

23

0

SRL

IPL0

PUSH.s and POP.s shadows

Nested

DO Stack

0

0

OAB

(1)

SAB

(1)

X Data Space Read Page Address

DA

(1)

DC

0

0

0

0

DSWPAG

X Data Space Write Page Address

8