Page 1

DS3883A

BTL 9-Bit Data Transceiver

General Description

The DS3883A is one in a series of transceivers designed

specifically for the implementation of high performance Futurebus+ and proprietary bus interfaces. The DS3883A, is a

BTL 9-bit Transceiver designed to conform to IEEE 1194.1

(Backplane Transceiver Logic—BTL) as specified in the

IEEE 896.2 Futurebus+ specification. Utilization of the

DS3883A simplifies the implementation of byte wide

address/data with parity lines and also may be used for the

Futurebus+ status, tag and command lines.

The DS3883A driver output configuration is an NPN open

collector which allows Wired-OR connection on the bus.

Each driver output incorporates a Schottky diode in series

with its collector to isolate the transistor output capacitance

from the bus thus reducing the bus loading in the inactive

state. The combined output capacitance of the driver and receiver input is less than 5 pF. The driver also has high sink

current capability to comply with the bus loading requirements defined within IEEE 1194.1 BTL specification.

Backplane Transceiver Logic (BTL) is a signaling standard

that was invented and first introduced by National Semiconductor, then developed by the IEEE to enhance the performance of backplane buses. BTL compatible transceivers

feature low output capacitance drivers to minimize bus loading, a 1V nominal signal swing for reduced power consumption and receivers with precision thresholds for maximum

noise immunity. BTL eliminates settling time delays that severely limit TTL bus performance, and thus provide significantly higher bus transfer rates. The backplane bus is intended to be operated with termination resistors (selected to

match the bus impedance) connected to 2.1V at both ends.

The low voltage is typically 1V.

Separate ground pins are provided for each BTL output to

minimize induced ground noise during simultaneous switching.The unique driver circuitry meets the maximum slew rate

of 0.5 V/ns which allows controlled rise and fall times to reduce noise coupling to adjacent lines.The transceiver’s control and driver inputs are designed with high impedance PNP

input structures and are fully TTL compatible.

The receiver is a high speed comparator that utilizes a bandgap reference for precision threshold control allowing maximum noise immunity to the BTL 1V signaling level. Separate

QV

CC

and QGND pins are provided to minimize the effects

of high current switching noise. The output is TRI-STATE

®

and fully TTL compatible.

The DS3883A supports live insertion as defined in 896.2

through the LI (Live Insertion) pin. To implement live insertion the LI pin should be connected to the live insertion

power connector. If this function is not supported the LI pin

must be tied to the V

CC

pin. The DS3883A also provides

glitch free power up/down protection during power sequencing.

The DS3883A has two types of power connections in addition to the LI pin. They are the Logic V

CC(VCC

) and the Quiet

V

CC

(QVCC). There are two logic VCCpins on the DS3883

that provide the supply voltage for the logic and control circuitry. Multiple power pins reduce the effects of package inductance and thereby minimize switching noise. As these

pins are common to the V

CC

bus internal to the device, a

voltage delta should never exist between these pins and the

voltage difference between V

CC

and QVCCshould never ex-

ceed

±

0.5V because of ESD circuitry.

Additionally, the ESD circuitry between the V

CC

pins and all

other pins except for BTL I/O’s and LI pins requires that any

voltage on these pins should not exceed the voltage on V

CC

+ 0.5V.

There are three different types of ground pins on the

DS3883A. They are the logic ground (GND), BTL grounds

(B0GND–B8GND) and the Bandgap reference ground

(QGND). All of these ground reference pins are isolated

within the chip to minimize the effects of high current switching transients. For optimum performance the QGND should

be returned to the connector through a quiet channel that

does not carry transient switching current. The GND and

B0GND–B8GND should be connected to the nearest backplane ground pin with the shortest possible path.

Since many different grounding schemes could be implemented and ESD circuitry exists on the DS3883, it is important to note that any voltage difference between ground pins,

QGND, GND or B0GND–B8GND should not exceed

±

0.5V

including power-up/down sequencing.

When CD (Chip Disable) is high, An and Bn are in a high im-

pedance state. To transmit data (An to Bn) the T/R signal is

high. To receive data (Bn to An) the T/R signal is low.

Features

n 9-bit Inverting BTL transceiver meets IEEE 1194.1

standard on Backplane Transceiver Logic (BTL)

n Supports live insertion

n Glitch free power-up/down protection

n Typically less than 5 pF bus-port capacitance

n Low bus-port voltage swing (typically 1V) at 80 mA

n Open collector bus-port output allows Wired-OR

n Controlled rise and fall time to reduce noise coupling

n TTL compatible driver and control inputs

n Built in bandgap reference with separate QV

CC

and

QGND pins for precise receiver thresholds

n Exceeds 2 kV ESD (Human Body Model)

n Individual bus-port ground pins minimize ground bounce

n Tight skew (1 ns typical)

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

July 1998

DS3883A BTL 9-Bit Data Transceiver

© 1999 National Semiconductor Corporation DS010719 www.national.com

Page 2

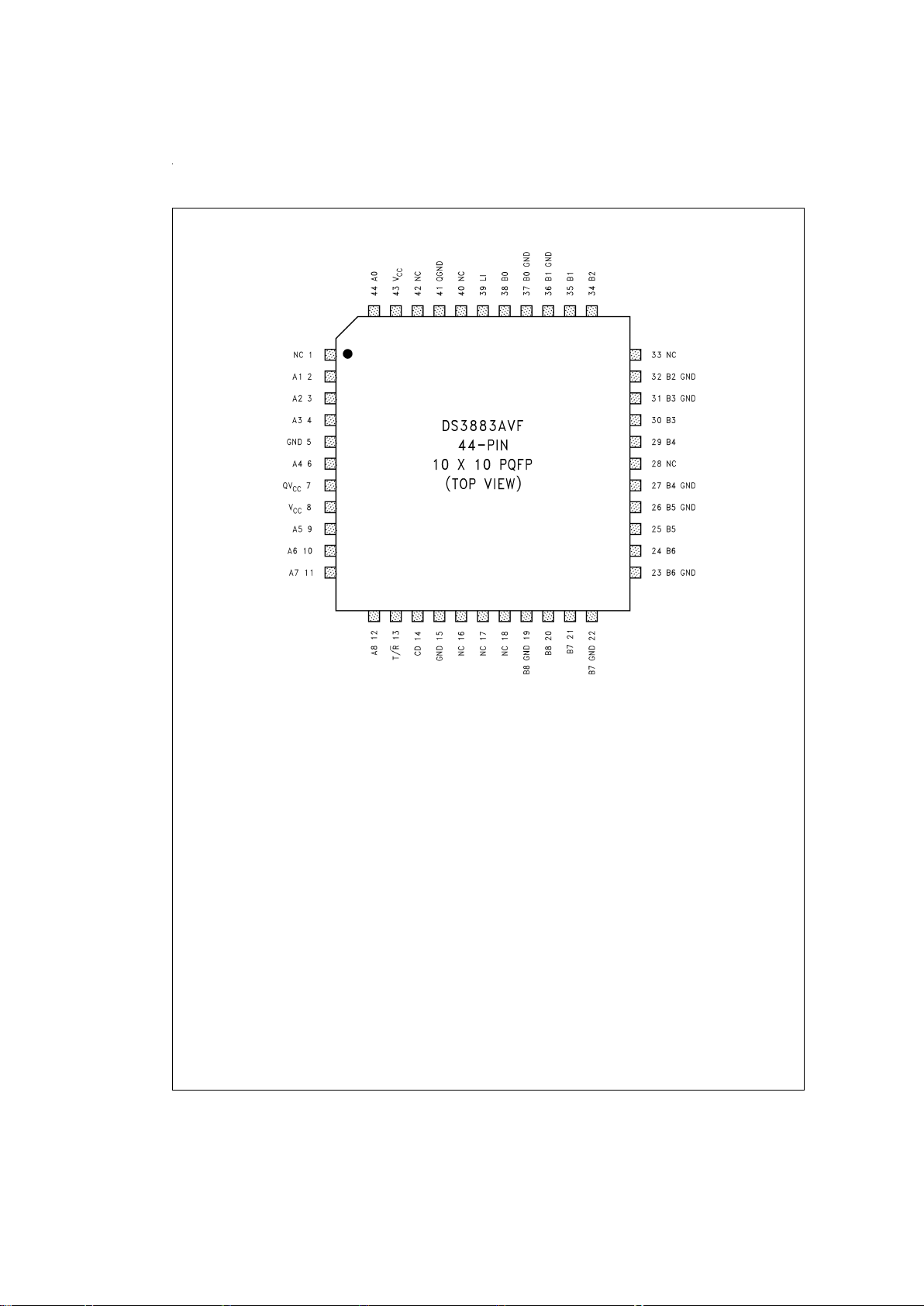

Connection Diagram

DS010719-17

Order Number DS3883AVF

See NS Package Number VF44B

www.national.com 2

Page 3

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage 6.5V

Control Input Voltage 6.5V

Driver Input and Receiver Output 5.5V

Receiver Input Current

±

15 mA

Bus Termination Voltage 2.4V

Power Dissipation at 25˚C

PQFP (VF44B) 1.3W

Derate PQFP Package (VF44B) 11.1 mW/˚C

Storage Temperature Range −65˚C to +150˚C

Lead Temperature

(Soldering, 4 seconds) 260˚C

Recommended Operating

Conditions

Min Max Units

Supply Voltage, V

CC

4.5 5.5 V

Bus Termination Voltage (V

T

) 2.06 2.14 V

Operating Free Air Temperature 0 70 ˚C

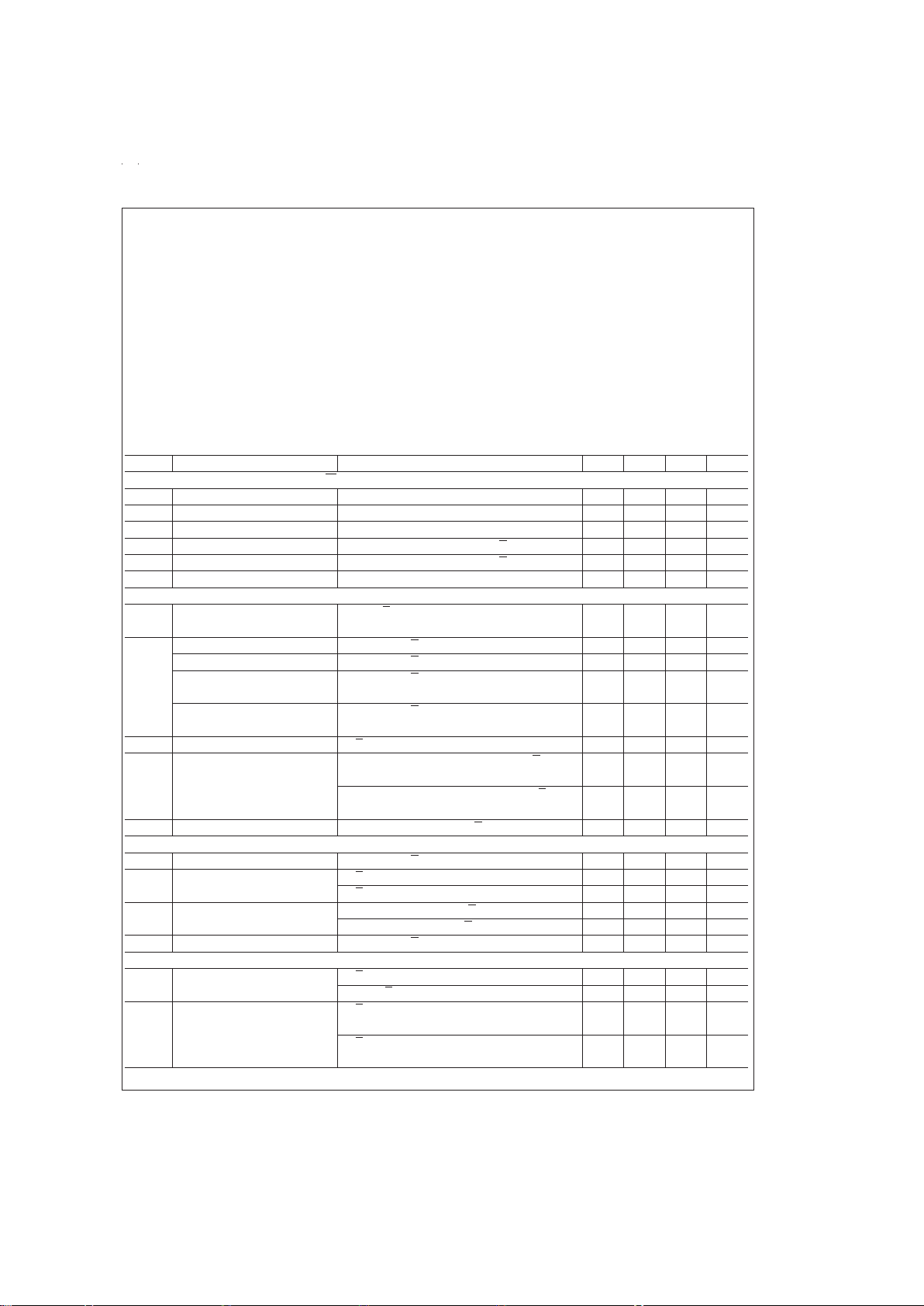

DC Electrical Characteristics (Notes 2, 3)

T

A

=

0˚C to +70˚C, V

CC

=

5V

±

10

%

Symbol Parameter Conditions Min Typ Max Units

DRIVER AND CONTROL INPUT (CD, T/R , An)

V

IH

Minimum Input High Voltage 2.0 V

V

IL

Maximum Input Low Voltage 0.8 V

I

I

Input Leakage Current V

IN

=

V

CC

=

5.5V 250 µA

I

IH

Input High Current V

IN

=

2.4V, AN=CD=0.5V, T/R=2.4V

40 µA

I

IL

Input Low Current V

IN

=

0.5V, AN=CD=0.5V, T/R=2.4V

−100 µA

V

CL

Input Diode Clamp Voltage I

CLAMP

=

−12 mA −1.2 V

DRIVER OUTPUT/RECEIVER INPUT (Bn)

V

OLB

Output Low Bus Voltage An=T/R=2.4V, CD=0.5V 0.75 1.0 1.1 V

(Note 5) I

OL

=

80 mA

I

OFF

Output Off Low Current An=0.5V, T/R=2.4V, Bn=0.75V, CD=0.5V −200 µA

Output Off High Current An=0.5V, T/R=2.4V, Bn=2.1V, CD=0.5V

200 µA

Output Off Low Current — An=0.5V, T/R=CD=2.4V, Bn=0.75V

−50 µA

Chip Disabled

Output Off Low Current — An=0.5V, T/R=CD=2.4V, Bn=2.1V

50 µA

Chip Disabled

V

TH

Receiver Input Threshold T/R=CD=0.5V 1.47 1.55 1.62 V

V

CLP

Positive Clamp Voltage V

CC

=

Max or 0V, I

Bn

=

1 mA, CD=T/R=0V

2.4 3.4 4.5 V

An=0V

V

CC

=

Max or 0V, I

Bn

=

10 mA, CD=T/R=0V

2.9 3.9 5.0 V

An=0V

V

CLN

Negative Clamp Voltage I

CLAMP

=

−12 mA, CD=T/R=0.5V

−1.2 V

RECEIVER OUTPUT (An)

V

OH

Voltage Output High Bn=1.1V, T/R=CD=0.5V, I

OH

=

−2 mA

2.4 3.2 V

V

OL

Voltage Output Low T/R=CD=0.5V, Bn=2.1V, I

OL

=

24 mA

0.35 0.5 V

T/R=CD=0.5V, Bn=2.1V, I

OL

=

8mA

0.35 0.4 V

I

OZ

TRI-STATE Leakage Current An=2.4V, CD=2.4V, T/R=0.5V 10 µA

An=0.5V, CD=2.4V, T/R=0.5V

−10 µA

I

OS

Output Short Circuit Current Bn=1.1V, T/R=CD=0.5V (Note 4) −40 −70 −100 mA

SUPPLY CURRENT

I

CC

Supply Current: Includes T/R=All An Inputs=2.4V, CD=0.5V 62 mA

V

CC

,QVCCand LI CD=T/R=0.5V, All Bn Inputs=2.1V 53 mA

I

LI

Live Insertion Current T/R=CD=An=0.5V, Bn=Open, 2.2 mA

V

CC

=

QV

CC

=

5.5V

T/R=All An=2.4V, CD=0.5V, Bn=Open

4.5 mA

V

CC

=

QV

CC

=

5.5V

www.national.com3

Page 4

DC Electrical Characteristics (Notes 2, 3) (Continued)

Note 1: “Absolute Maximum Ratings” are those beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should

be operated at these limits. The table of “Electrical Characteristics” provides conditions for actual device operation.

Note 2: All input and/or output pins shall notexceed V

CC

+ 0.5V and shall not exceed theabsolute maximum rating at any time, including power-upand power-down.

This prevents the ESD structure frombeing damaged due to excessive currents flowingfrom the input and/or output pins to QV

CC

and VCC. There is a diode between

each input and/or output to V

CC

which is forward biased when incorrect sequencing is applied. LI and Bn pins do not have power sequencing requirements with re-

spect to V

CC

and QVCC.

Note 3: All currentsinto device pins are positive;all currents out of device pins are negative. All voltages are referencedto device ground unless otherwisespecified.

All typical values are specified under these conditions: V

CC

=

5V and T

A

=

25˚C, unless otherwise stated.

Note 4: Only one output should be shorted at a time, and duration of the short should not exceed one second.

Note 5: Referenced to appropriate signal ground. Do not exceed maximum power dissipation of package.

AC Electrical Characteristics (Note 6)

T

A

=

0˚C to +70˚C, V

CC

=

5V

±

10

%

Symbol Parameter Conditions Min Typ Max Units

DRIVER

t

PHL

An to Bn Propagation Delay CD=0V, T/ R=3V 1 3.5 6 ns

t

PLH

(

Figure 1

and

Figure 2

) 1 3.5 6 ns

t

PHL

CD to Bn Enable Time T/R=An=3V 369ns

t

PLH

Disable Time (

Figure 1

and

Figure 3

) 2.5 5 8 ns

t

PHL

T/R to Bn Enable Time (

Figure 8

and

Figure 9

) 9 13.5 18 ns

t

PLH

Disable Time CD=0V 2 6 10 ns

t

r

Transition Time— Rise/Fall (

Figure 1

and

Figure 2

) 1 2.5 4.5 ns

t

f

20%to 80

%

CD=0V, T/R=3V (Note 10) 1 2 4.5 ns

SR Slew Rate is Calculated (

Figure 1

and

Figure 2

) (Note 10) 0.5 V/ns

from 1.3V to 1.8V CD=0V T/R=3V

t

SKEW

An to Bn Skew (Same Package) (Note 7) 1 3.5 ns

RECEIVER

t

PHL

Bn to An CD=T/ R=0V 247ns

t

PLH

(

Figure 4

and

Figure 5

) 1.5 4.5 7.5 ns

t

PLZ

CD to An Disable Time Bn=2.1V, T/R=0V 4 8 12 ns

t

PZL

Enable Time (

Figure 6

and

Figure 7

) 2.5 6 9 ns

t

PHZ

Disable Time Bn=1.1V, T/R=0V 3 6.5 10 ns

t

PZH

Enable Time (

Figure 6

and

Figure 7

)2610ns

t

PLZ

T/R to An Disable Time CD=0V Bn=2.1V 3 7 12 ns

t

PZL

Enable Time (

Figure 8

and

Figure 9

) 4 10 16 ns

t

PHZ

Disable Time Bn=1.1V, CD=0V 2 6.5 10 ns

t

PZH

Enable Time (

Figure 6

and

Figure 7

)3711ns

t

SKEW

Bn to An Skew (Same Package) (Note 7) 1 3.5 ns

PARAMETERS NOT TESTED

C

output

BTL Output Capacitance (Note 8) 5 pF

t

NR

Noise Rejection (Note 9) 1 ns

Note 6: Input waveforms shall have a rise/fall time of 3 ns. Propagation delays are measured with a single output switching.

Note 7: t

SKEW

is an absolute value defined as differences seen in propagation delays between drivers in the same package with identical load conditions.

Note 8: The parameter is tested using TDR techniques described in 1194.0 BTL backplane Design Guide.

Note 9: This parameter is tested during device characterization. The measurement revealed that the part will reject 1 ns pulse widths.

Note 10: Futurebus+ transceiversare required to limit bus signalrise and fall times to no faster than 0.5 V/ns, measured between 1.3V and 1.8V (approximately 20

%

to 80%of nominal voltage swing). The rise and fall times are measured with a transceiver loading equivalent to 12.5Ω tied to +2.1V DC.

www.national.com 4

Page 5

Pin Description

Pin Name Number Input/ Description

of Pins Output

A0–A8 9 I/O TTL TRI-STATE receiver output and driver input

B0–B8 9 I/O BTL receiver input and driver output

B0GND–B8GND 9 NA Parallel driver grounds reduce ground bounce due to high current

switching of driver outputs. (Note 11)

CD 1 I Chip Disable

GND 2 NA Ground for switching circuits. (Note 11)

LI 1 NA Power supply for live insertion. Boards that require live insertion should

connect LI to the live insertion pin on the connector. (Note 12)

NC 8 NA No Connect

QGND 1 NA Ground for receiver input bandgap reference and non-switching circuits.

(Note 11)

QV

CC

1NAV

CC

supply for bandgap reference and non-switching circuits. (Note 12)

T/R

1 I Transmit/Receive — transmit (An to Bn), receive (Bn to An)

V

CC

2NAV

CC

supply for switching circuits. (Note 12)

Note 11: The multiplicity of parallel ground paths reduces the effective inductance of bonding wires and leads, which then reduces the noise caused by transients

on the ground path. The various ground pins can be tied together provided that the external ground has low inductance. (i.e., ground plane with power pins and many

signal pins connected to the backplane ground.) If the external ground floats considerably during transients, precautionary steps should be taken to prevent QGND

from moving with reference to the backplane ground. The receiver threshold should have the same ground reference as the signal coming from the backplane. A voltage offset between their grounds will degrade the noise margin.

Note 12: The same considerations for ground are used for V

CC

in reducing lead inductance (see (Note 11) ). QVCCand VCCshould be tied together externally. If

live insertion is not supported, the LI pin can be tied together with QV

CC

and VCC.

CD T/R An Bn (BTL)

HXZ H

LLL H

LLH L

LHH L

LHL H

X

=

High or low logic state

Z=High impedance state

L=Low state

H=High state

Package Thermal Characteristics

Linear Feet per

Minute Air Flow

(LFPM)

θ

JA

(˚C/W)

44-Pin

PQFP

082

225 68

500 60

900 53

Note 13: The above values are typical values and are different from the Absolute Maximum Rating values, which include guardbands.

www.national.com5

Page 6

Logic Diagram

DS010719-1

www.national.com 6

Page 7

Test Circuit and Timing Waveforms

DS010719-3

FIGURE 1. Driver Propagation Delay Set-Up

DS010719-4

FIGURE 2. Driver: An to Bn, SR

DS010719-5

FIGURE 3. Driver: CD to Bn

DS010719-6

Switch Position

t

PLH

t

PHL

S1 Open Close

FIGURE 4. Receiver Propagation Delay Set-Up

DS010719-7

FIGURE 5. Receiver: Bn to An

www.national.com7

Page 8

Test Circuit and Timing Waveforms (Continued)

DS010719-8

Switch Position

t

PZL

t

PZH

t

PLZ

t

PHZ

S1 Close Open

S2 Open Close

FIGURE 6. Receiver Enable/Disable Set-Up

DS010719-9

FIGURE 7. Receiver: CD to An, T/R to An (t

PHZ

and t

PZH

only)

DS010719-18

FIGURE 8. T/R to An, T/R to Bn

DS010719-19

FIGURE 9.

T/R to Bn (t

PHL

and t

PLH

only),

T/R to An (t

PZL

and t

PLZ

only)

www.national.com 8

Page 9

Physical Dimensions inches (millimeters) unless otherwise noted

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant

into the body, or (b) support or sustain life, and

whose failure to perform when properly used in

accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a

significant injury to the user.

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

National Semiconductor

Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

National Semiconductor

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

www.national.com

Note: All dimensions in millimeters

44-Lead Plastic Quad Flatpak

Order Number DS3883AVF

NS Package Number VF44B

DS3883A BTL 9-Bit Data Transceiver

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Loading...

Loading...