Page 1

January 17, 2008

DS25CP102

3.125 Gbps 2X2 LVDS Crosspoint Switch with Transmit

Pre-Emphasis and Receive Equalization

DS25CP102 3.125 Gbps 2X2 LVDS Crosspoint Switch with Pre-Emphasis and Equalization

General Description

The DS25CP102 is a 3.125 Gbps 2x2 LVDS crosspoint switch

optimized for high-speed signal routing and switching over

lossy FR-4 printed circuit board backplanes and balanced cables. Fully differential signal paths ensure exceptional signal

integrity and noise immunity. The non-blocking architecture

allows connections of any input to any output or outputs.

The DS25CP102 features two levels (Off and On) of transmit

pre-emphasis (PE) and two levels (Off and On) of receive

equalization (EQ).

Wide input common mode range allows the switch to accept

signals with LVDS, CML and LVPECL levels; the output levels

are LVDS. A very small package footprint requires a minimal

space on the board while the flow-through pinout allows easy

board layout. Each differential input and output is internally

terminated with a 100Ω resistor to lower device insertion and

return losses, reduce component count and further minimize

board space.

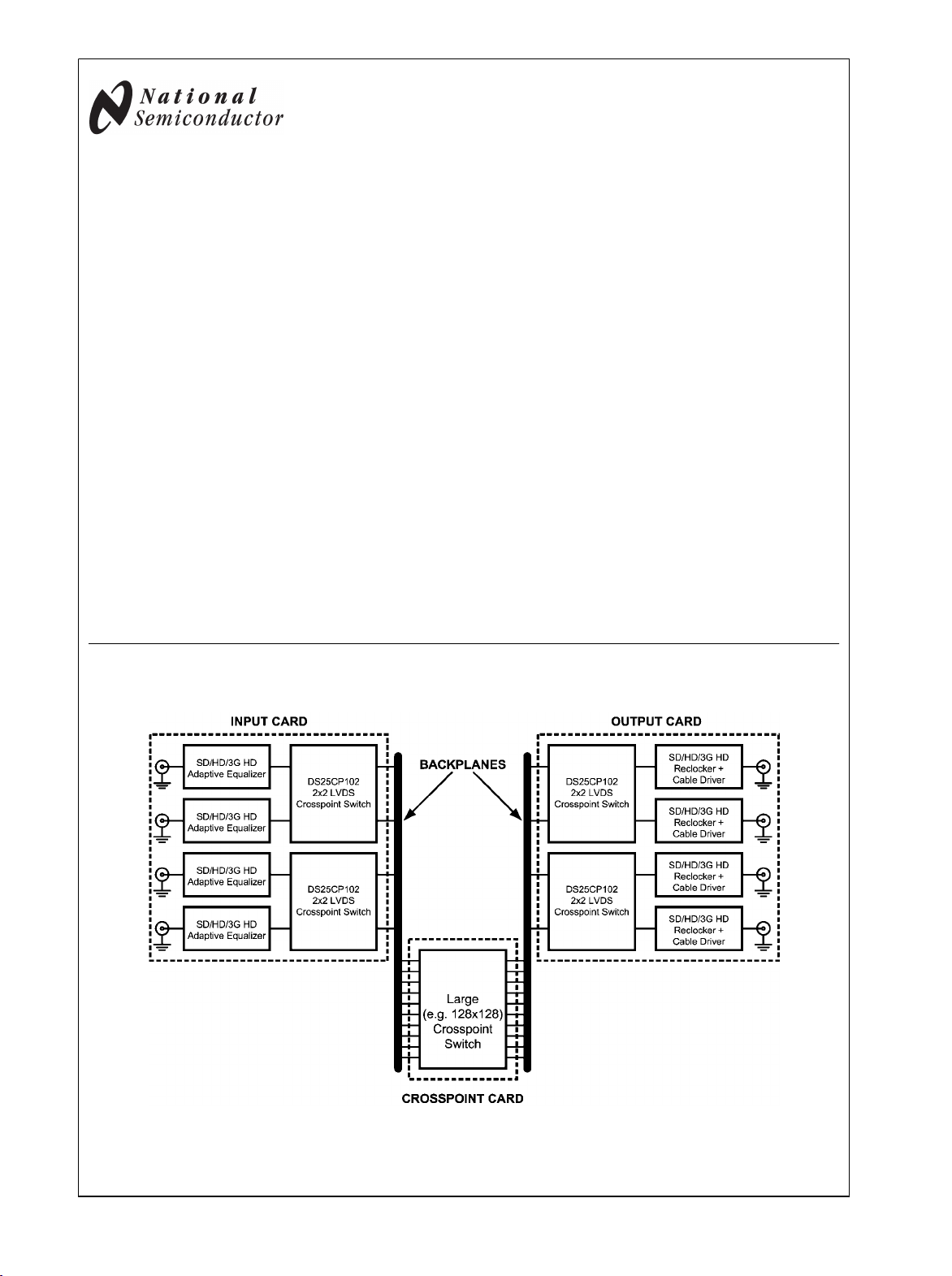

Typical Application

Features

DC - 3.125 Gbps low jitter, low skew, low power operation

■

Pin configurable, fully differential, non-blocking

■

architecture

Pin selectable transmit pre-emphasis and receive

■

equalization eliminate data dependant jitter

Wide Input Common Mode Voltage Range allows DC-

■

coupled interface to CML and LVPECL drivers

On-chip 100Ω input and output termination minimizes

■

insertion and return losses, reduces component count and

minimizes board space

8 kV ESD on LVDS I/O pins protects adjoining

■

components

Small 4 mm x 4 mm LLP-16 space saving package

■

Applications

High-speed channel select applications

■

Clock and data buffering and muxing

■

OC-48 / STM-16

■

SD/HD/3GHD SDI Routers

■

30008003

© 2008 National Semiconductor Corporation 300080 www.national.com

Page 2

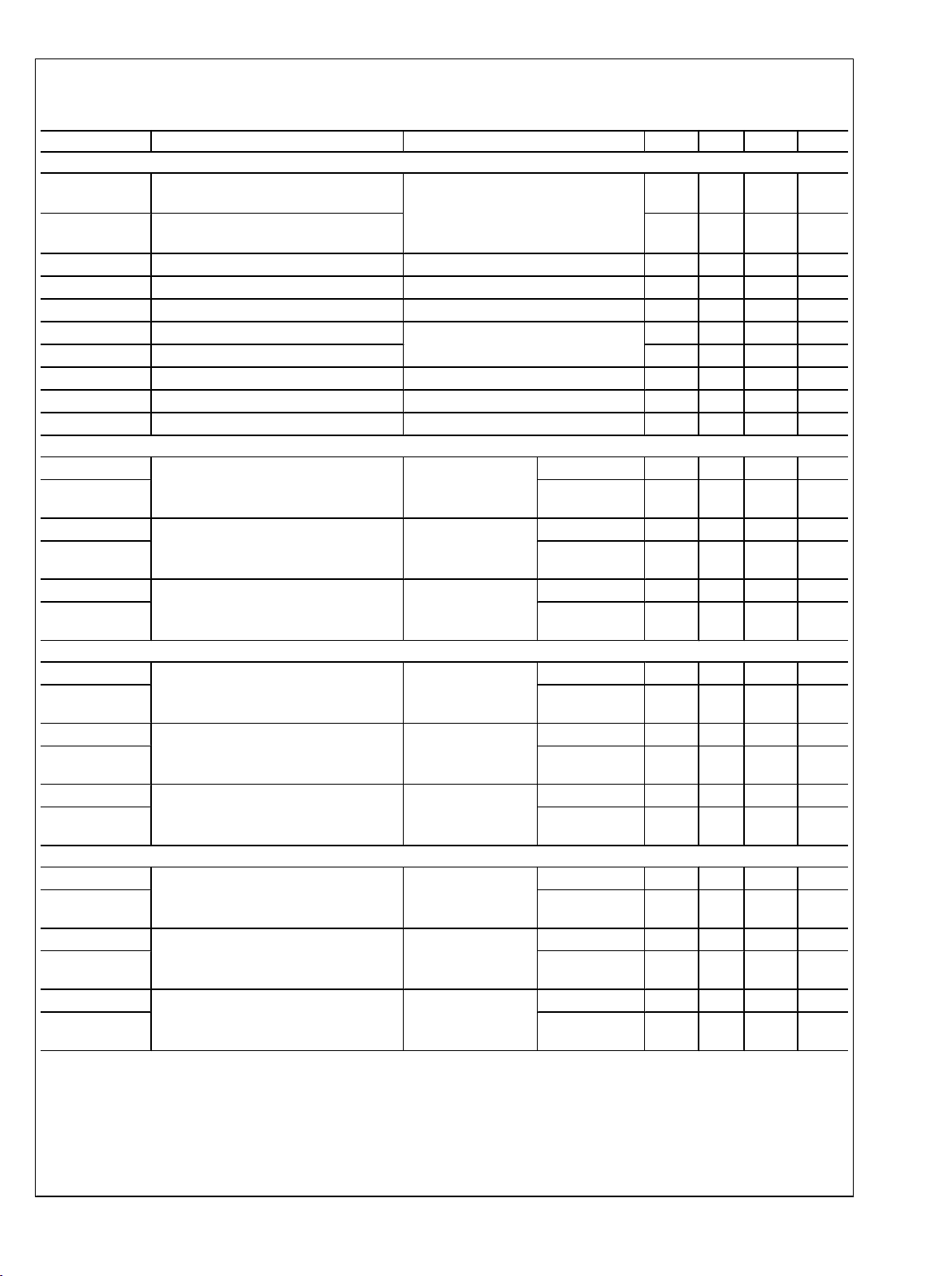

Ordering Code

NSID Function Available Equalization

DS25CP102

DS25CP102TSQ Crosspoint Switch Off / On Off / On

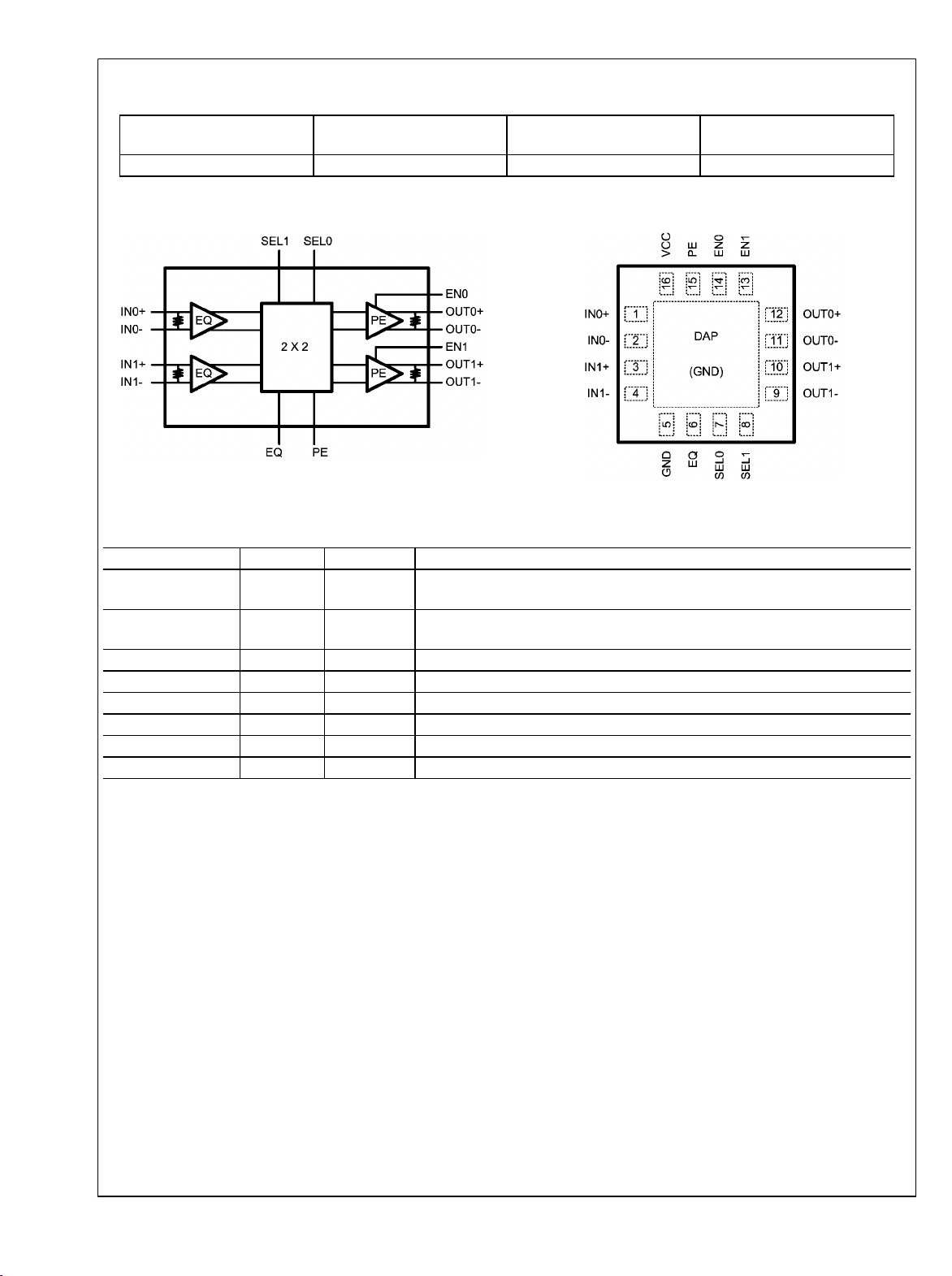

Block Diagram

30008001

Connection Diagram

Levels

Available Pre-Emphasis

Levels

30008002

Pin Descriptions

Pin Name Pin Number I/O, Type Pin Description

IN0+, IN0- ,

IN1+, IN1-

OUT0+, OUT0-,

OUT1+, OUT1-

SEL0, SEL1 7, 8 I, LVCMOS Switch configuration pins. There is a 20k pulldown resistor on this pin.

EN0, EN1 14, 13 I, LVCMOS Output enable pins. There is a 20k pulldown resistor on this pin.

PE 15 I, LVCMOS Transmit Pre-Emphasis select pin. There is a 20k pulldown resistor on this pin.

EQ 6 I, LVCMOS Receive Equalizaton select pin. There is a 20k pulldown resistor on this pin.

VDD 16 Power Power supply pin.

GND 5, DAP Power Ground pin and Device Attach Pad (DAP) ground.

1, 2,

3, 4

12, 11,

10, 9

I, LVDS Inverting and non-inverting high speed LVDS input pins.

O, LVDS Inverting and non-inverting high speed LVDS output pins.

www.national.com 2

Page 3

Absolute Maximum Ratings (Note 4)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage −0.3V to +4V

LVCMOS Input Voltage −0.3V to (VCC + 0.3V)

LVDS Input Voltage −0.3V to +4V

LVDS Differential Input Voltage 0V to 1.0V

LVDS Output Voltage −0.3V to (VCC + 0.3V)

LVDS Differential Output Voltage 0V to 1.0V

LVDS Output Short Circuit Current

Duration

Junction Temperature +150°C

Storage Temperature Range −65°C to +150°C

Lead Temperature Range

Soldering (4 sec.) +260°C

Maximum Package Power Dissipation at 25°C

SQA Package 2.99W

Derate SQA Package 23.9 mW/°C above +25°C

5 ms

Package Thermal Resistance

θ

θ

JA

JC

+41.8°C/W

+6.9°C/W

ESD Susceptibility

HBM (Note 1)

MM (Note 2)

CDM (Note 3)

Note 1: Human Body Model, applicable std. JESD22-A114C

Note 2: Machine Model, applicable std. JESD22-A115-A

Note 3: Field Induced Charge Device Model, applicable std.

JESD22-C101-C

≥8 kV

≥250V

≥1250V

Recommended Operating Conditions

Min Typ Max Units

Supply Voltage (VCC) 3.0 3.3 3.6 V

Receiver Differential Input

Voltage (VID)

Operating Free Air

Temperature (TA)

0 1 V

−40 +25 +85 °C

DC Electrical Characteristics (Notes 5, 6, 7)

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Units

LVCMOS DC SPECIFICATIONS

V

IH

V

IL

I

IH

I

IL

V

CL

LVDS INPUT DC SPECIFICATIONS

V

ID

V

TH

V

TL

V

CMR

High Level Input Voltage 2.0 V

CC

Low Level Input Voltage GND 0.8 V

High Level Input Current VIN = 3.6V

40 175 250

VCC = 3.6V

Low Level Input Current VIN = GND

0 ±10

VCC = 3.6V

Input Clamp Voltage ICL = −18 mA, VCC = 0V −0.9 −1.5 V

Input Differential Voltage 0 1 V

Differential Input High Threshold

Differential Input Low Threshold

VCM = +0.05V or VCC-0.05V

0 +100 mV

−100 0 mV

Common Mode Voltage Range VID = 100 mV 0.05 VCC -

0.05

V

μA

μA

V

Page 4

Symbol Parameter Conditions Min Typ Max Units

LVDS OUTPUT DC SPECIFICATIONS

V

OD

DS25CP102

ΔV

V

OS

ΔV

I

OS

C

OUT

R

OUT

Differential Output Voltage

Change in Magnitude of VOD for Complimentary

OD

Output States

Offset Voltage

Change in Magnitude of VOS for Complimentary

OS

Output States

RL = 100Ω

RL = 100Ω

250 350 450 mV

-35 35 mV

1.05 1.2 1.375 V

-35 35 mV

Output Short Circuit Current (Note 8) OUT to GND -35 -55 mA

OUT to V

CC

Output Capacitance Any LVDS Output Pin to GND

Output Termination Resistor Between OUT+ and OUT-

7 55 mA

1.2 pF

100

SUPPLY CURRENT

I

I

CC

CCZ

Supply Current PE = OFF, EQ = OFF 77 90 mA

Supply Current with Outputs Disabled EN0 = EN1 = 0 23 29 mA

Note 4: “Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability

and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in

the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the

device should not be operated beyond such conditions.

Note 5: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified

or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 6: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except VOD and

ΔVOD.

Note 7: Typical values represent most likely parametric norms for VCC = +3.3V and TA = +25°C, and at the Recommended Operation Conditions at the time of

product characterization and are not guaranteed.

Note 8: Output short circuit current (IOS) is specified as magnitude only, minus sign indicates direction only.

Ω

www.national.com 4

Page 5

AC Electrical Characteristics (Note 11)

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 9, 10)

Symbol Parameter Conditions Min Typ Max Units

LVDS OUTPUT AC SPECIFICATIONS

t

PLHD

t

PHLD

t

SKD1

t

SKD2

t

SKD3

t

LHT

t

HLT

t

ON

t

OFF

t

SEL

JITTER PERFORMANCE WITH EQ = Off, PE = Off (Figure 5)

t

RJ1

t

RJ2

t

DJ1

t

DJ2

t

TJ1

t

TJ2

JITTER PERFORMANCE WITH EQ = Off, PE = On (Figures 6, 9)

t

RJ1B

t

RJ2B

t

DJ1B

t

DJ2B

t

TJ1B

t

TJ2B

JITTER PERFORMANCE WITH EQ = On, PE = Off (Figures 7, 9)

t

RJ1D

t

RJ2D

t

DJ1D

t

DJ2D

t

TJ1D

t

TJ2D

Differential Propagation Delay Low to

High

Differential Propagation Delay High to

RL = 100Ω

365 500 ps

345 500 ps

Low

Pulse Skew |t

PLHD

− t

| (Note 12) 20 55 ps

PHLD

Channel to Channel Skew (Note 13) 12 25 ps

Part to Part Skew , (Note 14) 50 150 ps

Rise Time

Fall Time 65 120 ps

Output Enable Time

Output Disable Time

Select Time

Random Jitter (RMS Value)

No Test Channels

(Note 15)

Deterministic Jitter (Peak to Peak)

No Test Channels

(Note 16)

Total Jitter (Peak to Peak)

No Test Channels

(Note 17)

Random Jitter (RMS Value)

Test Channel B

(Note 15)

Deterministic Jitter (Peak to Peak)

Test Channel B

(Note 16)

Total Jitter (Peak to Peak)

Test Channel B

(Note 17)

Random Jitter (RMS Value)

Test Channel D

(Note 15)

Deterministic Jitter (Peak to Peak)

Test Channel D

(Note 16)

Total Jitter (Peak to Peak)

Test Channel D

(Note 17)

RL = 100Ω

ENn = LH to output active

ENn = HL to output inactive

SELn LH or HL to output

VID = 350 mV

VCM = 1.2V

Clock (RZ)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

2.5 Gbps 0.5 1 ps

3.125 Gbps 0.5 1 ps

2.5 Gbps 6 22 ps

3.125 Gbps 6 22 ps

2.5 Gbps 0.03 0.08

3.125 Gbps 0.05 0.11

2.5 Gbps 0.5 1 ps

3.125 Gbps 0.5 1 ps

2.5 Gbps 3 12 ps

3.125 Gbps 3 12 ps

2.5 Gbps 0.03 0.06

3.125 Gbps 0.04 0.09

2.5 Gbps 0.5 1 ps

3.125 Gbps 0.5 1 ps

2.5 Gbps 16 24 ps

3.125 Gbps 12 24 ps

2.5 Gbps 0.07 0.11

3.125 Gbps 0.07 0.11

65 120 ps

7 20

5 12 ns

3.5 12 ns

UI

UI

UI

UI

UI

UI

DS25CP102

μs

P-P

P-P

P-P

P-P

P-P

P-P

5 www.national.com

Page 6

Symbol Parameter Conditions Min Typ Max Units

JITTER PERFORMANCE WITH EQ = On, PE = On (Figures 8, 9)

t

RJ1BD

t

DS25CP102

RJ2BD

Random Jitter (RMS Value)

Input Test Channel D

Output Test Channel B

VID = 350 mV

VCM = 1.2V

Clock (RZ)

2.5 Gbps 0.5 1 ps

3.125 Gbps 0.5 1 ps

(Note 15)

t

DJ1BD

t

DJ2BD

Deterministic Jitter (Peak to Peak)

Input Test Channel D

Output Test Channel B

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 14 31 ps

3.125 Gbps 6 21 ps

(Note 16)

t

TJ1BD

t

TJ2BD

Total Jitter (Peak to Peak)

Input Test Channel D

Output Test Channel B

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

2.5 Gbps 0.08 0.15

3.125 Gbps 0.10 0.16

(Note 17)

Note 9: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified

or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 10: Typical values represent most likely parametric norms for VCC = +3.3V and TA = +25°C, and at the Recommended Operation Conditions at the time of

product characterization and are not guaranteed.

Note 11: Specification is guaranteed by characterization and is not tested in production.

Note 12: t

going edge of the same channel.

Note 13: t

all outputs).

Note 14: t

devices at the same VCC and within 5°C of each other within the operating temperature range.

Note 15: Measured on a clock edge with a histogram and an acummulation of 1500 histogram hits. Input stimulus jitter is subtracted geometrically.

Note 16: Tested with a combination of the 1100000101 (K28.5+ character) and 0011111010 (K28.5- character) patterns. Input stimulus jitter is subtracted

algebraically.

Note 17: Measured on an eye diagram with a histogram and an acummulation of 3500 histogram hits. Input stimulus jitter is subtracted.

, |t

− t

SKD1

PLHD

, Channel to Channel Skew, is the difference in propagation delay (t

SKD2

, Part to Part Skew, is defined as the difference between the minimum and maximum differential propagation delays. This specification applies to

SKD3

|, Pulse Skew, is the magnitude difference in differential propagation delay time between the positive going edge and the negative

PHLD

or t

PLHD

) among all output channels in Broadcast mode (any one input to

PHLD

UI

UI

P-P

P-P

www.national.com 6

Page 7

DC Test Circuits

FIGURE 1. Differential Driver DC Test Circuit

AC Test Circuits and Timing Diagrams

30008020

30008021

FIGURE 2. Differential Driver AC Test Circuit

Page 8

Pre-Emphasis and Equalization Test Circuits

DS25CP102

FIGURE 5. Jitter Performance Test Circuit

30008029

FIGURE 6. Pre-Emphasis Performance Test Circuit

FIGURE 7. Equalization Performance Test Circuit

30008027

30008026

www.national.com 8

Page 9

FIGURE 8. Pre-Emphasis and Equalization Performance Test Circuit

DS25CP102

30008030

30008028

FIGURE 9. Test Channel Block Diagram

Test Channel Loss Characteristics

The test channel was fabricated with Polyclad PCL-FR-370-

stant of 3.7 and Loss Tangent of 0.02). The edge coupled

differential striplines have the following geometries: Trace

Width (W) = 5 mils, Gap (S) = 5 mils, Height (B) = 16 mils.

Laminate/PCL-FRP-370 Prepreg materials (Dielectric con-

Test Channel Length

(inches)

500 MHz 750 MHz 1000 MHz 1250 MHz 1500 MHz 1560 MHz

Insertion Loss (dB)

A 10 -1.2 -1.7 -2.0 -2.4 -2.7 -2.8

B 20 -2.6 -3.5 -4.1 -4.8 -5.5 -5.6

C 30 -4.3 -5.7 -7.0 -8.2 -9.4 -9.7

D 15 -1.6 -2.2 -2.7 -3.2 -3.7 -3.8

E 30 -3.4 -4.5 -5.6 -6.6 -7.7 -7.9

F 60 -7.8 -10.3 -12.4 -14.5 -16.6 -17.0

9 www.national.com

Page 10

Functional Description

The DS25CP102 is a 3.125 Gbps 2x2 LVDS digital crosspoint

switch optimized for high-speed signal routing and switching

DS25CP102

SEL1 SEL0 OUT1 OUT0

0 0 IN0 IN0

0 1 IN0 IN1

1 0 IN1 IN0

1 1 IN1 IN1

EN1 EN0 OUT1 OUT0

0 0 Disabled Disabled

0 1 Disabled Enabled

1 0 Enabled Disabled

1 1 Enabled Enabled

TABLE 1. Switch Configuration Truth Table

TABLE 2. Output Enable Truth Table

over lossy FR-4 printed circuit board backplanes and balanced cables.

In addition, the DS25CP102 has a pre-emphasis control pin

for switching the transmit pre-emphasis to ON and OFF setting and an equalization control pin for switching the receive

Transmit Pre-Emphasis Truth Table

OUTPUTS OUT0 and OUT1

CONTROL Pin (PE) State Pre-Emphasis Level

0 OFF

1 ON

Transmit Pre-Emphasis Level Selection

Receive Equalization Truth Table

INPUTS IN0 and IN1

CONTROL Pin (EQ) State Equalization Level

0 OFF

1 ON

Receive Equalization Level Selection

equalization to ON and OFF setting. The following are the

transmit pre-emphasis and receive equalization truth tables.

www.national.com 10

Page 11

DS25CP102

Input Interfacing

The DS25CP102 accepts differential signals and allows simple AC or DC coupling. With a wide common mode range, the

DS25CP102 can be DC-coupled with all common differential

Typical LVDS Driver DC-Coupled Interface to DS25CP102 Input

drivers (i.e. LVPECL, LVDS, CML). The following three figures illustrate typical DC-coupled interface to common differential drivers. Note that the DS25CP102 inputs are internally

terminated with a 100Ω resistor.

30008031

Typical CML Driver DC-Coupled Interface to DS25CP102 Input

Typical LVPECL Driver DC-Coupled Interface to DS25CP102 Input

30008032

30008033

11 www.national.com

Page 12

Output Interfacing

The DS25CP102 outputs signals that are compliant to the

LVDS standard. Its outputs can be DC-coupled to most common differential receivers. The following figure illustrates typ-

DS25CP102

ical DC-coupled interface to common differential receivers

and assumes that the receivers have high impedance inputs.

While most differential receivers have a common mode input

range that can accomodate LVDS compliant signals, it is recommended to check respective receiver's data sheet prior to

implementing the suggested interface implementation.

Typical DS25CP102 Output DC-Coupled Interface to an LVDS, CML or LVPECL Receiver

30008034

www.national.com 12

Page 13

Typical Performance

DS25CP102

Total Jitter as a Function of Data Rate

Total Jitter as a Function of Input Common Mode Voltage

30008050

30008058

Residual Jitter as a Function of Data Rate, FR4 Stripline

30008052

Length and EQ Level

Supply Current as a Function of Data Rate and PE Level

30008057

Residual Jitter as a Function of Data Rate, FR4 Stripline

30008051

Length and PE Level

13 www.national.com

Page 14

DS25CP102

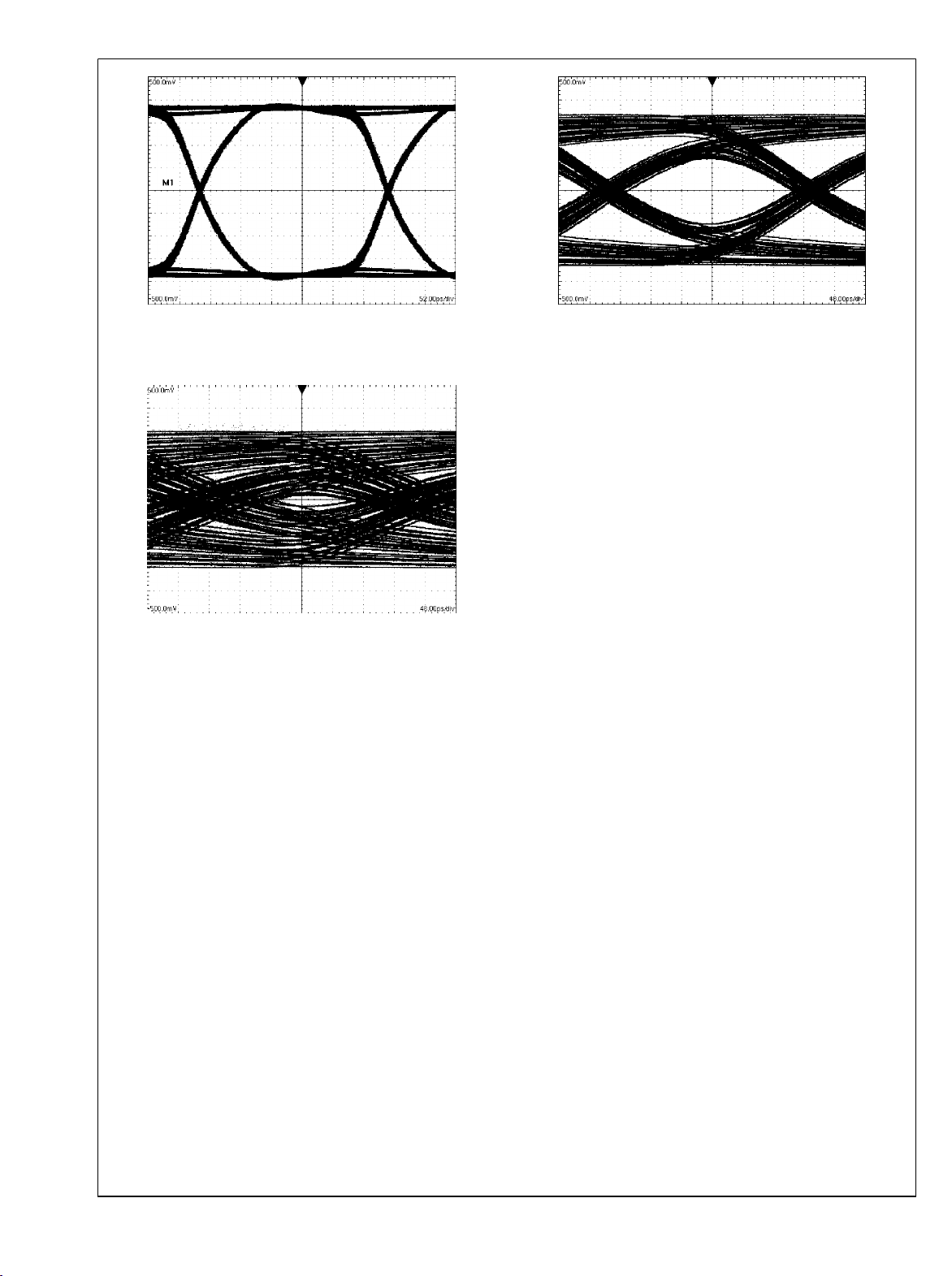

A 3.125 Gbps NRZ PRBS-7 without PE or EQ

30008060

After 2" Differential FR-4 Stripline

H: 50 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-7 without PE or EQ

30008061

After 40" Differential FR-4 Stripline

H: 50 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-7 with PE

After 40" Differential FR-4 Stripline

H: 50 ps / DIV, V: 100 mV / DIV

30008062

www.national.com 14

Page 15

Physical Dimensions inches (millimeters) unless otherwise noted

DS25CP102

Order Number DS25CP102TSQ

(See AN-1187 for PCB Design and Assembly Recommendations)

NS Package Number SQA16A

15 www.national.com

Page 16

Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

Products Design Support

Amplifiers www.national.com/amplifiers WEBENCH www.national.com/webench

Audio www.national.com/audio Analog University www.national.com/AU

Clock Conditioners www.national.com/timing App Notes www.national.com/appnotes

Data Converters www.national.com/adc Distributors www.national.com/contacts

Displays www.national.com/displays Green Compliance www.national.com/quality/green

Ethernet www.national.com/ethernet Packaging www.national.com/packaging

Interface www.national.com/interface Quality and Reliability www.national.com/quality

LVDS www.national.com/lvds Reference Designs www.national.com/refdesigns

Power Management www.national.com/power Feedback www.national.com/feedback

Switching Regulators www.national.com/switchers

LDOs www.national.com/ldo

LED Lighting www.national.com/led

PowerWise www.national.com/powerwise

Serial Digital Interface (SDI) www.national.com/sdi

Temperature Sensors www.national.com/tempsensors

Wireless (PLL/VCO) www.national.com/wireless

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION

(“NATIONAL”) PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY

OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO

SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS,

IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS

DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT

NATIONAL’S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL

PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR

APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND

APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE

NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO

LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE

AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR

PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY

RIGHT.

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and

whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected

to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform

can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other

brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor

DS25CP102 3.125 Gbps 2X2 LVDS Crosspoint Switch with Pre-Emphasis and Equalization

www.national.com

Americas Technical

Support Center

Email:

new.feedback@nsc.com

Tel: 1-800-272-9959

National Semiconductor Europe

Technical Support Center

Email: europe.support@nsc.com

German Tel: +49 (0) 180 5010 771

English Tel: +44 (0) 870 850 4288

National Semiconductor Asia

Pacific Technical Support Center

Email: ap.support@nsc.com

National Semiconductor Japan

Technical Support Center

Email: jpn.feedback@nsc.com

Loading...

Loading...