Page 1

TL/F/11118

DP8430V/31V/32V-33 microCMOS Programmable

256k/1M/4M Dynamic RAM Controller/Drivers

July 1993

DP8430V/31V/32V-33 microCMOS Programmable

256k/1M/4M Dynamic RAM Controller/Drivers

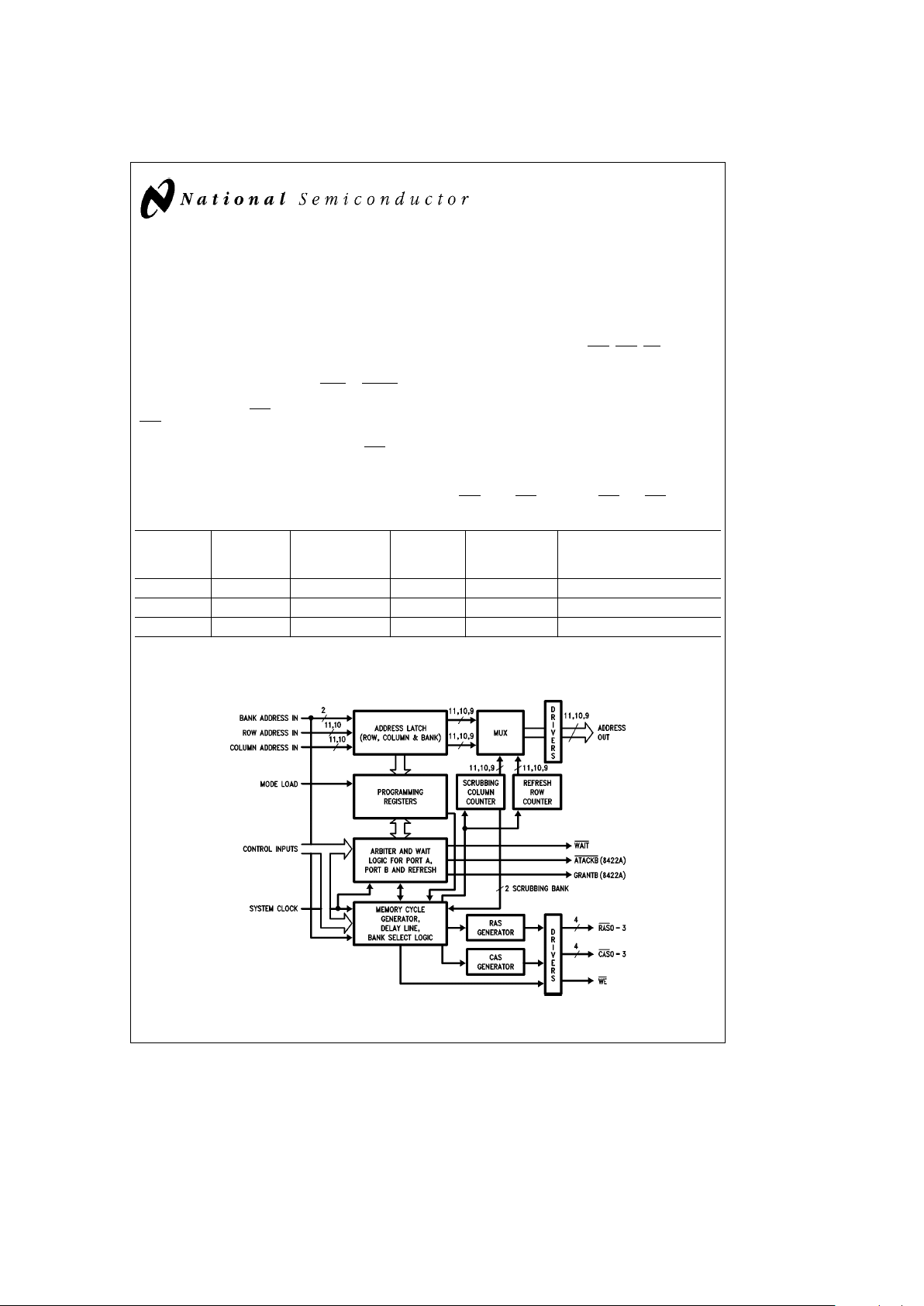

General Description

The DP8430V/31V/32V dynamic RAM controllers provide a

low cost, single chip interface between dynamic RAM and

all 8-, 16- and 32-bit systems. The DP8430V/31V/32V generate all the required access control signal timing for

DRAMs. An on-chip refresh request clock is used to automatically refresh the DRAM array. Refreshes and accesses

are arbitrated on chip. If necessary, a WAIT

or DTACK output inserts wait states into system access cycles, including

burst mode accesses. RAS

low time during refreshes and

RAS

precharge time after refreshes and back to back accesses are guaranteed through the insertion of wait states.

Separate on-chip precharge counters for each RAS

output

can be used for memory interleaving to avoid delayed back

to back accesses because of precharge. An additional feature of the DP8432V is two access ports to simplify dual

accessing. Arbitration among these ports and refresh is

done on chip.

Features

Y

On chip high precision delay line to guarantee critical

DRAM access timing parameters

Y

microCMOS process for low power

Y

High capacitance drivers for RAS, CAS,WEand DRAM

address on chip

Y

On chip support for nibble, page and static column

DRAMs

Y

Byte enable signals on chip allow byte writing in a word

size up to 32 bits with no external logic

Y

Can use a single clock source. Up to 33 MHz operating

frequency

Y

On board Port A/Port B (DP8432V only)/refresh arbitration logic

Y

Direct interface to all major microprocessors

Y

4 RAS and 4 CAS drivers (the RAS and CAS configuration is programmable)

Ý

of Pins

Ý

of Address

Largest Direct Drive Access

Control

(PLCC) Outputs

DRAM Memory Ports

Possible Capacity Available

DP8430V 68 9 256 kbit 4 Mbytes Single Access Port

DP8431V 68 10 1 Mbit 16 Mbytes Single Access Port

DP8432V 84 11 4 Mbit 64 Mbytes Dual Access Ports (A and B)

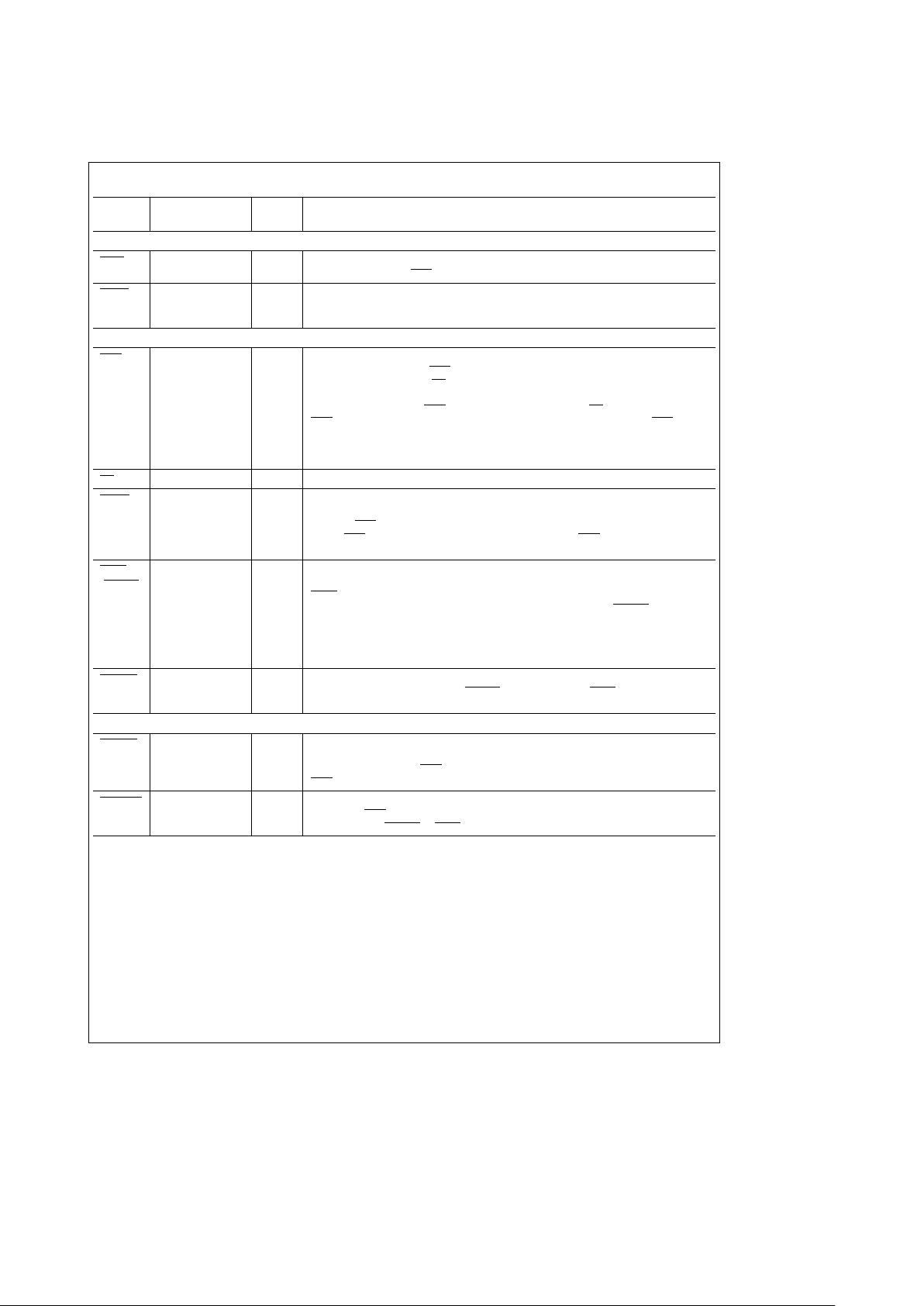

Block Diagram

DP8430V/31V/32V DRAM Controller

TL/F/11118– 1

FIGURE 1

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

Staggered Refresh

TM

is a trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M75/Printed in U. S. A.

Page 2

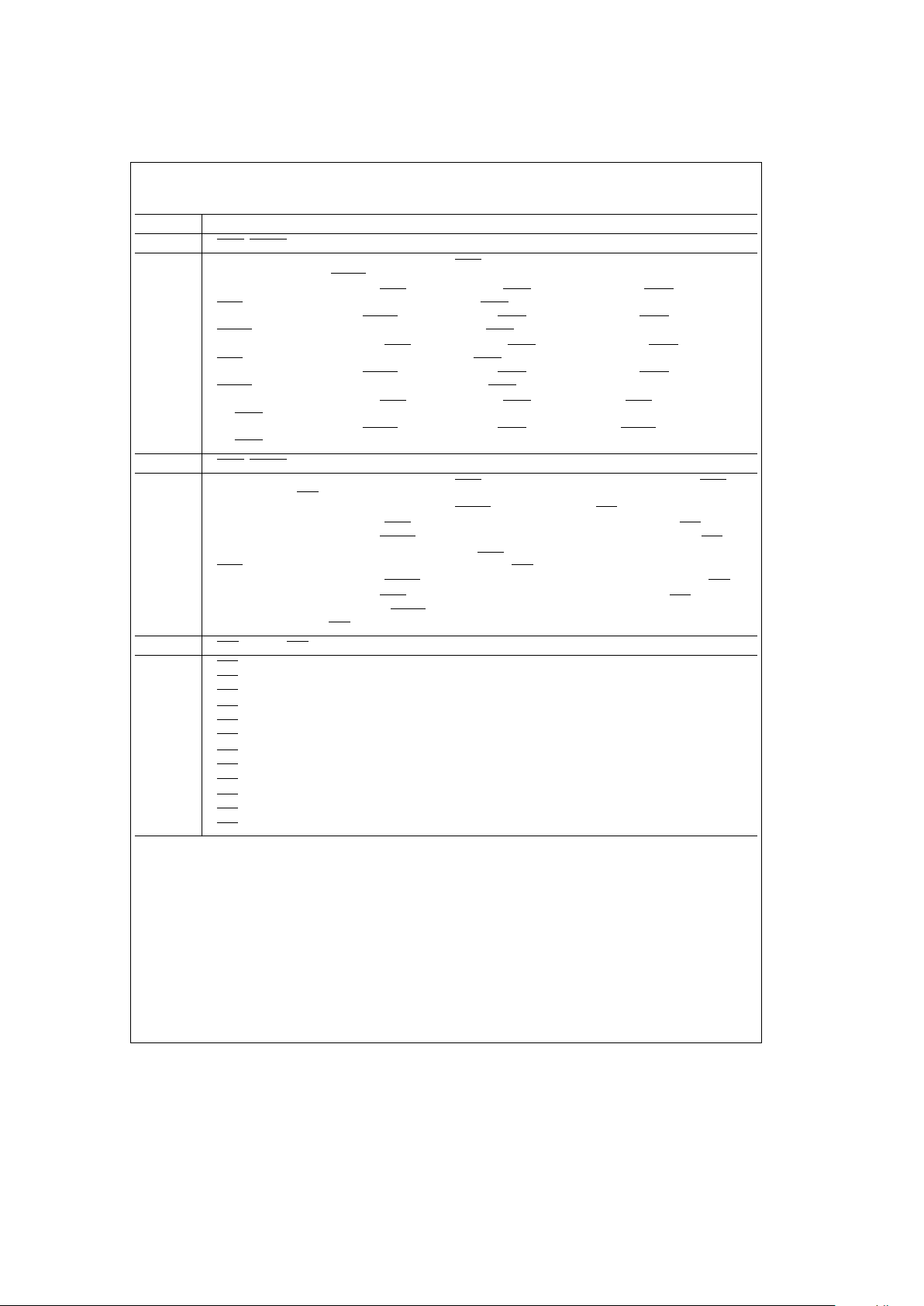

Table of Contents

1.0 INTRODUCTION

2.0 SIGNAL DESCRIPTIONS

2.1 Address, R/W and Programming Signals

2.2 DRAM Control Signals

2.3 Refresh Signals

2.4 Port A Access Signals

2.5 Port B Access Signals (DP8432V)

2.6 Common Dual Port Signals (DP8432V)

2.7 Power Signals and Capacitor Input

2.8 Clock Inputs

3.0 PROGRAMMING AND RESETTING

3.1 Reset

3.2 Programming Methods

3.2.1 Mode Load Only Programming

3.2.2 Chip Selected Access Programming

3.3 Internal Programming Modes

4.0 PORT A ACCESS MODES

4.1 Access Mode 0

4.2 Access Mode 1

4.3 Extending CAS with Either Access Mode

4.4 Read-Modify-Write Cycles with Either Access Mode

4.5 Additional Access Support Features

4.5.1 Address Latches and Column Increment

4.5.2 Address Pipelining

4.5.3 Delay CAS

During Write Accesses

5.0 REFRESH OPTIONS

5.1 Refresh Control Modes

5.1.1 Automatic Internal Refresh

5.1.2 Externally Controlled Refresh

5.2 Refresh Cycle Types

5.2.1 Conventional Refresh

5.2.2 Staggered Refresh

TM

5.2.3 Error Scrubbing Refresh

5.3 Extending Refresh

6.0 PORT A WAIT STATE SUPPORT

6.1 WAIT

Type Output

6.2 DTACK

Type Output

6.3 Dynamically Increasing the Number of Wait States

6.4 Guaranteeing RAS

Low Time and RAS Precharge

Time

7.0 RAS

AND CAS CONFIGURATION MODES

7.1 Byte Writing

7.2 Memory Interleaving

7.3 Address Pipelining

7.4 Error Scrubbing

7.5 Page/Burst Mode

8.0 TEST MODE

9.0 DRAM CRITICAL TIMING PARAMETERS

9.1 Programmable Values of t

RAH

and t

ASC

9.2 Calculation of t

RAH

and t

ASC

10.0 DUAL ACCESSING (DP8432V)

10.1 Port B Access Mode

10.2 Port B Wait State Support

10.3 Common Port A and Port B Dual Port Functions

10.3.1 GRANTB Output

10.3.2 LOCK

Input

11.0 ABSOLUTE MAXIMUM RATINGS

12.0 DC ELECTRICAL CHARACTERISTICS

13.0 AC TIMING PARAMETERS

14.0 DP8430V/31V/32V USER HINTS

2

Page 3

1.0 Introduction

The DP8430V/31V/32V DRAM controllers are the latest

devices based upon the DP8420A/21A/22A predecessors.

The DP8430V/31V/32V implement changes which do not

allow them to be pin compatible with any of the DP842XA or

the DP842XV DRAM controllers. Two changes have been

made: The limits for the input frequency to DELCLK have

been increased making possible the use of a single clock

source. A RESET input is now available making the reset

procedure easier. These changes, although minimal, facilitate the use of the controllers and make them even more

attractive for high performance applications. The controllers

incorporate address latches, refresh counter, row/column/

refresh address multiplexer, delay line, refresh/access/precharge arbitration logic and high capacitive drivers. The

DP8430V/31V/32V DRAM controllers allow any manufacturer’s CPU or bus to directly interface to DRAM arrays up to

64 Mbytes in size.

Reset:

The user must reset the controller before programming it.

Reset is achieved by asserting the RESET

input for at least

16 positive edges of clock.

Programming:

After reset, the user can program the controller by either

one of two methods: Mode Load Only Programming or Chip

Select Access Programming. The chip is programmed

through the address bus.

Initialization Period:

Once the DP8430V/31V/32V has been programmed for the

first time, a 60 ms initialization period is entered. During this

time the DRC performs refreshes to the DRAM array so

further warm up cycles are unnecessary. The initialization

period is entered only after the first programming after a

reset.

Accessing Modes:

After resetting and programming the chip, the DP8430V/

31V/32V is ready to access the DRAM. There are two

modes of accessing with these controllers. Mode 0, which

indicates RAS

synchronously and Mode 1, which indicates

RAS

asynchronously.

Refresh Modes:

Two refresh modes can be programmed. The user can

choose Automatic Internal Refresh or Externally Controlled

Refresh. With any refresh mode the user can perform burst

refreshes.

Refresh Types:

There are three types of refreshing available: Conventional,

Staggered and Error Scrubbing. Any refresh control mode

can be used with any type of refresh.

Wait Support:

The DP8430V/31V/32V have wait support available as

DTACK

or WAIT. Both are programmable. DTACK, Data

Transfer ACKnowledge, is useful for processors whose wait

signal is active high. WAIT

is useful for those processors

whose wait signal is active low. The user can choose either

at programming. These signals are used by the on chip arbiter to insert wait states to guarantee the arbitration between

accesses, refreshes and precharge. Both signals are independent of the access mode chosen and both signals can

be dynamically delayed further through the WAITIN

signal to

the DP8430V/31V/32V.

Sequential Accesses (Static Column/Page Mode):

The DP8430V/31V/32V have address latches, used to

latch the bank, row and column address inputs. Once the

address is latched, a COLumn INCrement (COLINC) feature

can be used to increment the column address. The address

latches can also be programmed to be fall through. COLINC

can be used for Sequential Accesses of Static Column

DRAMs. Also, COLINC in conjunction with ECAS

inputs can

be used for Sequential Accesses to Page Mode DRAMs.

RAS

and CAS Configuration (Byte Writing):

The RAS and CAS drivers can be configured to drive a one,

two or four bank memory array up to 32 bits in width. The

ECAS

signals can then be used to select one of four CAS

drivers for Byte Writing with no extra logic.

Memory Interleaving:

When configuring the DP8430V/31V/32V for more than

one bank, Memory Interleaving can be used. By tying the

low order address bits to the bank select lines B0 and B1,

sequential back to back accesses will not be delayed since

these controllers have separate precharge counters per

bank.

Address Pipelining:

The DP8430V/31V/32V are capable of performing Address

Pipelining. In address pipelining, the DRC will guarantee the

column address hold time and switch the internal multiplexor to place the row address on the address bus. At this

time, another memory access to another bank can be initiated.

Dual Accessing:

Finally, the DP8432V has all the features previously mentioned and unlike the DP8430V/31V, the DP8432V has a

second port to allow a second CPU to access the same

memory array. The DP8432V has four signals to support

Dual Accessing, these signals are AREQB

, ATACKB, LOCK

and GRANTB. All arbitration for the two ports and refresh is

done on chip by the controller through the insertion of wait

states. Since the DP8432V has only one input address bus,

the address lines must be multiplexed externally. The signal

GRANTB can be used for this purpose.

Terminology:

The following explains the terminology used in this data

sheet. The terms negated and asserted are used. Asserted

refers to a ‘‘true’’ signal. Thus, ‘‘ECAS0

asserted’’ means

the ECAS0

input is at a logic 0. The term ‘‘COLINC asserted’’ means the COLINC input is at a logic 1. The term negated refers to a ‘‘false’’ signal. Thus, ‘‘ECAS0

negated’’

means the ECAS0

input is at a logic 1. The term ‘‘COLINC

negated’’ means the input COLINC is at a logic 0. The table

shown below clarifies this terminology.

Signal Action Logic Level

Active High Asserted High

Active High Negated Low

Active Low Asserted Low

Active Low Negated High

3

Page 4

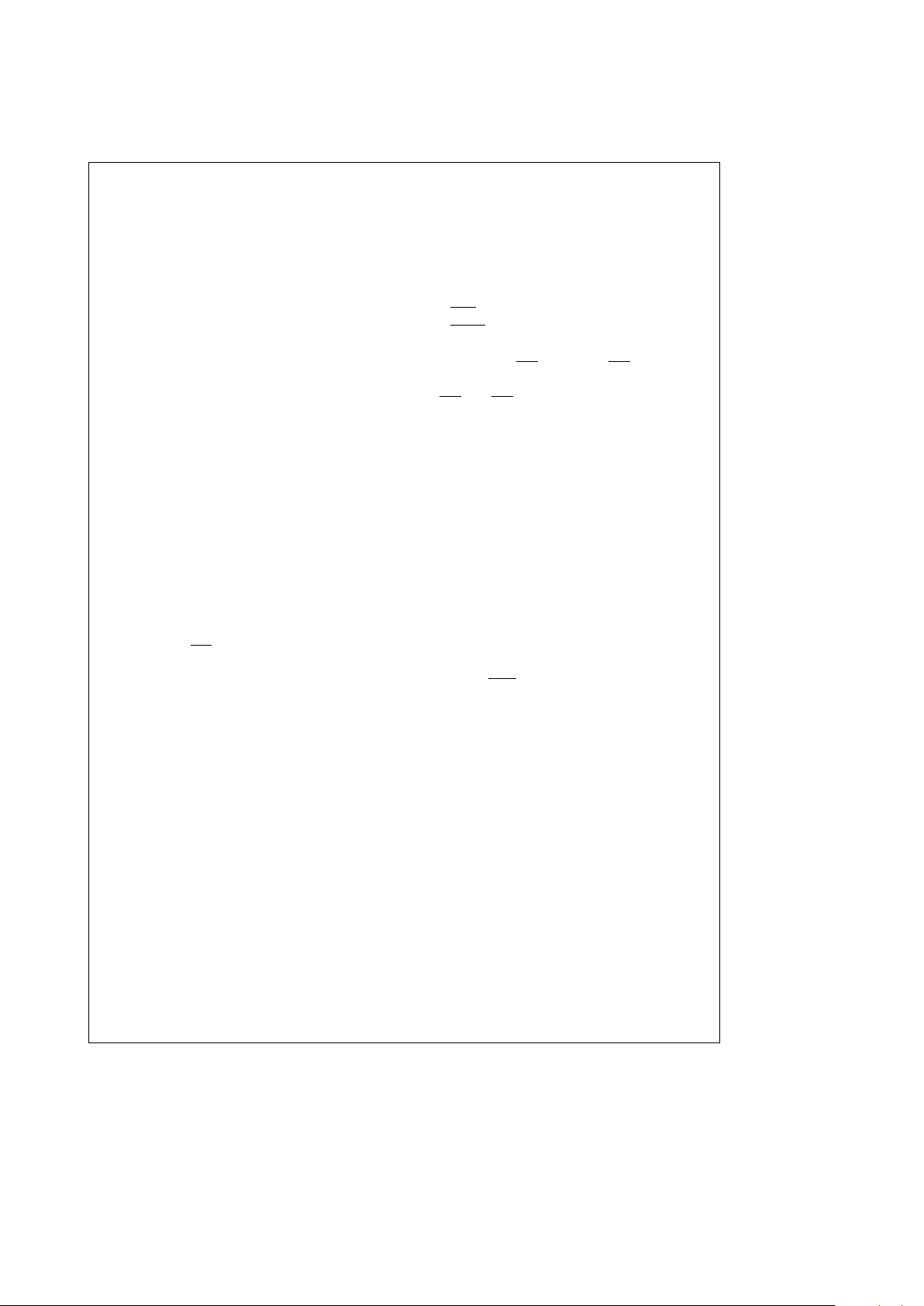

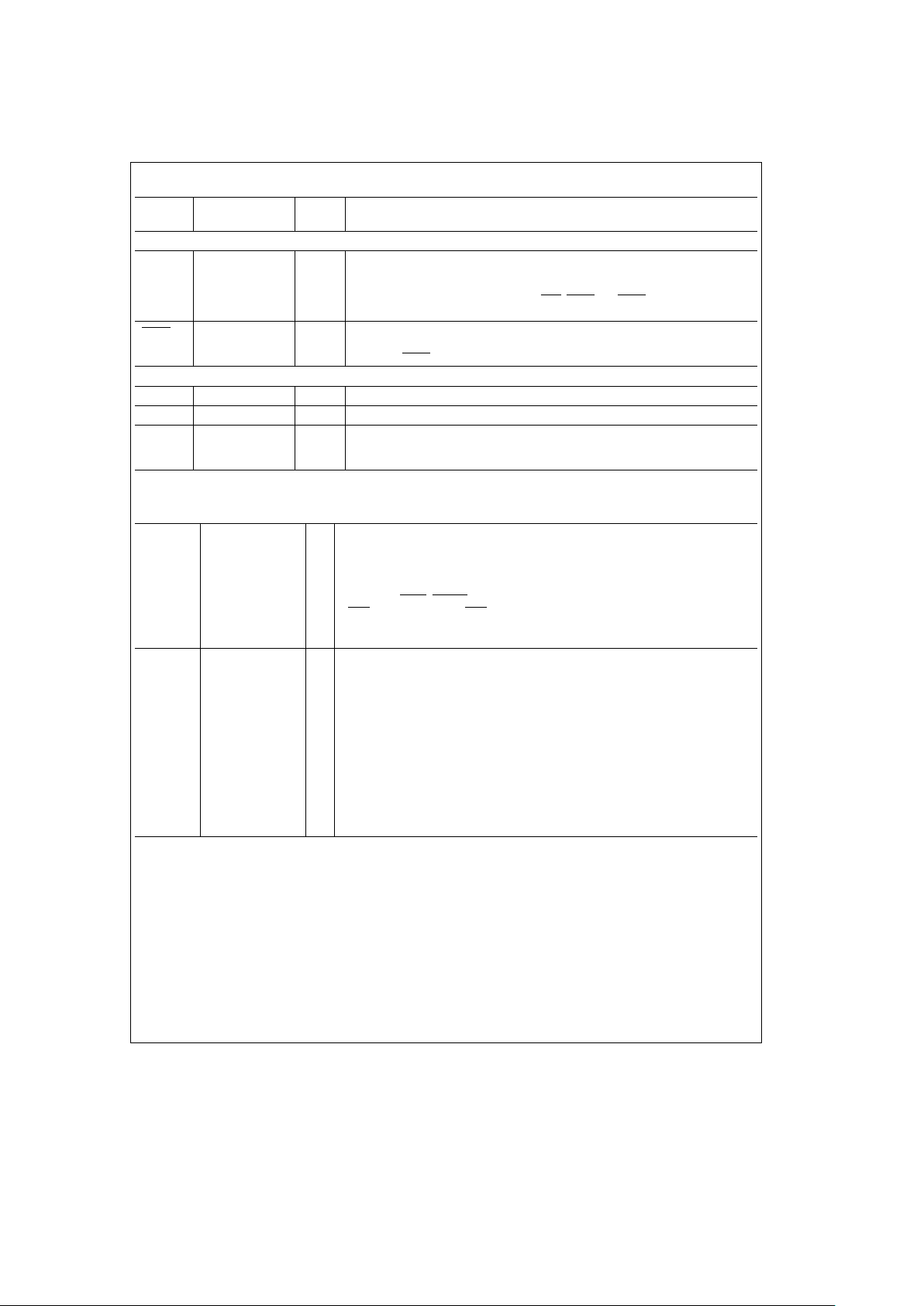

Connection Diagrams

TL/F/11118– 2

Top View

FIGURE 2

Order Number DP8430V-33

See NS Package Number V68A

TL/F/11118– 3

Top View

FIGURE 3

Order Number DP8431V-33

See NS Package Number V68A

TL/F/11118– 4

Top View

FIGURE 4

Order Number DP8432V-33

See NS Package Number V84A

4

Page 5

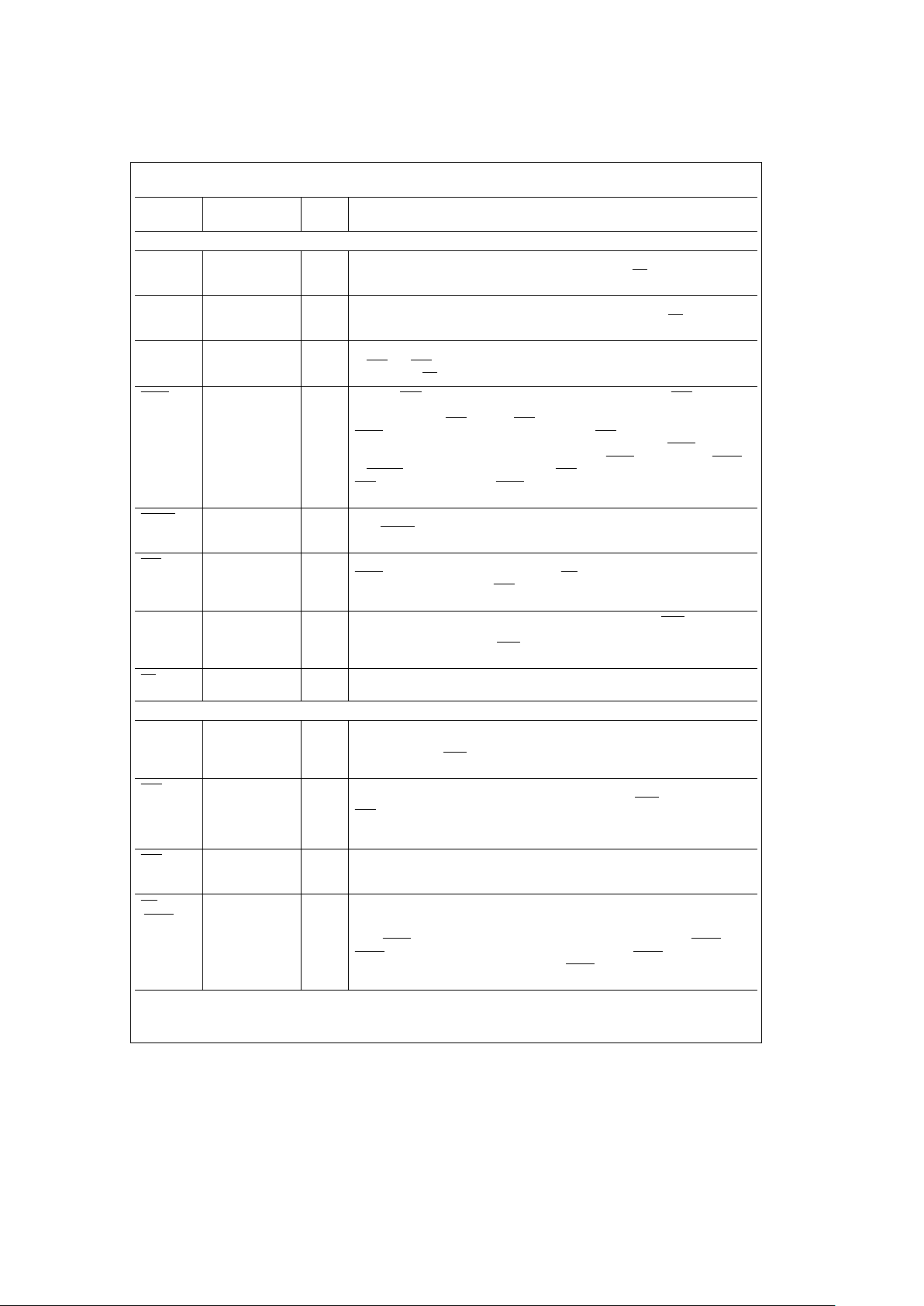

2.0 Signal Descriptions

Pin Device (If not Input/

Description

Name Applicable to All) Output

2.1 ADDRESS, R/W AND PROGRAMMING SIGNALS

R0–10 DP8432V I ROW ADDRESS: These inputs are used to specify the row address during an access

to the DRAM. They are also used to program the chip when ML

is asserted (except

R0–9 DP8430V/31V I

R10).

C0–10 DP8432V I COLUMN ADDRESS: These inputs are used to specify the column address during an

access to the DRAM. They are also used to program the chip when ML

is asserted

C0–9 DP8430V/31V I

(except C10).

B0, B1 I BANK SELECT: Depending on programming, these inputs are used to select a group

of RAS and CAS outputs to assert during an access. They are also used to program

the chip when ML

is asserted.

ECAS0–3 I ENABLE CAS: These inputs are used to enable a single or group of CAS outputs

when asserted. In combination with the B0, B1 and the programming bits, these

inputs select which CAS

output or CAS outputs will assert during an access. The

ECAS

signals can also be used to toggle a group of CAS outputs for page/nibble

mode accesses. They also can be used for byte write operations. If ECAS

0is

negated during programming, continuing to assert the ECAS

0 while negating AREQ

or AREQB during an access, will cause the CAS outputs to be extended while the

RAS

outputs are negated (the ECASn inputs have no effect during scrubbing

refreshes).

RESET I RESET: At power up, this input is used to reset the DRAM controller. The user must

keep RESET

low for at least 16 positive edges of clock. After programming this input

must remain negated (high) to avoid an unwanted reset.

WIN I WRITE ENABLE IN: This input is used to signify a write operation to the DRAM. If

ECAS0 is asserted during programming, the WE output will follow this input. This

input asserted will also cause CAS

to delay to the next positive clock edge if address

bit C9 is asserted during programming.

COLINC I COLUMN INCREMENT: When the address latches are used, and RFIP is negated,

this input functions as COLINC. Asserting this signal causes the column address to

(EXTNDRF) I

be incremented by one. When RFIP

is asserted, this signal is used to extend the

refresh cycle by any number of periods of CLK until it is negated.

ML I MODE LOAD: This input signal, when low, enables the internal programming register

that stores the programming information.

2.2 DRAM CONTROL SIGNALS

Q0–10 DP8432V O DRAM ADDRESS: These outputs are the multiplexed output of the R0 –9, 10 and

C0–9, 10 and form the DRAM address bus. These outputs contain the refresh

Q0–9 DP8431V O

address whenever RFIP

is asserted. They contain high capacitive drivers with 20X

Q0–8 DP8430V O

series damping resistors.

RAS0–3 O ROW ADDRESS STROBES: These outputs are asserted to latch the row address

contained on the outputs Q0–8, 9, 10 into the DRAM. When RFIP

is asserted, the

RAS

outputs are used to latch the refresh row address contained on the Q0–8, 9, 10

outputs in the DRAM. These outputs contain high capacitive drivers with 20X series

damping resistors.

CAS0–3 O COLUMN ADDRESS STROBES: These outputs are asserted to latch the column

address contained on the outputs Q0–8, 9, 10 into the DRAM. These outputs have

high capacitive drivers with 20X series damping resistors.

WE O WRITE ENABLE or REFRESH REQUEST: This output asserted specifies a write

operation to the DRAM. When negated, this output specifies a read operation to the

(RFRQ

)O

DRAM. When the DP8430V/31V/32V is programmed in address pipelining mode or

when ECAS0 is negated during programming, this output will function as RFRQ.

RFRQ

asserted, specifies that 13 msor15ms have passed. RFRQ can be used to

externally request a refresh through the input RFSH

. This output has a high

capacitive driver and a 20X series damping resistor.

5

Page 6

2.0 Signal Descriptions (Continued)

Pin Device (If not Input/

Description

Name Applicable to All) Output

2.3 REFRESH SIGNALS

RFIP O REFRESH IN PROGRESS: This output is asserted prior to a refresh cycle and is

negated when all the RAS

outputs are negated for that refresh.

RFSH I REFRESH: This input asserted will request a refresh. If this input is continually

asserted, the DP8430V/31V/32V will perform refresh cycles in a burst refresh

fashion until the input is negated.

2.4 PORT A ACCESS SIGNALS

ADS I ADDRESS STROBE or ADDRESS LATCH ENABLE: Depending on programming,

this input can function as ADS

or ALE. In mode 0, the input functions as ALE and

(ALE) I

when asserted along with CS

causes an internal latch to be set. Once this latch is set

an access will start from the positive clock edge of CLK as soon as possible. In Mode

1, the input functions as ADS

and when asserted along with CS, causes the access

RAS

to assert if no other event is taking place. If an event is taking place, RAS will be

asserted from the positive edge of CLK as soon as possible. In both cases, the low

going edge of this signal latches the bank, row and column address if programmed to

do so.

CS I CHIP SELECT: This input signal must be asserted to enable a Port A access.

AREQ I ACCESS REQUEST: This input signal in Mode 0 must be asserted some time after

the first positive clock edge after ALE has been asserted. When this signal is

negated, RAS

is negated for the access. In Mode 1, this signal must be asserted

before ADS

can be negated. When this signal is negated, RAS is negated for the

access.

WAIT O WAIT or DTACK: This output can be programmed to insert wait states into a CPU

access cycle. With R7 negated during programming, the output will function as a

(DTACK

)O

WAIT

type output. In this case, the output will be active low to signal a wait condition.

With R7 asserted during programming, the output will function as DTACK

. In this

case, the output will be negated to signify a wait condition and will be asserted to

signify the access has taken place. Each of these signals can be delayed by a

number of positive clock edges or negative clock levels of CLK to increase the

microprocessor’s access cycle through the insertion of wait states.

WAITIN I WAIT INCREASE: This input can be used to dynamically increase the number of

positive clock edges of CLK until DTACK

will be asserted or WAIT will be negated

during a DRAM access.

2.5 PORT B ACCESS SIGNALS

AREQB DP8432V I PORT B ACCESS REQUEST: This input asserted will latch the row, column and bank

address if programmed, and requests an access to take place for Port B. If the

only

access can take place, RAS

will assert immediately. If the access has to be delayed,

RAS

will assert as soon as possible from a positive edge of CLK.

ATACKB DP8432V O ADVANCED TRANSFER ACKNOWLEDGE PORT B: This output is asserted when

the access RAS

is asserted for a Port B access. This signal can be used to generate

only

the appropriate DTACK

or WAIT type signal for Port B’s CPU or bus.

6

Page 7

2.0 Signal Descriptions (Continued)

Pin Device (If not Input/

Description

Name Applicable to All) Output

2.6 COMMON DUAL PORT SIGNALS

GRANTB DP8432V O GRANT B: This output indicates which port is currently granted access to the DRAM

array. When GRANTB is asserted, Port B has access to the array. When GRANTB is

only

negated, Port A has access to the DRAM array. This signal is used to multiplex the

signals R0–8, 9, 10; C0 –8, 9, 10; B0 – 1; WIN

; LOCK and ECAS0 – 3 to the DP8432V

when using dual accessing.

LOCK DP8432V I LOCK: This input can be used by the currently granted port to ‘‘lock out’’ the other

port from the DRAM array by inserting wait states into the locked out port’s access

only

cycle until LOCK is negated.

2.7 POWER SIGNALS AND CAPACITOR INPUT

V

CC

I POWER: Supply Voltage.

GND I GROUND: Supply Voltage Reference.

CAP I CAPACITOR: This input is used by the internal PLL for stabilization. The value of the

ceramic capacitor should be 0.1 mF and should be connected between this input and

ground.

2.8 CLOCK INPUTS

There are two clock inputs to the DP8430V/31V/32V, CLK and DELCLK. These two clocks may both be tied to the same clock

input, or they may be two separate clocks, running at different frequencies, asynchronous to each other.

CLK I SYSTEM CLOCK: This input may be in the range of 0 Hz up to 25 MHz. This input is

generally a constant frequency but it may be controlled externally to change

frequencies or perhaps be stopped for some arbitrary period of time.

This input provides the clock to the internal state machine that arbitrates between

accesses and refreshes. This clock’s positive edges and negative levels are used to

extend the WAIT

(DTACK) signals. Ths clock is also used as the reference for the

RAS

precharge time and RAS low time during refresh.

All Port A and Port B accesses are assumed to be synchronous to the system clock

CLK.

DELCLK I DELAY LINE CLOCK: The input frequency to DELCLK should be in the range of

12 MHz to 40 MHz. This frequency will be internally divided by choosing a divisor

when programming the part. The result of the division should be a frequency of

2 MHz. This is because the Phase Lock Loop that generates the delay line assumes

an input clock frequency of 2 MHz. If after dividing DELCLK by one of the internal

divisors (6, 8, 10, 12, 14, 16, 18 or 20) the resulting frequency is not 2 MHz, the delay

line will suffer.

For example, if the DELCLK frequency is 18 MHz and a divide by 8 is chosen,

programming bits C0–2, the resulting frequency will be 2.25 which is 12.5% off of

2 MHz. Therefore, the DP8430V/31V/32V will produce delays that are shorter (faster

delays) than what is intended. On the other hand, if divide by 10 was chosen, the

resulting frequency will be 1.8 MHz, this frequency will produce delays that are longer

(slower delays) than intended.

This clock is also divided to create the internal refresh clock.

7

Page 8

3.0 Programming and Resetting

The DP8430V/31V/32V must be reset before it can be programmed. After reset, the DRAM controller is programmed

through the address bus by either one of two methods;

Mode Load Only Programming or Chip Select Access Programming. After the first programming after a reset, the chip

enters a 60 ms initialization period. During this period the

controller performs refreshes every 13 msor15ms, this

makes further DRAM warm up cycles unnecessary. After

this stage the DRAM controller can be programmed as

many times as the user wishes and the 60 ms initialization

period will not be entered into unless the chip is reset and

programmed again. During the 60 ms initialization period,

RFIP

is asserted and RAS toggles every 13 msor15ms

depending on the programming bit for refresh (C3). CAS

will

be negated and the Q outputs will count from 0 to 2047

refreshing the entire DRAM array. The initialization time period is given by the following formula. T

e

4096 * (Clock

Divisor Select) * (Refresh Clock Fine Tune)/(DELCLK Frq.)

3.1 RESET

The DP8430V/31V/32V have a RESET

input pin which facilitates the reset procedure required for proper operation.

Reset is accomplished by asserting the RESET

input for at

least 16 positive edges of clock as shown in

Figure 5

.

The DRC may be programmed anytime on the fly, but the

user must make sure that no access or refresh is in progress. RESET

is asynchronous.

3.2 PROGRAMMING METHODS

3.2.1 Mode Load Only Programming

To use this method the user asserts ML

enabling the inter-

nal programming register. After ML

is asserted, a valid programming selection is placed on the address bus, B0, B1

and ECAS0

inputs, then ML is negated. When ML is negated the programming bits are latched into the internal programming register and the DP8430V/31V/32V is programmed, see

Figure 6

. When programming the chip, the

controller must not be refreshing, RFIP

must be high (1) to

have a successful programming.

3.2.2 Chip Selected Access Programming

The chip can also be programmed by performing a chip

selected access. To program the chip using this method,

ML

is asserted, then CS is asserted and a valid program-

ming selection is placed on the address bus. When AREQ

is

asserted, the programming bits affecting the wait logic become effective immediately, then DTACK

is asserted allow-

ing the access to terminate. After the access, ML

is negated

and the rest of the programming bits take effect.

TL/F/11118– 5

FIGURE 5. Reset

TL/F/11118– 6

FIGURE 6. ML Only Programming

TL/F/11118– 7

FIGURE 7. CS Access Programming

8

Page 9

3.0 Programming and Resetting (Continued)

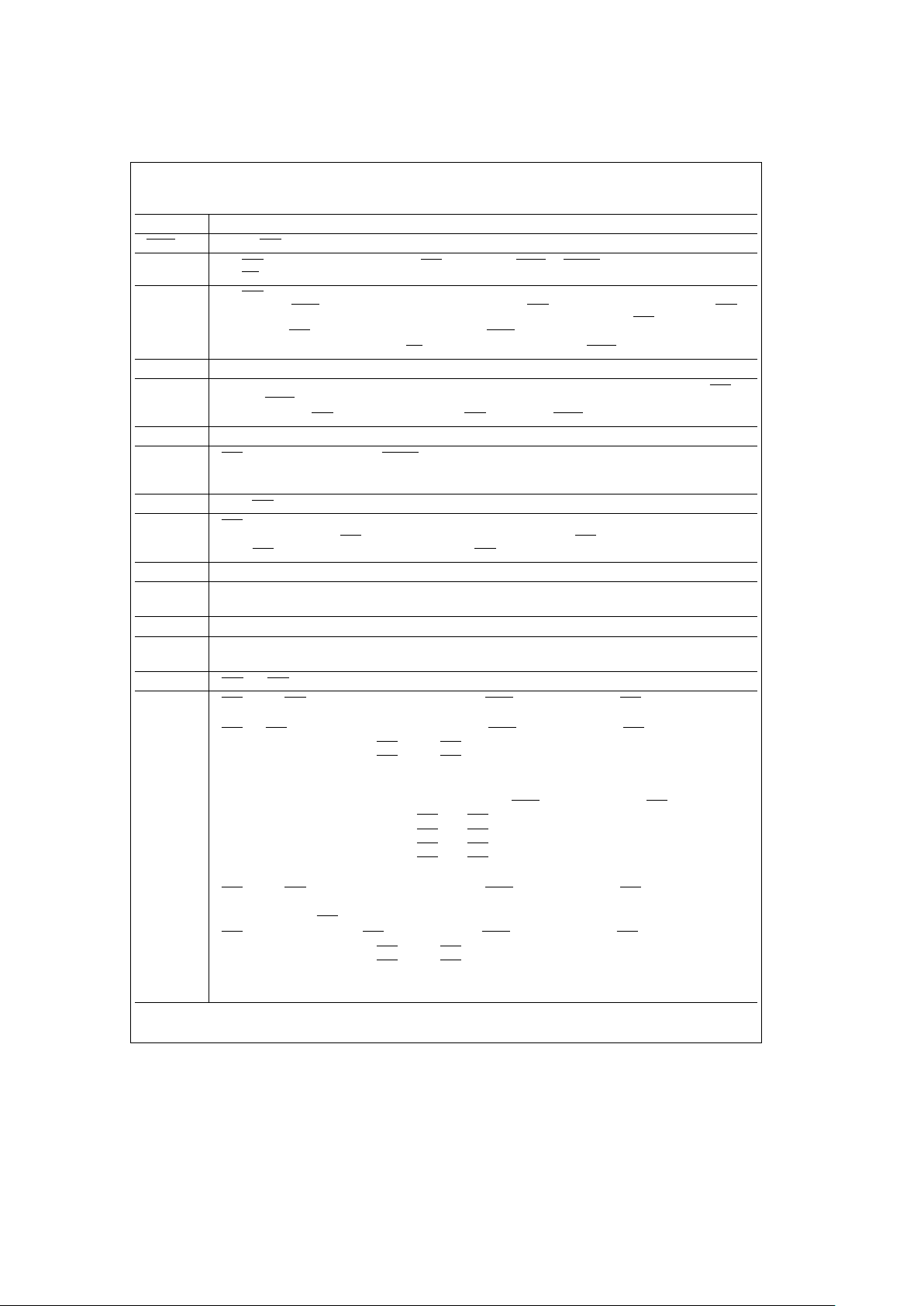

3.3 PROGRAMMING BIT DEFINITIONS

Symbol Description

ECAS0 Extend CAS/Refresh Request Select

0 The CASn outputs will be negated with the RASn outputs when AREQ (or AREQB, DP8432V only) is negated.

The WE

output pin will function as write enable. Automatic Internal Refresh selected.

1 The CASn outputs will be negated, during an acccess (Port A (or Port B, DP8432V only)) when their

corresponding ECAS

n inputs are negated. This feature allows the CAS outputs to be extended beyond the RAS

outputs negating. Scrubbing refreshes are NOT affected. During scrubbing refreshes the CAS outputs will negate

along with the RAS

outputs regardless of the state of the ECAS inputs.

Externally Controlled Refresh selected, WE will function as ReFresh ReQuest (RFRQ).

B1 Access Mode Select

0 ACCESS MODE 0: ALE pulsing high sets an internal latch. On the next positive edge of CLK, the access (RAS

)

will start. AREQ

will terminate the access.

1 ACCESS MODE 1: ADS

asserted starts the access (RAS) immediately. AREQ will terminate the access.

B0 Address Latch Mode

0 ADS or ALE asserted for Port A or AREQB asserted for Port B with the appropriate GRANT latch the input row,

column and bank address.

1 The row, column and bank latches are fall through.

C9 Delay CAS during WRITE Accesses

0 CAS is treated the same for both READ and WRITE accesses.

1 During WRITE accesses, CAS will be asserted by the event that occurs last: CAS asserted by the internal delay

line or CAS

asserted on the positive edge of CLK after RAS is asserted.

C8 Row Address Hold Time

0 Row Address Hold Timee25 ns minimum

1 Row Address Hold Timee15 ns minimum

C7 Column Address Setup Time

0 Column Address Setup Timee10 ns miniumum

1 Column Address Setup Timee0 ns minimum

C6, C5, C4 RAS and CAS Configuration Modes/Error Scrubbing during Refresh

0, 0, 0 RAS0 – 3 and CAS0–3 are all selected during an access. ECASn must be asserted for CASn to be asserted.

B0 and B1 are not used during an access. Error scrubbing during refresh.

0, 0, 1 RAS

and CAS pairs are selected during an access by B1. ECASn must be asserted for CAS

n to be asserted.

B1

e

0 during an access selects RAS0– 1 and CAS0–1.

B1e1 during an access selects RAS2– 3 and CAS2–3.

B0 is not used during an Access.

Error scrubbing during refresh.

0, 1, 0 RAS and CAS singles are selected during an access by B0 – 1. ECAS

n must be asserted for CASn to be asserted.

B1

e

0, B0e0 during an access selects RAS0 and CAS0.

B1

e

0, B0e1 during an access selects RAS1 and CAS1.

B1

e

1, B0e0 during an access selects RAS2 and CAS2.

B1e1, B0e1 during an access selects RAS3 and CAS3.

Error scrubbing during refresh.

0, 1, 1 RAS

0–3 and CAS0 –3 are all selected during an access. ECASn must be asserted for CASn to be asserted.

B1, B0 are not used during an access.

No error scrubbing. (RAS

only refreshing)

1, 0, 0 RAS pairs are selected by B1. CAS0 – 3 are all selected. ECASn must be asserted for CASn to be asserted.

B1

e

0 during an access selects RAS0– 1 and CAS0–3.

B1e1 during an access selects RAS2– 3 and CAS0–3.

B0 is not used during an access.

No error scrubbing.

9

Page 10

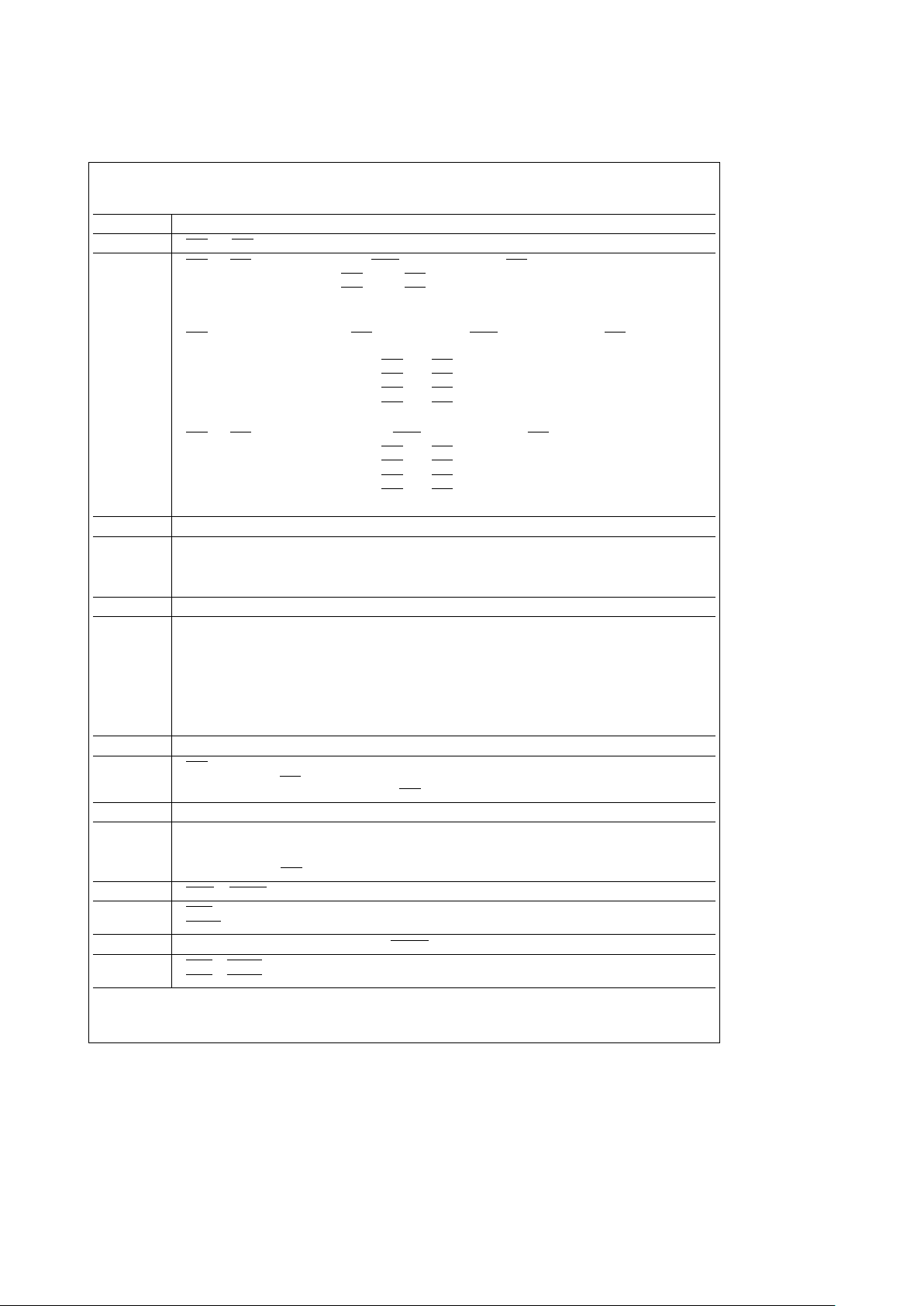

3.0 Programming and Resetting (Continued)

3.3 PROGRAMMING BIT DEFINITIONS (Continued)

Symbol Description

C6, C5, C4 RAS and CAS Configuration Modes (Continued)

1, 0, 1 RAS and CAS pairs are selected by B1. ECASn must be asserted for CASn to be asserted.

B1

e

0 during an access selects RAS0– 1 and CAS0–1.

B1

e

1 during an access selects RAS2– 3 and CAS2–3.

B0 is not used during an access.

No error scrubbing.

1, 1, 0 RAS singles are selected by B0 –1. CAS0 – 3 are all selected. ECASn must be asserted for CASntobe

asserted.

B1

e

0, B0e0 during an access selects RAS0 and CAS0–3.

B1

e

0, B0e1 during an access selects RAS1 and CAS0–3.

B1

e

1, B0e0 during an access selects RAS2 and CAS0–3.

B1

e

1, B0e1 during an access selects RAS3 and CAS0–3.

No error scrubbing.

1, 1, 1 RAS and CAS singles are selected by B0, 1. ECASn must be asserted for CASn to be asserted.

B1

e

0, B0e0 during an access selects RAS0 and CAS0.

B1

e

0, B0e1 during an access selects RAS1 and CAS1.

B1

e

1, B0e0 during an access selects RAS2 and CAS2.

B1

e

1, B0e1 during an access selects RAS3 and CAS3.

No error scrubbing.

C3 Refresh Clock Fine Tune Divisor

0 Divide delay line/refresh clock further by 30 (If DELCLK/Refresh Clock Clock Divisore2 MHze15 ms

refresh period).

1 Divide delay line/refresh clock further by 26 (If DELCLK/Refresh Clock Clock Divisor

e

2 MHze13 ms

refresh period).

C2, C1, C0 Delay Line/Refresh Clock Divisor Select

0, 0, 0 Divide DELCLK by 20 to get as close to 2 MHz as possible.

0, 0, 1 Divide DELCLK by 18 to get as close to 2 MHz as possible.

0, 1, 0 Divide DELCLK by 16 to get as close to 2 MHz as possible.

0, 1, 1 Divide DELCLK by 14 to get as close to 2 MHz as possible.

1, 0, 0 Divide DELCLK by 12 to get as close to 2 MHz as possible.

1, 0, 1 Divide DELCLK by 10 to get as close to 2 MHz as possible.

1, 1, 0 Divide DELCLK by 8 to get as close to 2 MHz as possible.

1, 1, 1 Divide DELCLK by 6 to get as close to 2 MHz as possible.

R9 Refresh Mode Select

0 RAS0 – 3 will all assert and negate at the same time during a refresh.

1 Staggered Refresh. RAS

outputs during refresh are separated by one positive clock edge. Depending on the

configuration mode chosen, either one or two RAS

s will be asserted.

R8 Address Pipelining Select

0 Address pipelining is selected. The DRAM controller will switch the DRAM column address back to the row

address after guaranteeing the column address hold time.

1 Non-address pipelining is selected. The DRAM controller will hold the column address on the DRAM address

bus until the access RAS

s are negated.

R7 WAIT or DTACK Select

0 WAIT type output is selected.

1 DTACK

(Data Transfer ACKnowledge) type output is selected.

R6 Add Wait States to the Current Access if WAITIN is Low

0 WAIT or DTACK will be delayed by one additional positive edge of CLK.

1 WAIT

or DTACK will be delayed by two additional positive edges of CLK.

10

Page 11

3.0 Programming and Resetting (Continued)

3.3 PROGRAMMING BIT DEFINITIONS (Continued)

Symbol Description

R5, R4 WAIT/DTACK during Burst (See Section 5.1.2 or 5.2.2)

0, 0 NO WAIT STATES; If R7e0 during programming, WAIT will remain negated during burst portion of access.

If R7

e

1 programming, DTACK will remain asserted during burst portion of access.

0, 1 1T; If R7e0 during programming, WAIT will assert when the ECAS inputs are negated with AREQ asserted.

WAIT

will negate from the positive edge of CLK after the ECASs have been asserted.

If R7e1 during programming, DTACK will negate when the ECAS inputs are negated with AREQ asserted.

DTACK

will assert from the positive edge of CLK after the ECASs have been asserted.

1, 0 (/2T; If R7e0 during programming, WAIT will assert when the ECAS inputs are negated with AREQ asserted.

WAIT

will negate on the negative level of CLK after the ECASs have been asserted.

If R7

e

1 during programming, DTACK will negate when the ECAS inputs are negated with AREQ asserted.

DTACK

will assert from the negative level of CLK after the ECASs have been asserted.

1, 1 0T; If R7e0 during programming, WAIT will assert when the ECAS inputs are negated. WAIT will negate when

the ECAS

inputs are asserted.

If R7e1 during programming, DTACK will negate when the ECAS inputs are negated. DTACK will assert when

the ECAS

inputs are asserted.

R3, R2 WAIT/DTACK Delay Times (See Section 5.1.1 or 5.2.1)

0, 0 NO WAIT STATES; If R7e0 during programming, WAIT will remain high during non-delayed accesses. WAIT

will negate when RAS is negated during delayed accesses.

NO WAIT STATES; If R7

e

1 during programming, DTACK will be asserted when RAS is asserted.

0, 1 (/2T; If R7e0 during programming, WAIT will negate on the negative level of CLK, after the access RAS.

1T; If R7e1 during programming, DTACK will be asserted on the positive edge of CLK after the access RAS.

1, 0 NO WAIT STATES, (/2T; If R7e0 during programming, WAIT will remain high during non-delayed accesses.

WAIT

will negate on the negative level of CLK, after the access RAS, during delayed accesses.

(/2T; If R7

e

1 during programming, DTACK will be asserted on the negative level of CLK after the access RAS.

1, 1 1T; If R7

e

0 during programming, WAIT will negate on the positive edge of CLK after the access RAS.

1(/2T; If R7

e

1 during programming, DTACK will be asserted on the negative level of CLK after the positive edge

of CLK after the access RAS

.

R1, R0 RAS Low and RAS Precharge Time

0, 0 RAS asserted during refreshe2 positive edges of CLK.

RAS

precharge timee1 positive edge of CLK.

RAS

will start from the first positive edge of CLK after GRANTB transitions (DP8432V).

0, 1 RAS asserted during refreshe3 positive edges of CLK.

RAS

precharge timee2 positive edges of CLK.

RAS

will start from the second positive edge of CLK after GRANTB transitions (DP8432V).

1, 0 RAS asserted during refreshe2 positive edges of CLK.

RAS

precharge timee2 positive edges of CLK.

RAS

will start from the first positive edge of CLK after GRANTB transitions (DP8432V).

1, 1 RAS

asserted during refreshe4 positive edges of CLK.

RAS

precharge timee3 positive edges of CLK.

RAS

will start from the second positive edge of CLK after GRANTB transitions (DP8432V).

11

Page 12

4.0 Port A Access Modes

The DP8430V/31V/32V have two general purpose access

modes. Mode 0 RAS

synchronous and Mode 1 RAS asynchronous. One of these modes is selected at programming

through the B1 input. A Port A access to DRAM is initiated

by two input signals: ADS

(ALE) and CS. The access is al-

ways terminated by one signal: AREQ

. These input signals

should be synchronous to the input clock.

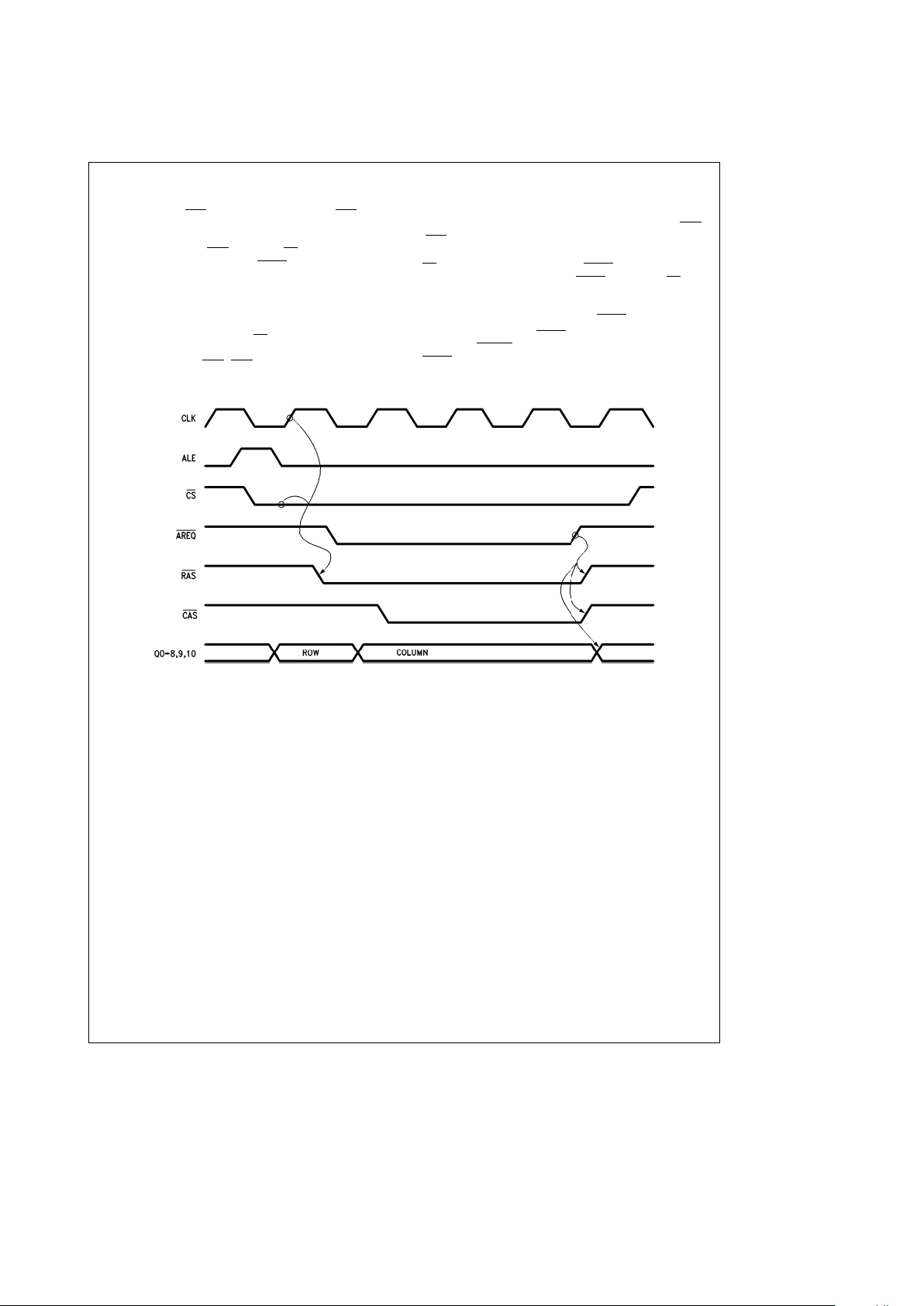

4.1 ACCESS MODE 0

Mode 0, synchronous access, is selected by negating the

input B1 during programming (B1

e

0). To initiate a Mode 0

access, ALE is pulse high and CS

is asserted. If precharge

time was met, a refresh of DRAM or a Port B access was

not in progress, the RAS

(RASs) would be asserted on the

first rising edge of clock. If a refresh or a Port B access is in

progress or precharge time is required, the controller will

wait until these events have taken place and assert RAS

(RASs) on the next positive edge of clock.

Sometime after the first positive edge of clock after ALE and

CS

have been asserted, the input AREQ must be asserted.

In single port applications, once AREQ

is asserted, CS can

be negated. On the other hand, ALE can stay asserted several periods of clock; however, ALE must be negated before

or during the period of CLK in which AREQ

is negated.

The controller samples AREQ on the every rising edge of

clock after DTACK

is asserted. The access will end when

AREQ

is sampled negated.

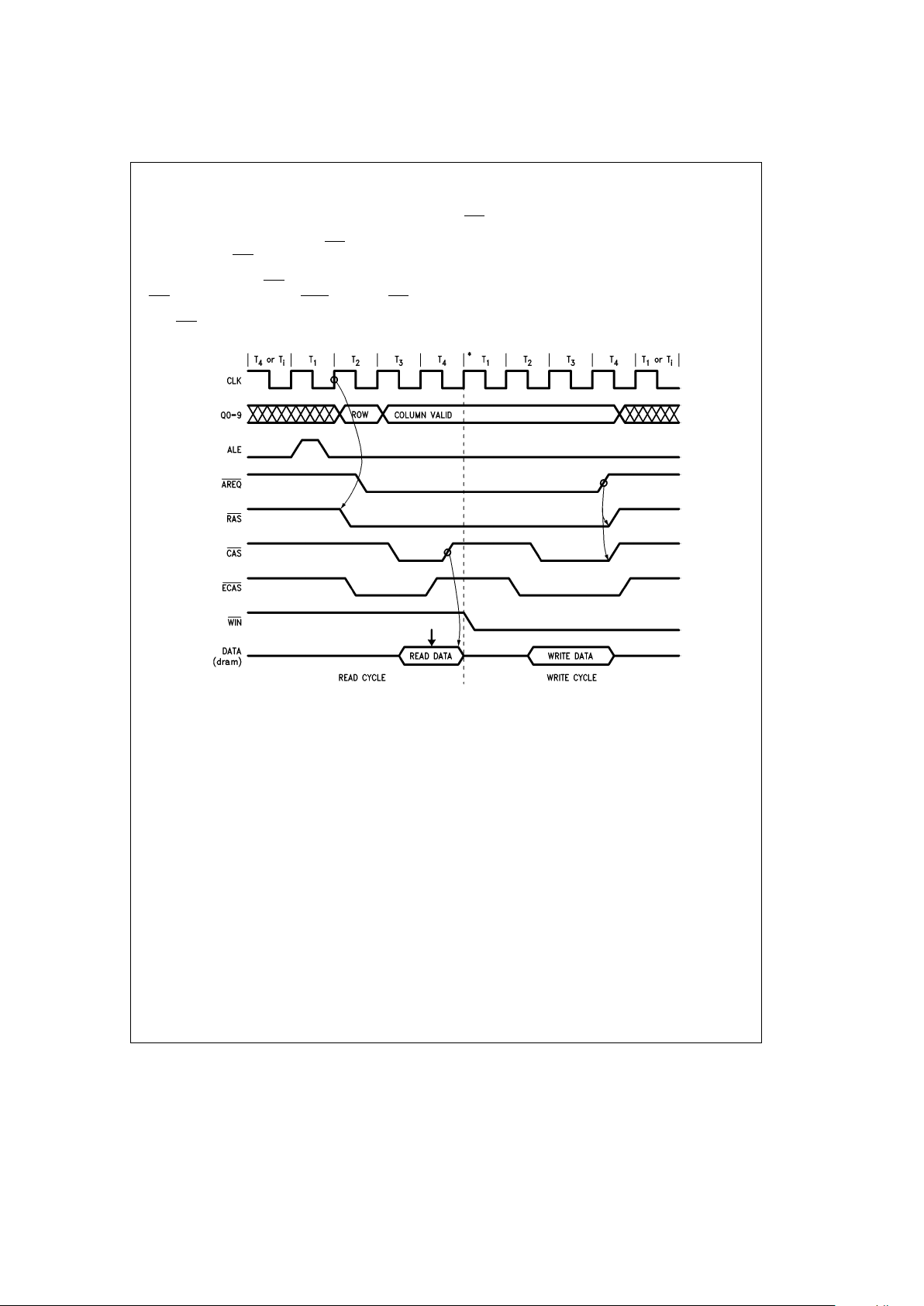

TL/F/11118– 8

FIGURE 8a. Access Mode 0

12

Page 13

4.0 Port A Access Modes (Continued)

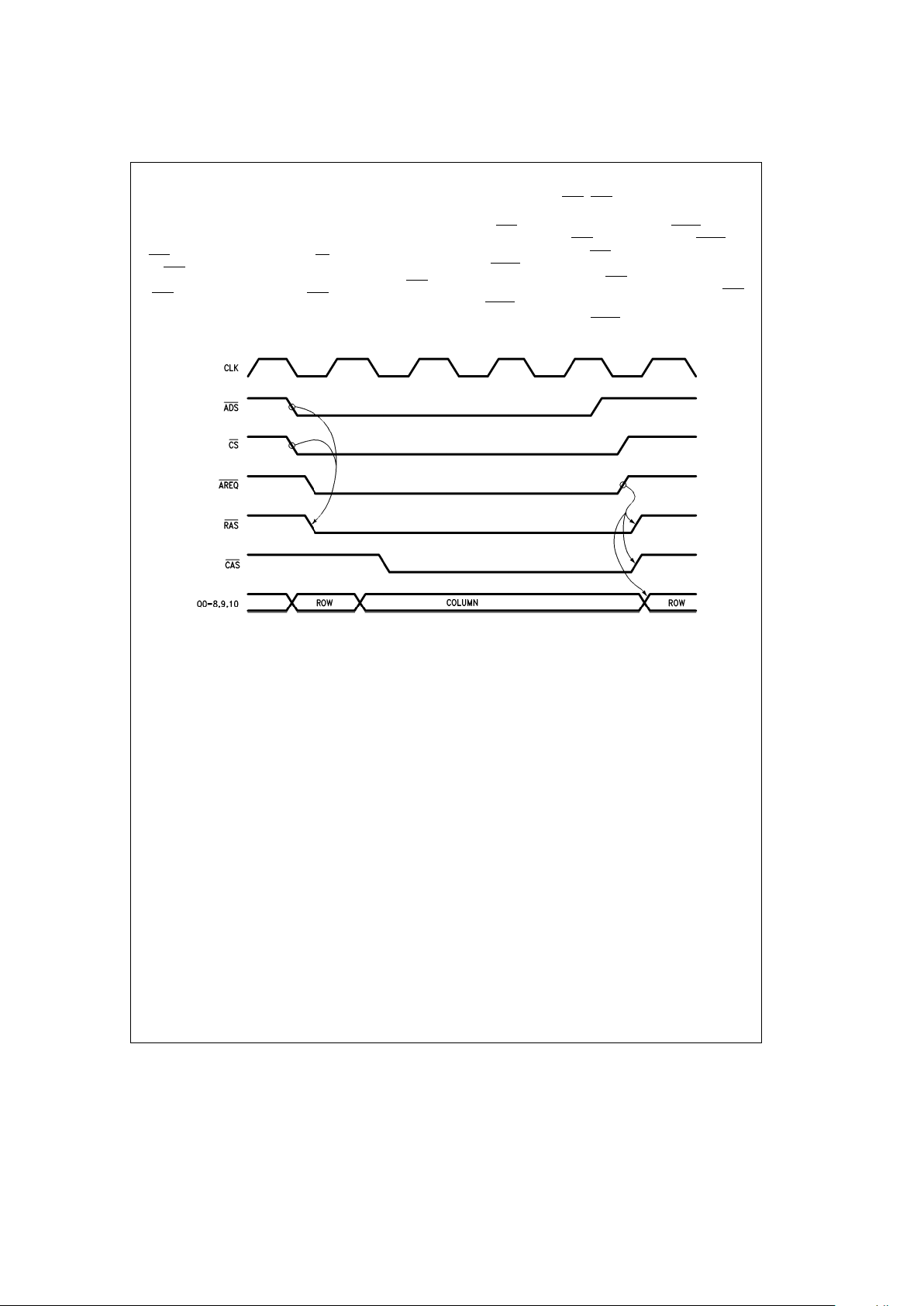

4.2 ACCESS MODE 1

Mode 1, asynchronous access, is selected by asserting the

input B1 during programming (B1

e

1). This mode allows accesses to start immediately from the access request input,

ADS

. To initiate a Mode 1 access, CS is asserted followed

by ADS

asserted. If precharge time was met, a refresh of

the DRAM or a Port B access was not in progress, the RAS

(RASs) would be asserted from ADS being asserted. If a

refresh or Port B access is in progress or precharge time is

required, the controller will wait until these events have tak-

en place and assert RAS

(RASs) from the next rising edge

of clock.

When ADS

is asserted or sometime after, AREQ must be

asserted. At this time, ADS

can be negated and AREQ will

continue the access. Also, ADS

can continue to be asserted

after AREQ

has been asserted and negated; however, a

new access will not start until ADS

is negated and asserted

again. When address pipelining is not implemented, ADS

and AREQ can be tied together.

The access will end when AREQ is negated.

TL/F/11118– 9

FIGURE 8b. Access Mode 1

13

Page 14

4.0 Port A Access Modes (Continued)

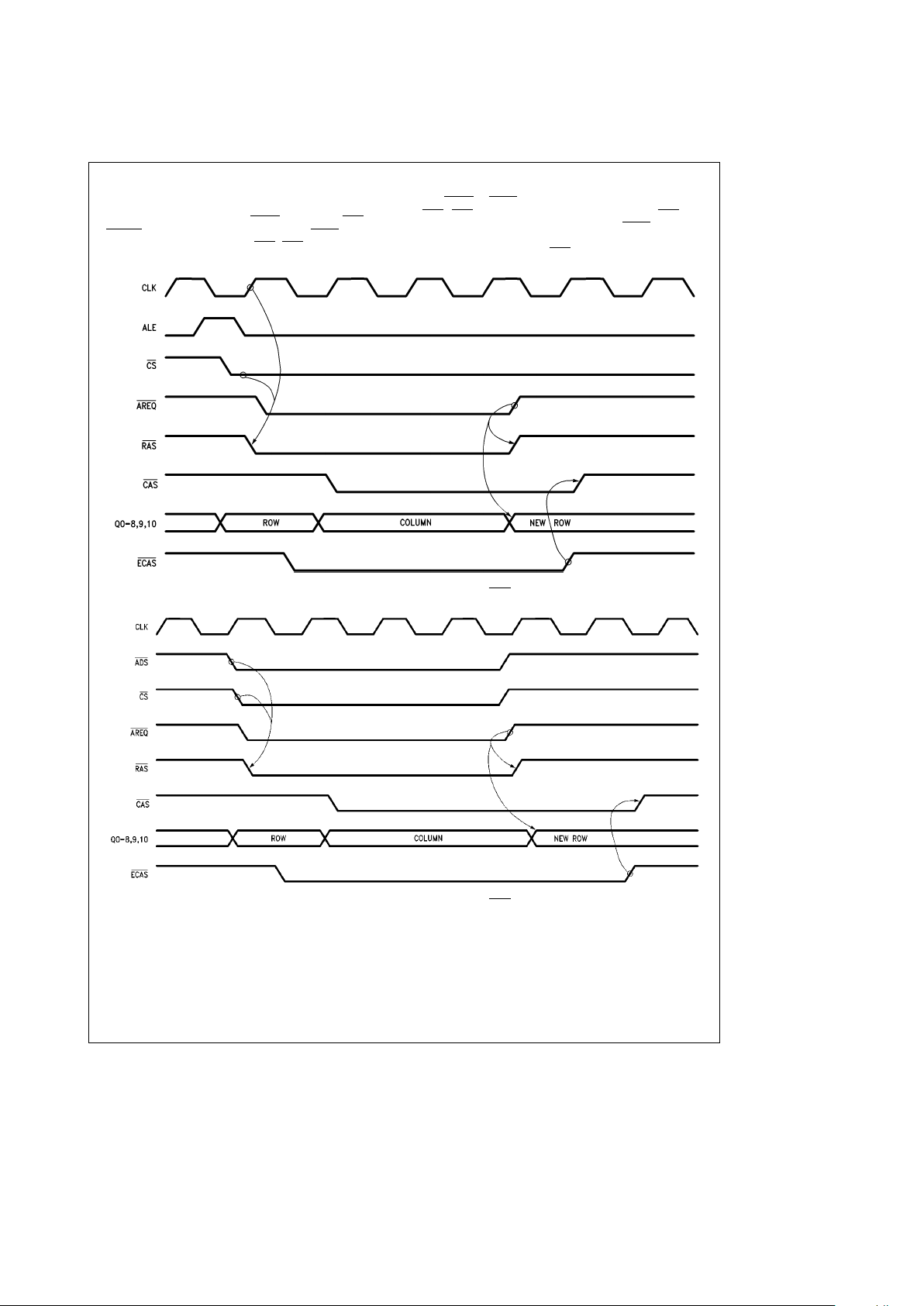

4.3 EXTENDING CAS WITH EITHER ACCESS MODE

In both access modes, once AREQ

is negated, RAS and

DTACK

if programmed will be negated. If ECAS0 was as-

serted (0) during programming, CAS

(CASs) will be negated

with AREQ

. If ECAS0 was negated (1) during programming,

CAS

(CASs) will continue to be asserted after RAS has

been negated, given that the appropriate ECAS

inputs are

asserted. This allows a DRAM to have data present on the

data out bus while gaining RAS

precharge time.

TL/F/11118– 10

FIGURE 9a. Access Mode 0 Extending CAS

TL/F/11118– 11

FIGURE 9b. Access Mode 1 Extending CAS

14

Page 15

4.0 Port A Access Modes (Continued)

4.4 READ-MODIFY-WRITE CYCLES WITH EITHER ACCESS MODE

There are 2 methods by which this chip can be used to do

read-modify-write access cycles. The first method involves

doing a late write access where the WIN

input is asserted

some delay after CAS

is asserted. The second method involves doing a page mode read access followed by a page

mode write access with RAS

held low (see

Figure 9c

).

CASn must be toggled using the ECASn inputs and WIN has

to be changed from negated to asserted (read to write)

while CAS

is negated. This method is better than changing

WIN

from negated to asserted in a late write access because here a problem may arise with DATA IN and DATA

OUT being valid at the same time. This may result in a data

line trying to drive two different levels simultaneously. The

page mode method of a read-modify-write access allows

the user to have transceivers in the system because the

data in (read data) is guaranteed to be high impedance during the time the data out (write data) is valid.

TL/F/11118– 12

*There may be idle states inserted here by the CPU.

FIGURE 9c. Read-Modify-Write Access Cycle

15

Page 16

4.0 Port A Access Modes (Continued)

4.5 ADDITIONAL ACCESS SUPPORT FEATURES

To support the different modes of accessing, the DP8430V/

31V/32V offer other access features. These additional features include: Address Latches and Column Increment (for

page/burst mode support), Address Pipelining, and Delay

CAS

(to allow the user with a multiplexed bus to ensure

valid data is present before CAS

is asserted).

4.5.1 Address Latches and Column Increment

The Address Latches can be programmed, through programming bit B0. They can be programmed to either latch

the address or remain in a fall-through mode. If the address

latches are used to latch the address, the controller will

function as follows:

In Mode 0, the rising edge of ALE places the latches in fallthrough, once ALE is negated, the address present in the

row, column and bank input is latched.

In Mode 1, the address latches are in fall through mode until

ADS

is asserted. ADS asserted latches the address.

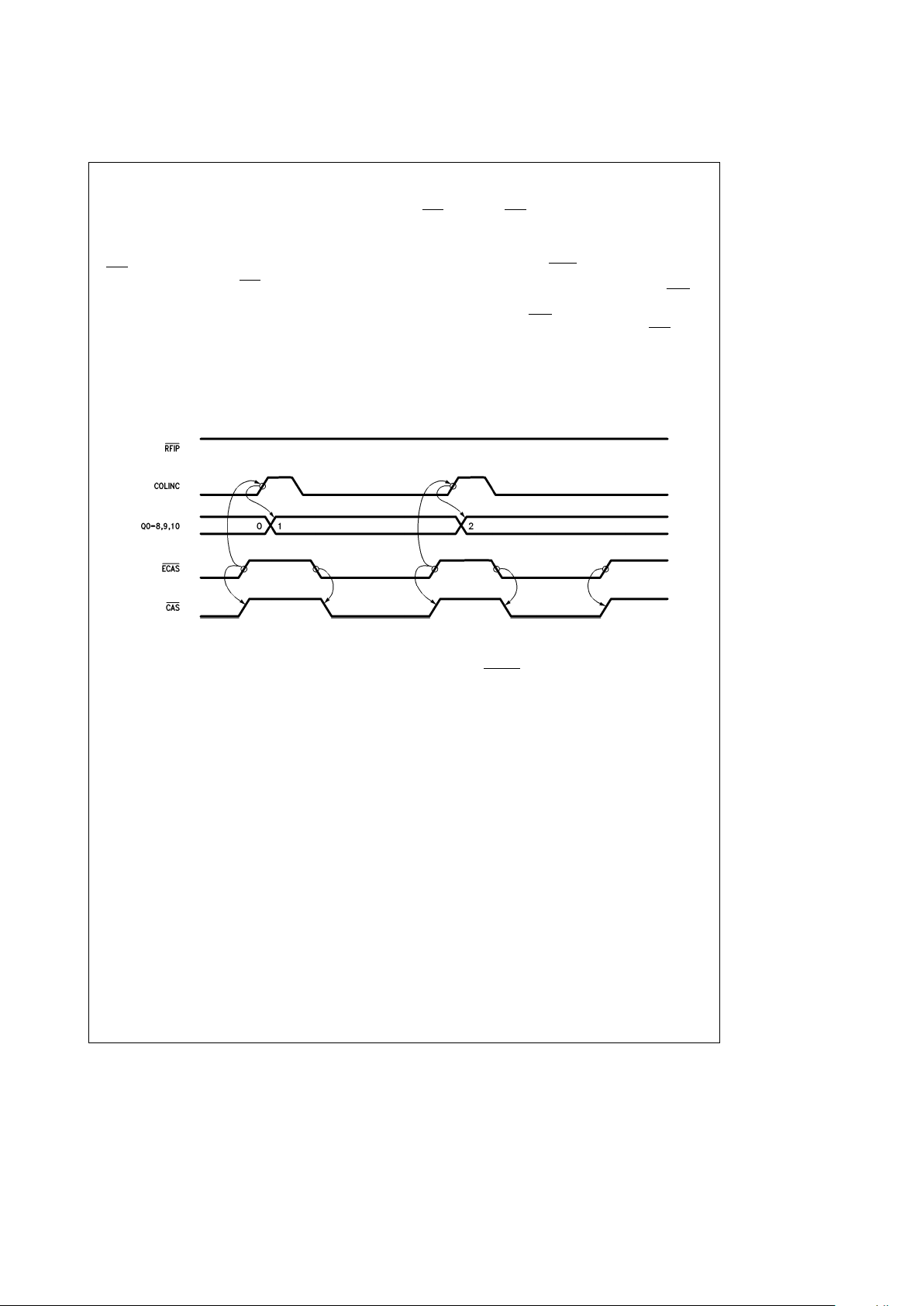

Once the address is latched, the column address can be

incremented with the input COLINC. COLINC can be used

for sequential accesses of static column DRAMs. COLINC

can also be used with the ECAS

inputs to support sequen-

tial accesses to page mode DRAMs as shown in

Figure 10

.

COLINC should only be asserted when the signal RFIP

is

negated during an access since this input functions as extended refresh when RFIP

is asserted. COLINC must be

negated (0) when the address is being latched (ADS

falling

edge in Mode 1). If COLINC is asserted with all of the bits of

the column address asserted (ones), the column address

will return to zero.

TL/F/11118– 13

FIGURE 10. Column Increment

The address latches function differently with the DP8432V.

The DP8432V will latch the address of the currently granted

port. If Port A is currently granted, the address will be

latched as described in Section 4.5.1. If Port A is not granted, and requests an access, the address will be latched on

the first or second positive edge of CLK after GRANTB has

been negated depending on the programming bits R0, R1.

For Port B, if GRANTB is asserted, the address will be

latched with AREQB

asserted. If GRANTB is negated, the

address will latch on the first or second positive edge of

CLK after GRANTB is asserted depending on the programming bits R0, R1.

16

Page 17

4.0 Port A Access Modes (Continued)

4.5.2 Address Pipelining

Address pipelining is the overlapping of accesses to different banks of DRAM. If the majority of successive accesses

are to a different bank, the accesses can be overlapped.

Because of this overlapping, the cycle time of the DRAM

accesses are greatly reduced. The DP8430V/31V/32V can

be programmed to allow a new row address to be placed on

the DRAM address bus after the column address hold time

has been met. At this time, a new access can be initiated

with ADS

or ALE, depending on the access mode, while

AREQ

is used to sustain the current access. The DP8432V

supports address pipelining for Port A only. This mode cannot be used with page, static column or nibble modes of

operations because the DRAM column address is switched

back to the row address after CAS

is asserted. This mode is

programmed through address bit R8 (see

Figures 11a

and

11b

).

During address pipelining in Mode 0, shown in

Figure 11c

,

ALE cannot be pulsed high to start another access until

AREQ

has been asserted for the previous access for at

least one period of CLK. DTACK

, if programmed, will be

negated once AREQ

is negated. WAIT, if programmed to

insert wait states, will be asserted once ALE and CS

are

asserted.

In Mode 1, shown in

Figure 11d

, ADS can be negated once

AREQ

is asserted. After meeting the minimum negated

pulse width for ADS

, ADS can again be asserted to start a

new access. DTACK

, if programmed, will be negated once

AREQ

is negated. WAIT, if programmed, will be asserted

once ADS

is asserted.

In either mode with either type of wait programmed, the

DP8430V/31V/32V will still delay the access for precharge

if sequential accesses are to the same bank or if a refresh

takes place.

TL/F/11118– 14

FIGURE 11a. Non-Address Pipelined Mode

TL/F/11118– 15

FIGURE 11b. Address Pipelined Mode

17

Page 18

4.0 Port A Access Modes (Continued)

TL/F/11118– 16

FIGURE 11c. Mode 0 Address Pipelining (WAIT of 0, (/2T Has Been Programmed.

WAIT

is Sampled at the ‘‘T3’’ Falling Clock Edge)

TL/F/11118– 17

FIGURE 11d. Mode 1 Address Pipelining (DTACK 1(/2T Programmed, DTACK is Sampled at the ‘‘T3’’ Falling Clock Edge)

18

Page 19

4.0 Port A Access Modes (Continued)

4.5.3 Delay CAS

during Write Accesses

Address bit C9 asserted during programming will cause CAS

to be delayed until the first positive edge of CLK after RAS

is asserted when the input WIN is asserted. Delaying CAS

during write accesses ensures that the data to be written to

DRAM will be setup to CAS

asserting as shown in

Figures

12a

and

12b.

If the possibility exists that data still may not

be present after the first positive edge of CLK, CAS

can be

delayed further with the ECAS

inputs. If address bit C9 is

negated during programming, read and write accesses will

be treated the same (with regard to CAS

).

TL/F/11118– 18

FIGURE 12a. Mode 0 Delay CAS

TL/F/11118– 19

FIGURE 12b. Mode 1 Delay CAS

19

Page 20

5.0 Refresh Options

The DP8430V/31V/32V support two refresh control mode

options:

1. Automatic Internally Controlled Refresh.

2. Externally Controlled Refresh.

With each of the control modes above, three types of refresh can be performed.

1. All RAS

Refresh.

2. Staggered Refresh.

3. Error Scrubbing During All RAS Refresh.

There are two inputs, EXTNDRF and RFSH

and two out-

puts, RFIP

and RFRQ, associated with refresh. There are

also ten programming bits: R0 – 1, R9, C0 –6 and ECAS0

used to program the various types of refreshing.

Asserting the input EXTNDRF, extends the refresh cycle for

a single or multiple integral periods of CLK.

The output RFIP

is asserted one period of CLK before the

first refresh RAS

is asserted. If an access is currently in

progress, RFIP

will be asserted up to one period of CLK

before the first refresh RAS

, after AREQ or AREQB is nega-

ted for the access (see

Figure 13

).

The DP8430V/31V/32V will increment the refresh address

counter automatically, independent of the refresh mode

used. The refresh address counter will be incremented once

all the refresh RAS

s have been negated.

In every combination of refresh control mode and refresh

type, the DP8430V/31V/32V is programmed to keep RAS

asserted a number of CLK periods. The time values of RAS

low during refresh are programmed through programming

bits R0 and R1.

5.1 REFRESH CONTROL MODES

5.1.1. Automatic Internal Refresh

To select Automatic Internal Refresh, the user must choose

ECAS0

e

0 during programming. The DP8430V/31V/32V

have an internal refresh clock. The period of the refresh

clock is generated from the programming bits C0 – 3. Every

period of the refresh clock, an internal refresh request is

generated. As long as a DRAM access is not currently in

progress and precharge time has been met, the internal refresh request will generate an automatic internal refresh. If a

DRAM access is in progress, the DP8430V/31V/32V onchip arbitration logic will wait until the access is finished

before performing the refresh. The refresh/access arbitration logic can insert a refresh cycle between two address

pipelined accesses. However, the refresh arbitration logic

can not interrupt an access cycle to perform a refresh.

TL/F/11118– 20

Explanation of Terms

RFRQeReFresh ReQuest internal to the DP8430V/31V/32V. RFRQ has the ability to hold off a pending access.

RFSH

e

Externally requested ReFreSH

RFIP

e

ReFresh in Progress

ACIP

e

Port A or Port B (DP8432V only) ACcess in Progress. This means that either RAS is low for an access or is in the process of

transitioning low for an access.

FIGURE 13. DP8430V/31V/32V Access/Refresh Arbitration State Program

20

Page 21

5.0 Refresh Options (Continued)

5.1.2 Externally Controlled Refresh Mode

To choose this refresh mode, the user must program

ECAS0

e

1. When this mode is selected, the user is responsible for generating refresh requests by asserting the

input RFSH

every time a refresh cycle is to be performed. In

this refresh mode, the output WE

functions a RFRQ.

When Externally Controlled Refresh is selected, the user

may choose to monitor the output ReFresh ReQuest

(RFRQ

) for an indication from the DRAM controller that a

refresh is needed. When this output asserts, it indicates that

the internal refresh clock has expired and that another refresh is necessary. Then the user has two options. First, he

can answer immediately asserting the input RFSH

requesting a refresh cycle. In this case a refresh will take place

immediately if no access is in progress and precharge time

for the previous access has been met. See

Figure 14a

.

TL/F/11118– 21

FIGURE 14a. Automatic Internal Refresh with Refresh Request (3T of RAS Low during Refresh Programmed)

Second, the user may choose not to assert the RFSH

input

delaying the refresh until later. RFRQ

will go high and then

assert (toggle) if additional periods of the internal refresh

clock have expired and the user has not performed a refresh by asserting the input RFSH

. See

Figure 14b

. If a time

critical event, or a long access like page or static column

mode can not be interrupted, RFRQ

pulsing high can be

used to increment an external counter. This counter can

later be used to perform a burst refresh of the number of

refreshes missed (through the RFSH

input). This scheme

can be thought of as Refresh Request/Acknowledge.

TL/F/11118– 22

FIGURE 14b. Refresh Request Timing

21

Page 22

5.0 Refresh Options (Continued)

In Externally Controlled Refresh the user does not have to

wait for RFRQ

to perform a refresh. The user can at any

time assert the RFSH

input. Pulsing RFSH low, sets an internal latch that is used to produce the internal refresh request. The refresh cycle will take place on the next positive

edge of clock, as shown in

Figure 15a

. If an access to the

DRAM is in progress or precharge time for the last access

has not been met, the refresh will be delayed. Since pulsing

RFSH

low sets a latch, the user doesn’t have to keep RFSH

low until the refresh starts. When the last refresh RAS negates, the internal refresh request latch is cleared.

By keeping the input RFSH

asserted past the positive edge

of CLK which ends the refresh cycle as shown in

Figure

15b

, the user will perform another refresh cycle. Each refresh cycle during a burst refresh will meet the refresh RAS

low time and the RAS precharge time (programming bits

R0–1). This scheme can be thought of as Externally Controlled Burst Refresh. If the user desires to burst refresh the

entire DRAM, he could generate an end of count signal

(burst refresh finished), by looking at one of the DP8430V/

31V/32V high address outputs (Q7, Q8, Q9 or Q10) and the

RFIP

output. The Qn outputs function as a decode of how

many row addresses have been refreshed. (Q7

e

128 re-

freshes, Q8

e

256 refreshes, Q9e512 refreshes and Q10

e

1024 refreshes).

TL/F/11118– 23

FIGURE 15a. Single Externally Refreshes (2 Periods of RAS Low during Refresh Programmed)

TL/F/11118– 24

FIGURE 15b. External Burst Refresh

(2 Periods of RAS

Precharge, 2 Periods of Refresh RAS Low during Refresh Programmed)

22

Page 23

5.0 Refresh Options (Continued)

5.2 REFRESH CYCLE TYPES

Three different types of refresh cycles are available for use.

The three different types are mutually exclusive and can be

used with any of the three modes of refresh control. The

three different refresh cycle types are: all RAS

refresh, stag-

gered RAS

refresh and error scrubbing during all RAS re-

fresh. In all refresh cycle types, the RAS

precharge time is

guaranteed: between the previous access RAS

ending and

the refresh RAS

0 starting; between refresh RAS3 ending

and access RAS

beginning; between burst refresh RASs.

5.2.1 Conventional RAS

Refresh

A conventional refresh cycle causes RAS0 –3 to all assert

from the first positive edge of CLK after RFIP

is asserted as

shown in

Figure 16

. RAS0 –3 will stay asserted until the

number of positive edges of CLK programmed have passed.

On the last positive edge, RAS

0–3, and RFIP will be negated. This type of refresh cycle is programmed by negating

address bit R9 during programming.

TL/F/11118– 25

FIGURE 16. Conventional RAS Refresh

5.2.2 Staggered RAS

Refresh

A staggered refresh staggers each RAS or group of RASs

by a positive edge of CLK as shown in

Figure 17

. The num-

ber of RAS

s, which will be asserted on each positive edge

of CLK, is determined by the RAS

, CAS configuration mode

programming bits C4 – C6. If single RAS

outputs are select-

ed during programming, then each RAS

will assert on suc-

cessive positive edges of CLK. If two RAS

outputs are se-

lected during programming then RAS

0 and RAS1 will assert

on the first positive edge of CLK after RFIP

is asserted.

RAS

2 and RAS3 will assert on the second positive edge of

CLK after RFIP

is asserted. If all RAS outputs were selected

during programming, all RAS

outputs would assert on the

first positive edge of CLK after RFIP

is asserted. Each RAS

or group of RASs will meet the programmed RAS low time

and then negate.

TL/F/11118– 26

FIGURE 17. Staggered RAS Refresh

23

Page 24

5.0 Refresh Options (Continued)

5.2.3 Error Scrubbing during Refresh

The DP8430V/31V/32V support error scrubbing during all

RAS

DRAM refreshes. Error scrubbing during refresh is selected through bits C4 –C6 with bit R9 negated during programming. Error scrubbing can not be used with staggered

refresh (see Section 8.0). Error scrubbing during refresh allows a CAS

or group of CASs to assert during the all RAS

refresh as shown in

Figure 18

. This allows data to be read

from the DRAM array and passed through an Error Detection And Correction Chip, EDAC. If the EDAC determines

that the data contains a single bit error and corrects that

error, the refresh cycle can be extended with the input ex-

tend refresh, EXTNDRF, and a read-modify-write operation

can be performed by asserting WE

. It is the responsibility of

the designer to ensure that WE

is negated. The DP8432V

has a 24-bit internal refresh address counter that contains

the 11 row, 11 column and 2 bank addresses. The

DP8430V/31V have a 22-bit internal refresh address counter that contains the 10 row, 10 column and 2 bank addresses. These counters are configured as bank, column, row

with the row address as the least significant bits. The bank

counter bits are then used with the programming selection

to determine which CAS

or group of CASs will assert during

a refresh.

TL/F/11118– 27

FIGURE 18. Error Scrubbing during Refresh (Two Refresh Cycles Shown)

24

Page 25

5.0 Refresh Options (Continued)

5.3 EXTENDING REFRESH

The programmed number of periods of CLK that refresh

RAS

s are asserted can be extended by one or multiple peri-

ods of CLK. Only the all RAS

(with or without error scrubbing) type of refresh can be extended. To extend a refresh

cycle, the input extend refresh, EXTNDRF, must be asserted before the positive edge of CLK that would have negated

all the RAS

outputs during the refresh cycle and after the

positive edge of CLK which starts all RAS

outputs during the

refresh as shown in

Figure 19

. This will extend the refresh to

the next positive edge of CLK and EXTNDRF will be sampled again. The refresh cycle will continue until EXTNDRF is

sampled low on a positive edge of CLK.

TL/F/11118– 28

FIGURE 19. Extending Refresh with the Extend Refresh (EXTNDRF) Input

6.0 Port A Wait State Support

Wait states allow a CPU’s access cycle to be increased by

one or multiple CPU clock periods. The wait or ready input is

named differently by CPU manufacturers. However, any

CPU’s wait or ready input is compatible with either the WAIT

or DTACK output of the DP8430V/31V/32V. The user determines whether to program WAIT

or DTACK (R7) and

which value to select for WAIT

or DTACK (R2, R3) depending upon the CPU used and where the CPU samples its wait

input during an access cycle.

The decision to terminate the CPU access cycle is directly

affected by the speed of the DRAMs used. The system designer must ensure that the data from the DRAMs will be

present for the CPU to sample or that the data has been

written to the DRAM before allowing the CPU access cycle

to terminate.

The insertion of wait states also allows a CPU’s access cycle to be extended until the DRAM access has taken place.

The DP8430V/31V/32V insert wait states into CPU access

cycles due to; guaranteeing precharge time, refresh currently in progress, user programmed wait states, the WAITIN

signal being asserted and GRANTB not being valid

(DP8432V only). If one of these events is taking place and

the CPU starts an access, the DP8430V/31V/32V will insert

wait states into the access cycle, thereby increasing the

length of the CPU’s access. Once the event has been completed, the DP8430V/31V/32V will allow the access to take

place and stop inserting wait states.

There are six programming bits, R2 – R7; an input, WAITIN

;

and an output that functions as WAIT

or DTACK.

6.1 WAIT

TYPE OUTPUT

With the R7 address bit negated during programming, the

user selects the WAIT

output. As long as WAIT is sampled

asserted by the CPU, wait states (extra clock periods) are

inserted into the current access cycle as shown in

Figure

20

. Once WAIT is sampled negated, the access cycle is

completed by the CPU. WAIT

is asserted at the beginning of

a chip selected access and is programmed to negate a

number of positive edges and/or negative levels of CLK

from the event that starts the access. WAIT

can also be

programmed to function in page/burst mode applications.

Once WAIT

is negated during an access, and the ECAS

inputs are negated with AREQ asserted, WAIT can be programmed to toggle, following the ECAS

inputs. Once AREQ

is negated, ending the access, WAIT will stay negated until

the next chip selected access. For more details about WAIT

Type Output, see Application Note AN-773.

TL/F/11118– 29

FIGURE 20. WAIT Type Output

25

Page 26

6.0 Port A Wait State Support (Continued)

6.2 DTACK

TYPE OUTPUT

With the R7 address bit asserted during programming, the

user selects the DTACK

type output. As long as DTACK is

sampled negated by the CPU, wait states are inserted into

the current access cycle as shown in

Figure 21.

Once

DTACK

is sampled asserted, the access cycle is completed

by the CPU. DTACK

, which is normally negated, is programmed to assert a number of positive edges and/or negative levels from the event that starts RAS

for the access.

DTACK

can also be programmed to function during page/

burst mode accesses. Once DTACK

is asserted and the

ECAS

inputs are negated with AREQ asserted, DTACK can

be programmed to negate and assert from the ECAS

inputs

toggling to perform a page/burst mode operation. Once

AREQ

is negated, ending the access, DTACK will be negated and stays negated until the next chip selected access.

For more details about DTACK

type output see Application

Note AN-773.

6.3 DYNAMICALLY INCREASING THE

NUMBER OF WAIT STATES

The user can increase the number of positive edges of CLK

before DTACK

is asserted or WAIT is negated. With the

input WAITIN

asserted, the user can delay DTACK asserting

or WAIT

negating either one or two more positive edges of

CLK. The number of edges is programmed through address

bit R6. If the user is increasing the number of positive edges

in a delay that contains a negative level, the positive edges

will be met before the negative level. For example if the user

programmed DTACK

of (/2T, asserting WAITIN, programmed as 2T, would increase the number of positive edges resulting in DTACK

of 2(/2T as shown in

Figure 22a

. Simi-

larly, WAITIN

can increase the number of positive edges in

a page/burst access. WAITIN

can be permanently asserted

in systems requiring an increased number of wait states.

WAITIN

can also be asserted and negated, depending on

the type of access. As an example, a user could invert the

WRITE

line from the CPU and connect the output to

WAITIN

. This could be used to perform write accesses with

1 wait state and read accesses with 2 wait states as shown

in

Figure 22b

.

TL/F/11118– 30

FIGURE 21. DTACK Type Output

TL/F/11118– 31

FIGURE 22a. WAITIN Example (DTACK is Sampled at the ‘‘T3’’ Falling Clock Edge)

26

Page 27

6.0 Port A Wait State Support (Continued)

TL/F/11118– 32

FIGURE 22b. WAITIN Example (WAIT is Sampled at the End of ‘‘T2’’).

6.4 GUARANTEEING RAS

LOW TIME

AND RAS

PRECHARGE TIME

The DP8430V/31V/32V will guarantee RAS precharge time

between accesses; between refreshes; and between access and refreshes. The programming bits R0 and R1 are

used to program combinations of RAS

precharge time and

RAS

low time referenced by positive edges of CLK. RAS

low time is programmed for refreshes only. During an access, the system designer guarantees the time RAS

is asserted through the DP8430V/31V/32V wait logic. Since inserting wait states into an access increases the length of

the CPU signals which are used to create ADS

or ALE and

AREQ

, the time that RAS is asserted can be guaranteed.

The precharge time is also guaranteed by the DP8430V/

31V/32V. Each RAS

output has a separate positive edge

of CLK counter. AREQ

is negated setup to a positive edge

of CLK to terminate the access. That positive edge is 1T.

The next positive edge is 2T. RAS

will not be asserted until

the programmed number of positive edges of CLK have

passed as shown in

Figure 23

. Once the programmed pre-

charge time has been met, RAS

will be asserted from the

positive edge of CLK. However, since there is a precharge

counter per RAS

, an access using another RAS will not be

delayed. Precharge time before a refresh is always referenced from the access RAS

negating before RAS0 for the

refresh asserting. After a refresh, precharge time is referenced from RAS

3 negating, for the refresh, to the access

RAS

asserting.

TL/F/11118– 33

FIGURE 23. Guaranteeing RAS Precharge (DTACK is Sampled at the ‘‘T2’’ Falling Clock Edge)

27

Page 28

7.0 RAS and CAS Configuration Modes

The DP8430V/31V/32V allow the user to configure the

DRAM array to contain one, two or four banks of DRAM.

Depending on the functions used, certain considerations

must be used when determining how to set up the DRAM

array. Programming address bits C4, C5 and C6 along with

bank selects, B0 – 1, and CAS

enables, ECAS0–3, deter-

mine which RAS

or group of RASs and which CAS or group

of CAS

s will be asserted during an access. Different memory schemes are described. The DP8430V/31V/32V is specified driving a heavy load of 72 DRAMs, representing four

banks of DRAM with 16-bit words and 2 parity bits. The

DP8430V/31V/32V can drive more than 72 DRAMs, but the

AC timing must be increased. Since the RAS

and CAS out-

puts are configurable, all RAS

and CAS outputs should be

used for the maximum amount of drive.

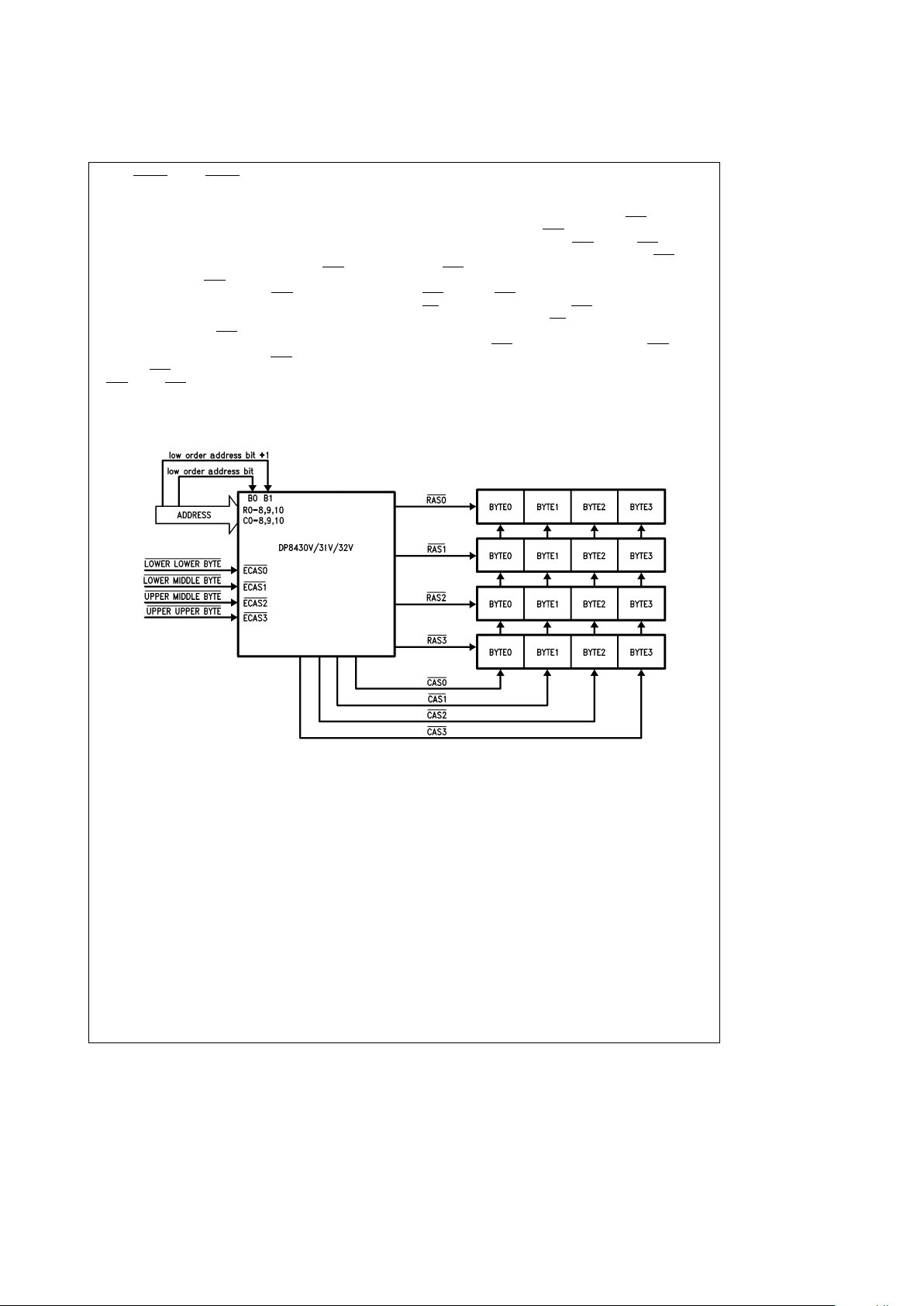

7.1 BYTE WRITING

By selecting a configuration in which all CAS

outputs are

selected during an access, the ECAS

inputs enable a single

or group of CAS

outputs to select a byte (or bytes) in a word

size of up to 32 bits. In this case, the RAS

outputs are used

to select which of up to 4 banks is to be used as shown in

Figures 24a

and

24b

. In systems with a word size of 16 bits,

the byte enables can be gated with a high order address bit

to produce four byte enables which gives an equivalent to 8

banks of 16-bit words as shown in

Figure 24d

. If less memo-

ry is required, each CAS

should be used to drive each nibble

in the 16-bit word as shown in

Figure 24c

.

TL/F/11118– 34

FIGURE 24a. DRAM Array Setup for 32-Bit System (C6, C5, C4e1, 1, 0 during Programming)

TL/F/11118– 35

FIGURE 24b. DRAM Array Setup for 32-Bit, 1 Bank System (C6, C5, C4e0, 0, 0 Allowing Error Scrubbing

or C6, C5, C4

e

0, 1, 1 No Error Scrubbing during Programming)

28

Page 29

7.0 RAS and CAS Configuration Modes (Continued)

TL/F/11118– 36

FIGURE 24c. DRAM Array Setup for 16-Bit System (C6, C5, C4e1, 1, 0 during Programming)

TL/F/11118– 37

FIGURE 24d. 8 Bank DRAM Array for 16-Bit System (C6, C5, C4e1, 1, 0 during Programming)

29

Page 30

7.0 RAS and CAS Configuration Modes (Continued)

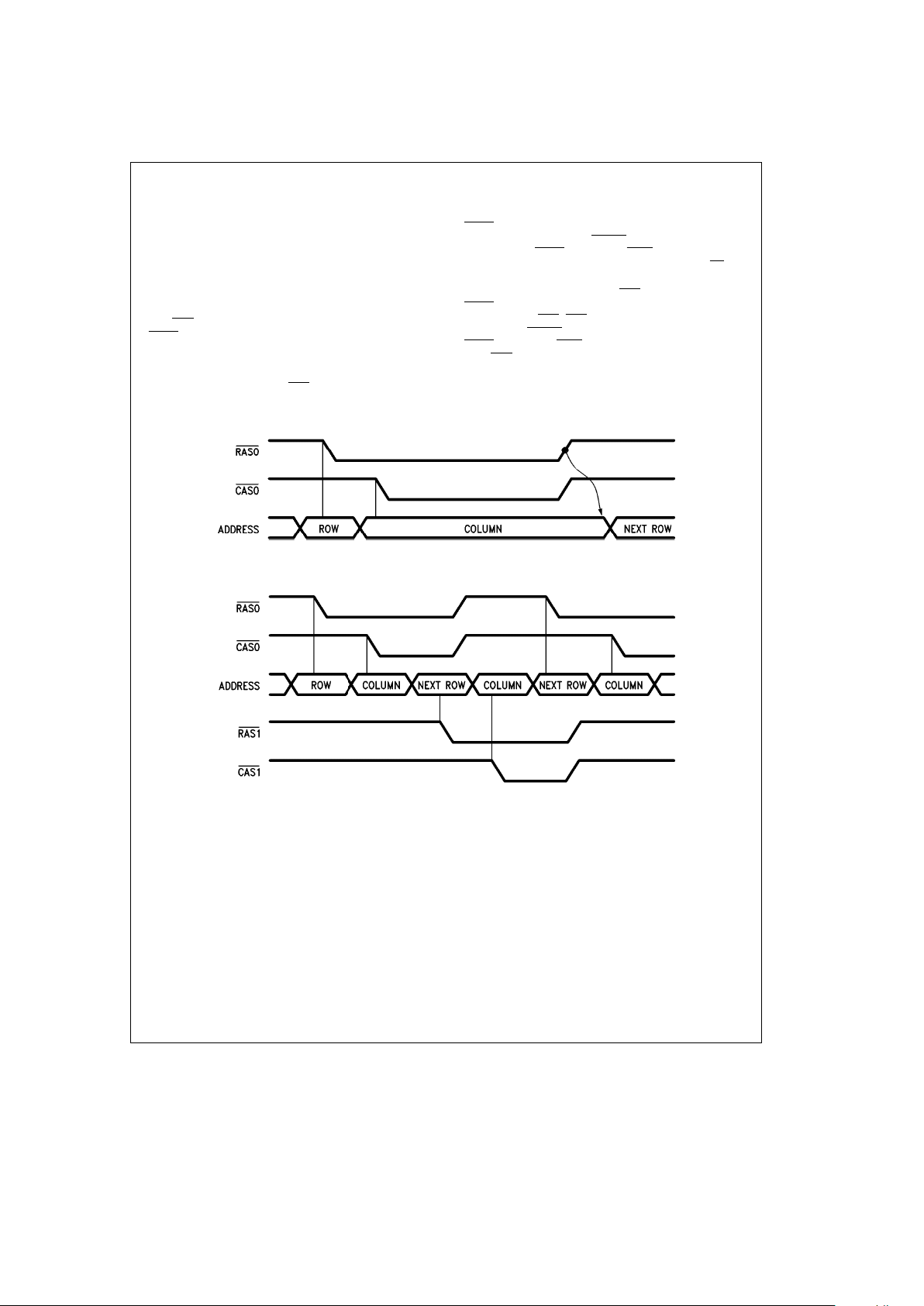

7.2 MEMORY INTERLEAVING

Memory interleaving allows the cycle time of DRAMs to be

reduced by having sequential accesses to different memory

banks. Since the DP8430V/31V/32V have separate precharge counters per bank, sequential accesses will not be

delayed if the accessed banks use different RAS

outputs.

To ensure different RAS

outputs will be used, a mode is

selected where either one or two RAS

outputs will be asserted during an access. The bank select or selects, B0 and

B1, are then tied to the least significant address bits, causing a different group of RAS

s to assert during each sequen-

tial access as shown in

Figure 25

. In this figure there should

be at least one clock period of all RAS

’s negated between

different RAS

’s being asserted to avoid the condition of a

CAS

before RAS refresh cycle.

7.3 ADDRESS PIPELINING

Address pipelining allows several access RAS

stobeas-

serted at once. Because RAS

s can overlap, each bank re-

quires either a mode where one RAS

and one CAS are used

per bank as shown in

Figure 26a

or where two RASs and

two CAS

s are used per bank as shown in

Figure 26b

. Byte

writing can be accomplished in a 16-bit word system if two

RAS

s and two CASs are used per bank. In other systems,

WE

s (or external gating on the CAS outputs) must be used

to perform byte writing. If WE

s are used separate data in

and data out buffers must be used. If the array is not layed

out this way, a CAS

to a bank can be low before RAS, which

will cause a refresh of the DRAM, not an access. To take

full advantage of address pipelining, memory interleaving is

used. To memory interleave, the least significant address

bits should be tied to the bank select inputs to ensure that

all ‘‘back to back’’ sequential accesses are not delayed,

since different memory banks are accessed.

TL/F/11118– 38

FIGURE 25. Memory Interleaving (C6, C5, C4e1, 1, 0 during Programming)

30

Page 31

7.0 RAS and CAS Configuration Modes (Continued)

TL/F/11118– 39

FIGURE 26a. DRAM Array Setup for 4 Banks Using Address Pipelining (C6, C5, C4e1, 1, 1

or C6, C5, C4

e

0, 1, 0 (Also Allowing Error Scrubbing) during Programming)

TL/F/11118– 40

FIGURE 26b. DRAM Array Setup for Address Pipelining with 2 Banks (C6, C5, C4e1, 0, 1

or C6, C5, C4

e

0, 0, 1 (Also Allowing Error Scrubbing) during Programming)

7.4 ERROR SCRUBBING

In error scrubbing during refresh, the user selects one, two

or four RAS

and CAS outputs per bank. When performing

error detection and correction, memory is always accessed

as words. Since the CAS

signals are not used to select

individual bytes, the ECAS

inputs can be tied low as shown

in

Figures 27a

and

27b

.

TL/F/11118– 41

FIGURE 27a. DRAM Array Setup for 4 Banks Using Error Scrubbing (C6, C5, C4e0, 1, 0 during Programming)

TL/F/11118– 42

FIGURE 27b. DRAM Array Setup for Error Scrubbing with 2 Banks (C6, C5, C4e0, 0, 1 during Programming)

31

Page 32

7.0 RAS and CAS Configuration Modes (Continued)

7.5 PAGE/BURST MODE

In a static column, page or burst mode system, the least

significant bits must be tied to the column address in order

to ensure that the page/burst accesses are to sequential

memory addresses, as shown in

Figure 28.

In a nibble

mode system, the least significant bits must be tied to the

highest column and row address bits in order to ensure that

sequential address bits are the ‘‘nibble’’ bits for nibble mode

accesses

(Figure 28)

. The ECAS inputs may then be tog-

gled with the DP8430V/31V/32V’s address latches in fallthrough mode, while AREQ

is asserted. The ECAS inputs

can also be used to select individual bytes. When using nibble mode DRAMS, the third and fourth address bits can be

tied to the bank select inputs to perform memory interleaving. In page or static column modes, the two address bits

after the page size can be tied to the bank select inputs to

select a new bank if the page size is exceeded.

TL/F/11118– 43

*See table below for row, column & bank address bit map. A0, A1 are used for byte addressing in this example.

Addresses Nibble Mode*

Page Mode/Static Column Mode Page Size

256 Bits/Page 512 Bits/Page 1024 Bits/Page 2048 Bits/Page

Column C9,R9eA2,A3 C0– 7eA2–9 C0–8eA2–10 C0–9eA2–11

C0–10

e

A2–12

Address C0 –8

e

X C8–10eX C9,10eX C10eX

Row

XXX X X

Address

B0 A4 A10 A11 A12 A13

B1 A5 A11 A12 A13 A14

Assume that the least significant address bits are used for byte addressing. Given a 32-bit system A0,A1 would be

used for byte addressing.

X

e

DON’T CARE, the user can do as he pleases.

*Nibble mode values for R and C assume a system using 1 Mbit DRAMs.

FIGURE 28. Page, Static Column, Nibble Mode System

32

Page 33

8.0 Test Mode

Staggered refresh in combination with the error scrubbing

mode places the DP8430V/31V/32V in test mode. In this

mode, the 24-bit refresh counter is divided into a 13-bit and

11-bit counter. During refreshes both counters are incremented to reduce test time.

9.0 DRAM Critical Timing

Parameters

The two critical timing parameters, shown in

Figure 29

, that

must be met when controlling the access timing to a DRAM

are the row address hold time, t

RAH

, and the column ad-

dress setup time, t

ASC

. Since the DP8430V/31V/32V contain a precise internal delay line, the values of these parameters can be selected at programming time. These values

will also increase and decrease if DELCLK varies from

2 MHz.

9.1 PROGRAMMABLE VALUES OF t

RAH

AND t

ASC

The DP8430V/31V/32V allow the values of t

RAH

and t

ASC

to be selected at programming time. For each parameter,

two choices can be selected. t

RAH

, the row address hold

time, is measured from RAS

asserted to the row address

starting to change to the column address. The two choices

for t

RAH

are 15 ns and 25 ns, programmable through ad-

dress bit C8.

t

ASC

, the column address setup time, is measured from the

column address valid to CAS

asserted. The two choices for

t

ASC

are 0 ns and 10 ns, programmable through address bit

C7.

9.2 CALCULATION OF t

RAH

AND t

ASC

There are two clock inputs to the DP8430V/31V/32V.

These two clocks, DELCLK and CLK can either be tied together to the same clock or be tied to different clocks running asynchronously at different frequencies.

The clock input, DELCLK, controls the internal delay line

and refresh request clock. DELCLK should be a multiple of

2 MHz. If DELCLK is not a multiple of 2 MHz, t

RAH

and t

ASC

will change. The new values of t

RAH

and t

ASC

can be calcu-

lated by the following formulas:

If t

RAH

was programmed to equal 15 ns then t

RAH

e

15*(((DELCLK Divisor)* 2 MHz/(DELCLK Frequency))b1)

a

15 ns.

If t

RAH

was programmed to equal 25 ns then t

RAH

e

25*(((DELCLK Divisor)* 2 MHz/(DELCLK Frequency))b1)

a

25 ns.

If t

ASC

was programmed to equal 0 ns then t

ASC

e

12.5*

((DELCLK Divisor)* 2 MHz/(DELCLK Frequency))

b

12.5 ns.

If t

ASC

was programmed to equal 10 ns then t

ASC

e

22.5*

((DELCLK Divisor)* 2 MHz/(DELCLK Frequency))

b

12.5 ns.

Since the values of t

RAH

and t

ASC

are increased or de-

creased, the time to CAS

asserted will also increase or decrease. These parameters can be adjusted by the following

formula:

Delay to CAS

e

Actual Spec.aActual t

RAH

b

Programmed t

RAH

a

Actual t

ASC

b

Programmed t

ASC

.

TL/F/11118– 44

FIGURE 29. t

RAH

and t

ASC

33

Page 34

10.0 Dual Accessing (DP8432V)

The DP8432V has all the functions previously described. In

addition to those features, the DP8432V also has the capabilities to arbitrate among refresh, Port A and a second port,

Port B. This allows two CPUs to access a common DRAM

array. DRAM refresh has the highest priority followed by the

currently granted port. The ungranted port has the lowest

priority. The last granted port will continue to stay granted

even after the access has terminated, until an access request is received from the ungranted port (see

Figure 30a

).

The dual access configuration assumes that both Port A

and Port B are synchronous to the system clock. If they are

not synchronous to the system clock they should be externally synchronized (Ex. By running the access requests

through several Flip-Flops, see

Figure 32a

).

10.1 PORT B ACCESS MODE

Port B accesses are initiated from a single input, AREQB

.

When AREQB

is asserted, an access request is generated.

If GRANTB is asserted and a refresh is not taking place or

precharge time is not required, RAS

will be asserted when

AREQB