Page 1

1

4Bit Single Chip Microcontroller

DMC42C2008

DESCRIPTION

FEATURE

The DMC42C2008 is a 4-bit single chip micro- Memory Mapped I/O

computer with 8K bytes ROM, and is manufactured

with CMOS silicon gate technology. Program Memory : 8192 x 10 bits

The DMC42C2008 includes peripherals such as 8-bit

Timer/Event Counters, 4-bit A/D Converter, 14-bit Data Memory : 512 x 4 bits

PWM, 8-bit PWM, 6-bit PWM, Watchdog Timer, 4-ch

External Interrupts and OSD controller. Instructions

It provides the hardware features, architectural - Various Bit Manipulation

enhancements and instructions that are necessary - 8 bit Data Transfer, Compare, Arithmatic

to make it a powerful and cost effective controller - 7 bit Relative Branch

for applications requiring up to 64K bytes of program- - 1 byte Absolute Call

mable memory.

Instruction cycle times

- Main ( XI = 4.19MHz )

. 15.3 us ( XI/64 = 65.5KHz )

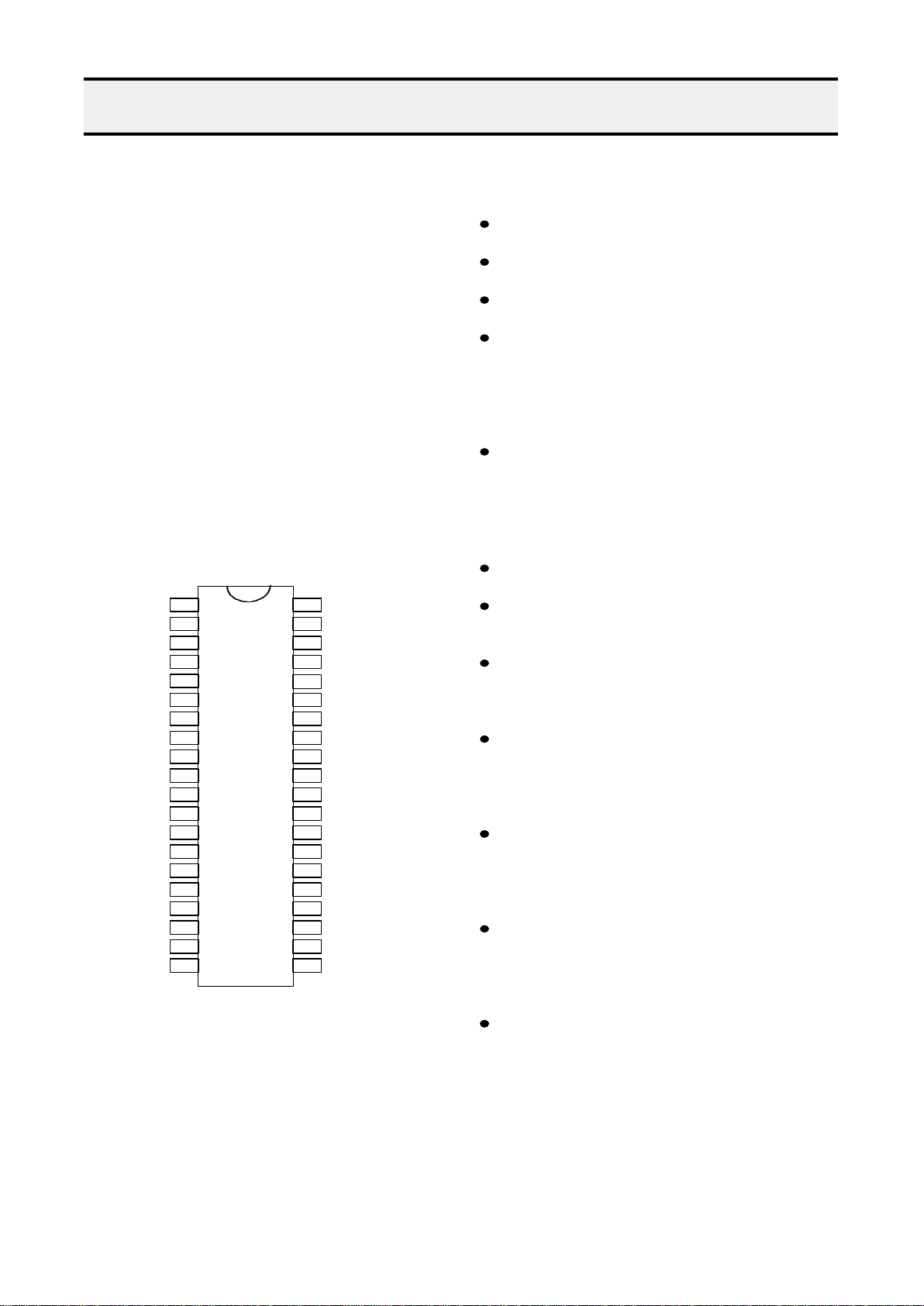

PIN CONFIGURATION

. 1.91 us ( XI/8 = 524.0KHz )

. 0.95 us ( XI/4 = 1.05MHz )

4 Register Bank

PC.0/PWM14 PC.1/PWM60

General Register

P8.3 PC.2/PWM61

- 8 x 4 bit x 4 Banks

P0.3/INT3 PC.3/PWM62

P0.2/INT2 PWMOTB/80

Accumulator

P0.1/INT1 PWMOTB/81

- Bit Accumulator (CY), 4 bit Accumulator (A),

P0.0/INT0 PWMOTB/82

8 bit Accumulator (XA)

XI P3.0

XO P3.1

Multiple Vectored Interrupt Source

RESETB P3.2

- External Interrupts : 4

P8.2 P3.3

- Internal Interrupts : 3

VSS P1.0

- Vsync Interrupts : 1

P8.1 P1.1

P8.0 P1.2

Watch timer

VDD P1.3

- fast mode : 3.91 msec

P2.3 VBLNKPAD

- normal mode : 0.5 sec

P2.2 VBPAD

- buzzer output : 1, 2, 4 KHz

P2.0 P6.1/VGPAD

P2.1 P6.0/VRPAD

Basic interval timer

OSCIN VSYNCBP

- 8 kinds of period

OSCOUT HSYNCBP

- Used stabilization wait timer to wake up

Stop mode

Two 8-bit timer / event counters

403938

37363534333231302928272625242322211234567891011121314151617181920

D

M

C

4

2

C

2

0

0

Page 2

2

4Bit Single Chip Microcontroller

DMC42C2008

4 Bit A/D Converter

Power saving mode

Programmable Comparator Input

- STOP : Main clock, CPU clock stop

AFC Input Signal Detection Circuit

- STBY : Only CPU clock stop

Main clock operation

PWM

- 14 Bits PWM Output x 1Ch

Package : 40 DIP

- 8 Bits PWM Output x 3Ch

- 6 Bits PWM Output x 3Ch

29 I/O Pins

- CMOS I/O Pins : 22

(Digital CMOS Levels Schmitt Triggered)

- PWM Pins : 7

OSD CONTROLLER SPEC.

Character ROM ; 12 x 16 x 96 bits

Display Mode ; 3 Modes

Character, Fringe,

Video RAM ; 120 x 10 Bits

Background

OSD Clock ; 4MHz ~ 7MHz

Background Color ; 8 Colors

- Character Background Area Mode

Character Number ; 96

- All TV Display Area Mode

Display Capacity ; 20 Columns x 6 Lines

OSD Oscillator Control Modes ;

(120 Character)

(Always Oscillate, Oscillates

Only in the Display Period

Character Size ; 16 Kinds (4 x 4 Kinds)

LC Oscillator)

- Horizontal 1T, 2T, 3T, 4T/Dots

- Vertical 1H, 2H, 3H, 4H/Dots

Display Position ; 1'st line, 2'nd line

Variable

Character Color ; 8 Colors

Black, Blue, Green, Red,

Structure of Character

Magenta, Yellow, White,

12 (Width) x 16 (Height) dots

Cyan

Vsync Interrupt

Page 3

3

4Bit Single Chip Microcontroller

DMC42C2008

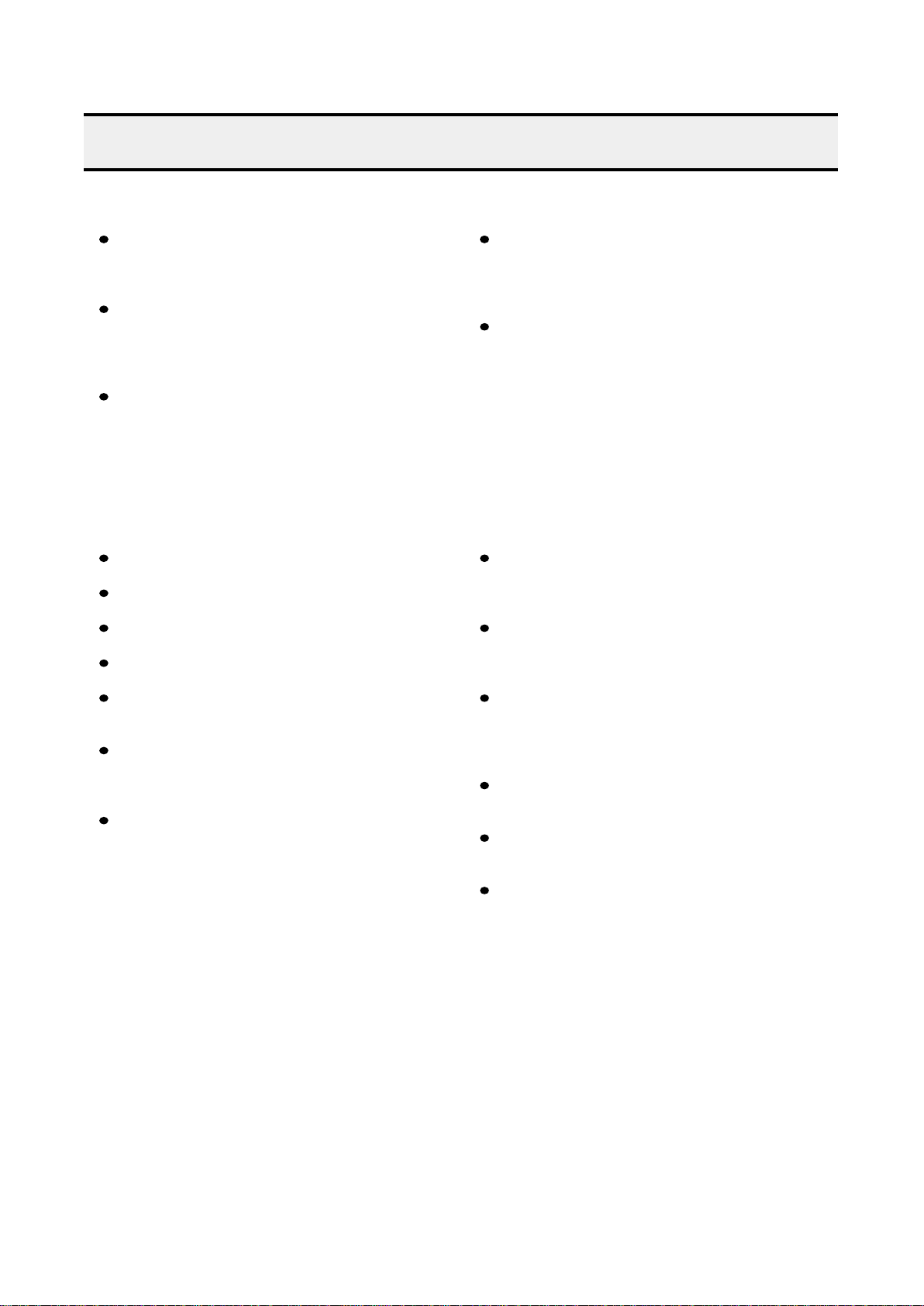

TI0/P0.0

TO0/P2.2

TI1/P0.1

TO1/P2.3

INT0/P0.0

INT1/P0.1

INT2/P0.2

INT3/P0.3

14BIT RED

OUTPUT

GREEN

8BIT

OUTPUT BLUE

6BIT

F x /2

CPU BLANK

OUTPUT CLOCK

HSYNC

AD0-AD4 VSYNC

OSCIN

OSCOUT

VDD VSS RESETB TEST

P2.0/CLO XI XO

WATCH DOG

TIMER

BASIC

INTERVAL

TIMER

TIMER/

EVENT

COUNTER 0

INTERRUPT

CONTROL

PWM

14 BIT

PWM

8 BIT

PWM

6 BIT

4-BIT

ADC

DMC42CORE

PROGRAM

(8192 x 10BITS)

DATA

MEMORY

(512 x 4BITS)

CLOCK

OUTPUT

CONTROL

CLOCK

DIVIDER

CLOCK

GENERA-

TOR

STAND

-BY

CONTROL

PORT 0

PORT 1

PORTC

PORT 8

PORT 6

PORT 3

PORT 2

PWMOT

OSD

P0.0-

P1.0-P1.3

PC.0-

P8.0-P8.3

P6.0-

P3.0-P3.3

P2.0-P2.3

PWMOT

B

TIMER/

EVENT

COUNTER 1

IRQBT

IRQTC0

IRQTC1

n

BLOCK DIAGRAM

Page 4

4

4Bit Single Chip Microcontroller

DMC42C2008

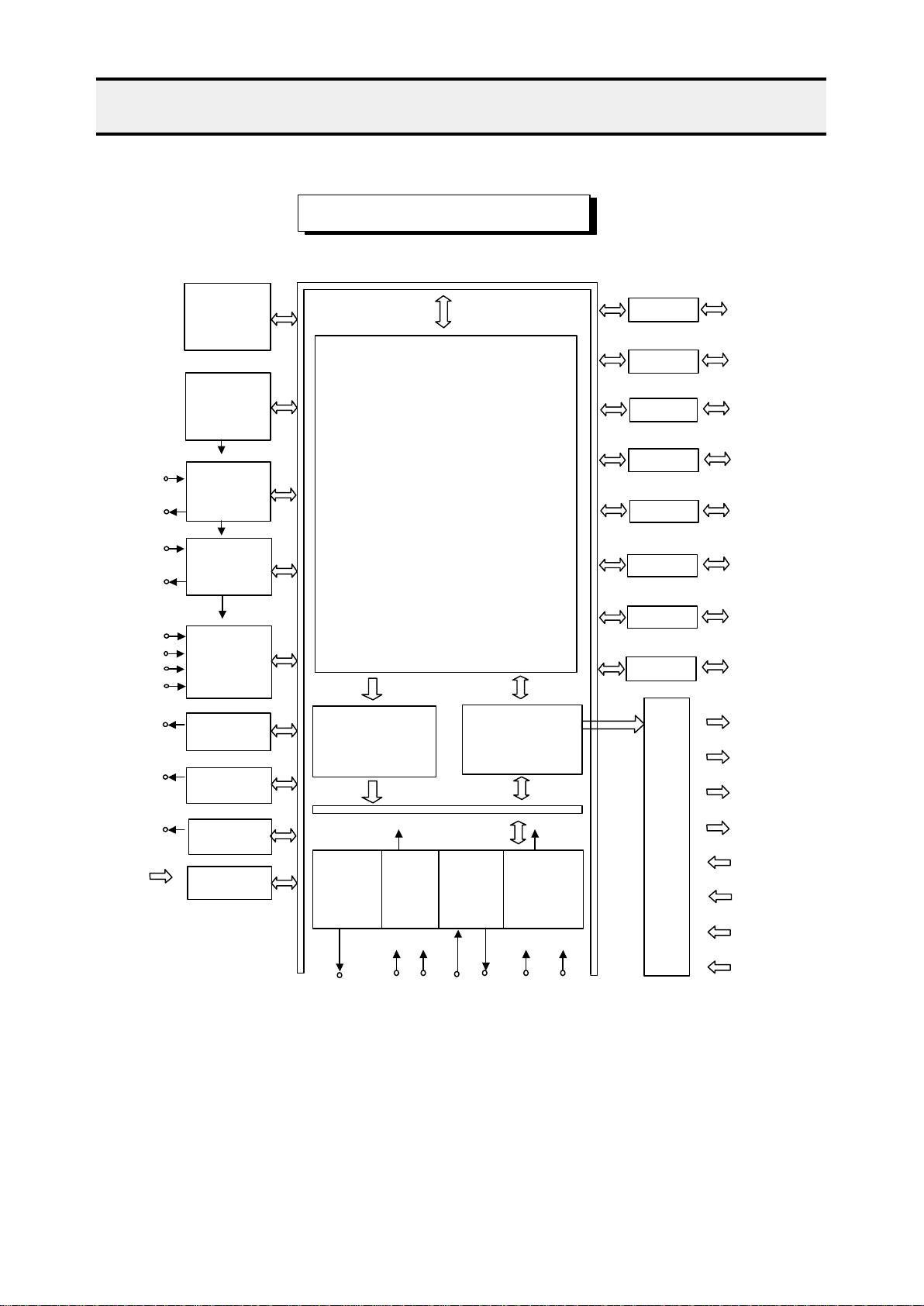

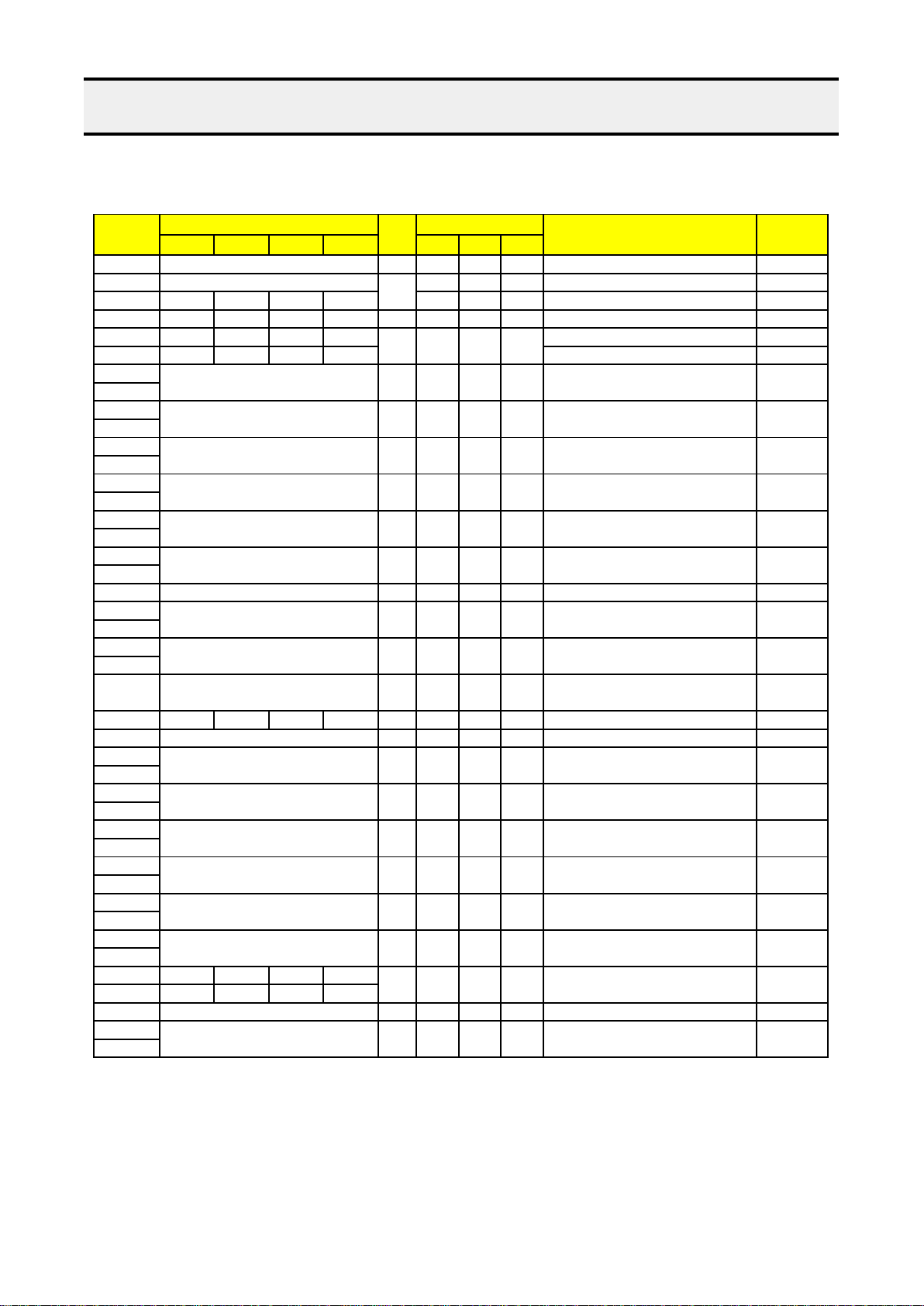

PROGRAM MEMORY (ROM)

VECTOR ADDRESS

CONTENTS Prioty INTERRUPT SUORCE

0000H

VECTOR

0000H

0 RESET

Reset Signal

ADDRESS AREA

0002H

1 IRQBT

Basic Interval Timer

001FH 0004H

2 IRQ0

External interrupt 0

0020H

ZERO-PAGE

0006H

3 IRQ1

External interrupt 1

CALL AREA

0008H

4 IRQTC0

Timer Event Counter 0

002FH 000AH

5 IRQTC1

Timer Event Counter 1

0060H 000CH

6 IRQ2

External interrupt 2

000EH

0010H

8 IRQ3

External interrupt 3

0012H

0014H

10 IRQAD

8 bit ADC

8K Byte

0016H

0018H

12 IRQWT

Watch Timer

001AH

001CH

1FFFH 001EH

15 -

reserved

DATA MEMORY (RAM)

DIRECT INDIRECT STACK GENERAL

m @HL @DE @DL REGISTER

$00

RB=0

RB=1

PAGE0

RB=2

RB=4

(256 Byte)

MP=0

SPS=0

$FF

$00

PAGE1

(256 Byte)

MB=0

MB=0

MP=1

SPS=1

BANK 0

$FF

(1K)

$00

200~27F

PAGE2

OSD RAM

(256 Byte)

MP=2

SPS=2

$FF

$00

PAGE3

I/O

(256 Byte)

MEMORY

MP=3

; Usable

$FF

Page 5

5

4Bit Single Chip Microcontroller

DMC42C2008

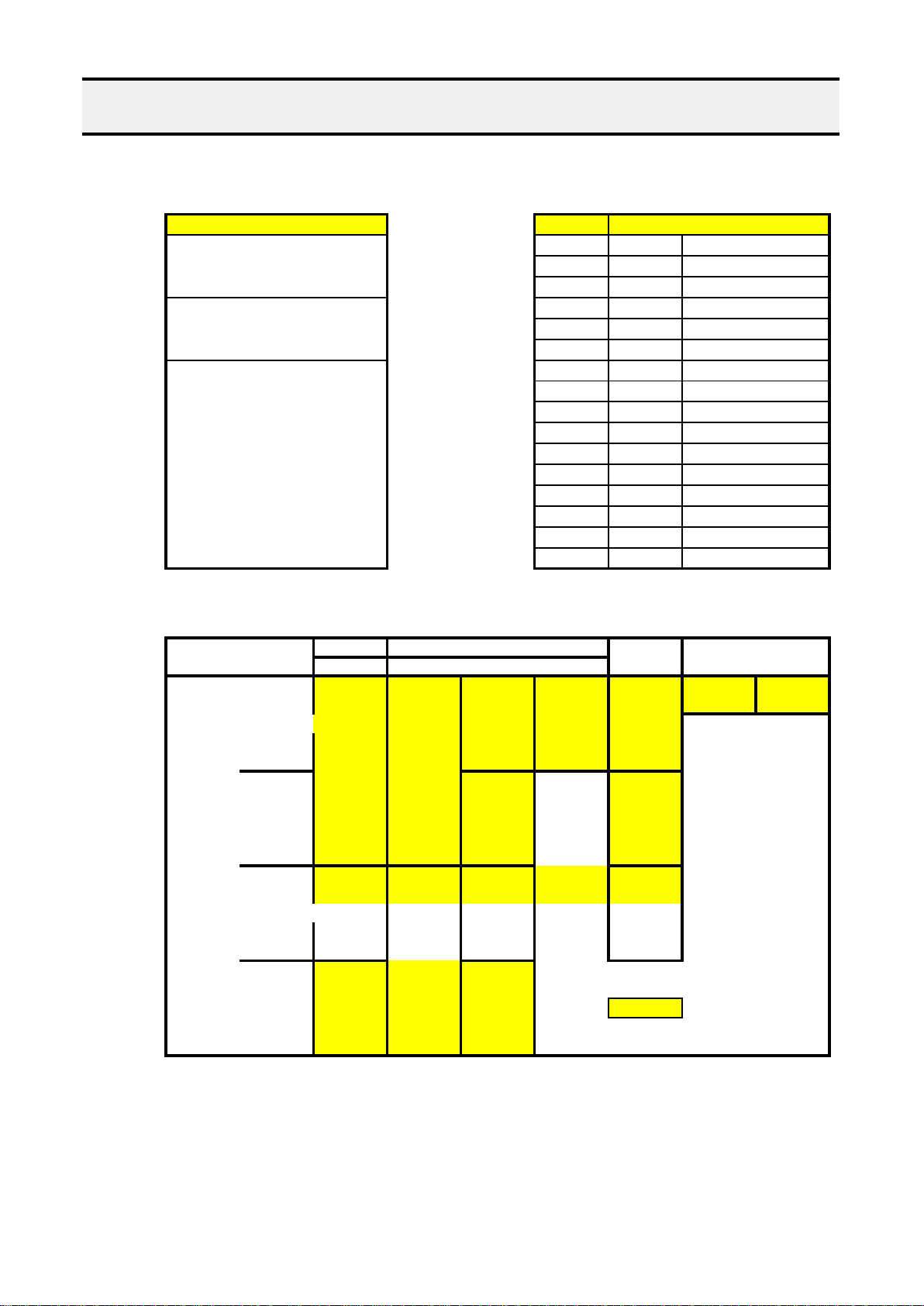

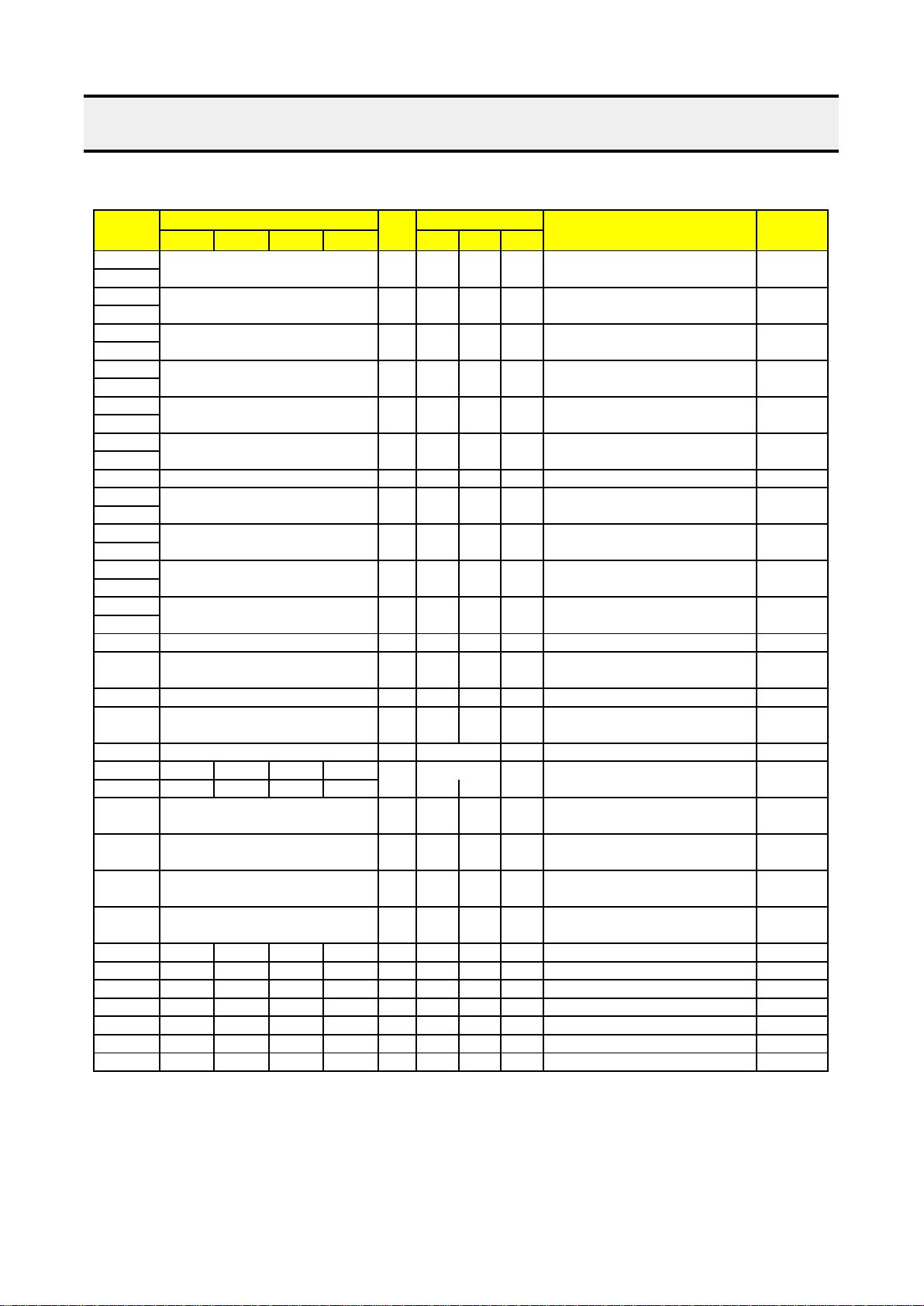

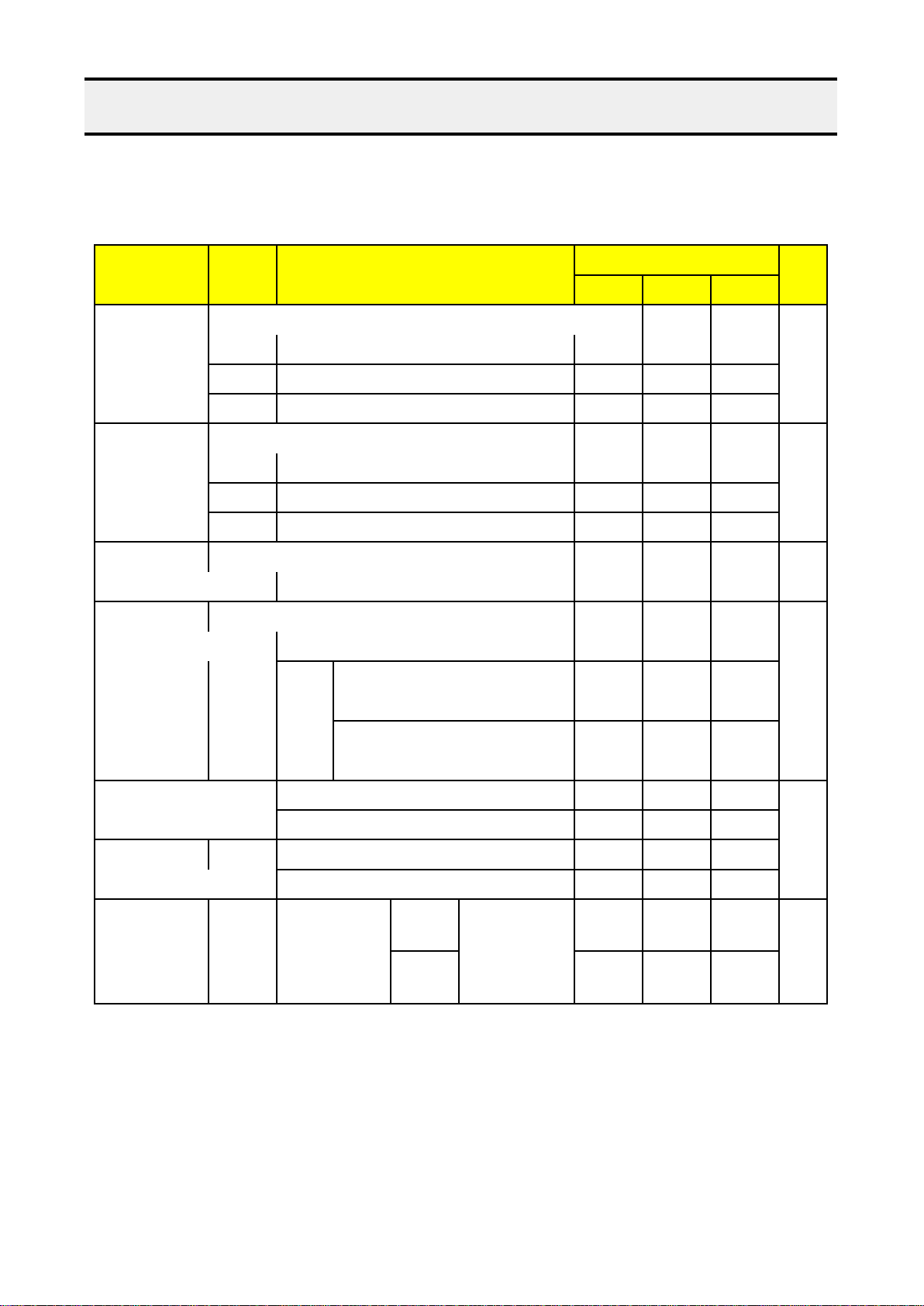

I/O ADDRESS MAP

ADDRESS Hardware Module Name R/W Addressing Unit REMARKS INITIAL

b3 b2 b1 b0 1 bit 4 bit 8bit VALUE

318H Stack pointer low (SPL) R/W O Stack pointer low E

319H Stack pointer high (SPH) R/W O stack pointer high F

31AH SP3 SP2 SP1 SP0 R/W O Stack Page Select Low (SPSL) 0

31BH - - SP5 SP4 R/W O Stack Page Select High (SPSh) 0

31CH AC IS1 IS0 R/W O O O Psw low (PSWL) 0

31DH CY Z OV T Psw high (PSWH) 0

320H T/E counter mode register 0 W 320H.3 O Clock source select. counter 00

321H (TMOD0) start (ch0)

322H T/E counter register 0 R readable count value (ch0) 00

323H (TMCNT0)

324H T/E reference register 0 W count reference register (ch0) FF

325H (TMREF0)

326H T/E counter mode register 1 W 326H.3 clock source select. counter start 00

327H (TMOD1) (ch1)

328H T/E counter register 1 R readable count value (ch1) 00

329H (TMCNT1)

32AH T/E reference register 1 W count reference register (ch1) FF

32BH (TMREF1)

332H Basic Timer mode register(BMOD) R/W 332H.3 clock select, Bit start 0

334H Basic interval timer count R readable count register 00

335H register(BITCNT)

336H Watch timer mode register R/W 336H.3 clock/buzzer select. bit3 00

337H (WMOD) readable

338H Watch dog timer mode register W clock source sel. timer EN/DIS 00

(WDTM)

339H WDTF R WDT flag 0

340H Pwm mode register0(PWMOD0) R/W 6.14bit pwm counter EN/DIS 0

342H Pwm0 data register high W O 14bit pwm data register high 00

343H (PWMODH)

344H Pwm0 data register low W O 14bit pwm data register low 00

345H (PWMODL)

346H Pwm channel start mode register W O 6bit*6ch, 14bit pwm start EN/DIS 00

347H (PWMSM)

348H Pwm60 data register (PWMDR0) W O 6bit pwm channel 0 data register 00

349H

34AH Pwm61 data register (PWMDR1) W O 6bit pwm channel 1 data register 00

34BH

34CH Pwm62 data register (PWMDR2) W O 6bit pwm channel 2 data register 00

34DH

354H PWM3 PWM2 PWM1 PWM0 W O pwm output enable mode 00

355H PWM6 PWM5 PWM4 register (PWM0 = 14bit)

358H Pwm mode register 1 (PWMOD1) W O 8bit pwm control

35AH Pwm80 data register (PWMDR80) W O 8bit pwm channel 0 data register 00

35BH

Page 6

6

4Bit Single Chip Microcontroller

DMC42C2008

ADDRESS Hardware Module Name R/W Addressing Unit REMARKS INITIAL

b3 b2 b1 b0 1 bit 4 bit 8bit VALUE

35CH Pwm81 data register (PWMDR81) W O 8bit pwm channel 1 data register 00

35DH

35EH Pwm82 data register (PWMDR82) W O 8bit pwm channel 2 data register 00

35FH

360H 1'st line horizontal display mode W O 1'st line horizontal position set. 00

361H register (HDPM1) 000000h-111111h

362H 1'st line vertical display mode W O 1'st line vertical position set. 00

363H register (VDPM1) 000000h-111111h

364H H/V character size mode W O 1, 2, 3, 4Tc/dot 00

365H register (HVSMOD) 1, 2, 3, 4H/dot

366H Display mode & background color W O dspon, R/G/B control 00

367H register (DBCM)

368H W O osd out enable 0

36AH I/O polarity control register W O Y(BLK), R/G/B output, H/Vsync 00

36BH (POLCON) control

36CH 2'nd line horizontal display mode W O 2'nd line horizoncal position set. 00

36DH register (HDPM2) 000011h-111111h

36EH 2'nd line vertical display mode W O 2'nd line vertical position set. 00

36FH register (VDPM2) 000000h-111111h

380H Adc4 mode register (ADCM4) W O Reference voltage setting. start 00

381H

382H Adc4 output latch (ADCOL4) R O conversion data 0

3A0H Power control register O system clock select, idle, stop 00

(PCON) R/W mode

3A2H Operating mode register (SCMOD) R/W O main/sub system clock select 0

3A4H Clock output mode register W O cpu clock output select, clock 00

(CLOMD) out EN/DIS

3B2H Power on flag (PONF) P/W 3B2H.0 O power on reset flag 0

3C2H IME R/W 3C2H.3 O Interrupt priorty select, IME flag. 00

3C3H IPSR3 IPSR2 IPSR1 IPSR0

3C4H External interrupt mode register0 W O external interrupt 0 edge 00

(IMOD0) detection

3C5H External interrupt mode register1 W O external interrupt 1 edge 00

(IMOD1) detection

3C6H External interrupt mode register2 W O external interrupt 2 edge 00

(IMOD2) detection

3C7H External interrupt mode register3 W O external interrupt 3 edge 00

(IMOD3) detection

3D8H IE2 IRQ2 IEBT IRQBT R/W O O Interrupt EN/IRQ flag 0

3D9H IEWT IRQWT R/W O O Interrupt EN/IRQ flag 0

3DAH R/W O O Interrupt EN/IRQ flag 0

3DBH IETC1 IRQTC1 IETC0 IRQTC0 R/W O O Interrupt EN/IRQ flag 0

3DCH IE1 IRQ1 IE0 IRQ0 R/W O O Interrupt EN/IRQ flag 0

3DDH R/W O O Interrupt EN/IRQ flag 0

3DEH IE3 IRQ3 R/W O O Interrupt EN/IRQ flag 0

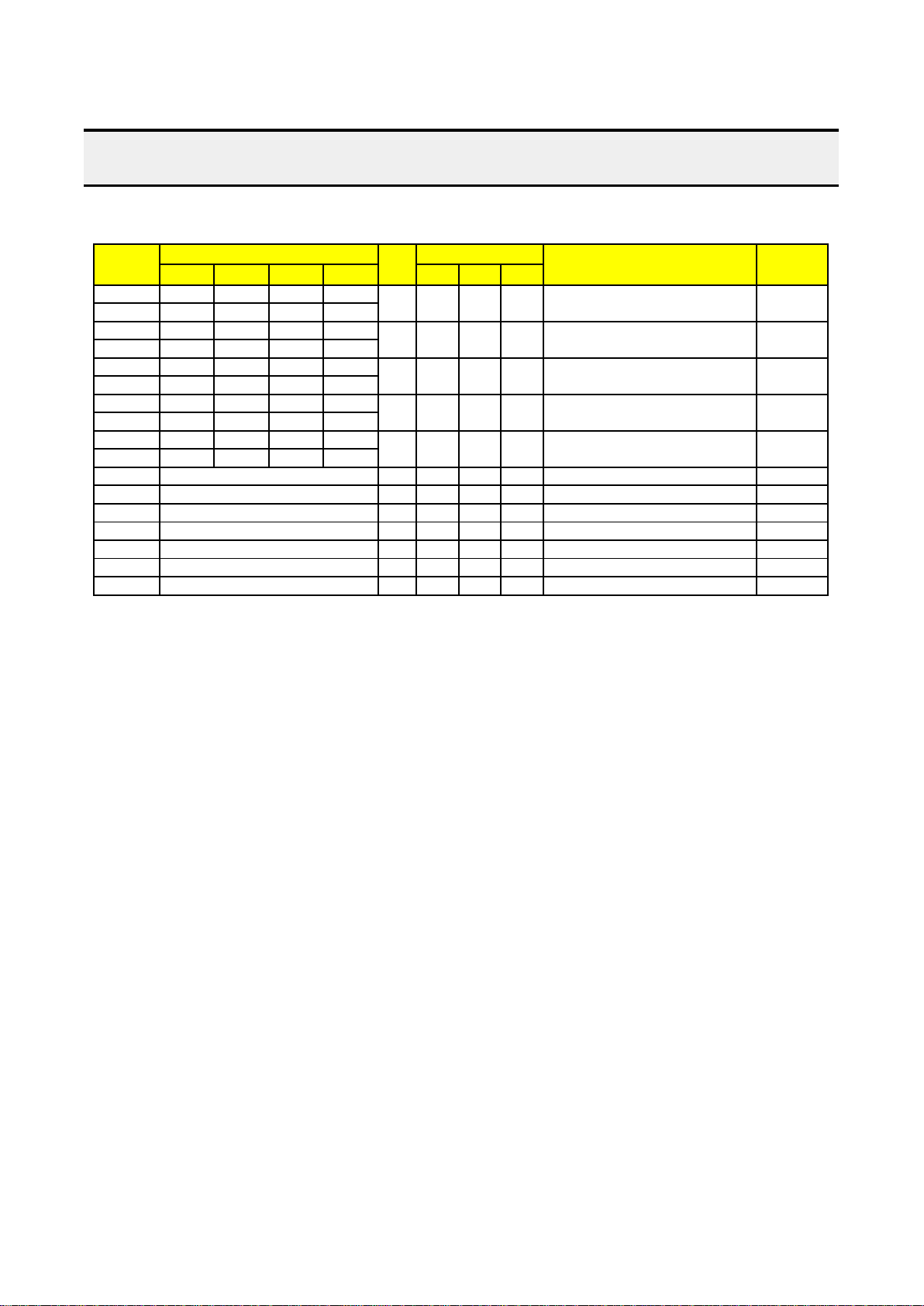

Page 7

7

4Bit Single Chip Microcontroller

DMC42C2008

ADDRESS Hardware Module Name R/W Addressing Unit REMARKS INITIAL

b3 b2 b1 b0 1 bit 4 bit 8bit VALUE

3E0H PW03 PW02 PW01 PW00 W O port 0, 1 mode register (PMGA) 00

3E1H PW13 PW12 PW11 PW10

3E2H PW23 PW22 PW21 PW20 W O port 2, 3 mode register (PMGB) 00

3E3H PW33 PW32 PW31 PW30

3E6H PW63 PW62 PW61 PW60 W O port 6, 7 mode register (PMGD) 00

3E7H PW73 PW72 PW71 PW70

3E8H PW83 PW82 PW81 PW80 W O port 8, 9 mode register (PMGE) 00

3E9H PW93 PW92 PW91 PW90

3ECH PWC3 PWC2 PWC1 PWC0 W O port c, d mode register (PMGG) 00

3EDH PWD3 PWD2 PWD1 PWD0

3F0H PORT0 (R0) R/W O O R0 Port Data Regiter 0

3F1H PORT1 (R1) R/W O O R1 Port Data Regiter 0

3F2H PORT2 (R2) R/W O O R2 Port Data Regiter 0

3F3H PORT3 (R3) R/W O O R3 Port Data Regiter 0

3F6H PORT6 (R6) R/W O O R6 Port Data Regiter 0

3F8H PORT8 (R8) R/W O O R8 Port Data Regiter 0

3FCH PORTC (RC) R/W O O RC Port Data Regiter 0

Page 8

8

4Bit Single Chip Microcontroller

DMC42C2008

PIN DESCRIPTION

PIN SHARED I/O FUNCTION RESET PORT

SYMBOL PIN TYPE

P0.0 INT0/TI0 * External Interrupt Input Port by means of

EPA11 The Rising/Falling Edge Detection

P0.1 INT0/TI1 INPUT BPS

EPA12

I/O

PUR(M.O)

P0.2 INT2

* Event Pulse Input Port for the Timer/Event

EPA13 Counter 1bit Data Input Port

P0.3 INT3 (EXCEPT ; INT2, INT3) (PORT0)

CEX

P1.0-P1.3

EPD0---EPD3

I/O * 4 bit I/O Port (PORT1)

INPUT, PUR(M.O)

BPS

P2.0 CLO I/O * Clock Output Port (PORT2)

INPUT, PUR(M.O)

BPS

P2.1

COMPIN I/O * Compare Analog Input INPUT BPAS

* 4 bit I/O Port (PORT2) PUR(M.O)

P2.2 --- I/O * 4 bit I/O Port (PORT2) INPUT BPS

P2.3

--- PUR(M.O)

P3.0-P3.3

EPA4---EPA7

I/O * 4 bit I/O Port (PORT3)

INPUT, PUR(M.O)

BP-PDND

P6.0 --- I/O * OSD Red, Green, Output Port (PORT6) INPUT BP-PDNDS

P6.1 EPD4 PUR(M.O)

P8.0-P8.2

EPA8--EPA10

I/O * 4 bit I/O Port INPUT BPS

P8.3 PUR(M.O)

PC.0 PWM14 O PWM14 Output Port Push Pull (PORTC) HIGH LEVEL OP

EPA0

PC.1-PC.3 PWM6 O PWM6 Output Port Open Drain (PORTC) HIGH LEVEL OD

EPA1---EPA3

PWMOT80 PWM8 Only PWM8 Output Port Open Drain HIGH LEVEL

PWMOT81 PWM8 O (PWMOTB) OD

PWMOT82 PWM8

HSYNC --- I OSD Horizontal Signal Input Port INPUT IP

VSYNC VPPOEX I OSD Vertical Signal Input Port INPUT IP

VBPAD --- O Video Blue Signal Output Port HIGH LEVEL OP

VBLKPAD --- O Video Blank Signal Output Port HIGH LEVEL OP

XI --- I Main Oscillator Input

XO --- O Main Oscillator Output

OSCIN --- I OSD Oscillator Input

OSCOUT --- O OSD Oscillator Output

RESETB --- I Reset Port

Page 9

9

4Bit Single Chip Microcontroller

DMC42C2008

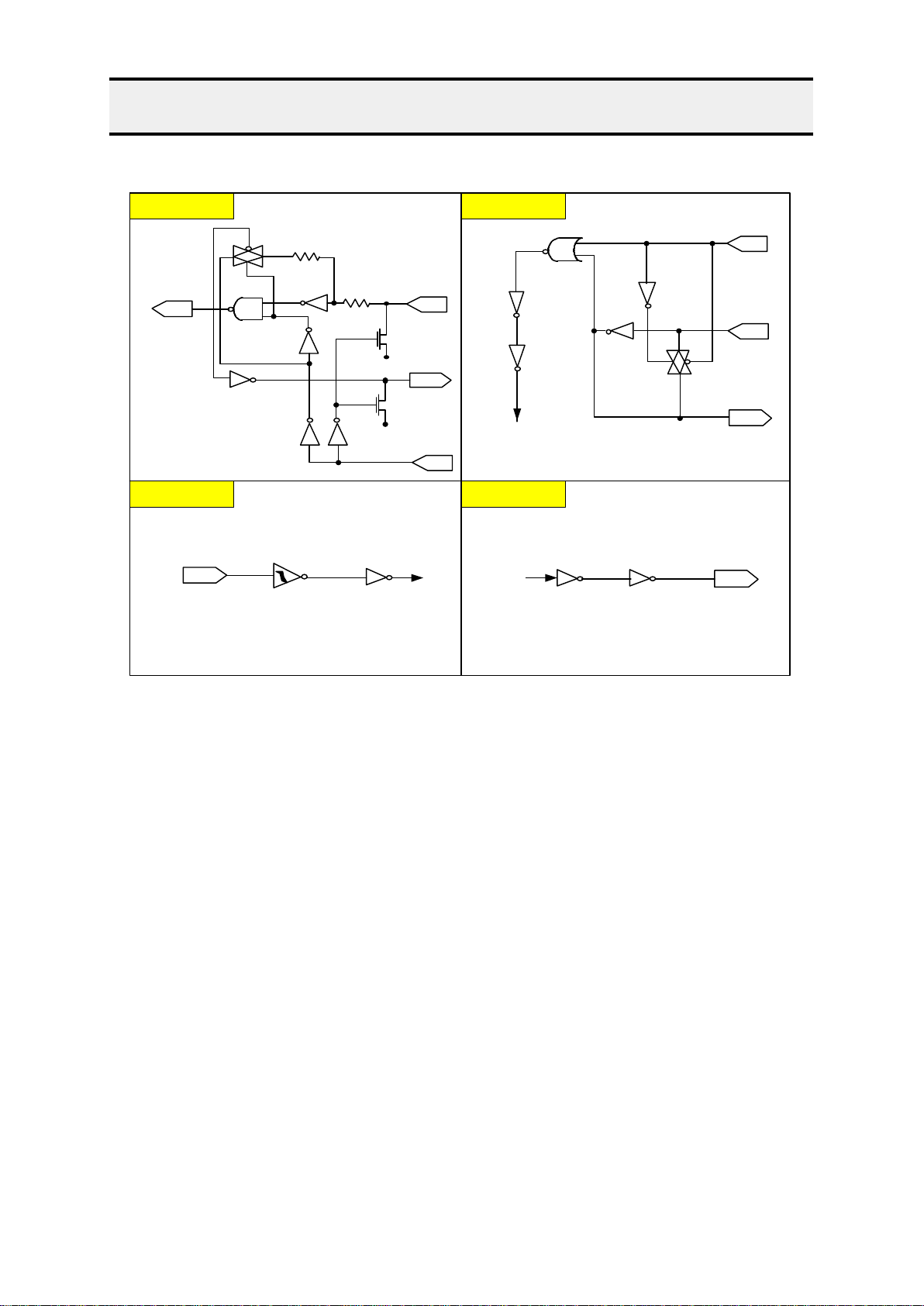

I/O CIRCUITS

NOTE) PUR : Pull-Up Resistor

M.O : Mask Option

BP-PDNDS BP-PDND

OD

V

SS

DATA

OUTPUT

DISABLE

BPS

PUR

OUTPUT

DATA

BD

DATA

INTERNA

PUR

(M.O)

OUTPU

T

PUR

(M.O)

DATA

OUTPU

Output

TR

Disable

INTERNA

OUTPU

DATA

INTERNA

PUR

(M.O)

BPAS

DATA

OUTPU

T

PUR

(M.O)

ANALOG

INPUT

CONTROL

INTERNA

ANALOG

Output

TR

Disable

Output

TR

Disable

Output

TR

Disable

Page 10

10

4Bit Single Chip Microcontroller

DMC42C2008

XI

SYSTOP

INTERNA

OSCOUT

OSCIN

INTERNA

XI

XO

OSC X-TAL

IP OP

Page 11

11

4Bit Single Chip Microcontroller

DMC42C2008

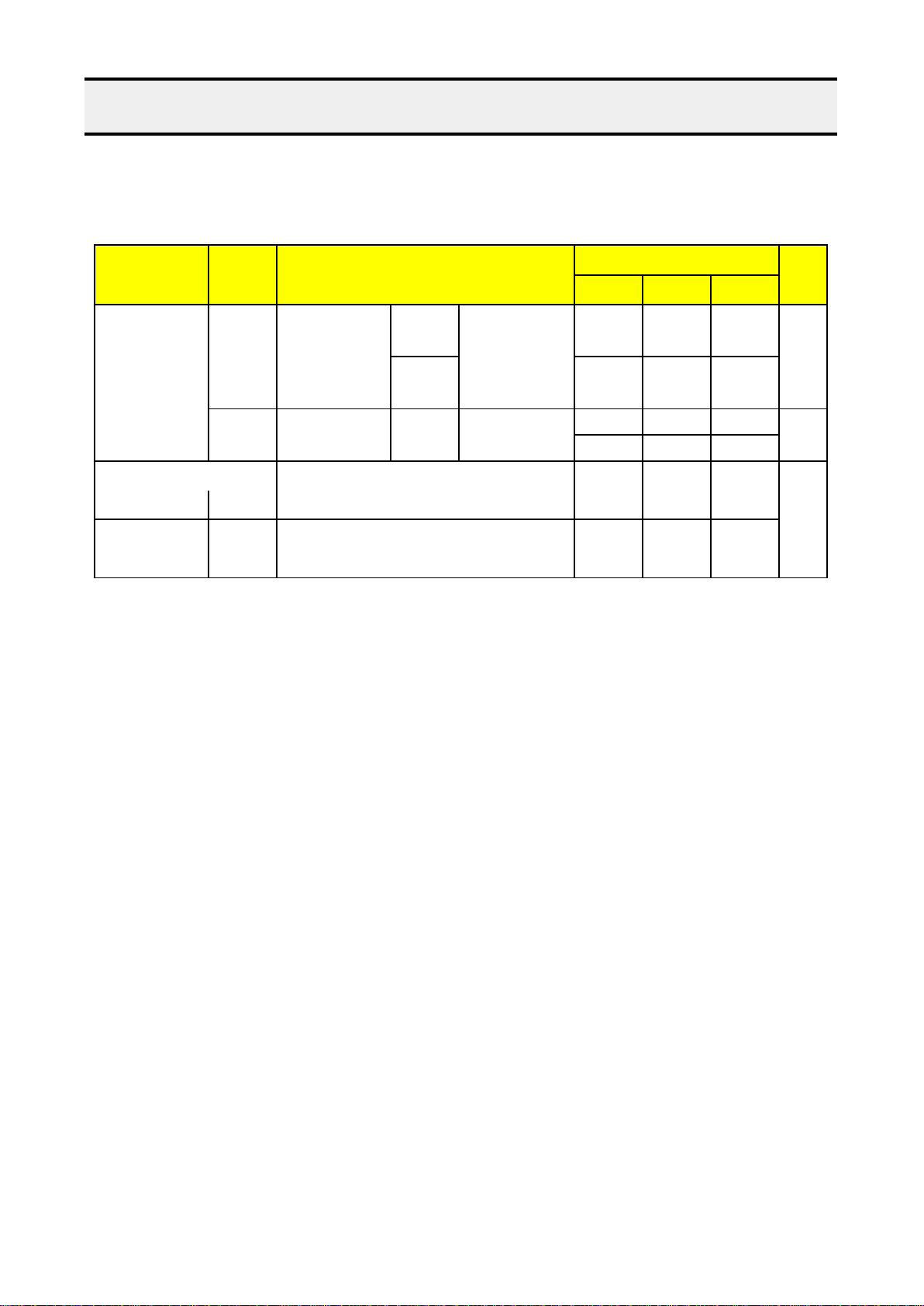

ABSOLUTE MAXIMUM RATINGS

(TA = 0¡É to 70¡É, VDD = 5V ±10%, fX = 4.19MHz)

PARAMETER SYMBOL CONDITION RATING UNIT

Supply Voltage - -0.3 to +7.0 V

Input Voltage All I/O ports -0.3 to VDD+0.3 V

Output Voltage All I/O ports -0.3 to VDD+0.3 V

Output Current High One I/O port active -10 mA

All I/O ports active -100

Output Current Low One I/O port active 20 mA

All I/O ports active 200

Operating Temperature Industrial -40 to +85

¡É

Commercial 0 to +70

Storage Temperature Tstg - -55 to +125

¡É

* Exceeding beyond those listed values under "Absolute Maximum Ratings" may cause permanent damage

to the device.

VDD

VI

VO

IOH

IOL

TA

Page 12

12

4Bit Single Chip Microcontroller

DMC42C2008

DC ELECTRICAL CHARACTERISTICS

PARAMETER

SYMBOL

TEST LIMIT UNIT

CONDITION MIN. TYP. MAX.

High Level Port 0, 1, 2, 6, 8, HSYNC, VSYNC, RESETB -

Input Voltage (Schmitt Input) V

-

Port 3 -

Low Level

Port 0, 1, 2, 6, 8, HSYNC, VSYNC, RESETB

0 -

Input Voltage (Schmitt Input) V

0 -

Port 3 0 -

High Level

Port 0, 1, 2, 3, 6, 8, PC0, VBPAD, VBLKPAD

VDD - 0.4 - - V

Output Voltage

Low Level

Port 0, 1, 2, 3, 6, 8, PC0, VBPAD, VBLKPAD

- - 0.4

Output Voltage

PC1, PC2, PC3, PWMOT8 (0 ~ 2) - - 0.4 V

Open

Drain PC1, PC2, PC3, PWMOT8 (0 ~ 2) - - 2

High Level Input All Pin Except XI, OSCIN - 1.2 3

Leakage Current XI, OSCIN - 5 15 uA

Low Level Input All Pin Except XI, OSCIN - -1.2 -3

Leakage Current XI, OSCIN - -5 -15

Supply Current Dynamic - - 10

Main Clock (XI)

Mode VDD = 5V ±10% mA

= 4.19MHz Idle - - 5

Mode

VIL1

VIH1

IIL

VOL

VOH

(IOH = - 0.75mA)

XI, OSCIN

XI, OSCIN

IIH

VIH2

VIH3

0.8

VDD -

0.7

VDD

VDD

VDD

VIL2

VIL3

0.3

0.2

0.4

IDD1

(IOL = 1mA)

(IOL = 0.75mA)

(IOL = 10mA)

(VSS = 0, VDD = 5V ±10%, TA = 25¡É, fX = 4.19MHz)

Page 13

13

4Bit Single Chip Microcontroller

DMC42C2008

DC ELECTRICAL CHARACTERISTICS

PARAMETER

SYMBOL

TEST LIMIT UNIT

CONDITION MIN. TYP. MAX.

Supply Current Dynamic - - 2

Main Clock (XI)

Mode VDD = 3V ±10% mA

= 2MHz Idle - - 1

Mode

Main Clock (XI) Stop

VDD = 5V ±10%

- - 5 uA

= 4.19MHz Mode - - 3

Internal Pull-up All Ports - - 40

Resistor (M.O) VI or VO = 0V, VDD = 5V

Pull-up VI = 0V, VDD = 5V ±10% 20 - 60 Kohm

Resistor RESETB

IDD2

IDD3

(VSS = 0, VDD = 5V ±10%, TA = 25¡É, fX = 4.19MHz)

RL1

RPU

Page 14

14

4Bit Single Chip Microcontroller

DMC42C2008

AC ELECTRICAL CHARACTERISTICS

(TA = -40 to +85¡É, VDD = 2.7 to 6.0V)

PARAMETER SYMBOL TEST CONDITION MIN. TYP. MAX. UNIT

Cycle Time 0.95 - 64 uS

3.8 - 64 uS

TI Input Frequency 0 - 1 MHz

0 - 275 KHz

TI Input High, Low 0.48 - - uS

Level Width 1.8 - - uS

INT 0 ~ 4 Input Level

5 - - uS

High, Low 5 - - uS

RESETB Low Level 5 - - uS

Hsync Start to Vosc Stop

TdHsOl

1TpC 2TpV

Hsync End to Vosc Start

TdHsOh

1TpV

VDD = 4.5 to 6.0V

VDD = 2.7 to 3.3V

VDD = 4.5 to 6.0V

VDD = 2.7 to 3.3V

VDD = 4.5 to 6.0V

tCYf

TI

t

TIH

t

TILtRSL

VDD = 2.7 to 3.3V

t

INTHtINTL

Page 15

15

4Bit Single Chip Microcontroller

DMC42C2008

AC Timing Measurement Points (Except XI and XTI)

HSYNC

Internal/OSC2

On-Screen-Display

Measurement

0.8VD0.2VD0.8V

D

1/XI

1/XTI

1/fTI

tINT tINT

tXL

tXH

tXTL

tXT

tTIL tTIH

tRS

VDD-

0.4V

VDD-

0.4V

0.8V

D

0.2V

D

0.8V

D

0.2V

D

0.2V

D

Clock Timing

XI

XTI

TI0

Interrupt Input Timing

INT0~3

RESET

RESETB Input Timing

Timer Event Counter

TdHsOl

TdHsOh

Page 16

16

4Bit Single Chip Microcontroller

DMC42C2008

RAM DATA RETENTION CHARACTERISTICS ( in STOP Mode )

(TA = -40 to +85¡É)

PARAMETER SYMBOL TEST CONDITION MIN. TYP. MAX. UNIT

2.0 - 6.0 V

- 0.1 10 uA

0 - - uS

When released by RESETB -

217/fx

- mS

- NOTE 1) - mS

NOTE 1) Depends on the setting of the basic interval timer mode register.

(refer to the table below)

( fX = 4.19MHz )

BMOD2 BMOD1 BMOD0 Oscillation Stabilization

0 0 0

220/fX (Approximately 250ms)

0 1 1

217/fX (Approximately 31.3ms)

1 0 0

215/fX (Approximately 7.82ms)

1 0 1

213/fX (Approximately 1.95ms)

Data Retention

Supply Voltage

Data Retention

Supply Current

Release Signal Set

Time

VDDDR

IDDDR

tSREL

VDDDR = 2.0V

When released by interrupt

Signal

Oscillation

Stabilization

tWAIT

Page 17

17

4Bit Single Chip Microcontroller

DMC42C2008

RAM DATA RETENTION TIMING

When STOP mode is released by RESETB input

When STOP mode is released by interrupt signal

STOP Mode

RAM Data retention

VDDDR

VDD

tSREL

t

WAI

STOP instruction execution

Operation

Stabilization Wait Time

STOP Mode

RAM Data retention

VDDDR

VDD

t

WAI

STOP instruction execution

RESET

Interrupt Signal

(Rising Edge)

Internal Reset Operation

Stabilization Wait Time

Operation

Page 18

18

4Bit Single Chip Microcontroller

DMC42P2008

DESCRIPTION

The DMC42P2008 is a system evaluation LSI having a build in One-Time-Programming circuit.

A programming and verification for the internal EPROM is achieved by using a adaptor socket.

The function of this device is exactly same as the DMC42C2008 with programming of internal EPROM.

The DMC42P2008 is the OTP version of the DMC42C2008 with replacement of MASK to EPROM as

as an internal ROM.

PIN CONFIGURATIONS

P8.3

INT3 / P0.3 / CEX

INT2 / P0.2 / EPA13

INT1 / P0.1 / EPA12

INT0 / P0.0 / EPA11

XI

XO

RESETB

P8.2 / EPA10

VSS

P8.1 / EPA9

P8.0 / EPA8

VDD

P2.3

P2.2

P2.0

P2.1

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

D

M

C

4

2

P

2

0

0

PC.2/EPA2/PWM61

PC.3/EPA3/PWM62

PWMOTB/81

PWMOTB/82

P3.0 / EPA4

P3.1 / EPA5

P3.2 / EPA6

P3.3 / EPA7

P1.0 / EPD0

P1.1 / EPD1

P1.2 / EPD2

P1.3 / EPD3

VBLNKPAD

VBPAD

P6.1 / EPD4 / VGPAD

P6.0 / VRPAD

VSYNCBP / V

PP

/OEX

HSYNCBP

PC.1/EPA1/PWM60

PWMOTB/80

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

OSCIN

OSCOUT

PC.0/EPA0/PWM1

DMC42P2008

Page 19

19

4Bit Single Chip Microcontroller

DMC42P2008

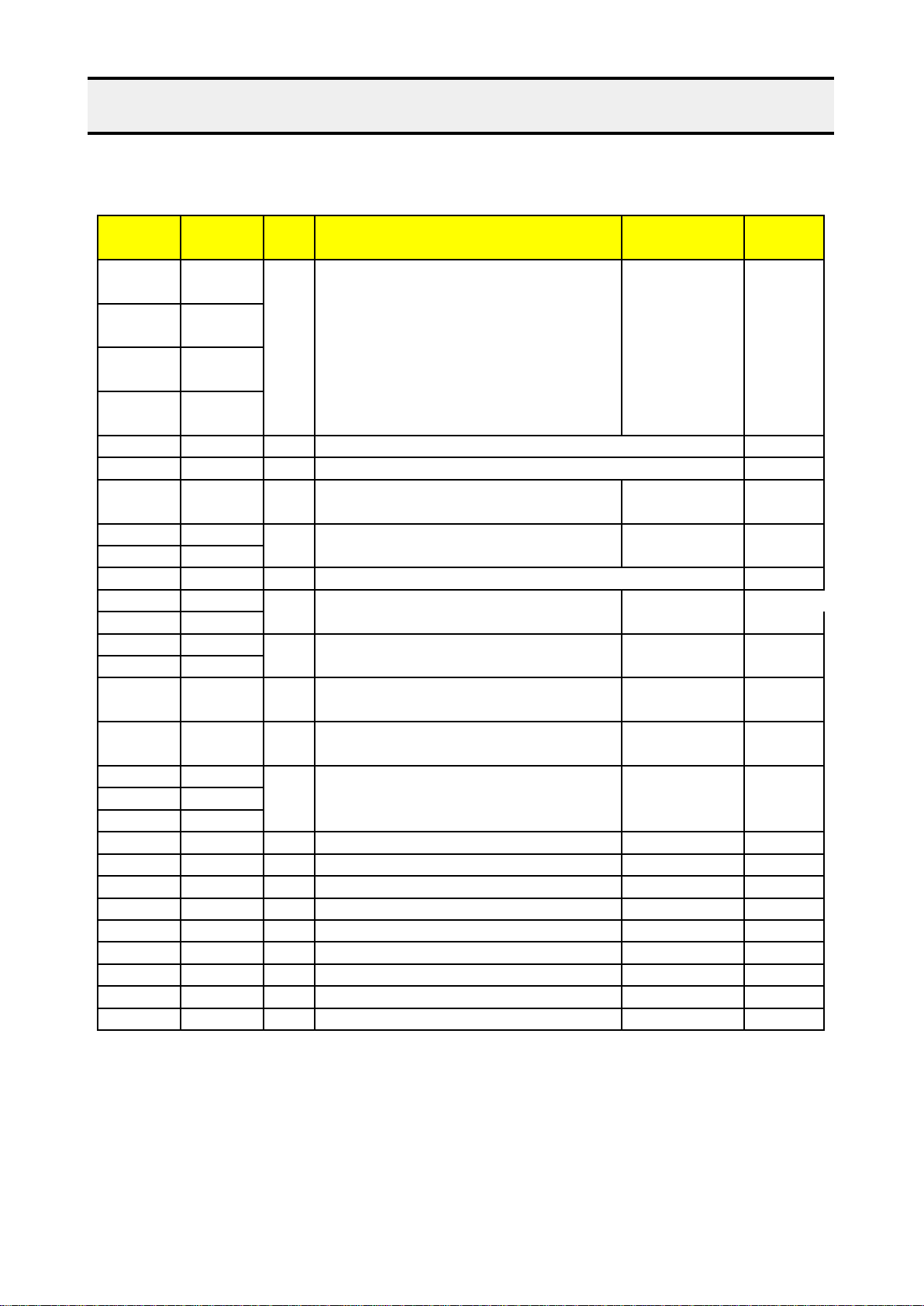

DEVICE OPERATION

The operational modes of the DMC42P2008 are listed in Table 1.

A single 5V power supply is required in the read mode.

All inputs are TTL levels except for VPP / OEX.

PINS

MODE

READ 5.0V

PROGRAM 6.0V

VERIFY 6.0V

PROGRAM INHIBIT 6.0V High Z

TABLE 1. Operating Modes

MODE

EPROM MODE USER MODE

TEST

TABLE 2. The modes of DMC42P2008

DC PROGRAMMING CHARACTERISTICS

LIMIT UNIT

MIN. MAX.

Input Low Voltage -0.1 0.8 V

Input High Voltage 2.0 V

Output Low Voltage during Verify - 0.45 V

Output High Voltage during Verify 2.4 - V

Quick-pulse Programming 12.5 13.0 V

Quick-pulse Programming 6.0 6.5 V

CEX VPP / OEX

VDD

OUTPU

PIN NAME

RESETB

V

IL

VDDVILVIHVOLVOHVPPVDDIOL = 2.1mA

VILVILVILVILVPPVILVPPVIHDIND

OUT

D

OUT

VILV

IH

V

PP

= 12.5±0.5V

TEST CONDITIONPARAMETER

SYMBO

IOH = -400uA

Page 20

20

4Bit Single Chip Microcontroller

DMC42C/P2008

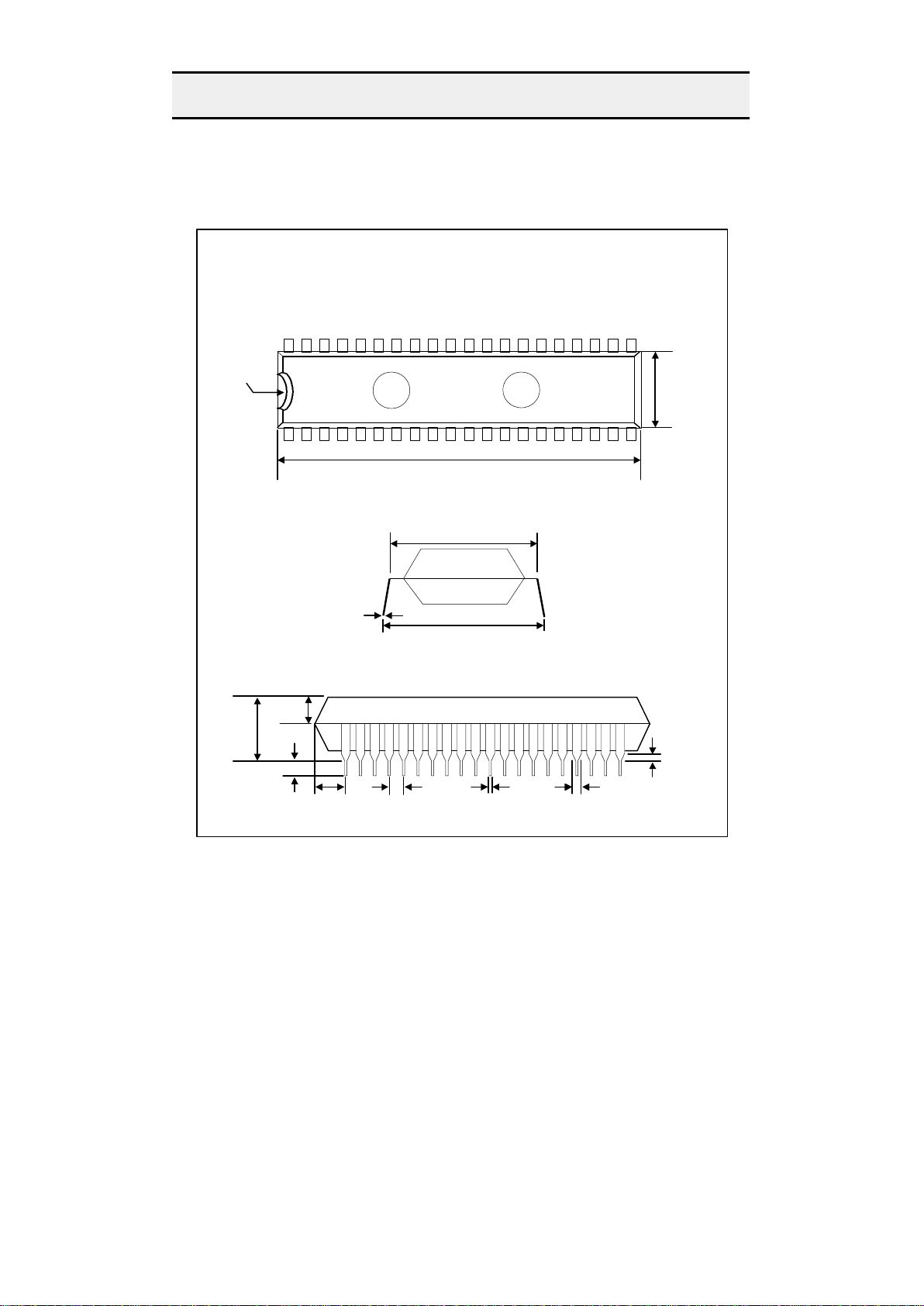

PACKAGE DIMENSION

[ UNIT : Millimeter ]

40 DIP

.620 RAD

52.3±0.2

13.85±0.35

40

1

21

15.50±0.2

15.9±0.10

0.4±0.1

1.7±0.2

3.32±0.08

1.86±0.34

2.54

0.44±0.06

1.26±0.24

0.65±0.15

Page 21

¤Ì

1

0

2 3

0 1 2 3 4 5

0

1

2

3

4 5

S

L

40

50

60

70

80

90

A0

B0

C0

D0

E0

F0

STANDARD FORMAT (I)

30

10

20

Page 22

L

S

M

S

STANDARD FORMAT(II)

00

10

20

30

40

50

60

70

80

90

A0

B0

C0

D0

E0

F0

0 1 2 3 4 5

Loading...

Loading...