Datasheet DM74LS169AN, DM74LS169AMX, DM74LS169AM, DM74LS169ACW Datasheet (Fairchild Semiconductor)

© 2000 Fairchild Semiconductor Corporation DS006401 www.fairchildsemi.com

August 1986

Revised April 2000

DM74LS169A Synchronous 4-Bit Up/Down Binary Counter

DM74LS169A

Synchronous 4-Bit Up/Down Binary Counter

General Description

This synchronous pre settable counter f eatures an inter nal

carry look-ahead for cascading in high-speed counting

applications. Synchronou s operation is provided by ha ving

all flip-flops clocked simult aneously, so that the outputs all

change at the same time when so instr ucted by the coun tenable inputs and int ernal gating. This m ode of operation

helps eliminate the output counting spikes that are normally associated with asynchronous (ripple clock)

counters. A buffered clock i nput triggers the four ma sterslave flip-flops on the rising edge of the clock waveform.

This counter is fully programmable; that is, the outputs may

each be preset either HIG H or LOW. The load input circuitry allows loading with the carry-enable output of cascaded counters. As loading is synchr onous, setting up a

low level at the load inp ut disab l es the cou nte r a nd cau ses

the outputs to agre e with the data inputs after the next

clock pulse.

The carry look-ahead cir cuitry permits casca ding counters

for n-bit synchronous applications without additional gating.

Both count-enable inputs (P

and T) must be LOW to count.

The direction of the co unt is determ ined b y the leve l of t he

UP/DOWN input. When the input is HIGH, the counter

counts UP; when LOW, it counts DOWN. Input T

is fed for-

ward to enable the ca rry outputs. The carry output thus

enabled will produce a low-level output pulse with a duration approximately e qual to th e high portion o f the Q

A

out-

put when counting UP, and approximately equ al to the low

portion of the Q

A

output when counting DOWN. This low-

level overflow carry pulse can be used to en able successively cascaded stages . Transitions at the enable P

or T

inputs are allowed regardless of the level of the clock input.

All inputs are diode clamped to minimize transmission -line

effects, thereby simplifying system design.

This counter features a fully independent clock circuit.

Changes at control inputs ( enable P

, enable T, load, UP/

DOWN), which modify the ope rating mode, hav e no effect

until clocking occur s. The function o f the co unter ( whether

enabled, disabled, loading, or counting) will be dictated

solely by the conditions m eeting the sta ble setup and hold

times.

Features

■ Fully synchronous operation for counting and

programming.

■ Internal look-ahead for fast counting.

■ Carry out put for n-bi t cascading.

■ Fully independent clock circuit

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

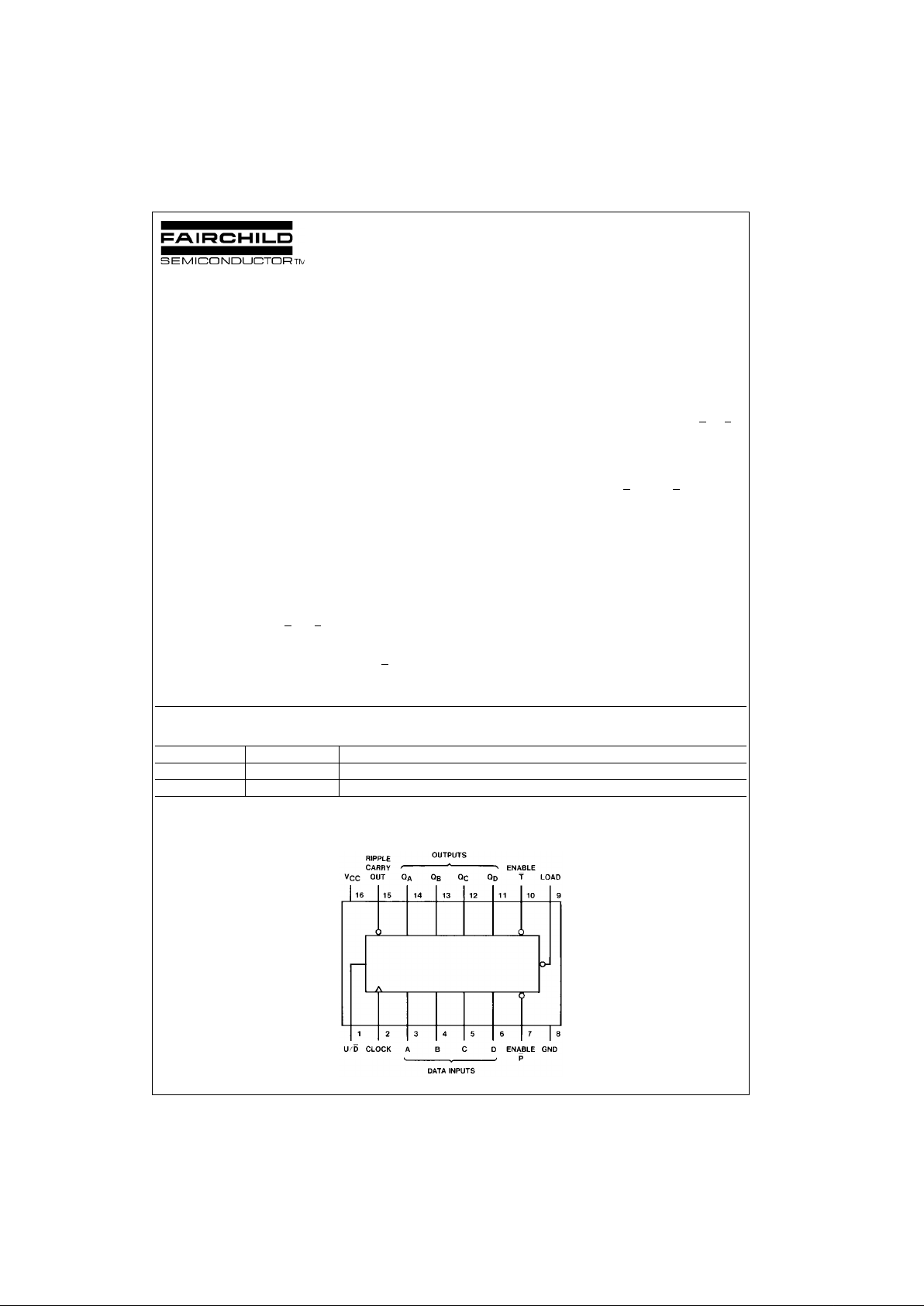

Connection Diagram

Order Number Package Number Package Description

DM74LS169AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74LS169AN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

DM74LS169A

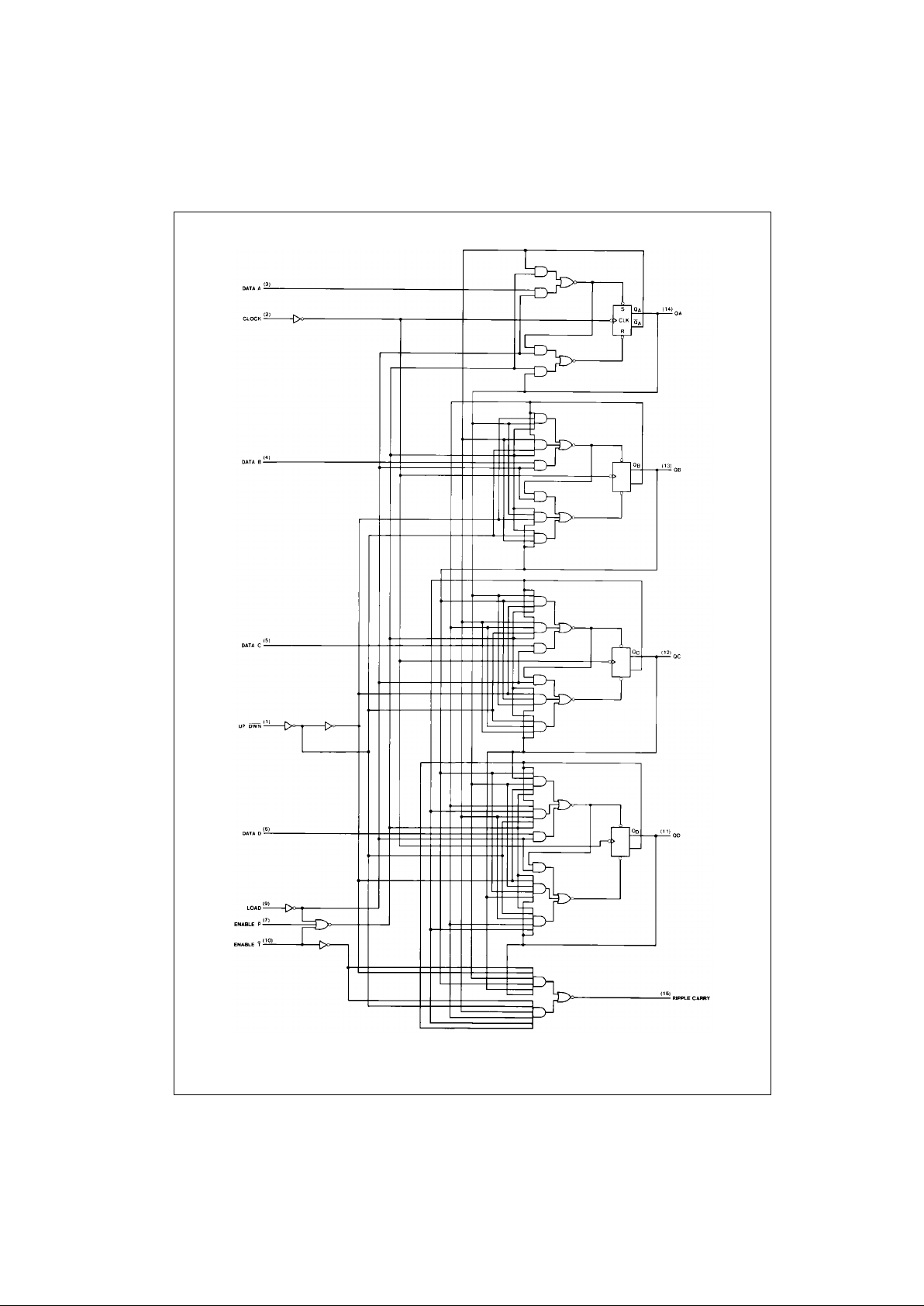

Logic Diagram

3 www.fairchildsemi.com

DM74LS169A

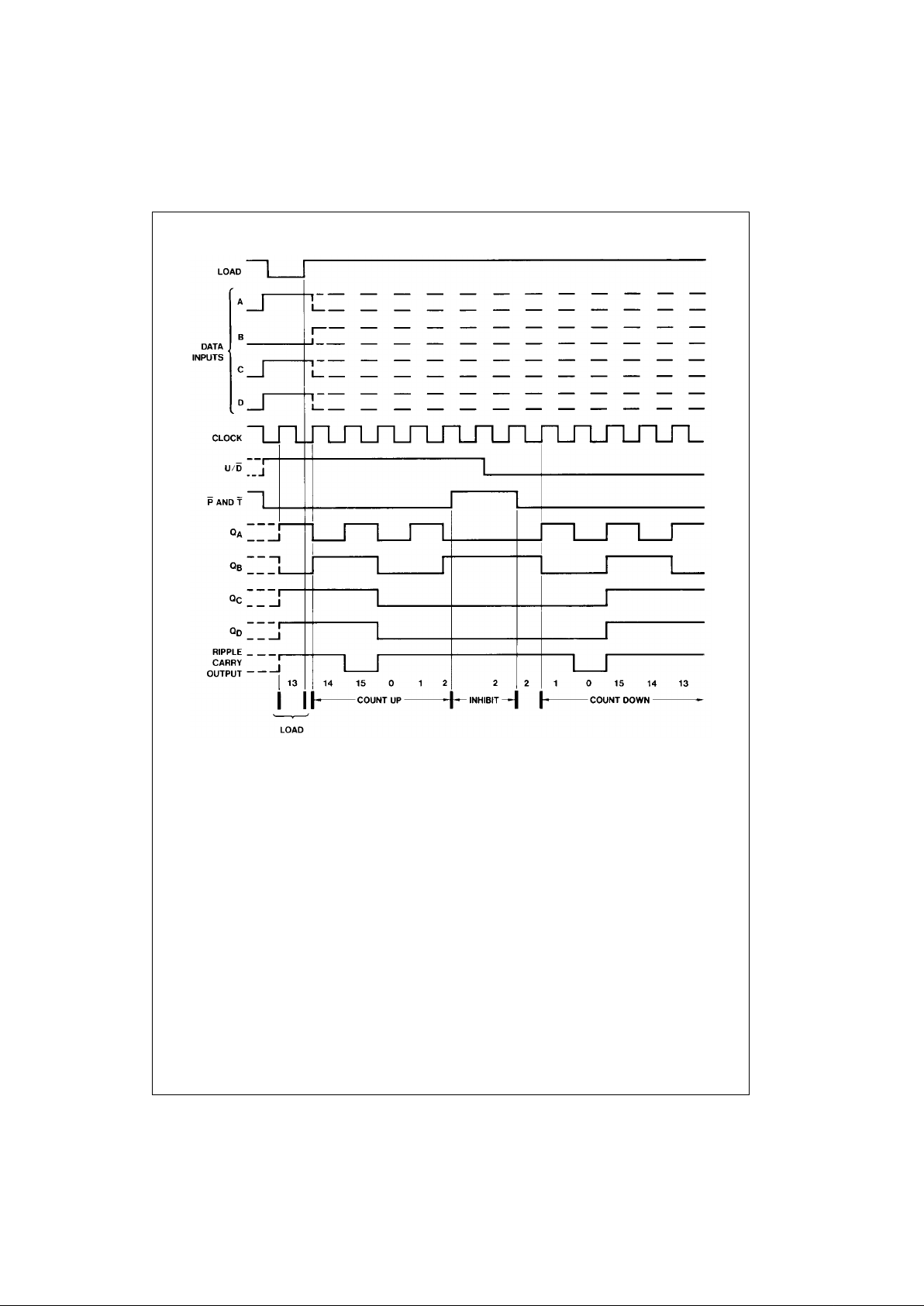

Timing Diagram

Typical Load, Count, and Inhibit Sequences

www.fairchildsemi.com 4

DM74LS169A

Absolute Maximum Ratings(Note 1)

Note 1: The “Absolute Maximum Ratin gs” are those v alues beyon d which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the co ndition s

for actual device operation.

Recommended Operating Conditions

Note 2: CL = 15 pF, RL = 2 kΩ, TA = 25°C and VCC = 5V.

Note 3: C

L

= 50 pF, RL = 2 kΩ, TA = 25°C and VCC = 5V.

Note 4: T

A

= 25°C and VCC = 5V.

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Note 5: All typicals are at VCC = 5V and TA = 25°C.

Note 6: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 7: I

CC

is measured after a mo m entary 4.5V, then ground, is applied to t he CLOCK with all other inputs grounded and all t he outputs OPEN.

Supply Voltage 7V

Input Voltage 7V

Operating Free Air Temperature Range 0°C to +70°C

Storage Temperature Range −65°C to +150°C

Symbol Parameter Min Nom Max Units

V

CC

Supply Voltage 4.75 5 5.25 V

V

IH

HIGH Level Input Voltage 2 V

V

IL

LOW Level Input Voltage 0.8 V

I

OH

HIGH Level Output Current −0.4 mA

I

OL

LOW Level Output Current 8 mA

f

CLK

Clock Frequency (Note 2) 0 25 MHz

Clock Frequency (Note 3) 0 20 MHz

t

W

Clock Pulse Width (Note 4) 25 ns

t

SU

Setup Time Data 20

(Note 4) Enable

20

T

or P ns

Load 25

U/D 30

t

H

Hold Time (Note 4) 0 ns

T

A

Free Air Operating Temperature 0 70 °C

Symbol Parameter Conditions Min

Typ

Max Units

(Note 5)

V

I

Input Clamp Voltage VCC = Min, II = −18 mA −1.5 V

V

OH

HIGH Level VCC = Min, IOH = Max

2.7 3.4 V

Output Voltage VIL = Max, VIH = Min

V

OL

LOW Level VCC = Min, IOL = Max

0.35 0.5

Output Voltage VIL = Max, VIH = Min V

IOL = 4 mA, VCC = Min 0.25 0.4

I

I

Input Current @ Max VCC = Max Enable T 0.2

mA

Input Voltage VI = 7V Others 0.1

I

IH

HIGH Level VCC = Max Enable T 40

µA

Input Current VI = 2.7V Others 20

I

IL

LOW Level VCC = Max Enable T −0.8

mA

Input Current VI = 0.4V Others −0.4

I

OS

Short Circuit Output Current VCC = Max (Note 6) −20 −100 mA

I

CC

Supply Current VCC = Max (Note 7) 20 34 mA

5 www.fairchildsemi.com

DM74LS169A

Switching Characteristic

at VCC = 5V and TA = 25°C

Note 8: The propagation delay from UP/DOWN to RIPPLE CARRY must be measured with the counter at either a minimum or a maximum count. As the

logic level of the UP/ DOWN input is changed, th e ripple carry ou tput will follow. If the c ount is minimum , the RIPPLE C ARRY output tran sition will be in

phase. If the count is max imum, the RIPPLE C AR RY output will be out of phase.

From (Input) RL = 2 kΩ

Symbol Parameter To (Output) CL = 15 pF CL = 50 pF Units

Min Max Min Max

f

MAX

Maximum Clock Frequency 25 20 MHz

t

PLH

Propagation Delay Time Clock to

35 39 ns

LOW-to-HIGH Level Output Ripple Carry

t

PHL

Propagation Delay Time Clock to

35 44 ns

HIGH-to-LOW Level Output Ripple Carry

t

PLH

Propagation Delay Time Clock to

20 24 ns

LOW-to-HIGH Level Output Any Q

t

PHL

Propagation Delay Time Clock to

23 32 ns

HIGH-to-LOW Level Output Any Q

t

PLH

Propagation Delay Time Enable T to

18 24 ns

LOW-to-HIGH Level Output Ripple Carry

t

PHL

Propagation Delay Time Enable T to

18 28 ns

HIGH-to-LOW Level Output Ripple Carry

t

PLH

Propagation Delay Time Up/Down to

25 30 ns

LOW-to-HIGH Level Output Ripple Carry (Note 8)

t

PHL

Propagation Delay Time Up/Down to

29 38 ns

HIGH-to-LOW Level Output Ripple Carry (Note 8)

www.fairchildsemi.com 6

DM74LS169A

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

Package Number M16A

7 www.fairchildsemi.com

DM74LS169A Synchronous 4-Bit Up/Down Binary Counter

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Package Number N16E

Fairchild does not assume any responsibility for use of any circu itry described, no circuit patent license s are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are dev ic es or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided i n the labe li ng, can be re asonably expected to result in a significant injury to the

user.

2. A critical componen t in any com ponent o f a l ife supp ort

device or system whose failu re to perform can b e reasonably expected to c ause th e fa i lure of the li fe s upp or t

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Loading...

Loading...