Page 1

PIC32MM0256GPM064 FAMILY

32-Bit Flash Microcontroller with MIPS32® microAptiv™ UC Core,

Low Power and USB

Operating Conditions

• 2.0V to 3.6V, -40ºC to +125ºC, DC to 25 MHz

Low-Power Modes

• Low-Power modes:

- Idle – CPU off, peripherals run from system clock

- Sleep – CPU and peripherals off:

- Fast wake-up Sleep with retention

- Low-power Sleep with retention

•0.65 μA Sleep current for RAM Retention

Regulator mode and 5 μA for Regulator Standby mode

• On-Chip 1.8V Voltage Regulator (VREG)

• On-Chip Ultra Low-Power Retention Regulator

High-Performance 32-Bit RISC CPU

• microAptiv™ UC 32-Bit Core with 5-Stage Pipeline

• microMIPS™ Instruction Set for 35% Smaller Code and

98% Performance compared to MIPS32 Instructions

• 1.53 DMIPS/MHz (37 DMIPS) (Dhrystone 2.1) Performance

• 3.17 CoreMark®/MHz (79 CoreMark) Performance

• 16-Bit/32-Bit Wide Instructions with 32-Bit Wide Data Path

• Two Sets of 32 Core Register Files (32-bit) to Reduce

Interrupt Latency

• Single-Cycle 32x16 Multiply and Two-Cycle 32x32 Multiply

• 64-Bit, Zero Wait State Flash with ECC to Maximize

Endurance/Retention

Microcontroller Features

• Up to 256K Flash Memory:

- 20,000 erase/write cycle endurance

- 20 years minimum data retention

- Self-programmable under software control

• Up to 32K SRAM Memory

• Multiple Interrupt Vectors with Individually

Programmable Priority

• Fail-Safe Clock Monitor mode

• Configurable Watchdog Timer with On-Chip, Low-Power

RC Oscillator

• Programmable Code Protection

• Selectable Oscillator Options Including:

- High-precision, 8 MHz Internal RC (FRC)

Oscillator – 2x/3x/4x/6x/12x/24x PLL, which can be

clocked from FRC or the Primary Oscillator

- Primary high-speed, crystal/resonator oscillator or

external clock

Peripheral Features

• USB 2.0 Compliant Full-Speed and Low-Speed Device,

Host and On-The-Go (OTG) Controller:

- Dedicated DMA

- Device mode operation from FRC oscillator;

no crystal oscillator required

• Atomic Set, Clear and Invert Operation on Select

Peripheral Registers

• High-Current Sink/Source

• Independent, Low-Power 32 kHz Timer Oscillator

• Three 4-Wire SPI modules:

- 16-byte FIFO

- Variable width

- I2S mode

• Three I2C Master and Slave w/Address Masking and

IPMI Support

• Three Enhanced Addressable UARTs:

- RS-232, RS-485 and LIN/J2602 support

- IrDA® with on-chip hardware encoder and decoder

• External Edge and Level Change Interrupt on All Ports

• Hardware Real-Time Clock and Calendar (RTCC)

• Up to 24 Peripheral Pin Select (PPS) Remappable Pins

• 21 Total 16-Bit Timers:

- Three dedicated 16-bit timers/counters

- Two can be concatenated to form a 32-bit timer

- Two additional 16-bit timers in each MCCP and

SCCP module, totaling 18

• Capture/Compare/PWM/Timer modules:

- Two 16-bit timers or one 32-bit timer in each module

- PWM resolution down to 21 ns

- Three Multiple Output (MCCP) modules:

- Flexible configuration as PWM, input capture,

output compare or timers

- Six PWM outputs

- Programmable dead time

- Auto-shutdown

- Six Single Output (SCCP) modules:

- Flexible configuration as PWM, input capture,

output compare or timers

- Single PWM output

• Reference Clock Output (REFO)

• Four Configurable Logic Cells (CLCs) with Internal

Connections to Select Peripherals and PPS

• Four-Channel Hardware DMA with Automatic Data Size

Detection and CRC Engine

Debug Features

• Two Programming and Debugging Interfaces:

- Two-wire ICSP™ interface with non-intrusive access

and real-time data exchange with application

- Four-wire MIPS® standard Enhanced JTAG interface

• IEEE Standard 1149.2 Compatible (JTAG) Boundary Scan

2016-2019 Microchip Technology Inc. DS60001387D-page 1

Page 2

PIC32MM0256GPM064 FAMILY

Analog Features

• Three Analog Comparators with Input Multiplexing

• Programmable High/Low-Voltage Detect (HLVD)

• 5-Bit Comparator Voltage Reference DAC with Pin Output

• Up to 24-Channel, Software-Selectable 10/12-Bit SAR

Analog-to-Digital Converter (ADC):

- 12-bit 200K samples/second conversion rate

(single Sample-and-Hold)

- 10-bit 300k samples/second conversion rate

(single Sample-and-Hold)

- Sleep mode operation

- Low-voltage boost for input

- Band gap reference input feature

- Windowed threshold compare feature

- Auto-scan feature

• Brown-out Reset (BOR)

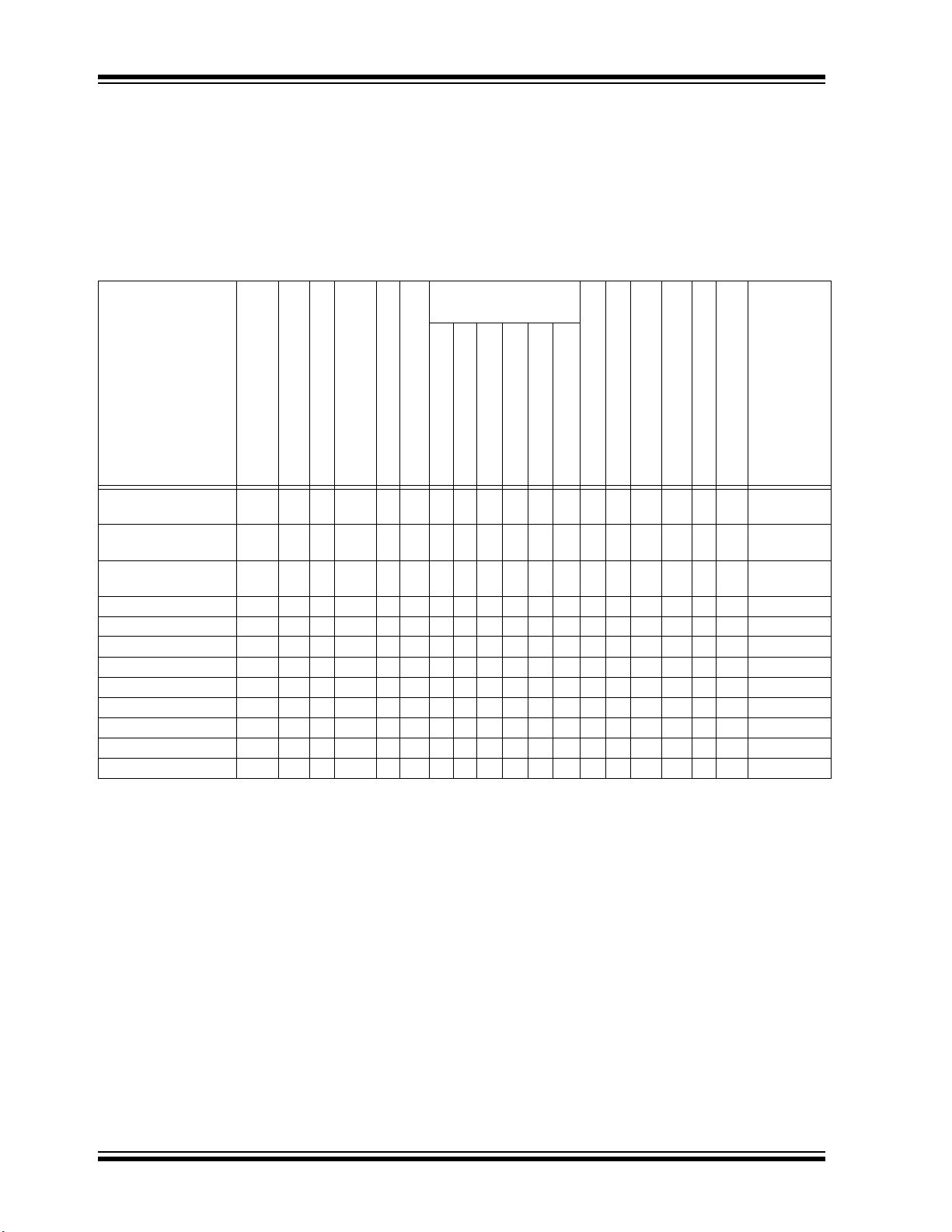

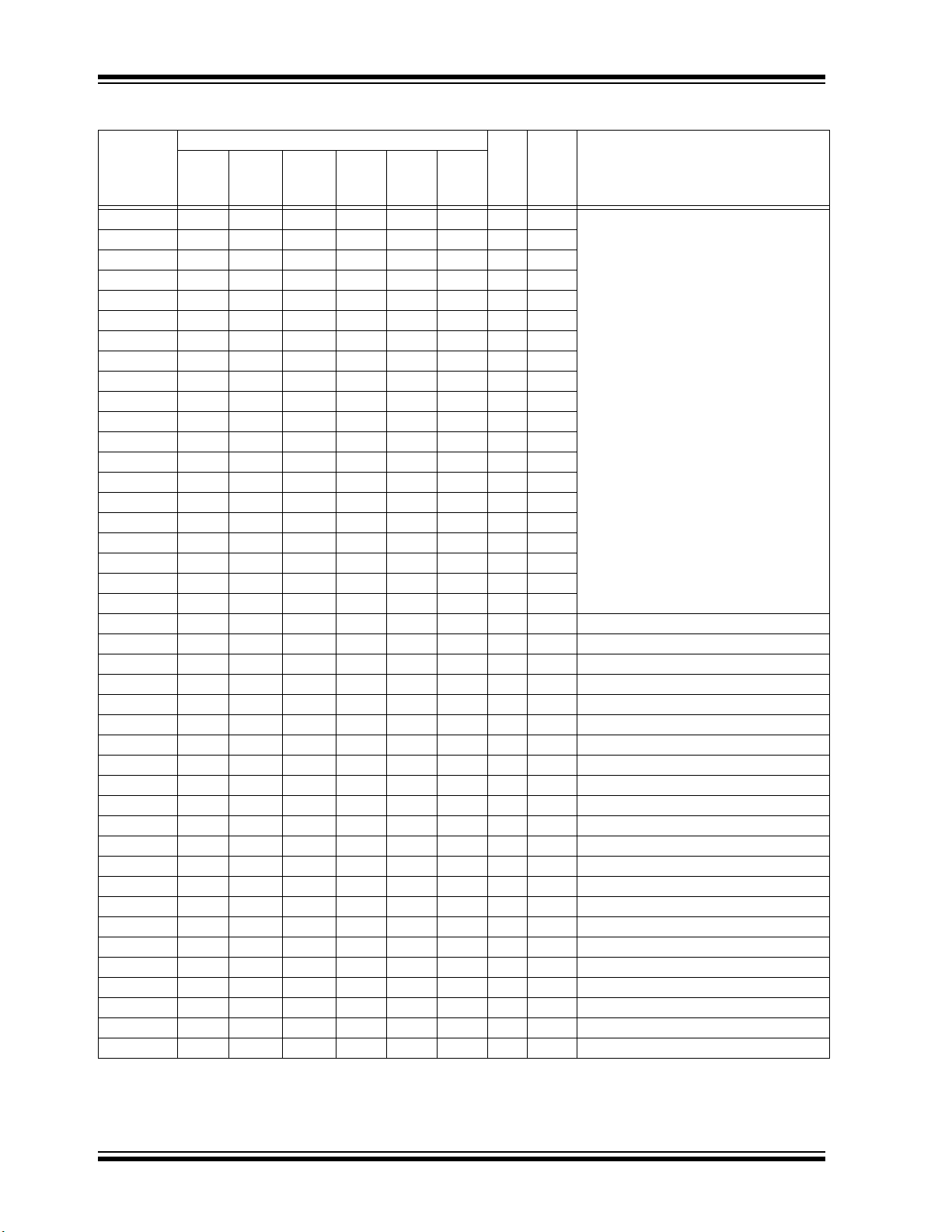

TABLE 1: PIC32MM0256GPM064 FAMILY DEVICES

Remappable

Peripherals

Device

PIC32MM0064GPM028 28 64 16 21/18 21 18 3 3 3 6 4 3 12 3 Yes Yes 3 Yes SSOP/QFN/

PIC32MM0128GPM028 28 128 16 21/18 21 18 3 3 3 6 4 3 12 3 Yes Yes 3 Yes SSOP/QFN/

PIC32MM0256GPM028 28 256 32 21/18 21 18 3 3 3 6 4 3 12 3 Yes Yes 3 Yes SSOP/QFN/

PIC32MM0064GPM036 36/40 64 16 27/20 21 20 3 3 3 6 4 3 15 3 Yes Yes 3 Yes VQFN/UQFN

PIC32MM0128GPM036 36/40 128 16 27/20 21 20 3 3 3 6 4 3 15 3 Yes Yes 3 Yes VQFN/UQFN

PIC32MM0256GPM036 36/40 256 32 27/20 21 20 3 3 3 6 4 3 15 3 Yes Yes 3 Yes VQFN/UQFN

PIC32MM0064GPM048 48 64 16 38/24 21 24 3 3 3 6 4 3 17 3 Yes Yes 3 Yes UQFN/TQFP

PIC32MM0128GPM048 48 128 16 38/24 21 24 3 3 3 6 4 3 17 3 Yes Yes 3 Yes UQFN/TQFP

PIC32MM0256GPM048 48 256 32 38/24 21 24 3 3 3 6 4 3 17 3 Yes Yes 3 Yes UQFN/TQFP

PIC32MM0064GPM064 64 64 16 52/24 21 24 3 3 3 6 4 3 20 3 Yes Yes 3 Yes QFN/TQFP

PIC32MM0128GPM064 64 128 16 52/24 21 24 3 3 3 6 4 3 20 3 Yes Yes 3 Yes QFN/TQFP

PIC32MM0256GPM064 64 256 32 52/24 21 24 3 3 3 6 4 3 20 3 Yes Yes 3 Yes QFN/TQFP

Note 1: UART1 has assigned pins. UART2 and UART3 are remappable.

2: SPI1 and SPI3 have assigned pins. SPI2 is remappable.

3: SCCP can be configured as a PWM with one output, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

4: MCCP can be configured as a PWM with up to six outputs, input capture, output compare, 2 x 16-bit timers or

1 x 32-bit timer.

Pins

Program Memory (Kbytes)

Data Memory (Kbytes)

16-Bit Timers Maximum

General Purpose I/O/PPS

PWM Outputs Maximum

Dedicated 16-Bit Timers

(4)

(3)

/LIN/J2602

(1)

UART

MCCP

SCCP

S

2

/I

(2)

CLC

SPI

10/12-Bit ADC (External Channels)

CRC

Comparators

RTCC

C

2

I

USB

Packages

UQFN

UQFN

UQFN

DS60001387D-page 2 2016-2019 Microchip Technology Inc.

Page 3

Pin Diagrams

28-Pin SSOP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

MCLR

PGEC2/RP1/RA0

PGED2/RP2/RA1

PGED1/RP6/RB0

PGEC1/RP7/RB1

RP8/RB2

TDI/RP9/RB3

V

SS

OSC1/RP3/RA2

OSC2/RP4/RA3

(1)

SOSCI/RP10/RB4

SOSCO/RP5/RA4

V

DD

PGED3/RP11/RB5

V

BUS/RB6

RP12/RB7

TCK/RP13/RB8

(1)

TMS/RP14/RB9

(1,2)

PGEC3/TDO/RP18/RC9

(1)

VCAP

D-/RB10

D+/RB11

V

USB3V3

RP15/RB13

(1)

RP16/RB14

RP17/RB15

(1)

AVSS/VSS

AVDD/VDD

Legend: Shaded pins are up to 5V tolerant.

Note 1: High drive strength pin.

2: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

PIC32MM0256GPM028

PIC32MM0256GPM064 FAMILY

TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN SSOP DEVICES

Pin Function Pin Function

1MCLR 15 VBUS/RB6

2PGEC2/V

3PGED2/V

4 PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0 18 TMS/REFCLKI/RP14/SDA1/T1CK/T1G/T2CK/T2G/U1RTS/U1BCLK/SDO1/OCM1B/

5 PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1 19 PGEC3/TDO/RP18/ASCL1

6 AN4/C1INB/RP8/SDA2/OCM2E/RB2 20 VCAP

7 TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3 21 D-/RB10

8V

SS 22 D+/RB11

9 OSC1/CLKI/AN5/RP3/OCM1C/RA2 23 V

10 OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3

11 SOSCI/AN7/RP10/OCM3C/RB4 25 CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14

12 SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4 26 AN10/C3INA/REFCLKO/RP17/U1RX/SS1

13 VDD 27 AVSS/VSS

14 PGED3/RP11/ASDA1

OCM3E/RB5

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

3: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

REF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0 16 RP12/SDA3/SDI3/OCM3F/RB7

REF-/AN1/RP2/OCM1F/RA1 17 TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8

(1)

(2)

/USBID/SS3/FSYNC3/

INT2/RB9

USB3V3

(1,3)

24 AN8/LVDIN/RP15/SCL3/SCK3/OCM3A/RB13

28 AVDD/VDD

(2)

/T3CK/T3G/USBOEN/SDO3/OCM2A/RC9

(1)

(1)

/FSYNC1/OCM2B/INT0/RB15

(1)

(1)

2016-2019 Microchip Technology Inc. DS60001387D-page 3

Page 4

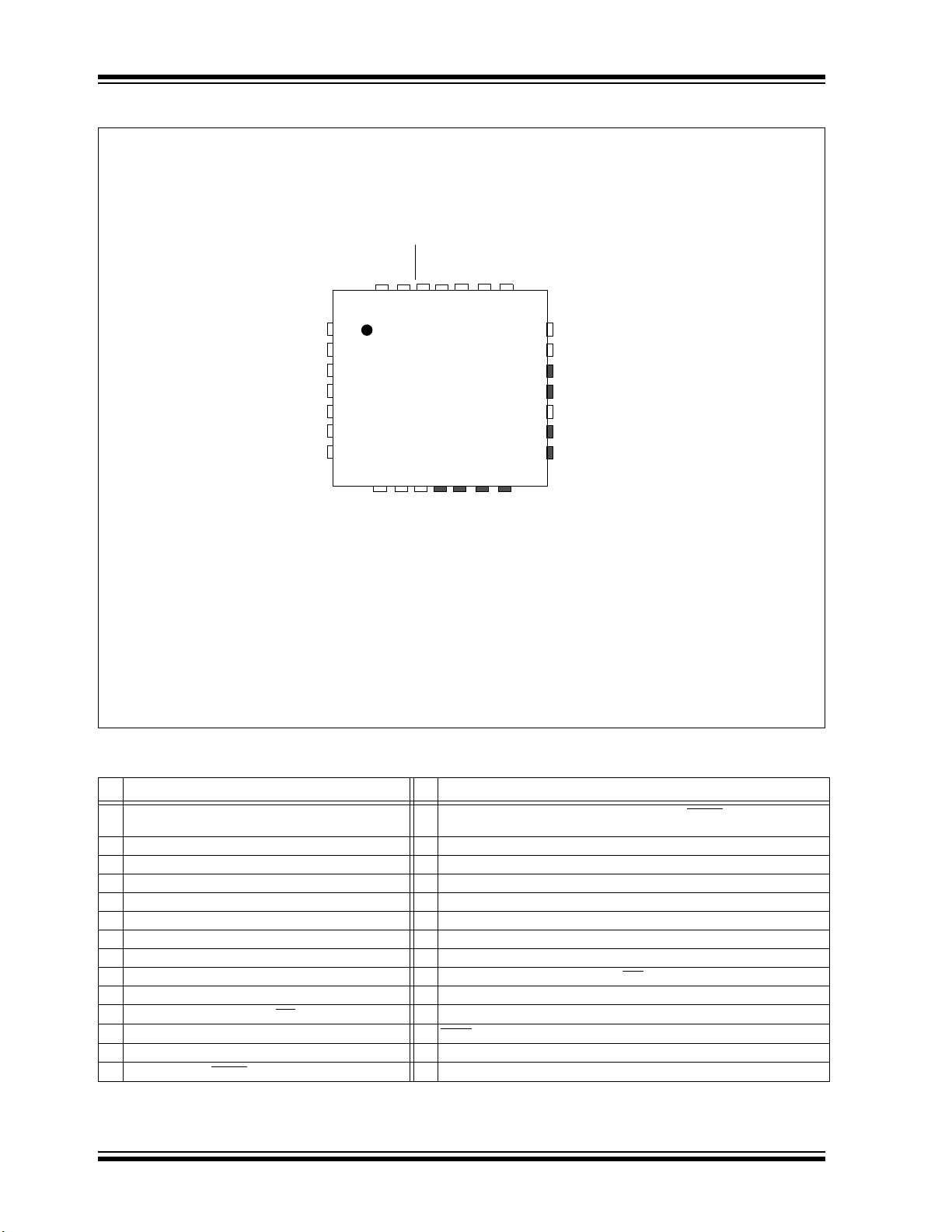

PIC32MM0256GPM064 FAMILY

28-Pin QFN/UQFN

(3)

10 11

2

3

6

1

18

19

20

21

22

12 13 14

15

8

7

16

17

232425262728

9

5

4

PGEC1/RP7/RB1

RP8/RB2

TDI/RP9/RB3

Vss

OSC1/RP3/RA2

OSC2/RP4/RA3

(1)

PGED1/RP6/RB0

SOSCI/RP10/RB4

SOSCO/RP5/RA4

V

DD

PGED3/RP11/RB5

V

BUS/RB6

RP12/RB7

TCK/RP13/RB8

(1)

TMS/RP14/RB9

(1,2)

PGEC3/TDO/RP18/RC9

(1)

VCAP

D-/RB10

D+/RB11

V

USB3V3

RP15/RB13

(1)

RP16/RB14

RP17/RB15

(1)

AVSS/VSS

AVDD/VDD

MCLR

PGEC2/RP1/RA0

PGED2/RP2/RA1

PIC32MM0256GPM028

Legend: Shaded pins are up to 5V tolerant.

Note 1: High drive strength pin.

2: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

3: The back side thermal pad is not electrically connected.

Pin Diagrams (Continued)

TABLE 3: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN QFN/UQFN DEVICES

Pin Function Pin Function

1 PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0 15 TMS/REFCLKI/RP14/SDA1/T1CK/T1G/T2CK/T2G/U1RTS/U1BCLK/SDO1/

2 PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1 16 PGEC3/TDO/RP18/ASCL1

3 AN4/C1INB/RP8/SDA2/OCM2E/RB2 17 VCAP

4 TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3 18 D-/RB10

5V

SS 19 D+/RB11

6 OSC1/CLKI/AN5/RP3/OCM1C/RA2 20 V

7 OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3

8 SOSCI/AN7/RP10/OCM3C/RB4 22 CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14

9 SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4 23 AN10/C3INA/REFCLKO/RP17/U1RX/SS1

10 VDD 24 AVSS/VSS

11 PGED3 /RP11/ASDA1

12 VBUS/RB6 26 MCLR

13 RP12/SDA3/SDI3/OCM3F/RB7 27 PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0

14 TCK/RP13/SCL1/U1CTS

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

3: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

(2)

/USBID/SS3/FSYNC3/OCM3E/RB5 25 AVDD/VDD

/SCK1/OCM1A/RB8

(1)

(1)

21 AN8/LVDIN/RP15/SCL3/SCK3/OCM3A/RB13

28 PGED2/VREF-/AN1/RP2/OCM1F/RA1

OCM1B/INT2/RB9

USB3V3

(1,3)

(2)

/T3CK/T3G/USBOEN/SDO3/OCM2A/RC9

(1)

/FSYNC1/OCM2B/INT0/RB15

(1)

(1)

DS60001387D-page 4 2016-2019 Microchip Technology Inc.

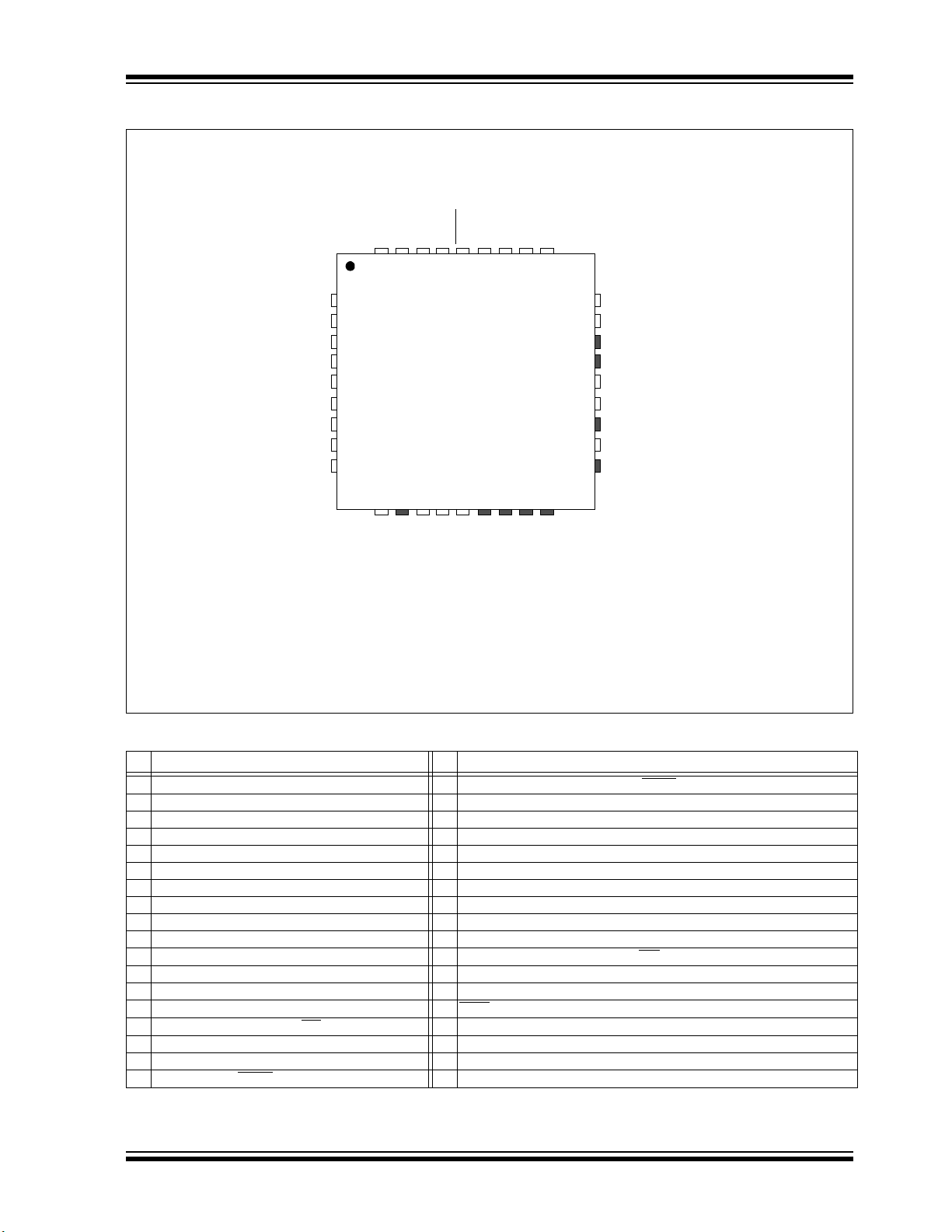

Page 5

Pin Diagrams (Continued)

36-Pin QFN

(3)

RP8/RB2

TDI/RP9/RB3

RC0

RC1

RP19/RC2

V

SS

OSC1/RP3/RA2

OSC2/RP4/RA3

(1)

SOSCI/RP10/RB4

SOSCO/

RP5

/RA4

RP24/RA9

V

SS

VDD

RC3

V

BUS/RB6

RP12/RB7

TCK/

RP13

/RB8

(1)

TMS/RP14/RB9

(1,2)

RC8

PGEC3/TDO/RP18/RC9

(1)

VCAP

VDD

D+/RB11

V

USB3V3

D-/RB10

RP15/RB13

(1)

RP16/RB14

RP17/RB15

(1)

AVSS/VSS

AVDD/VDD

MCLR

PGEC2/

RP1

/RA0

PGED2/

RP2

/RA1

PGED1/

RP6

/RB0

PGEC1/

RP7

/RB1

9

1

2

3

4

5

161718

101112

13

31

7

6

3635343332

14

15

24

25

26

27

19

20

21

22

23

29

28

8

30

PIC32MM0256GPM036

PGED3/

RP11

/RB5

Legend: Shaded pins are up to 5V tolerant.

Note 1: High drive strength pin.

2: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

3: The back side thermal pad is not electrically connected.

PIC32MM0256GPM064 FAMILY

TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN QFN DEVICES

Pin Function Pin Function

1 AN4/C1INB/

2 TDI/AN11/C1INA/

3 AN12/C2IND/T2CK/T2G/RC0 21 PGEC3/TDO/

4 AN13/T3CK/T3G/RC1 22 V

5

RP19

6V

SS

7 OSC1/CLKI/AN5/

8 OSC2/CLKO/AN6/C3IND/

9 SOSCI/AN7/

10 SOSCO/SCLKI/

RP24

11

12 V

SS

13 V

DD

14 RC3 32 MCLR

15 PGED3/

BUS

16 V

RP12

17

18 TCK/

Note 1:

2:

3: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

RP8

/OCM2A/RC2 23 V

/OCM3A/RA9 29 AN10/C3INA/REFCLKO/

RP11

/RB6 34 PGED2/V

/SDA3/SDI3/OCM3F/RB7 35 PGED1/AN2/C1IND/C2INB/C3INC/

RP13

/SCL1/U1CTS/SCK1/OCM1A/RB8

High drive strength pin.

Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

/SDA2/OCM2E/RB2 19 TMS/REFCLKI/

RP9

/SCL2/OCM2F/RB3 20 AN14/LVDIN/C2INC/RC8

RP3

/OCM1C/RA2 25 D+/RB11

RP10

RP4

/OCM1D/RA3

/OCM3C/RB4 27 AN8/

RP5

/PWRLCLK/OCM3D/RA4 28 CV

(2)

/ASDA1

/USBID/SS3/FSYNC3/OCM3E/RB5 33 PGEC2/V

(1)

(1)

RP14

/SDA1/T1CK/T1G/U1RTS/U1BCLK/SDO1/OCM1B/INT2/RB9

CAP

DD

24 D-/RB10

26 V

USB3V3

RP15

REF

/AN9/C3INB/

30 AVSS/V

31 AVDD/V

36 PGEC1/AN3/C1INC/C2INA/

SS

DD

RP18

/ASCL1

/SCL3/SCK3/RB13

RP16

/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14

RP17

REF

+/CV

REF

+/AN0/

REF

-/AN1/

RP2

/OCM1F/RA1

(2)

/USBOEN/SDO3/RC9

(1)

/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15

RP1

/OCM1E/INT3/RA0

RP6

/OCM2C/RB0

RP7

/OCM2D/RB1

(1,3)

(1)

(1)

2016-2019 Microchip Technology Inc. DS60001387D-page 5

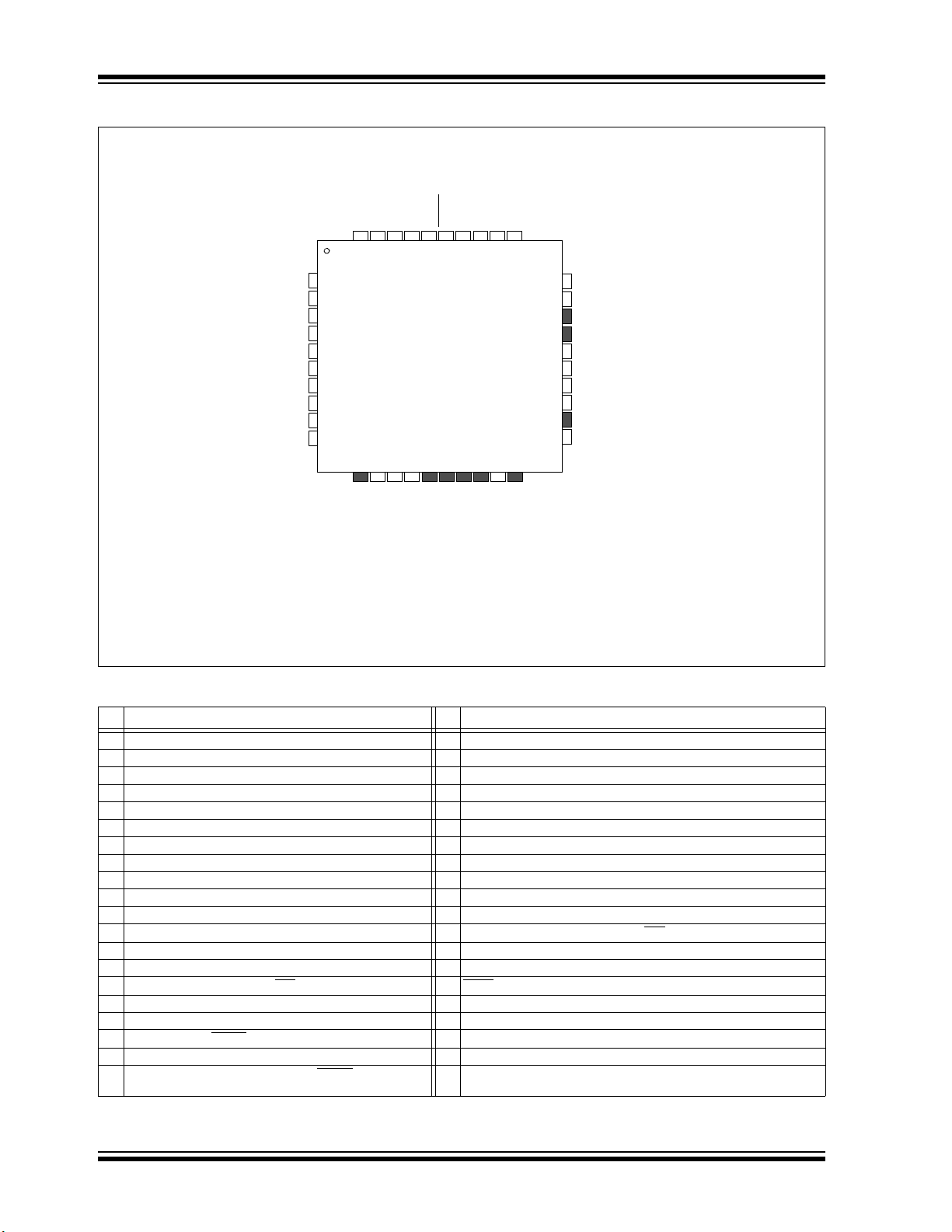

Page 6

PIC32MM0256GPM064 FAMILY

40-Pin UQFN

(3)

111213141516171819

20

403938373635343332

31

29

28

27

26

25

24

23

22

30

10

RC0

RP8

/RB2

TDI/

RP9

/RB3

RC1

RP19

/RC2

V

SS

OSC1/

RP3

/RA2

OSC2/

RP4

/RA3

(1)

SOSCI/

RP10

/RB4

RP24

/RA9

V

SS

V

DD

RC3

PGED3/

RP11

/RB5

V

BUS

/RB6

RP12

/RB7

TCK/

RP13

/RB8

(1)

N/C

TMS/

RP14

/RB9

(1,2)

RC8

PGEC3/TDO/

RP18

/RC9

(1)

N/C

V

CAP

N/C

AV

DD

/V

DD

MCLR

PGEC2/

RP1

/RA0

PGED2/

RP2

/RA1

PGED1/

RP6

/RB0

PGEC1/

RP7

/RB1

N/C

AV

SS

/V

SS

RP17

/RB15

(1)

RP16

/RB14

111213141516171819

20

403938373635343332

31

29

28

27

26

25

24

23

22

21

30

10

V

DD

D-/RB10

D+/RB11

V

USB3V3

RP15

/RB13

(1)

1

2

3

4

5

6

7

8

9

PIC32MM0256GPM036

1

2

3

4

5

6

7

8

9

SOSCO/

RP5

/RA4

Legend: Shaded pins are up to 5V tolerant.

Note 1: High drive strength pin.

2: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

3: The back side thermal pad is not electrically connected.

Pin Diagrams (Continued)

TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 40-PIN UQFN DEVICES

Pin Function Pin Function

1 AN4/C1INB/RP8/SDA2/OCM2E/RB2 21 AN14/LVDIN/C2INC/RC8

2 TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3 22 PGEC3/TDO/RP18/ASCL1

3 AN12/C2IND/T2CK/T2G/RC0 23 N/C

4 AN13/T3CK/T3G/RC1 24 V

5 RP19/OCM2A/RC2 25 N/C

6V

7 OSC1/CLKI/AN5/RP3/OCM1C/RA2 27 D-/RB10

8 OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3

9 SOSCI/AN7/RP10/OCM3C/RB4 29 V

10 SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4 30 AN8/RP15/SCL3/SCK3/RB13

11 RP24/OCM3A/RA9 31 CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14

12 V

13 VDD 33 AVSS/VSS

14 RC3 34 AVDD/VDD

15 PGED3/RP11/ASDA1

16 VBUS/RB6 36 PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0

17 RP12/SDA3/SDI3/OCM3F/RB7 37 PGED2/V

18 TCK/RP13/SCL1/U1CTS

19 N/C 39 PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1

20 TMS/REFCLKI/RP14/SDA1/T1CK/T1G/U1RTS

Note 1:

SS 26 VDD

(2)

/USBID/SS3/FSYNC3/OCM3E/RB5 35 MCLR

SS 32 AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15

SDO1/OCM1B/INT2/RB9

High drive strength pin.

2:

Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

3: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

/SCK1/OCM1A/RB8

(1,3)

DS60001387D-page 6 2016-2019 Microchip Technology Inc.

(1)

(1)

/U1BCLK/

(2)

/SDO3/USBOEN/RC9

CAP

28 D+/RB11

USB3V3

38 PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0

40 N/C

(1)

REF-/AN1/RP2/OCM1F/RA1

(1)

(1)

Page 7

Pin Diagrams (Continued)

48-Pin UQFN, TQFP

(3)

10

11

2

3

4

5

6

1

1819202122

23

131415

38

8

7

4443424140

39

16

17

29

30

31

32

33

34

35

25

26

27

28

474546

9

37

12

24

36

48

PIC32MM0256GPM048

TMS/RP14/RB9

(1,2)

RP23/RC6

RP20/RC7

RC8

PGEC3/TDO/RP18/RC9

(1)

VSS

VCAP

RA15

D-/RB10

D+/RB11

V

USB3V3

RP15/RB13

(1)

RP22/RA10

(1)

RP21/RA7

RP16/RB14

RP17/RB15

(1)

AVSS/VSS

AVDD/VDD

MCLR

RA6

PGEC2/RP1/RA0

PGED2/RP2/RA1

PGED1/RP6/RB0

PGEC1/RP7/RB1

RP8/RB2

TDI/RP9/RB3

RC0

RC1

RP19/RC2

VDD

VSS

OSC1/RP3/RA2

OSC2/RP4/RA3

(1)

SOSCO/RP5/RA4

SOSCI/RP10/RB4

RA8

(1)

RP24/RA9

RD0

(1)

RC3

RC4

RC5

VSSVDD

RC12

RP12/RB7

PGED3/RP11/RB5

V

BUS/RB6

TCK/RP13/RB8

(1)

Legend: Shaded pins are up to 5V tolerant.

Note 1: High drive strength pin.

2: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

3: The back side thermal pad is not electrically connected.

PIC32MM0256GPM064 FAMILY

2016-2019 Microchip Technology Inc. DS60001387D-page 7

Page 8

PIC32MM0256GPM064 FAMILY

TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 48-PIN UQFN/TQFP DEVICES

Pin Function Pin Function

1TMS/RP14/SDA1/OCM1B/INT2/RB9

(1,3)

2 RP23/RC6 26 TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3

3 RP20/RC7 27 AN12/C2IND/T2CK/T2G/RC0

4 AN14/LVDIN/C2INC/RC8 28 AN13/T3CK/T3G/RC1

5 PGEC3/TDO/RP18/ASCL1

6V

SS 30 VDD

(2)

/USBOEN/RC9

(1)

7VCAP 31 VSS

8 RTCC/RA15 32 OSC1/CLKI/AN5/RP3/OCM1C/RA2

9 D-/RB10 33 OSC2/CLKO/AN6/C3IND/RP4/RA3

10 D+/RB11 34 SDO3/RA8

11 VUSB3V3 35 SOSCI/AN7/RP10/OCM3C/RB4

12 AN8/RP15/SCL3/RB13

13 RP22/SCK3/RA10

(1)

(1)

14 RP21/SDI3/RA7 38 REFCLKI/T1CK/T1G/U1RTS

15 CVREF/AN9/C3INB/RP16/VBUSON/SDI1/OCM3B/INT1/RB14 39 OCM2B/RC3

16 AN10/C3INA/REFCLKO/RP17/SS1

17 AV

SS/VSS 41 AN15/OCM1D/RC5

18 AV

DD/VDD 42 VSS

/FSYNC1/INT0/RB15

(1)

19 MCLR 43 VDD

20 AN19/U1RX/RA6 44 U1TX/RC12

21 PGEC2/V

22 PGED2/V

REF+/CVREF+/AN0/RP1/RA0 45 PGED3/RP11/ASDA1

REF-/AN1/RP2/OCM1F/RA1 46 VBUS/RB6

23 PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0 47 RP12/SDA3/OCM3F/RB7

24 PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1 48 TCK/RP13/SCL1/U1CTS

Note 1: High drive strength pin.

2:

Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

3: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

25 AN4/C1INB/RP8/SDA2/OCM2E/RB2

29 RP19/OCM2A/RC2

(1)

(1)

36 SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4

37 RP24/OCM3A/RA9

/U1BCLK/SDO1/RD0

40 OCM1E/INT3/RC4

(2)

/USBID/SS3/FSYNC3/OCM3E/RB5

/SCK1/OCM1A/RB8

(1)

(1)

DS60001387D-page 8 2016-2019 Microchip Technology Inc.

Page 9

Pin Diagrams (Continued)

64-Pin QFN, TQFP

(3)

PIC32MM0256GPM064

646362616059585756555453525150

49

1

48

247

346

4

45

5

44

643

7

42

8

41

9

40

10 39

11

38

12 37

13

36

14

35

15 34

16 33

171819202122232425262728293031

32

RP22/RA10

(1)

RP15/RB13

(1)

VUSB3V3

D+/RB11

D-/RB10

RA14

RA15

VDDVCAP

PGEC3/TDO/RP18/RC9

(1)

RA5

RD1

RC8

RP20/RC7

RP23/RC6

TMS/RP14/RB9

(1,3)

TCK/RP13/RB8

(1)

RC13

(1)

RP12/RB7

RC10

V

BUS/RB6

PGED3/RP11/RB5

RC15

RC12

V

DD

VSS

RC5

RC4

RC3

RD0

(1)

RD3

VDD

VSS

RC0

RC1

RP19/RC2

RC11

V

DD

VSS

OSC1/RP3/RA2

OSC2/RP4/RA3

(1)

RA8

(1)

SOSCI/RP10/RB4

SOSCO/RP5/RA4

RP24/RA9

RD4

RD2

RP21/RA7

RP16/RB14

RP17/RB15

(1)

AVSS/VSS

AVDD/VDD

RA13

RA12

RA11

MCLR

RA6

PGEC2/RP1/RA0

PGED2/RP2/RA1

PGED1/RP6/RB0

PGEC1/RP7/RB1

RP8/RB2

TDI/RP9/RB3

RC14

Legend: Shaded pins are up to 5V tolerant.

Note 1: High drive strength pin.

2: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

3: The back side thermal pad is not electrically connected.

PIC32MM0256GPM064 FAMILY

2016-2019 Microchip Technology Inc. DS60001387D-page 9

Page 10

PIC32MM0256GPM064 FAMILY

TABLE 7: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 64-PIN QFN/TQFP DEVICES

Pin Function Pin Function

1 RP21/SDI3/RA7 33 OCM3B/RD3

REF/AN9/C3INB/RP16/VBUSON/RB14 34 REFCLKI/T1CK/T1G/U1RTS/U1BCLK/SDO1/RD0

2CV

3 AN10/C3INA/REFCLKO/RP17/RB15

4AV

SS 36 OCM1E/INT3/RC4

5AV

DD 37 AN15/OCM1D/RC5

6 AN16/U1CTS

/RA13 38 VSS

(1)

35 OCM2B/RC3

7 AN17/OCM1A/RA12 39 VDD

8 AN18/RA11 40 U1TX/RC12

9MCLR

41 OCM3D/RC14

10 AN19/U1RX/RA6 42 OCM3E/RC15

11 PGEC2/V

12 PGED2/V

REF+/CVREF+/AN0/RP1/RA0 43 PGED3/RP11/ASDA1

REF-/AN1/RP2/OCM1F/RA1 44 VBUS/RB6

(2)

/USBID/RB5

13 PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0 45 OCM3F/RC10

14 PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1 46 RP12/SDA3/RB7

15 AN4/C1INB/RP8/SDA2/OCM2E/RB2 47 SCK1/RC13

16 TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3 48 TCK/RP13/SCL1/RB8

17 VDD 49 TMS/RP14/SDA1/INT2/RB9

(1)

(1)

(1,3)

18 VSS 50 RP23/RC6

19 AN12/C2IND/T2CK/T2G/RC0 51 RP20/RC7

20 AN13/T3CK/T3G/RC1 52 AN14/LVDIN/C2INC/RC8

21 RP19/OCM2A/RC2 53 OCM1B/RD1

22 SS3

/FSYNC3/RC11 54 OCM3A/RA5

23 V

DD 55 PGEC3/TDO/RP18/ASCL1

(2)

/USBOEN/RC9

24 VSS 56 VCAP

25 OSC1/CLKI/AN5/RP3/OCM1C/RA2 57 VDD

26 OSC2/CLKO/AN6/C3IND/RP4/RA3

27 SDO3/RA8

(1)

(1)

58 RTCC/RA15

59 OCM3C/RA14

28 SOSCI/AN7/RP10/RB4 60 D-/RB10

29 SOSCO/SCLKI/RP5/PWRLCLK/RA4 61 D+/RB11

30 RP24/RA9 62 V

31 SDI1/INT1/RD4 63 AN8/RP15/SCL3/RB13

32 SS1/FSYNC1/INT0/RD2 64 RP22/SCK3/RA10

USB3V3

(1)

(1)

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

3: This pin may toggle during ICSP programming. Refer to Section 2.6 “JTAG”.

(1)

(1)

DS60001387D-page 10 2016-2019 Microchip Technology Inc.

Page 11

PIC32MM0256GPM064 FAMILY

Table of Contents

1.0 Device Overview ........................................................................................................................................................................ 15

2.0 Guidelines for Getting Started with 32-Bit Microcontrollers........................................................................................................ 23

3.0 CPU............................................................................................................................................................................................ 29

4.0 Memory Organization................................................................................................................................................................. 39

5.0 Flash Program Memory.............................................................................................................................................................. 45

6.0 Resets........................................................................................................................................................................................ 53

7.0 CPU Exceptions and Interrupt Controller ................................................................................................................................... 59

8.0 Direct Memory Access (DMA) Controller ................................................................................................................................... 77

9.0 Oscillator Configuration .............................................................................................................................................................. 97

10.0 I/O Ports ................................................................................................................................................................................... 113

11.0 Timer1 ...................................................................................................................................................................................... 127

12.0 Timer2 and Timer3 .................................................................................................................................................................. 131

13.0 Watchdog Timer (WDT) ........................................................................................................................................................... 137

14.0 Capture/Compare/PWM/Timer Modules (MCCP and SCCP) .................................................................................................. 141

15.0 Serial Peripheral Interface (SPI) and Inter-IC Sound (I2S)....................................................................................................... 157

16.0 Inter-Integrated Circuit (I2C) ..................................................................................................................................................... 165

17.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 173

18.0 USB On-The-Go (OTG)............................................................................................................................................................ 179

19.0 Real-Time Clock and Calendar (RTCC) ................................................................................................................................... 207

20.0 12-Bit ADC Converter with Threshold Detect........................................................................................................................... 215

21.0 Configurable Logic Cell (CLC).................................................................................................................................................. 227

22.0 Comparator .............................................................................................................................................................................. 243

23.0 Voltage Reference (CVREF) ..................................................................................................................................................... 249

24.0 High/Low-Voltage Detect (HLVD)............................................................................................................................................. 253

25.0 Power-Saving Features ........................................................................................................................................................... 257

26.0 Special Features ...................................................................................................................................................................... 263

27.0 Instruction Set .......................................................................................................................................................................... 281

28.0 Development Support............................................................................................................................................................... 283

29.0 Electrical Characteristics.......................................................................................................................................................... 285

30.0 Packaging Information.............................................................................................................................................................. 317

Appendix A: Revision History............................................................................................................................................................. 347

Index ................................................................................................................................................................................................. 349

The Microchip Website ...................................................................................................................................................................... 353

Customer Change Notification Service .............................................................................................................................................. 353

Customer Support .............................................................................................................................................................................. 353

Product Identification System ............................................................................................................................................................ 355

2016-2019 Microchip Technology Inc. DS60001387D-page 11

Page 12

PIC32MM0256GPM064 FAMILY

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Website; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our website at www.microchip.com to receive the most current information on all of our products.

DS60001387D-page 12 2016-2019 Microchip Technology Inc.

Page 13

PIC32MM0256GPM064 FAMILY

Referenced Sources

This device data sheet is based on the following

individual sections of the “PIC32 Family Reference

Manual”. These documents should be considered as

the general reference for the operation of a particular

module or device feature.

Note: To access the documents listed below,

browse the documentation section of the

Microchip website (www.microchip.com).

• Section 1. “Introduction” (www.microchip.com/DS60001127)

• Section 5. “Flash Programming” (www.microchip.com/DS60001121)

• Section 7. “Resets” (www.microchip.com/DS60001118)

• Section 8. “Interrupts” (www.microchip.com/DS60001108)

• Section 10. “Power-Saving Modes” (www.microchip.com/DS60001130)

• Section 12. “I/O Ports” (www.microchip.com/DS60001120)

• Section 14. “Timers” (www.microchip.com/DS60001105)

• Section 19. “Comparator” (www.microchip.com/DS60001110)

• Section 20. “Comparator Voltage Reference” (www.microchip.com/DS61109)

• Section 21. “UART” (www.microchip.com/DS60001107)

• Section 23. “Serial Peripheral Interface (SPI)” (www.microchip.com/DS61106)

• Section 24. “Inter-Integrated Circuit™ (I

• Section 25. “12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect” (www.microchip.com/DS60001359)

• Section 27. “USB On-The-Go (OTG)” (www.microchip.com/DS61126)

• Section 28. “RTCC with Timestamp” (www.microchip.com/DS60001362)

• Section 30. “Capture/Compare/PWM/Timer (MCCP and SCCP)” (www.microchip.com/DS60001381)

• Section 31. “DMA Controller” (www.microchip.com/DS60001117)

• Section 33. “Programming and Diagnostics” (www.microchip.com/DS61129)

• Section 36. “Configurable Logic Cell” (www.microchip.com/DS60001363)

• Section 48. “Memory Organization and Permissions” (DS60001214)

• Section 50. “CPU for Devices with MIPS32

• Section 59. “Oscillators with DCO” (www.microchip.com/DS60001329)

• Section 62. “Dual Watchdog Timer” (www.microchip.com/DS60001365)

2

C™)” (www.microchip.com/DS60001116)

®

microAptiv™ and M-Class Cores” (www.microchip.com/DS60001192)

2016-2019 Microchip Technology Inc. DS60001387D-page 13

Page 14

PIC32MM0256GPM064 FAMILY

NOTES:

DS60001387D-page 14 2016-2019 Microchip Technology Inc.

Page 15

PIC32MM0256GPM064 FAMILY

UART1,2,3

Comparators

PORTA

PORTB

Priority

ISDS

EJTAGINT

Bus Matrix

RAM Peripheral Bridge

64

64-Bit Wide

Flash

32

32 32

Peripheral Bus Clocked by PBCLK

Program Flash Memory

Controller

32

32

32

Interrupt

Controller

PORTC

I2C1,2,3

SPI1,2,3

SCCP4-9

MCCP1,2,3

OSC1/CLKI

OSC2/CLKO

V

DD,

Timing

Generation

V

SS

MCLR

Power-up

Time r

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Time r

Brown-out

Reset

Precision

Reference

Band Gap

Regulator

Volt ag e

VCAP

Primary

Dividers

SYSCLK

PBCLK (1:1 with SYSCLK)

Peripheral Bus Clocked by PBCLK

PLL

RTCC

12-Bit ADC

Timer1,2,3

32

32

Oscillator

FRC/LPRC

Oscillators

SOSCO, SCLKI,

Secondary

Oscillator

AVDD, AVSS

I/O Change

Notification

HLVD

MIPS32® microAptiv™ UC

CPU Core

32

PORTD

DMA with

CRC

SOSCI

JTAG

BSCAN

32

Flash

Controller

32

USB

(write)

ICD

Flash Line

Buffer

1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features

of the PIC32MM0256GPM064 family of

devices. It is not intended to be a comprehensive reference source. To complement

the information in this data sheet, refer to

the PIC32 Family Reference Manuals,

This data sheet contains device-specific information for

the PIC32MM0256GPM064 family devices.

Figure 1-1 illustrates a general block diagram of the core

and peripheral modules in the PIC32MM0256GPM064

family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins

shown in the device pin tables.

which are available from the Microchip

website (www.microchip.com/PIC32). The

information in this data sheet supersedes

the information in the FRM.

FIGURE 1-1: PIC32MM0256GPM064 FAMILY BLOCK DIAGRAM

2016-2019 Microchip Technology Inc. DS60001387D-page 15

Page 16

PIC32MM0256GPM064 FAMILY

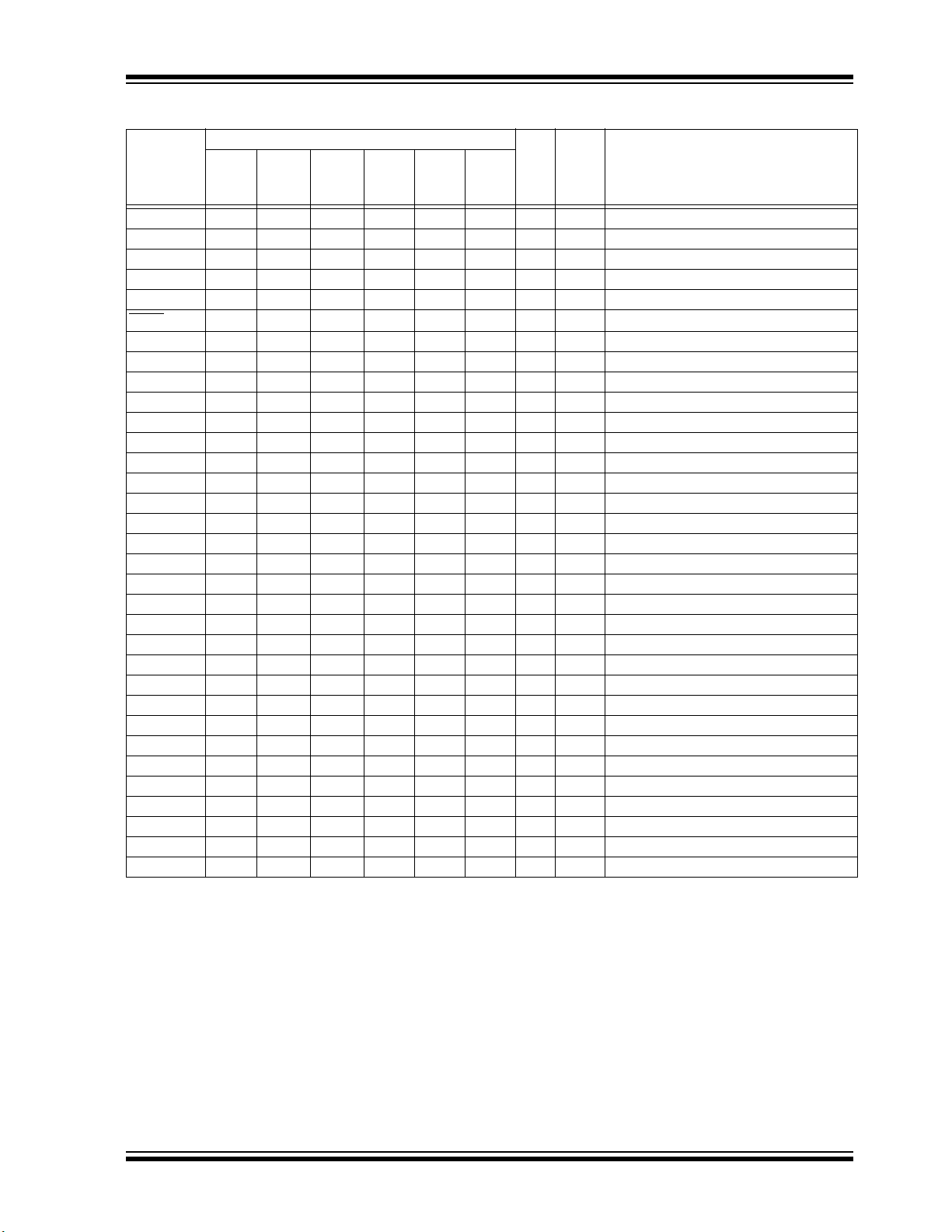

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION

Pin Number

Pin

Pin Name

AN0 2 27 33 36 21 11 I ANA Analog-to-Digital Converter input channels

AN1 3 28 34 37 22 12 I ANA

AN2 4 1 35 382313IANA

AN3 5 2 36 392414IANA

AN4 6 3 1 1 25 15 I ANA

AN5 9 6 7 7 32 25 I ANA

AN6 10 7 8 8 33 26 I ANA

AN7 11 8 9 9 35 28 I ANA

AN8 24 21 27301263IANA

AN9 25 22 28 31 15 2 I ANA

AN10 26 23 29 32 16 3 I ANA

AN11 7 4 2 2 26 16 I ANA

AN12 — — 3 3 27 19 I ANA

AN13 — — 4 4 28 20 I ANA

AN14 — — 20 21 4 52 I ANA

AN15 — — — — 41 37 I ANA

AN16 — — — — — 6 I ANA

AN17 — — — — — 7 I ANA

AN18 — — — — — 8 I ANA

AN19 — — — — 20 10 I ANA

DD 28 25 31 34 18 5 P — Analog modules power supply

AV

AV

SS 27 24 30 33 17 4 P — Analog modules ground

C1INA 7 4 2 2 26 16 I ANA Comparator 1 Input A

C1INB 6 3 1 1 25 15 I ANA Comparator 1 Input B

C1INC 5 2 36 39 24 14 I ANA Comparator 1 Input C

C1IND 4 1 35 38 23 13 I ANA Comparator 1 Input D

C2INA 5 2 36 39 24 14 I ANA Comparator 2 Input A

C2INB 4 1 35 38 23 13 I ANA Comparator 2 Input B

C2INC — — 20 21 4 52 I ANA Comparator 2 Input C

C2IND — — 3 3 27 19 I ANA Comparator 2 Input D

C3INA 26 23 29 32 16 3 I ANA Comparator 3 Input A

C3INB 25 22 28 31 15 2 I ANA Comparator 3 Input B

C3INC 4 1 35 38 23 13 I ANA Comparator 3 Input C

C3IND 10 7 8 8 33 26 I ANA Comparator 3 Input D

CLKI 9 6 7 7 32 25 I ST External Clock source input (EC mode)

CLKO 10 7 8 8 33 26 O DIG System clock output

REF 25 22 28 31 15 2 O ANA Comparator voltage reference output

CV

REF+ 2 27 33 36 21 11 I ANA Positive comparator voltage reference input

CV

D+ 22 19 25 28 10 61 I/O — USB transceiver differential plus line

D- 21 18 24 27 9 60 I/O — USB transceiver differential minus line

FSYNC1 26 23 29 32 16 32 I/O ST/DIG SPI1 frame signal input or output

FSYNC3 14 11 15 15 45 22 I/O ST/DIG SPI3 frame signal input or output

Legend: ST = Schmitt Trigger input buffer DIG = Digital input/output P = Power

28-Pin

SSOP

I2C = I

28-Pin

QFN/

UQFN

2

C/SMBus input buffer ANA = Analog level input/output

36-Pin

QFN

40-Pin

UQFN

48-Pin

QFN/

TQFP

64-Pin

QFN/

TQFP

Typ e

Buffer

Typ e

Description

DS60001387D-page 16 2016-2019 Microchip Technology Inc.

Page 17

PIC32MM0256GPM064 FAMILY

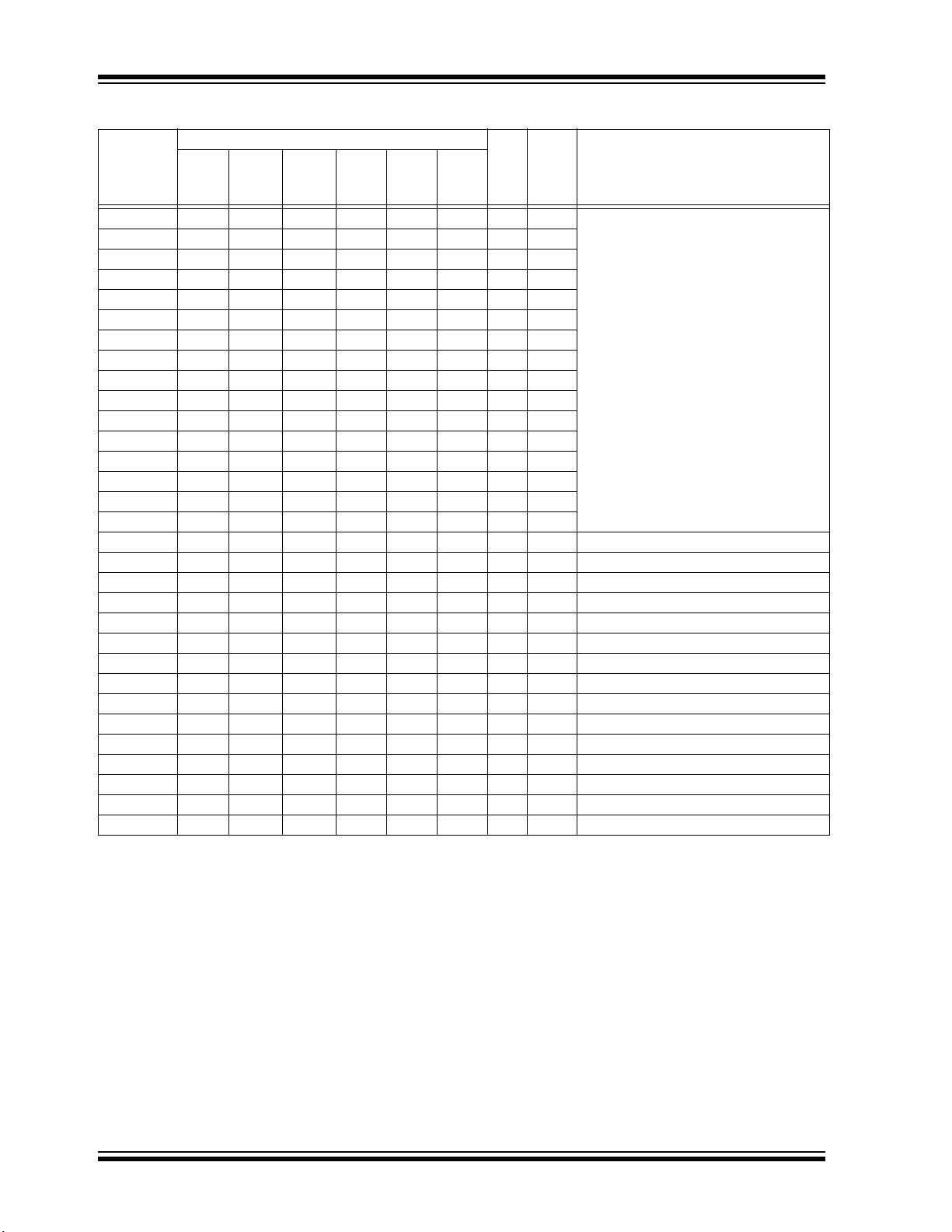

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

Pin Number

Pin

Pin Name

INT0 26 23 29 32 16 32 I ST External Interrupt 0

INT1 25 22 28 31 15 31 I ST External Interrupt 1

INT2 18 15 19 20 1 49 I ST External Interrupt 2

INT3 2 27 33 36 40 36 I ST External Interrupt 3

LVDIN 24 21 20 21 4 52 I ANA High/Low-Voltage Detect input

MCLR

OCM1A 17 14 18 18 48 7 O DIG MCCP1 Output A

OCM1B 18 15 19 20 1 53 O DIG MCCP1 Output B

OCM1C 9 6 7 7 32 25 O DIG MCCP1 Output C

OCM1D 10 7 8 8 41 37 O DIG MCCP1 Output D

OCM1E 2 27 33 36 40 36 O DIG MCCP1 Output E

OCM1F 3 28 34 37 22 12 O DIG MCCP1 Output F

OCM2A 19 16 5 5 29 21 O DIG MCCP2 Output A

OCM2B 26 23 29 32 39 35 O DIG MCCP2 Output B

OCM2C 4 1 35 38 23 13 O DIG MCCP2 Output C

OCM2D 5 2 36 39 24 14 O DIG MCCP2 Output D

OCM2E 6 3 1 1 25 15 O DIG MCCP2 Output E

OCM2F 7 4 2 2 26 16 O DIG MCCP2 Output F

OCM3A 24 21 11 11 37 54 O DIG MCCP3 Output A

OCM3B 25 22 28 31 15 33 O DIG MCCP3 Output B

OCM3C 11 8 9 9 35 59 O DIG MCCP3 Output C

OCM3D 12 9 10 10 36 41 O DIG MCCP3 Output D

OCM3E 14 11 15 15 45 42 O DIG MCCP3 Output E

OCM3F 16 13 17 17 47 45 O DIG MCCP3 Output F

OSC1 9 6 7 7 32 25 — — Primary Oscillator crystal

OSC2 10 7 8 8 33 26 — — Primary Oscillator crystal

PGEC1 5 2 36 39 24 14 I ST ICSP™ Port 1 programming clock input

PGEC2 2 27 33 36 21 11 I ST ICSP Port 2 programming clock input

PGEC3 19 16 21 22 5 55 I ST ICSP Port 3 programming clock input

PGED1 4 1 35 38 23 13 I/O ST/DIG ICSP Port 1 programming data

PGED2 3 28 34 37 22 12 I/O ST/DIG ICSP Port 2 programming data

PGED3 14 11 15 15 45 43 I/O ST/DIG ICSP Port 3 programming data

PWRLCLK 12 9 10 10 36 29 I ST Real-Time Clock 50/60 Hz clock input

Legend: ST = Schmitt Trigger input buffer DIG = Digital input/output P = Power

28-Pin

SSOP

I2C = I

28-Pin

QFN/

UQFN

1 26 32 35 19 9 I ST Master Clear (device Reset)

2

C/SMBus input buffer ANA = Analog level input/output

36-Pin

QFN

40-Pin

UQFN

48-Pin

QFN/

TQFP

64-Pin

QFN/

TQFP

Typ e

Buffer

Typ e

Description

2016-2019 Microchip Technology Inc. DS60001387D-page 17

Page 18

PIC32MM0256GPM064 FAMILY

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

Pin Number

Pin

Pin Name

RA0 2 27 33 36 21 11 I/O ST/DIG PORTA digital I/Os

RA1 3 28 34 37 22 12 I/O ST/DIG

RA2 9 6 7 7 32 25 I/O ST/DIG

RA3 10 7 8 8 33 26 I/O ST/DIG

RA4 12 9 10 10 36 29 I/O ST/DIG

RA5 — — — — — 54 I/O ST/DIG

RA6 — — — — 20 10 I/O ST/DIG

RA7 — — — — 14 1 I/O ST/DIG

RA8 — — — — 34 27 I/O ST/DIG

RA9 — — 11 11 37 30 I/O ST/DIG

RA10 — — — — 13 64 I/O ST/DIG

RA11 — — — — — 8 I/O ST/DIG

RA12 — — — — — 7 I/O ST/DIG

RA13 — — — — — 6 I/O ST/DIG

RA14 — — — — — 59 I/O ST/DIG

RA15 — — — — 8 58 I/O ST/DIG

RB0 4 1 35 38 23 13 I/O ST/DIG PORTB digital I/Os

RB1 5 2 36 392414I/OST/DIG

RB2 6 3 1 1 25 15 I/O ST/DIG

RB3 7 4 2 2 26 16 I/O ST/DIG

RB4 11 8 9 9 35 28 I/O ST/DIG

RB5 14 11 15154543I/OST/DIG

RB6 15 12 16164644I/OST/DIG

RB7 16 13 17174746I/OST/DIG

RB8 17 14 18184848I/OST/DIG

RB9 18 15 19 20 1 49 I/O ST/DIG

RB10 21 18 24 27 9 60 I/O ST/DIG

RB11 22 19 25 28 10 61 I/O ST/DIG

RB13 24 21 27 30 12 63 I/O ST/DIG

RB14 25 22 28 31 15 2 I/O ST/DIG

RB15 26 23 29 32 16 3 I/O ST/DIG

Legend: ST = Schmitt Trigger input buffer DIG = Digital input/output P = Power

28-Pin

SSOP

I2C = I

28-Pin

QFN/

UQFN

2

C/SMBus input buffer ANA = Analog level input/output

36-Pin

QFN

40-Pin

UQFN

48-Pin

QFN/

TQFP

64-Pin

QFN/

TQFP

Typ e

Buffer

Typ e

Description

DS60001387D-page 18 2016-2019 Microchip Technology Inc.

Page 19

PIC32MM0256GPM064 FAMILY

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

Pin Number

Pin

Pin Name

RC0 — — 3 3 27 19 I/O ST/DIG PORTC digital I/Os

RC1 — — 4 4 28 20 I/O ST/DIG

RC2 — — 5 5 29 21 I/O ST/DIG

RC3 — — 14 143935I/OST/DIG

RC4 — — — — 40 36 I/O ST/DIG

RC5 — — — — 41 37 I/O ST/DIG

RC6 — — — — 2 50 I/O ST/DIG

RC7 — — — — 3 51 I/O ST/DIG

RC8 — — 20 21 4 52 I/O ST/DIG

RC9 19 16 21 22 5 55 I/O ST/DIG

RC10 — — — — — 45 I/O ST/DIG

RC11 — — — — — 22 I/O ST/DIG

RC12 — — — — 44 40 I/O ST/DIG

RC13 — — — — — 47 I/O ST/DIG

RC14 — — — — — 41 I/O ST/DIG

RC15 — — — — — 42 I/O ST/DIG

RD0 — — — — 38 34 I/O ST/DIG PORTD digital I/Os

RD1 — — — — — 53 I/O ST/DIG

RD2 — — — — — 32 I/O ST/DIG

RD3 — — — — — 33 I/O ST/DIG

RD4 — — — — — 31 I/O ST/DIG

REFCLKI 18 15 19 20 38 34 I ST External reference clock input

REFCLKO 26 23 29 32 16 3 O ST External reference clock output

RP1 2 27 33 36 21 11 I/O ST/DIG Remappable peripherals (input or output)

RP2 3 28 34 37 22 12 I/O ST/DIG

RP3 9 6 7 7 32 25 I/O ST/DIG

RP4 10 7 8 8 33 26 I/O ST/DIG

RP5 12 9 10 10 36 29 I/O ST/DIG

RP6 4 1 35 382313I/OST/DIG

RP7 5 2 36 392414I/OST/DIG

RP8 6 3 1 1 25 15 I/O ST/DIG

RP9 7 4 2 2 26 16 I/O ST/DIG

RP10 11 8 9 9 35 28 I/O ST/DIG

RP11 14 11 15 15 45 43 I/O ST/DIG

RP12 16 13 17 17 47 46 I/O ST/DIG

RP13 17 14 18 18 48 48 I/O ST/DIG

RP14 18 15 19 20 1 49 I/O ST/DIG

RP15 24 21 27 30 12 63 I/O ST/DIG

RP16 25 22 28 31 15 2 I/O ST/DIG

RP17 26 23 29 32 16 3 I/O ST/DIG

RP18 19 16 21 22 5 55 I/O ST/DIG

RP19 — — 5 5 29 21 I/O ST/DIG

RP20 — — — — 3 51 I/O ST/DIG

Legend: ST = Schmitt Trigger input buffer DIG = Digital input/output P = Power

28-Pin

SSOP

I2C = I

28-Pin

QFN/

UQFN

2

C/SMBus input buffer ANA = Analog level input/output

36-Pin

QFN

40-Pin

UQFN

48-Pin

QFN/

TQFP

64-Pin

QFN/

TQFP

Typ e

Buffer

Typ e

Description

2016-2019 Microchip Technology Inc. DS60001387D-page 19

Page 20

PIC32MM0256GPM064 FAMILY

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

Pin Number

Pin

Pin Name

RP21 — — — — 14 1 I/O ST/DIG Remappable peripherals (input or output)

RP22 — — — — 13 64 I/O ST/DIG

RP23 — — — — 2 50 I/O ST/DIG

RP2 4 — — 11 11 37 30 I /O S T/DIG

RTCC 25 22 28 31 8 58 O DIG Real-Time Clock/Calendar alarm/seconds

SCK1 17 14 18 18 48 47 I/O ST/DIG SPI1 clock (input or output)

SCK3 24 21 27 30 13 64 I/O ST/DIG SPI3 clock (input or output)

SCL1 17 14 18 18 48 48 I/O I2C I2C1 synchronous serial clock input/output

ASCL1 19 16 21 22 5 55 I/O I2C Alternate I2C1 synchronous serial clock input/

SCL2 7 4 2 2 26 16 I/O I2C I2C2 synchronous serial clock input/output

SCL3 24 21 27 30 12 63 I/O I2C I2C3 synchronous serial clock input/output

SCLKI 12 9 10 10 36 29 I ST Secondary Oscillator digital clock input

SDA1 18 15 19 20 1 49 I/O I2C I2C1 data input/output

ASDA1 14 11 15 15 45 43 I/O I2C Alternate I2C1 data input/output

SDA2 6 3 1 1 25 15 I/O I2C I2C2 data input/output

SDA3 16 13 17 17 47 46 I/O I2C I2C3 data input/output

SDI1 25 22 28 31 15 31 I ST SPI1 data input

SDI3 16 13 17 17 14 1 I ST SPI3 data input

SDO1 18 15 19 20 38 34 O DIG SPI1 data output

SDO3 19 16 21 22 34 27 O DIG SPI3 data output

SOSCI 11 8 9 9 35 28 — — Secondary Oscillator crystal

SOSCO 12 9 10 10 36 29 — — Secondary Oscillator crystal

SS1

SS3

T1CK 18 15 19 20 38 34 I ST Timer1 external clock input

T2CK 18 15 3 3 27 19 I ST Timer2 external clock input

T3CK 19 16 4 4 28 20 I ST Timer3 external clock input

T1G 18 15 19 20 38 34 I ST Timer1 clock gate input

T2G 18 15 3 3 27 19 I ST Timer2 clock gate input

T3G 19 16 4 4 28 20 I ST Timer3 clock gate input

TCK 17 14 18 18 48 48 I ST JTAG clock input

TDI 7 4 2 2 26 16 I ST JTAG data input

TDO 19 16 21 22 5 55 O DIG JTAG data output

TMS 18 15 19 20 1 49 I ST JTAG mode select input

Legend: ST = Schmitt Trigger input buffer DIG = Digital input/output P = Power

28-Pin

SSOP

I2C = I

28-Pin

QFN/

UQFN

26 23 29 32 16 32 I ST SPI1 slave select input

14 11 15 15 45 22 I ST SPI3 slave select input

2

C/SMBus input buffer ANA = Analog level input/output

36-Pin

QFN

40-Pin

UQFN

48-Pin

QFN/

TQFP

64-Pin

QFN/

TQFP

Typ e

Buffer

Typ e

Description

output

output

DS60001387D-page 20 2016-2019 Microchip Technology Inc.

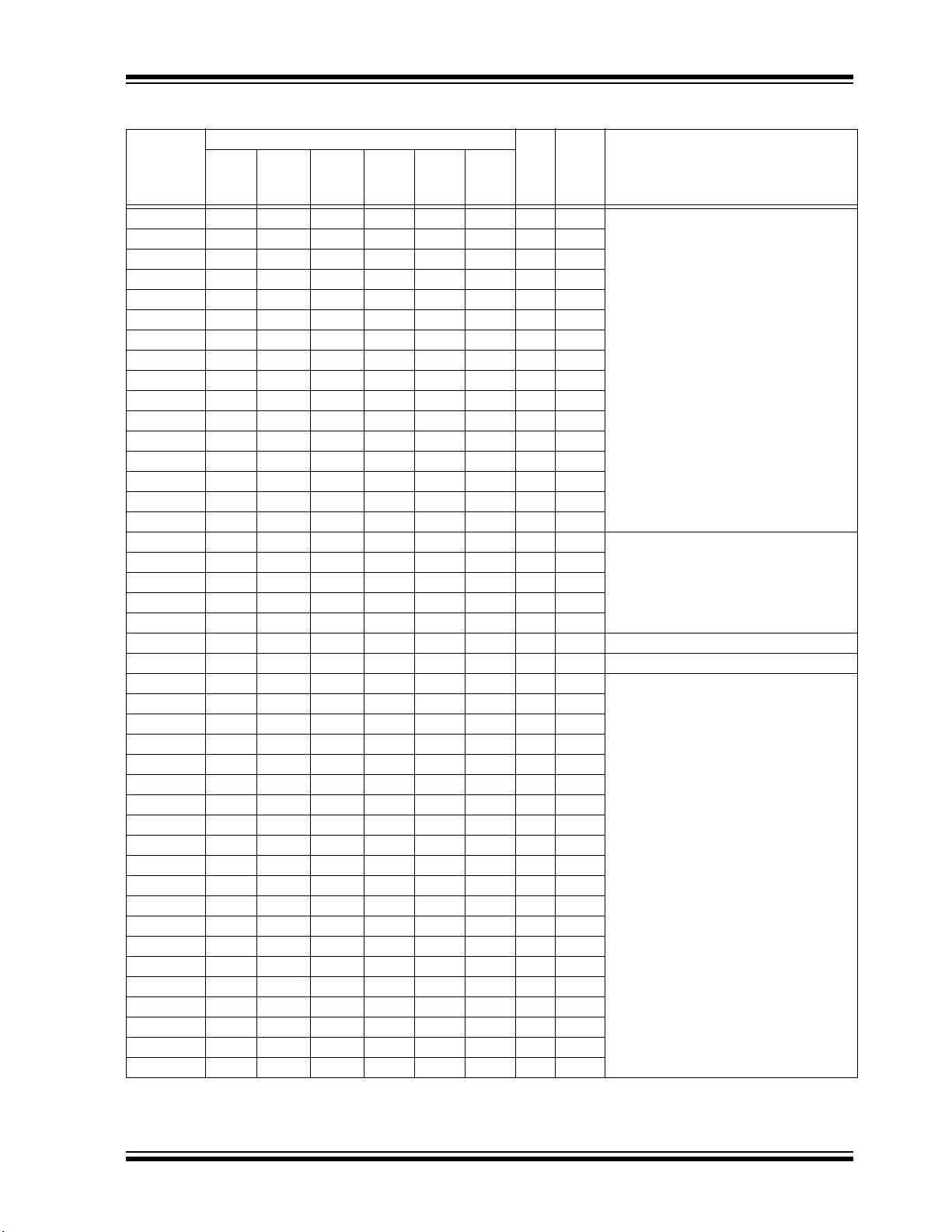

Page 21

PIC32MM0256GPM064 FAMILY

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

Pin Number

Pin

Pin Name

U1BCLK 18 15 19 20 38 34 O DIG UART1 IrDA® 16x baud clock output

U1CTS

U1RTS

U1RX 26 23 29 32 20 10 I ST UART1 receive data input

U1TX 25 22 28 31 44 40 O DIG UART1 transmit data output

USBID 14 11 15 15 45 43 I ST USB OTG ID (OTG mode only)

USBOEN 19 16 21 22 5 55 O — USB transceiver output enable flag

VBUSON 25 22 28 31 15 2 O — USB host and On-The-Go (OTG) bus power

BUS 15 12 16 16 46 44 P — USB VBUS connection (5V nominal)

V

V

USB3V3 23 20 26 29 11 62 P — USB transceiver power input (3.3V nominal)

CAP 20 17 22 24 7 56 P — Core voltage regulator filter capacitor

V

DD 13,28 10,25 13,23,31 13,26,

V

V

REF- 3 28 34 37 22 12 I ANA Analog-to-Digital Converter negative

REF+ 2 27 33 36 21 11 I ANA Analog-to-Digital Converter positive

V

SS 8,27 5,24 6,12,30 6,12,33 6,17,31,

V

Legend: ST = Schmitt Trigger input buffer DIG = Digital input/output P = Power

28-Pin

SSOP

I2C = I

28-Pin

QFN/

UQFN

17 14 18 18 48 6 I ST UART1 Clear-to-Send

18 15 19 20 38 34 O DIG UART1 Ready-to-Send

2

C/SMBus input buffer ANA = Analog level input/output

36-Pin

QFN

40-Pin

UQFN

34

48-Pin

TQFP

18,30,4317,23,

QFN/

42

64-Pin

QFN/

TQFP

39,57

18,24,38P — Digital modules ground

Buffer

Typ e

Typ e

control output; only available in external USB

Transceiver mode

connection

P — Digital modules power supply

reference

reference

Description

2016-2019 Microchip Technology Inc. DS60001387D-page 21

Page 22

PIC32MM0256GPM064 FAMILY

NOTES:

DS60001387D-page 22 2016-2019 Microchip Technology Inc.

Page 23

PIC32MM0256GPM064 FAMILY

2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features

of the PIC32MM0256GPM064 family of

devices. It is not intended to be a comprehensive reference source. To complement

the information in this data sheet, refer to the

“PIC32 Family Reference Manual”, which is

available from the Microchip website

www.microchip.com/PIC32). The infor-

(

mation in this data sheet supersedes the

information in the FRM.

2.1 Basic Connection Requirements

Getting started with the PIC32MM0256GPM064 family

of 32-bit Microcontrollers (MCUs) requires attention to

a minimal set of device pin connections before pro

ceeding with development. The following is a list of pin

names, which must always be connected:

•All VDD and VSS pins

(see Section 2.2 “Decoupling Capacitors”)

•All AVDD and AVSS pins, even if the ADC module

is not used (see

Capacitors”)

• MCLR pin (see Section 2.3 “Master Clear

(MCLR) Pin”)

•VCAP pin (see Section 2.4 “Voltage Regulator

Pin (VCAP)”)

• PGECx/PGEDx pins, used for In-Circuit Serial

Programming™ (ICSP™) and debugging

purposes (see Section 2.5 “ICSP Pins”)

• OSC1 and OSC2 pins, when external oscillator

source is used (see

Oscillator Pins”)

•VUSB3V3 pin, this pin must be powered for USB

operation (see Section 18.4 “Powering the USB

Transceiver”)

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage

reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be

Section 2.2 “Decoupling

Section 2.7 “External

.

connected, regardless of ADC use and

the ADC voltage reference source.

2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply

pins, such as V

Figure 2-1.

See

Consider the following criteria when using decoupling

capacitors:

• Value and type of capacitor: A value of 0.1 µF

(100 nF), 10-20V is recommended. The capacitor

should be a low Equivalent Series Resistance

(low-ESR) capacitor and have resonance frequency

in the range of 20

recommended that ceramic capacitors be used.

• Placement on the printed circuit board: The

decoupling capacitors should be placed as close to

the pins as possible. It is recommended that the

capacitors be placed on the same side of the board

as the device. If space is constricted, the capacitor

-

can be placed on another layer on the PCB using a

via; however, ensure that the trace length from the

pin to the capacitor is within one-quarter inch

mm) in length.

(6

• Handling high-frequency noise: If the board is

experiencing high-frequency noise, upward of tens

of MHz, add a second ceramic-type capacitor in

parallel to the above described decoupling capaci

tor. The value of the second capacitor can be in the

range of 0.01

capacitor next to the primary decoupling capacitor.

In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the

power and ground pins as possible. For example,

0.1 µF in parallel with 0.001 µF.

• Maximizing performance: On the board layout

from the power supply circuit, run the power and

return traces to the decoupling capacitors first, and

then to the device pins. This ensures that the

decoupling capacitors are first in the power chain.

Equally important is to keep the trace length

between the capacitor and the power pins to a

minimum, thereby reducing PCB track inductance.

DD, VSS, AVDD and AVSS, is required.

MHz and higher. It is further

-

µF to 0.001 µF. Place this second

2016-2019 Microchip Technology Inc. DS60001387D-page 23

Page 24

PIC32MM0256GPM064 FAMILY

PIC32

VDD

VSS

VDD

VSS

VSS

VDD

AVDD

AVSS

VDD

VSS

0.1 µF

Ceramic

0.1 µF

Ceramic

0.1 µF

Ceramic

0.1 µF

Ceramic

C

R

V

DD

MCLR

0.1 µF

Ceramic

R1

CEFC

10 µF

VCAP/VCORE

Note 1: Refer to Section 18.4 “Powering the USB

Transceiver” for requirements of this pin.

V

USB3V3

USB

Power

(1)

Note 1: 470 R1 1 k will limit any current flowing into

MCLR

from the external capacitor, C, in the event of

MCLR

pin breakdown, due to Electrostatic Discharge

(ESD) or Electrical Overstress (EOS). Ensure that the

MCLR

pin VIH and VIL specifications are met without

interfering with the debugger/programmer tools.

2: The capacitor can be sized to prevent unintentional

Resets from brief glitches or to extend the device

Reset period during POR.

3: No pull-ups or bypass capacitors are allowed on active

debug/program PGECx/PGEDx pins.

R1

(1)

10k

V

DD

MCLR

PIC32

1 k

0.1 µF

(2)

PGECx

(3)

PGEDx

(3)

ICSP™

1

5

4

2

3

6

V

DD

VSS

NC

R

C

FIGURE 2-1: RECOMMENDED

MINIMUM CONNECTION

2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve

power supply stability. Typical values range from 4.7 µF

to 47 µF. This capacitor should be located as close to

the device as possible.

For example, as illustrated in Figure 2-2, it is

recommended that the capacitor, C, be isolated from

the

MCLR pin during programming and debugging

operations.

Place the components illustrated in Figure 2-2 within

one-quarter inch (6 mm) from the MCLR pin.

FIGURE 2-2: EXAMPLE OF MCLR PIN

CONNECTIONS

(1,2,3)

2.3 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device

functions:

•Device Reset

• Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset.

Figure 2-2 illustrates a typical MCLR circuit. During

device programming and debugging, the resistance

and capacitance that can be added to the pin must

be considered. Device programmers and debuggers

drive the

levels (V

not be adversely affected. Therefore, specific values

of R and C will need to be adjusted based on the

application and PCB requirements.

Note: When MCLR is used to wake the device

DS60001387D-page 24 2016-2019 Microchip Technology Inc.

MCLR pin. Consequently, specific voltage

IH and VIL) and fast signal transitions must

from Retention Sleep, a POR Reset will

occur.

Page 25

PIC32MM0256GPM064 FAMILY

10

1

0.1

0.01

0.001

0.01 0.1 1 10 100 1000 10,000

Frequency (MHz)

ESR ()

Note: Typical data measurement at +25°C, 0V DC bias.

2.4 Voltage Regulator Pin (VCAP)

A low-ESR (< 5Ω) capacitor is required on the VCAP pin

to stabilize the output voltage of the on-chip voltage

regulator. The V

CAP pin must not be connected to VDD

FIGURE 2-3: FREQUENCY vs. ESR

PERFORMANCE FOR

SUGGESTED V

CAP

and must use a capacitor of 10 µF connected to ground.

The type can be ceramic or tantalum. Suitable examples

of capacitors are shown in

Table 2-1. Capacitors with

equivalent specification can be used.

The placement of this capacitor should be close to VCAP.

It is recommended that the trace length not exceed

inch (6 mm). Refer to Section 29.0 “Electrical

0.25

Characteristics” for additional information.

Designers may use Figure 2-3 to evaluate ESR

equivalence of candidate devices.

.

TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

Make Part #

TDK C3216X7R1C106K 10 µF ±10% 16V -55 to +125ºC

TDK C3216X5R1C106K 10 µF ±10% 16V -55 to +85ºC

Panasonic ECJ-3YX1C106K 10 µF ±10% 16V -55 to +125ºC

Panasonic ECJ-4YB1C106K 10 µF ±10% 16V -55 to +85ºC

Murata GRM319R61C106KE15D 10 µF ±10% 16V -55 to +85ºC

Nominal

Capacitance

Base Tolerance Rated Voltage Temp. Rang e

2016-2019 Microchip Technology Inc. DS60001387D-page 25

Page 26

PIC32MM0256GPM064 FAMILY

-80

-70

-60

-50

-40

-30

-20

-10

0

10

5 1011121314151617

DC Bias Voltage (VDC)

Capacitance Change (%)

01234 67 89

6.3V Capacitor

10V Capacitor

16V Capacitor

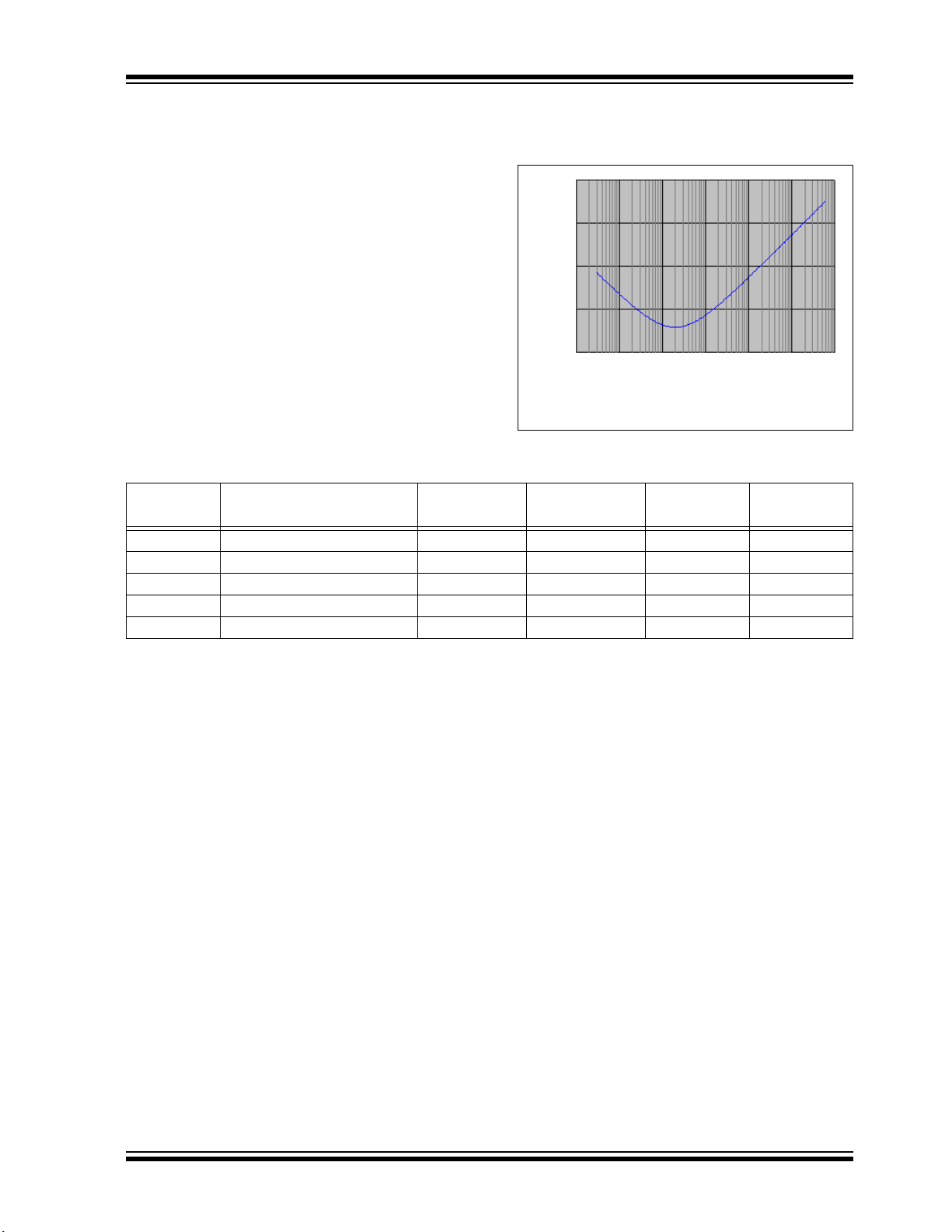

2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount

ceramic capacitors have become very cost effective in

sizes up to a few tens of microfarad. The low-ESR, small

physical size and other properties make ceramic

capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However,

some care is needed in selecting the capacitor to

ensure that it maintains sufficient capacitance over the

intended operating range of the application.

Typical low-cost, 10 µF ceramic capacitors are available

in X5R, X7R and Y5V dielectric ratings (other types are

also available, but are less common). The initial

tolerance specifications for these types of capacitors

are often specified as ±10% to ±20% (X5R and X7R)

or -20%/+80% (Y5V). However, the effective capaci

tance that these capacitors provide in an application

circuit will also vary based on additional factors, such as

the applied DC bias voltage and the temperature. The

total in-circuit tolerance is, therefore, much wider than

the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex: ±15% over a wide

temperature range, but consult the manufacturer’s data

sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance

specifications of +22%/-82%. Due to the extreme

temperature tolerance, a 10 µF nominal rated Y5V type

capacitor may not deliver enough total capacitance to

meet minimum internal voltage regulator stability and

transient response requirements. Therefore, Y5V

capacitors are not recommended for use with the

internal regulator.

In addition to temperature tolerance, the effective

capacitance of large value ceramic capacitors can vary

substantially, based on the amount of DC voltage applied

to the capacitor. This effect can be very significant, but is

often overlooked or is not always documented.

Typical DC bias voltage vs. capacitance graph for X7R

type capacitors is shown in

Figure 2-4.

-

When selecting a ceramic capacitor to be used with the

internal voltage regulator, it is suggested to select a

high-voltage rating, so that the operating voltage is a

small percentage of the maximum rated capacitor

voltage. The minimum DC rating for the ceramic

capacitor on V

shown in

CAP is 16V. Suggested capacitors are

Table 2-1.

2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit

Serial Programming™ (ICSP™) and debugging pur

poses. It is recommended to keep the trace length

between the ICSP connector and the ICSP pins on

the device as short as possible. If the ICSP connec

tor is expected to experience an ESD event, a series

resistor is recommended, with the value in the range

of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the

PGECx and PGEDx pins are not recommended as they

will interfere with the programmer/debugger communications to the device. If such discrete components are

an application requirement, they should be removed

from the circuit during programming and debugging.

Alternatively, refer to the AC/DC characteristics and

timing requirements information in the respective

device Flash programming specification for information

on capacitive loading limits and pin Input Voltage High

IH) and Input Voltage Low (VIL) requirements.

(V

Ensure that the “Communication Channel Select”

(i.e., PGECx/PGEDx pins) programmed into the device

matches the physical connections for the ICSP to

MPLAB

®

ICD 3 or MPLAB REAL ICE™ In-Circuit

Emulator.

For more information on MPLAB® ICD 3 and REAL ICE

connection requirements, refer to the following

documents that are available from the Microchip website.

• “Using MPLAB® ICD 3” (poster) (DS51765)

• “Development Tools Design Advisory” (DS51764)

• “MPLAB® REAL ICE™ In-Circuit Emulator User’s

Guide” (DS51616)

• “Using MPLAB® REAL ICE™ In-Circuit Emulator”

(poster) (DS51749)

-

-

FIGURE 2-4: DC BIAS VOLTAGE vs.

DS60001387D-page 26 2016-2019 Microchip Technology Inc.

CAPACITANCE

CHARACTERISTICS

Page 27

PIC32MM0256GPM064 FAMILY

Main Oscillator

Guard Ring

Guard Trace

Secondary

Oscillator

2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing

and debugging according to the Joint Test Action Group

(JTAG) standard. It is recommended to keep the trace

length between the JTAG connector, and the JTAG pins

on the device, as short as possible. If the JTAG connector

is expected to experience an ESD event, a series resistor

is recommended, with the value in the range of a few tens

of Ohms, not to exceed 100

Pull-up resistors, series diodes and capacitors on the

TMS, TDO, TDI and TCK pins are not recommended as

they will interfere with the programmer/debugger communications to the device. If such discrete components

are an application requirement, they should be removed

from the circuit during programming and debugging.

Alternatively, refer to the AC/DC characteristics and

timing requirements information in the respective device

Flash programming specification for information on

capacitive loading limits, and pin Input Voltage High (V

and Input Voltage Low (V

Note 1: The TMS pin function may be active

multiple times during ICSP device Erase,

Programming and Debugging. When the

TMS function is active, the integrated

pull-up resistor, ~6k, will pull the pin to

DD. When the TMS function is inactive,

V

the pin will be tri-state. The TMS function

being enabled and disabled repeatedly

results in the pin “toggling.”

• Do not connect circuity to the TMS

pin that could be adversely affected

by the toggling.

• If circuity connected to the TMS pin

is sensitive to the “toggling” do not

program the device in circuit.

• Use a strong pull-down resistor

such as 1k between the TMS pin to

ground to overpower the pull-up.

Ohms.

IH)

IL) requirements.

2.7 External Oscillator Pins

This family of devices has options for two external

oscillators: a high-frequency Primary Oscillator and a

low-frequency Secondary Oscillator (refer to

Section 9.0 “Oscillator Configuration” for details).

The oscillator circuit should be placed on the same side

of the board as the device. Also, place the oscillator

circuit close to the respective oscillator pins, not

exceeding one-half inch (12 mm) distance between

them. The load capacitors should be placed next to the

oscillator itself, on the same side of the board. Use a

grounded copper pour around the oscillator circuit to

isolate them from surrounding circuits. The grounded

copper pour should be routed directly to the MCU

ground. Do not run any signal traces or power traces

inside the ground pour. Also, if using a two-sided board,

avoid any traces on the other side of the board where

the crystal is placed. A suggested layout is illustrated in

Figure 2-5.

For additional information and design guidance on

oscillator circuits, please refer to these Microchip

Application Notes, available at the corporate website:

(www.microchip.com).

•AN826, “Crystal Oscillator Basics and Crystal

Selection for rfPIC™ and PICmicro

•AN849, “Basic PICmicro® Oscillator Design”

•AN943, “Practical PICmicro® Oscillator Analysis

and Design”

•AN949, “Making Your Oscillator Work”

®

Devices”

FIGURE 2-5: SUGGESTED OSCILLATOR

CIRCUIT PLACEMENT

2.8 Unused I/Os

To minimize power consumption, unused I/O pins

should not be allowed to float as inputs. They can be

configured as outputs and driven to a logic low or logic

high state.

Alternatively, inputs can be reserved by ensuring the

pin is always configured as an input and externally con

necting the pin to VSS or VDD. A current-limiting resistor

may be used to create this connection if there is any

risk of inadvertently configuring the pin as an output

with the logic output state opposite of the chosen power

rail.

-

2016-2019 Microchip Technology Inc. DS60001387D-page 27

Page 28

PIC32MM0256GPM064 FAMILY

NOTES:

DS60001387D-page 28 2016-2019 Microchip Technology Inc.

Page 29

PIC32MM0256GPM064 FAMILY

3.0 CPU

Note: This data sheet summarizes the features

of the PIC32MM0256GPM064 family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to Section 50. “CPU for

Devices with MIPS32

M-Class Cores” (www.microchip.com/

DS60001192) in the “PIC32 Family Refer

ence Manual”. MIPS32® microAptiv™ UC

microprocessor core resources are available at: www.imgtec.com. The information

in this data sheet supersedes the

information in the FRM.

The MIPS32® microAptiv™ UC microprocessor core is

the heart of the PIC32MM0256GPM064 family

devices. The CPU fetches instructions, decodes each

instruction, fetches source operands, executes each

instruction and writes the results of the instruction

execution to the proper destinations.

3.1 Features

The PIC32MM0256GPM064 family processor core key

features include:

• Five-Stage Pipeline

• 32-Bit Address and Data Paths

• MIPS32 Enhanced Architecture:

- Multiply-add and multiply-subtract instructions.

- Targeted multiply instruction.

- Zero and one detect instructions.

- WAIT instruction.

- Conditional move instructions.

- Vectored interrupts.

- Atomic interrupt enable/disable.

- One GPR shadow set to minimize latency of

interrupts.

- Bit field manipulation instructions.

• microMIPS™ Instruction Set:

- microMIPS allows improving the code size

density over MIPS32, while maintaining

MIPS32 performance.

- microMIPS supports all MIPS32 instructions

(except for branch-likely instructions) with

new optimized 32-bit encoding. Frequent

MIPS32 instructions are available as 16-bit

instructions.

- Added seventeen new and thirty-five

MIPS32

instructions in 16-bit opcode format.

- Stack Pointer implicit in instruction.

- MIPS32 assembly and ABI compatible.

®

corresponding, commonly used

®

microAptiv™ and

-

• Memory Management Unit with Simple Fixed

Mapping Translation (FMT) Mechanism

• Multiply/Divide Unit (MDU):

- Configurable using high-performance

multiplier array.

- Maximum issue rate of one 32x16 multiply

per clock.

- Maximum issue rate of one 32x32 multiply

every other clock.

- Early-in iterative divide. Minimum 11 and

maximum 33 clock latency (dividend (rs) sign

extension dependent).

• Power Control:

- No minimum frequency: 0 MHz.

- Power-Down mode (triggered by WAIT

instruction).

• EJTAG Debug/Profiling:

- CPU control with start, stop and single

stepping.

- Software breakpoints via the SDBBP

instruction.

- Simple hardware breakpoints on virtual

addresses, four instructions and

two data breakpoints.

- PC and/or load/store address sampling for

profiling.

- Performance counters.

- Supports Fast Debug Channel (FDC).

A block diagram of the PIC32MM0256GPM064 family

processor core is shown in

Figure 3-1.

2016-2019 Microchip Technology Inc. DS60001387D-page 29

Page 30

PIC32MM0256GPM064 FAMILY

System Bus

Execution Unit

ALU/Shift

Atomic/LdSt

MCU ASE

System

Coprocessor

Enhanced MDU

GPR

(two sets)

Debug/Profiling

Breakpoints

Fast Debug Channel

Performance Counters

Power

System

Interface

Interrupt

Interface

MMU

Decode

(microMIPS™)

EJTAG

2-Wire Debug

Management

SYSCLK

MIPS32® microAptiv™ UC Microprocessor Core

FIGURE 3-1: PIC32MM0256GPM064 FAMILY MICROPROCESSOR CORE BLOCK DIAGRAM

DS60001387D-page 30 2016-2019 Microchip Technology Inc.

Page 31

PIC32MM0256GPM064 FAMILY

3.2 Architecture Overview

The MIPS32® microAptiv™ UC microprocessor core in

the PIC32MM0256GPM064 family devices contains

several logic blocks, working together in parallel, pro

viding an efficient high-performance computing engine.

The following blocks are included with the core:

• Execution Unit

• General Purpose Register (GPR)

• Multiply/Divide Unit (MDU)

• System Control Coprocessor (CP0)

• Memory Management Unit (MMU)

• Power Management

• microMIPS Instructions Decoder

• Enhanced JTAG (EJTAG) Controller

3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/

store architecture with single-cycle ALU operations

(logical, shift, add, subtract) and an autonomous Multiply/

Divide Unit (MDU). The core contains thirty-two 32-bit

General Purpose Registers (GPRs) used for integer

operations and address calculation. One additional

register file shadow set (containing thirty-two registers) is

added to minimize context switching overhead during

interrupt/exception processing. The register file consists

of two read ports and one write port, and is fully bypassed

to minimize operation latency in the pipeline.

The execution unit includes:

• 32-bit adder used for calculating the data address

• Address unit for calculating the next instruction address

• Logic for branch determination and branch target

address calculation

• Load aligner

• Bypass multiplexers used to avoid Stalls when

executing instruction streams where data producing instructions are followed closely by consumers

for their results

• Leading zero/one detect unit for implementing the

CLZ and CLO instructions

• Arithmetic Logic Unit (ALU) for performing

arithmetic and bitwise logical operations

• Shifter and store aligner

-

3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The microAptiv UC core includes a Multiply/Divide Unit

(MDU) that contains a separate pipeline for multiply

and divide operations. This pipeline operates in parallel

with the Integer Unit (IU) pipeline and does not stall

when the IU pipeline stalls. This allows the longrunning MDU operations to be partially masked by

system Stalls and/or other Integer Unit instructions.

The high-performance MDU consists of a 32x16 booth

recoded multiplier, Result/Accumulation registers (HI

and LO), a divide state machine, and the necessary

multiplexers and control logic. The first number shown