Datasheet CY7C4808V25-200, CY7C4808V25-166, CY7C4806V25-200, CY7C4806V25-166, CY7C4804V25-200 Datasheet (Cypress Semiconductor)

...Page 1

PRELIMINARY

2.5V 4K/16K/64K x 80 Unidirectional

Synchronous FIFO w/Bus Matching

CY7C4808V25

CY7C4806V25

CY7C4804V25

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

July 18, 2000

sure

0251

Features

• High-speed, lo w-po wer, unidir ectional, fir st-i n fi rst- out

(FIFO) memories w/bus matching capabilities

• 64K x 80 (CY7C4808V25)

• 16K x 80 (CY7C4806V25)

• 4K x 80 (CY7C4804V25)

• 2.5V ± 100 mV power suppl y

• All I/Os are 1. 5 V HST L

• Individual clock frequency up to 200 MHz (5 ns

read/write cycle times)

• High-speed access with t

A

= 3.3 ns

• Bus matching on both ports: x80, x40, x20, x10

• Free-running CLKA and CLKB. Clocks may be asynchronous or coinci dent

• CY standard or First-W ord Fall-Through m odes

• Serial and parallel progr am ming of Almost Empty/Ful l

flags, each with 3 defaul t values (8, 16, 64)

• Master and Partial reset capability

• Retransmi t capability

• Big or Little Endian format on Port B

• 288 FBGA 19 mm x 19 mm (1.0-mm ball pit ch) packaging

• Width and depth expansion capability

• Fabricated using Cypress 0.21-micron CMOS Technology for optimum speed/power

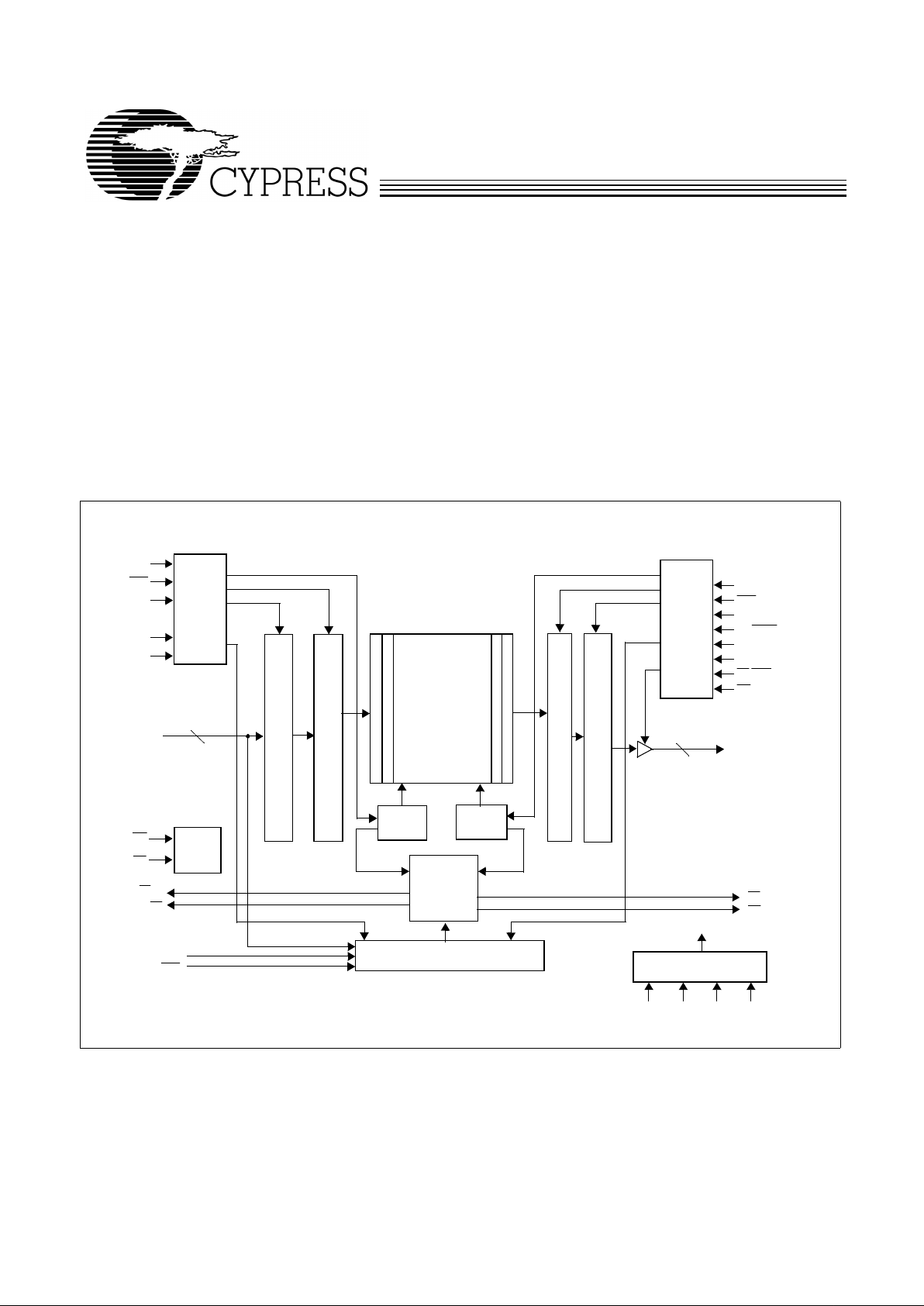

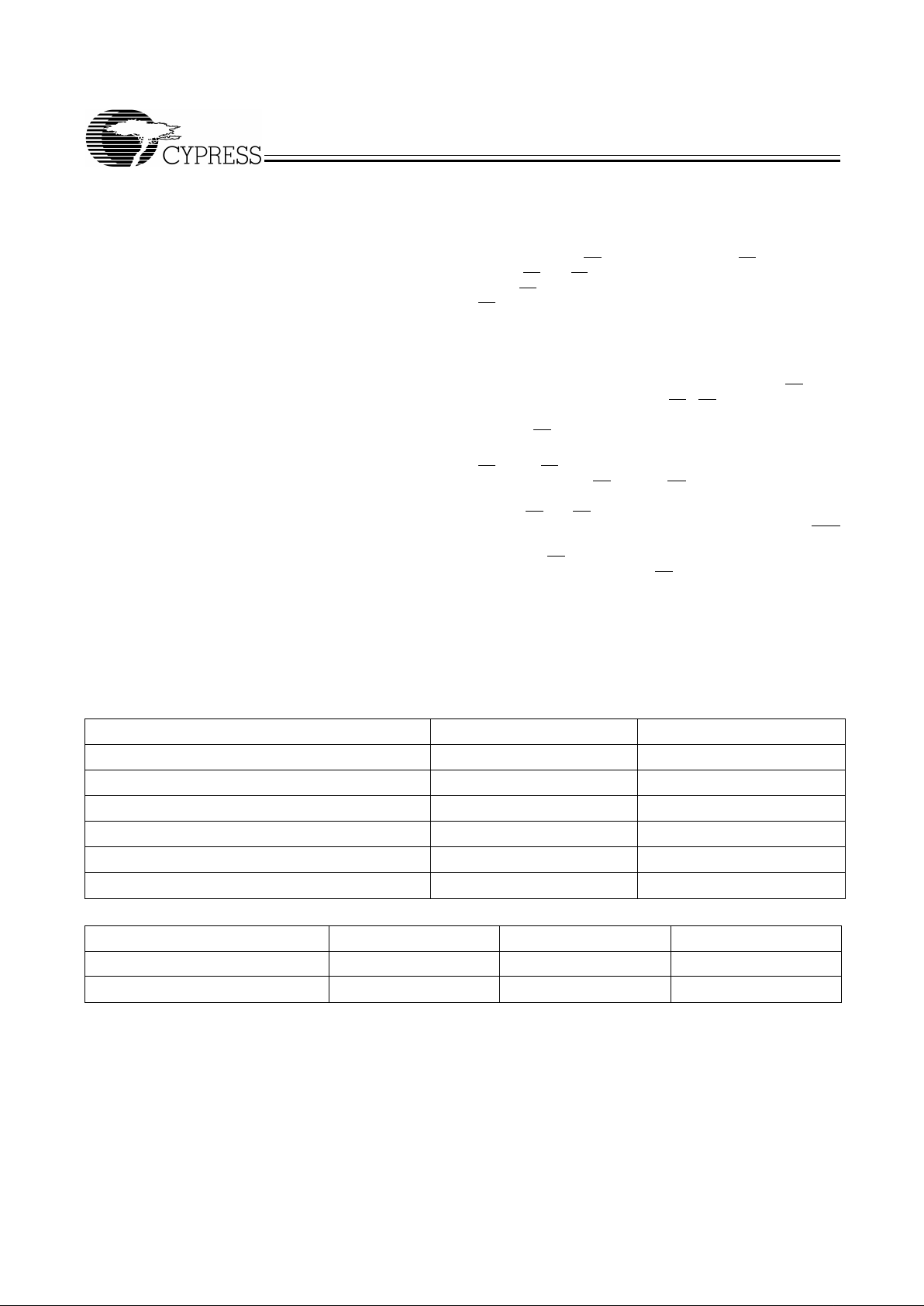

Prelimi n ary Top Level Block Diagram

Port A

Control

Logic

Port B

Control

Logic

Bus Matching Input Register

Bus Matching Output Register

Dual Ported

Status

Flag Logic

Programmable Flag Offset Registers

4K/16K/64Kx80

FIFO

CLKA

CSA

ENA

MR

PR

FF/IR

AF

FS0/SD

FS1/SEN

A

79–0

B

79–0

CLKB

CSB

ENB

BE/FWFT

SIZE1B

SIZE2B

EF/OR

AE

Read Data Path Logic

80

80

Reset

Logic

SIZE1A

SIZE2A

Write Data Path Logic

RT/SPM

JTAG Controller

TDI TCK TMS TRST

TDO

OE

Read

PointerPointer

Write

Memory

For the most recent information, visi t th e Cypress web site at www.cypress.com

Page 2

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

2

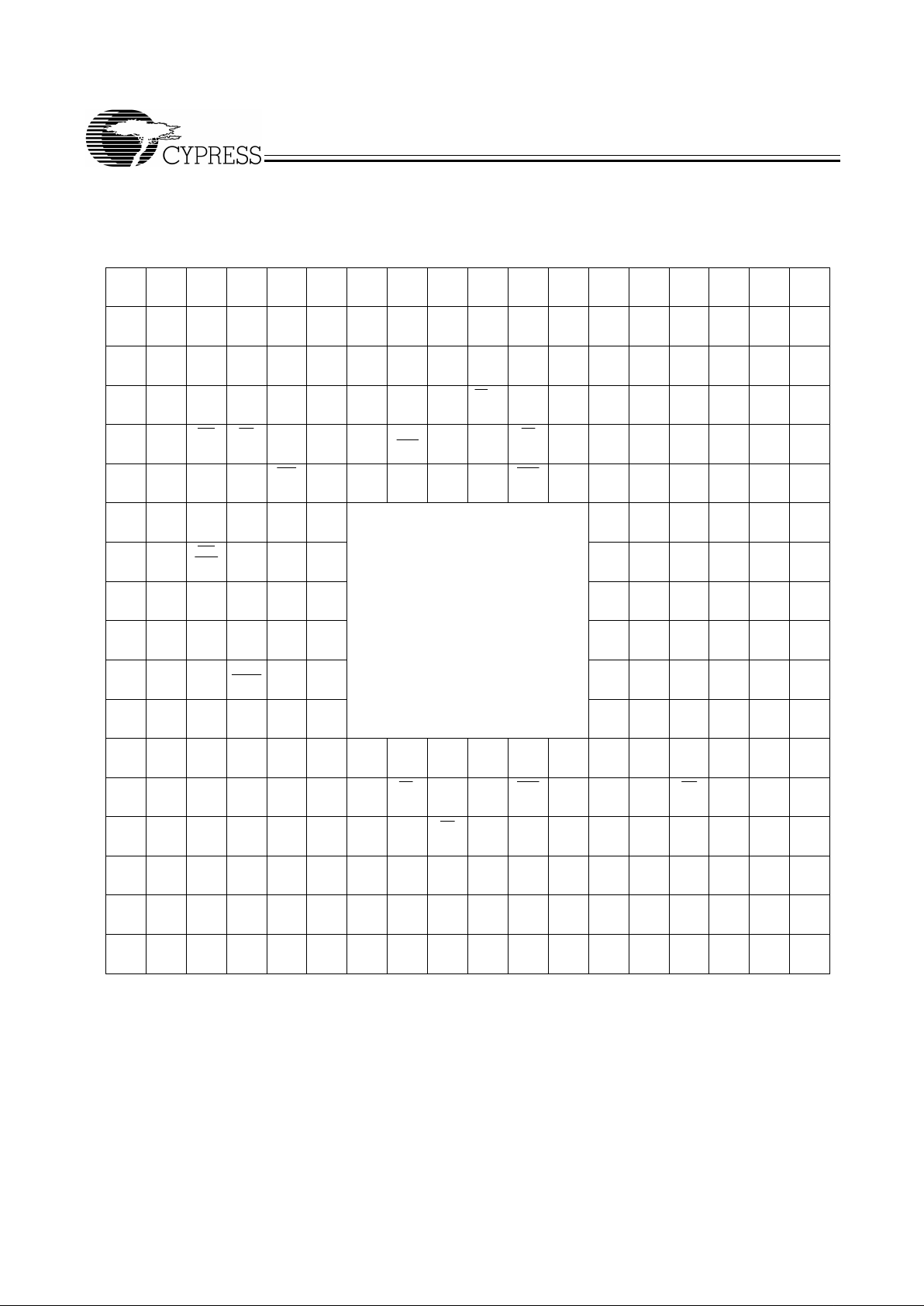

Pin Configuration for CY7C4804V25 (Top Vie w )

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

AV

DDQVDDQ

A16 A19 V

DDQ

A30 A34 GND CLKA A42 GND A48 A51 V

DDQ

A55 A57 V

DDQVDDQ

A

BV

DDQ

A10 A14 A17 V

DDQ

A29 A33 GND A39 A41 GND A45 A50 V

DDQ

A54 A56 A58 V

DDQ

B

CA9 A8 V

DDQ

A13 A18 A28 A32 A36 A38 V

DDQ

A44 A46 A49 A52 A53 V

DDQ

A59 A60 C

DA7 A6 A11V

DDQ

A20 GND A27 SH GND FF/IR VDD A43 GND A47 V

DDQ

A63 A67 A69 D

EV

DDQVDDQ

MR PR VDDA25 GND FS1/

SEN

GND GND AF GND GND VDD TDI A66 V

DDQVDDQ

E

FA12A15SIZE1AGND A21 A24 A31 A35 A37 ENA CSA A40 A61 VDD GND A64 A65 A68 F

GA5 A2SIZE2BFS0/

SD

GND A23 A62 GND TDO A70 A71 A72 G

HGNDGNDRT/

SPM

V

DD

SIZE 1BA4 A73 A74 TCK A75 GND GND H

JB2 B3V

DDQ

A1 GND A0 A76 GND GND A77 A78 A79 J

K B6 B7 B4 GND GND A3 B76 GND B77 V

DDQ

B78 B79 K

L GND GND B5 BE/

FWFT

A22 A26 B73 B74 TMS B75 GND GND L

M B10 B9 VREF B8 GND SIZE

2A

B69 GND TRST B70 B71 B72 M

N B14 B13 B12 GND B1 B11 B31 B35 B37 B40 B43 B45 B65 NC GND B66 B67 B68 N

PV

DDQVDDQ

B15 NC NC B0 GND EF/

OR

GND GND CSB GND NC VDD OE B64 V

DDQVDDQ

P

RB18 B17B16V

DDQ

NC GND NC VDD AE GND ZQ ENB GND NC V

DDQ

B61 B62 B63 R

TB20 B19 V

DDQ

B24 B27 B28 B32 B36 V

DDQ

B41B44B46B49 B52B53V

DDQ

B59 B60 T

UV

DDQ

B21 B22 B25 V

DDQ

B29 B33 GND B38 B42 GND B47 B50 V

DDQ

B54 B56 B58 V

DDQ

U

VV

DDQVDDQ

B23 B26 V

DDQ

B30 B34 GND B39 CLKB GND B48 B51 V

DDQ

B55 B57 V

DDQVDDQ

V

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

Page 3

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

3

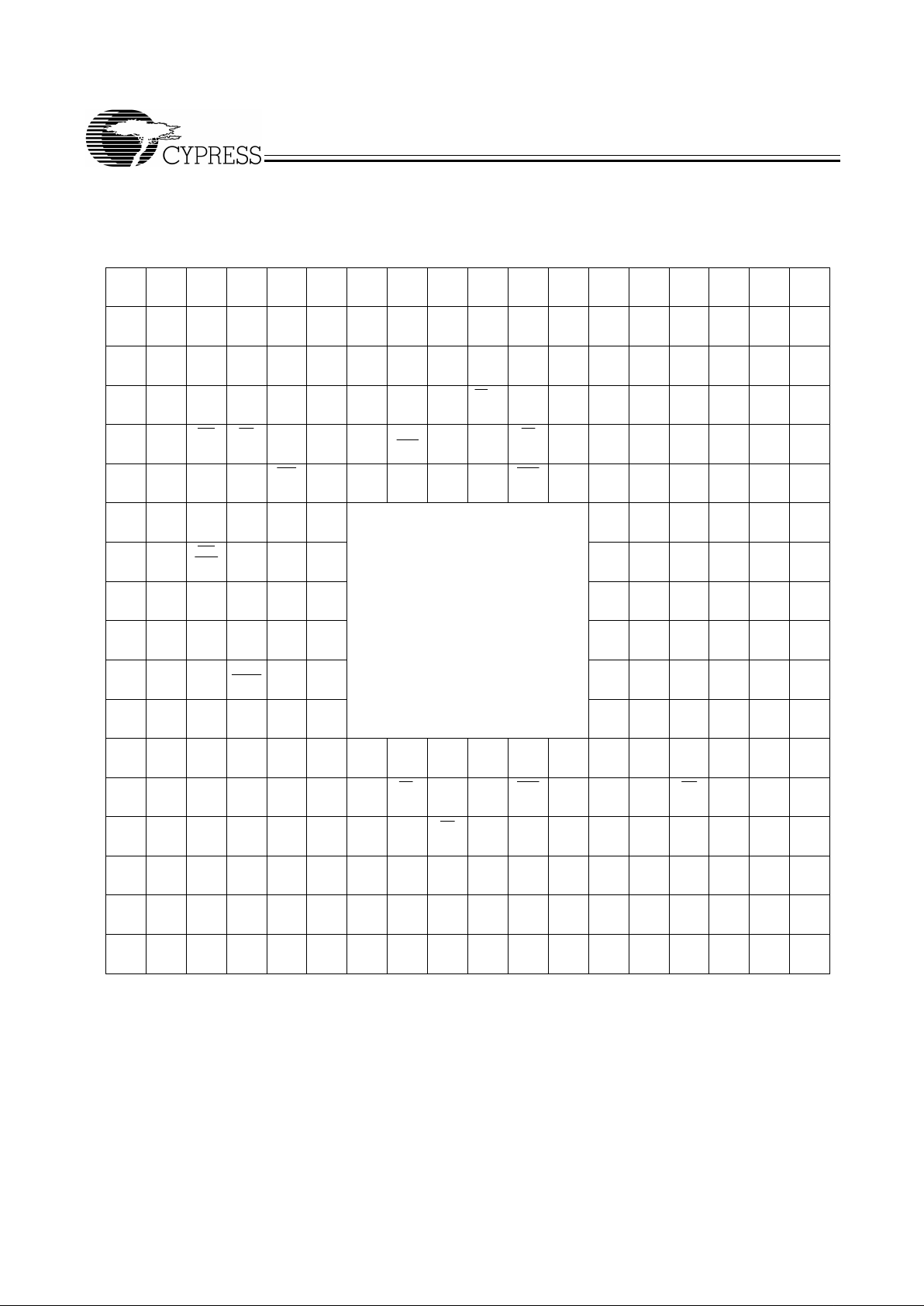

Pin Configuration for CY7C4806V25 (Top View)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

AV

DDQVDDQ

A16 A19 V

DDQ

A30 A34 GND CLKA A42 GND A48 A51 V

DDQ

A55 A57 V

DDQVDDQ

A

BV

DDQ

A10 A14 A17 V

DDQ

A29 A33 GND A39 A41 GND A45 A50 V

DDQ

A54 A56 A58 V

DDQ

B

CA9 A8 V

DDQ

A13 A18 A28 A32 A36 A38 V

DDQ

A44 A46 A49 A52 A53 V

DDQ

A59 A60 C

DA7 A6 A11V

DDQ

A20 GND A27 SH GND FF/IR VDD A43 GND A47 V

DDQ

A63 A67 A69 D

EV

DDQVDDQ

MR PR VDDA25 GND FS1/

SEN

GND GND AF GND VDD VDD TDI A66 V

DDQVDDQ

E

FA12A15SIZE1AGND A21 A24 A31 A35 A37 ENA CSA A40 A61 VDD GND A64 A65 A68 F

GA5 A2SIZE2BFS0/

SD

GND A23 A62 GND TDO A70 A71 A72 G

HGNDGNDRT/

SPM

V

DD

SIZE 1BA4 A73 A74 TCK A75 GND GND H

JB2 B3V

DDQ

A1 GND A0 A76 GND GND A77 A78 A79 J

K B6 B7 B4 GND GND A3 B76 GND B77 V

DDQ

B78 B79 K

L GND GND B5 BE/

FWFT

A22 A26 B73 B74 TMS B75 GND GND L

M B10 B9 VREF B8 GND SIZE

2A

B69 GND TRST B70 B71 B72 M

N B14 B13 B12 GND B1 B11 B31 B35 B37 B40 B43 B45 B65 NC GND B66 B67 B68 N

PV

DDQVDDQ

B15 NC NC B0 GND EF/

OR

GND GND CSB GND NC VDD OE B64 V

DDQVDDQ

P

RB18 B17B16V

DDQ

NC GND NC VDD AE GND ZQ ENB GND NC V

DDQ

B61 B62 B63 R

TB20 B19 V

DDQ

B24 B27 B28 B32 B36 V

DDQ

B41B44B46B49 B52B53V

DDQ

B59 B60 T

UV

DDQ

B21 B22 B25 V

DDQ

B29 B33 GND B38 B42 GND B47 B50 V

DDQ

B54 B56 B58 V

DDQ

U

VV

DDQVDDQ

B23 B26 V

DDQ

B30 B34 GND B39 CLKB GND B48 B51 V

DDQ

B55 B57 V

DDQVDDQ

V

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

Page 4

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

4

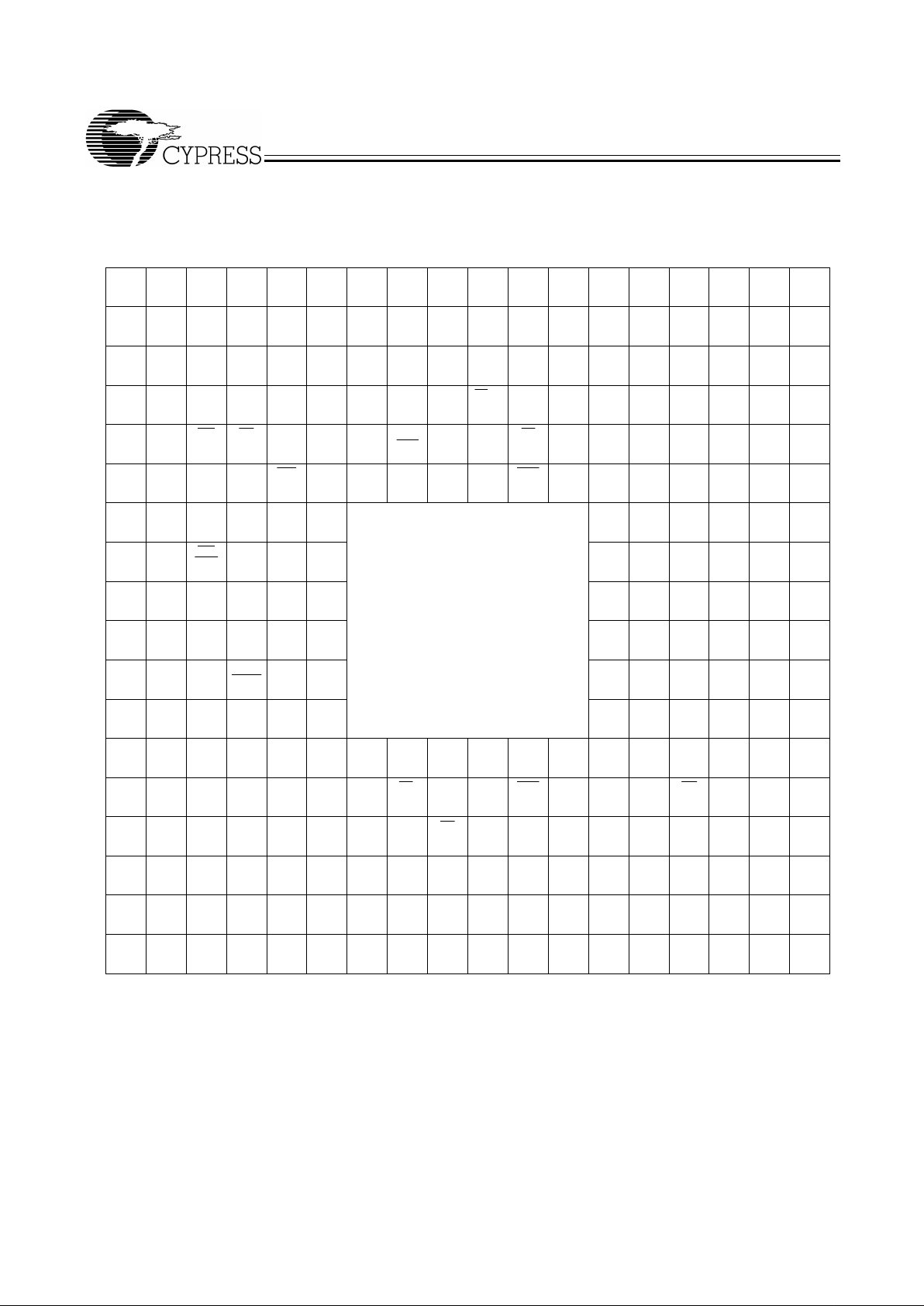

Pin Configuration for CY7C4808V25 (Top View)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

AV

DDQVDDQ

A16 A19 V

DDQ

A30 A34 GND CLKA A42 GND A48 A51 V

DDQ

A55 A57 V

DDQVDDQ

A

BV

DDQ

A10 A14 A17 V

DDQ

A29 A33 GND A39 A41 GND A45 A50 V

DDQ

A54 A56 A58 V

DDQ

B

CA9 A8 V

DDQ

A13 A18 A28 A32 A36 A38 V

DDQ

A44 A46 A49 A52 A53 V

DDQ

A59 A60 C

DA7 A6 A11V

DDQ

A20 GND A27 SH GND FF/IR VDD A43 GND A47 V

DDQ

A63 A67 A69 D

EV

DDQVDDQ

MR PR VDDA25 GND FS1/

SEN

GND GND AF GND GND VDD TDI A66 V

DDQVDDQ

E

FA12A15SIZE1AGND A21 A24 A31 A35 A37 ENA CSA A40 A61 GND GND A64 A65 A68 F

GA5 A2SIZE2BFS0/

SD

GND A23 A62 GND TDO A70 A71 A72 G

HGNDGNDRT/

SPM

V

DD

SIZE 1BA4 A73 A74 TCK A75 GND GND H

JB2 B3V

DDQ

A1 GND A0 A76 GND GND A77 A78 A79 J

K B6 B7 B4 GND GND A3 B76 GND B77 V

DDQ

B78 B79 K

L GND GND B5 BE/

FWFT

A22 A26 B73 B74 TMS B75 GND GND L

M B10 B9 VREF B8 GND SIZE

2A

B69 GND TRST B70 B71 B72 M

N B14 B13 B12 GND B1 B11 B31 B35 B37 B40 B43 B45 B65 NC GND B66 B67 B68 N

PV

DDQVDDQ

B15 NC NC B0 GND EF/

OR

GND GND CSB GND NC VDD OE B64 V

DDQVDDQ

P

RB18 B17B16V

DDQ

NC GND NC VDD AE GND ZQ ENB GND NC V

DDQ

B61 B62 B63 R

TB20 B19 V

DDQ

B24 B27 B28 B32 B36 V

DDQ

B41B44B46B49 B52B53V

DDQ

B59 B60 T

UV

DDQ

B21 B22 B25 V

DDQ

B29 B33 GND B38 B42 GND B47 B50 V

DDQ

B54 B56 B58 V

DDQ

U

VV

DDQVDDQ

B23 B26 V

DDQ

B30 B34 GND B39 CLKB GND B48 B51 V

DDQ

B55 B57 V

DDQVDDQ

V

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

Page 5

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

5

Functional Description

The CY7C480XV25 family of FIFOs is comprised of

high-speed, low-power, CMOS Synchronous (clocked) FIFO

memories, meaning both independent ports employ a synchronous interface. All data transfers through a port are gated

to the LOW -t o-HIGH tra nsition of the cloc k on ei ther port by t he

enable signa l. The cloc ks fo r each port are independen t of one

another and can be asynchronous or coincident. The enable

for each port is arranged to provide a simple unidirectional

interface between microprocessors and/or buses with synchronous control.

T w o kinds of reset are av ailabl e on the CY7C480XV25: Master

Reset and Partial Reset. Mas ter Reset ini tiali z es the read and

write pointers to the first location of the memory array, configures the FIFO for Big Endian or Little Endian byte arrangement, selects the CY standard or First-Word Fall-Through

(FWFT) mode, and determines the configuration of the programmabl e flags . The f lags can b e prog rammed eit her in s erial

mode or in parallel mode. The FIFO also comes with three

possible default flag offset settings: 8, 16, or 64.

Partial Reset also sets the read and write pointers to the first

location of the memory. Unlike Master Reset, any settings existing prior to Pa rtial Reset (i .e., pr ogrammi ng method and partial flag default offsets) are retained. Partial Reset is useful

since it p ermits flus hing of the FIFO memory without changi ng

any configuration settings.

The CY7C480XV25 have two modes of operation: CY Standard Mode or First-Word Fall-Through Mode (FWFT). In the

CY Standard Mode, the first word written to an empty FIFO is

deposited into the memory array. A read operation is required

to access that word (along with all other subsequent words

residing in m emory). In the FWFT Mode, the first w ord written

to an empty FIFO appears automatically on the outputs, and

no read ope ra tion is r equir ed. Ne v ertheless , ac cess ing su bsequent words does necessitate formal read request. FWFT

mode is primarily used for cascading multiple FIFOs.

The FIFO has an EF

/OR flag on port B and FF/IR flag on Port

A. The EF

and FF functions are selected in the CY Standard

Mode. EF

indicates whether or not the FIFO memory is empty .

FF

shows whether or not the memory is full. The IR and OR

functions are select ed in the Fir st-W ord F all-Thr ough mode . IR

indicates whether or not the FIFO has memory locations av ai lable. OR sho ws whet her th e FIFO has data available f or r eading or not. It marks the presence of valid data on the outputs.

The FIFO has a programmable Almost Empty f lag (AE

) and a

programma ble Almost Full f lag (AF

). AE indicates the number

of words left in the FIFO memory is at the user-defined

amount. AF

indicates the number of words written into the

FIFO memory has achieved a predetermined amount.

FF

/IR and AF flags a re synchroni zed to port A cloc k tha t writes

data into its array. EF

/OR and AE flags are synchronized to

Port B clock that reads data from its array. Programmable offsets for AE

and AF are loaded in parall el via P ort A or in serial

via the SD input. The Serial Programming Mode pin (SPM

)

makes this sel ection. Three def ault offsets sett ing are also provided. The AE

threshold can be set at 8, 16, or 64 locations

from the empty boundary and AF

threshold ca n be set at 8, 16,

or 64 locations from the full boundary. All these choices are

made using the FS0 and FS1 inputs during Master Reset.

The CY7C480XV25 FIFOs are characterized for operation

from 0°C to 70°C commercial, and from –40°C to 8 5°C in dustrial.

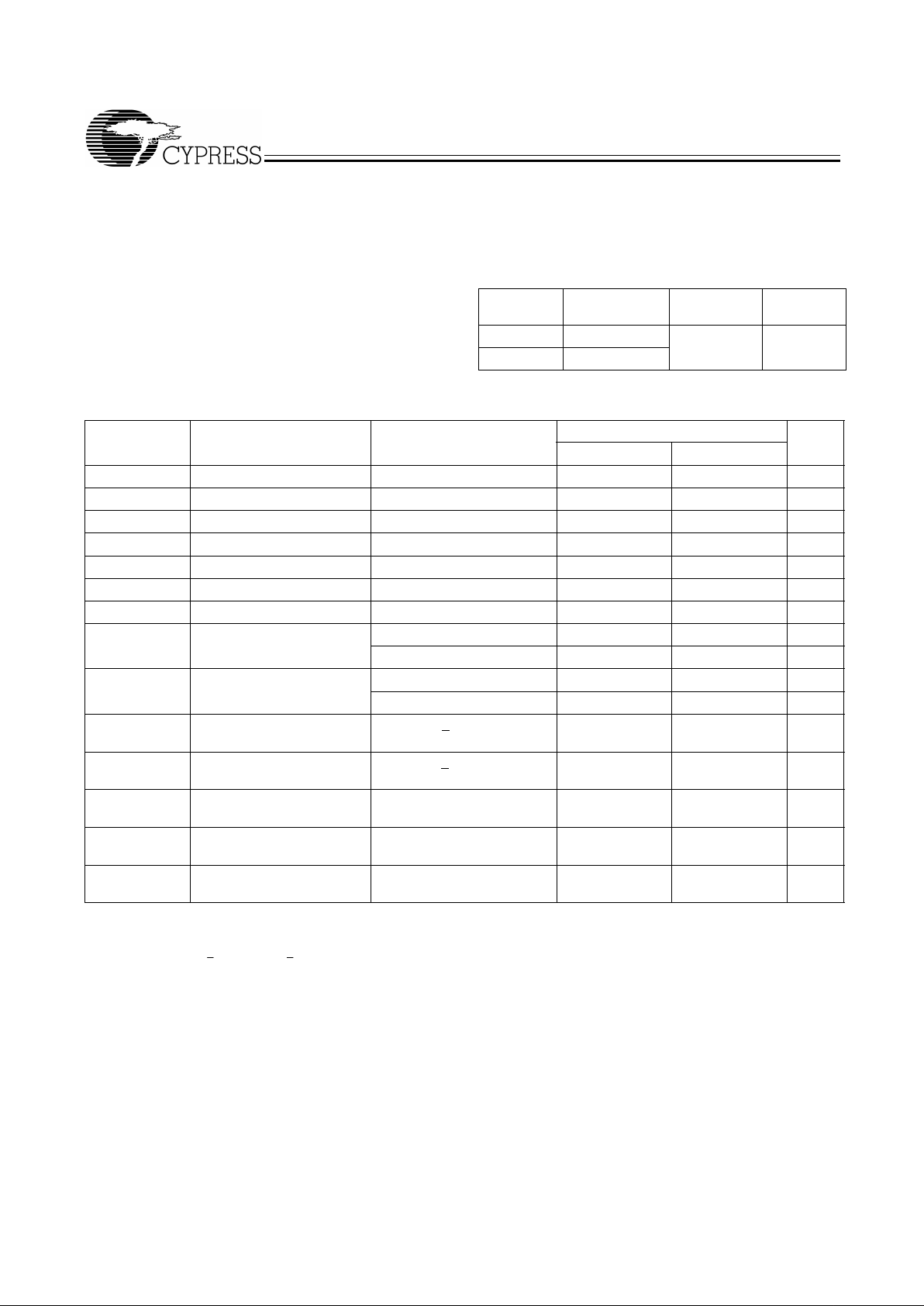

Selection Guide

CY7C480XV25-200 CY7C480XV25-166

Maximum Frequency (MHz) 200 166

Maximum Access Time (ns) 3.3 3.7

Minimum Cycle Time (ns) 5 6

Minimum Data or Enabl e Set-Up (ns) 0.9 0.9

Minimum Data or Enable Hold (ns) 0.6 0.6

Maximum Flag Delay (ns) 3.3 3.7

CY7C4808V25 CY7C4806V25 CY7C4804V25

Density 64K x 80 16K x 80 4K x 80

Pac kage 288 FBGA 288 FBGA 288 FBGA

Page 6

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

6

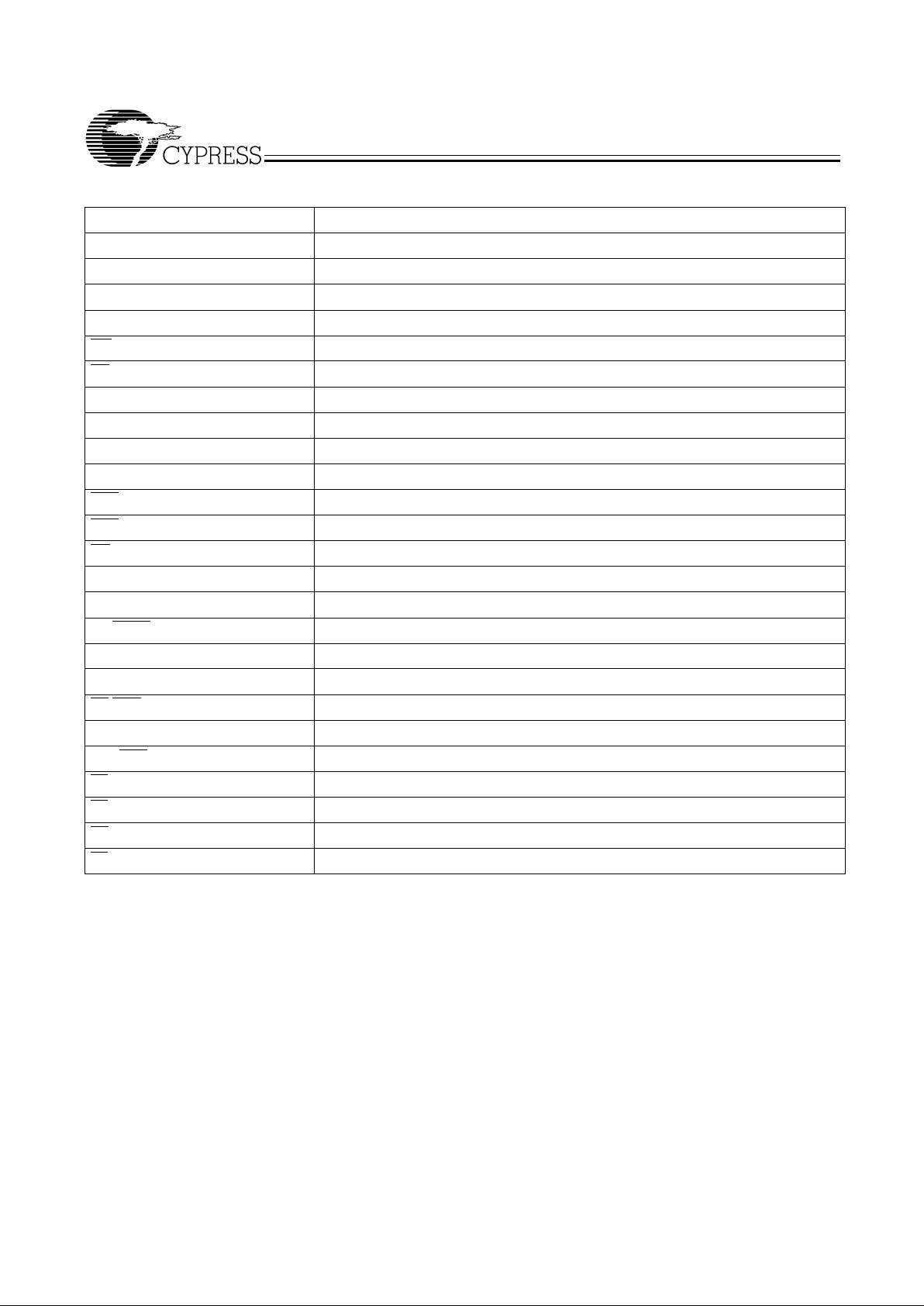

Pin Description

Pin Description

V

DDQ

Po wer supply for I/Os

V

DD

Po wer supply for internal logic

GND Ground

V

REF

Reference voltage

MR

Master reset

PR

Partial reset

A

0–A79

Input data bus

B

0–B79

Outp u t da ta bus

ENA Port A enable pin

ENB Port B enable pin

CSA

Port A chip select

CSB

Port B chip select

OE

Output enable

CLKA Port A clock

CLKB Port B clock

BE/FWFT

Big/Little Endian and CY Standard/First-Word Fall-Through mode select pin

SIZE1A, SIZE2A Port A bus siz e configuration pins

SIZE1B, SIZE2B Port B bus siz e configuration pins

RT

/SPM Retransmit pin/serial programming select

TDI, TDO, TCK, TMS , TRST JTAG pins

FS1/SEN

, FS0/SD Programmable flags configuration pins

EF

/OR Empty/Output Ready flag (Port B)

FF

/IR Full/Input Ready flag (Por t A)

AE

Programmable Almost Empty flag (P ort B)

AF

Programmable Almost Full flag (Port A)

Page 7

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

7

Maximum R atings

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .............. .. .. ........... .. ....–65

°

C to +150°C

Ambient Temperature with

Power Applied ....... ... .. ............... .. ... .............. . –55

°

C to +125°C

Supply Voltage to Ground Potential ...............–0.5 V to +3 .6 V

DC Vo lt age Applied to Outputs

in High Z State

[1]

................................... –0.5V to V

DDQ

+0.5V

DC Input Voltage

[1]

................................ –0.5V to V

DDQ

+0.5V

Current into Outputs (LOW)......................................... 20 mA

Static Discharge Voltage ...........................................>2001V

(per MIL-STD-883, Method 3015)

Latch-Up Current.....................................................>200 mA

Notes:

1. Minimum voltage equal –2.0V for pulse duration less than 20ns.

2. All voltage referenced to ground.

3. Overshoot: V

IH

(AC) < VDD+1.5V for t < t

clk

/2, Power-Up: VIH<2.6V and VDD<2.4V and V

DDQ

<1.4V for t<200 ns.

Operating Range

Range

Ambient

Temperature

V

DD

V

DDQ

Commercial 0°C to +7 0°C 2.5V ± 100 mV 1.4V to 1.9V

Industrial –40°C to +85°C

DC Specifications

(All I/Os e xcept JTAG ports will be at HSTL level)

[2, 3]

CY7C480XV25

Parameter Description Test Co ndit ions Min. Max. Unit

V

DD

Power Supply Voltage 2.4 2.6 V

V

DDQ

I/O Supply Voltage 1.4 1.9 V

V

REF

Input Reference Voltage Typical value = 0.75V 0.68 1.0 V

V

OH

Outp ut HIGH Voltage (V

DDQ

/2) + 0.3 V

DDQ

V

V

OL

Output LOW Voltage V

SS

(V

DDQ

/2) – 0.3 V

V

IH

Input HIGH V o ltage V

REF

+ 0.1 (V

DDQ

/2) + 0.3 V

V

IL

Input LOW Voltage –0.3 V

REF

– 0.1 V

V

OH_JTA G

JTAG Port Output

High Voltage

I

OH

= –100 µA 2.1 V

I

OH

= –2 mA 1.7 V

V

OL_JTA G

JTAG Port Output

Low V oltage

IOL= 100 µA 0.2 V

IOL= 2 mA 0.7 V

V

IH_JTA G

JTAG Port Input

High Voltage

V

OUT>VVOH

(min.) 1.7 VDD+0.3 V

V

IL_JTA G

JTAG Port Input

Low V oltage

V

OUT<VVOL

(max.) –0.3 0.7 V

I

IX

Input Leakage

Current

–10 +10

µA

I

OZL,IOZH

Outp ut OFF,

High Z Current

–10 +10

µA

I

SB

Average Standby

Current

10 mA

Page 8

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

8

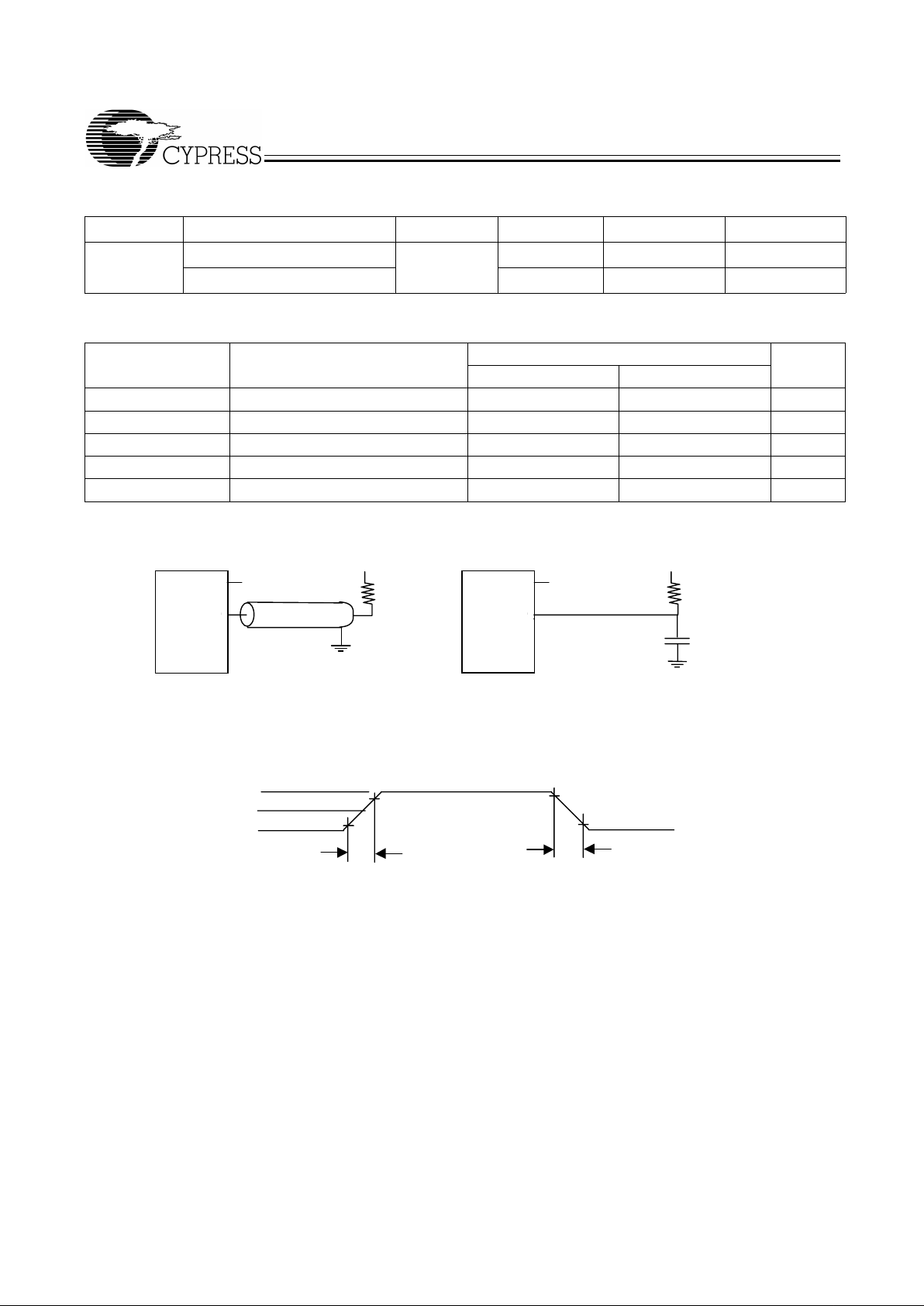

AC Test Loads and Waveforms

Notes:

4. Both clocks switching at maximum speeds, data switching at half the clock frequency.

5. Unless otherwise noted, test conditions assume signal transition time of 2 V/ns, timing reference levels of 0.75V , V

ref

= 0.75V, RQ = 250Ω, V

DDQ

= 1.5V, input

pulse levels of 0.25V to 1.25V, and output loading of the specified I

OL/IOH

and load capacitance shown in (b) of AC test loads.

DC Specifications

(continued)

[4]

Parameter Description Conditions 200 MHz 166 MHz Unit

I

CC

Operating current (Typical) VDD = max.,

I

OUT =

0 mA

225 185 mA

Operating current (Max.) 300 250 mA

AC Spe cificati ons

(A 50Ω load terminated into 0. 75V is used wit h V

DDQ

)

CY7C480XV25

Parameter Description Min. Max. Unit

F

MAX

Max. Frequency 200 MHz

t

CYC

Clock Cycle Time 5 ns

t

SD

Input Data Set-Up Time 0.9 ns

t

HD

Input Data Hold Time 0.6 ns

t

A

Access Time 3.3 ns

V

REF

(V

DDQ

)/2

Output

Device

Under

Test

Z

O

= 50

Ω

R

L

= 50

Ω

V

TH

= (V

DDQ

)/2

RL = 50

Ω

V

REF

(

V

DDQ

)/2

O

utput

D

evice

U

nder

T

est

V

TH

= (V

DDQ

)/2

5

pF

ALL INPUT PULSES

0.75V

1.25V

0.25V

10%

90%

t

R

tF9

0%

1

0%

t

R

≤ 0.5 ns, tF ≤ 0.5 ns

[5]

(a) Test Loads

(b) Test Loads

Page 9

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

9

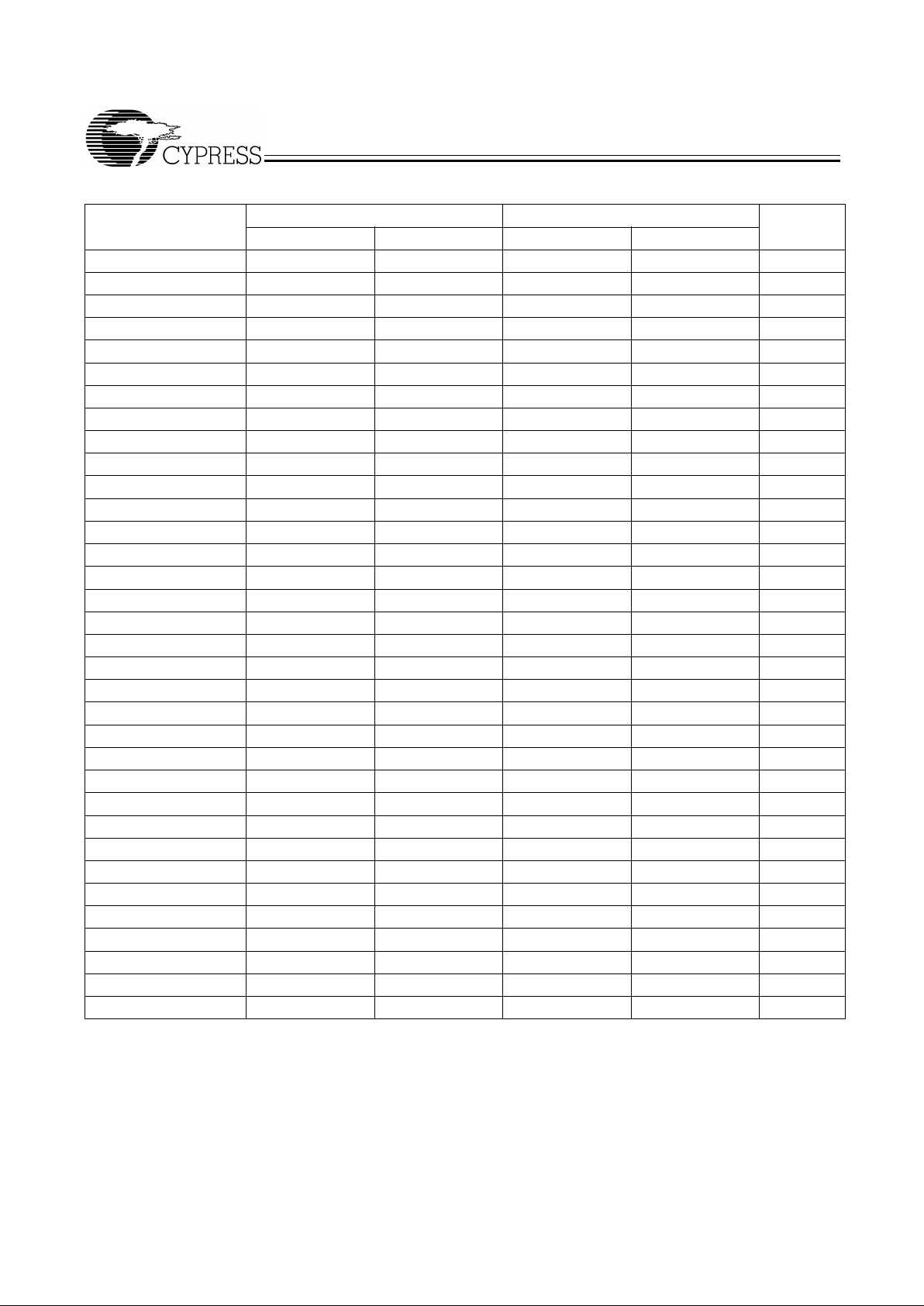

Timing Parameters

7C480XV25-200 7C480XV25-166

Parameter Min. Max. Min. Max. Unit

f

S

200 166 MHz

t

CLK

5 6 ns

t

CLKH

2.5 3 ns

t

CLKL

2.5 3 ns

t

DS

0.9 0.9 ns

t

ENS

0.9 0.9 ns

t

RSTS

2 2 ns

t

FSS

2 2 ns

t

BES

2 2 ns

t

SMPS

2 2 ns

t

SDS

0.9 0.9 ns

t

SENS

0.9 0.9 ns

t

FWS

0.9 0.9 ns

t

DH

0.6 0.6 ns

t

ENH

0.6 0.6 ns

t

RSTH

2 2 ns

t

FSH

2 2 ns

t

BEH

2 2 ns

t

SPMH

2 2 ns

t

SDH

0.6 0.6 ns

t

SENH

0.6 0.6 ns

t

SPH

0.6 0.6 ns

t

SKEW1

8 10 ns

t

SKEW2

8 10 ns

t

A

3.3 3.7 ns

t

WFF

3.3 3.7 ns

t

REF

3.3 3.7 ns

t

PAE

3.3 3.7 ns

t

PAF

3.3 3.7 ns

t

RSF

4 4 ns

t

EN

3.5 3.5 ns

t

DIS

3.5 3.5 ns

t

PRT

25 25 ns

t

RTR

45 45 ns

Page 10

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

10

Switchin g Waveforms

Notes:

6. PR

must be HIGH during Master Reset.

7. MR must be HIGH during Partial Reset.

Master Reset Loading X and Y with a Preset Value of Eight

CLKA

t

RSF

t

RSF

t

WFF

t

FSS

t

FSH

t

SPMS

t

SPMH

t

BES

t

BEH

t

RSTH

t

RSTS

t

FWS

CLKB

MR

BE/FWFT

RT/SPM

FS1/SEN,

FS0/SD

FF

/IR

EF

/OR

AE

AF

[6]

t

RSF

t

RSF

Partial Reset (CY Standard and FWFT Modes)

t

RSF

t

RSF

t

RSTS

t

RSTH

CLKA

CLKB

PR

FF/IR

EF

/OR

AE

AF

[7]

t

WFF

t

RSF

t

RSF

Page 11

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

11

Notes:

8. CSA

= LOW. It is not necessary to program offset register on consecutive clock cycles.

9. It is not necessary to program offset register bits on consecutive clock cycles. FIFO write attempts are ignored until IR is set HIGH.

10. Programmable offsets are written serially to the SD input in the order AF offset (Y) then AE offset (X).

Switchin g Waveforms

(continued)

Parallel Program ming of t he Almost-Full Flag and Almost-Empty Flag Offset Values after Reset

(CY Standard and FWFT Modes)

t

WFF

t

FSS

t

DS

t

SPMS

t

SPMH

t

FSH

t

ENS

t

ENH

t

DH

AF Offset (Y)

First Word

into FIFO

CLKA

MRS

RT/SPM

FS1/SEN,

FS0/SD

FF/

IR

ENA

A

0−79

[8]

AE Offset (X)

Serial Programming of the Almost-Full Flag and Almost-Empty Flag

Offset Values (CY Standard and FWFT Modes)

t

FSS

t

SPH

t

SENS

t

SENH

t

SENH

t

SENS

t

SDH

t

SDS

t

SDH

t

SDS

t

WFF

AF Offset (Y) MSB

t

SPMS

t

SPMH

CLKA

MR

RT/SPM

FF/IR

FS1/SEN

FS0/SD

AE Offset (X) LSB

t

FSStFSH

[9]

[10]

Page 12

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

12

Note:

11. Unused bits B

40–79

are zeroes for word-size reads.

Switchin g Waveforms

(continued)

OR

t

CLKH

t

CLKL

t

ENS

t

DIS

t

ENS

t

EN

t

CLK

t

DIS

t

ENH

t

ENS

t

ENH

t

A

t

A

t

A

t

A

t

EN

t

EN

W1 W2

W1

W2

W3

Previous Data

No Operation

CLKB

EF

/OR

CSB

ENB

B

0–79

(Standard Mode)

B

0–79

(FWFT Mode)

Port B Long-Word Read Cycle Timing for FIFO (CY Standard and FWFT Modes)

OE

HIGH

OR

t

DIS

t

ENS

t

ENH

t

A

t

A

t

A

t

A

t

EN

t

EN

t

DIS

Previous Data

Read 1

Read 1

Read 2

Read 2

Read 3

No Operation

CLKB

EF

/OR

CSB

ENB

B

0–39

(Standard Mode)

B

0–39

(FWFT Mode)

Port B Word Read Cycle Timing f or FIF O (CY Standard and FWFT Modes)

OE

[11]

HIGH

Page 13

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

13

Notes:

12. Unused bits B

20–79

are zeroes for short word-size reads.

13. Unused bits B

10–79

are zeroes for byte-size reads.

Switchin g Waveforms

(continued)

OR

t

DIS

t

ENStENH

t

A

t

A

t

A

t

A

t

EN

t

EN

t

DIS

t

A

t

A

t

A

t

A

Previous Data

Read 1

Read 1

Read 2

Read 2

Read 3

Read 3

Read 4

Read 4

Read 5

No Operation

HIGH

CLKB

EF

/OR

CSB

ENB

B

0–19

(Standard Mode)

B

0–19

(FWFT Mode)

Port B Short Wor d Read Cycle Timing for FIFO (CY Standar d and FWFT Modes)

OE

[12]

OR

t

DIS

t

ENStENH

t

A

t

A

t

A

t

A

t

EN

t

EN

t

DIS

t

A

t

A

t

A

t

A

Previous Data

Read 1

Read 1

Read 2

Read 2

Read 3

Read 3

Read 4

Read 4

Read 5

No Operation

HIGH

CLKB

EF

/OR

CSB

ENB

B

0–9

(Standard Mode)

B

0–9

(FWFT Mode)

Port B Byte Read Cycle Timing for FIFO (CY Standard and FWFT Modes)

[13]

OE

Page 14

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

14

Notes:

14. If Port B size is word, short word or byte, EF

is set LOW by the last word, short word or byte read from the FIFO, respectively.

15. t

SKEW1

(7 ns minimum) is the time between a rising CLKA edge and a rising CLKB edge for OR flag to transition HIGH. If the time between these two edges

is less than t

SKEW1

, then the transition of OR HIGH may occur one CLKB cycle later than shown. CLKA and CLKB above are assumed to run at 200MHz (5

ns cycle time), which results in OR flag being updated after the 4th CLKB edge. If the clock cycles are more than 7 ns, OR flag may get updated after the

3rd clock edge, depending on when the clock edges occur. In general, OR flag update cycle = (t

SKEW1

) + (2 clock cycle) + (t

REF

).

Switchin g Waveforms

(continued)

t

CLKH

t

CLKL

t

ENS

t

CLK

t

ENH

t

A

t

DS

W1

LOW

t

DH

HIGH

FIFO Empty

LOW

Old Data in FIFO Output Register

W1

t

ENStENH

t

REF

t

REF

t

CLKHtCLKL

t

CLK

t

SKEW1

[15]

CLKA

CSA

ENA

FF

/IR

A

0–79

CLKB

EF

/OR

CSB

ENB

B

0–79

OR Flag Timing and First Data Word Fal l Thr ough when FIFO is Empty (FWFT Mode)

LOW

OE

[14]

Page 15

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

15

Notes:

16. t

SKEW1

is the minimum time between a rising CLKA edge and a rising CLKB edge for EF to transition HIGH. If the time between these two edges is less than

t

SKEW1

, then the transition of EF HIGH may occur one CLKB cycle later than shown. CLKA and CLKB above are assumed to run at 200 MHz (5 ns cycle

time), which results in EF

flag being updated after the 3rd CLKB edge. If the clock cycles are more than 7 ns, EF flag may get updated after the 2nd clock

edge, depending on when the clock edges occur. In general, EF flag update cycle = (t

SKEW1

) + (1 clock cycle) + (t

REF

).

Switchin g Waveforms

(continued)

t

CLKH

t

CLKL

t

ENStENH

t

A

t

DS

W1

LOW

t

DH

HIGH

FIFO Empty

LOW

W1

t

ENS

t

ENH

t

REF

t

REF

t

CLKH

t

CLKL

t

CLK

t

CLK

t

SKEW1

[16]

CLKA

CSA

ENA

FF

/IR

A

0–79

CLKB

EF

/OR

CSB

ENB

B

0–79

EF Flag Timing and First Data Read Fall Through when FIFO is Empty (CY Standard Mode)

[14]

LOW

OE

Page 16

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

16

Notes:

17. If Port B size is word, short word or byte, t

SKEW1

is referenced to the rising CLKB edge that reads the last word, short word or byte write of the long-word,

respectively.

18. t

SKEW1

is the minimum time between a rising CLKB edge and a rising CLKA edge for FF/IR to transition HIGH. If the time between the rising CLKB edge

and rising CLKA edge is less than t

SKEW1

, then the transition of FF/IR HIGH may occur one CLKA cycle later than shown. CLKA and CLKB above are

assumed to run at 200 MHz (5 ns cycle time), which results in FF/IR flag being updated after the 3rd CLKA edge. If the clock cycles are more than 7 ns,

FF/IR flag may get updated after the 2nd clock edge, depending on when the clock edges occur. In general, FF/IR flag update cycle = (t

SKEW1

) + (1 clock

cycle) + (t

WFF

).

Switchin g Waveforms

(continued)

t

CLKHtCLKL

t

ENS

t

ENH

t

A

LOW

HIGH

FIFO Full

LOW

t

ENS

t

ENH

t

WFF

t

WFF

t

CLKH

t

CLKL

t

CLK

t

CLK

t

SKEW1

[18]

t

DH

t

DS

Previous Word in FIFO Output Register

Next Word From FIFO

CLKB

CSB

ENB

EF

/OR

B

0–79

CLKA

FF

/IR

CSA

ENA

A

0−79

FF/IR Flag Timing and Fir st Availab le Write when FIFO is Full (CY Standard and FWFT Mode)

[17]

Page 17

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

17

Notes:

19. FIFO Write (CSA

= LOW) on Port A, FIFO read (CSB = LOW) on Port B. Data in the FIFO output register has been read from the FIFO.

20. D = Maximum FIFO Depth = 4K for the CY7C4804V25, 16K for the CY7C4806V25, and 64K for the CY7C4808V25.

21. If Port B size is word, short word or byte, t

SKEW2

is referenced to the rising CLKB edge that writes the last word, short word or byte of the long word, respectively.

22. t

SKEW2

is the minimum time between a rising CLKA edge and a rising CLKB edge for AF to transition HIGH in the next CLKA cycle. If the time between these

two edges is less than t

SKEW2

, then AF may transition HIGH one CLKB cycle later than shown. CLKA and CLKB above are assumed to run at 200MHz (5

ns cycle time), which results in AF

flag being updated after the 3rd CLKA edge. If the clock cycles are more than 7 ns, AF flag may get updated after the

2nd clock edge, depending on when the clock edges occur. In general, AF flag update cycle = (t

SKEW2

) + (1 clock cycle) + (t

PAF

).

23. FIFO Write (CSA = LOW) on Port A, FIFO read (CSB = LOW) on Port B. Data in the FIFO output register has been read from the FIFO.

24. If Port B size is word, short word or byte, AE is set LOW by the last word, short word or byte read from FIFO, respectively.

25. t

SKEW2

is the minimum time between a rising CLKA edge and a rising CLKB edge for AE to transition HIGH in the next CLKB cycle. If the time between the

rising CLKA edge and rising CLKB edge is less than t

SKEW2

, then AE may transition HIGH one CLKB cycle later than shown. CLKA and CLKB above are

assumed to run at 200 MHz (5 ns cycle time), which results in AE

flag being updated after the 3rd CLKB edge. If the clock cycles are more than 7 ns, AE

flag may get updated after the 2nd clock edge, depending on when the clock edges occur. In general, AE flag update cycle = (t

SKEW2

) + (1 clock cycle) + (t

PAE

).

Switchin g Waveforms

(continued)

Timing for AF when FIFO is Almost Full (CY Standard and FWFT Modes)

t

PAF

t

ENH

t

ENS

t

PAF

t

ENS

t

ENH

[D–(Y+1)] Long

words in FIFO

(D–Y) Long words in FIFO

t

SKEW2

[22]

CLKA

ENA

AF

CLKB

ENB

[19, 20, 21]

[D–(Y+3)]

t

PAE

t

PAE

t

SKEW2

[25]

t

ENS

X+3 Long words in FIFO

X Long words in FIFO

CLKA

ENA

CLKB

AE

ENB

Timing for AE

when FIFO is Almost Empty (CY Standard and FWFT Modes)

[23, 24]

t

ENH

t

ENS

t

ENH

Page 18

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

18

Notes:

26. Clocks are free-running in this case.

27. The flags may change state during Retransmit as a result of the offset of the read and write pointers, but flags will be valid at t

RTR

.

28. For the AE and AF flags, two clock cycles are necessary after t

RTR

to update these flags.

Switchin g Waveforms

(continued)

FIFO Retransmit Timing

ENB

RT

t

PRT

t

RTR

EF/FF

[26, 27, 28 ]

Page 19

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

19

Signal Description

Master Reset (MR)

The FIFO memory of the CY7C480XV25 undergoes a complete reset by taking its associated Master Reset (MR

) input

LOW for at least fo ur P ort A clock (CLKA) and fou r P ort B clock

(CLKB) LOW -to-HIGH tran sitions . The Master Reset inpu t can

switch asy nchronous ly to the clocks. A Master Reset initializes

the internal read and write pointers and forces the Full/Input

Ready flag (FF

/IR) LOW, the Empty/Output Ready flag

(EF

/OR) LOW, the Almost Empty flag (AE) LOW, and the Al-

most Fu ll flag (AF

) HIGH. A fter a Mas ter Reset, t he FIFO’s

Full/Input Ready flag is set HIGH after two clock cycles to begin normal operation. A Master Reset must be performed on

the FIFO after pow er up, before data is written to its memory .

A LOW- to-HI GH tran siti on on a F IFO Mas ter Res et (MR

) input

latches th e v alue o f the Bi g Endian (BE) i nput, determi ning t he

order by which b ytes are transfe rred through Port B.

A LOW-to-HIGH transition on a FIFO reset (M R

) input latches

the values of the Flag Select (FS0, FS1) and Serial Programming Mode (SPM

) inputs for choosi ng the Almost Full and Almost Empty offset programming method (see Almost Empty

and Almost Full flag offset programming below) .

Partia l Re se t (PR

)

Each of the two FI FO m em orie s of the CY7C480XV25 undergoes a limited reset by taking i ts associated P artial Reset (PR

)

input LOW for at least four Port A clock (CLKA) and four Por t

B clock (CLKB) LOW-to-HIGH transitions. The Partial Reset

inputs can switch asynchronously to the clocks. A Partial Reset initializes the internal read and write pointers and forces

the Full/Input Ready flag (FF

/IR) LOW, the Empty/Output

Ready flag (EF

/OR) LOW, the Almost Empty flag (AE) LOW,

and the Almost Full flag (AF

) HIGH. A ft er a Partial R es e t, th e

FIFO’s Full/In put Ready f lag is set HI GH af ter t wo cloc k c ycles

to begin normal operation.

Whatever flag offsets, programming method (parallel or serial), and timing mode (FWFT or CY Standard mode) are currently selected at the time a Partial Reset is initiated, those

settings will remain unchanged upon completion of the reset

operation. A Partial Reset may be useful in the case where

reprogramming a FIFO following a Master Reset would be inconvenient.

Big Endian/First-Word Fall-Through (BE/FWFT

)

This is a dual-purpose pin. At t he time of Master Reset, the BE

select function is active, permitting a choice of Big or Little

Endian byte ar rangement f or dat a written to or read from ei ther

one of the ports. This selecti on determines the order by which

bytes (or short words or wor ds) of data are transf erred through

this port. For the following examples, assume that a byte (or

short words or word) bus size has been selected for Port B.

(Note that when Port B is configured for a long-word size, the

Big Endian function has no application and the BE input is a

“don’t care”.)

A HIGH on the BE/FWFT

input when the Master Reset (MR)

input goes f rom LOW to HIGH wi ll select a Big Endi an arrang ement. When data is moving from Port A to Por t B, the most

significant byte (short word/word) of the long-word written to

Port A will be transferred to Port B first; the least significant

byte (short word/word) of the long-word written to Port A will

be transferred to Port B last.

A LOW on the BE/FWFT

input when the Master Reset (MR)

input goes from LOW to HIGH will select a Little Endian arrangement. When data is moving from Port A to Port B, the

least significant byte (short word/word) of the long-word written to Port A will be transferred to Port B first; the most significant by te (short word/word) of the long-word written to Port A

will be transferred to Port B last.

After Master Reset, the FWFT select f unction is acti ve, permitting a choice between two possible timing modes: CY Standard Mode or First-Word Fall-Through (FWFT) Mode. Once

the Master Reset (MR

) input is HIGH, a HIGH o n the BE/ FWFT

input at the second LOW-to-HIGH transition of CLKA will select CY Standa rd Mode. This mode uses the Em pty Fl ag function (EF

) to indicate whether or not there are any words

present in the F IFO memory . It uses t he Full Flag funct ion (FF

)

to indicate whether or not the FIFO memory has any free

space for writing. I n CY Standar d Mode , e v ery word read fr om

the FIFO, inclu ding the f irst , must be requeste d using a f o rmal

read operati on.

Once the Master Reset (MR

) inpu t is HIG H, a LOW on the

BE/FWFT

input LOW-to-HIGH transition of CLKA will select

FWFT Mode. This mode uses the Output Ready function (OR)

to indicate wh ether or n ot there i s val id data at the data outputs

(B

0–79

). It also uses the Input Ready function (IR) to indicate

whether or not the FIFO memory has any free space for writing. In the FWFT mode , the firs t word written to an em pty FIFO

goes directly to dat a outputs, no read request necessary. Subsequent words m ust be acce ssed by perf ormin g a fo rmal rea d

operation.

Following Master Reset, the level applied to the BE/FWFT

input to choose the desired timing mode must remain static

throughout th e FIFO operation.

Programming the Almost Empty and Almost Full Flags

Two registers in the CY7C480 XV25 are u sed to hol d the o ffset

values for the Almost Empty and Almost Full fl ags. The Port A

Almost Empty flag ( AE

) offset regis ter is l abeled X. The Port B

Almost Full flag (AF

) offset register is labeled Y. The index of

each regist er name corres ponds wit h preset val ues during th e

reset of a FIFO, programmed in parallel using t he FIFO’s Port

A data inputs, or programmed in serial using the Serial Data

(SD) input (see Table 2).

To load a FIFO’s Almost Empty flag and Al most Full f lag offset

registers with one of the three preset values listed in Table 2,

the Serial Program Mode (SPM

) and at least one of the

flag-select inputs must b e HIGH during the LO W -to-HIGH tr ansition of it s M aster Reset input (MR

). For example, to load the

preset value of 64 into X and Y, SPM

, FS0, and FS1 must be

HIGH when the FIFO reset (MR

) returns HI GH.

To program the X and Y register s from P ort A, perform a Master Reset with SPM

HIGH and FS0 and FS1 LOW during the

LOW -to-HIGH t ransitio n of MR

. After this reset is complete, the

first two writes to the FIFO do not store data in memory but

load the offset registers in the order Y and X. The Port A data

inputs used by the offset registers are (A

0–11

), (A

0–13

), or

(A

0–15

),for the CY7C48 0XV25, re spec tiv ely. The highest numbered input is used as the most significant bit of the binary

number in each case. Valid programming values for the registers range from 0 to 4095 for the CY7C4804V25; 0 to 16383

for t he CY7C4806V25; 0 to 65535 for the CY7C4808V25. Before programming the offset registers, FF

/IR is set HIGH.

FIFOs begin normal operati on after programmi ng is comple te.

Page 20

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

20

To program the X and Y registers serially, initiate a Master

Reset with SPM

LOW , FS0/SD LO W , and FS1/SEN HIGH dur-

ing the LOW -to-H IGH transit ion of MR

. After this reset is complete, the X and Y register values are loaded bit- wis e through

the FS0/SD input on each LOW-to-HIGH transition of CLKA

that the FS1/SEN

input is LOW. Twenty-four, twenty-eight or

thirty-two bit wri tes are needed to complete the programming.

The two regist ers are written in the order Y then finall y X. The

first-bit write stores the most significant bit of the Y regist er and

the last-bit write sto res the least significa nt bit of the X register .

When the option t o prog ra m the of fset re gisters seri ally i s ch osen, the Port A Full/Input Ready (FF

/IR) flag remains LOW

until all register bits are written. FF

/IR is set HIGH by the

LOW-to-HIGH transition of CLKA aft er the last bit is loaded to

allow normal FIFO operation.

SPM

, FS0/SD, and FS1/SEN function the same way in both

CY Standard and FWFT modes.

FIFO Write/Read Operation

The state of the Port A data (A

0–79

) lines is controlled by Port

A Chip Select (CSA

) and Output Enab le (OE). The A

0–79

lines

are in the high-impedance state when either CSA

or OE is

HIGH.

Data is loaded into the FIFO from the A

0–79

inputs on a

LOW-to-HIGH transition of CLKA when CSA

is LOW, ENA is

HIGH, and FF

/IR is HIGH (see Table 3). FIFO writes on Port A

are independent of any concurrent Port B operation.

The Port B control sign als are ident ical to those of P ort A. The

state of the Port B data (B

0–79

) lines is controlled by the Por t

B Chip Select (CSB

) and Output Enab le (OE). The B

0–79

lines

are in the high-impeda nce state when CSB

or OE is HIGH. The

B

0–79

lines are active outputs when CSB or OE is LOW.

Data i s transferred to the B

0–79

outputs by a LOW-to-HIGH

transition of CLKB when CSB

is LOW, OE is LOW, ENB is

HIGH, and EF

/OR is HIGH (see Ta bl e 4 ). FIFO reads and

writes on Port B are independent of any concurrent Port A

operation.

The set-up and hold t ime constraints to t he port cl ocks for the

port Chip Selects are only for enabling write and read operations and a re not r elat ed to hi gh-impe dance contr ol of the da ta

outputs. If a port enable is LOW during a cloc k cycle , the port’s

Chip Select may change sta tes during the set -up and ho ld t ime

window of the cycle.

When operating the FIFO in FWFT Mode and the Output

Ready flag is LOW, the next word wri tt en is automati cally sent

to the FI FO ’s output regis ter b y the LOW-to-HIGH transition of

CLKB, data residing in the FIFO’s memory array is clocked to

the output register only when a read is selected using the

port’s Chip Select, and Enable.

When operating t he FIFO i n CY Standar d Mode , data r esidi ng

in the FIFO’s memory array is clocked to the output register

only when a read is selected using the port’s Chip Select, and

Enable.

Synchronized FIFO Flags

Each FIFO is synchronized to its port clock through at least

two flip-f lop st ages . Thi s is done to impr o ve f lag- sig nal r eliabil ity by reducing the probability of the metastable events when

CLKA and CLKB operate asynchronously to one another.

EF

/OR and AE are synchronized to CLKA. FF/IR and AF are

synchroniz ed to CLKB . Table 5 shows the relationship of eac h

port flag to the FIFO.

Empty/Output Ready Flags (EF

/OR)

These are dual- purpose flags. In the FW FT Mode, the Output

Ready (OR) function is select ed. When the Ou tput Ready flag

is HIGH, ne w data is pr esent in t he FIFO output register . Whe n

the Output Ready flag is LOW, the previous data word is

present in the FIFO outp ut regi ster and at tempted FI FO read s

are ignored.

In the CY Standard Mode, the Empty Flag (EF

) function is

selected. When the Empty Flag is HIGH, data is available in

the FIFO’s memory for reading to the output register. When

Empty Flag is LOW, the previous data word is present in the

FIFO output register and attempted FIFO reads are ig nored.

The Empty/Output Ready flag of a FIFO is synchronized to

CLKB. For both the FWFT and CY Standard modes, the FIFO

read pointer is incremented each time a new word is clocked

to its output register. The state machine that controls an Output Ready fl ag m onitors a write pointer and read poin ter comparator tha t indicates when the FIFO status is empty , empty+1,

or empty+2.

In FWFT Mode, from the time a w ord is writt en to a FIFO , it ca n

be shifted to the FIFO output register in a minimum of three

cycles of CLKB. Therefore, the CLKB Output Ready flag is

LOW if a word i n memory is the next data to be sen t to the FIFO

output register and three cycles have not elapsed since the

time the wor d was written. The O utput Ready fla g of the FIFO

remains LOW until the third LOW-to-HIGH transition of CLKB

occurs, simultaneously forcing the Output Ready flag HIGH

and shifting the wor d to the FIFO output register.

In the CY Standard Mode , from the time a word is written to a

FIFO, the Empty flag will indicate the presence of data available for reading in a minimum of two cycles of CLKB. Therefore, an Empty fla g is LOW if a word in memory is the n ext data

to be sent to the FIFO output regis ter and two cycles have not

elapsed since the time the word was written. The Empty flag

of the FI FO rem ains LO W unt il the secon d L OW-to-HIGH transition of CLKB occurs, forcing the Empty flag HIGH; only then

can data be read.

A LOW-to-HIGH transition on the CLKB begins the first synchronization cycle of a write if the clock transition occurs at

time t

SKEW1

or greater after the write. Otherwise, the subse-

quent clock cycle can be the first synchronization cycle.

Full/Input Ready Flags (FF

/IR)

This is a dual-purpose flag. In FWFT Mode, the Input Ready

(IR) function is selected. In CY Standard Mode, the Full Flag

(FF

) function is selected. For both timing modes, when the

Full/Input Rea dy flag is HIGH, a memory l ocatio n is free i n the

memory to receive new data. No memory locations are free

when the Full/Input Ready flag is LOW and attempted writes

to the FIFO are ignored.

The Full/Input Ready flag of a FIFO is sync hronized to CLKA.

For both FWFT and CY Standard modes, each time a word is

written to a FIFO, its write pointer is incremented. The state

machine that c ontrols a Full/Input Ready flag monitors a write

pointer and read pointer comparator that indicates when the

FIFO mem or y statu s is full, full–1, or full–2. From the tim e a

word is read from a FIFO, its previous memory location is

ready to be written to in a minimum of two cycles CLKA. Therefore, a Full/Input Ready flag is LOW if less than two cycles of

Page 21

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

21

CLKA have elapsed since the next memory write location has

been read. The second LOW -to-HIGH tra nsition on CLKA after

the read sets the Full/Input Ready flag HIGH.

A LOW-to-HIGH transition on CLKA begins the first synchronization cycle of a read if the clock transition occurs at time

t

SKEW1

or greater after the read. Otherwise, the subsequent

clock cycle can be the first synchronization cycle.

Almost Empty Flags (AE

)

The Almost Empty flag of a FI FO is synchronized t o CLKB. The

state machine that controls an Almost Empty flag monitors a

write pointer and read pointer comparator that indicates when

the FIFO memory status is almost empty, almost empty+1, or

almost empty+2. The Almost Empty state is defined by the

contents of register X for AE

. These registers are loaded with

preset values during a FIFO reset, programmed from Port A,

or programmed serially (see Almost Empty flag and Almost

Full flag offset programming above). An Almost Empty flag is

LOW when its FIFO contains X or less words and is HIGH

when its FIFO contains (X+1) or more words. A data word

present in the FIFO output register has been read from memory.

Two LOW-to-HIGH transitions of CLKB are required after a

FIFO write for its Almost Empty flag to re fl ect the new level of

fill. Therefore, the Alm o st Full flag of a FI F O con ta i ni ng ( X +1)

or more words remains LOW if two cycles of CLKB have not

elapsed since the write that filled the memory to the (X+1)

level. An Almost Empty flag is set HIGH by the second

LOW-to-HIGH transition of CLKB after the FIFO write that fills

memory to the (X+1) l e v el . A LO W - to-HIG H tr ansition of CLKB

begins the firs t synch ronization c ycle if i t occurs a t time t

SKEW2

or greater after the write that fills the FIFO to (X+1) words.

Otherwise, the subsequent synchronizing clock cycle may be

the first synchronization cycle.

Almost Full Flags (AF

)

The Almost Full flag of a FIFO is synchronized to CLKA. The

state machine that co ntrols a n Almost Fu ll fl ag monitor s a write

pointer and read pointer comparator that indicates when the

FIFO memory status is almost full, almost full–1, or almost

full–2. The Almost Full state is de fined by the conten ts of register Y for AF

. These registers are loaded with preset values

during a FIFO reset, pr ogrammed fro m Port A, or pr ogrammed

serially (see Almost Empty flag and Al most Full fla g offs et pr ogramming above). An Almost Full flag is LOW when the number of words in its FIFO is greater than or equal to (4096–Y),

(16384–Y), or (65536–Y), for the CY7C480XV25 res pecti vel y.

An Almost Full flag is HIGH when the number of words in its

FIFO is less than or equal to [4096–(Y+ 1)] , [16384–(Y+1)], or

[65536–(Y+1)], f or the CY7C480XV25 respectively.

Two LOW-to-HIGH transitions of CLKA are required after a

FIFO read for it s Almost Full flag to r efl ect the new le vel of fill.

Therefore, the Almost Full flag of a FIFO containing

[4096/16384/65536–(Y+1)] or less wor ds re m a in s LOW if two

cycles of CLKA have not elapsed since the read that reduced

the number of words in memory to

[4096/16384/65536–(Y+1)]. An Almost Full flag is set HIGH by

the second LOW-to-HIGH transition of CLKA after the FIFO

read that reduces the number of words in memory to

[4096/16384/65536–(Y+1)]. A LOW-to-HIGH transition of

CLKA begins the first synchronization cy cle if it occurs at time

t

SKEW2

or greater after the read that reduces the number of

words in memory to [4096/16384/65536–(Y+1)]. Otherwise,

the subsequent s ynchronizi ng clock cycle ma y be the first synchronizati on cycle.

Bus Sizing

Both Port A and Por t B buses can be configured in an 80-bit

long-word, 40-bi t word , 20-bi t short word or 10- bit b yte f ormat.

The levels applied to Bus Size Select (SIZE1A, SIZE2A,

SIZE1B, SIZE2B) determine the bus size. Bus size on either

port can be set independent of each ot her. These levels should

be static throughout FIFO operation. Both bus size selections

are implemented at the completion of Master Reset, by the

time the Full/I nput Ready flag is set HIGH.

Only 80-bit long-word data is written to or read from the two

FIFO memories. Bus-matchin g opera tions are done bef ore the

data is written into the memory (for Port A) and after (for Por t

B) data is re ad from the memory.

Bus-Matching FIFO Reads

Data is read from the FI FO memo ry in 80-bit long-word increments. If a long- word b us siz e is i mple mented, t he enti re l ongword immediately shifts to the FIFO output register. If byte or

word size is implemented on Port B, only the first one or two

bytes appear on the sel ect ed portion of the FIFO output register, with the rest of the long-word stored in auxiliary registers.

In this case, subsequent FIFO reads output the rest of the

long-word to the FIFO output register.

When reading data from the FIFO in the byte, short word, or

word format, the unused outputs are zero.

Retrans m i t (RT

)

The retransmit feature is beneficial when transferring packets

of data. It enables the receipt of data to be acknowledged by

the receiv er and retransmitted if necessary.

The retransmit feature is intended for use when a number of

writes equal to or less than the depth of the FIFO have occurred and at least one word has been read since the last reset

cycle. A LOW pulse on RT

resets the internal read pointer to

the first ph ysical loca tion of the FIFO. CLKA and CLKB ma y be

free running but ENB must be deasserted during and t

RTR

after

the retr ansm it pulse. Wit h every v alid read cycle after retransmit, previously accessed data is read and the read pointer is

incremented u ntil it is equal to t he writ e point er . Flags are go verned by the relative locations of the read and write pointers

and are updated during a retransmit cycle. Data written to the

FIFO after activation of RT

are transmitted al so . The full depth

of the FIFO can be repeatedly retransmitted.

Page 22

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

22

T able 1. Endian/Bus Matching Configuration

[29]

Each character (“A”, “B”,..., “H”) repr ese n ts 10-b it d a ta

BE/FWFT Size 1A Size 2A Port A Size 1B Size 2B Port B bit#79 bit#0

1 0 0 x80 0 0 x80 Write to FIFO ABCDE FGH

Read from FIFO ABCDEFGH

0 1 x40 Read from FIFO ABCD

EFGH

1 0 x20 Read from FIFO AB

CD

EF

GH

1 1 x10 Read from FIFO A

B

C

D

E

F

G

H

0 1 x40 0 0 x80 Write to FIFO ABCD

EFGH

Read from FIFO ABCDEFGH

0 1 x40 Read from FIFO ABCD

EFGH

1 0 x20 Read from FIFO AB

CD

EF

GH

1 1 x10 Read from FIFO A

B

C

D

E

F

G

H

Note:

29. BE is selected at Master Reset; SIZE1A, SIZE2A, SIZE1B AND SIZE2B must be static throughout device operation.

Page 23

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

23

1 0 x20 0 0 x80 Write to FIFO AB

CD

EF

GF

Read from FIFO ABCDEFGH

0 1 x40 Read from FIFO ABCD

EFGH

1 0 x20 Read from FIFO AB

CD

EF

GH

1 1 x10 Read from FIFO A

B

C

D

E

F

G

H

T able 1. Endian/Bus Matching Configuration

[29]

Each character (“A”, “B”,..., “H”) repr ese n ts 10-b it d a ta

BE/FWFT Size 1A Size 2A Port A Size 1B Size 2B Port B bit#79 bit#0

Page 24

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

24

1 1 1 x10 0 0 x80 Write to FIFO A

B

C

D

E

F

G

H

Read from FIFO ABCDEFGH

0 1 x40 Read from FIFO ABCD

EFGH

1 0 x20 Read from FIFO AB

CD

EF

GH

1 1 x10 Read from FIFO A

B

C

D

E

F

G

H

T able 1. Endian/Bus Matching Configuration

[29]

Each character (“A”, “B”,..., “H”) repr ese n ts 10-b it d a ta

BE/FWFT Size 1A Size 2A Port A Size 1B Size 2B Port B bit#79 bit#0

Page 25

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

25

0 0 0 x80 0 0 x80 Write to FIFO ABCDE FGH

Read from FIFO ABCDEFGH

0 1 x40 Read from FIFO EFGH

ABCD

1 0 x20 Read from FIFO GH

EF

CD

AB

1 1 x10 Read from FIFO H

G

F

E

D

C

B

A

0 1 x40 0 0 x80 Write to FIFO ABCD

EFGH

Read from FIFO EFGHABCD

0 1 x40 Read from FIFO ABCD

EFGH

1 0 x20 Read from FIFO CD

AB

GH

EF

1 1 x10 Read from FIFO D

C

B

A

H

G

F

E

T able 1. Endian/Bus Matching Configuration

[29]

Each character (“A”, “B”,..., “H”) repr ese n ts 10-b it d a ta

BE/FWFT Size 1A Size 2A Port A Size 1B Size 2B Port B bit#79 bit#0

Page 26

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

26

0 1 0 x20 0 0 x80 Write to FIFO AB

CD

EF

GH

Read from FIFO GH EF CD AB

0 1 x40 Read from FIFO CDAB

GHEF

1 0 x20 Read from FIFO AB

CD

EF

GH

1 1 x10 Read from FIFO B

A

D

C

F

E

H

G

1 1 x10 0 0 x80 Write to FIFO A

B

C

D

E

F

G

H

Read from FIFO HGFEDCBA

0 1 x40 Read from FIFO DCBA

HGFE

1 0 x20 Read from FIFO BA

DC

FE

HG

T able 1. Endian/Bus Matching Configuration

[29]

Each character (“A”, “B”,..., “H”) repr ese n ts 10-b it d a ta

BE/FWFT Size 1A Size 2A Port A Size 1B Size 2B Port B bit#79 bit#0

Page 27

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

27

0 1 1 x10 1 1 x10 Read from FIFO A

B

C

D

E

F

G

H

T able 1. Endian/Bus Matching Configuration

[29]

Each character (“A”, “B”,..., “H”) repr ese n ts 10-b it d a ta

BE/FWFT Size 1A Size 2A Port A Size 1B Size 2B Port B bit#79 bit#0

Page 28

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

28

..able

T able 2. Flag Programming

SPM FS1/SEN FS0/SD MR X and Y Registers

[30]

H H H

↑

64

H H L

↑

16

H L H

↑

8

H L L

↑

Par allel programming via Port A

L H L

↑

Serial programming via SD

L H H

↑

Reserved

L L H

↑

Reserved

L L L

↑

Reserved

T able 3. Port A Enable Function

CSA

ENA CLKA A

0–79

Inputs Port Function

H X X In high-impedance state None

L L X In high-impedance state None

LH ↑ In high- impedance state FIFO write

T able 4. Port B Enable Function

CSB

ENB CLKB B

0–79

Inputs Port Function

H X X In high-impedance state None

L L X Active, FIFO output regist er None

LH ↑ Active, FIFO output register FIFO read

T able 5. FIFO Flag Operation (CY Standard and FWFT Modes)

Number of Words in FIFO Memory

[31, 32, 33, 34 ]

Synchronized to CLKB Synchronized to CLKA

CY7C4804V25 CY7C4806V25 CY7C4808V25 EF/OR AE AF FF/IR

0 0 0 L L H H

1 TO X 1 TO X 1 TO X H L H H

(X+1) to

[4096–(Y+1)]

(X+1) to

[16834–(Y+1)]

(X+1) to

[65536–(Y+1)]

H H H H

(4096–Y1) to 4095 (16384–Y1) to

16383

(65536–Y1) to

65535

H H L H

4096 16384 65536 H H L L

Notes:

30. X register holds the offset for AE

; Y register holds the offset for AF.

31. X is the Almost Empty offset for FIFO used by AE. Y is the Almost Full offset for FIFO used by AF. Both X and Y are selected during a FIFO reset or Port A

programming.

32. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

33. Data in the output register does not count as a “word in FIFO memory”. Since in FWFT Mode, the first word written to an empty FIFO goes unrequested to

the output register (no read operation necessary), it is not included in the FIFO memory count.

34. The OR and IR functions are active during FWFT mode; the EF

and FF functions are active in CY Standard Mode.

Page 29

CY7C4808V25

CY7C4806V25

CY7C4804V25PRELIMINARY

29

Shaded areas contain advance information.

Document #: 38-00874-D

2.5V 64K x80 Unidirectional Synchronous FIFO w/bus matching

Speed

(MHz) Ordering Code

Package

Name

Package

Type

Operating

Range

166 CY7C4808V25-166BBC BB288 288-Ball Grid Array (1.0 mm pitch, 19x19mm) Commercial

200 CY7C4808V25-200BBC

200 CY7C4808V25-200BBI BB288 288-Ball Grid Array (1.0 mm pitch, 19x19mm) Industrial

2.5V 16K x80 Unidirectional Synchronous FIFO w/bus matching

Speed

(MHz) Ordering Code

Package

Name

Package

Type

Operating

Range

166 CY7C4806V25-166BBC BB288 288-Ball Grid Array (1.0 mm pitch, 19x19mm) Commercial

200 CY7C4806V25-200BBC

2.5V 4K x80 Unidirectional Synchronous FIFO w/bus matching

Speed

(MHz)

Ordering Code

Package

Name

Package

Type

Operating

Range

166 CY7C4804V25-166BBC BB288 288-Ball Grid Array (1. 0 mm pi tch, 19x19mm) Commercial

200 CY7C4804V25-200BBC BB288 Commercial

Page 30

CY7C4808V25

CY7C4806V25

CY7C4804V25

PRELIMINARY

© Cypress Semiconductor Corporation, 2000. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it con vey or imply any license under patent or other rights. Cypress Semiconductor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

Package Diagram

288-Ball Grid Array (1.0 pitch, 19 x 19 mm) BB288

51-85129

Loading...

Loading...