Page 1

CS4222

20-Bit Stereo Audio Codec with Volume Control

Features

l

99 dB 20-bit A/D Converters

l

99 dB 20-bit D/A Converters

l

110 dB DAC Signal-to-Noise Ratio (EIAJ)

l

Analog Volume Control

- 0.5 dB Step Resolution

- 113.5 dB Attenuation

l

Soft Mute Capability

l

Differential Inputs/Outputs

l

On-chip Anti-aliasing and Output Smoothing

Filters

l

De-emphasis for 32, 44.1 and 48 kHz

l

Stand-Alone or Control Port Mode

l

Single +5 V power supply

I

Description

The CS4222 is a highly integrated, high performance,

20-bit, audio codec providing stereo analog-to-digital

and stereo digital-to-analog converters using delta-sigma conversion techniques. The device operates from a

single +5 V power supply, and features low power consumption. Selecta ble de- emphasis fil ter for 32, 44.1, and

48 kHz sample rates is also included.

The CS4222 also incl udes an analog volume control capable of 113.5 dB attenuation in 0.5 dB resolution. The

analog volume control architecture preserves dynamic

range during attenuation. Volume control changes are

implemented using a "soft" ramping or zero crossing

technique.

Applications include reverb processors, musical instruments, DAT, and multitrack recorders.

The CS4222 is packaged in a 28-pin plastic SSOP.

ORDERING INFORMATION

CS4222-KS -10° to +70° C 28-pin SSOP

CDB4222 Evaluation Board

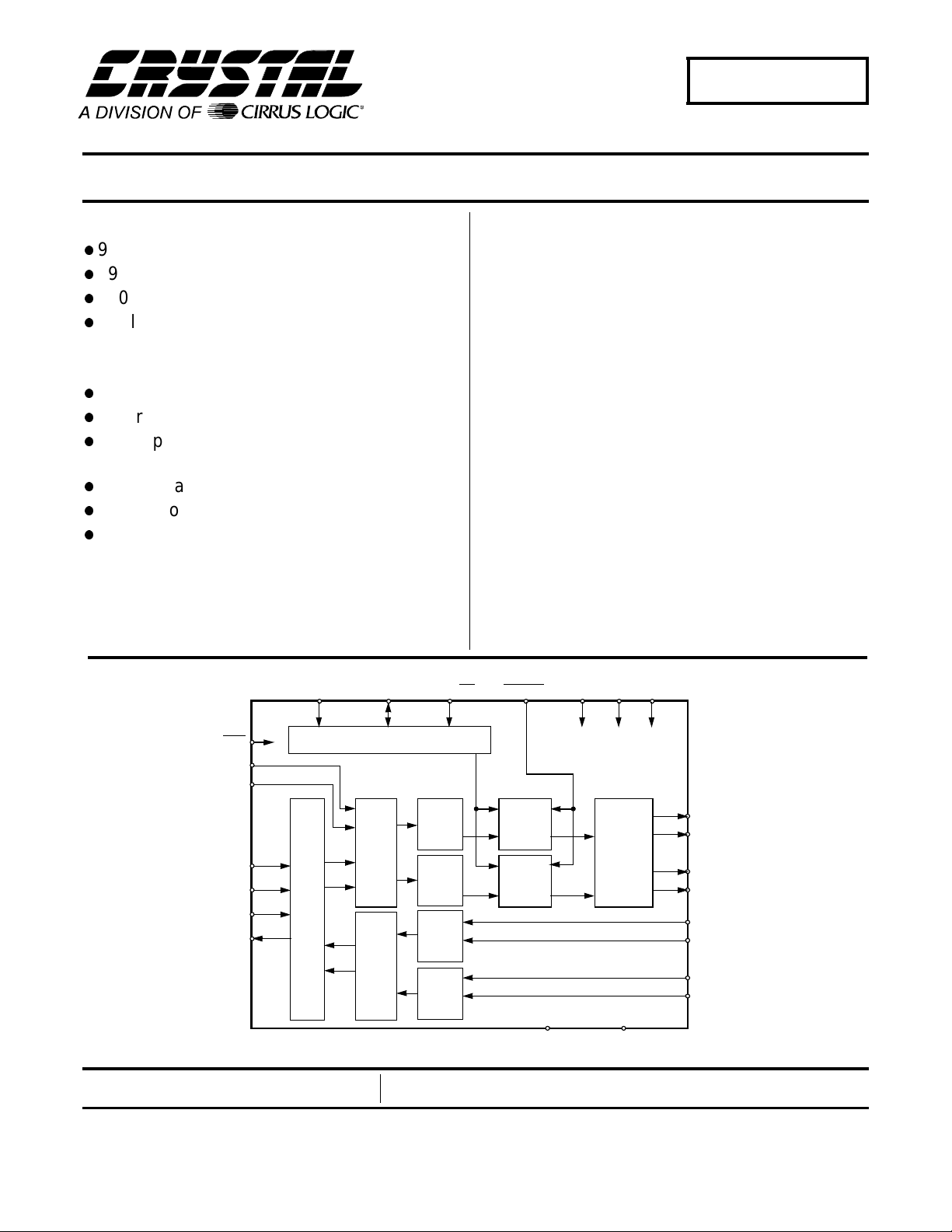

SCL/CCLK

RST

DEM1

DEM0

LRCK

SCLK

SDIN

SDOUT

Serial Audio Da ta Interface

Preliminary Product Information

Cirrus Logic, Inc.

Crystal Semiconductor Products Division

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.crystal.com

SDA/CDIN AD0/CS

Control Port

Left

DAC

Digital Filters

Digital Filters

Right

with De-Emphas i s

DAC

Left

ADC

Right

ADC

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

SMUTE VD

Volume

Control

Volume

Control

Copyright Cirrus Logic, I nc. 1997

(All Rights Reserv ed)

MCLK VA

DGND

Pass and

Analog Low

AGND

Output Stage

AOUTL+

AOUTL-

AOUTR+

AOUTR-

AINLAINL+

AINRAINR+

JAN ‘97

DS236PP3

1

Page 2

CS4222

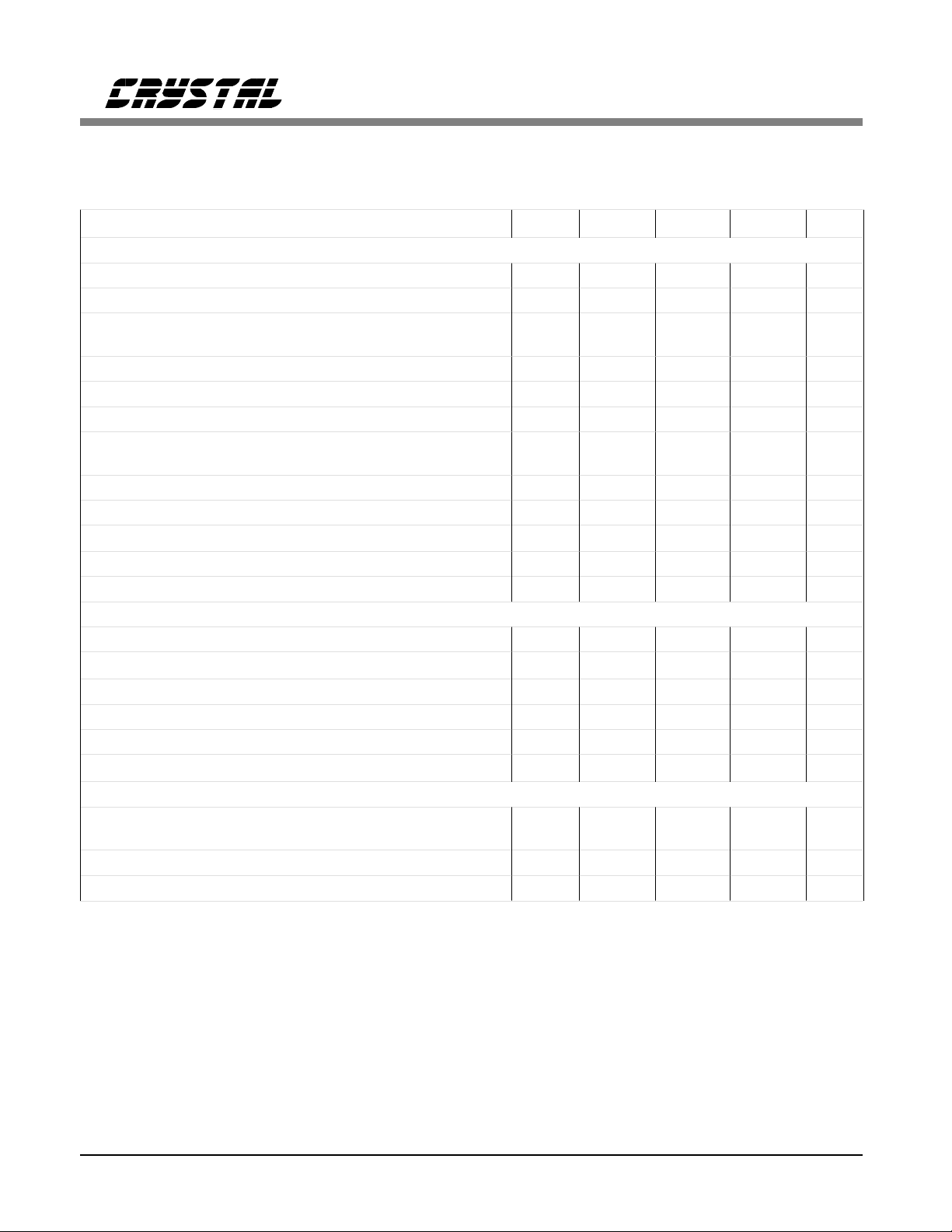

ANALOG CHARACTERISTICS

( TA = 25°C; VA, VD = +5V; Full Scale Input Sine wave,

997 Hz; Fs = 48 kHz; Measurement Bandwidth is 20 Hz to 20 kHz; Local components as shown in "Recommended Connection Diagram"; SPI mode, Format 0, unless otherwise specified.)

Parameter Symbol Min Typ Max Uni ts

Analog Input Characteristics

ADC Resolution - - 20 Bits

Total Harmonic Distortion THD 0.003 - %

Dynamic Range (A-weighted):

(unweighted):

TBD

TBD

99

96

-

-

dB

dB

Total Harmonic Distortion + Noise -1 dB (Note 1) THD+N - -90 TBD dB

Interchannel Isolation (1 kHz) - 90 - dB

Interchannel Gain Mismatch - 0.1 - dB

Offset Error (with High Pass Filter)

(HPF defeated with CAL)

-

-

-

TBD

0

-

LSB

LSB

Full Scale Input Voltage (Differential) 1.9 2.0 2.1 Vrms

Gain Drift - 100 - ppm/°C

Input Resistance 10 - -

kΩ

Input Capacitance - - 15 pF

Common Mode Input Voltage - 2.3 - V

A/D De ci mati on F ilt er C harac te rist ic s

Passband (Note 2) 0 - 21.8 kHz

Passband Ripple - -

±0.01

dB

Stopb and (Note 2) 30 - 6114 kHz

Stopb and Att enu ati on (Note 3) 80 - - dB

Group Delay (Fs = Output Sample Rate) (Note 4) t

Group Delay Variation vs. Frequency

∆ t

gd

gd

-15/Fs- s

--0

µs

High Pass Filter Characteristics

Frequency Response: -3 dB (Note 2)

-0.1 dB

-

-

3.7

20

-

-

Hz

Hz

Phase Dev iat ion @ 20 Hz (Note 2) - 10 - De gree

Passband Ripple - - 0 dB

Notes: 1. Referenced to typical full-scale differential input voltage (2 Vrms)

2. Filter characteristics scale with output sample rate. For output sample rates, Fs, other than 48 kHz,

the 0.01 dB passband edge is 0.4535xFs and the stopband edge is 0.625xFs.

3. The analog modulator samples the input at 6.144 MHz for an Fs equal to 48 kHz. There is

no rejection of input signals which are multiples of the sampling frequency ( n x 6.144 MHz ±21.8 kHz

where n = 0,1, 2, 3.. .).

4. Group delay for Fs = 48 kHz, t

= 15/48 kHz = 312µs

gd

* Parame ter de finit ions ar e give n at the end of thi s data s heet.

Specifications are subject to change without notice.

2 DS236PP3

Page 3

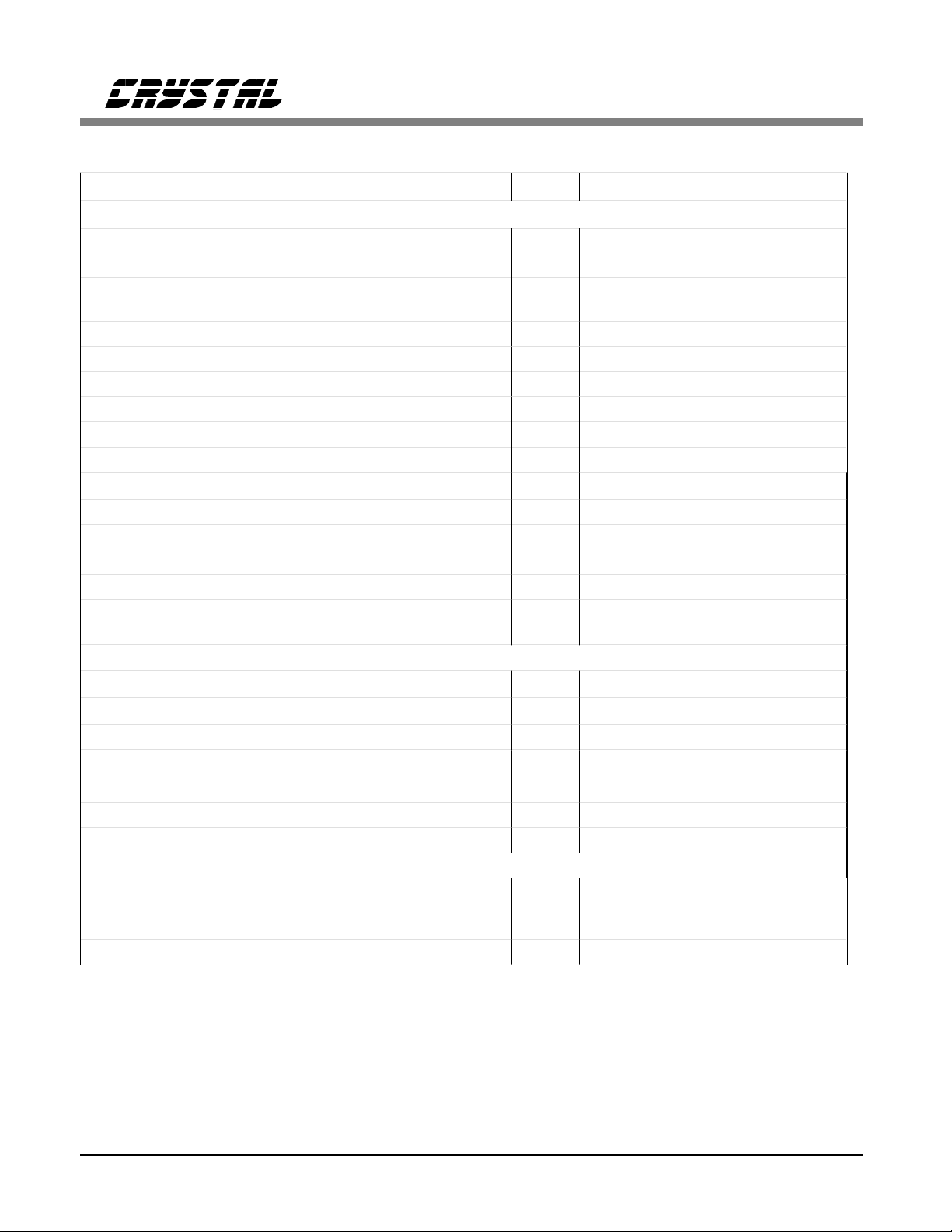

ANALOG CHARACTERISTICS (Continued)

Parameter Symbol Min Typ Max Units

CS4222

Analog Output Characteristics

DAC Resolution - - 20 Bits

Signal-to-Noise, Idle- Channel Noise ( DAC muted, A-weighted) TBD 110 - dB

Dynamic Range (DAC not muted, A-weighted)

Total Harmonic Distortion THD - 0.003 - %

Total Harmonic Distortion + Noise THD+N - -88 TBD dB

Interchannel Isolation (1kHz) - 90 - dB

Interchannel Gain Mismatch - 0.1 - dB

Attenuation Step Size (All Outputs) 0.35 0.5 0.65 dB

Programmable Output Attenuation Span 110 113.5 - dB

Differential Offset Voltage -

Common Mode Ou tput Vo lta ge - 2.3 - V

Full Scale Output Voltage 1.9 2.0 2.1 Vrms

Gain Drift - 100 - ppm/°C

Out-of-Band Energy (Fs/2 to 2Fs) - -60 - dBFS

Analog Output Load Resistance:

- Minimum Attenuation, 10 kΩ, 100 pF load; unless otherwise specified.

(DAC not muted, unweighted)

Capacitance:

TBD

TBD

10

-

99

96

±10

-

-

-

-

-mV

-

100

dB

dB

kΩ

pF

Combined Digital and Analog Filter Characteristics

Frequency Response 10 Hz to 20 kHz Deviation from Linear Phase Passband: to 0.01 dB corner (Notes 5,6) 0 - 21.8 kHz

Passband Ripple (Note 6) - Stopband (Notes 5,6) 26.2 - - kHz

Stopband Attenuation (Notes 7) 70 - - dB

Group Delay (Fs = Input Word Rate) t

gd

-16 / Fs- s

±0.1

±0.5

-dB

- Degrees

±0.01

dB

Power Supply

Power Supply Current VA

VD

Total Power Down

Power Supply Rejection Ratio (1 kHz, 10 mV

Notes: 5. The passband and stopband edges scale with frequency. For input word rates, Fs, other than

48 kHz, the 0.01 dB passband edge is 0.4535xFs and the stopband edge is 0.5465xFs.

6. Digital filter characteristics .

7. Measurement bandwidth is 10Hz to 3Fs.

)-50-dB

rms

-

-

-

30

20

0.2

TBD

TBD

-

mA

mA

mA

Specifications are subject to change without notice

DS236PP3 3

Page 4

CS4222

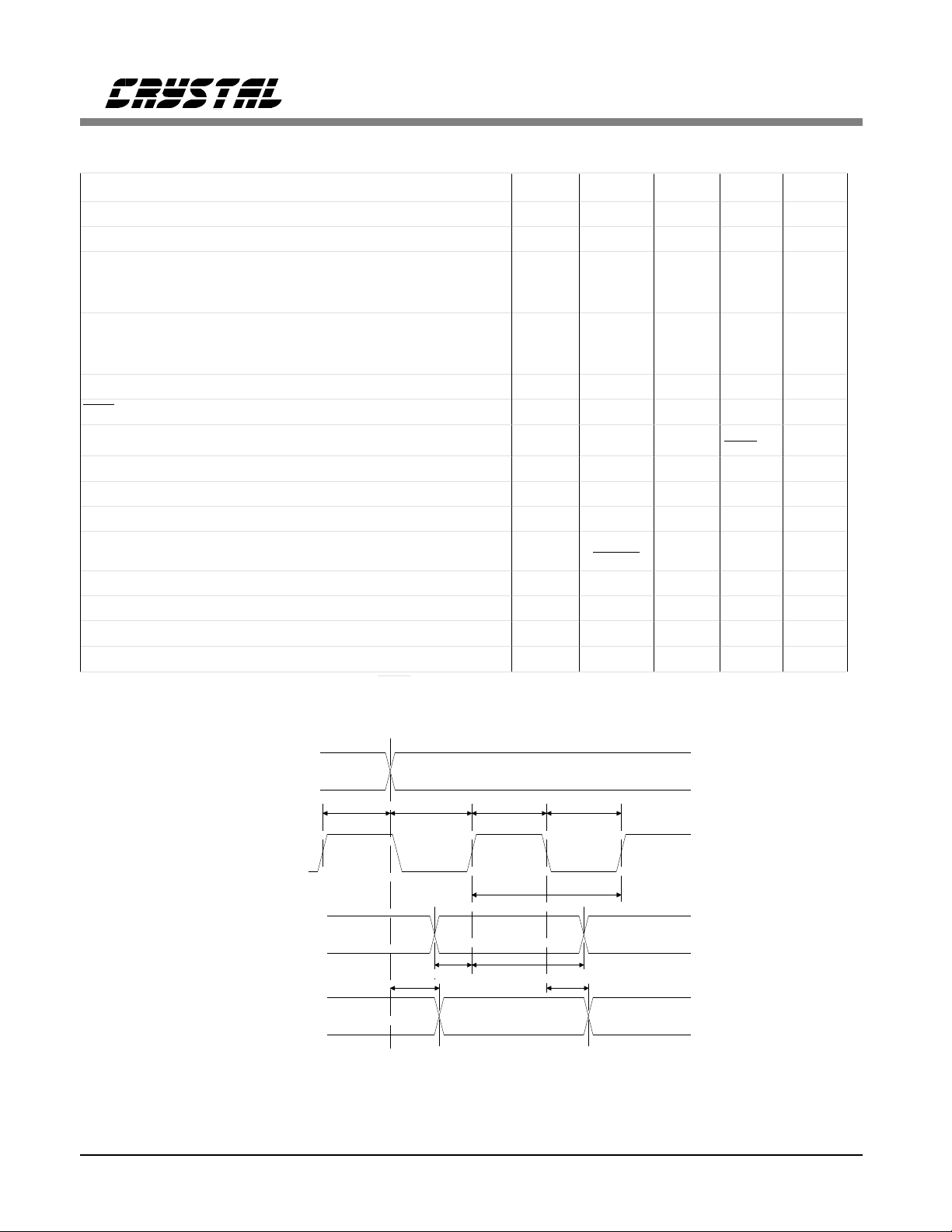

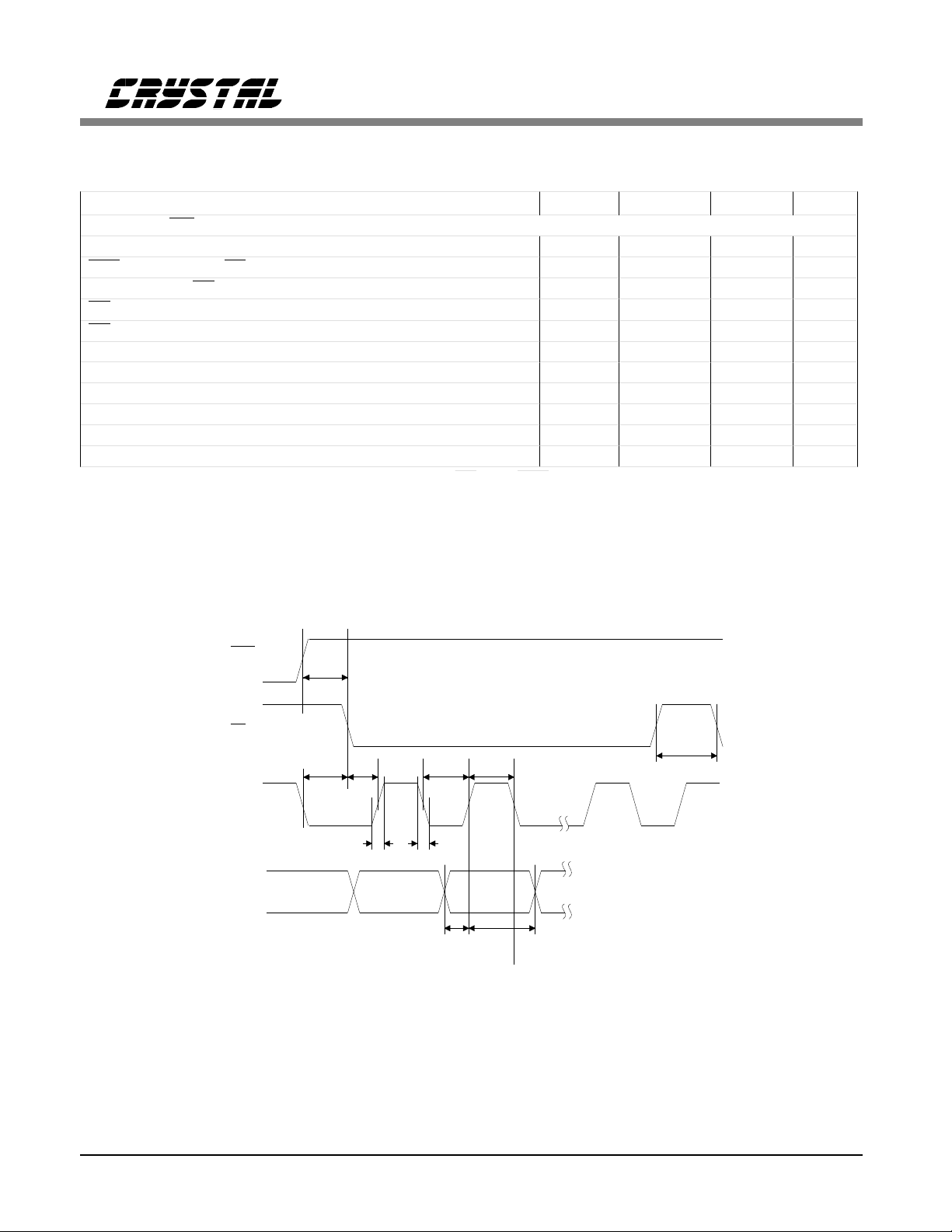

SWITCHING CHARACTERISTICS

(TA = 25°C; VA, VD = +5V ±5%, outputs loaded with 30pF)

Parameter Symbol Min Typ Max Units

Audio ADC’s & DAC’s Sample Rate Fs 4 - 50 kHz

MCLK Frequency (MCLK = 256, 384, or 512 Fs) 1.024 - 26 MHz

MCLK Pulse Width High MCLK = 512 Fs

MCLK = 384 Fs

MCLK = 256 Fs

MCLK Pulse Width Low MCLK = 512 Fs

MCLK = 384 Fs

MCLK = 256 Fs

10

21

31

10

21

31

-

-

-

-

-

-

-

-

-

-

-

-

ns

ns

ns

ns

ns

ns

MCLK Jitter Tolerance - 500 - ps RMS

RST Lo w Ti me (Note 8) 10 - - ms

SCLK Falling edge to SDOUT output valid (DSCK=0 ) t

LRCK edge to MSB valid t

SDIN Setup Time Before SCLK Rising Edge (DSCK=0) t

SDIN Hold Time After SCLK Rising Edge (DSCK=0) t

SCLK Period t

SCLK High Time t

SCLK Low Time t

SCLK Rising to LRCK Edge (DSCK=0) t

LRCK Edge to SCLK Rising (DSCK=0) t

dpd

lrpd

ds

dh

sckw

sckh

sckl

lrckd

lrcks

--

- - 25 ns

- - 25 ns

- - 25 ns

1

(128) Fs

--ns

40 - - ns

40 - - ns

20 - - ns

40 - - ns

1

(384)

Fs

+ 20 ns

Notes: 8. After powering up the CS4222, PDN should be held low for 10 ms to allow the power supply

to settle.

LRCK

t

lrckd

SCLK*

SDIN

SDOUT

*SCLK shown for DSCK = 0, SCLK inve rt ed f or DSCK = 1.

t

lrpd

t

lrcks

t

ds

t

sckh

t

dh

MSB

t

sckw

t

sckl

t

dpd

MSB-1

Serial Audio Port Data I/O timing

4 DS236PP3

Page 5

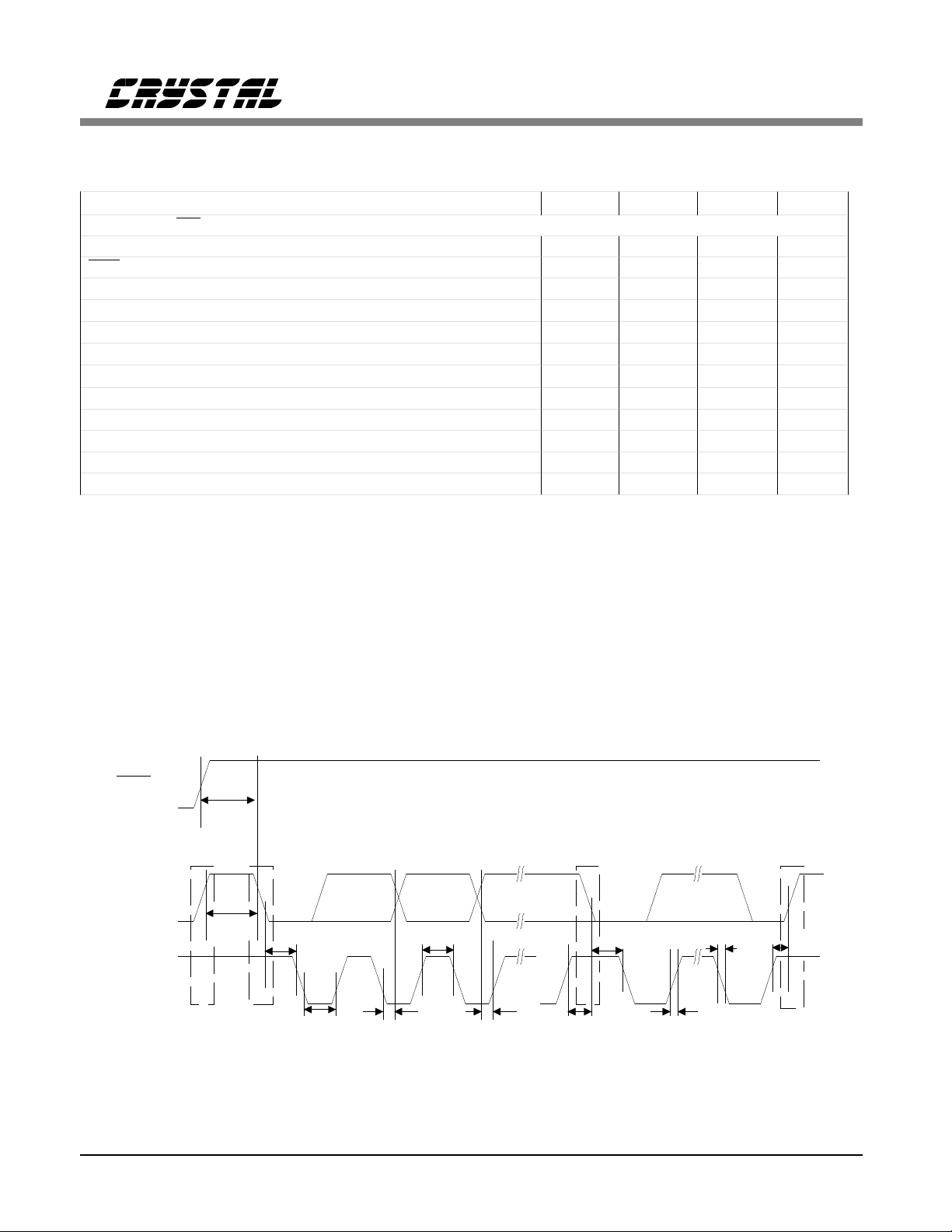

SWITCHING CHARACTERISTICS - CONTROL PORT

(TA = 25°C VD, VA = 5V±5%; I nputs: logic 0 = DGND, logic 1 = VD, CL = 30pF)

Parameter Symbol Min Max Units

SPI Mode (SPI/I2C = 0)

CCLK Clock Frequency f

RST rising edge to CS falling t

CCLK edge to

CS falling (Note 9) t

CS High Time Between Transmissions t

CS Falling to CCLK Edge t

CCLK Low Time t

CCLK High Time t

CDIN to CCLK Rising Setup Time t

CCLK Rising to DATA Hold Time (Note 10) t

Rise Time of CCLK and CDIN (Note 11) t

Fall Time of CCLK and CDIN (Note 11) t

Notes: 9. t

only needed before first falling e dge of CS a fter RST rising edge.

spi

= 0 at all other times.

t

spi

10. Data must be held for sufficient time to bridge the transition time of CCLK.

11. For F

< 1 MHz

SCK

sck

srs

spi

csh

css

scl

sch

dsu

dh

r2

f2

CS4222

-6MHz

500 - ns

500 - ns

1.0 20 - ns

66 - ns

66 - ns

40 - ns

15 - ns

- 100 ns

- 100 ns

µs

RST

CS

CCLK

CDIN

t

t

srs

spi

t

t

r2

css

t

scl

t

t

f2

dsu

t

sch

t

dh

t

csh

DS236PP3 5

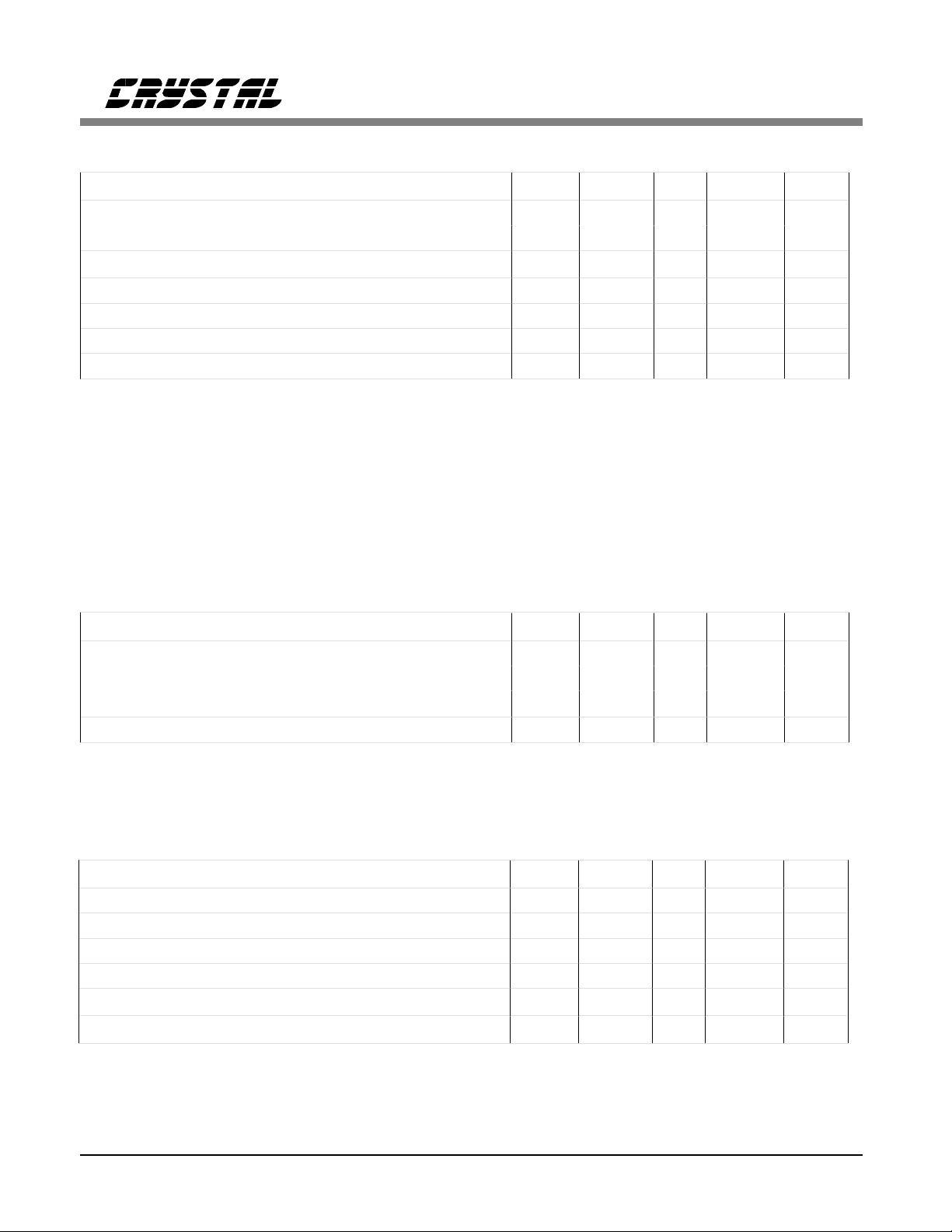

Page 6

SWITCHING CHARACTERISTICS - CONTROL PORT

(TA = 25°C; VD, VA = 5V±5%; Inputs: logic 0 = DGND, logic 1 = VD, CL = 30pF)

Parameter Symbol Min Max Units

I2C® Mode (SPI/I2C = 1) (Note 12 )

SCL Clock Frequency f

RST Rising Edge to Start t

Bus Free Time Between Transmissions t

Start Condition Hold Time (prio r to first clock pulse) t

Clock Low Time t

Clock High Time t

Setup Time for Repeated Start Condition t

SDA Hold Time from SCL Falling (Note 13) t

SDA Setup Time to SCL Rising t

Rise Time of Both SDA and SCL Lines t

Fall Time of Both SDA and SCL Lines t

Setup Time for Stop Condition t

2C®

Notes: 12. Use of the I

2C®

is a registered trad emark of Philips Semicon ductors.

I

bus interface requires a license f rom Philips.

13. Data must be held for sufficient time to bridge the 300ns transition time of SCL.

scl

irs

buf

hdst

low

high

sust

hdd

sud

r

f

susp

CS4222

- 100 kHz

500 - ns

4.7 -

4.0 -

4.7 -

4.0 -

4.7 0-

250 - ns

-1

- 300 ns

4.7

µs

µs

µs

µs

µs

µs

µs

µs

RST

t

irs

Repeated

Stop

Start

Start

Stop

SDA

t

buf

t

hdst

t

high

t

hdst

t

f

t

susp

SCL

t

low

t

hdd

t

sud

t

sust

t

r

6 DS236PP3

Page 7

CS4222

ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0V, all voltages with respect to 0V.)

Parameter Symbol Min Typ Max Units

Power Supplies Digital VD -0 .3 - 6.0 V

Analog VA -0.3 - 6.0 V

Input Current (Note 14) - -

±10

Analog Input Voltage (Note 15) -0.7 - VA+0.7 V

Digital Input Voltage (Note 15) -0.7 - VD+0.7 V

Ambient Temperature (Power Applied) -55 - +125 °C

Storage Temperature -65 - +150 °C

Warning: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Note: 14. Any pin except supplies. Transient currents of up to ±100mA on the analog input pins will

not cause SCR latch-up.

15. The maximum over or under voltage is limited by the input current.

mA

RECOMMENDED OPERATING CONDITIONS ( AGND, DGND = 0V, all voltages with respect

to 0V.)

Parameter Symbol Min Typ Max Units

Power Supplies Digital VD 4.75 5.0 5.25 V

Analog VA 4.75 5.0 5.25 V

VA - VD

Operating Ambient Temperature T

A

--0.4V

-10 25 70 °C

DIGITAL CHARACTERISTICS (TA = 25 °C; VA, VD = 5V ± 5%)

Parameter Symbol Min Typ Max Units

High-level Input Voltage V

Low-level Input Voltage V

High-level Output Voltage at I

Low-level Output Voltage at I

= -2.0 mA V

0

= 2.0 mA V

0

IH

IL

OH

OL

Input Leakage Current (Digital Inputs) - - 10

Output Leakage Current (High Impedance Digital Outputs) - - 10

2.8 - VD+0 .3 V

-0.3 - 1. 0 V

VD-1.0 - - V

--0.4V

µA

µA

DS236PP3 7

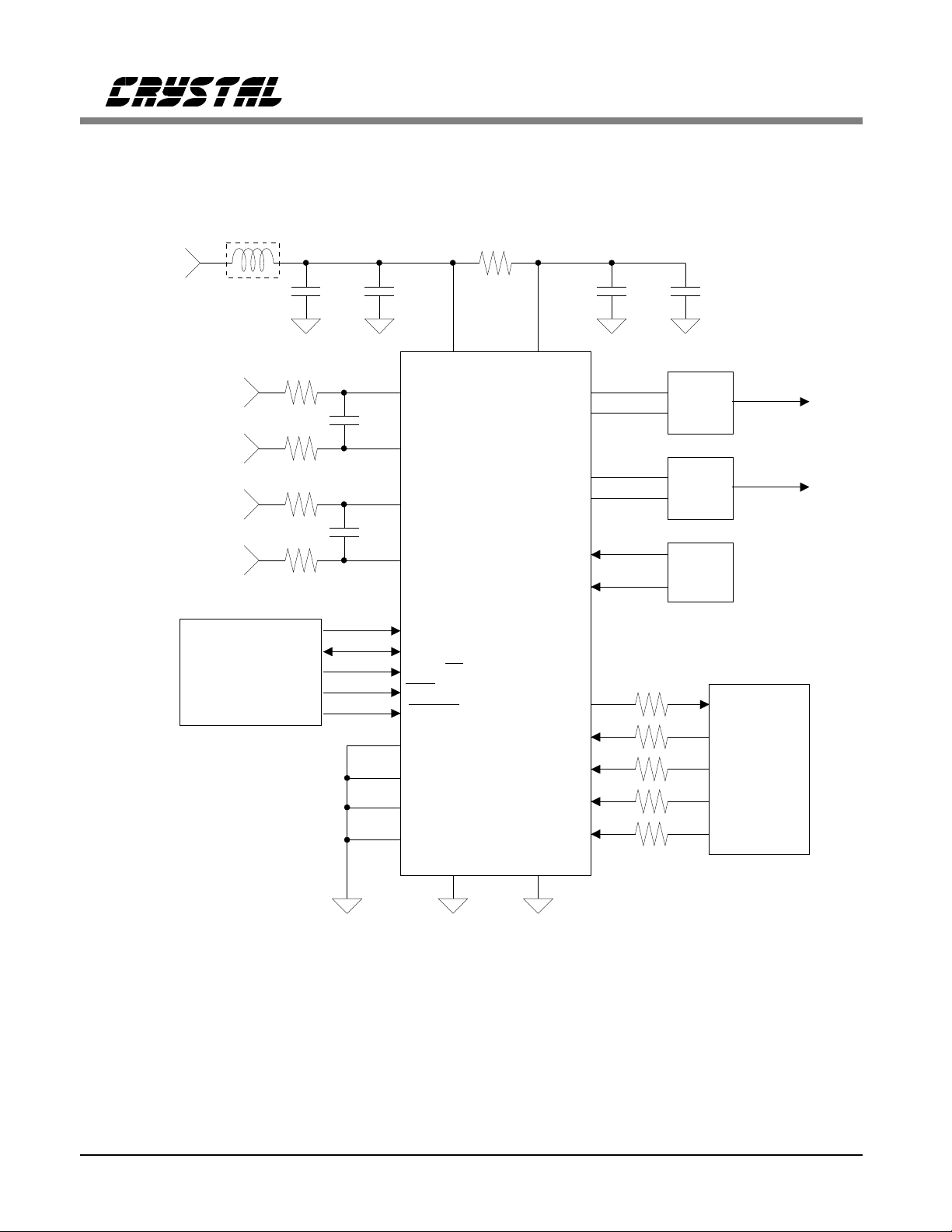

Page 8

CS4222

Ferrite Bead

+5V

Supply

150

150

150

150

Microcontroller

Note: Pins 10,11, and 12

should be tied to DGND

in stand -a lo ne mode.

+ 0.1 µF

1 µF

Ω

20

AINL+

2.2 nF

Ω

19

AINL-

Ω

17

AINR+

2.2 nF

Ω

16

AINR-

10

SCL/CCLK

11

SDA/CDIN

12

AD0/CS

27

RST

2

SMUTE

1

NC

14

NC

15

NC

28

NC

Ω

2

21

VA

6

VD

AOUTL+

AOUTL-

AOUTR+

AOUTR-

CS4222

DEM1

DEM0

SDOUT

LRCK

SCLK

MCLK

AGND DGND

22 7

SDIN

0.1 µF + 1 µF

25

26

24

23

18

13

8

9

4

5

3

Analog

Filter

Analog

Filter

Digital

Audio

Source

R

s

R

s

R

s

R

s

R

s

Audio

DSP

1

R = 500

s

R = 50

s

1

Ω

Ω

Figure 1. Recommended Connecti on Diagra m

(Also see reco mmen ded l ayo ut d iag ram, Fi gure 10)

8 DS236PP3

Page 9

CS4222

FUNCTIONAL DESCRIPTION

Overview

The CS4222 has 2 channels of 20-bit analog-todigital conversion and 2 channels of 20-bit

digital-to-analog conversion. All ADCs and

DACs are delta-sigma converters. The DAC outputs have adjustable output attenuation

implemented in 0.5 dB step resolution. The device also includes a soft mute function and

digital de-emphasis for 32, 44.1, and 48 kHz.

Digital audio data for the DACs and from the

ADCs is communicated over separate serial

ports. This allows concurrent writing to and

reading from the device. Control for the functions available on the CS4222 are commu nicated

over a serial microcontroller interface. Figure 1

shows the recommended connection diagram for

the CS4222.

The device can be operated with or without the

control port interface. Additional functions are

available when the control port interface is used

as outlined in Table 1.

Control Port

Volume control -

Adjustable Mute ra mp rate Fixed Mute ramp rate

Enable zero crossing detect Disabled

Disable mute on zero input Enabled

De-emphasis De-emphasis

Mute DAC outputs Mute DAC outputs

ADC Input Peak Level

Detect

16, 18, 20 bit Inte rface 20 bit I

Individual ADC/DAC power

down

Cal on command Cal on power-up

High pass enable/disable High pass enabled

Table 1. Control Port vs. Stand-alone

Stand-alone

-

2

S Interface

Codec power down

Analog Inputs

Line Le vel Inpu ts

AINR-, AINR+, AINL-, and AINL + are the differential line level input pins (See Figure 1).

Figure 2 shows an AC coupled optional input

buffer which combines level shifting with singleended to differential conversion. Analog inputs

must be DC coupled into the CS4222 with a

2.3V common mode input voltage. Any DC off-

Figure 2. Optional Line Input Buffer

DS236PP3 9

Page 10

CS4222

set at the input to the CS4222 will be removed

by the internal high-pass filters. See Figure 3 for

the differential input signal description. The

ADC outputs may be muted (set to zero) by

writing the ADMR and ADML bits, and the

ADC can be independ ently powered down using

the PDAD bit. ADMR, ADML, and PDAD are

all located in the ADC control byte (#1).

Input Level Monitoring

The CS4222 includes independent Peak Input

Level Monitoring for each channel. The analogto-digital converter continua lly monitors the peak

digital signal for bo th channels, prior to the dig ital limiter, and records these values in the

LVL2-0 (left channel) and LVR2-0 (right channel) bits in the Converter Status Report Byte

(#6). These bits indicate whether the input level

is clipping, -1 to -6 dB from full scale in 1 dB

resolution, or below -6 dB from full scale. The

LVL/LVR bits are "sticky" bits and are reset to

zero when read.

High Pass Filter

The operational amplifiers in the input circuitry

driving the CS4222 may generate a small DC

offset into the A/D converter. The CS4222 includes a high pass filter after the decimator to

remove any DC offset which could result in recording a DC level, possibly yielding "clicks"

when switching between devices in a multichannel system. The characteristics of this first-order

high pass filter are outlined below for Fs equal

to 48 kHz. The filter response scales linearly

with sample rate. The hig h pass filter may be defeated independently for the left and right

channels by writing HPDR and HPDL in the

ADC control byte (#1).

Frequency Response -3dB @ 3.7 Hz

-0.1 dB @ 20 Hz

Phase Deviation 10 degrees @ 20 Hz

Passband Ripple None

Analog Outputs

Line Level Outputs

The CS4222 co ntains an on-chi p buffer amplifier

producing d ifferential outputs capable of driving

10 kΩ loads. Each output (AOUTL+, AOUTL-,

AOUTR+, AOUTR-) will produce a nominal

2.83 Vpp (1 Vrms) output with a 2.3 volt common mode for a full scale digital input. This is

equivalent to a 5.66 Vpp (2 Vrms) differential

signal as s hown in Figure 3. The recommended

off-chip analog filter is either a 2nd order Butterworth or a 3rd order Butterworth, if greater

out-of-band noise filtering is desired. The

CS4222 DAC interpolation filter has been precompensated for an external 2nd order

Butterworth filter with a 3dB corner at Fs, or a

3rd order Butt erworth filter with a 3dB corner at

0.75 Fs to pr ovide a flat fr equency response and

linear phase over the passband (see Figure 4 for

Fs = 48 kHz). If the recommended filter is not

used, small frequency response magnitude and

phase errors will occu r. In addit ion to providing

out-of-band noise attenuation, the output filters

shown in Figure 4 provide differential to singleended conversion.

The DACs can be powered down using the

PDDA bit in the DAC c ontrol register (#2).

CS4222

AIN+/AOUT+

AIN+/A OU T-

Full Scale Input level = (AIN+) - (AIN-)= 5.66 Vpp

Full Scale Output level = (AOUT+) - (AOU T-)= 5.66 Vpp

Figure 3. Full Scale Input/Output Voltage

(2.3 + 1.4)V

2.3V

(2.3 - 1.4)V

(2.3 + 1.4)V

2.3V

(2.3 - 1.4)V

Table 2. High Pass Filter Characteristics

10 DS236PP3

Page 11

CS4222

Figure 4.

Analog/Digita l Volume Control - C ontrol Port

Analog Digital

0

Mode Only

Signal

The DAC outpu ts are each routed through an attenuator which is adjustable in 0.5 dB steps.

Output attenuation is available through the Out-

Noise

put Attenuator Data Bytes (#3 & #4). Level

changes are implemented with an analog volume

Amplitude (dB)

control until the residual output noise is equal to

the noise floor in the mute state at which point

volume changes are performed digitally. This

technique is superior to purely digital volume

0 -113.5

Attenuation (dB)

Figure 5. Hybrid Analog/Digital Attenuation

control techniques as the noise is attenuated by

the same amount as the signal, thus preserving

dynamic range (see Fi gure 5).

from the current level to the new level in 0.5 dB

steps. The default rate of volume change is 8

LRCK cycles for each 0.5 dB step (equivalent to

The CS4222 implements a " soft" volume contro l

647 µs at Fs = 48 kHz). The rate of volume

whereby level changes are achieved by ramping

DS236PP3 11

Page 12

CS4222

change is adj ustable to 4, 16, or 32 LRC K cycles

with the RMP1/0 bits in the DAC control byte

(#2).

"Soft" volume control may be disabled through

the SOFT bit in th e DAC bit Control Byte (#2).

When "soft" volume control is defeated, level

changes step from the current level to the new

level in a single st ep. The volume change takes

effect on a zero crossing to minimize audible artifacts. If there is no zero crossing, then the

requested level change will occur after a timeout period between 512 and 1024 sample periods

(10.7 ms to 21.3 ms at 48 kHz sample rate).

There is a separate zero crossing detector for

each channel. ACCR and ACCL bits in the Converter Status Report Byte (#6) give feedback on

when a volume control change has taken effect

for the right and left channel . This bit goes high

when a new setting is loaded and returns low

when it has taken effect .

Soft Mute/Mute on Zero Input Dat a

Muting can be achieved via hardware or software control. Soft mute can be achieved by

lowering the

SMUTE pin at which point the output level will ramp down in 0.5 dB steps to a

muted state. Upon returning the

SMUTE pin

high, the output will ramp up to the volume control setting in the Output Attenuator Data Bytes

(#3 & #4). "Soft" mute may be disable d through

the SOFT bit in the DAC Control Byte (#2).

When "soft" mute is defeated, muting occurs on

zero crossings or after a time-out period, similar

to the volume control changes.

Under software control, each output can be independently muted via mute control bits, MUTR

and MUTL, in the DAC Control Byte (#2). Soft

mute or zero crossing mute will be implemented

depending on the state of the SOFT bit in the

DAC Cont rol Byte (#2).

they receive between 512 and 1024 consecutive

zeros (or -1 code). Detection and muting is done

independently for left and right channels. A single non-zero value will immediately unmute the

DAC output. This feature is enabled on powerup, and it may be disabled wi th the MUTC b it in

the DAC Control Byte (#2).

Master Clock Generation

The Master Clock, MCLK, is used to ope rate the

digital filters and the delta-sigma modulator.

MCLK must be either 256x, 384x, or 512x the

desired Input Sample Rate, Fs. Fs is the frequency at which digital audio samples for each

channel are i nput to the DAC or ou tput from the

ADC and is equal to the LRCK frequency. The

MCLK to LRCK frequency ratio is detected

automatically during the initialization sequence by

counting the number of MCLK transitions during

a single LRCK period. Internal dividers are then

set to generate the proper clocks for the digital

filters, delta-sigma modulators and switched-capacitor filter. Table 3 illustrates the standard

audio sample rates and the required MCLK fre-

quencies. If MCLK stops for 10µs, the CS4222

will enter a power down state unt il the clock returns. The control port registers will maintain

their current settings. It is required to have

SCLK and LRCK derived from the master clock.

Fs (kHz) MCLK (MHz)

256x 384x 512x

32 8.1920 12.2880 16.3840

44.1 11.2896 16.9344 22.5792

48 12.2880 18.4320 24.5760

Table 3. Common Clock Frequencies

Muting on consecutive zero input data is also

provided where all DAC outputs will mute if

12 DS236PP3

Page 13

CS4222

FORMAT 0:

(Stand-Alone and

Control Port Mode)

FORMAT 1:

(Control Port

Mode only)

FORMAT 2, 3, 4:

Format 2: M = 20

Format 3: M = 18

Format 4: M = 16

(Control Port

Mode only)

Note: SCLK shown for DSCK = 0. SCLK inverted for DSCK = 1.

LRCK

SCLK

SDIN MSB LSB

LRCK

SCLK

SDIN

LRCK

SCLK

SDIN

MSB LSB

LSB LSBMSB LSBMSB

Left Right

Left Right

Left Right

M SCLKs

Figure 6. Audio DSP Data Input Formats.

MSB LSB

MSB LSB MSB

M SCLKs

FORMAT 0:

(Stand-Alone and

Control Port Mode)

FORMAT 1:

(Control Port

Mode only)

Note: SC LK shown for DSCK = 0. SCLK inverted for DSCK = 1.

LRCK

SCLK

SDIN MSB LS B

LRCK

SCLK

SDIN MSB LSB

Left Right

Left Right

MSB LSB

MSB LSB MSB

Figure 7. Audio DSP Port Data Output Formats.

DS236PP3 13

Page 14

CS4222

Serial Audio Data Interface

Serial Audio Interface Si gnals

The serial interface clock, SCLK, is used for

transmitting and re ceiving audio data. The active

edge of SCLK is chosen by s etting the DSCK bi t

in the DSP Port Mode Byte (#6); the default

upon power-up is that d ata is valid on the rising

edge for both input and output. SCLK is an input from an external source and at least 20

SCLK’s per half period of LRCK are required

for proper operation.

The Left/Right clock (LRCK) is used to indicate

left and right dat a and the start of a new sample

period. The frequency of LRCK must be equal

to the system samp le rate, Fs.

SDIN is the data input pin which drives a pair of

DACs. SDOUT is the output data pin from the

ADC’s.

Serial Audio Interface Formats

The serial au dio port supports 5 in put and 2 output formats, shown in Figures 6 and 7. These

formats are chosen through the DSP Port Mode

Byte (#5) with the DDO and DDI2/1/0 bits. The

data output fo rmat is 20 bits and may be left jus tified or I

2

S compatible depending on the state

of the DDO bit. The input data format is set

with the DDI bits to be left or right justified or

2

I

S compatible. In addition, the polarity of the

SCLK edge used to clock in/out data from the

CS4222 may be set via the DSC K bit in t he DSP

Port Mode By te (#5). The default in put and output format is I

2

S compatible.

Control Po rt Interfa ce

The control port is used to load all the internal

settings. The operation of the control port may

be completely a synchronous with t he audio sample rate. However, to avoid potential i nterference

problems, the control port pins should remain

static if no operati on is required.

The control port has 2 modes: SPI and I

2C®

with the CS4222 operating as a slave device. If

2

I

C operation is desired, AD0/CS should be tied

to VD or DGND. If the CS4222 ever detects a

negative transition on AD0/

CS after power-up,

SPI mode will be selected.

SPI Mode

In SPI mode,

CS is the CS4222 chip select signal, CCLK is t he control port b it clock, CDIN is

the input data line from the microcontroller and

the chip address is 0010000. All signals are inputs and data is clocked in on the rising edge of

CCLK.

Figure 8 shows the operation of th e control port

in SPI mode. To write to a register, bring

CS

low. The first 7 bits on CDIN form the chip address, and must be 0010000. The eighth bit is a

read/write indicator (R/

W), which must be low

to write. Register reading from the CS4222 is

,

CS

CCLK

CHIP

ADDRESS

CDIN

14 DS236PP3

0010000

MAP = Memory Address Pointer

Figure 8. Con trol Port Timi ng, S PI mo de

R/W

MAP

MSB

byte 1

DATA

LSB

byte n

Page 15

SDA

SCL

001000

ADDR

AD0

R/W

ACK

DATA

1-8

Note 1

ACK

DATA

1-8

CS4222

ACK

Start

Note: If operation is a write, this byte contains the Memory Address Pointer, MAP.

Figure 9. Control Port Timing, I2C® Mode

not supported in the SPI mode. The next 8 bits

form the Memory Address Pointer (MAP), which

is set to the address of the register that is to be

updated. The next 8 bits are the data which will

be placed into regis ter designated by the MAP.

The CS4222 ha s a MAP auto increment cap ability, enabled by the INCR bit i n the MAP register.

If INCR is a zero, then the MAP will stay constant for successive writes. If INCR is set to a 1,

then MAP will auto increment after each byte is

written, allowing block writes of successive registers. Register reading from the CS4222 is not

supported in the SPI mode.

2C ®

I

Mode

Stop

reads or writes of consecutive registers. Each

byte is separated by an acknowledge bit. Use of

2

the I

C bus®compatible interface requires a li-

cense from Philips. I

2

C bus® is a registered

trademark of Phili ps Semiconducto r.

Control Port Bit Definitions

All registers can be written and read in I

2

C

mode, except the Converter Status Report Byte

(#6) and the CLKE and CALP bits in the ADC

control byte (#1) which are read only. SPI mode

only allows for register writing. See the following bit definition tables for bit assignment

information.

2C®

In I

mode, SDA is a bidirectional data line.

Data is clocked into and out of the part by the

clock, SCL, wi th the clock to data relations hip as

shown in Figure 9. The re is no

CS pin. Pin AD0

forms the partial chip address and should be tied

to VD or DGND as desired. The upper 6 bits of

the 7 bit address field must be 001000. To communicate with the CS4222 the LSB of the chip

address field, which is the first byte sent to the

CS4222, should match the setting of the AD0

pin. The eighth bit of the address byte is the

R/

W bit (high for a rea d, low for a write). If the

operation i s a write, th e next byte is the Memory

Address Pointer which selects the register to be

read or written. If the operation is a read, the

contents of the register pointed to by the Memory Address Pointer will be output. Setting the

auto increment bit in MAP, allows successive

DS236PP3 15

Page 16

CS4222

De-Emphasis

The CS4222 is capable of digital de-emphasis

for 32, 44.1, or 48 kHz sample rates. Implementation of digital de-emphasis requires

reconfiguration of the digital filter to maintain

the filter response shown in Figure 10 at multiple sample rate s.

De-emphasis control is achieved with the

DEM1/0 pins or through the DE M2-0 bits in the

DAC Control Byte (#2). The default state on

power-up is de-emphasis controlled via the

DEM1/0 pins (DEM2-0 bits=0). DEM1/0 pin

control is defined in Tab le 4.

DEM 1 DEM 0 De-em pha sis

0032 kHz

0144.1 kHz

1048 kHz

11OFF

Table 4. De-Emphasis filter control

Power-up/Reset/Power Down/Ca libration

Upon power up, the user should hold

RST=0 for

approximately 10 ms. In this state, the control

port is reset to its default settings and the part

remains in the power down mode. At the end of

RST, the device performs an offset calibration

which lasts ap proximately 50 ms after which the

device enters normal operation. A calibration

may also be initiated via the CAL bit in the

ADC Control Byte (#1). The CALP bit in the

ADC Control Byte is a read only bit indicating

the status of t he calibration .

Reset/Power Down is achieved by lowering the

RST pin causing the part to enter power down.

Once

RST goes high, the control port is func-

tional and the d esired setti ngs should be lo aded.

The CS4222 will also ent er power down mode if

the master clock source stops for approximately

10 µs or if the LRCK is not synchronous to the

master clock. The control port will retain its

current setting s.

Gain

dB

0dB

-10dB

T1=50

Figure 10. De-emphasis Curve.

s

µ

F1 F2

T2 = 15

Frequency

Additionally, the PDAD (ADC Control Byte #1)

and PDDA (DAC Control Byte #2) bits can be

used to power down the ADC’s and DAC’s independently. If both are set to 1, the CS4222 will

power down the entire chip. The control port

will retain its c urrent setting s.

The CS4222 will mute the analog outputs and

enter the power down mode if the supply drops

below approximately 4 volts.

s

µ

Power Supply, Layout and Grounding

The CS4222 should be located on the analog

ground plane along with associated analog circuitry and should be positioned near the split

between ground planes (see Figure 11). Preferably, the device should also have its own power

plane. The +5V supply should be connected to

the CS4222 via a ferrite bead, positioned closer

than 1" to the device. A single connection be-

16 DS236PP3

Page 17

tween the CS4222 ground and the board ground

should be p ositioned as shown in Figure 1 1. See

the CDB4222 evaluation board data sheet for

recommended layout of the decoupling components.

ADC and DAC Filter Response Plots

Figures 12 through 17 show the overall frequency response, passband ripple and transition

band for the CS4222 ADC’s and DAC’s.

CS4222

1/8"

>

Digital

Ground

Plane

CPU & Digital

Logic

Figure 11. Suggested Layout Guideline (See CDB4222 Data Sheet)

DS236PP3 17

+5V

Ferrite

Bead

Ground

Connection

CS4222

Codec

digital

signals

Analog

Ground

Plane

Codec

analog

signals &

components

Note that the CS4222

is oriented with its

digital pins towards the

digital end of the board.

Page 18

CS4222

Figure 12. ADC Filter Response.

Figure 13. ADC Passband Ripple.

Figure 15. DAC Frequency Response.

Figure 16. DAC Passband Ripple.

Figure 14. ADC Transition Band.

18 DS236PP3

Figure 17. DAC Transition Band.

Page 19

CS4222

Memory Address Pointer (MAP)

B7 B6 B5 B4 B3 B2 B1 B0

INCR 0 0 0 0 MAP2 MA P1 MAP0

MAP2-MAP0 Register Pointer

INCR Auto Increment Control Bit

0 - No auto increment

1 - Auto increment on

This register defaults to 00h.

Reserved Byte (0)

This byte is reserved for internal use and must

be set to 00h for norma l operation.

This register defaults to 00h.

ADC Control Byte (1)

B7 B6 B5 B4 B3 B2 B1 B0

PDAD HPDR HPDL ADMR A DML CAL CA LP CLKE

PDAD Power Down ADC

0 - Normal

1 - Power down

HPDR-HPDL High pass filter defeat, right an d left

0 - High pass filters active

1 - High pass filters defeated

DAC Control Byte (2)

B7 B6 B5 B4 B3 B2 B1 B0

PDDA MUTC MUTR MUTL SOFT 0 RMP1 RMP0

PDDA Power Down DAC

0 - Norm al

1 - Power down

MUTC Controls mute on consecutive zeros

function

0 - 512 consecutive zeros will mute DAC

1 - DAC outp ut will not mute on zeros.

MUTR-MUTL Mute control bits

0 - Norm al outp ut level

1 - Sel ect ed DAC outp ut m ute d

SOFT Soft Mute Control

0 - Volume control changes, muting and

mute-on-zeros occur with "ramp"

1 - Volume control changes, muting and

mute-on -zeros oc cur on zer o cros sings

RMP1-0 Soft Volume 0.5 dB step rate

0 - 1 step per 8 LRCK’s

1 - 1 step per 4 LRCK’s

2 - 1 step per 16 LRCK’s

3 - 1 step per 32 LRCK’s

This register defaults to 00h.

ADMR-ADML ADC Muting, right and left

0 - Normal

1 - Output muted

CAL Calibration cont rol bit

0 - Normal operation

1 - Rising edge initiates calibration

The following bits are read only:

CALP Calibration statu s

0 - Calibration done

1 - Calibration in progress

CLKE Clocking Error

0 - No error

1 - error

This register defaults to 00h.

DS236PP3 19

Page 20

CS4222

Output Attenuat or Data Byte (3 , 4)

B7 B6 B5 B4 B3 B2 B1 B0

ATT7 ATT6 ATT5 ATT4 ATT3 ATT2 ATT1 ATT0

ATT7-ATT0 Sets attenuator level

0 - No attenuation

227 - 113. 5 dB at tenuat ion

>227 - DAC muted

ATT0 represents 0.5 dB of attenuation

This register defaults to 00h.

DSP Port Mode Byte (5)

B7 B6 B5 B4 B3 B2 B1 B0

DEM2 DEM1 DEM0 DSCK DDO DDF2 DDF1 DDF0

DEM2-0 Se lects de-emphasis contro l source

0 - De-emphasis controlled by pins

1 - 44.1 kHz de-emphasis setting

2 - 48 kHz de-emphasis setting

3 - 32 kHz de-emphasis setting

4 - De-emphasis disabled

5 - Not used

6 - Not used

7 - Not used

Converter Statu s Report Byte (Read On ly) (6)

B7 B6 B5 B4 B3 B2 B1 B0

ACCR ACCL LVR2 LVR1 LVR0 LVL2 LVL2 LVL0

ACCR-ACCL Acceptance bit

0 - ATT7-0 has been accepted

1 - New setting waiting for zero crossing

LVL2-0,LVR2-0 Left and Right ADC output level

0 - Norm al outp ut levels

1 - -6 dB level

2 - -5 dB level

3 - -4 dB level

4 - -3 dB level

5 - -2 dB level

6 - -1 dB level

7 - Clippi ng

LVL2-0 and LVR2-0 bits are ’sticky’. They constantly

monitor the ADC output for the peak levels and hold

the maximum output. They are reset to 0 when read.

This register is read only.

DSCK Set the polar ity of clo cking data

0 - Data valid on rising edge of SCLK

1 - Data valid on falling edge of SCLK

DDO Data output format

2

S compatible

0 - I

1 - Left justified

DDI2-DDI0 Data input format

2

S compatible

0 - I

1 - Left justified

2 - Right justified, 20-bit

3 - Right justified, 18-bit

4 - Right justified, 16-bit

5 - Not used

6 - Not used

7 - Not used

This register defaults to 00h.

20 DS236PP3

Page 21

PIN DESCRIPTIONS

NC NC

1

SMUTE RST

MCLK AOUTL-

LRCK AOUTL+

SCLK AOUTR+

DGND AGND

SDOUT VA

SDIN AINL+

SCL/CCLK AINL-

SDA/CDIN DEM1

AD0/

DEM0 AINR-

2

3

4

5

VD AOUTR-

6

7

8

9

10

11

CS AINR+

12

13

NC NC

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

CS4222

Power Supply

VA - Positive Analog Power, Pin 21.

Positive analog supply. Nominally +5 volts.

VD - Positive Digital Power, Pin 6.

Positive supply for the digita l section. No minally +5 volts.

AGND - Analog Ground, Pin 22.

Analog ground referen ce.

DGND - Digital Ground, Pin 7.

Digital ground for the digital sec tion.

Analog Inputs

AINR-, AINR+ - Differential Right Channel Analog Input, Pins 16 and 17.

Analog input co nnections of th e right channel differen tial inputs. Typically 2 Vrms differential

(1 Vrms for each input pin) for a full-scale analog input signal.

AINL-, AINL+ - Differential Left Channel Analog Input, Pins 19 a nd 20.

Analog input co nnections of the left channel differential inputs. Typically 2 Vrms differential

(1 Vrms for each input pin) for a full-scale analog input signal.

DS236PP3 21

Page 22

Analog Outputs

AOUTR-, AOUTR+ - Differential Right Channel Analog Outputs, Pins 23 and 24.

Analog output connections for the Right channel differential outputs. Nominally 2 Vrms

(differential) for full-scale dig ital input signa l.

AOUTL-, AOUTL+ - Differential Left Channel Analog Outputs, Pins 25 and 26.

Analog output connections for the Left channel differential outputs. Nominally 2 Vrms

(differential) for full-scale dig ital input signa l.

Digital Inputs

MCLK - Master Clock, Pin 3.

Clock source for the del ta-sigma modulator sampling and dig ital filters. The frequency of this

clock must be eith er 256x, 38 4x, or 512x Fs.

LRCK - Left/Right Clock, Pin 4.

LRCK determines which channel, left or right, is to be input/output on SDIN/SDOUT.

Although t he outputs for each ADC channel are transmitted at different times, L eft/Right pairs

represent simultaneously sampled analog inputs. LRCK is an input clock whose frequency

must be equal to Fs.

CS4222

SCLK - Serial Data Clock, Pin 5.

Clocks the individual bi ts of the serial data o ut from SDOUT and in from SDIN.

SDIN - Serial Data Input, Pin 9.

Two’s complement MSB-first serial data of either 16, 18, or 20 bits is input on this pin. The

data is clocked into the CS4222 via the SCLK clock and the channel is determined by the

LRCK clock. The default interface format on power-up is an I

This may be changed b y writing the con trol port (DSP Port Mode B yte #5).

DEM1, DEM0 - De-Emphasis Select, Pins 18 and 13.

Controls the a ctivation of the standard 50/15 µs de-empha sis filter. 32 , 44.1, or 48 kHz sample

rate selection defined in Table 4.

SMUTE - Soft Mute, Pin 2.

SMUTE low activates a muting function for both the left and right channel D/A converter

outputs. Soft muting is achieved by ramping down the volume in 0.5 dB steps until achieving

mute if SOFT bit (DAC Control Byte #2) is set to 0 (d efault).

Digital Outputs

SDOUT - Serial Data Output, Pin 8.

Two’s complement MSB-first serial data of 20 bits is output on this pin. The data is clocked

out via the SCL K clock and the channel is determined b y LRCK.

2

S compatible 20-bit interface.

22 DS236PP3

Page 23

Control Port Signals

SCL/CCLK - Serial Control Interface Clock, Pin 10.

SCL/CCLK is the serial control interface clock an d is used to clock cont rol bits into and out of

the CS4222 This pin should be tie d to DGND in stand-alone mo de.

AD0/

CS - Address Bit/Control Port Chip Select, Pin 12.

2

In I

C® mode, AD0 is a chip address bit. In SPI mode, CS is used to en able the control port

interface on the CS4222. The CS4222 will enter SPI mode if a negative transition is ever seen

on this pin after p ower up. This pin should be ti ed to DGND in stand-alone mode .

SDA/CDIN - Serial Control Data In, Pin 11.

SDA/CDIN is the input data line for the control port interface. This pin should be tied to

DGND in stand-alone mod e.

Miscellaneous Pins

RST - Reset, Pin 27.

When low, the CS 4222 enters a low power mode and all internal stat es are reset, includ ing the

control por t. When high , the contr ol port beco mes operat ional and normal operation will occur.

CS4222

NC - No Connect, Pins 1, 14, 15 and 28

These pins are not connected internally and should be tied to DGND to minimize noise

coupling.

PARAMETE R DEFINITIONS

Dynamic Range

The ratio of the full scale rms value of the signal to the rms sum of all other spectral

components over the specified bandwidth. Dynamic range is a signal-to-noise measurement

over the specified bandwidth made with a -60 dBFS signal. 60dB is then added to the resulting

measurement t o refer the measurement to full scale. This techn ique ensures that the disto rtion

components are below the noise level and do not affect the measurement. This measurement

technique has bee n accept ed by the Audio Engi neering Soc iety, AES17-1991, and t he Elect ronic

Industries Association of Japan, EIAJ CP-307.

Total Harmonic Distor tion + Noise

The ratio of the rms value of the signal to the rms sum of all other spectral components over

the specified bandwid th (typically 20Hz t o 20kHz), includin g distortion components. Expressed

in decibels. ADCs are measured at -1 dBFS as suggested in AE S17-1991 Annex A and DACs

are measured at 0 dBFS.

DS236PP3 23

Page 24

Idle Channel Noise / Si gnal-to-Noise-Ratio

The ratio of the rms analog output level with 1kHz full scale digital input to the rms analog

output level with all zeros into the digital input. Measured A-weighted over a 10Hz to 20kHz

bandwidth. Units in decibels. This specification has been standardized by the Audio

Engineering Soci ety, AES17-1991, and referred to as Idle Channel Noise. This specificatio n has

also been standardized by the Electronic Industries Association of Japan, EIAJ CP-307, and

referred to as Signal-to-Noise-Ra tio.

Total Harmonic Distor tion (THD)

THD is the rati o of the test sig nal amplitude to the rms sum of all the in-ban d harmonics of th e

test signal. Unit s in decibels.

Interchannel Isolation

A measure of cro sstalk between chann els. Measured for each ch annel at the converter’s output

with no sign al to the in put under test and a full-scale s ignal applied to the other chann el. Units

in decibels.

Frequency Response

A measure of the amplitude response variation from 20Hz to 20kHz relative to the amplitude

response at 1kHz. Un its in decibe ls.

CS4222

Interchannel Gain Mismatch

For the ADCs, the difference in input voltage that generates the full scale code for each

channel. For the DACs, the difference in output voltages for each channel with a full scale

digital input. Units are in dec ibels.

Gain Error

The deviation from the nominal fu ll scale outp ut for a ful l scale in put.

Gain Drift

The change i n gain value with te mperature. Uni ts in ppm/° C.

Offset Error

For the ADCs, the deviation i n LSB’s of the output from mid-scale with t he selected inputs tie d

to a common potential. For the DAC’s, the differential output voltage with mid-scale input

code. Units are in volts.

24 DS236PP3

Page 25

PACKAGE DIMENSIONS

N

CS4222

E

13

2

TOP VIEW

1

D

A

A

2

A

e

1

2

b

Seating

Plane

L

SIDE VIEW

Notes:

1. "D" and "E " ar e reference datums

1

and do not include mold flash or

protrusions, but do include mold

mismatch and are measured at the

parting line, mold flash or protrusions

shall not exceed 0.20mm per side.

2. Dimension b does not include

dambar protrusion/intrusion.

Allowable dambar protr us ion shall

be 0.13mm total in excess of b

dimension at maximum material

condition. Dambar intrusion shall

not reduce dimension b by more than

0.07mm at least mat erial conditi on.

3. These dimen s ions apply to the flat

section of the lead between 0.10 and

0.25mm from lead tips.

SSOP Package

Dimensions

1

E

1

END VIEW

MILLIMETERS

DIM

MIN NOM MAX

A

A

A

D

E

E

N

∝

N

20

28

--

0.05

1

1.62

2

0.22

b

see other table

7.40

5.00

1

e

0.61

0.63

L

see other table

0°

MILLIMETERS

MIN NOM MAX

6.90

9.90

2.13

0.15 0.25

1.75 1.88

0.30 0.38

7.80 8.20

5.30 5.60

0.65 0.69

0.90 1.03

4°

7.20 7.50

10.20 10.50

8°

INCHES

MIN NOM MAX

-

0.002

0.064 0.070 0.074

0.009

see other table

0.291 0.307 0.323

0.197 0.209 0.220

0.024 0.026 0.027

0.025 0.035 0.040

see other table

0°4° 8°

D

MIN NOM MAX

0.272 0.283 0.295

0.390 0.402 0.413

-

0.006

0.012

INCHES

0.084

0.010

0.015

Note

2, 3

1

1

Note

1

1

DS236PP3 25

Page 26

Loading...

Loading...