Datasheet CS3845GDW16, CS3845GDR8, CS3845GDR14, CS3845GD8, CS3845GD14 Datasheet (Cherry Semiconductor)

...Page 1

1

Features

■

Optimized for Offline

Control

■

Temp. Compensated

Oscillator

■

50% Max Duty-cycle Clamp

■ V

REF

Stabilized before

Output Stage is Enabled

■ Low Start-up Current

■ Pulse-by-pulse Current

Limiting

■ Improved Undervoltage

Lockout

■ Double Pulse Suppression

■ 1% Trimmed Bandgap Ref.

■ High Current Totem Pole

Output

Package Options

CS2844/3845 SERIES

Current Mode PWM

Control Circuit

with 50% Max Duty Cycle

CS2844/CS3844

CS2845/CS3845

Description

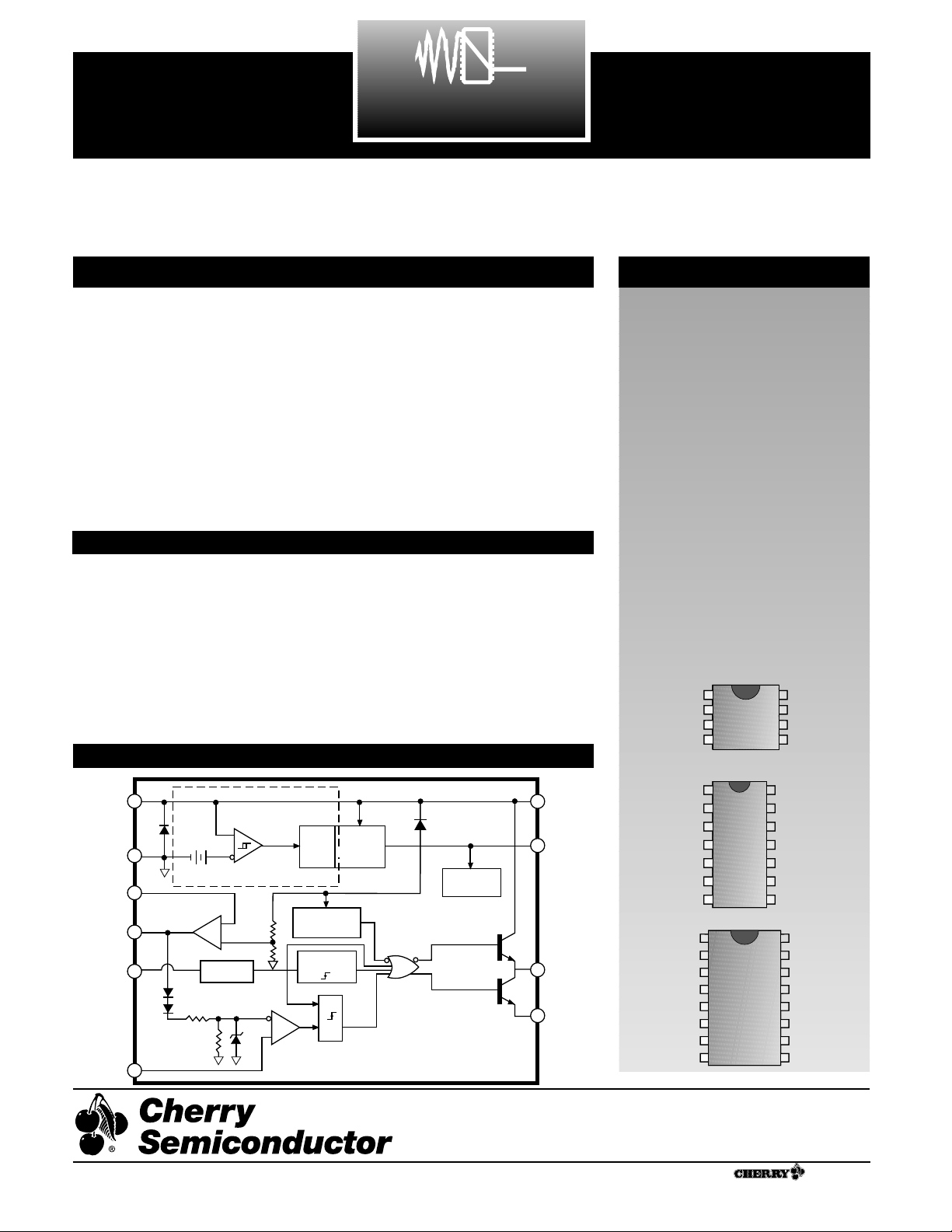

Block Diagram

Absolute Maximum Ratings

Supply Voltage (ICC<30mA).........................................................................Self Limiting

Supply Voltage (Low Impedance Source) .................................................................30V

Output Current..............................................................................................................±1A

Output Energy (Capacitive Load)................................................................................5µJ

Analog Inputs (V

FB

, V

SENSE

) .........................................................................-0.3V to 5.5V

Error Amp Output Sink Current .............................................................................10mA

Lead Temperature Soldering

Wave Solder (through hole styles only) ...................10 sec. max, 260°C peak

Reflow (SMD styles only) ....................60 sec. max above 183°C, 230°C peak

1

COMP

2

3

4

V

FB

Sense

OSC

V

REF

V

CC

V

OUT

Gnd

8

7

6

5

8 Lead PDIP & SO Narrow

10

7

14

13

12

8

1

2

3

4

5

6

11

9

COMP

NC

V

FB

NC

Sense

NC

OSC

V

REF

NC

V

CC

VCC Pwr

V

OUT

Pwr Gnd

Gnd

14 Lead SO Narrow

The CS3844/45 provides all the necessary features to implement off-line

fixed frequency current-mode control

with a minimum number of external

components.

The CS3844 family incorporates a new

precision temperature-controlled oscillator to minimize variations in frequency. An internal toggle flip-flop,

which blanks the output every other

clock cycle, limits the duty-cycle range

to less than 50%. An undervoltage

lockout ensures that V

REF

is stabilized

before the output stage is enabled. In

the CS2844/CS3844 turn on occurs at

16V and turn off at 10V. In the

CS2845/CS3845 turn on is at 8.4V and

turn off at 7.6V.

Other features include low start-up

current, pulse-by-pulse current limiting, and a high-current totem pole output for driving capacitive loads, such

as gate of a power MOSFET. The output is low in the off state, consistent

with N-channel devices.

16

15

14

13

12

11

11

10

9

1

2

3

4

5

6

7

8

NC

NC

COMP

V

FB

SENSE

OSC

NC

NC

NC

V

REF

V

CC

V

CCPwr

V

O

Gnd

Pwr Gnd

NC

16 Lead SO Wide

Cherry Semiconductor Corporation

2000 South County Trail, East Greenwich, RI 02818

Tel: (401)885-3600 Fax: (401)885-5786

Email: info@cherry-semi.com

Web Site: www.cherry-semi.com

A Company

®

Rev. 3/17/99

V

Gnd

V

COMP

OSC

Sense

V

Undervoltage Lock-out

CC

16V/10V

(8.4V/7.6V)

Error

Amplifier

Oscillator

2 R

R

CC

34V

FB

+

2.50V

1V

Set/

5.0 Volt

Reset

Reference

V

REF

R

Undervoltage

Lockout

R

Toggle

Flip-Flop

S

R

PWM

Current

Sensing

Comparator

Latch

NOR

( ) indicates CS-2845/3845

Internal

Bias

V

Pwr

CC

V

REF

V

OUT

Pwr Gnd

Page 2

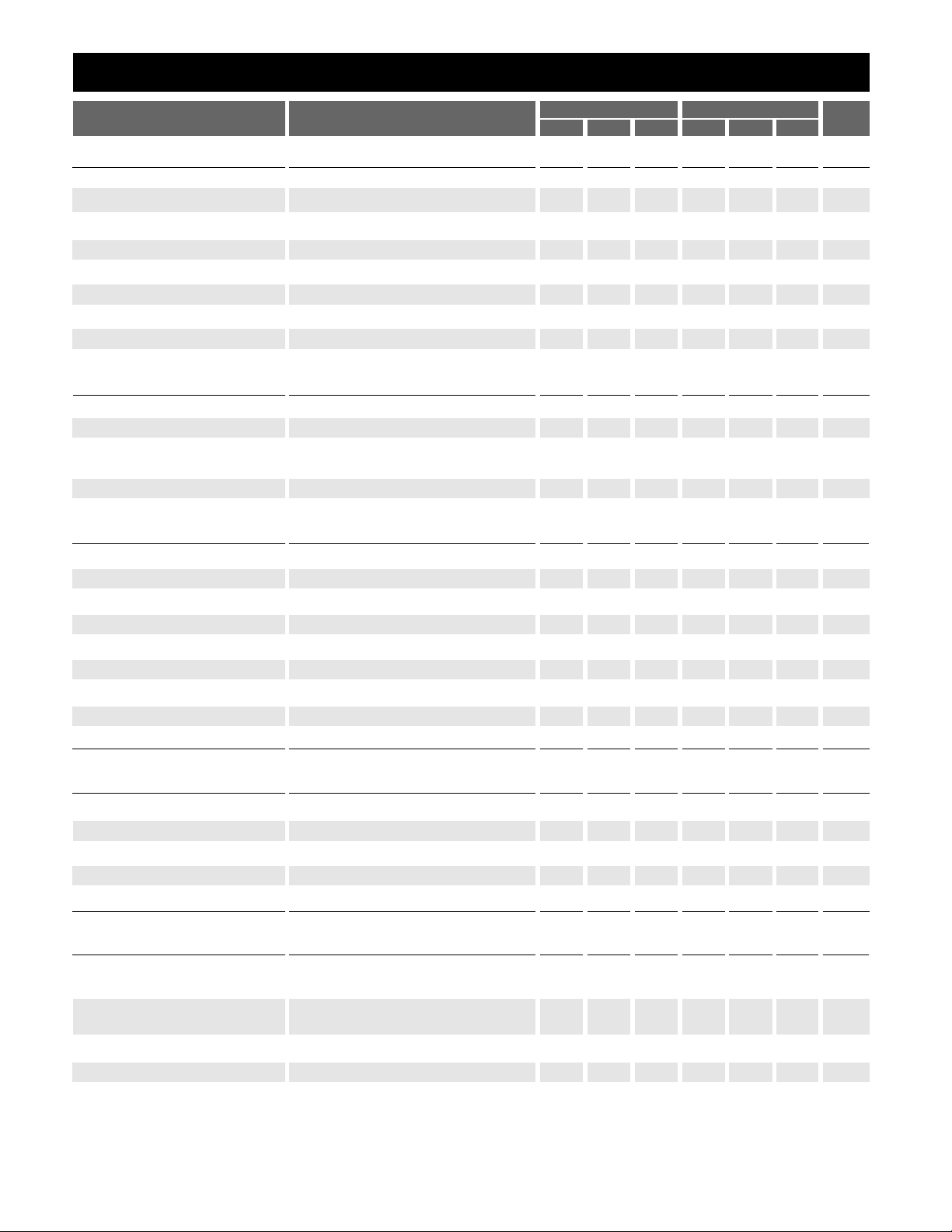

2

Electrical Characteristics: -25 ≤ TA ≤ 85˚C for CS2844/2845, 0 ≤TA ≤ 70˚C for CS3844/3845. V

CC

= 15V (Note 1); RT = 10kΩ,

C

T

= 3.3nF for sawtooth mode., unless otherwise stated.

CS2844/CS2845 CS3844/CS3845

PARAMETER TEST CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

CS2844/3845 SERIES

■ Reference Section

Output Voltage TJ=25˚C, I

REF

=1mA 4.95 5.00 5.05 4.90 5.00 5.10 V

Line Regulation 12≤VCC≤25V 6 20 6 20 mV

Load Regulation 1≤I

REF

≤20mA 6 25 6 25 mV

Temperature Stability (Note 2) 0.2 0.4 0.2 0.4 mV/˚C

Total Output Variation Line, Load, Temp. (Note 2) 4.90 5.10 4.82 5.18 V

Output Noise Voltage 10Hz≤ f≤10kHz, TJ=25˚C (Note 2) 50 50 µV

Long Term Stability TA=125˚C, 1000 Hrs. (Note 2) 5 25 5 25 mV

Output Short Circuit TA=25˚C -30 -100 -180 -30 -100 -180 mA

■ Oscillator Section

Initial Accuracy Sawtooth Mode, TJ=25˚C 475257475257kHz

Voltage Stability 12≤VCC≤25V 0.2 1.0 0.2 1.0 %

Temperature Stability Sawtooth Mode T

MIN≤TA≤TMAX

(Note 2) 5 5 %

Amplitude V

OSC

(peak to peak) 1.7 1.7 V

■ Error Amp Section

Input Voltage V

COMP

=2.5V 2.45 2.50 2.55 2.42 2.50 2.58 V

Input Bias Current VFB=0V -0.3 -1.0 -0.3 -2.0 µA

A

VOL

2≤V

OUT

≤4V 65 90 65 90 dB

Unity Gain Bandwidth (Note 2) 0.7 1.0 0.7 1.0 MHz

PSRR 12≤VCC≤25V 60 70 60 70 dB

Output Sink Current VFB=2.7V, V

COMP

=1.1V 2 6 2 6 mA

Output Source Current VFB=2.3V, V

COMP

=5V -0.5 -0.8 -0.5 -0.8 mA

V

OUT

HIGH VFB=2.3V, RL=15kΩ to Gnd 5 6 5 6 V

V

OUT

LOW VFB=2.7V, RL=15kΩ to V

REF

0.7 1.1 0.7 1.1 V

■ Current Sense Section

Gain (Notes 3 & 4) 2.85 3.00 3.15 2.85 3.00 3.15 V/V

Maximum Input Signal V

COMP

=5V (Note 3) 0.9 1.0 1.1 0.9 1.0 1.1 V

PSRR 12≤VCC≤25V (Note 3) 70 70 dB

Input Bias Current V

Sense

=0V -2 -10 -2 -10 µA

Delay to Output TJ=25˚C (Note 2) 150 300 150 300 ns

■ Output Section

Output Low Level I

SINK

=20mA 0.1 0.4 0.1 0.4 V

I

SINK

=200mA 1.5 2.2 1.5 2.2 V

Output High Level I

SOURCE

=20mA 13.0 13.5 13.0 13.5 V

I

SOURCE

=200mA 12.0 13.5 12.0 13.5 V

Rise Time TJ=25˚C, CL=1nF (Note 2) 50 150 50 150 ns

Fall Time TJ=25˚C, CL=1nF (Note 2) 50 150 50 150 ns

Page 3

3

CS2844/3845 SERIES

CS2844/CS2845 CS3844/CS3845

PARAMETER TEST CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

CS2844 CS3844 CS2845/CS3845

PARAMETER TEST CONDITIONS MIN TYP MAX MIN TYP MAX MIN TYP MAX UNITS

Notes: 1. Adjust Vccabove the start threshold before setting at 15V. 3. Parameter measured at trip point of latch with VFB=0.

2.These parameters, although guaranteed, are not 100% tested in production. 4. Gain defined as:

A = ; 0 ≤ V

Sense

≤ 0.8V.

∆V

COMP

∆V

Sense

■ Under-Voltage Lockout Section

Start Threshold 15 16 17 14.5 16 17.5 7.8 8.4 9.0 V

Min. Operating After Turn On 9 10 11 8.5 10 11.5 7.0 7.6 8.2 V

Voltage

Package Pin Description

PACKAGE PIN # PIN SYMBOL FUNCTION

■ Total Standby Current

Start-Up Current 0.5 1.0 0.5 1.0 mA

Operating Supply Current VFB=V

Sense

=0V RT=10kΩ, CT=3.3nF 11 17 11 17 mA

VCCZener Voltage ICC=25mA 34 34 V

■ PWM Section

Maximum Duty Cycle 46 48 50 46 48 50 %

Minimum Duty Cycle 0 0 %

8L 14L 16L

PDIP/SO SO Narrow SO Wide

1 1 3 COMP Error amp output, used to compensate error amplifier.

234 V

FB

Error amp inverting input.

3 5 5 Sense Noninverting input to Current Sense Comparator.

4 7 6 OSC Oscillator timing network with Capacitor to Ground, resis-

tor to V

REF

.

5 9 11 Gnd Ground.

8 10 Pwr Gnd Output driver Ground.

61012V

OUT

Output drive pin.

11 13 V

CC

Pwr Output driver positive supply.

71214 VCCPositive power supply.

81415 V

REF

Output of 5V internal reference.

2,4,6,13 1,2,7,8,9,16 NC No Connection.

Electrical Characteristics: -25≤TA≤85˚C for CS2844/2845, 0≤TA≤70˚C for CS3844/3845. VCC=15V (Note 1); RT=10kΩ,

C

T

=3.3nF for sawtooth mode., unless otherwise stated.

Page 4

4

CS2844/3845 SERIES

Undervoltage Lockout

During Undervoltage Lockout (Figure 1), the output driver is biased to sink minor amounts of current. The output

should be shunted to ground with a resistor to prevent

activating the power switch with extraneous leakage currents.

PWM Waveform

To generate the PWM waveform, the control voltage from

the error amplifier is compared to a current sense signal

which represents the peak output inductor current (Figure

2). An increase in VCCcauses the inductor current slope to

increase, thus reducing the duty cycle. This is an inherent

feed-forward characteristic of current mode control, since

the control voltage does not have to change during

changes of input supply voltage.

When the power supply sees a sudden large output current increase, the control voltage will increase allowing

the duty cycle to momentarily increase. Since the duty

cycle tends to exceed the maximum allowed to prevent

transformer saturation in some power supplies, the internal oscillator waveform provides the maximum duty cycle

clamp as programmed by the selection of OSC components.

Circuit Description

Test Circuit Open Loop Laboratory Test Fixture

V

REF

V

CC

V

OUT

1kΩ

1W

0.1µF

0.1µF

V

REF

V

CC

V

OUT

Gnd

V

FB

Sense

OSC

COMP

5kΩ

100kΩ

4.7kΩ

1kΩ

Error Amp

Adjust

4.7kΩ

Sense

Adjust

R

T

2N2222

C

T

Gnd

A

Figure 1: Startup voltage for CSX844 and CSX845.

V

CC

V

16V 8.4V

ON

V

OFF

<15mA

I

CC

<1mA

V

ONVOFF

ON/OFF Command

to reset of IC

CSX844 CSX845

10V 7.6V

V

CC

Page 5

5

Setting the Oscillator

The times Tcand Tdcan be determined as follows:

Grounding

High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and bypass

capacitors should be connected close to Gnd in a single

point ground.

The transistor and 5kΩ potentiometer are used to sample

the oscillator waveform and apply an adjustable ramp to

Sense.

CS2844/3845 SERIES

Circuit Description: continued

Substituting in typical values for the parameters in the

above formulas:

V

REF

= 5.0V, V

upper

= 2.7V, V

lower

= 1.0V, Id= 8.3mA,

then

tc≈ 0.5534RTC

T

td= RTCTln

For better accuracy RTshould be ≥10kΩ.

)

2.3 - 0.0083 R

T

4.0 - 0.0083 R

T

(

V

Figure 2: Timing Diagram

Figure 3: Duty Cycle parameters.

tc= RTCTln

td= RTCTln

)

V

REF

- IdRT- V

lower

V

REF

- IdRT- V

upper

(

)

V

REF

- V

lower

V

REF

- V

upper

(

OSC

OSC

RESET

Toggle

F/F Output

EA Output

Switch

Current

V

CC

I

O

V

O

V

upper

V

lower

t

t

t

on

t

C

on = tC

off = tC+2td

t

off

t

d

Page 6

Part Number 0˚C to -25˚C Description

70˚C to 85˚C

CS2844LN8 • 8L PDIP

CS2844LD14 • 14L SO

CS2844LDR14 • 14L SO (Tape & Reel)

CS2844LDW16 • 16L SO Wide

CS2844LDWR16 • 16L SO Wide (Tape & Reel)

CS2845LN8 • 8L PDIP

CS2845LDW16 • 16L SO Wide

CS2845LDWR16 • 16L SO Wide (Tape & Reel)

CS3844GN8 • 8L PDIP

CS3844GD8 • 8L SO

CS3844GDR8 • 8L SO (Tape & Reel)

CS3844GD14 • 14L SO

CS3844GDR14 • 14L SO (Tape & Reel)

CS3844GDW16 • 16L SO Wide

CS3844GDWR16 • 16L SO Wide (Tape & Reel)

CS3845GN8 • 8L PDIP

CS3845GD8 • 8L SO

CS3845GDR8 • 8L SO (Tape & Reel)

CS3845GD14 • 14L SO

CS3845GDR14 • 14L SO (Tape & Reel)

CS3845GDW16 • 16L SO Wide

CS3845GDWR16 • 16L SO Wide (Tape & Reel)

6

Ordering Information

CS2844/3845 SERIES

D

Lead Count Metric English

Max Min Max Min

8 Lead PDIP 10.16 9.02 .400 .355

8 Lead SO Narrow 5.00 4.80 .197 .189

14L SO Narrow 8.75 8.55 .344 .337

16L SO Wide 10.50 10.10 .413 .398

Thermal 8 L 8L SO 14 L SO 16L SO

Data PDIP Narrow Narrow Wide

R

ΘJC

typ 52 45 30 23 ˚C/W

R

ΘJA

typ 100 165 125 105 ˚C/W

Package Specification

PACKAGE DIMENSIONS IN mm (INCHES)

PACKAGE THERMAL DATA

© 1999 Cherry Semiconductor Corporation

Cherry Semiconductor Corporation reserves the

right to make changes to the specifications without

notice. Please contact Cherry Semiconductor

Corporation for the latest available information.

Rev. 3/17/99

Plastic DIP (N); 300 mil wide

0.39 (.015)

MIN.

2.54 (.100) BSC

1.77 (.070)

1.14 (.045)

D

Some 8 and 16 lead

packages may have

1/2 lead at the end

of the package.

All specs are the same.

.203 (.008)

.356 (.014)

REF: JEDEC MS-001

3.68 (.145)

2.92 (.115)

8.26 (.325)

7.62 (.300)

7.11 (.280)

6.10 (.240)

.356 (.014)

.558 (.022)

Surface Mount Narrow Body (D); 150 mil wide

1.27 (.050) BSC

0.51 (.020)

0.33 (.013)

6.20 (.244)

5.80 (.228)

4.00 (.157)

3.80 (.150)

1.57 (.062)

1.37 (.054)

D

0.25 (0.10)

0.10 (.004)

1.75 (.069) MAX

1.27 (.050)

0.40 (.016)

REF: JEDEC MS-012

0.25 (.010)

0.19 (.008)

Surface Mount Wide Body (DW); 300 mil wide

1.27 (.050) BSC

7.60 (.299)

7.40 (.291)

10.65 (.419)

10.00 (.394)

D

0.32 (.013)

0.23 (.009)

1.27 (.050)

0.40 (.016)

REF: JEDEC MS-013

2.49 (.098)

2.24 (.088)

0.51 (.020)

0.33 (.013)

2.65 (.104)

2.35 (.093)

0.30 (.012)

0.10 (.004)

Loading...

Loading...