Page 1

1

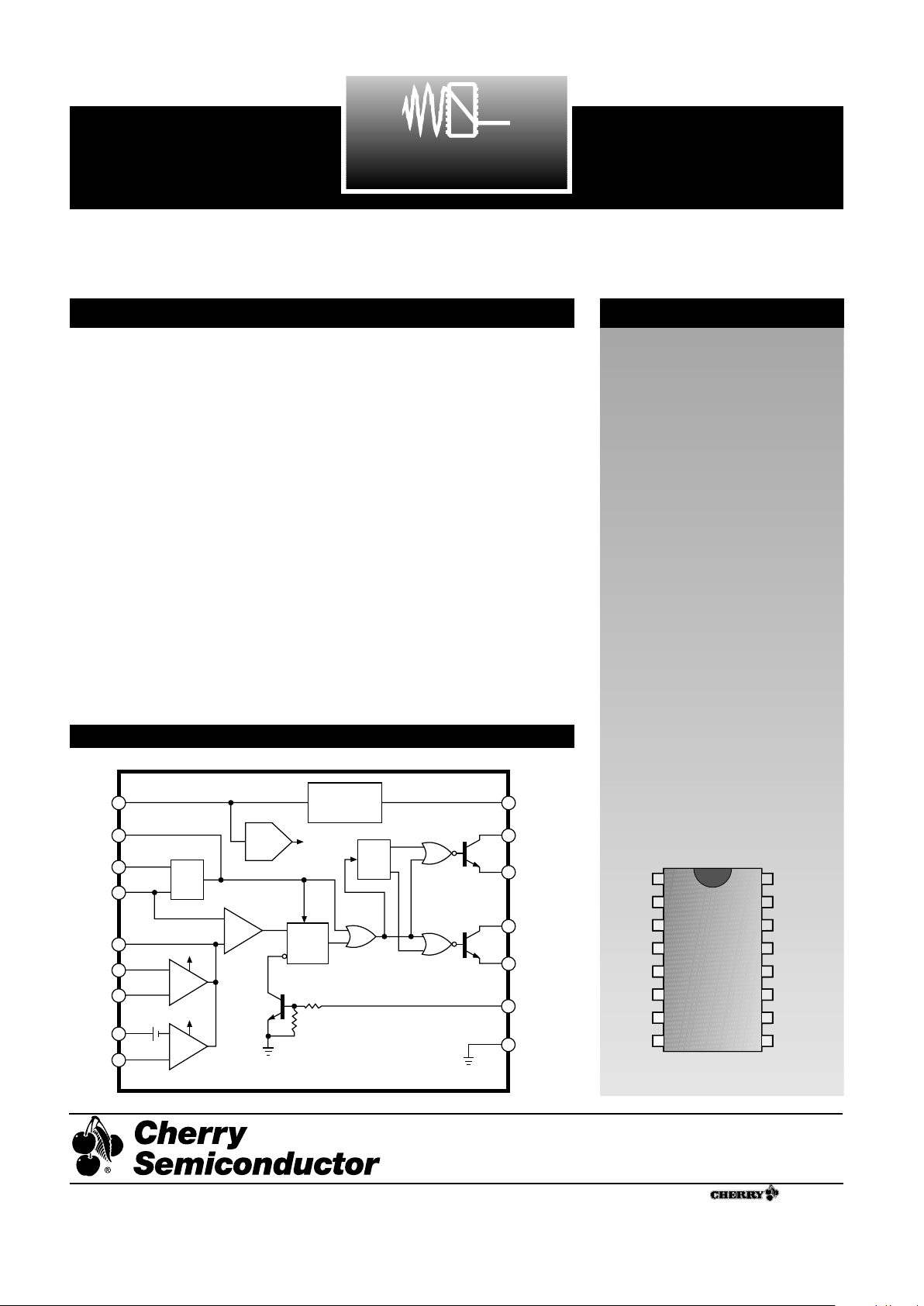

Features

V

IN

SYNC

C

T

COMP

I

SENSE

+

V

OUT

A

R

T

V

OUT

B

E

B

Gnd

EA-

EA+

I

SENSE

-

SHUTDOWN

E

A

V

REF

-

+

+

-

COMP

EA

CL

5V Reference

Regulator

Flip

Flop

PWM

Latch

OSC

UV

Sense

Power to

Internal

Circuitry

T

R

S

CLOCK

S

RAMP

V

IN

V

IN

200mV

1kΩ

10kΩ

■

Precision Reference

Internally Trimmed to ±1%

■

Current Limit

■ Undervoltage Lockout

■ Start-up Supply Current

< 4mA

■ Output to 200mA

■ 60V Output Capability

■ Wide Common-mode

Input Range for Error and

Current Limit Amplifiers

■ PWM Latch Insures Single

Pulse per Period

■ Double Pulse Suppression

■ 200ns Shutdown

■ Guaranteed Frequency

■ Thermal Shutdown

Package Options

16 Lead PDIP & SO Wide

CS3524A

Voltage Mode PWM Control Circuit

with 200mA Output Drivers

16

15

14

13

12

11

11

10

9

1

2

3

4

5

6

7

8

EA-

EA

+

SYNC

I

SENSE

+

I

SENSE

-

R

T

C

T

Gnd

V

REF

V

IN

E

B

V

OUT

B

V

OUT

A

E

A

SHUTDOWN

COMP

CS3524A

Description

Block Diagram

The CS3524A PWM control circuit

retains the same versatile architecture

of the industry standard CS3524

(SG3524) while adding substantial

improvements.

The CS3524 is pin-compatible with

“non-A” versions, and in most applications can be directly interchanged. The

CS3524A, however, eliminates many of

the design restrictions which had previously required additional external

circuitry.

The CS3524A includes a precision 5V

reference trimmed to ±1% accuracy

(eliminating the need for potentiometer

adjustments), an error amplifier with

an output voltage swing extending to

5V, and a current sense amplifier useful in either the ground or power supply output lines. The uncommitted

60V, 200mA NPN output pair greatly

enhances the output drive capability.

The CS3524A features an undervoltage

lockout circuit which disables all internal circuitry (except the reference) until

the input voltage has risen to 8V. This

holds standby current low until turnon, and greatly simplifies the design of

low power, off-line supplies. The turnon circuit has approximately 600mV of

hysteresis for jitter free activation.

Other improvements include a PWM

latch that insures freedom from multiple pulsing within a period, even in

noisy environments; logic to eliminate

double pulsing on a single output, a

200ns external shutdown capability,

and automatic thermal protection from

excessive chip temperature. The oscillator circuit is usable to 500kHz and is

easier to synchronize with an external

clock pulse.

A Company

®

Rev. 10/28/96

Cherry Semiconductor Corporation

2000 South County Trail, East Greenwich, RI 02818

Tel: (401)885-3600 Fax: (401)885-5786

Email: info@cherry-semi.com

Web Site: www.cherry-semi.com

Page 2

2

Electrical Characteristics: 0˚C ≤ T

A

≤ +70˚C for the CS3524A; VIN= VCC= 20V; unless otherwise stated.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Absolute Maximum Ratings

Supply Voltage (VIN).................................................................................................................................................................40V

Collector Supply Voltage (VCC) ...............................................................................................................................................60V

Output Current (Each Output)...........................................................................................................................................200mA

Reference Output Current.....................................................................................................................................................50mA

Oscillator Charging Current ..................................................................................................................................................5mA

Power Dissipation at TA=25˚C.........................................................................................................................................1000mW

Power Dissipation at TJ=+25˚C........................................................................................................................................2000mW

Derate for Case Temperature above +25˚C........................................................................................................16mW/˚C

Storage Temperature Range ................................................................................................................................-65˚C to +150˚C

Lead Temperature Soldering: Wave Solder (through hole styles only)..........................................10 sec. max, 260°C peak

Reflow (SMD styles only) ......................................................................................60 sec. max above 183°C, 230°C peak

CS3524A

■ Turn-on Characteristics

Input Voltage Operating range after Turn-on 8 40 V

Turn-on Threshold 5.5 7.5 8.5 V

Turn-on Current VINTurn-on - 100mV 2.5 4.0 mA

Operating Current VIN= 8 to 40V 5 10 mA

Turn-on Hysteresis* 0.6 V

■ Reference Section

Output Voltage TA= 25˚C 4.90 5.00 5.20 V

Line Regulation VIN= 10 to 40V 10 30 mV

Load Regulation IL= 0 to 20mA 20 50 mA

Temperature Stability* Over Operating Range 20 50 mV

Short Circuit Current V

REF

= 0, TA= 25˚C 80 100 mA

Output Noise Voltage* 10Hz ≤ f ≤ 10kHz, TA= 25˚C 40 µVrms

Long Term Stability* TA= 125˚C; 1000 Hrs. 20 50 mV

■ Oscillator Section (Unless otherwise specified, R

T

= 2700Ω, CT= 0.01µF)

Initial Accuracy TA= 25˚C394347kHz

Temperature Stability* Over Operating Temperature Range 1 2 %

Minimum Frequency RT= 150kΩ, CT= 0.1µF 120 Hz

Maximum Frequency RT= 2.0kΩ, CT= 470pF 500 kHz

Output Amplitude* TA= 25˚C 3.5 V

Output Pulse Width* TA= 25˚C 0.5 µs

Ramp Peak 3.3 3.5 3.7 V

Ramp Valley 0.7 0.9 1.0 V

■ Error Amplifier Section (Unless otherwise specified, V

CM

= 2.5V)

Input Offset Voltage 2 10 mV

Input Bias Current 1 10 µA

Input Offset Current 0.5 1.0 µA

Common Mode

Rejection Ratio VCM= 1.5 to 5.5V 60 75 dB

Power Supply Rejection Ratio VIN= 10 to 40V 50 60 dB

Output Swing Minimum Total Range 0.5 5.0 V

* These parameters are guaranteed by design but not 100% tested in production.

Page 3

3

CS3524A

Electrical Characteristics: continued

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Typical Performance Characteristics

80

60

40

20

0

100 1k 10k 100k 1M

FREQUENCY (Hz)

RF = ∞

OPEN VOLTAGE GAIN (dB)

RF = 1MΩ

RF = 300kΩ

RF = 100kΩ

RF = 30kΩ

VIN = 20V

TA = 25˚C

RF is impedance to ground.

Values below 30kΩ will begin

to limit the maximum

duty-cycle.

50

40

30

20

10

0

12345

INPUT VOLTAGE V

IN

DUTY-CYCLE (ONE OUTPUT) - %

VIN = 20V

R

T

= 2700Ω

TA = 25˚C

0

CT = 10 µF

CT = 1 µF

Note: Duty-Cycle is

percent of two

clock periods that

one output conducts

Duty Cycle vs. Input Voltage

Error Amplifier Voltage Gain vs. Frequency Over RF

■ Error Amplifier Section (Unless otherwise specified, V

CM

= 2.5V): continued

Open Loop Voltage Gain ∆

V

OUT

= 1 to 4V, RL ≥ 10 MΩ 60 80 dB

Gain-Bandwidth* TA= 25˚C, AV= 0dB 3 MHz

■ Current Limit Amplifier (Unless otherwise specified, V

SENSE

= VO)

Input Offset Voltage TA= 25˚C, EA Set for Max. Output 180 200 220 mV

Input Offset Voltage Over Operating Temperature Range 170 230 mV

Input Bias Current -1 -10 µA

Common Mode

Rejection Ratio V

SENSE

= 0 to 15V 50 60 dB

Power Supply Rejection Ratio VIN= 10 to 40V 50 60 dB

Output Swing Minimum Total Range 0.5 5.0 V

Open Loop Voltage Gain ∆

V

OUT

= 1 to 4V, RL≥ 10MΩ 70 80 dB

Delay Time* ∆V

IN

= 300mV 300 ns

■ Output Section (Each Output)

Collector Emitter Voltage I

C

= 100µA 60 80 V

Collector Leakage Current VCE= 50V 0.1 20.0 µA

Saturation IC= 20mA 0.2 0.4 V

IC= 200mA 1.0 2.2 V

Emitter Output Voltage IE= 50mA 17 18 V

Rise Time* TA= 25˚C, R = 2kΩ 200 ns

Fall Time* TA= 25˚C, R = 2kΩ 100 ns

Comparator Delay* TA= 25˚C, V

COMP

to V

OUT

300 ns

Shutdown Delay* TA= 25˚C, V

SHUT

to V

OUT

200 ns

Shutdown Threshold TA= 25˚C, RC= 2kΩ 0.5 0.7 1.0 V

Thermal Shutdown* 165 ˚C

* These parameters are guaranteed by design but not 100% tested in production.

Page 4

4

CS3524A

Typical Performance Characteristics continued

1M

2 5 10 20 100

TIMING RESISTOR - RT (kΩ)

OSCILLATOR FREQUENCY (Hz)

1 50

100k

10k

1k

100

VIN = 20V

T

A

= 25˚C

C

T

= 1.0nf

C

T

= 3.0nf

C

T

= 10nf

C

T

= 30nf

C

T

= 100nf

1.15

RTC

T

f≈

10

2 5 10 20 100

TIMING CAPACITOR - CT (nf)

OUTPUT DEAD TIME (µs)

1 50

5.0

2.0

1.0

0.5

0.2

0.1

VIN = 20V

RT = 2700Ω

TA = 25˚C

Note: Dead time = osc output pulse

width plus output delay

Output Dead Time vs. Timing Capacitor Value

Oscillator Frequency vs. Timing Components Resistor

Over Timing Capacitance

6

1234

DELAY TIME (µs)

OUTPUT (V)

INPUT at I

SENSE+

0

5

4

3

2

1

0

0.2

0.1

0.0

INTPUT (V)

VIN 20V TA 25˚C

EA+ = V

REF

I

SENSE–

= Gnd

OUTPUT at COMP

5%

Overdrive

10%

20%

50%

20

15

10

5

0

1.0

0.5

0.0

0123

DELAY TIME (µs)

OUTPUT (V)

VIN = 20V

R

L

= 2kΩ

T

A

= 25˚C

INTPUT (V)

OUTPUT at

V

O

A

OR V

O

B

INPUT at

SHUTDOWN

Note: Minimum input pulse width

to latch is 200ns

20

15

10

5

0

5

0

0123

DELAY TIME (µs)

OUTPUT (V)INTPUT (V)

4

3

2

1

VIN = 20V

RL = 2kΩ

TA = 25˚C

OUTPUT at

V

OA

or V

OB

INPUT at V

OB

Note: Minimum input pulse width

to latch is 200ns

Shutdown Delay From PWM Comparator

Turn-Off Delay From Shutdown

Current Limit Amplifier Delay

10

9

8

7

6

5

4

3

2

1

0

01020304050

Note: Outputs off. RT = ∞

SUPPLY VOLTAGE VIN (V)

TA = -55°C

TA = 25°C

TA = 125°C

QUIESCENT CURRENT (mA)

Quiescent Supply Current vs. Supply Voltage Over

Temperature

Page 5

5

Typical Performance Characteristics continued

5

4

3

2

1

0

50 100 150 200 250

OUTPUT COLLECTOR CURRENT (mA)

V

CE

SAT (V)

TA = 125˚C

0

TA = 25˚C

TA = –55˚C

Output Saturation Voltage vs. Output Current Over

Temperature

I

S

CS3524A

0.1

R

T

C

T

0.1

10kΩ

2kΩ

10kΩ

1kΩ

2kΩ

100kΩ 100kΩ

SHUTDOWN

2kΩ

1W

2kΩ

1W

V

CC

V

IN

SYNC

V

REF

V

OUT

A

V

OUT

B

E

A

E

B

R

T

CTEA+

EA–

COMP

I

SENSE

+

I

SENSE

-

SHUTDOWN

Gnd

Open Loop Test Circuit

Note: The CS3524A should be able to be tested in any 3524 test circuit with two possible exceptions:

1. The higher gain-bandwidth of the current limit amplifier in the CS 3524A may cause oscillations in an uncompensated 3524 test circuit.

2. The effect of the shutdown, cannot be seen at the compensation terminal, but must be

observed at the outputs.

CS3524A

Page 6

Part Number Description

CS3524AGN16 16 Lead PDIP

CS3524AGDW16 16 Lead SO Wide

CS3524AGDWR16 16 Lead SO Wide (tape & reel)

6

Thermal Data 16 Lead 16L

PDIP SO Wide

R

Θ

JC

typ 42 23 ˚C/W

R

Θ

JA

typ 80 105 ˚C/W

D

Lead Count Metric English

Max Min Max Min

16 Lead PDIP 19.69 18.67 .775 .735

16L SO Wide 10.50 10.10 .413 .398

Package Specification

PACKAGE DIMENSIONS IN mm (INCHES)

Ordering Information

PACKAGE THERMAL DATA

Rev. 10/28/96

CS3524A

© 1999 Cherry Semiconductor Corporation

Cherry Semiconductor Corporation reserves the

right to make changes to the specifications without

notice. Please contact Cherry Semiconductor

Corporation for the latest available information.

Plastic DIP (N); 300 mil wide

0.39 (.015)

MIN.

2.54 (.100) BSC

1.77 (.070)

1.14 (.045)

D

Some 8 and 16 lead

packages may have

1/2 lead at the end

of the package.

All specs are the same.

.203 (.008)

.356 (.014)

REF: JEDEC MS-001

3.68 (.145)

2.92 (.115)

8.26 (.325)

7.62 (.300)

7.11 (.280)

6.10 (.240)

.356 (.014)

.558 (.022)

Surface Mount Wide Body (DW); 300 mil wide

1.27 (.050) BSC

7.60 (.299)

7.40 (.291)

10.65 (.419)

10.00 (.394)

D

0.32 (.013)

0.23 (.009)

1.27 (.050)

0.40 (.016)

REF: JEDEC MS-013

2.49 (.098)

2.24 (.088)

0.51 (.020)

0.33 (.013)

2.65 (.104)

2.35 (.093)

0.30 (.012)

0.10 (.004)

Loading...

Loading...