Page 1

COMMUNICATION SEMICONDUCTORS

CMX838

DATA BULLETIN

FRS/PMR446/GMRS

Family Radio Processor

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

ADVANCE INFORMATION

Features and Applications

• Advanced one-of-any CTCSS

subaudio 50 tone processor

• Fast decode time

• IRQ on any / all valid tones

• Fast scan, group calling, auto

response tone select and

Tone Cloning™ support

• Supply Independent output level

• RF Synthesizer

• FRS, PMR446 and GMRS RF

channels

• Configurable charge pump

• Audio call tone generator

• Audio processing

• Mic amplifier

• Pre/Deemphasis

• Limiter with Supply Independent

output level

• Post limiter filtering

• Mic, Rx and Tx digital gain controls

• Single and dual Tx outputs

• Signal source and external function

switches

• Low power, 3V t o 5V suppl y

• Powersave and sleep modes

• Serial control interface

MICIN

RXIN

RXOUT

TXMOD1

XTAL

AUX I/O

C-BUS

-RF

IN

+RF

IN

REF

IN

SV

SS

SV

DD

XTAL

XTAL

I

SET

CP

OUT

RF SYNTHESIZER

S

TXMOD2

MICOUT

TIMING

GENERATION

IRQ

RPLY DATA

CMD DATA

SERIAL CLOCK

CS

PROGRAMMABLE SUB-

AUDIO PROCESSOR

MODULATION OUTPUT

SELECT AND LEVEL

CONTROL

AUDIO PROCESSOR

BIAS

V

BIAS

V

SS

V

DD

A

GENERAL PURPOSE

TIMER AND TONE

GENERATOR

The highly integrated CMX838 Family Radio Processor includes subaudio, audio, and synthesizer functions

to serve as the core engine for low cost, high performance FRS, PMR446, and GMRS radio designs. Its

flexibility supports both simple and advanced multi-channel radios without cost penalties. Integrated Tx

voltage reference and baseband clock generation circuits eliminate the need for external components. The

CMX838’s features directly supports advanced end product functions such as: group calling, scanning,

automatic scanner response tone setup, and Tone Cloning™.

By using the CMX838 one global radio design can support multiple standards and markets.

Controlled via a serial interface (C-BUS) the Family Radio Processor operates from a 3V to 5V supply and is

available in 28-pin TSSOP (CMX838E1) and 28-pin SOIC (CMX838D1) packages.

Page 2

FRS/PMR446/GMRS Family Radio Processor 2 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

CONTENTS

Section Page

1 Block Diagram............................................................................................................... 7

2 Signal List...................................................................................................................... 8

3 External Components................................................................................................. 10

4 General Description....................................................................................................11

4.1 Audio ...............................................................................................................................11

4.1.1 Digitally Controlled Amplifiers (DCA).................................................................................... 11

4.1.2 Transmit Input Amplifier........................................................................................................12

4.1.3 Audio Switched Capacitor Filters.......................................................................................... 12

4.1.3.1 Preemphasis/Low-pass Filter......................................................................................... 13

4.1.3.2 High-pass Filter ..............................................................................................................14

4.1.3.3 Deviation Limiter Low-pass Filter................................................................................... 14

4.1.4 Deemphasis.......................................................................................................................... 15

4.1.5 Transmit Audio Path .............................................................................................................15

4.1.6 Rec ei ve Audio Path ..............................................................................................................16

4.1.7 Aud io Pat h witho ut Deemphasis or Preemphasis ................................................................ 16

4.1.8 Deviation Limiter................................................................................................................... 17

4.2 Tone Signaling Processor................................................................................................18

4.2.1 Tone encoding/decoding ...................................................................................................... 18

4.2.2 Subaudio RX and TX Filter Characteristics.......................................................................... 19

4.2.3 CTCSS Subaudio Decoder and Encoder Tone Set.............................................................. 21

4.2.4 Tone Signaling Processor Configuration Task Descriptions ................................................ 22

4.2.4.1 Normal Run Mode (Task 0)............................................................................................22

4.2.4.2 Reserved For Test (Task 1-3) ........................................................................................ 22

4.2.4.3 RX Configuration ............................................................................................................ 23

4.2.4.4 TX Configuration............................................................................................................. 24

4.2.4.5 Initialize and Configure................................................................................................... 24

4.3 RF Synthesizer ................................................................................................................ 27

4.3.1 Operating Range and Specifications.................................................................................... 27

4.3.2 Main Divider.......................................................................................................................... 27

4.3.3 Phas e Detec t or & Charge Pump .......................................................................................... 27

4.3.4 Lock Detect Output............................................................................................................... 28

4.3.5 Reference Circuits ................................................................................................................ 28

4.4 Baseband Timing Generation ..........................................................................................28

Page 3

FRS/PMR446/GMRS Family Radio Processor 3 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

5 Software Programming............................................................................................... 29

5.1 C-BUS Serial Interface.....................................................................................................29

5.1.1 8-Bit C-BUS Register Map.................................................................................................... 30

5.1.2 16-Bit C-BUS Register Map.................................................................................................. 31

5.1.2.1 GENERAL RESET ($01)................................................................................................31

5.1.2.2 SETUP Register ($80).................................................................................................... 32

5.1.2.3 AUDIO CONTROL Register ($81).................................................................................. 33

5.1.2.4 RX AUDIO LEVEL CONTROL Register ($82) ............................................................... 34

5.1.2.5 AUDIO POWER AND BANDWIDTH CONTROL Register ($83) ................................... 35

5.1.2.6 TXMOD 1 & 2 CONTROL Register ($88)....................................................................... 36

5.1.2.7 SYNTHESIZER BASEBAND CLK CONTROL Register ($89)....................................... 38

5.1.2.8 SYNTHESIZER GENERAL CONTROL Register ($8A)................................................. 39

5.1.2.9 SYNTHESIZER CHANNEL SELECT Register ($8B)..................................................... 40

5.1.2.10 SYNTHESIZER STATUS Register ($8C)....................................................................... 40

5.1.2.11 SYNTHESIZER 1ST IF OFFSET Register ($8D)........................................................... 41

5.1.2.12 16 BIT SUBAUDIO TASK DATA Register ($8E)............................................................ 41

5.1.2.13 16 BIT SUBAUDIO TEST DATA Register ($8F) ............................................................ 41

5.1.2.14 SYNTHESIZER TEST Register ($90) ............................................................................ 41

5.1.2.15 16 BIT SUBAUDIO TEST READ DATA Register ($91) ................................................. 42

5.1.2.16 SUBAUDIO PROCESSOR GENERAL CONTROL Register ($93)................................ 42

5.1.2.17 SUBAUDIO STATUS Register ($94).............................................................................. 43

5.1.2.18 SUBAUDIO TASK 8 BIT DATA Register ($95).............................................................. 43

5.1.2.19 SUBAUDIO ANALOG CONTROL Register ($97).......................................................... 44

6 Application Notes........................................................................................................ 46

6.1 Overview..........................................................................................................................46

6.2 Basic FRS Radio Architecture..........................................................................................47

6.3 CMX838 Architectural Overview ......................................................................................48

6.4 Detailed CMX838 Architecture......................................................................................... 48

6.4.1 Aud io Proc ess ing..................................................................................................................49

6.4.2 Tone Signaling Processor..................................................................................................... 51

6.4.3 Lev el Control......................................................................................................................... 53

6.4.4 Synthesizer and Charge Pump............................................................................................. 55

6.4.5 Clock Generation.................................................................................................................. 55

6.4.6 Powersave Functions ........................................................................................................... 56

6.5 Control Registers Illustrated.............................................................................................56

6.6 Application Examples.......................................................................................................58

6.6.1 CMX 838 Ini tia li za tion ............................................................................................................ 58

6.6.1.1 Register Descriptions: .................................................................................................... 58

6.6.2 TX, subaudio encoding, single point modulation.................................................................. 59

6.6.2.1 Register Descriptions: .................................................................................................... 59

6.6.3 RX, subaudio decode CTCSS tone or tones........................................................................61

6.6.3.1 Register Descriptions: .................................................................................................... 61

6.6.4 RX, multiple subaudio tone detect - Tone Cloning™............................................................ 63

6.6.4.1 Register Descriptions: .................................................................................................... 63

Page 4

FRS/PMR446/GMRS Family Radio Processor 4 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

7 Performance Specification......................................................................................... 65

7.1 Electrical Performance ..................................................................................................... 65

7.1.1 Abs ol ute Maximum Ratings.................................................................................................. 65

7.1.2 Operating Limits....................................................................................................................65

7.1.3 Operating Characteristics ..................................................................................................... 66

7.1.4 Timing................................................................................................................................... 69

7.2 Packaging........................................................................................................................70

MX-COM, Inc. reserves the right to change specifications at any time and without notice.

Page 5

FRS/PMR446/GMRS Family Radio Processor 5 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

FIGURES

Figure Page

Figure 1: Block Diagram.....................................................................................................................................7

Figure 2: Recommended External Components..............................................................................................10

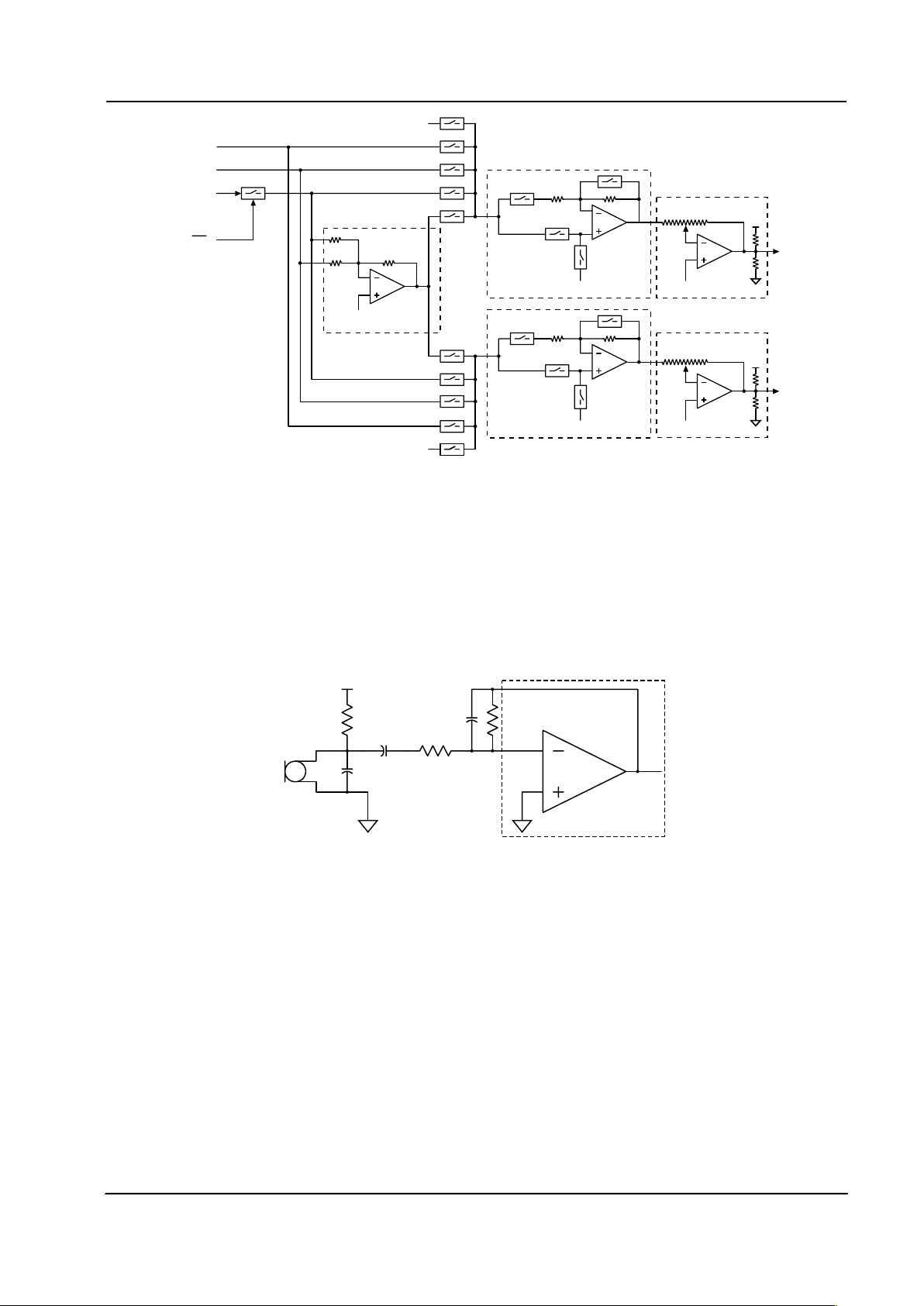

Figure 3: Audio Processing Block Diagram......................................................................................................11

Figure 4: Digitally controlled amplifiers and switch matrix for adjusting and switching transmit audio and

subaudio signals. ..............................................................................................................................12

Figure 5: TX Input Amplifier.............................................................................................................................. 12

Figure 6: Magnitude response for input low-pass filter. ................................................................................... 13

Figure 7: Magnitude response for preemphasis filter.......................................................................................13

Figure 8: Magnitude response of high-pass filter.............................................................................................14

Figure 9: Magnitude response of post-deviation limiter low-pass filter. ........................................................... 14

Figure 10: Magnitude response of deemphasis filter.......................................................................................15

Figure 11: Transmit audio path frequency response with preemphasis. ......................................................... 15

Figure 12: Receive audio path frequency response with deemphasis.............................................................16

Figure 13: Audio path frequency response without preemphasis or deemphasis. .......................................... 16

Figure 14: Deviation limiter block diagram . ......................................................................................................17

Figure 15: Subaudio Block Diagram.................................................................................................................18

Figure 16: Subaudio RX filter gain for normal CTCSS operation.....................................................................19

Figure 17: Subaudio RX filter delay for normal CTCSS operation................................................................... 19

Figure 18: Subaudio TX level for normal CTCSS operation (Magnitude scale with respect to 0dBV) ............20

Figure 19: Subaudio TX filter delay for normal CTCSS operation. ..................................................................20

Figure 20: RF Synthesizer block diagram........................................................................................................27

Figure 21: Block diagram of main programmable divider.................................................................................27

Figure 22: C-BUS transaction timing diagram..................................................................................................29

Figure 23: Basic FRS Radio Tx Architecture ................................................................................................... 47

Figure 24: Basic FRS Radio Rx Architecture...................................................................................................47

Figure 25: CMX838 Main Function Blocks....................................................................................................... 48

Figure 26: CMX838 Main Sections................................................................................................................... 48

Figure 27: Audio Processing ............................................................................................................................ 49

Figure 28: Example Audio RX Path.................................................................................................................. 49

Figure 29: Example Audio TX Voice Path........................................................................................................50

Figure 30: Example Audio TX Internally Generated T one with Lou ds peak er Enabled Path ...........................50

Figure 31: Tone Signaling Processor...............................................................................................................51

Figure 32: Example CTCSS Tone Decoder Path.............................................................................................52

Figure 33: Example CTCSS Tone Encoder Path.............................................................................................52

Figure 34: Example Internal Audio Tone Enco der Pat h................................................................................... 53

Figure 35: Level Control...................................................................................................................................53

Figure 36: Example Single Point Modulati on Level Pat h ................................................................................. 54

Figure 37: Example Two-Point Modulation Level Paths .................................................................................. 54

Figure 38: Example Single Point Modul ation with Varied Subaudio Level Paths............................................54

Figure 39: Synthesizer and Charge Pump.......................................................................................................55

Figure 40: Clock Generation ............................................................................................................................ 55

Figure 41: Powersave Scope and Related Control Regis ters.......................................................................... 56

Page 6

FRS/PMR446/GMRS Family Radio Processor 6 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

Figure 42: Synthesizer to Baseband Clock Control, $89 ................................................................................. 56

Figure 43: Setup, $80.......................................................................................................................................57

Figure 44: Audio ($81), RX Audio Level ($82) and Subaudio Analog ($97) Control ....................................... 57

Figure 45: Audio Power and Bandwidth Control, $83 ...................................................................................... 58

Figure 46: TXMOD1 & TXMOD2 Control, $88.................................................................................................58

Figure 47: Application Exam ple TX, Subaudio Enc od i ng, Sin gle Poi nt Modu lat ion ........................................61

Figure 48: C-BUS Timing ................................................................................................................................. 69

Figure 49: 28-pin TSSOP (E1) Mechanical Outline: Order as part no. CMX838E1 ....................................... 70

Figure 50: 28-pin SOIC (D1) Mechanical Outline: Order as part no. CMX838D1...........................................70

Page 7

FRS/PMR446/GMRS Family Radio Processor 7 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

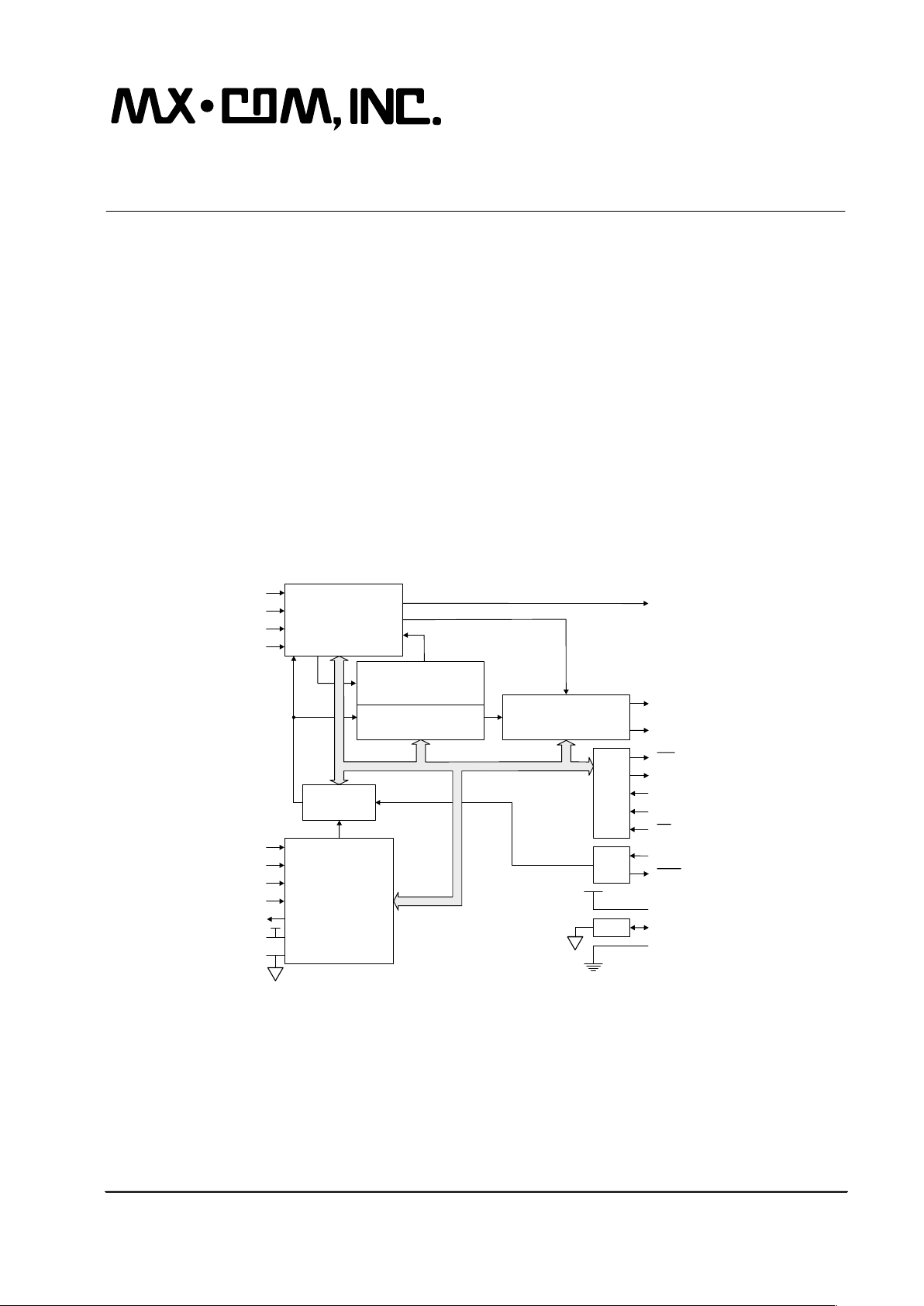

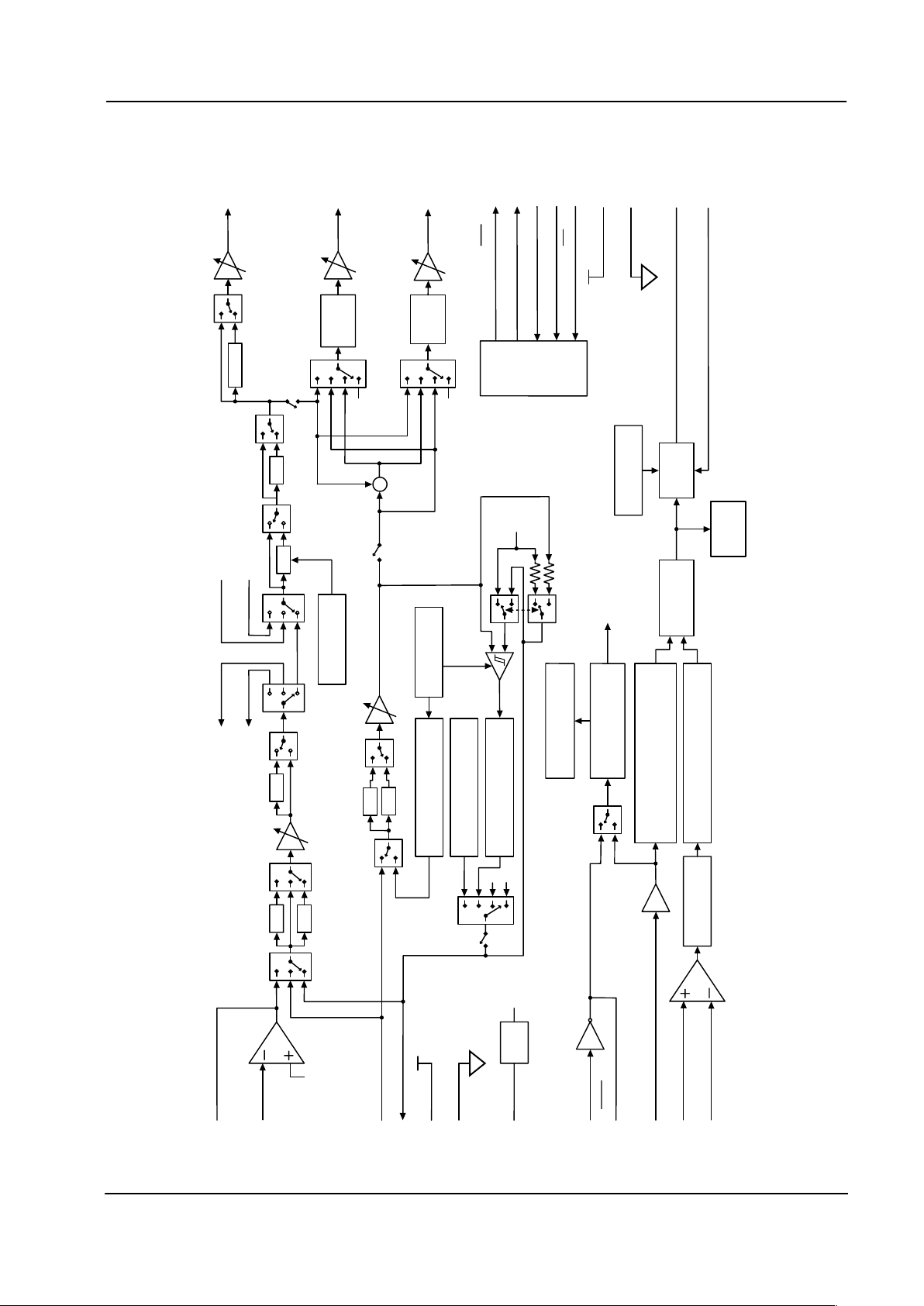

1 Block Diagram

CTCSS DECODERS

+

CTCSS ENCODE

RXIN

BIAS

AUX I/O

C-BUS

Serial

Interface

DIVIDE 32/33

PROGRAMMABLE DIVIDER

12 BIT PROGRAMMABLE

REFERENCE COUNTER

PHASE

DETECTOR

CHARGE

PUMP

LOCK

DETECT

+RF

I N

-RF

I N

REF

I N

SV

SS

SV

DD

V

BIAS

XTAL

XTAL

I

SET

CP

OUT

V

SS

V

DD

S

BASEBAND

TIMING GENERATION

SERIAL CLOCK

CS

LPF

V

BIAS

V

BIAS

V

BIAS

AUDIOTONE ENCODE

0°/180°

phase

0°/180°

phase

CMD DATA

RPLY DATA

IRQ

TXMOD1

TXMOD2

RX NOTONE/

TX DURATION TIMER

VOLTAGE REF

BPF

MICIN

MICOUT

PRE

LPF

HPF

LPF

LIM

B

IN

A

IN

A

OUTBOUT

V

BIAS

VOLTAGE REF

DEEMP

VOLTAGE REF

1

0

V

BIAS

RXOUT

Figure 1: Block Diagram

Page 8

FRS/PMR446/GMRS Family Radio Processor 8 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

2 Signal List

Package Signal Description

Pin No.

E1/D1

Name Type

1 RXIN input Receive input for both audio and subaudio signals.

2 AUX I/O input/output When configured as an input this pin can be used to route

externally generated ringing or alert signals to the Rx and

Tx audio paths.

When configured as an output this pin allows for

monitoring internally generated ringing or alert signals.

See Section 4.2.4.5.3

3 MICOUT output Microphone amplifier feedback output.

4 MICIN input Microphone amplifier input. This is the inverting input to a

high gain opamp, suitable for use with common

microphones.

5 CP

OUT

output Synthesizer charge pump output. Apply to external loop

filter that drives the control input of an external VCO

6

I

SET

input Synthesizer charge pump current control. Connect via

external resistor to SV

SS

to set charge pump current.

7 SVDD power Synthesizer positive supply. This signal must be

decoupled to SV

SS

by a capacitor mounted close to the

device pins.

8 -RFIN input Synthesizer RF negative input. Connect this pin to SVSS

(synthesizer common) when a non-differential input signal

is applied to +RF

IN

.

9 +RFIN input Synthesizer RF positive input.

10 SVSS power Synthesizer negative supply.

11 REFIN input Synthesizer reference oscillator input.

12 XTAL input The input to the on-chip oscillator, for external Xtal circuit

or clock. This input should be connected to V

SS

, Circuit

Common, when the device is configured to generate the

XTAL clock internally from the REF

IN

clock.

13

XTAL

output Inverted output of the on-chip crystal oscillator. This pin

should not be connected (left open) when the device is

configured to generate the XTAL clock internally from the

REF

IN

clock.

14

CS

input C-BUS select data loading control function input. This

input controls C-BUS transfer initiation, completion and

cancellation.

15

IRQ

output Interrupt output, logic '0' active level. This is a 'wire-

Orable' output, enabling the connection of multiple

peripherals to 1 interrupt port on an external µController.

This pin has a low impedance pull-down to logic "0" when

active and a high-impedance when inactive. An external

pull-up resistor is required. Interrupt outputs may be

configured via mask bits via C-BUS commands.

16 RPLY DATA output Reply data output to C-BUS serial control port. Output

reply data bytes are synchronized to the CLK clock input

under the control of the

CS input. This 3-state output is

held at high impedance when not driving output data.

17 CMD DATA input Command data input to C-BUS serial control port. Data is

loaded into this device in 8-bit bytes, MSB (D7) first, and

LSB (D0) last, synchronized to the CLK clock input.

Page 9

FRS/PMR446/GMRS Family Radio Processor 9 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

Package Signal Description

18 SERIAL CLOCK input Serial clock input to C-BUS serial control port. This clock

input controls transfer timing of commands and data to

and from the device.

19 VSS power Negative supply (Circuit Common)

20 TXMOD2 output Transmit Output 2 internally switch selected to be at any

of (1) V

BIAS

, (2) transmit subaudio or (3) transmit audio

summed with subaudio.

21 TXMOD1 output Transmit Output 1 internally switch selected to be at any

of (1) V

BIAS

, (2) transmit audio or (3) transmit audio

summed with subaudio.

22 VDD supply Positive supply. Levels and voltages are dependent upon

this supply. This signal must be decoupled to V

SS

by a

capacitor mounted close to the device pins.

23 RXOUT output Processed receive audio output.

24 BIN input External processing Path B input.

25 AIN input External processing Path A input.

26 V

BIAS

bi-directional A bias line for the internal circuitry, driven to VDD/2 by a

high impedance source. This signal must be decoupled by

a capacitor mounted close to the device pins.

27 B

OUT

output External processing Path B output. This provides internal

switch controlled access to either Rx or Tx audio signals

for external processing such as expanding and

unscrambling.

28 A

OUT

output External processing Path A output. This provides internal

switch controlled access to either Rx or Tx audio signals

for external processing such as compressing and

scrambling.

Table 1: Signal List

Page 10

FRS/PMR446/GMRS Family Radio Processor 10 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

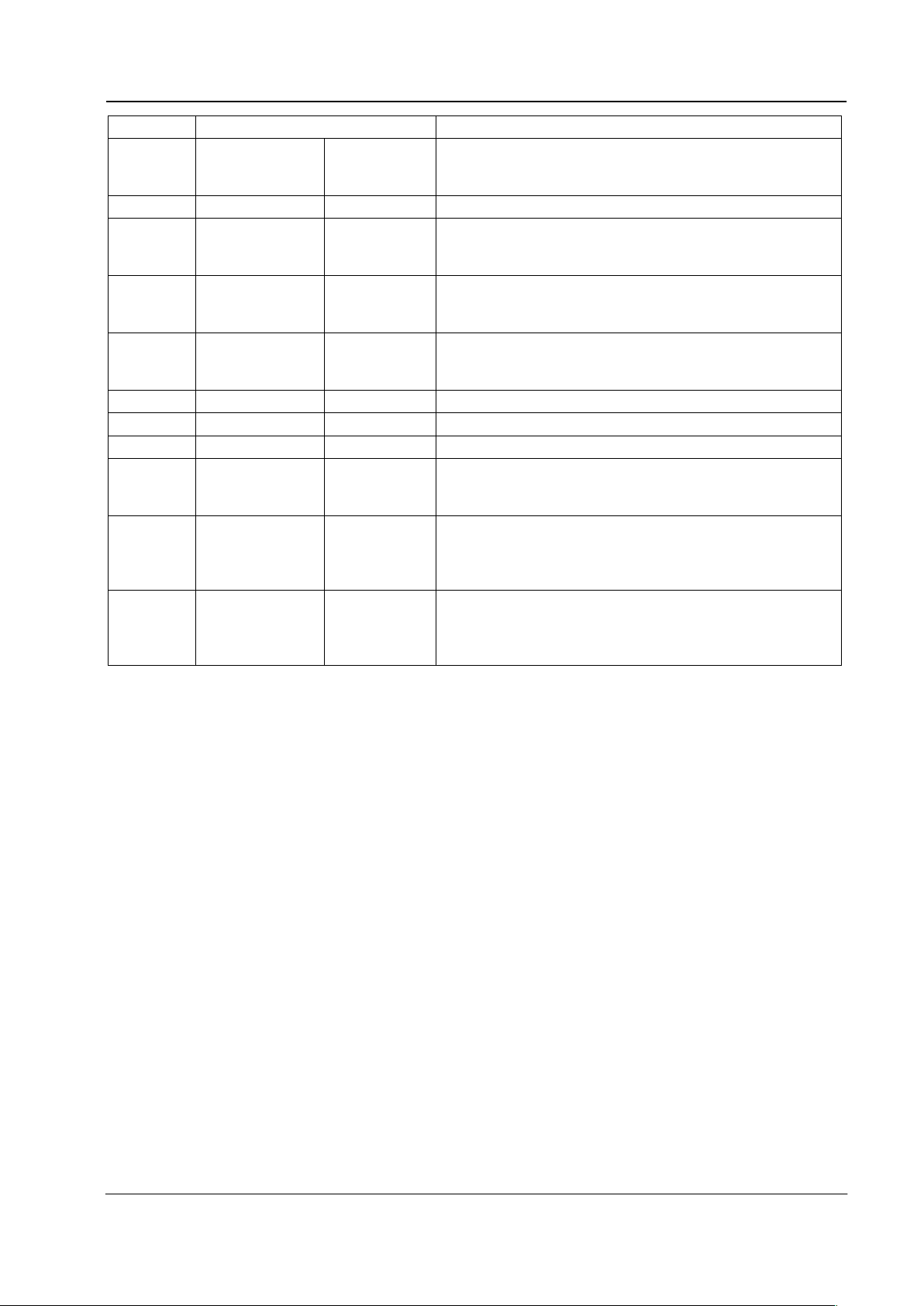

3 External Components

A

OUT

B

OUT

V

BIAS

A

IN

B

IN

RXOUT

V

DD

TXMOD1

TXMOD2

RXIN

IRQ

RPLY DATA

CMD DATA

SERIAL CLOCK

V

SS

CMX838E1

AUX I/O

MICOUT

MICIN

CP

OUT

I

SET

SV

DD

REF

IN

-RF

IN

+RF

IN

SV

SS

XTAL

XTAL

CS

C-BUS

Serial

Control

Interface

C1

C2

C3

C4

C5

C6

C7

C8

C15

C14

C13

C12

C11

C10

C9

U2

RF

Section

REF

OSC

VCO

From RF Receiver

FromTone Generator

Microphone

RF

Section

R1

R2

R4

R3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

C16

Optional

External

Audio

Processing

Figure 2: Recommended External Components

R1 Note 1

470k

Ω

±5% C9 0.1µF ±20%

R2 Note 1

10k

Ω

±5% C10 0.1µF ±20%

R3 Note 2

100k

Ω

±10% C11 0.1µF ±20%

R4 Note 3 ±10% C12 0.1µF ±20%

C1 0.1µF ±20% C13 0.1µF ±20%

C2 0.1µF ±20% C14 0.1µF ±20%

C3 Note 1 33pF ±20% C15 0.1µF ±20%

C4 Note 1 0.1µF ±20% C16 47.0pF ±20%

C5 Note 2 0.1µF ±20%

C6 0.1µF ±20%

C7 0.1µF ±20% U2 Speaker driver

e.g. LM386

C8 0.1µF ±20%

External Components Notes:

1. R1, R2, C3 and C4 form the gain components for the Tx Input Amplifier (microphone amplifier). R1

should be chosen as required by the signal level, using the following formula:

Gain = -R1/R2

C3 x R1 should be chosen so as not to compromise the high frequency performance and C4 x R2

should be chosen so as not to compromise the low frequency performance.

2. R3 and C5 values are dependent on microphone specifications.

3. R4 Sets charge pump source current. The value of R4 can vary between about 50k

Ω and 250kΩ. This

gives a charge pump current range of 0.8mA to 8.4mA

Page 11

FRS/PMR446/GMRS Family Radio Processor 11 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

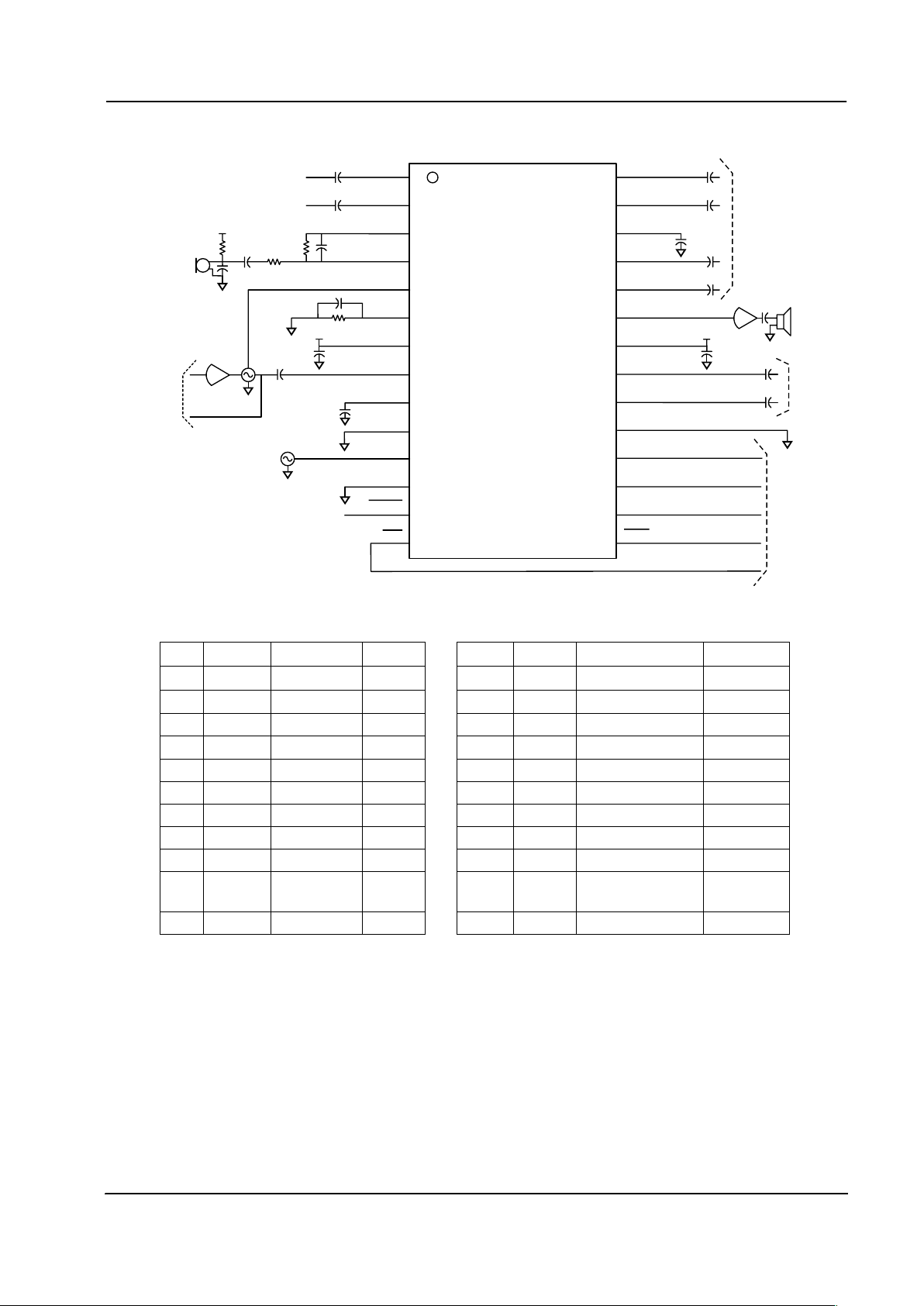

4 General Description

4.1 Audio

The audio signal processing is designed to meet or exceed the requirements for basic audio filtering, gain

control and deviation limiting in a FRS radio. Figure 3 is a block diagram of the audio circuitry.

RXIN

TX SUBAUDIO (From On-Chip SubaudioTone Generator)

RXOUT

AUX I/O

MICIN

MICOUT

V

REF

LP

PRE

1

1

1

DE

1

TXMOD1

A

OUT

B

OUT

A

IN

B

IN

DEEMPHASIS NETWORK

DEVIATION LIMITER AND POST-LIMITER LPF

PREEMPHASIS OR 2

ORDER LPF

ND

6 ORDER HPF

TH

LPF BYPASS

LIMITER BYPASS

AUDIO

INPUT 1

SELECT

AUDIO OUT

SELECT

PRE LPF CTRL HPF BYPASS

DEBP

RX AUDIO OUT

LEVEL

AUDIO

LEVEL

V

REF

V

BIAS

TOS

VLHVLL

TOS

TXMOD2

TX/RX

TONE GENERATOR

AUXPUPEN

AUDIO

INPUT 2

SELECT

TXMOD

SWITCH

MATRIX and

PHASE

CONTROL

See Figure 4

Figure 3: Audio Processing Block Diagram

4.1.1 Digitally Controlled Amplifiers (DCA )

There are five DCAs on-chip. They are used to set signal levels for audio in/out, subaudio in/out, receive

audio out (volume control), modulation out1, and modulation out2. The audio in/out DCA is adjustable in

0.5dB steps over a +7.5dB to –7.5dB range, see Section 5.1.2.3.

The volume control level DCA is adjustable

in 1.5dB steps over a +12dB to –33dB range, see Section 5.1.2.4. The subaudio signal level in/out DCA is

adjustable in 0.5dB steps over a +7.5dB to –7.5dB range, see Section 5.1.2.19

The modulation level controls are composed of two DCAs, and a switch matrix, see Figure 4. Each

modulation level DCA, modulation out1 and modulation out2, can be switched to select either the output of

the audio processor, or the output of the tone generator, or the addition of the audio and tone. In addition,

there is an internally generated DC volume (labeled ‘TOS’ in Figure 4), which can be sent to the MOD1 and

MOD2 DCA’s. This signal is not generally applicable to FRS radios. However, in some cases it may be

desirable for testing or signal generation. The modulation out1 DCA is adjustable in 0.5dB steps over a

+7.5dB to –7.5dB range and the Modulation Out2 DCA is adjustable in 0.25dB steps over a +3.75dB to

-3.75dB range, see Section 5.1.2.6. To obtain inverse signals of mod 1and mod 2, the MSB from the first byte

(bit 7) and the MSB from second byte (bit 15) have to set to logic 1, see Section 5.1.2.6.

Page 12

FRS/PMR446/GMRS Family Radio Processor 12 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

TXMOD1

TXMOD2

V

BIAS

V

BIAS

V

BIAS

V

BIAS

V

BIAS

V

BIAS

TOS

SUBAUDIOTONE IN

LOW R

LOW R

LOW R

LOW R

LOW R

LOW R

LOW R

LOW R

SUM

Gain/Attenuation

Gain = +/-1

TX/RX

V

BIAS

Gain/Attenuation

Gain = +/-1

AUDIO IN

Figure 4: Digitally controlled amplifiers and switch matrix for adjusting and switching transmit audio

and subaudio signals.

4.1.2 Transmit Input Amplifier

The transmit input amplifier is a high gain low-noise operational amplifier. Figure 5 is a simplified schematic

showing the external components required for typical application with an electret condenser microphone. The

external component values should be selected such that the feedback resistor will be greater than 10k

Ω and

the minimum gain should be greater than 6dB.

In some cases, it may be desirable to implement a pre-emphasis characteristic of appropriately configuring

the external component values around the TX input amplifier. In this case, the internal preemphasis should be

bypassed (via C-BUS).

Figure 5: TX Input Amplifier

4.1.3 Audio Switched Capacitor Filters

Four standard (composed of biquadratic sections) switched capacitor filters are used in the audio section. A

preemphasis filter (+6dB per octave from 300 to 3000 Hz intended for transmit only) is implemented using

2

nd

order switched capacitor network, which can be configured (via C-BUS) to be a 2nd order low-pass. A

6

th

order high-pass filter is used to remove subaudible tones and bandwidth limit the incoming receive or

transmit audio signal prior to being input to the limiter. A 4

th

order low-pass filter follows the deviation limiter.

This filter smoothes the transients generated by the deviation limiter. Finally, a deemphasis filter (-6dB per

octave from 300 to 3000 Hz intended for receive only) is implemented using a 2

nd

order switched capacitor

network. See Section 5.1.2 for details on configuring audio filters.

Page 13

FRS/PMR446/GMRS Family Radio Processor 13 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

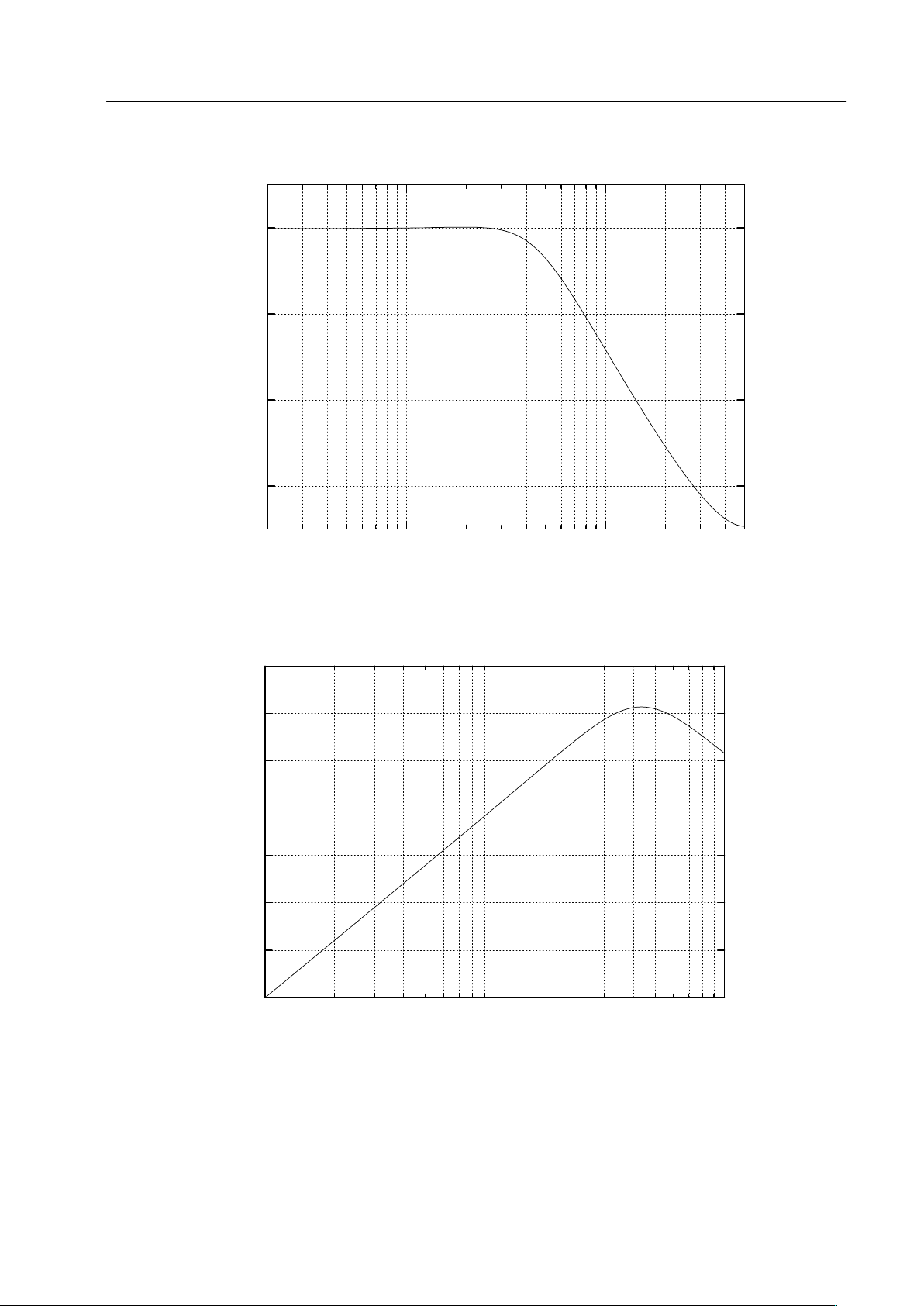

4.1.3.1 Preemphasis/Low-pass Filter

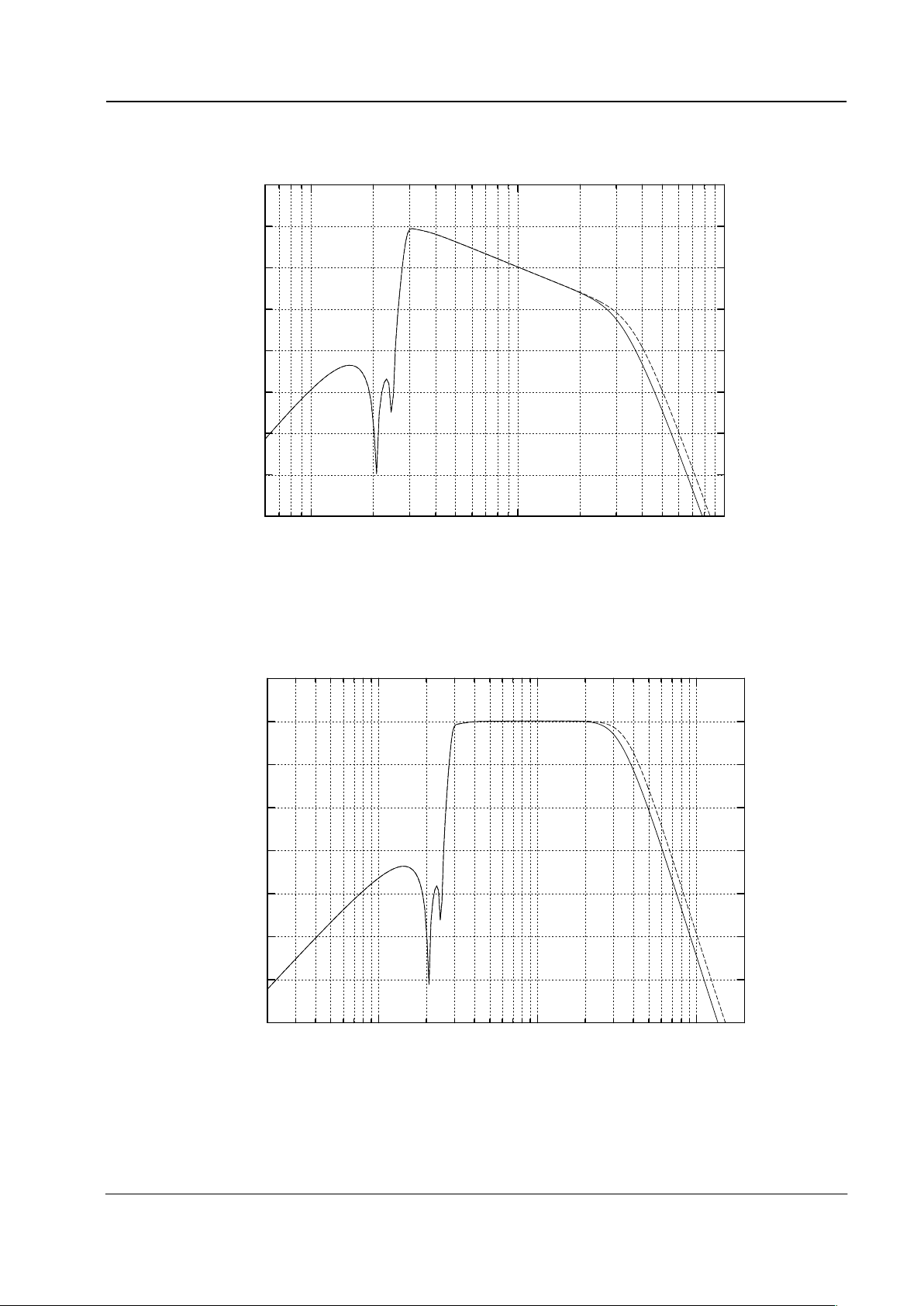

Figure 6 shows magnitude response for the Input Preemphasis/Low-pass Filter when programmed for lowpass mode. This mode would typically be selected when processing Rx audio.

-35

-30

-25

-20

-15

-10

-5

0

5

1000 10000

Magnitude (dB)

Frequency (Hz)

Figure 6: Magnitude response for input low-pass filter.

Figure 7 shows magnitude response for the Input Preemphasis/Low-pass Filter when programmed for

Preemphasis mode. This mode would typically be selected when processing Tx audio.

-20

-15

-10

-5

0

5

10

15

100 1000 10000

Magnitude (dB)

Frequency (Hz)

Figure 7: Magnitude response for preemphasis filter.

Page 14

FRS/PMR446/GMRS Family Radio Processor 14 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

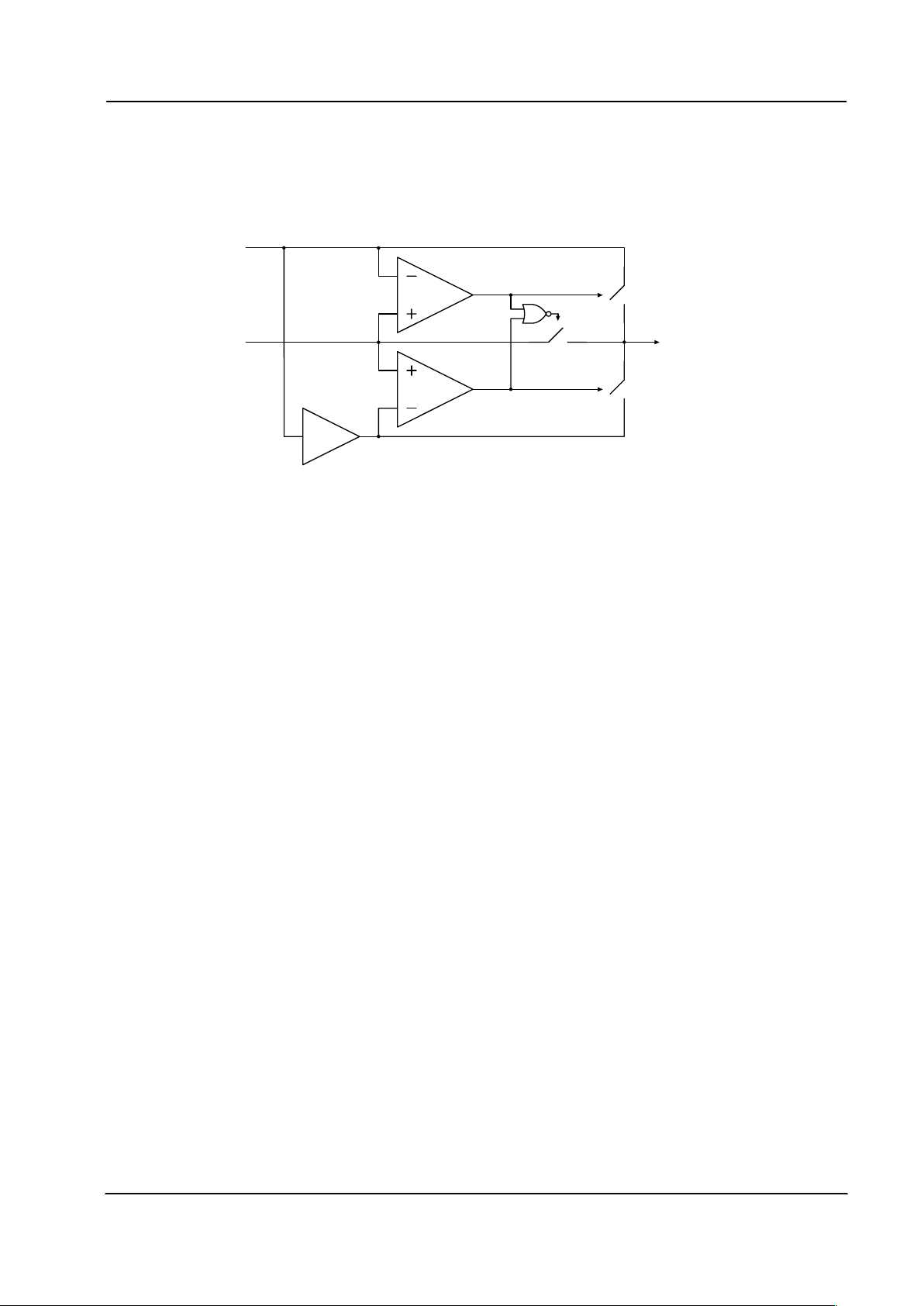

4.1.3.2 High-pass Filter

Figure 8 shows the magnitude response for the Audio High Pass Filter. This filter’s purpose is to suppress

subaudio tones when processing both Rx and Tx audio.

-80

-70

-60

-50

-40

-30

-20

-10

0

10

10 100 1000 10000

Magnitude (dB)

Frequency (Hz)

Figure 8: Magnitude response of high-pass filter.

4.1.3.3 Deviation Limiter Low-pass Filter

The magnitude response for narrowband and wideband modes is shown in Figure 9. Narrow-band mode is

generally required for transmitting in systems having RF Channel BW

≤12.5kHz (e.g. FRS).

-40

-35

-30

-25

-20

-15

-10

-5

0

5

1000 10000

Magnitude (dB)

Frequency (Hz)

WIDE BAND

NARROW BAND

Figure 9: Magnitude response of post-deviation limiter low-pass filter.

Page 15

FRS/PMR446/GMRS Family Radio Processor 15 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

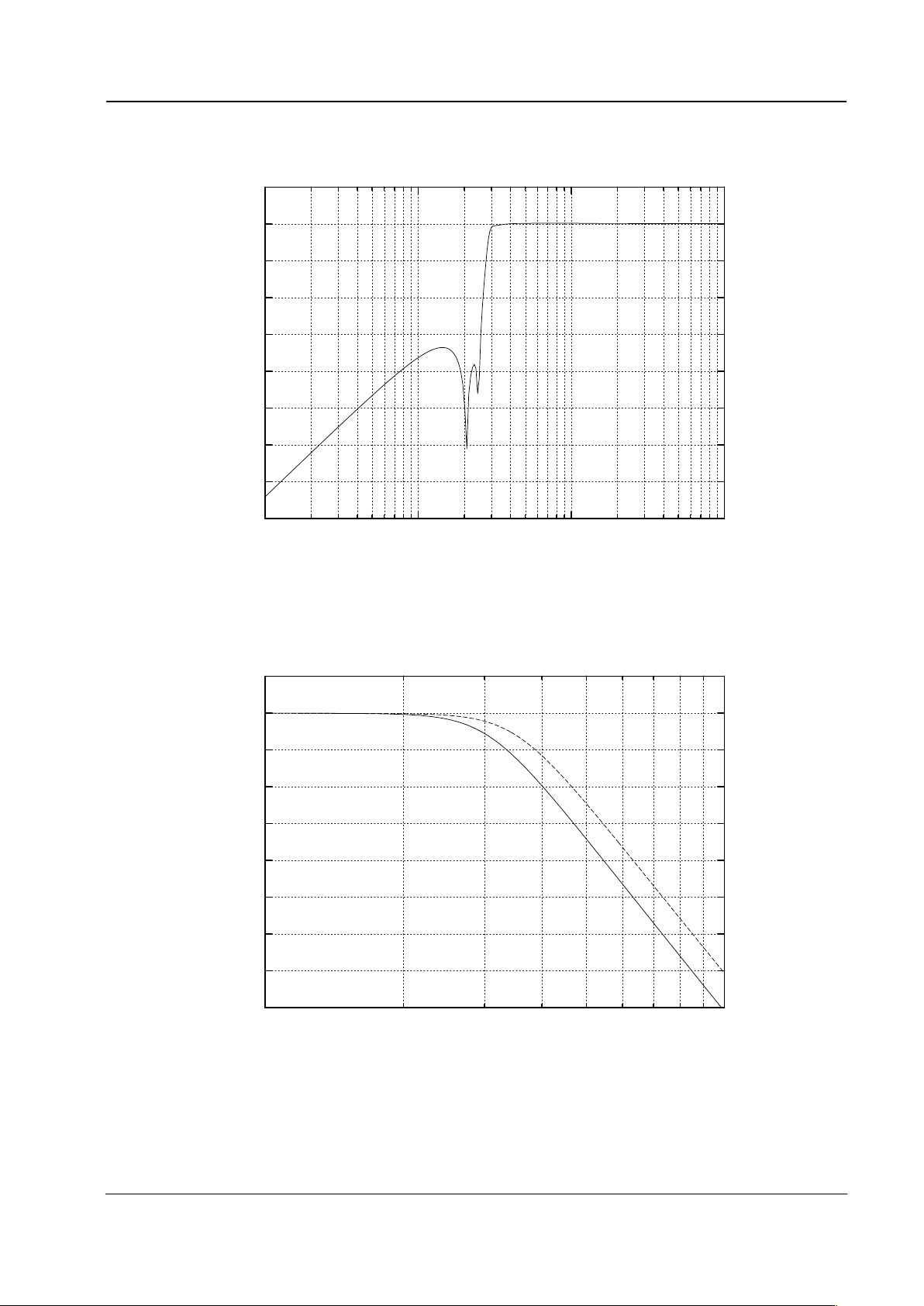

4.1.4 Deemphasis

Figure 10 shows magnitude response for the Deemphasis Filter. This filter precedes the Rx Audio Level

Control and is generally required to process Rx audio.

-20

-15

-10

-5

0

5

10

15

100 1000 10000

Magnitude (dB)

Frequency (Hz)

Figure 10: Magnitude response of deemphasis filter.

4.1.5 Transmit Audio Path

Overall magnitude response for the transmit audio path for wideband and narrowband with preemphasis is

shown in Figure 11.

-80

-60

-40

-20

0

20

100 1000 10000

Magnitude (dB)

Frequency (Hz)

NARROW BAND

WIDE BAND

Figure 11: Transmit audio path frequency response with preemphasis.

Page 16

FRS/PMR446/GMRS Family Radio Processor 16 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.1.6 Receive Audio Path

Overall magnitude response for the receive audio path for wideband and narrowband with deemphasis is

shown in Figure 12.

-60

-50

-40

-30

-20

-10

0

10

20

100 1000 10000

Magnitude (dB)

Frequency (Hz)

NARROW BAND

WIDE BAND

Figure 12: Receive audio path frequency response with deemphasis.

4.1.7 Audio Path without Deemphasis or Preemphasis

The magnitude response for the audio path (could apply to transmit or receive) without the preemphasis or

deemphasis is shown in Figure 13.

-70

-60

-50

-40

-30

-20

-10

0

10

100 1000 10000

Magnitude (dB)

Frequency (Hz)

NARROW BAND

WIDE BAND

Figure 13: Audio path frequency response without preemphasis or deemphasis.

Page 17

FRS/PMR446/GMRS Family Radio Processor 17 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

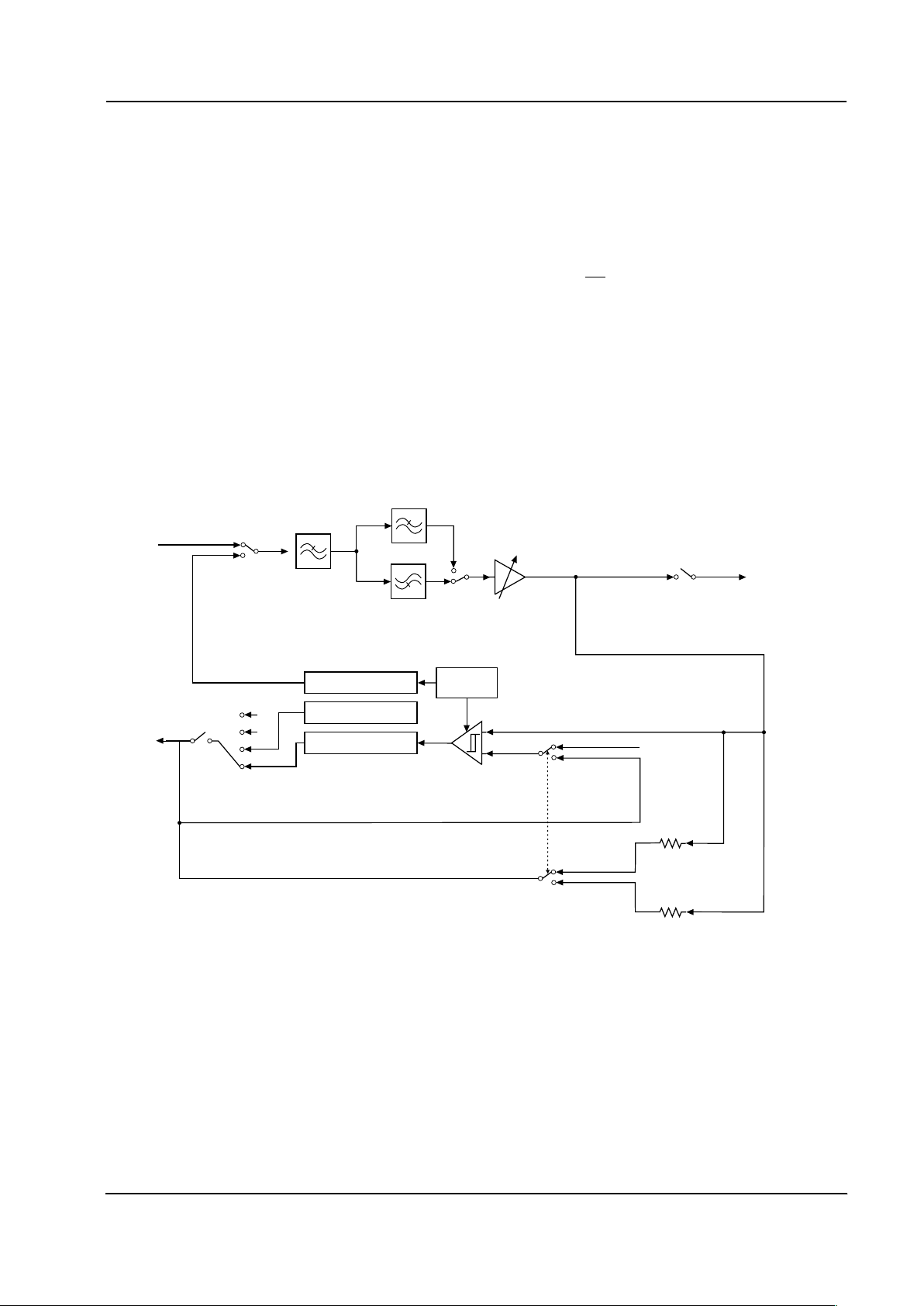

4.1.8 Deviation Limiter

The purpose of the deviation limiter is to limit the signal level at baseband prior to reaching the RF modulator.

This is necessary to avoid co-channel interference as well as conform to the spectral constraints stipulated by

regulatory agencies (e.g. FCC). Figure 14 is a block diagram of the limiter circuitry. Applying a DC voltage

between V

DD

and VDD/2 to the reference input sets the maximum peak-to-peak signal level. This reference is

internally set so the maximum signal level is 2.196V

P-P

and is constant over supply voltage.

-1

REF

I N

TX AUDIO

LIMITED SPEECH TO

POST DEVIATION

LIMITER FILTER

Figure 14: Deviation limiter block diagram.

Page 18

FRS/PMR446/GMRS Family Radio Processor 18 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

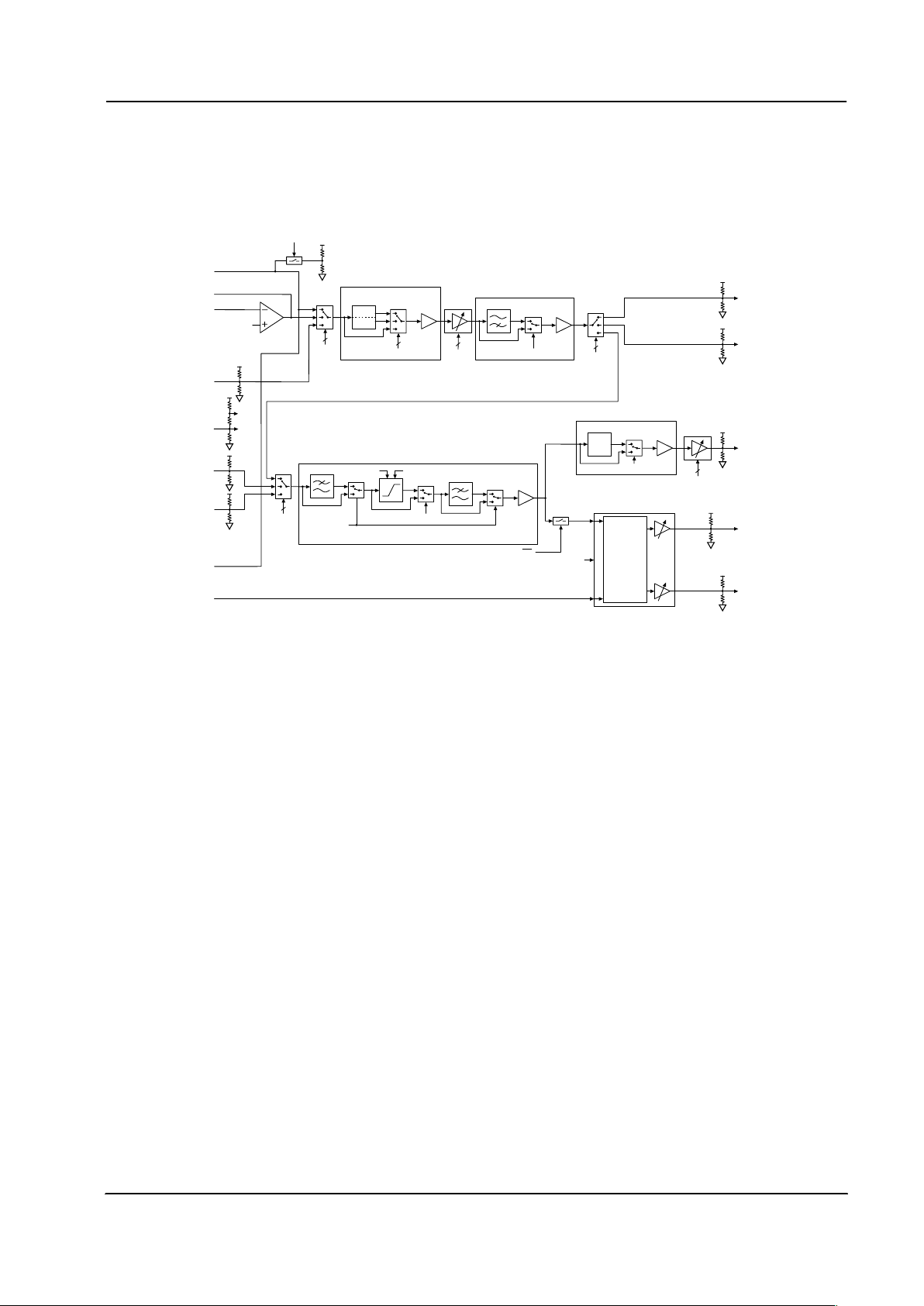

4.2 Tone Signaling Processor

4.2.1 Tone encoding/decoding

The tone signaling processor includes CTCSS encode and decode functions as well as an audio frequency

ringing/alert tone generator. The signaling processor is comprised of a configurable analog filter controlled by

the SUBAUDIO ANALOG CONTROL Register ($97) and a digital processor controlled by configuration tasks.

All device configuration data is passed over the device’s C-BUS serial interface. The configuration tasks to

setup the digital processor are simply C-BUS transaction sequences, which download task argument data

followed by a task request command. In typical applications, once the tone signaling processor is initialized,

its primary behavior (CTCSS encode and decode) is steered by the

RXTX/ bit of the SETUP Register ($80).

The subaudio filter is shared between transmit and receive. It is used to remove the speech signal from the

receive subaudio signal, leaving only the subaudible squelch signal as input to the digital processor. This filter

is also used to smooth the digitally generated subaudible signals in the transmit mode. Following the filter is a

gain trimmer stage that can adjust the signal level

±7.5dB in 0.5dB steps into the decoding section or out to

the modulation section. Approximately 20dB of gain is provided in the receive path and 20dB of attenuation in

the transmit path.

LPF1

CTCSS encode

CTCSS decoders

Band Gap

Reference

audio tone encode

V

BIAS

0

1

RXIN

to Modulation

Control Block

AUX

AUX Output

Control

Task

External DC

Restoration

Subaudio

Filter

Input

Select

Subaudio

HPF/LPF

Select

Subaudio

Filter

Output

Enable

Subaudio

LPF1

Gain

2 or 22db

HPF

LPF2

Subaudio

RX and TX

Levels

-7.5 to 7.5dB

External DC

Restoration

Control with

Initialization Tasks

Subaudio

LPF2

Gain

0 or -18dB

Figure 15: Subaudio Block Diagram

Page 19

FRS/PMR446/GMRS Family Radio Processor 19 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

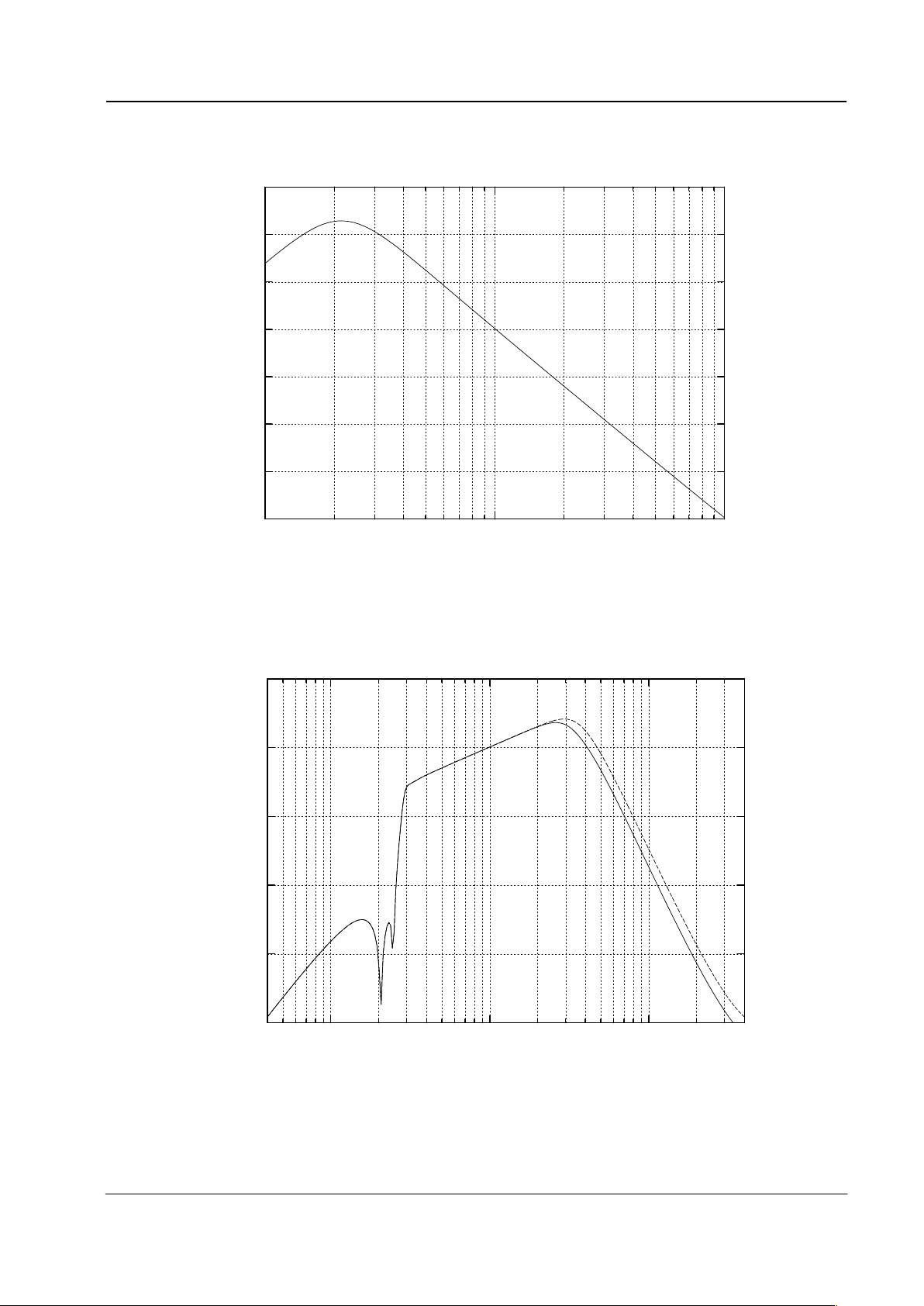

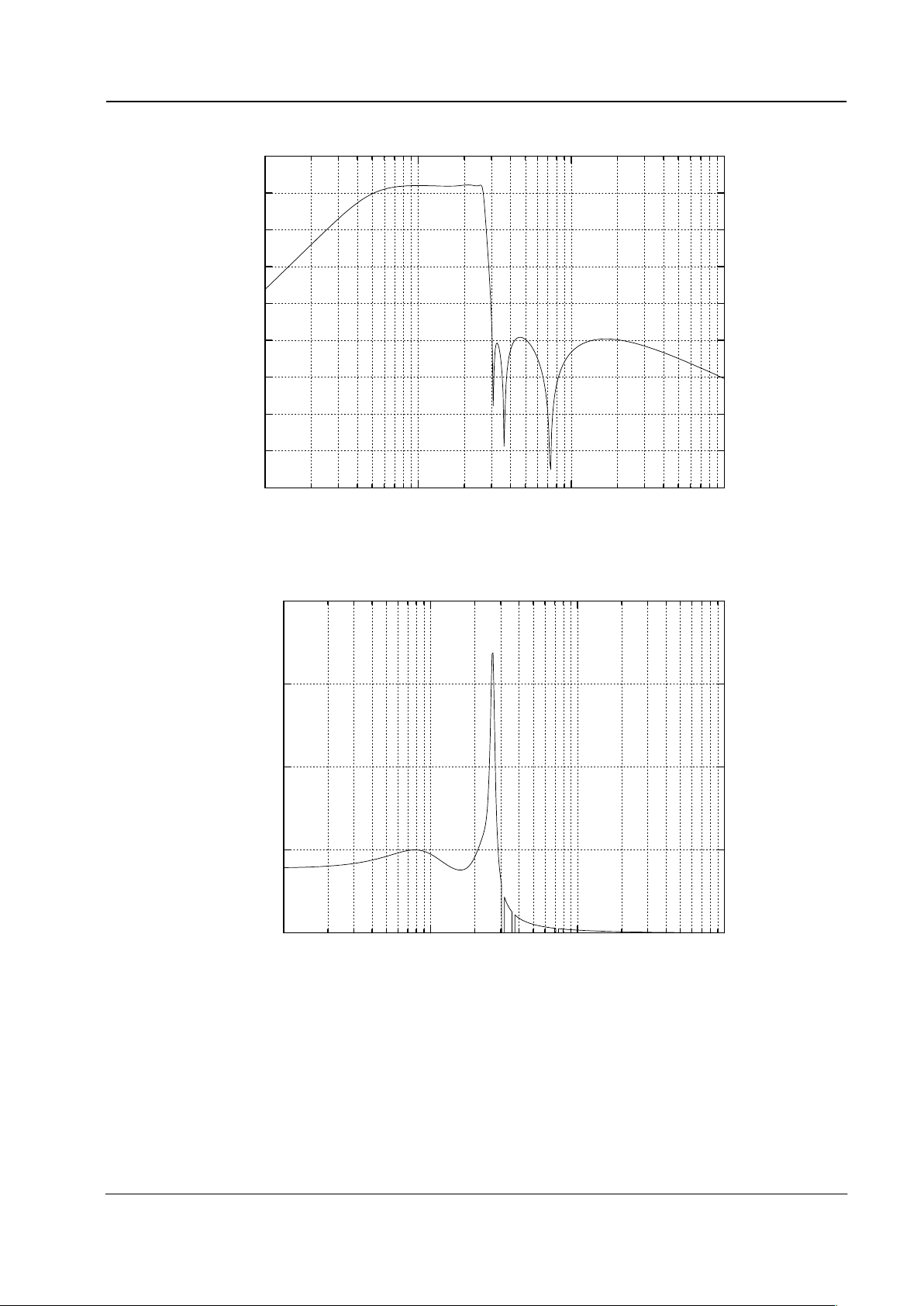

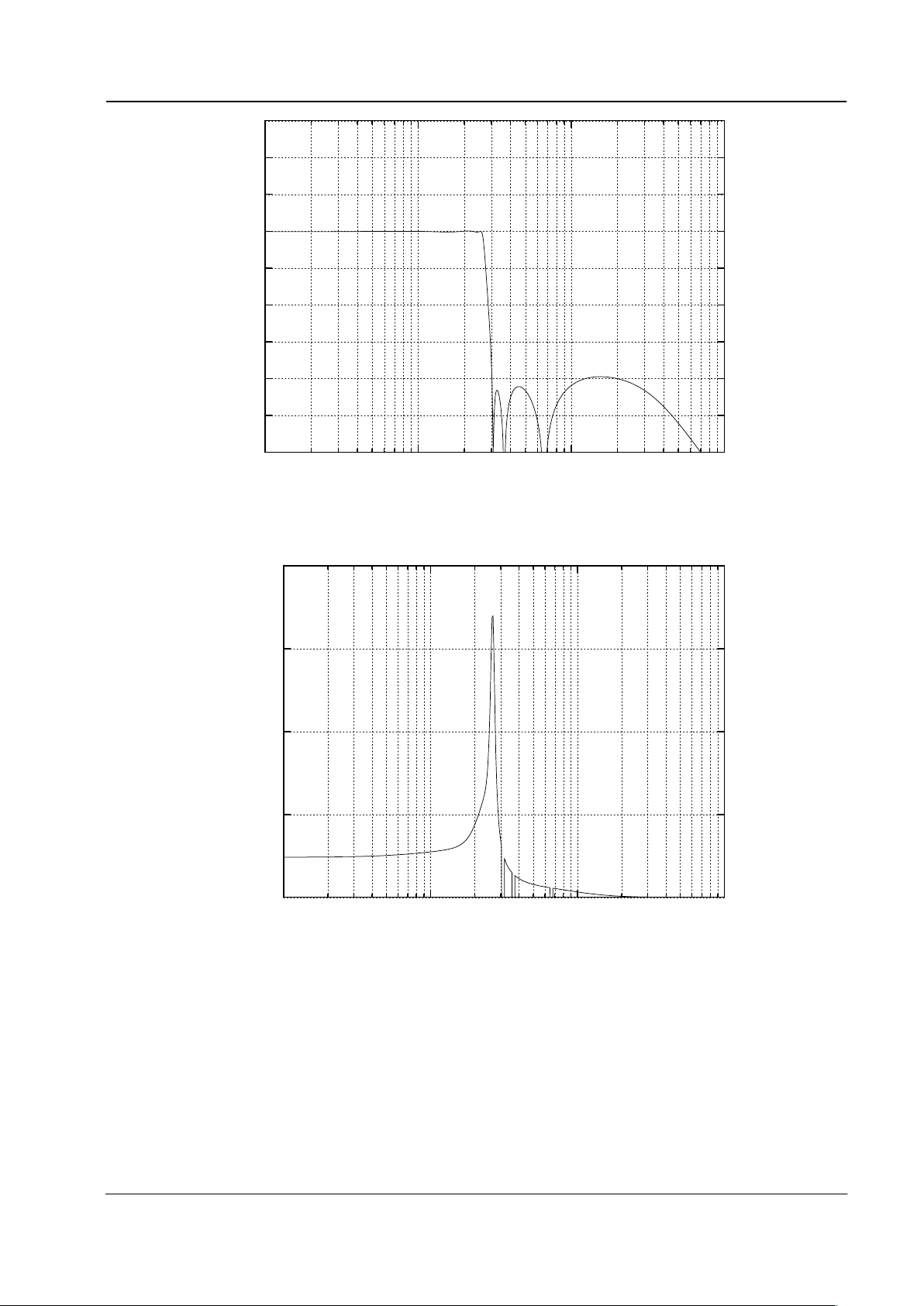

4.2.2 Subaudio RX and TX Filter Characteristics

-60

-50

-40

-30

-20

-10

0

10

20

30

10 100 1000 10000

Magnitude (dB)

Frequency (Hz)

Figure 16: Subaudio RX filter gain for normal CTCSS operation.

0

0.005

0.01

0.015

0.02

10 100 1000 10000

Delay (sec)

Frequency (Hz)

Figure 17: Subaudio RX filter delay for normal CTCSS operation.

Page 20

FRS/PMR446/GMRS Family Radio Processor 20 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

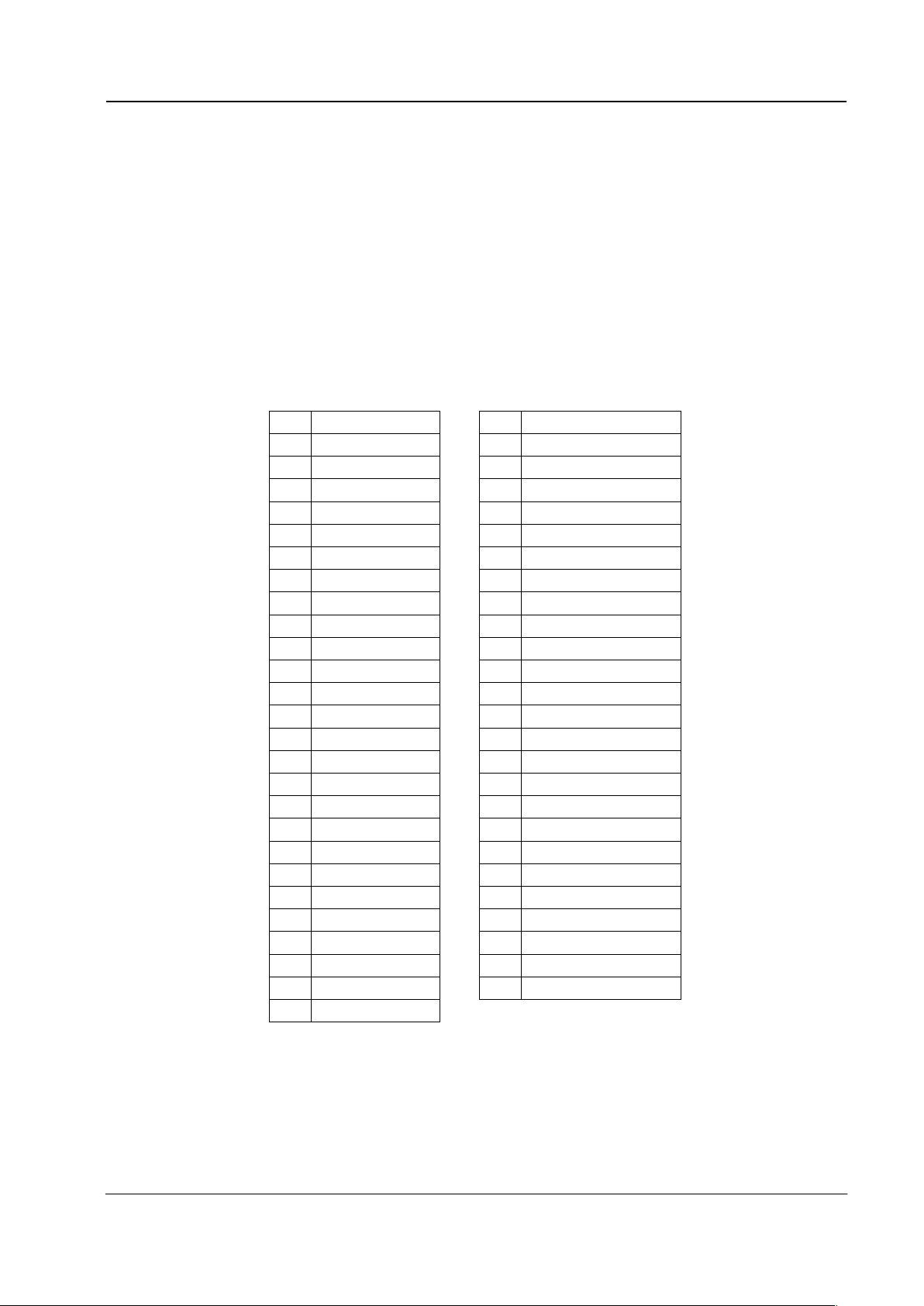

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

10 100 1000 10000

Magnitude (dB)

Frequency (Hz)

Figure 18: Subaudio TX level for normal CTCSS operation (Magnitude scale with respect to 0dBV)

0

0.005

0.01

0.015

0.02

10 100 1000 10000

Delay (sec)

Frequency (Hz)

Figure 19: Subaudio TX filter delay for normal CTCSS operation.

Page 21

FRS/PMR446/GMRS Family Radio Processor 21 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.2.3 CTCSS Subaudio Decoder and Encoder Tone Set

The CMX838 supports all popular subaudio tones with a unique, full performance, 'one-of-any' rapid detect

capability that adds support for end product group calling and Tone Cloning™ features. The digital processor

essentially contains 51 decoders to analyze the receive signal. Each decoder can independently be enabled

or disabled via configuration tasks.

The result of the subaudio signal analysis is available in the subaudio status register ($94). Both a decode

status bit, and a decoder index number are reported in the status register. The decode status bit is a logic one

when an enabled decoder senses that the input signal matches its center frequency – the index number will

be that of the matching decoder. If the input signal does not contain a subaudio signal that matches an

enabled decoder’s center frequency then the status bit is a logic zero – in this case the decoder index number

is reported as:

A. 62 if there is a significant subaudio frequency present.

B. 63 if the no tone timer has expired indicating there is no significant subaudio frequency present now, or

C. 0 if no subaudio signal has been seen since the subaudio processor was enabled or most recently placed

in RX mode.

No. Frequency (Hz) No. Frequency (Hz)

1. 67.0 27. 159.8*

2. 69.3 28. 162.2

3. 71.9 29. 165.5*

4. 74.4 30. 167.9

5. 77.0 31. 171.3*

6. 79.7 32. 173.8

7. 82.5 33. 177.3*

8. 85.4 34. 179.9

9. 88.5 35. 183.5*

10. 91.5 36. 186.2

11. 94.8 37. 189.9*

12. 97.4 38. 192.8

13. 100.0 39. 196.6*

14. 103.5 40. 199.5*

15. 107.2 41. 203.5

16. 110.9 42. 206.5*

17. 114.8 43. 210.7

18. 118.8 44. 218.1

19. 123.0 45. 225.7

20. 127.3 46. 229.1*

21. 131.8 47. 233.6

22. 136.5 48. 241.8

23. 141.3 49. 250.3

24. 146.2 50. 254.1*

25. 151.4 51. User Programmable

26. 156.7

* Subaudible Tones not included in TIA-603 standard

Table 2: CTCSS Subaudio Tone Frequencies with their Corresponding Index Number

Page 22

FRS/PMR446/GMRS Family Radio Processor 22 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.2.4 Tone Signaling Processor Configuration Task Descriptions

Task ID Task Description Argument Data In

Normal Run Mode 0 Normal Operation N/A

Reserved For Test 1, 2, 3 Special Test Functions N/A

4 Enable/Disable Tone Detector $95

5 Program User Defined Subaudio Tone $8E

6 Adjust Detector Band Width $8E

RX Configure

7 Adjust No Tone Timer Duration $8E

8 Select Sub-Audio Tone From Preprogrammed List $95

9 Program User Defined Subaudio Tone $8E

10 Program Audio Frequency Ringing Tone $8E

TX Configure

11 Program TX Timer $8E

12 Enter Fast Initialization Mode N/A

13 Quickly Enable/Disable Multiple Detectors $95

14 Configure Aux Pin as Output $95

Initialize and Configure

15 Soft Reset N/A

Table 3: Tone Signaling Processor Initialization and Configuration Tasks

Tone signaling configuration tasks initialize the tone signaling processor. While the processor is running,

either generating or detecting tones (controlled by the

RXTX

/

bit of register $80), configuration tasks can be

issued at a rate up to one per 250

µs. The required argument register(s) should not be modified for at least

this time after issuing a task. Before issuing tasks that require argument data, first load the argument data in

the argument data register. Then load the desired task in the task field of the sub-audio general control

register. The Power control (i.e. enabled) and IRQ control (set however you want) should be logically OR’ed

with the desired task field to define the data to load in register $93. All C-BUS writes to the subaudio general

control register ($93), that enable (or keep enabled) the tone signaling processor, constitute issuing a task.

Before tasks are issued, the base band clocks must be setup.

4.2.4.1 Normal Run Mode (Task 0)

To place the device in Normal Run mode issue Task 0. In this mode, the tone signaling processor will either

encode or decode depending on the

RXTX

/

bit of register ($80).

4.2.4.2 Reserved For Test (Task 1-3)

Do not issue tasks 1, 2 or 3 as these are reserved for test.

Page 23

FRS/PMR446/GMRS Family Radio Processor 23 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.2.4.3 RX Configuration

The following four tasks are used to control the decode behavior.

4.2.4.3.1 Enable or Disable Tone Detector (Task 4)

This task can be used to enable or disable tone detectors 1 to 51. Tone Detectors 1 to 50 have preset

detection center frequencies while tone detector 51 has a user programmable center frequency. This task

may be issued multiple times to configure a tone watch list. It is recommended not to include non TIA-603

tones with their adjacent TIA tones in a watch list.

Load argument in register $95, then issue task 4. Repeat as needed to configure tone watch list.

The argument data has the following format in the 8 bit task data register ($95).

Bit 7 Bit 6 Bits 5-0

1=enable

0=disable

Don’t

care

Tone detector index number (1-51)

Additionally using index 63 can enable or disable all detectors while issuing just

one task. Enabling index 62 enables detection of all TIA-603 Tones. There is no

single command to disable just the TIA-603 Tone Detectors – instead use index 63

to disable all detectors.

For example to enable the 67Hz Tone Detector:

$95 0x81 // data to enable tone index 1 (67Hz)

$93 0x64 // task command to actually enable tone detector (and IRQ’s)

4.2.4.3.2 Program User Defined RX Sub-Audio Tone (Task 5)

This task is used to program the center frequency of user programmable detector 51. Load the Argument

value in register $8E, then issue task 5.

The argument can be calculated according to the following equations.

RNArgument

f

N

INTR

f

INTN

+⋅=

¸

¸

¹

·

¨

¨

©

§

⋅

⋅

−+=

¸

¹

·

¨

©

§

⋅⋅

=

64

96

100000

5115.0

100000

51196

The argument data for 65 Hz would be 31*64+14 = 0x07CE

The programmed center frequency can be back calculated by:

)511(96

100000RN

f

−

⋅

=

In the example above the actual center frequency would be 64.97 Hz.

A C-BUS sequence to setup tone detector 51 for 65Hz and enable just it would be:

$8E 0x07CE // Argument data for user defined 65Hz RX Tone.

$93 0x45 // Task 5 command (No IRQ’s enabled)

wait 250µs

$95 0x3F // Task 4 argument data to disable all decoders

$93 0x44 // Task 4 command (No IRQ’s enabled)

wait 250µs

$95 0xB3 // Task 4 argument data to enable decoder 51 (The user definable one)

$93 0x64 // Task 4 command (with IRQ’s enabled)

wait 250µs

$93 0x60 // Task 0 command (to place device normal run mode with IRQ’s enabled)

// last command is not required if the device was already in normal run mode

Page 24

FRS/PMR446/GMRS Family Radio Processor 24 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.2.4.3.3 Adjust Detector Band Width (Task 6)

The default bandwidth can be increased or decreased in increments of approximately 0.2% by loading a small

positive or negative (2’s complement) value in register $8E and then issuing task 6. For the standard TIA tone

set the default BW setting is recommended – so there is no need to adjust it. By default, the detector has a

small BW hysteresis to minimize chatter in marginal conditions.

4.2.4.3.4 Adjust No Tone Timer Duration (Task 7)

The default no tone timer duration can be increased or decreased in increments of 60µs by loading a positive

or negative (2’s complement) value in register $8E and then issuing task 7.

()

TimerDeltaINTArgument ⋅+= 667.165.0

Where TimerDelta is the amount by which you want to increase or decrease the Default No Tone Timer in

milliseconds.

For example, to increase the default no tone timer by 10ms, load 167 (0xA7) into register $8E before issuing

task 7.

$8E 0x00A7

$93 0x67 // Task 7 command to adjust no tone timer with IRQ’s enabled

4.2.4.4 TX Configuration

4.2.4.4.1 Select Sub-Audio Tone From Preprogrammed List (Task 8)

To select a preprogrammed sub-audio tone, load the index argument (1 to 50) in register $95 then issue

task 8.

For example to set up TX tone to 114.8 Hz, the required C-BUS sequence would be

$95 0x11

$95 0x48

4.2.4.4.2 Program User Defined TX Sub-Audio Tone (Task 9)

To program a user defined sub-audio tone, load the argument in register $8E then issue task 9. Where the

argument is defined by,

¸

¹

·

¨

©

§

⋅⋅

+=

100000

6553636

5.0

f

INTArgument

For example to set up TX tone to 65 Hz, the required C-BUS sequence would be

$8E 0x05FE

$93 0x49

4.2.4.4.3 Program Audio Frequency Ringing Tone (Task 10)

To program a user-defined audio ringing tone, load the argument in register $8E then issue task 10. Where

the argument is defined by,

¸

¹

·

¨

©

§

⋅⋅

+=

100000

655366

5.0

f

INTArgument

For example to set up the ringing tone frequency to 620 Hz, the required C-BUS sequence would be

$8E 0x0986

$93 0x4A

4.2.4.4.4 Program TX Timer (Task 11)

Load the argument in register $8E, then issue task 11. Where the argument is defined by, TBD.

4.2.4.5 Initialize and Configure

4.2.4.5.1 Enter Fast Initialization Mode (Task 12)

Issuing task 12 takes the tone signaling processor out of normal running mode and dedicates the processor to

handling initialization tasks to increase the maximum task rate. In this mode neither the tone encoders nor the

decoders run. To return to normal running mode issue task 0. In this fast initialization mode tasks can be

issued at a rate of one per 50µs. Ensure that the required argument registers are not updated for at least this

time after a task is issued.

Page 25

FRS/PMR446/GMRS Family Radio Processor 25 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.2.4.5.2 Quickly Enable/Disable Multiple Detectors (Task 13)

Issuing task 13 places the tone signaling processor in a mode that allows multiple detectors to be to be

quickly configured. Like for task 12 neither the tone encoders nor the decoders run in this mode. The

argument data is defined as for task 4. This mode reverts to Fast Initialization Mode when any other task is

issued. To return to normal running mode issue task 0. The following example shows how to enable only

Tone detectors 1, 7, 10, 12, 18, and 20. Multiple calls to Task 4 can accomplish this, but would require more

C-BUS transactions and waiting 250µs after each task 4 call, but could allow the tone decoders to continue to

run.

// to disable all tone detectors and enter mode to quickly enable multiple detectors

$95 0x3F

$93 0x4D // value = 0x80 | 0x0D

wait 250µs // to ensure device runs Task 13

$95 0x81 // to enable tone detector 1 (67.0 Hz) value = 0x80 | 0x01

$95 0x87 // to enable tone detector 7 (82.5 Hz)

$95 0x8A // to enable tone detector 10 (91.5 Hz)

$95 0x8C // to enable tone detector 12 (97.4 Hz)

$95 0x92 // to enable tone detector 18 (118.8 Hz)

$95 0x94 // to enable tone detector 20 (127.3 Hz)

// to place device back in normal running mode

$93 Power Control + IRQ Control + Task 0

4.2.4.5.3 Configure Aux Pin as Output (Task 14)

Task 14 can be used to select and enable various digital outputs at the AUX pin. Load the argument data in

register $95 then issue the task.

The argument data has the following format in the 8 bit task data register ($95).

Bit 7 Bit 6-3 Bit 2-0 (These bits are Don’t Care if Bit 7 is a logic 0)

1=enable aux

pin as output

0=enable aux

pin as input

Don’t care

Bit 2 Bit 1 Bit 0 AUX output signal

1 0 0 RX Decode Status bit

1 0 1 Audio Frequency Ringing Tone

1 1 0 Output logic 0

1 1 1 Output logic 1

For example to have the device produce a 620Hz ringing tone frequency set up the ringing frequency with

task 10 then enable the output with task 14. Note that once the Audio Ringing Generator is enabled the

frequency can be changed by reissuing task 10.

$8E 0x0986 // 620 Hz

$93 0x4A

wait 250µs

$95 0x85

$93 0x4E

wait at least 250 µs

$8E 0x06C2 // 440 Hz

$93 0x4A

Page 26

FRS/PMR446/GMRS Family Radio Processor 26 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.2.4.5.4 Soft Reset (Task 15)

The tone signaling processor must be fully initialized after the chip is powered up. After powering up, the first

time the tone-signaling processor is enabled, it should be with the task field set to 15. This clears the

configuration memory and reverts to Fast Initialization Mode when any other task is issued. After all desired

initialization is performed, return to normal running mode by issuing task 0.

Power up Sequence

//Power up the Device

// issue general reset

$01

// set up base band clocks before enabling the sub-audio processor

$89 0xXX // specific setting depends on your system (See Section 5.1.2.7)

$8A 0xXX // specific setting depends on your system (See Section 5.1.2.8)

// issue Sub-audio processor soft reset

$93 0x4F

// wait for soft reset to complete

wait 250µs

// set up TX sub-audio frequency

$95 TX tone index

$93 0x48

// set up one RX sub-audio frequency

$95 (0x80 | RX tone index)

$93 0x44

// setup normal run mode for sub-audio processor

$93 (0x40 | IRQ control | Task 0)

// setup RX and TX sub-audio analog trimmers to 0dB

$97 0x1010

// setup other C-BUS registers as needed (e.g. Register $80 to select

RXTX/ , $88 for TX Mod 1 and Mod 2

Control, etc.)

Page 27

FRS/PMR446/GMRS Family Radio Processor 27 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.3 RF Synthesizer

This section describes the implemented core functions of an Integer-N frequency Synthesizer. This includes

modules for the RF 32/33 prescaler, programmable divider, phase detector, lock indicator, reference counter

and charge pump. The Block diagram for the module is shown in Figure 20.

divide 32/33

programmable divider

12 bit programmable

reference counter

phase

detector

charge

pump

lock

detect

-RF

IN

+RF

IN

REF

IN

SV

SS

I

SET

CP

OUT

S

SV

DD

Figure 20: RF Synthesizer block diagram.

4.3.1 Operating Range and Specifications

The RF synthesizer is capable of supporting narrowband (6.25kHz < channel BW <25kHz) applications in the

RF range from 100MHz to 500MHz. In other words, there are no blind channels over this range.

4.3.2 Main Divider

An input buffer amplifies and limits the RF signal from the VCO to a level that drives the dual modulus

prescaler. The main RF divider is implemented using the dual-modulus 32/33 prescaler in conjunction with a

programmable counter. This counter is realized using two programmable counters (

A & M Counters).

The

M-counter uses a 12-bit programming word and the A-counter uses a 5-bit word, see Figure 21.

divide 32/33RF IN

programmable 5 bit

A-counter

programmable 12 bit

M-counter

TO PHASE

DETECTOR

DATA WORD

512

17

RESET

MODULUS

Figure 21: Block diagram of main programmable divider.

The forward division ratio, N, can be expressed as:

N = (32M + A)

Where

A and M represent the programmed data words.

4.3.3 Phase Detector & Charge Pump

A Phase/Frequency detector is implemented where steps have been taken to remove the dead-band normally

associated with this type of detector and charge pump arrangement.

An external resistor, R

SET

, sets I

CHP

, the nominal charge pump current. The current through this resistor is set

by a 1.26V on-chip reference at the I

SET

pin where, I

SET

= 1.26 ÷ R

SET.

The magnitude of the charge pump

current is either 40*I

SET

or 80*I

SET

depending upon the state of the IHL bit programmed through the C-BUS

serial interface, see Section 5.1.2.8 for programming details.

IHL = 0, I

CHP

= 40*I

SET

IHL = 1, I

CHP

= 80*I

SET

The value of R

SET

can vary between about 50kΩ and 250kΩ. This gives a charge pump current range of

0.8mA to 8.4mA.

Page 28

FRS/PMR446/GMRS Family Radio Processor 28 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

4.3.4 Lock Detect Output

The Lock detect status is active high when the phase error corresponds to a time difference of less than about

20ns, 40ns, 60ns, or 80ns at the phase detector comparison inputs. The comparison period is chosen using

the Lock Delay bits of the Channel Select Register ($8B). The lock status is updated according to the lock

detect mode chosen using the Synthesizer General Control Register ($8A). Lock detect data is collected once

every period of the reference signal.

4.3.5 Reference Circuits

The input from the external crystal oscillator is buffered and amplified to CMOS levels. This reference signal is

then divided in frequency by a 12-Bit programmable counter.

The Reference Divider is loaded from a ROM that yields one of four possible reference frequencies: 6.25kHz,

12.5kHz, 20kHz, and 25kHz. Frequency selection is dependent on the RF service bits of the Synthesizer

General Control Register ($8A) or two of the channel select bits when generic RF service is chosen ($8B).

4.4 Baseband Timing Generation

Internal baseband timing is developed from a configurable choice of two sources: a crystal clock signal

(XTAL/CLOCK) or an externally applied synthesiz er reference clock signal (REF

IN

). An on-chip crystal

oscillator amplifier is provided to form a crystal oscillator via the addition of an external crystal.

Several frequency options are supported for both crystal and synthesizer clock source options.

Configuration details are described in Section 5.1.2.7.

Page 29

FRS/PMR446/GMRS Family Radio Processor 29 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

5 Software Programming

5.1 C-BUS Serial Interface

C-BUS is the serial interface used by a µC to transfer data, control, and status information, to and from the

internal registers of the chip. Every transaction consists of one address byte that may be followed by one or

two bytes of data.

Data sent from the µC to the chip on the CMD DATA line is clocked in on the rising edge of SERIAL CLOCK.

RPLY DATA sent from the chip to the µC is valid when SERIAL CLOCK is high. See Figure 22. This serial

interface is compatible with most common µC serial interfaces such as SCI, SPI, and Microwire.

CS

a) Single byte from µC

SERIAL CLOCK

CMD DATA

Address (01 Hex = Reset)

= Level not important

Note:

The SERIAL CLOCK line may be high

or low at the start and end of each

transaction.

Hi-Z

RPLY DATA

7

6

5

4

3

2

1

0

7

6

5

4321

0

c) One Address byte from µC and 2 Reply bytes from the Chip

CS

SERIAL CLOCK

Hi-Z

Address

Data from Chip Data from Chip

CMD DATA

RPLY DATA

7

6

5

432

1

0

7

6

5

4321

0

b) One Address and 2 Data bytes from µC

CS

SERIAL CLOCK

CMD DATA

Address

Hi-Z

Data to Chip Data to Chip

RPLY DATA

7

6

5

4321

0

7

6

5

4321

0

7

6

5

432

1

0

Figure 22: C-BUS transaction timing diagram.

Page 30

FRS/PMR446/GMRS Family Radio Processor 30 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

5.1.1 8-Bit C-BUS Register Map

8 BIT REGISTER

NAME

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

GENERAL RESET

[Write $01]

N/A

Audio Path Control

SETUP REGISTER

[Write $80]

TX

enable

Input 1 control Input 2 control Output control

Audio Filter bypass control

AUDIO CONTROL

[Write $81]

Preemphasis Low-pass

bypass control

High-

pass

bypass

control

AUDIO LEVEL

+/- 7.5dB in 0.5dB steps

RX VOLUME

CONTROL

[Write $82]

Limiter & Limiter Filter

& Deemphasis bypass control

VOLUME CONTROL

+12 to –33dB in 1.5dB steps

AUDIO POWE R A ND

BW CONTROL

[WRITE $83]

POWER CONTROL

FOR MOD 1 & 2 AND

MICAMP

POWER

CONTROL FOR

AUDIO FILTERS

AND LIMITER

POWER

CONTROL FOR

VOLUME

CONTROL

AUDIO

BANDWIDTH

SEL

UNUSED

SYNTHESIZER

BASEBAND CLK

CONTROL

[Write $89]

SYNTHESIZER &

BASEBAND CLOCK

SOURCE SELECT

SYNTHESIZER

REFERENCE INPUT FREQUENCY

SELECT

XTAL/CLOCK

INPUT

FREQUENCY

SELECT

CHARGE PUMP

CURRENT

SYNTHESIZER

GENERAL

CONTROL

[Write $8A]

ENABLE,

POWERSAVE,

&

TEST MODE CONTROL

LOCK DETECTOR

CONTROL

&

IRQ MASK

HIGH

LOW

polarity

RF SYSTEM

FRS, GMRS, PMR

446, or GENERIC

RESERVED SET TO "0"

CHANNEL SELECTION

INDEXED CONTROL OF VALID FRS,

GMRS & PMR446 RF CHANNELS

SYNTHESIZER

CHANNEL SEL

[Write $8B]

IN GENERIC RF SYSTEM MODE (set in [SGC])

SYNTHESIZED FREQUENCY IS SET VIA THESE BITS AND BITS IN [SBCC] & [SIFOS]

REGISTERS

SYNTHESIZER

STATUS

[Read $8C]

Lock

Algorithm

Status

LOCK STATUS OF MOST RECENT 7 PHASE COMPARISONS

TEST 0

[WRITE $90]

SYNTHESIZER TEST MODES

SUBAUDIO

GENERAL

CONTROL

[Write $93]

POWER CONTROL

FOR SUBAUDIO

SUBAUDIO

IRQ

CONTROL

SUBAUDIO TASK SELECTION

SUBAUDIO STATUS

[Read $94]

[SAS]

SYNTHESIZER

IRQ

FLAG

Decode Decoded Tone Index

8 BIT SUBAUDIO

TASK DATA

[Write $95]

SUBAUDIO TASK DATA BYTE

8 BIT SUBAUDIO

TEST DATA

[Write $96]

SUBAUDIO TEST DATA BYTE

Table 4: 8 Bit Registers

Page 31

FRS/PMR446/GMRS Family Radio Processor 31 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

5.1.2 16-Bit C-BUS Register Map

16 BIT REGISTER

NAME

BIT 15 /

BIT 7

BIT 14 /

BIT 6

BIT 13 /

BIT 5

BIT 12 /

BIT 4

BIT 11 /

BIT 3

BIT 10 /

BIT 2

BIT 9 /

BIT 1

BIT 8 /

BIT 0

MOD 2 switch bank Control

0/180

phase

select

SUBAUDIO

enable

AUDIO

enable

MOD 2 LEVEL

+/- 7.5dB in 0.5dB steps

MOD 1 switch bank Control

TX MOD 1&2

CONTROL

[Write $88]

0/180

phase

select

SUBAUDIO

enable

AUDIO

enable

MOD 1 LEVEL

+/- 3.75dB in 0.25dB steps

SYNTHESIZER 1ST

IF OFFSET

[Write $8D]

[SIFOS]

SIGNED 16 Bit NUMBER PROPORTIONAL TO IF OFFSET, AUTOMATICALLY APPLIED

WHEN DEVICE IS IN RX MODE [SR] & ONE OF THREE SPECIFIC RF SYSTEM

MODES (FRS, GMRS, PMR 446) IS SELECTED IN [SGC]

IN GENERIC RF SYSTEM MODE (SELECTED IN [SGC]), SYNTHESIZED FREQUENCY

IS SET DIRECTLY VIA THESE 16 BITS AND BITS IN [SBCC] & [SCS] REGISTERS

16 BIT SUBAUDIO

TASK DATA

[Write $8E]

SUBAUDIO TASK DATA WORD

16 BIT SUBAUDIO

TEST DATA

[Write $8F]

SUBAUDIO TEST DATA WORD

16 BIT SUBAUDIO

TEST READ DATA

[Read $91]

SUBAUDIO TEST READ WORD

Subaudio filter path control TX Level Control +/-7.5dB in 0.5dB steps

SUBAUDIO ANALOG

CONTROL

[Write $97]

Subaudio filter path control RX Level Control +/-7.5dB in 0.5dB steps

Table 5: 16 Bit Registers

5.1.2.1 GENERAL RESET ($01)

The reset command has no data attached to it. Application of the GENERAL RESET, sets all write only

register bits to ‘0’.

Page 32

FRS/PMR446/GMRS Family Radio Processor 32 CMX838 Advance Information

¤

¤¤

¤2001 MX-COM, Inc. www.mxcom.com Tel: 800 638 5577 336 744 5050 Fax: 336 744 5054 Doc. # 20480221.002

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service mark s are held by their res pec t ive companies.

5.1.2.2 SETUP Register ($80)

TRANSMIT/

RECEIVE

(

R

X

TX/ )

Bit 7

In the Audio section, this bit controls a single pole single throw switch in the audio path

between the deviation limiter/low-pass filter and the transmit modulation digitally

controlled amplifiers. A logic ‘1’ allows audio to flow between these blocks. In the

synthesizer section, this bit in conjunction with the synthesizer intermediate frequency

offset register (SIFOS register) allows for autonomous switching between two

synthesizer frequencies (for example where the required receive frequency equals the

transmit center frequency offset high or low by the radios first intermediate frequency).

A logic ‘1’ will enables synthesis of the transmit frequency, while a logic ‘0’ enables the

offset frequency. In the subaudio section, this bit enables the subaudio encoder

(logic ‘1’) or decoder (logic ‘0’).

AUDIO INPUT 1

SELECT

Bit 6 and Bit 5