Page 1

Semiconductor

/

OBSOLETE PRODUCT

CD22402

[ /Title

(CD2240

2)

Subject

(Sync

Generator for

TV

Applicationsand

Video

Process-

NO RECOMMENDED REPLACEMENT

Call Central Applications 1-800-442-7747

May 1999

or email: centapp@harris.com

Features

• Interlaced Composite Sync Output

• Automatic Genlock Capability

• Crystal Oscillator Operation

• 525 or 625 Line Operation

• Vertical Reset Option

• Wide Power Supply Operating Voltage . . . . .4V to 15V

Applications

• Cameras

• Monitors and Displays

•CATV

• Teletext

• Video Games

• Sync Restorer

• Video Service Instruments

Part Number Information

TEMP.

PART NUMBER

CD22402D -55 to 125 24 Ld SBDIP D24.6

CD22402E -40 to 85 24 Ld PDIP E24.6

RANGE (oC) PACKAGE

PKG.

NO.

Sync Generator for TV Applications

and Video Processing Systems

Description

The Harris CD22402 (Note) is a CMOS LSI sync generator that

produces all the timing signals required to drive a fully 2-to-1

interlaced 525-line 30-frame/second, or 625-line 25-frame/second TV camera or video processing system. A complete sync

waveform is produced which begins each field with six serrated

vertical sync pulses, preceded and followed by six half-width

double frequency equalizing pulses. The sync output is gated by

the master clock to preserve horizontal phase continuity during

the vertical interval.

The CD22402 can be operated either in “genlock” mode, in

which it is synchronized with a reference sync pulse train from

another TV camera, or in “stand-alone” mode, in which it is synchronized with a local on-chip crystal oscillator (the crystal and

two passive components are off chip). Also, the circuit can

sense the presence or absence of a reference sync pulse train

and automatically select the “genlock” or “stand-alone” mode.

A frame sync pulse is produced at the beginning of every odd

field. The vertical counter can be reset to either the first equalizing

pulse or the first vertical sync pulse of the vertical interval. The

interlaced sync provided by the CD22402 differs from RS-170 by

having slightly narrower sync and equalizing pulses. The clock

frequency of 32 times horizontal rate allows for approximately 4µs

horizontal pulse widths and 2µs equalizing pulses. Otherwise

operation can be phase locked to a color sub-carrier for a full

interlaced operating system.

The CD22402 is operable with a single supply over a voltage

range of 4V to 15V.

Pinout

CD22402 (PDIP, SBDIP)

TOP VIEW

DELA Y, GENLOCK TO CRYSTAL OSCILLATOR

CRYSTAL OSCILLATOR FEEDBACK T AP

HORIZONTAL DRIVE OUTPUT

MIXED SYNC OUTPUT

GENLOCK OSCILLATOR CAPACITOR CONNECTION

MIXED BEAM BLANKING OUTPUT

VERTICAL COUNTER RESET TO FIRST EQU ALIZING PULSE

VERTICAL DRIVE OUTPUT

VERTICAL RESET TO FIRST VERTICAL SYNC PULSE

HORIZONTAL CLAMP OUTPUT

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1999

1

2

V

3

SS

4

5

6

7

8

9

10

11

12

V

SS

8-40

24

RESISTOR CONNECTION FOR GENLOCK OSCILLATOR

23

MASTER FREQUENCY INPUT

22

R-C CONNECTION FOR GENLOCK OSCILLATOR

21

DELA Y, GENLOCK TO CRYSTAL OSCILLATOR

20

GENLOCK INPUT (COMPOSITE SYNC)

19

V

DD

18

525 LINE TO 625 LINE OPERATION SWITCH

17

VERTICAL PROCESSING BLANKING OUTPUT

16

SHORT VERTICAL DRIVE OUTPUT

15

FRAME SYNC OUTPUT (ODD FIELD)

14

HORIZONTAL PR OCESSING BLANKING OUTPUT

13

MIXED PROCESSING BLANKING OUTPUT

File Number 1686.5

Page 2

CD22402

Pin Descriptions

PIN NO. SYMBOL DESCRIPTION

1 XRC Delay, Genlock to Crystal Oscillator. Resistor, diode and capacitor connection for delay that automatically

turns on thecrystal oscillator whenthe genlock input is removed.When the signal on Terminal 1 is high the crystal oscillator is inhibited. Typical values for R and C are 1MΩ and 0.001µF. For operation as a crystal controlled

stand alone sync generator without genlock, Terminal 1 should be hardwired to VSS.

2 XTP Crystal Oscillator Feedback Tap. Feedback connection (tap) forcrystal oscillator. When a crystal (shunted by

a1MΩ resistor) is connected between this terminal and Terminal 23, and a 100pF capacitor is connected from

this terminal to VSS, the sync generator creates its own master frequency. Fora 525-line, 30-frame/second raster,the crystal frequency is 504.000kHz (Note 1);and fora 625-line, 25-frame/second raster,the crystal frequen-

cy is 500.000kHz (Note 1).

3VSSNegative Power Supply Voltage. This terminal must be hardwired to Terminal 12 (VSS).

4HDHorizontal Drive Output

5MSMixed Sync Output

6CCapacitor Connection for R-C Genlock Oscillator

7 MBB Mixed Beam Blanking Output

8 VRE Vertical Counter Resetto First Equalizing Pulse. Alow level signal on thisterminal resets thevertical counter

to the first equalizing pulse of a field. When not in use this terminal should be connected to VDD.

9VDVertical Drive Output

10 VRV Vertical Counter Reset to First Vertical Sync Pulse. A low level signal on this terminal resets the sync gen-

erator to the first vertical sync pulse of a field. For genlock operation, Terminal 10 is used as a resistor and ca-

pacitor connection for an integrator networkthat detects vertical syncpulses in a master syncwaveform to which

the sync generator is to be genlocked. R is 22kΩ, and C is 0.001µF. When not in use this terminal should be

connected to VDD.

11 HC Horizontal Clamp Output

12 V

13 MPB Mixed Processing Blanking Output

14 HPB Horizontal Processing Blanking Output

15 FS2 Frame Sync Output (Odd Field). A pulse coincidingwith the first equalizing pulse is produced atthe beginning

16 SVD Short Vertical Drive Output

17 VPB Vertical Processing Blanking Output

18 SW Operation Switch for 525-Line or 625-Line Raster. A high level signal on Terminal 18 causes the sync gener-

19 V

20 GEN Genlock Input Composite Sync. A negative going reference mixed sync waveform applied to Terminal 20 dis-

21 XR Delay, Genlock to Crystal Oscillator, Resistor and Diode Connection for Delay,Genlock to Crystal Oscil-

22 RC Resistor and Capacitor Connection for Genlock Oscillator. If the genlock oscillator is not used this terminal

23 XIN Master Frequency Input.

24 R Resistor Connection for Genlock Oscillator.

NOTE: 32 times horizontal frequency.

Negative Power Supply Voltage

SS

of every odd field.

ator to generate a 625-line raster. An internal pulldown resistor is connected to Terminal 18, so in the absence

of an applied input to this terminal, a 525-line raster is produced.

Positive Power Supply Voltage. VDD can be any voltage between +4 and +15 relative to VSS.

DD

ables the crystal oscillator and locks the R-C genlock oscillator to the horizontal pulses of the reference sync

waveform. Vertical sync detection is achieved by an R-C integrator connected from Terminal 20 to Terminal 10

(vertical reset to first vertical sync pulse). An internal pull-up resistor is connected to Terminal 20 so that in the

absence of an applied input the crystal oscillator is enabled and the R-C genlock oscillator is disabled.

lator. Automatically turns on the crystal oscillator when the input to Terminal 20 is removed.

should be connected to VSS. C should be 100pF, and R should be a 10kΩ potentiometer.

8-41

Page 3

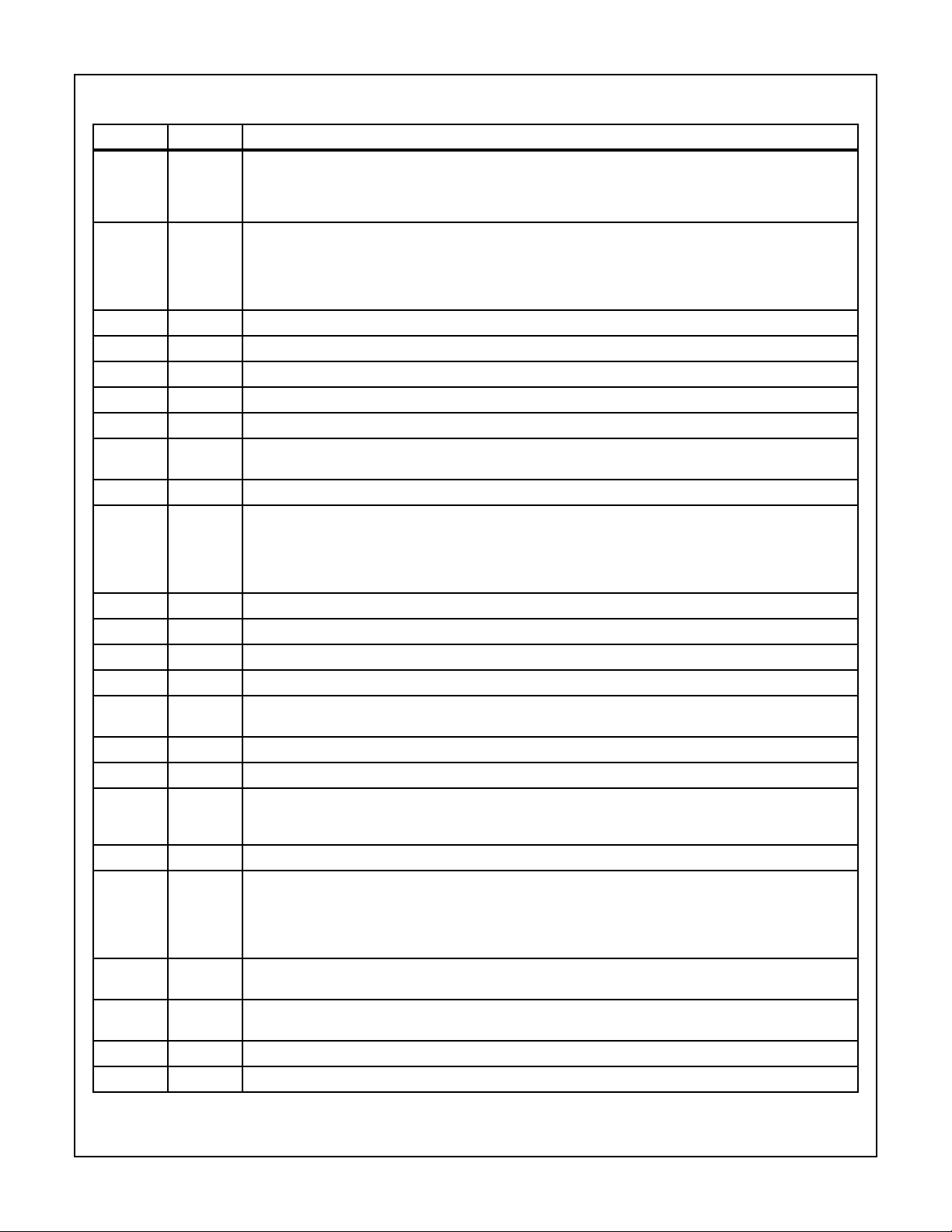

Block Diagram

10

VRV

CD22402

CD22402 MONOCHROME TV SYNC GENERATOR WITH AUTOMATIC GENLOCK

R

RC C

24 22 6 8 18

VRE SW

GEN

XR

XRC

XIN

XTP

= PINS 3 AND 12

V

SS

= PIN 19

V

DD

R-C

GENLOCK

OSCILLATOR

20

21

1

23

2

AUTOMATIC

GENLOCK

CONTROL

CRYSTAL

OSCILLATOR

14 11 4 5 13 7 15 16 9 17

HPB HC HD MS MPB MBB FS2 SVD VD VPB

HORIZONTAL

COUNTER

÷16

÷2

LINE

DECODER

COMPOSITE

DECODER

VERTICAL

COUNTER

÷525/625

FIELD

DECODER

FRAME

SYNC

DECODER

8-42

Page 4

CD22402

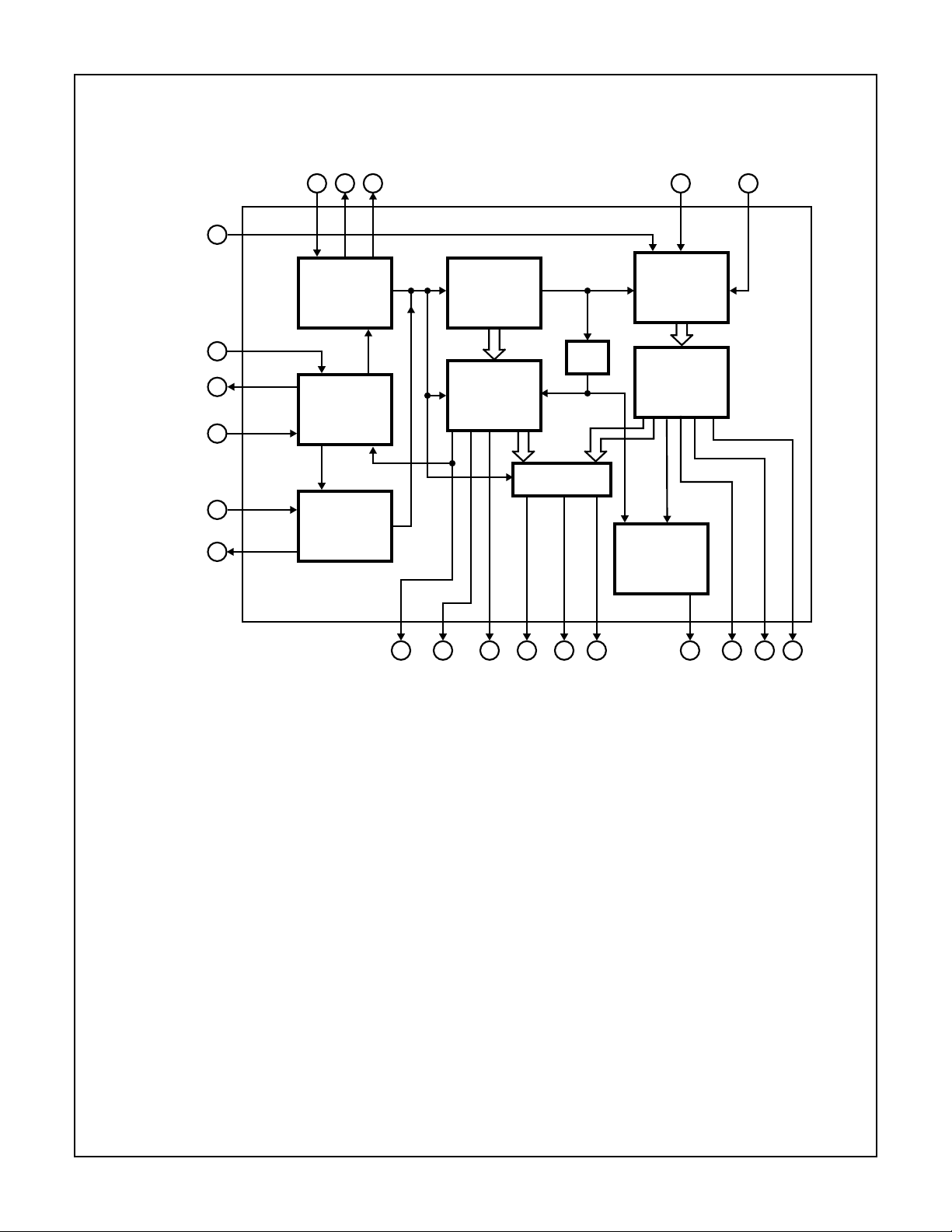

Absolute Maximum Ratings Thermal Information

DC Supply Voltage (Referenced to VSS Terminal). . . . . . . . . . . 15V

Input Voltage Range, All Inputs (Notes 2, 3) . . . . . . VSS≤ VI≤ V

DC Input Current, Any One Input (Note 2) . . . . . . . . . . . . . . ±10mA

Operating Conditions

Temperature Range

CD22402D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CD22402E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

2. To prevent damage to theinput protection circuit,input signals should never be greater than VDDnor less thanVSS. Input currentsmust

not exceed 10mA even when the power is off.

3. A connection must be provided at every input terminal. All unused inputs must be connected to VDD or VSS, whichever is appropriate.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

DD

SBDIP Package. . . . . . . . . . . . . . . . . . 50 10

PDIP Package. . . . . . . . . . . . . . . . . . . 50 N/A

Maximum Junction Temperature (SBDIP Package) . . . . . . . . 175oC

Maximum Junction Temperature (PDIP Package) . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

Electrical Specifications Values at -55

Values at -40oC, 25oC, 85oC Apply to E Package

P ARAMETER SYMBOL

DC ELECTRICAL SPECIFICATIONS

Quiescent Device Current IDD (Max) - 5 ----0.50.75 1 mA

Output Low (Sink) Current IOL (Min) 0.5 5 100 96 66 56 80 160 - µA

Output High (Source) Current

Output Voltage Low Level VOL (Max) - 5 0.15 0.15 0.15 0.15 - - 0.15 V

Output Voltage High Level VOH (Min) - 5 4.85 4.85 4.85 4.85 4.85 - - V

Input Low Voltage VIL (Max) 0.5, 4.5 5 1.5 1.5 1.4 1.4 - 2.25 1.5 V

Input High Voltage VIH (Min) 0.5, 4.5 5 3.6 3.6 3.5 3.5 3.5 2.25 - V

Input Current IIN (Max) - - -----10-pA

Refer to the CD4000B Series data book 250.5 for general operating and application considerations.

IOH (Min) 4.5 5 -100 -96 -66 -56 -80 -160 - µA

o

C, 25oC, 125oC Apply to D Package

TEST

CONDITIONS

V

V

O

(V)

-10----1.522.5mA

-15----345mA

5 5 1200 1155 787 672 960 1920 - µA

0.5 10 248 239 164 140 200 400 - µA

10 10 3000 2868 1968 1680 2400 4800 - µA

0 5 -1200 -1155 -787 -672 -960 -1920 - µA

9.5 10 -248 -239 -164 -140 -200 -400 - µA

0 10 -3000 -2868 -1968 -1680 -2400 -4800 - µA

- 10 0.15 0.15 0.15 0.15 - - 0.15 V

- 10 9.85 9.85 9.85 9.85 9.85 - - V

1, 9 10 3 3 2.9 2.9 - 4.5 3 V

1, 9 10 7.1 7.1 7 7 7 4.5 - V

DD

(V) MIN TYP MAX

o

-55

C -40oC85oC 125oC

25oC

UNITS

8-43

Page 5

CD22402

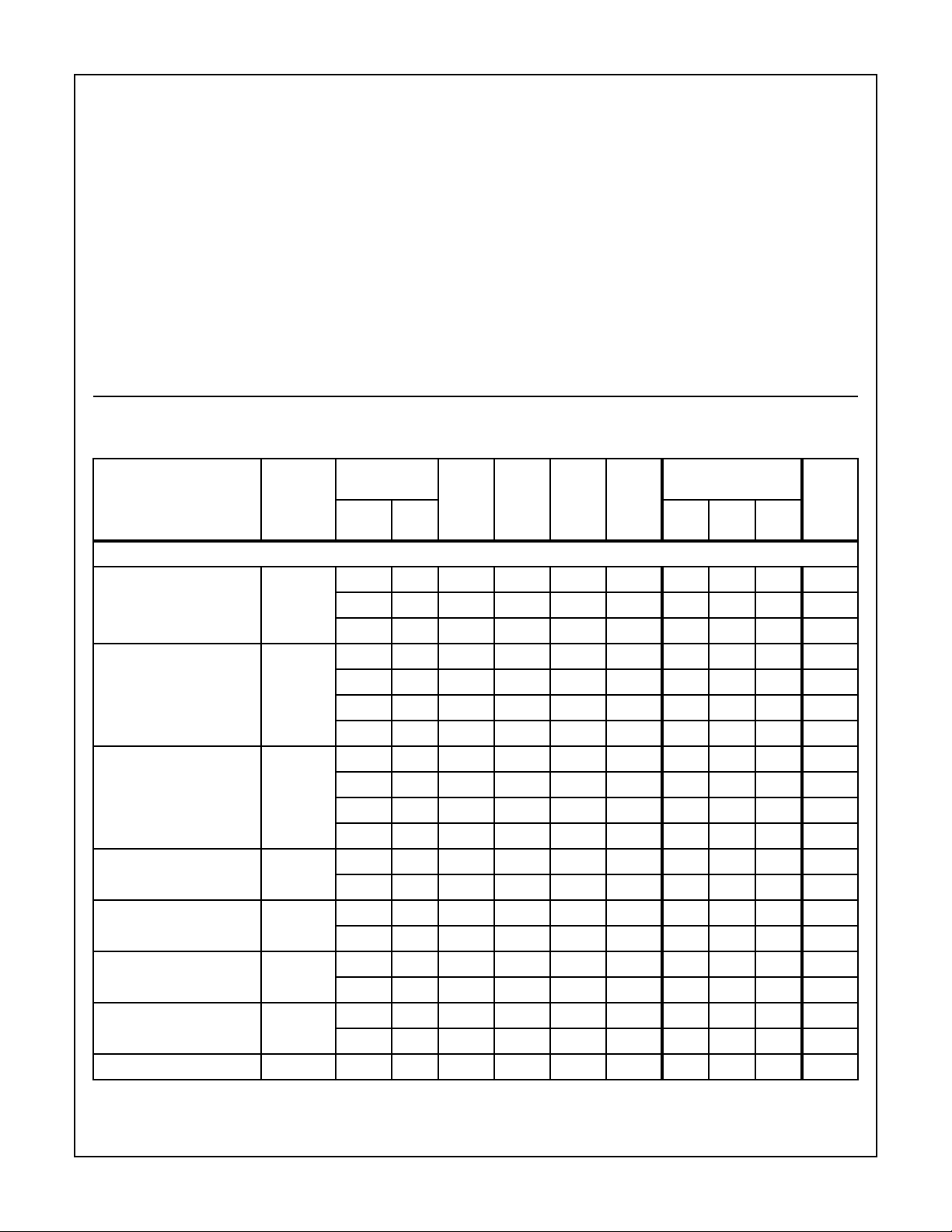

Switching Electrical Specifications T

= 25oC and CL = 15pF. Typical Temperature Coefficient for All Values of VDD = 0.3%/oC

A

TEST

CONDITIONS

PARAMETER (NOTE 4) SYMBOL

Output State Propagation Delay Time (50% to 50%)

Low-to-High Level t

High-to-Low Level t

PLH

PHL

5 - 40 80 ns

10 - 20 40 ns

Output State Transition Time (10% to 90%)

Low-to-High t

High-to-Low t

Input Capacitance (Per Input) C

TLH

THL

I

5 - 45 90 ns

10 - 30 60 ns

--5-pF

NOTE:

4. The characteristics given are defined for unbuffered gate in the CMOS process of the CD22402.

Logic Diagram

VERTICAL DRIVE (VERT. RESET

TO FIRST VERT. PULSE)

10K 10K

INTEGRATOR

10

+

RSQ

Q

22 24

GENLOCK OSC.

MIN TYP MAX UNITSVDD (V)

51pF

6

1M

20

(NOTE 5)

21

1

(NOTE 6)

23

2

GENLOCK

SYNC

1M

0.001µF

CRYSTAL

32 TIMES

503.496kHz

HOR.

DR

1N914

HORIZ.

100pF

NOTES:

5. Pin 21 high when pin 20 is high (or open).

6. Pin 1 high inhibits clock.

FIGURE 1. DETAIL OF THE OSCILLATOR/GENLOCK PORTION OF THE CD22402

SRQ

Q

HOR. PROCESS

BLANKING

CLOCK TO

COUNTERS

8-44

Page 6

Timing Waveforms

CD22402

MICROSECONDS

504kHz

OSC. PIN 2 OR 6

MIXED BLANKING

PIN 13

HORIZ. DRIVE PIN 4

MIXED BEAM

(CATHODE)

BLANKING

PIN 7

HORIZ. CLAMP

PIN 11

MIXED SYNC

PIN 5

0 1.98 3.97 5.95 7.94 9.92 11.90

11.9µs

3.97µs

7.94µs

1.98µs

3.97µs

H. SYNC

1.98µs

EQUALIZING

PULSE

V. SYNC

25.8µs

27.78 31.75 33.73

3.97µs

FIGURE 2. SYNC GENERATOR TIMING - 525/60Hz, HORIZONTAL TIMING WAVEFORMS

1.98µs

TO FIRST

EQUALIZING

LINE NO

MIXED SYNC

PIN 5

VERT. DRIVE

PIN 9

VERTICAL

PROCESSING

BLANKING

PIN 17

WIDE BLANKING

PIN 13

SHORT VERTICAL

DRIVE PIN 16

MIXED BEAM

(CATHODE)

BLANKING

PIN 7

FRAME SYNC

PIN 15

(ON ALTERNATE FIELDS)

PULSE

VERTICAL RESET

TO FIRST

VERTICAL PULSE

0 1 2 3 4 5 6 7 8 9 10 21

0.57ms

1.33ms

0.19ms

1.98µs (NOT TO SCALE)

FIGURE 3. SYNC GENERATOR TIMING - 525/60Hz, VERTICAL TIMING WAVEFORMS

8-45

Page 7

CD22402

Timing Waveforms

MICROSECONDS

OSC. PIN 2 OR 6

MIXED BLANKING

HORIZ. DRIVE PIN 4

MIXED SYNC

500kHz

PIN 13

CATHODE

BLANKING

PIN 7

HORIZ. CLAMP

PIN 11

PIN 5

H. SYNC

EQUALIZING

V. SYNC

(Continued)

024681012

12µs

4µs

8µs

2µs

4µs

2µs

PULSE

26µs

28 32

2µs

4µs

VERTICAL RESET TO

FIRST EQUALIZING

LINE NO

MIXED SYNC

PIN 5

VERT. DRIVE

PIN 9

VERTICAL

PROCESSING

BLANKING

PIN 17

WIDE BLANKING

SHORT VERTICAL

(ON ALTERNATE FIELDS)

PIN 13

DRIVE PIN 16

CATHODE

BLANKING

PIN 7

FRAME SYNC

PIN 15

FIGURE 4. SYNC GENERATOR TIMING - 625/50Hz, HORIZONTAL TIMING WAVEFORMS

VERTICAL RESET

TO FIRST

PULSE

0 1 2 3 4 5 6 7 8 9 10 21

2µs (NOT TO SCALE)

VERTICAL PULSE

0.57ms

1.36ms

0.194ms

FIGURE 5. SYNC GENERATOR TIMING - 625/50Hz, VERTICAL TIMING WAVEFORMS

8-46

Page 8

CD22402

Timing Waveforms

FIELD NO. 1

PIN 5

PIN 9

FIELD NO. 2

PIN 5

PIN 9

(Continued)

LINE 0 LINE 9

LINE 262-1/2 (312-1/2)

FIRST EQUALIZING PULSE

1 CLK

2 CLKS

LINE 271 (321)

1 CLK

2 CLKS

SEE NOTES 1, 2

2 CLKS

2 CLKS

1 CLK

14 CLKS

FIGURE 6. EXPANDED VERTICAL-TIMING WAVEFORM DETAIL OF SYNC GENERATOR TIMING (VERTICAL DRIVE - PIN 9)

FIELD NO. 1

PIN 5

PIN 17

FIELD NO. 2

PIN 5

PIN 17

LINE 0 LINE 21

FIRST EQUALIZING PULSE

1 CLK

2 CLKS

LINE 262-1/2 (312-1/2)

1 CLK

LINE 283 (333)

2 CLKS

2 CLKS

2 CLKS

2 CLKS

SEE NOTES 1, 2

14 CLKS

FIGURE 7. EXPANDED VERTICAL-TIMING WAVEFORM DETAIL OF SYNC GENERATOR TIMING (VERTICAL PROCESSING

BLANKING - PIN 17)

8-47

Page 9

CD22402

Timing Waveforms

FIELD NO. 1

FIELD NO. 2

LINE 0

PIN 5

PIN 13

LINE 262-1/2 (312-1/2)

PIN 5

PIN 13

(Continued)

FIRST EQUALIZING PULSE

1 CLK

2 CLKS

1 CLK

1 CLK

LINE 21

2 CLKS

1 CLK

6 CLKS

LINE 283 (333)

2 CLKS

2 CLKS

SEE NOTES 1, 2

14 CLKS

FIGURE 8. EXPANDED VERTICAL-TIMING WAVEFORM DETAIL OF SYNC GENERATOR TIMING (MIXED PROCESSING

BLANKING - PIN 13)

FIELD NO. 1

FIELD NO. 2

PIN 5

PIN 16

PIN 5

PIN 16

LINE 3

2 CLKS

LINE 265-1/2 (315-1/2)

LINE 6

1 CLK

2 CLKS

LINE 268-1/2 (318-1/2)

2 CLKS

SEE NOTES 1, 2

FIGURE 9. EXPANDED VERTICAL-TIMING WAVEFORM DETAIL OF SYNC GENERATORTIMING

(SHORT VERTICAL DRIVE - PIN 16)

8-48

2 CLKS

Page 10

CD22402

Timing Waveforms

PIN 5

PIN 7

PIN 5

1 CLK

PIN 7

(Continued)

LINE 2

1 CLK

4

CLKS

LINE 265 (315)

LINE 3

15

CLKS

2 CLKS

LINE 265-1/2 (315-1/2) LINE 268-1/2 (318-1/2) LINE 269 (319)

15 CLKS

4 CLKS 2 CLKS

2 CLKS

SEE NOTES 7, 8

LINE 6 LINE 7

16 CLKS

4 CLKS2 CLKS

NOTES:

7. Waveforms shown are for 525 line/60Hz, line number in parenthesis are for (625 line/50Hz).

8. Timing widths by clock count; for 525 line, 1 CLK = 1.98µs; for 625 line, 1 CLK = 2µs; 1 horizontal period = 32 CLKS.

FIGURE 10. EXPANDED VERTICAL-TIMING WAVEFORM DETAIL OF SYNC GENERATOR TIMING (MIXED BEAM BLANKING - PIN 7)

Typical Applications

COMPOSITE VIDEO INPUT

VERTICAL SYNC

FROM SHORT

VERTICAL

FROM POWER LINE

FOR LINE-LOCK

OPERATION

CROSSING

DETECTOR

(Refer to Application Note AN8742, for more information)

V

20

10

8

6

22

24

1

21

23

2

3, 12

DD

19

4

11

7

13

14

9

16

5

15

17

18

MIXED SYNC. OR

(OPTIONAL)

DRIVE

ZERO

HORIZ. PHASE ADJ.

HORIZ.

SYNC

RESTORER

100pF

GEN LOCK

OSC.

PLL

AUTO GEN

LOCK

CONTROL

1MΩ

CRYSTAL

OSC.

100pF

φ

VERT.

10kΩ

1MΩ

HORIZONTAL DRIVE

HORIZONTAL CLAMP

MIXED BEAM (CATHODE) BLANKING

MIXED PROCESSING BLANKING

HORIZONTAL PROCESSING BLANKING

VERTICAL DRIVE

SHORT VERTICAL DRIVE

MIXED SYNC

FRAME SYNC OUTPUT (ODD FIELD)

VERTICAL PROCESSING BLANKING OUTPUT

OPERATION SWITCH FOR 525-LINE OR

625-LINE RASTER

FIGURE 11. TYPICAL APPLICATION IN A TV CAMERA

8-49

Page 11

CD22402

13

-

14

100kΩ

1

1kΩ

0.0022µF

10µF2kΩ

0.1µF

2MΩ

100kΩ

1N914

0.5 TO 2V

VIDEO SIGNAL IN

P-P

= +5

V

CC

GND

3.3µF

75Ω

10kΩ

V

SSVDD

2

3

10µF

-

1

+

2kΩ

NOTE: The genlock input to pins 10 and 20 of the CD22402 are direct coupled to the output from Pins 8 and 14 of the CA5470. Refer to

Application Note AN-8742 for additional information.

FIGURE 12. SUGGESTED SYNC-SEPARATOR CIRCUIT USING THE CA5470 BIMOS-E QUAD OP AMP IN THE VDD RANGE

OF 4V TO 12V

12

5

6

4

+

+

7

2

-

0.0022µF

0.0022µF

10kΩ

10kΩ

9

3

10

+

CA5470 BIMOS-E QUAD OP AMP

PIN 4 TO +5V (V

PIN 11 TO GND (V

DD

SS

NEG. HORIZ. SYNC OUT

(TO PIN 20 - CD22402)

POS. HORIZ. SYNC OUT

8

NEG. VERTICAL SYNC OUT

(TO PIN 10 - CD22402)

)

)

8-50

Loading...

Loading...