Page 1

Bt8370/8375/8376

Fully Integrated T1/E1 Framer and Line Interface

The Bt8370/8375/8376 is a family of single chip transceivers for T1/E1 and Integrated

Service Digital Network (ISDN) primary rate interfaces, operating at 1.544 Mbps or

2.048 Mbps. These devices combine a sophisticated framer, transmit and receive slip

buffers, and an on-chip physical line interface to provide a complete T1/E1 transceiver.

The fully featured Bt8370 and short-haul Bt8375 and Bt8376 devices provide a

programmable clock rate adapter for simplifying system bus interfacing. The adapter

synthesizes standard clock signals from the receive or transmit line rate clocks or from an

external reference.

Operations are controlled through memory-mapped registers accessible via a parallel

microprocessor port. Current ANSI, ETSI, ITU-T, and Bellcore standards are supported for

alarm and error monitoring, signaling supervision (e.g., LAPD/SS7), per-channel trunk

conditioning, and Facility Data Link (FDL) maintenance. A serial Time Division Multiplexed

(TDM) system bus interface allows the backplane Pulse Code Modulation (PCM) data

highway to operate at rates from 1.536 to 8.192 Mbps. Extensive test and diagnostic

functions include a full set of digital and analog loopbacks, PRBS test pattern generation,

BER meter, and forced error insertion.

The physical line interface circuit recovers clock and data from analog signals with +3 to

–43 dB cable attenuation, appropriate for both sho rt (– 18 dB) and lo ng-hau l T 1/E 1

applications. Receive line equalization (EQ) and transmit Line Build Out (LBO) filters are

implemented using Digital Signal Processor (DSP) circuits for reliable performance. Data

and/or clock jitter attenuation can be inserted on either the receive or transmit path. The

transmit section includes precision pulse shaping and amplitude pre-emphasis for cross

connect applications, as well as a set of LBO filters for long-haul Channel Service Unit

(CSU) applications. A complementary driver output is provided to couple 75/100/120 Ω

lines via an external transformer.

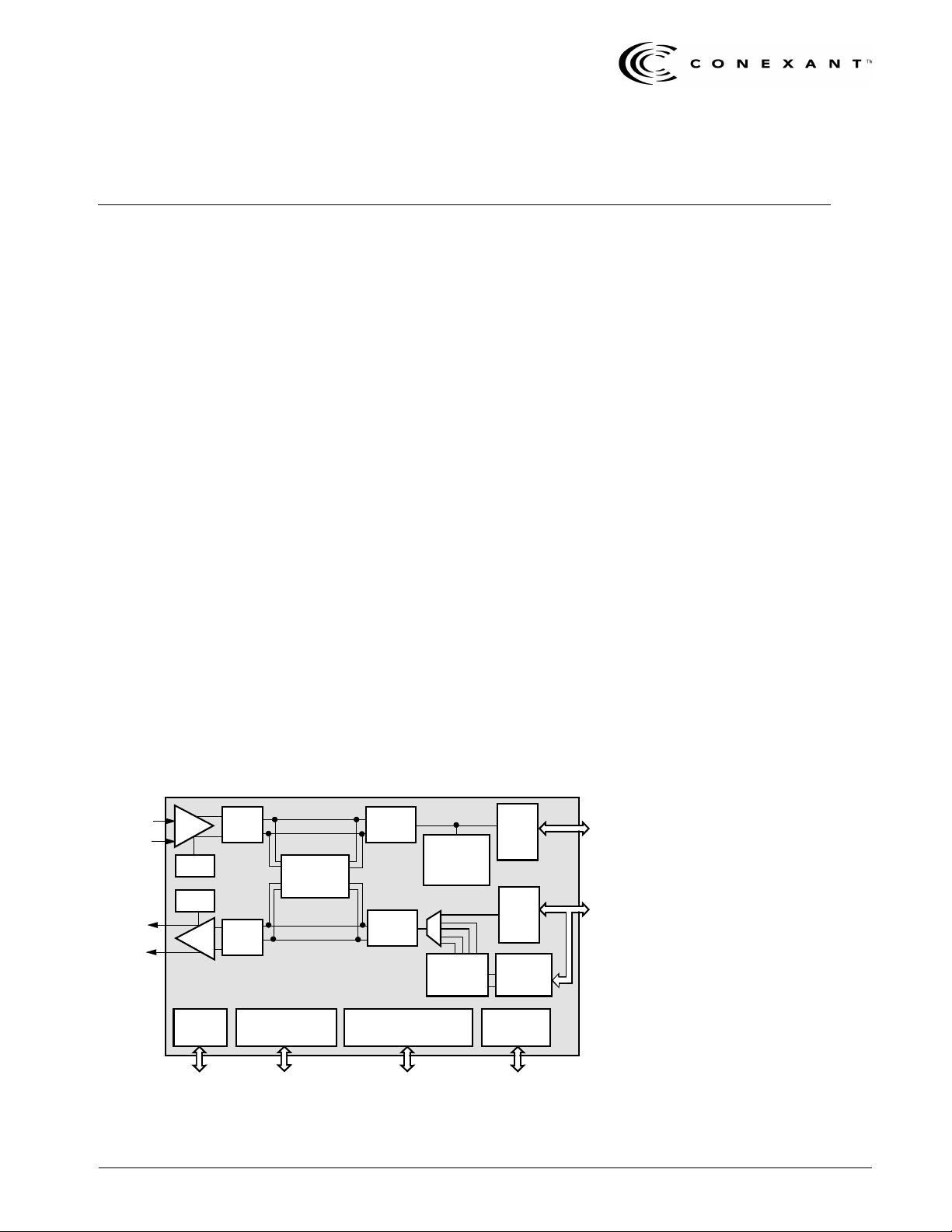

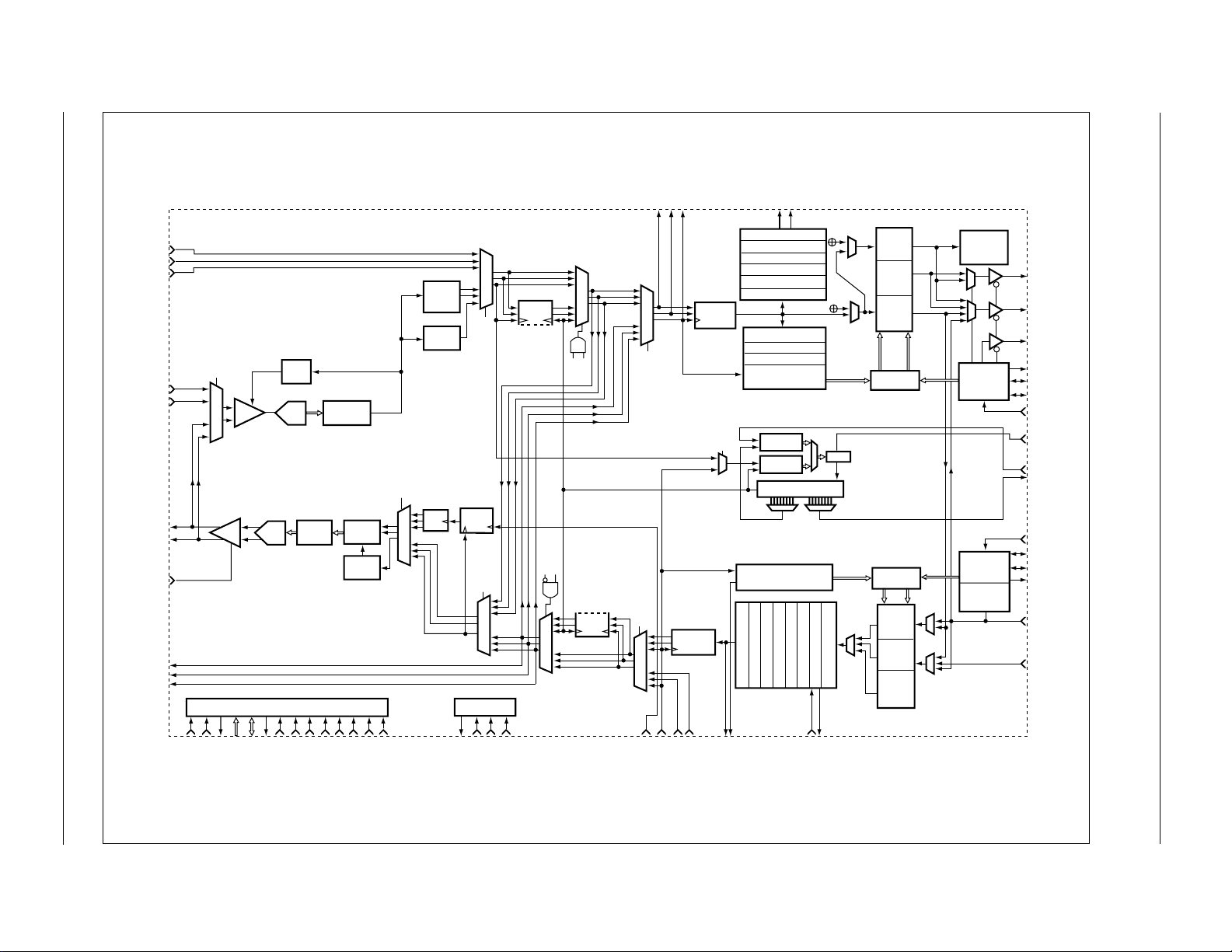

Functional Block Diagram

Distinguishing Features

• Single-chip T1/E1 framer with

short/long-haul physical line

interface

• Frames to popular T1/E1 standards:

– T1: SF, ESF, SLC 96, T1DM

– E1: PCM

ISDN primary rate

• On-chip physical line inte rface

compatible with:

– DSX-1/E1 short-haul signals

– DS-1 (T1.403) and ETSI long-haul

signals

• T wo-frame transmit and receive PCM

slip buffers

• Clock rate adapter synthesizes jitter

attenuated system clocks from an

internal or external reference

• Parallel 8-bit microprocessor port

supports Intel or Motorola buses

• Automated Facility Data Link (FDL)

management

• BERT generation and counting

• Two full-duplex HDLC controllers for

data link and LAPD/SS7 signaling

• B8ZS/HDB3/Bit 7 zero suppression

• 80-pin MQFP surface-mount package

• Operates from a single +5 Vdc ±5%

power supply

• Low-power CMOS technology

30, G.704, G.706, G.732

-

Receive

Analog

Transmit

Analog

RX

RPLL

TPLL

TX

JTAG

Test Port

EQ

Pulse

LBO

Control/Status

Registers

Motorola/Intel

Processor Bus

TX or RX

Jitter

Attenuator

ZCS

Decode

T1/E1

Receive

Framer

ZCS

Encode

Overhead

Insertion

Data Link Controllers

DL1 + DL2

External DL3

RX

Slip

Buffer

TX

Slip

Buffer

T1/E1

Transmit

Framer

Clock Rate

Adaptor

CLAD I/ODual-Rail/NRZ/

Receive

System

Bus

Transmit

System

Bus

Applications

• T1/E1 Channel Service Unit/Data

Service Unit (CSU/DSU)

• Digital Access Cross-Connect

Systems (DACS)

• T1/E1 Multiplexer (MUX)

• PBXs and PCM channel bank

• T1/E1 HDSL terminal unit

• ISDN Primary Rate Access (PRA)

Data Sheet N8370DSE

June 30, 1999

Page 2

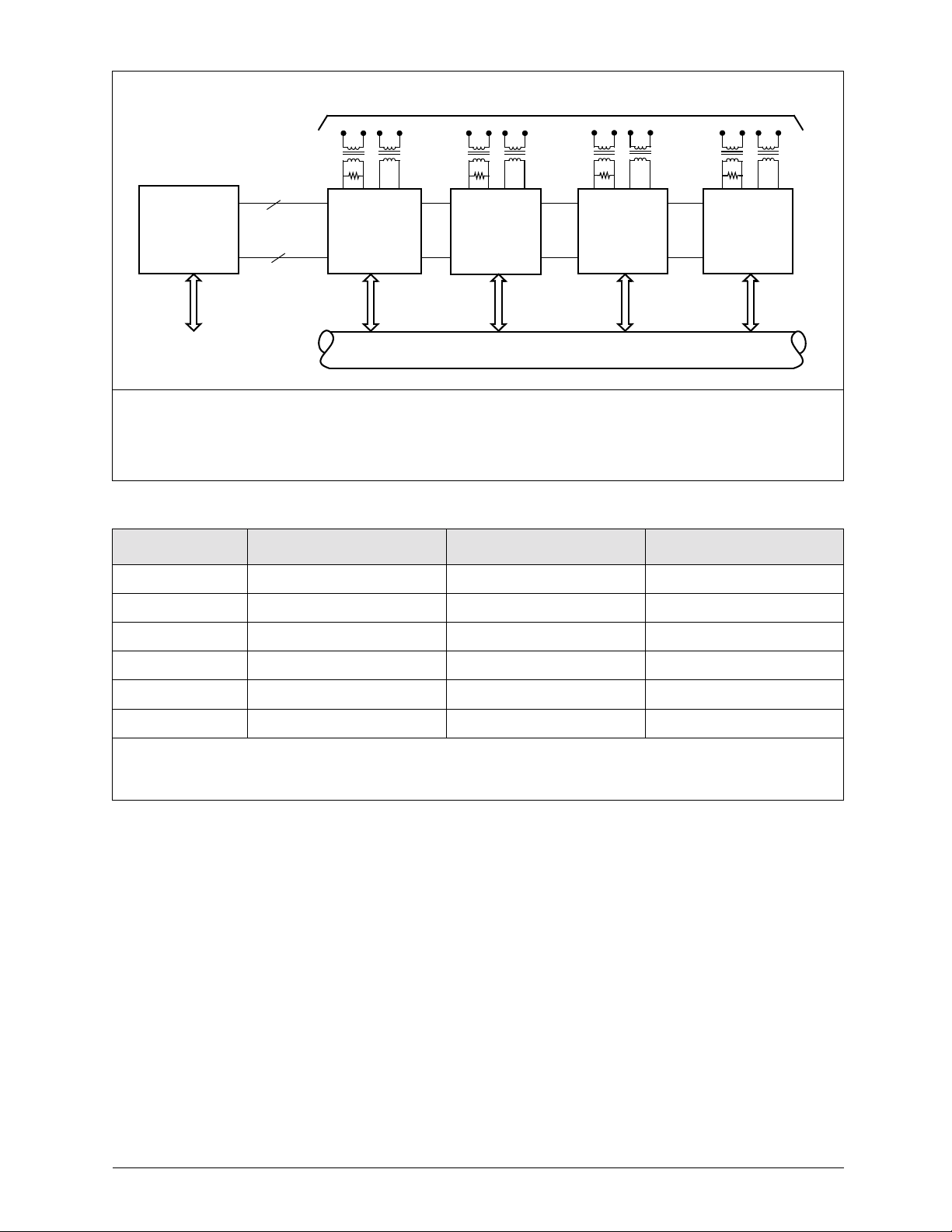

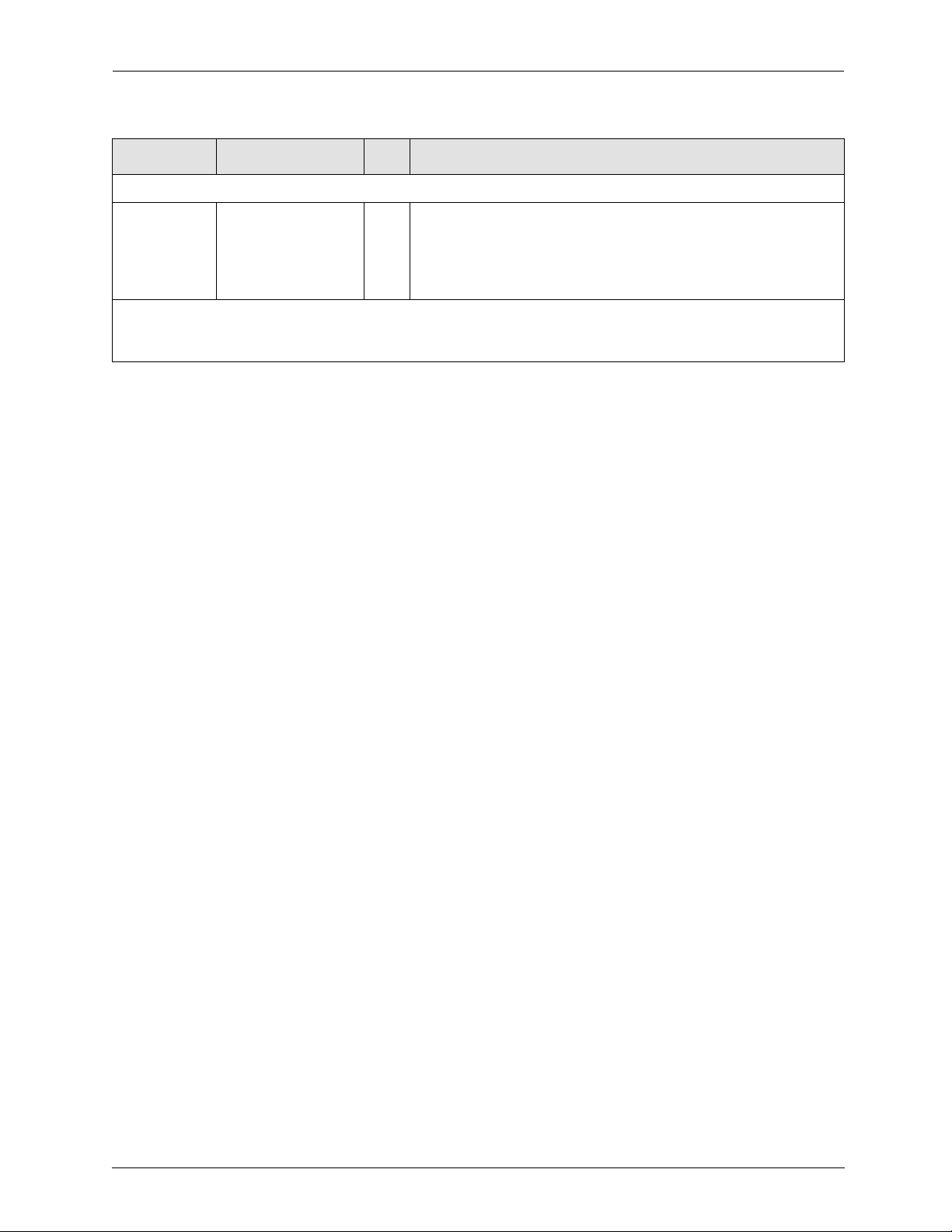

Bt8370EVM—Bt8370 Evaluation Module, Quad T1/E1 ISDN PRI Board

T1 or E1 connection at DSX or CSU levels

Address

Bus

MC68302

Microprocessor

9

Data Bus

8

Bt8370

Bt8370

Bt8370 Bt8370 Bt8370

RS232 User

Interface

Local PCM Highway (128 Channel, 8 MHz)

An evaluation module is available and provides a convenient platform to test and evaluate Bt8370 performance and features. The Bt8370EVM provides up to four T1/E1 transceivers, all necessary line interface circuitry for T1 and E1 connections, and a simple RS232 serial user interface for setting device parameters and displaying status information on

any VT100 compatible terminal. Contact the local sales representative for ordering information and pricing.

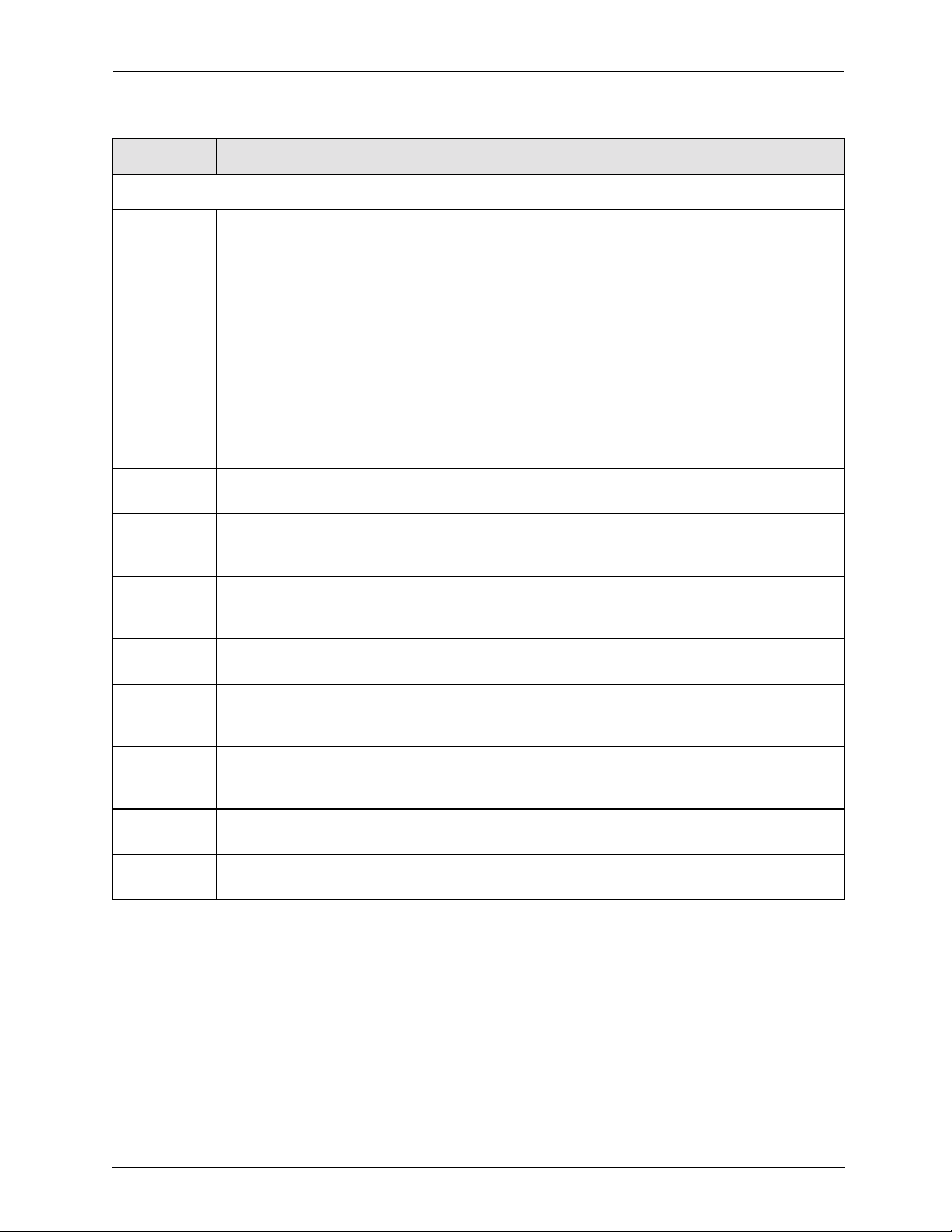

Ordering Information

Model Number Package Operating Temperature Reduced Features

Bt8370EPF 80-Pin MQFP –40 to 85 °C none

Bt8370KPF 80-Pin MQFP 0 to 70 °C none

Bt8375EPF 80-Pin MQFP –40 to 85 °C Short-Haul

Bt8375KPF 80-Pin MQFP 0 to 70 °C Short-Haul

Bt8376EPF 80-Pin MQFP –40 to 85 °C Short-Haul, No CLAD output

Bt8376KPF 80-Pin MQFP 0 to 70 °C Short-Haul, No CLAD output

NOTE(S):

(1)

Cost reduced Bt8375 and Bt8376 are pin and register-compatible versions of Bt8370 with reduced features. Contact the local

sales representative for ordering information and pricing.

(1)

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant and “What’s Next in Communications Technologies” are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Printed in U.S.A.

All Rights Reserved

Reader Response:

To improv e the quality of our publications, w e welcome y our feedback. Please send comments or

suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical

questions at this address. Please contact your local Conexant sales office or applications engineer if you have

technical questions.

N8370DSE

Conexant

Page 3

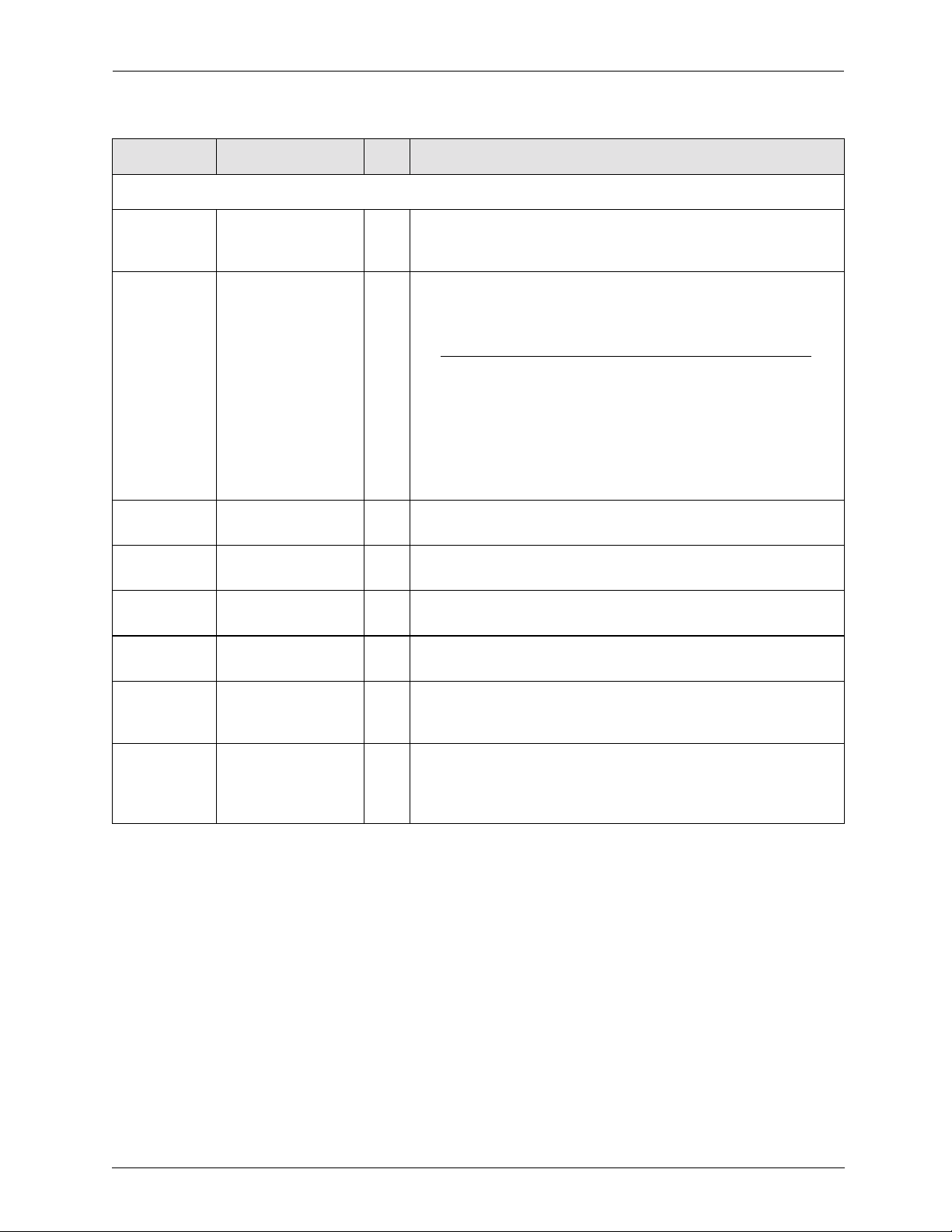

Table of Contents

List of Figures

List of Tables

1.0 Pin Descriptions

1.1 Pin Assignments

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xv

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

2.0 Circuit Description

2.1 Bt8370/8375/8376 Block Diagrams

2.2 Receive Line Interface Unit

2.2.1 Data Recovery

2.2.1.1 Automatic Gain Control

2.2.1.2 Variable Gain Amplifier

2.2.1.3 Adaptive Equalizer

2.2.1.4 Data Slicer

2.2.2 Clock Recovery

2.2.2.1 Phase Locked Loop

2.3 Jitter Attenuator

2.3.1 Elastic Store

2.4 Receiver

2.4.1 ZCS Decoder

2.4.2 In-Band Loopback Code Detection

2.4.3 Error Counters

2.4.4 Error Monitor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.4.3.1 Frame Bit Error Counter

2.4.3.2 CRC Error Counter

2.4.3.3 LCV Error Counter

2.4.3.4 FEBE Counter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

N8370DSE

Conexant

iii

Page 4

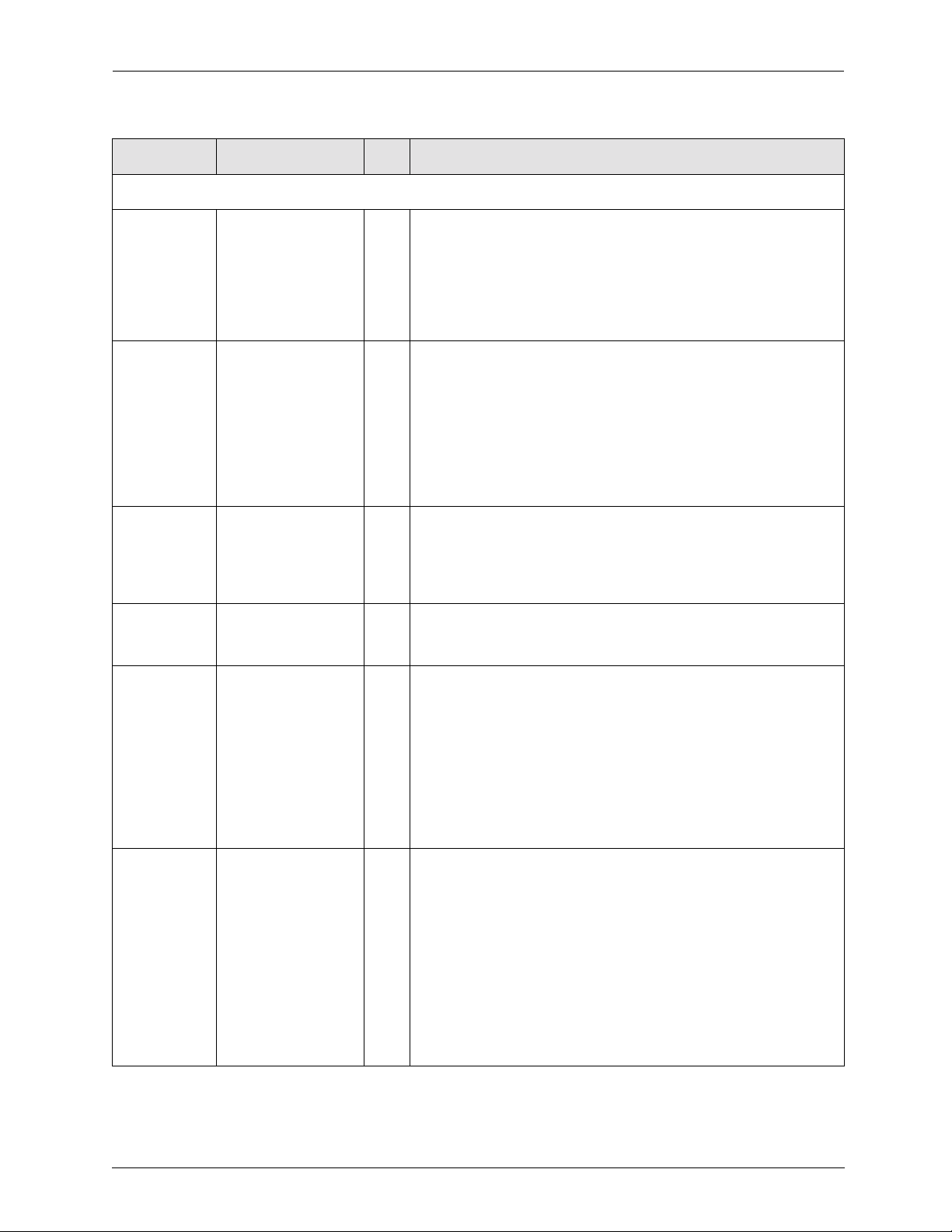

Table of Contents

Bt8370/8375/8376

2.4.5 Alarm Monitor

2.4.5.1 Loss of Frame

2.4.5.2 Loss of Signal

2.4.5.3 Analog Loss of Signal

2.4.5.4 Alarm Indication Signal

2.4.5.5 Yellow Alarm

2.4.5.6 Multiframe YEL

2.4.5.7 Severely Errored Frame

2.4.5.8 Change of Frame Alignment

2.4.5.9 Receive Multiframe AIS

2.4.6 Test Pattern Receiver

2.4.7 Receive Framing

2.4.8 External Receive Data Link

2.4.9 Sa-Byte Receive Buffers

2.4.10 Receive Data Link

2.4.10.1 Data Link Controllers

2.4.10.2 RBOP Receiver

2.5 Receive System Bus

2.5.1 Timebase

2.5.2 Slip Buffer

2.5.3 Signaling Buffer

2.5.4 Signaling Stack

2.5.5 Embedded Framing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

Fully Integrated T1/E1 Framer and Line Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.6 Clock Rate Adapter

2.6.1 Configuring the CLAD Registers

2.7 Transmit System Bus

2.7.1 Timebase

2.7.2 Slip Buffer

2.7.3 Signaling Buffer

2.7.4 Transmit Framing

2.7.5 Embedded Framing

2.8 Transmitter

2.8.1 External Transmit Data Link

2.8.2 Transmit Data Links

2.8.3 Sa-Byte Overwrite Buffer

2.8.4 Overhead Pattern Generator

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-53

2.8.2.1 Data Link Controllers

2.8.2.2 PRM Generator

2.8.4.1 Framing Pattern Generation

2.8.4.2 Alarm Generator

2.8.4.3 CRC Generation

2.8.4.4 Far-End Block Error Generation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-63

iv

Conexant

N8370DSE

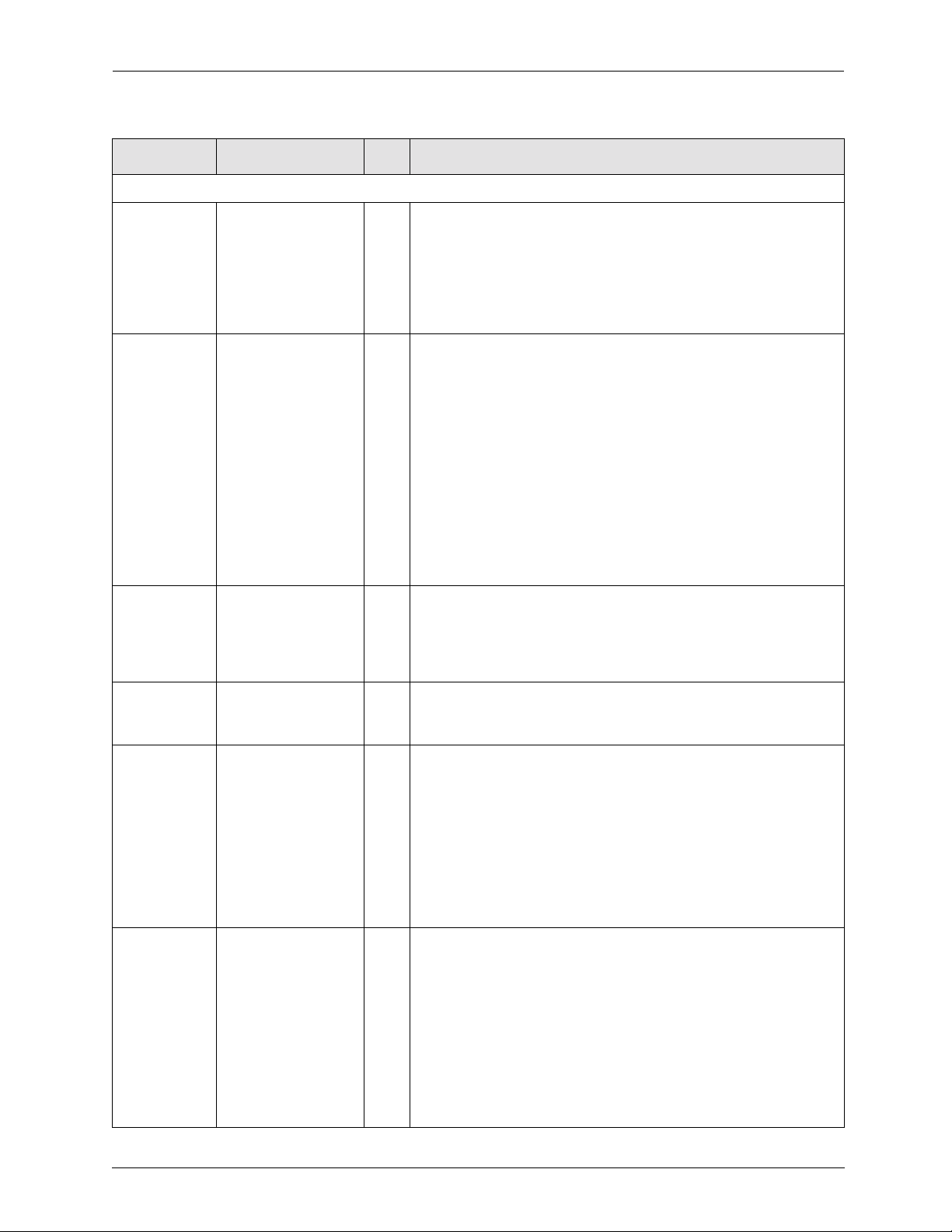

Page 5

Bt8370/8375/8376

Table of Contents

Fully Integrated T1/E1 Framer and Line Interface

2.8.5 Test Pattern Generator

2.8.6 Transmit Error Insertion

2.8.7 In-Band Loopback Code Generator

2.8.8 ZCS Encoder

2.9 Transmit Line Interface Unit

2.9.1 Pulse Shape

2.9.2 Transmit Phase Lock Loop

2.9.2.1 Clock Reference

2.9.2.2 Output Jitter

2.9.3 Line Build Out

2.9.4 Line Driver

2.9.4.1 Termination Impedance

2.9.4.2 Return Loss

2.9.4.3 Output Enable

2.9.5 Pulse Imbalance

2.10 Microprocessor Interface

2.10.1 Address/Data Bus

2.10.2 Bus Control Signals

2.10.3 Interrupt Requests

2.10.4 Device Reset

2.10.4.1 Power-On Reset (POR)

2.10.4.2 Hardware Reset

2.10.4.3 Software Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-65

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-77

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-85

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-82

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-83

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-65

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-76

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-76

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-77

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-82

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-85

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-85

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-85

2.11 Loopbacks

2.11.1 Remote Line Loopback

2.11.2 Remote Payload Loopback

2.11.3 Remote Per-Channel Loopbacks

2.11.4 Local Analog Loopback

2.11.5 Local Framer Loopback

2.11.6 Local Per-Channel Loopback

2.12 Joint Test Access Group

2.12.1 Instructions

2.12.2 Device Identification Register

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-88

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-88

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-89

N8370DSE

Conexant

v

Page 6

Table of Contents

Bt8370/8375/8376

3.0 Registers

3.1 Address Map

3.2 Global Control and Status Registers

3.3 Interrupt Control Register

3.4 Interrupt Status Registers

Fully Integrated T1/E1 Framer and Line Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

000—Device Identification (DID)

001—Primary Control Register (CR0)

002—Jitter Attenuator Configuration (JAT_CR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

003—Interrupt Request Register (IRR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

004—Alarm 1 Interrupt Status (ISR7)

005—Alarm 2 Interrupt Status (ISR6)

006—Error Interrupt Status (ISR5)

007—Counter Overflow Interrupt Status (ISR4)

008—Timer Interrupt Status (ISR3)

009—Data Link 1 Interrupt Status (ISR2)

00A—Data Link 2 Interrupt Status (ISR1)

00B—Pattern Interrupt Status (ISR0)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

3.5 Interrupt Enable Registers

00C—Alarm 1 Interrupt Enable Register (IER7)

00D—Alarm 2 Interrupt Enable Register (IER6)

00E—Error Interrupt Enable Register (IER5)

00F—Count Overflow Interrupt Enable Register (IER4)

010—Timer Interrupt Enable Register (IER3)

011—Data Link 1 Interrupt Enable Register (IER2)

012—Data Link 2 Interrupt Enable Register (IER1)

013—Pattern Interrupt Enable Register (IER0)

3.6 Primary Control and Status Registers

014—Loopback Configuration Register (LOOP)

015—External Data Link Time Slot (DL3_TS)

016—External Data Link Bit (DL3_BIT)

017—Offline Framer Status (FSTAT)

018—Programmable Input/Output (PIO)

019—Programmable Output Enable (POE)

01A—Clock Input Mux (CMUX)

01B—Test Mux Configuration (TMUX)

01C—Test Configuration (TEST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

. . . . . . . . . . . . . . . . . . . . . . . . . 3-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-37

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-37

vi

Conexant

N8370DSE

Page 7

Bt8370/8375/8376

Table of Contents

Fully Integrated T1/E1 Framer and Line Interface

3.7 Receive LIU Registers

020—LIU Configuration (LIU_CR)

021—Receive LIU Status (RSTAT)

022—Receive LIU Configuration (RLIU_CR)

023—RPLL Low Pass Filter (LPF)

024—Variable Gain Amplifier Maximum (VGA_MAX)

025—Equalizer Coefficient Data Register (EQ_DAT)

026—Equalizer Coefficient Table Pointer (EQ_PTR)

027—Data Slicer Threshold (DSLICE)

028—Equalizer Output Levels

029—Variable Gain Amplifier Status

02A—Pre_Equalizer (PRE_EQ)

030–037—LMS Adjusted Equalizer Coefficient Status (COEFF)

038–03C—Equalizer Gain Thresholds (GAIN)

3.8 Receiver Registers

040—Receiver Configuration (RCR0)

041—Receive Test Pattern Configuration (RPATT)

042—Receive Loopback Code Detector Configuration (RLB)

043—Loopback Activate Code Pattern (LBA)

044—Loopback Deactivate Code Pattern (LBD)

045—Receive Alarm Signal Configuration (RALM)

046—Alarm/Error/Counter Latch Configuration (LATCH)

047—Alarm 1 Status (ALM1)

048—Alarm 2 Status (ALM2)

049—Alarm 3 Status (ALM3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-40

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-41

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-42

. . . . . . . . . . . . . . . . . . . . . . . . . . . 3-42

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-46

. . . . . . . . . . . . . . . . . . . 3-46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-48

. . . . . . . . . . . . . . . . . . . . . 3-50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-51

. . . . . . . . . . . . . . . . . . . . . . . . 3-52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-56

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-57

3.9 Performance Monitoring Registers

050—Framing Bit Error Counter LSB (FERR)

051—Framing Bit Error Counter MSB (FERR)

052—CRC Error Counter LSB (CERR)

053—CRC Error Counter MSB (CERR)

054—Line Code Violation Counter LSB (LCV)

055—Line Code Violation Counter MSB (LCV)

056—Far End Block Error Counter LSB (FEBE)

057—Far End Block Error Counter MSB (FEBE)

058—PRBS Bit Error Counter LSB (BERR)

059—PRBS Bit Error Counter MSB (BERR)

05A—SEF/LOF/COFA Alarm Counter (AERR)

3.10 Receive Sa-Byte Buffers

05B—Receive Sa4 Byte Buffer (RSA4)

05C—Receive Sa5 Byte Buffer (RSA5)

05D—Receive Sa6 Byte Buffer (RSA6)

05E—Receive Sa7 Byte Buffer (RSA7)

05F—Receive Sa8 Byte Buffer (RSA8)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-63

N8370DSE

Conexant

vii

Page 8

Table of Contents

Bt8370/8375/8376

3.11 Transmit LIU Registers

060–067—Transmit Pulse Shape Configuration (SHAPE)

068—Transmit LIU Configuration (TLIU_CR)

3.12 Transmitter Registers

070—Transmit Framer Configuration (TCR0)

071—Transmitter Configuration (TCR1)

072—Transmit Frame Format (TFRM)

073—Transmit Error Insert (TERROR)

074—Transmit Manual Sa-Byte/FEBE Configuration (TMAN)

075—Transmit Alarm Signal Configuration (TALM)

076—Transmit Test Pattern Configuration (TPATT)

077—Transmit Inband Loopback Code Configuration (TLB)

078—Transmit Inband Loopback Code Pattern (LBP)

3.13 Transmit Sa-Byte Buffers

07B—Transmit Sa4 Byte Buffer (TSA4)

07C—Transmit Sa5 Byte Buffer (TSA5)

07D—Transmit Sa6 Byte Buffer (TSA6)

07E—Transmit Sa7 Byte Buffer (TSA7)

07F—Transmit Sa8 Byte Buffer (TSA8)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-80

Fully Integrated T1/E1 Framer and Line Interface

. . . . . . . . . . . . . . . . . . . . . . . 3-64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-71

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-73

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-74

. . . . . . . . . . . . . . . . . . . . . 3-75

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-76

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-77

. . . . . . . . . . . . . . . . . . . . . . 3-79

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-79

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-82

3.14 Clock Rate Adapter Registers

090—Clock Rate Adapter Configuration (CLAD_CR)

091—CLAD Frequency Select (CSEL)

092—CLAD Phase Detector Scale Factor (CPHASE)

093—CLAD Test (CTEST)

3.15 Bit-Oriented Protocol Registers

0A0—Bit Oriented Protocol Transceiver (BOP)

0A1—Transmit BOP Codeword (TBOP)

0A2—Receive BOP Codeword (RBOP)

0A3—BOP Status (BOP_STAT)

3.16 Data Link Registers

0A4—DL1 Time Slot Enable (DL1_TS)

0A5—DL1 Bit Enable (DL1_BIT)

0A6—DL1 Control (DL1_CTL)

0A7—RDL #1 FIFO Fill Control (RDL1_FFC)

0A8—Receive Data Link FIFO #1 (RDL1)

0A9—RDL #1 Status (RDL1_STAT)

0AA—Performance Report Message (PRM)

0AB—TDL #1 FIFO Empty Control (TDL1_FEC)

0AC—TDL #1 End Of Message Control (TDL1_EOM)

0AD—Transmit Data Link FIFO #1 (TDL1)

0AE—TDL #1 Status (TDL1_STAT)

0AF—DL2 Time Slot Enable (DL2_TS)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-83

. . . . . . . . . . . . . . . . . . . . . . . . . . . 3-83

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-84

. . . . . . . . . . . . . . . . . . . . . . . . . . . 3-85

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-89

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-96

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-98

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-99

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-100

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-100

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-100

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-101

viii

Conexant

N8370DSE

Page 9

Bt8370/8375/8376

Table of Contents

Fully Integrated T1/E1 Framer and Line Interface

0B0—DL2 Bit Enable (DL2_BIT)

0B1—DL2 Control (DL2_CTL)

0B2—RDL #2 FIFO Fill Control (RDL2_FFC)

0B3—Receive Data Link FIFO #2 (RDL2)

0B4—RDL #2 Status (RDL2_STAT)

0B6—TDL #2 FIFO Empty Control (TDL2_FEC)

0B7—TDL #2 End Of Message Control (TDL2_EOM)

0B8—Transmit Data Link FIFO #2 (TDL2)

0B9—TDL #2 Status (TDL2_STAT)

0BA—DLINK Test Configuration (DL_TEST1)

0BB—DLINK Test Status (DL_TEST2)

0BC—DLINK Test Status (DL_TEST3)

0BD—DLINK Test Control #1 or Configuration #2 (DL_TEST4)

0BE—DLINK Test Control #2 or Configuration #2 (DL_TEST5)

3.17 System Bus Registers

0D0—System Bus Interface Configuration (SBI_CR)

0D1—Receive System Bus Configuration (RSB_CR)

0D2—RSB Sync Bit Offset (RSYNC_BIT)

0D3—RSB Sync Time Slot Offset (RSYNC_TS)

0D4—Transmit System Bus Configuration (TSB_CR)

0D5—TSB Sync Bit Offset (TSYNC_BIT)

0D6—TSB Sync Time Slot Offset (TSYNC_TS)

0D7—Receive Signaling Configuration (RSIG_CR)

0D8—Signaling Reinsertion Frame Offset (RSYNC_FRM)

0D9—Slip Buffer Status (SSTAT)

0DA—Receive Signaling Stack (STACK)

0DB—RSLIP Phase Status (RPHASE)

0DC—TSLIP Phase Status (TPHASE)

0DD—RAM Parity Status (PERR)

0E0–0FF—System Bus Per-Channel Control (SBCn; n = 0 to 31)

100–11F—Transmit Per-Channel Control (TPCn; n = 0 to 31)

120–13F—Transmit Signaling Buffer (TSIGn; n = 0 to 31)

140–15F—Transmit PCM Slip Buffer (TSLIP_LOn; n = 0 to 31)

160–17F—Transmit PCM Slip Buffer (TSLIP_HIn; n = 0 to 31)

180–19F—Receive Per-Channel Control (RPCn; n = 0 to 31)

1A0–1BF—Receive Signaling Buffer (RSIGn; n = 0 to 31)

1C0–1DF—Receive PCM Slip Buffer (RSLIP_LOn; n = 0 to 31)

1E0–1FF—Receive PCM Slip Buffer (RSLIP_HIn; n = 0 to 31)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-112

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-102

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-102

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-104

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-107

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-108

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-108

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-109

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-109

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-110

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-110

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-110

. . . . . . . . . . . . . . . . . . 3-110

. . . . . . . . . . . . . . . . . . . 3-111

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-112

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-114

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-115

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-116

. . . . . . . . . . . . . . . . . . . . . . . . . 3-117

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-119

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-119

. . . . . . . . . . . . . . . . . . . . . . . . . . . 3-121

. . . . . . . . . . . . . . . . . . . . . . 3-123

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-123

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-126

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-127

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-127

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-128

. . . . . . . . . . . . . . . . . 3-128

. . . . . . . . . . . . . . . . . . . 3-129

. . . . . . . . . . . . . . . . . . . . . . 3-131

. . . . . . . . . . . . . . . . . . 3-132

. . . . . . . . . . . . . . . . . . . 3-132

. . . . . . . . . . . . . . . . . . . . 3-133

. . . . . . . . . . . . . . . . . . . . . . 3-134

. . . . . . . . . . . . . . . . . . 3-135

. . . . . . . . . . . . . . . . . . . 3-135

3.18 Register Summary

N8370DSE

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-136

Conexant

ix

Page 10

Table of Contents

Bt8370/8375/8376

4.0 Applications

4.1 External Component Specifications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 -1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

5.0 Electrical/Mechanical Specifications

5.1 Absolute Maximum Ratings

5.2 Recommended Operating Conditions

5.3 Electrical Characteristics

5.4 AC Characteristics

5.5 MPU Interface Timing

5.6 System Bus Interface (SBI) Timing

5.7 JTAG Interface Timing

5.8 Mechanical Specifications

Appendix A

A.1 Superframe Format (SF)

A.2 T1DM Format

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Fully Integrated T1/E1 Framer and Line Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

A.3 SLC 96 Format (SLC)

A.4 Extended Superframe Format (ESF)

A.5 E1 Frame Format

A.6 IRSM CEPT Frame Format

Appendix B

B.1 Applicable Standards

Appendix C

C.1 System Bus Compatibility

Appendix D

D.1 Notation and Acronyms

D.2 Acronyms and Abbreviations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

C.1.1 AT&T Concentration Highway Interface (CHI)

C.1.2 CHI Programming Options

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-1

D.1.1 Arithmetic Notation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-2

D.2.1 Revision History

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-5

x

Conexant

N8370DSE

Page 11

Bt8370/8375/8376

List of Figures

Fully Integrated T1/E1 Framer and Line Interface

List of Figures

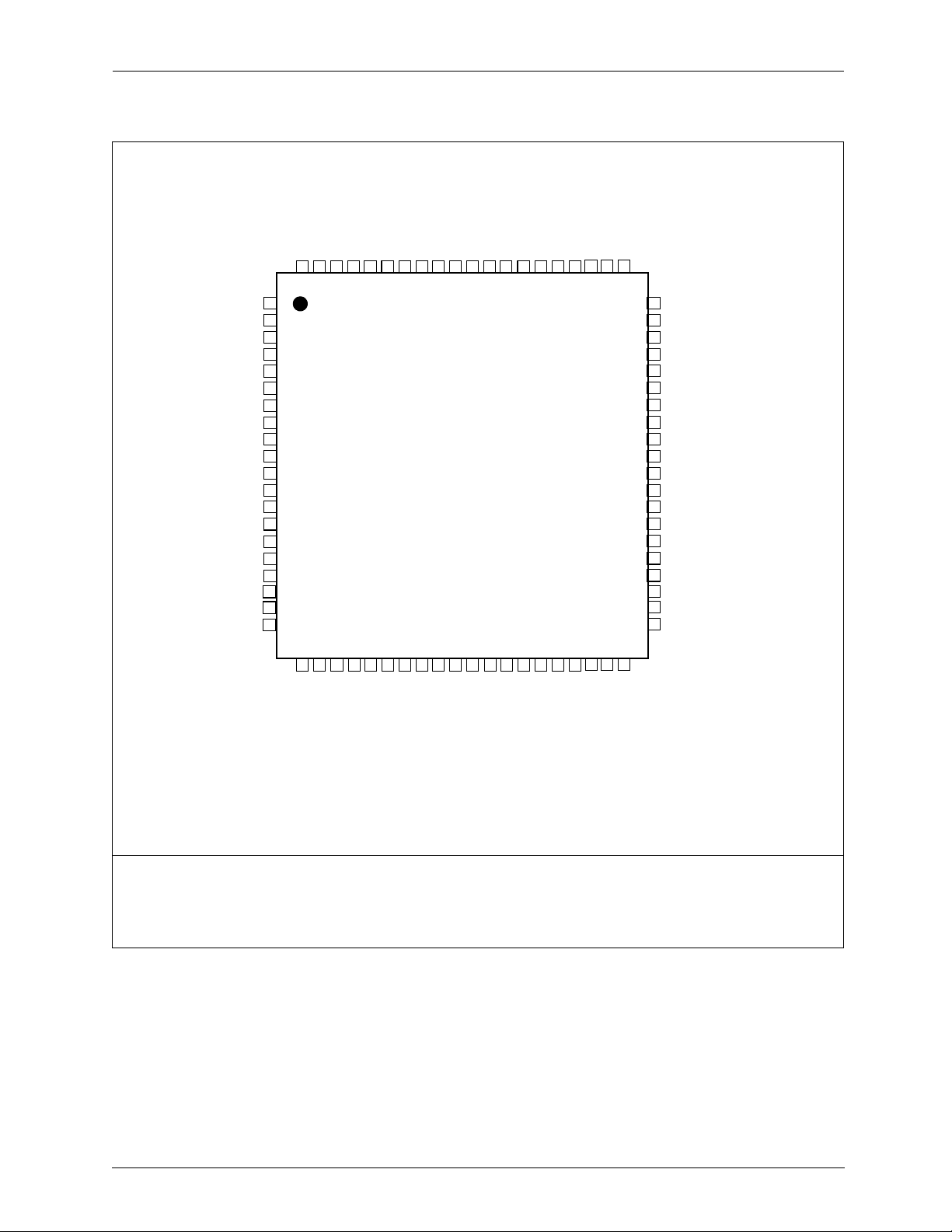

Figure 1-1. Bt8370/8375/8376 Pinout Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

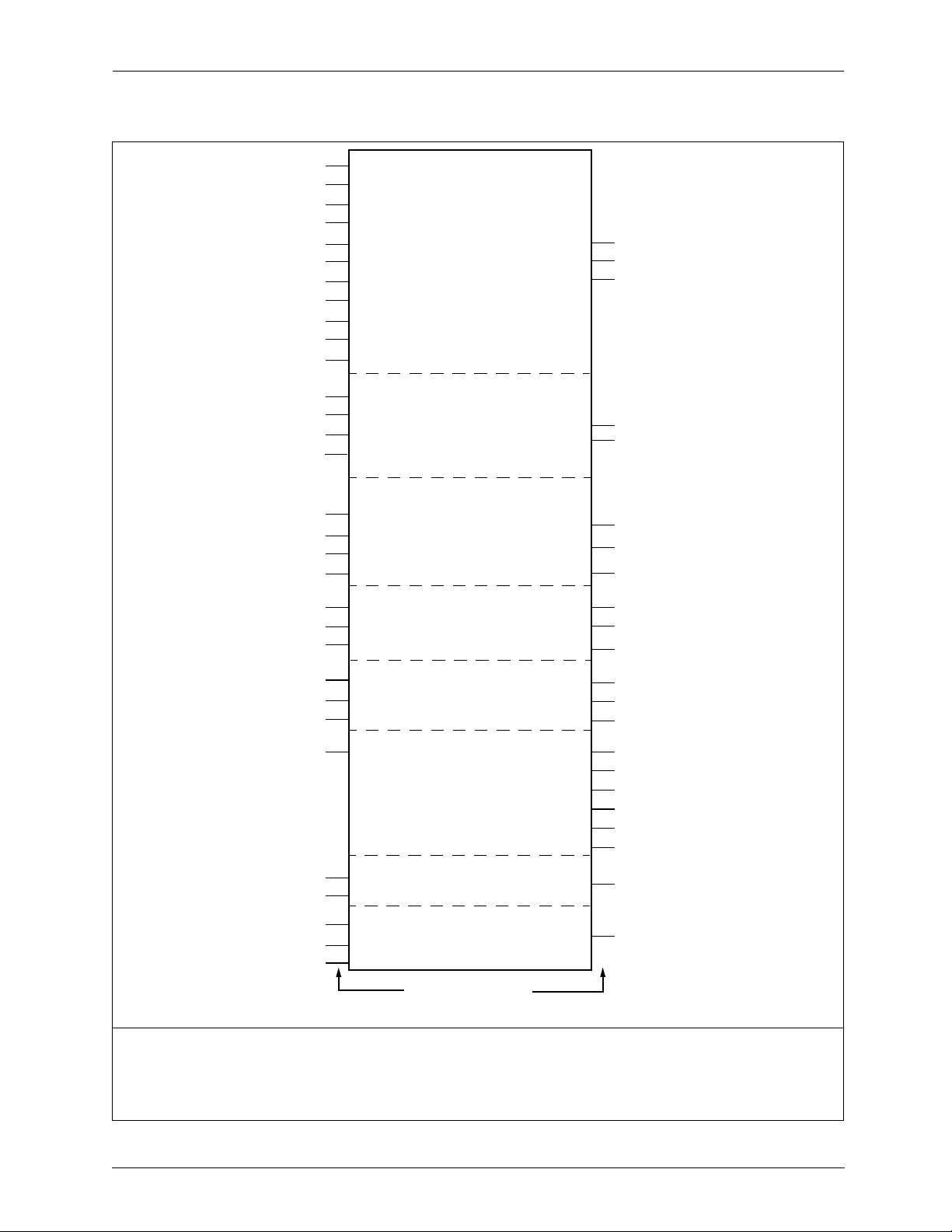

Figure 1-2. Bt8370/8375/8376 Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 2-1. Detailed Bt8370 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2. Detailed Bt8375 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Figure 2-3. Detailed Bt8376 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Figure 2-4. RLIU Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 2-5. RLIU Waveforms—Bipolar Input Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 2-6. RLIU Waveforms—P and N Rail Digital Input Signal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 2-7. Receive Input Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-8. Jitter Attenuator Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-9. CLAD/JAT Input Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Figure 2-10. CLAD/JAT Jitter Transfer Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

Figure 2-11. RCVR Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Figure 2-12. Receive External Data Link Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

Figure 2-13. Polled Receive Data Link Processing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-29

Figure 2-14. Interrupt Driven Receive Data Link Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

Figure 2-15. RSB Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

Figure 2-16. RSB 4.096 MHz Bus Mode Time Slot Interleaving. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Figure 2-17. RSB 8.192 MHz Bus Mode Time Slot Interleaving. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Figure 2-18. RSB Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

Figure 2-19. T1 Line to E1 System Bus Time Slot Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

Figure 2-20. G.802 Embedded Framing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

Figure 2-21. Clock Rate Adapter/Jitter Attenuator Block Diagram (Bt8370 and Bt8375 Devices) . . . . . 2-40

Figure 2-22. Clock Rate Adapter/Jitter Attenuator Block Diagram (Bt8376 Device Only). . . . . . . . . . . . 2-41

Figure 2-23. TSB Interface Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

Figure 2-24. Transmit System Bus Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

Figure 2-25. TSB 4.096 MHz Bus Mode Time Slot Interleaving. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

Figure 2-26. TSB 8.192 MHz Bus Mode Time Slot Interleaving. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

Figure 2-27. Transmit Framing and Timebase Alignment Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

Figure 2-28. XMTR Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-53

Figure 2-29. Transmit External Data Link Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

Figure 2-30. Polled Transmit Data Link Processing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-57

Figure 2-31. Interrupt Driven Transmit Data Link Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-58

Figure 2-32. Zero Code Substitution Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-66

Figure 2-33. TLIU Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-68

Figure 2-34. TLIU Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-69

Figure 2-35. Standard DS1 Pulse Template. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-70

Figure 2-36. T1 Pulse Template Test Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-70

Figure 2-37. Standard E1 (G.703) Pulse Template. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-71

N8370DSE

Conexant

xi

Page 12

List of Figures

Bt8370/8375/8376

Figure 2-38. E1 (G.703) Pulse Template Test Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-71

Figure 2-39. Digitized AMI Pulse Shape . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-74

Figure 2-40. TPLL Input Clock Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-76

Figure 2-41. 0 dB LBO Isolated Pulse Template. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-78

Figure 2-42. 7.5 dB LBO Isolated Pulse Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-78

Figure 2-43. 15.0 dB LBO Isolated Pulse Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-79

Figure 2-44. 22.5 dB LBO Isolated Pulse Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-79

Figure 2-45. External Termination Resistor Placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-80

Figure 2-46. Nominal Return Loss. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-81

Figure 2-47. Output Pulse Height versus Transmit Termination Impedance . . . . . . . . . . . . . . . . . . . . . 2-82

Figure 2-48. Microprocessor Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-83

Figure 2-49. JTAG Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-88

Figure 3-1. Receive Equalizer Eye Pattern Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-45

Figure 4-1. Option A: Long Haul Application with Ground Reference on the Line Side . . . . . . . . . . . . . 4-3

Figure 4-2. Option B: Long Haul with No Ground Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Figure 4-3. Option C: Long Haul Application with No Ground Reference on the Line . . . . . . . . . . . . . . 4-7

Figure 4-4. Option D: Short Haul Interface Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Figure 5-1. Minimum Clock Pulse Widths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Figure 5-2. Input Data Setup/Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Figure 5-3. Output Data Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Figure 5-4. 1-Second Input/Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Figure 5-5. SBI Timing: Setup and Hold Time for RFSYNC/RMSYNC and

TFSYNC/TMSYNC Input Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Figure 5-6. Motorola Asynchronous Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Figure 5-7. Motorola Asynchronous Write Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Figure 5-8. Intel Asynchronous Read Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

Figure 5-9. Intel Asynchronous Write Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-12

Figure 5-10. Motorola Synchronous Read Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Figure 5-11. Motorola Synchronous Write Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

Figure 5-12. Intel Synchronous Read Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

Figure 5-13. Intel Synchronous Write Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

Figure 5-14. SBI Timing - 1536K Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

Figure 5-15. SBI Timing—1544K Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

Figure 5-16. SBI Timing—2048K Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

Figure 5-17. SBI Timing—4096K Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

Figure 5-18. SBI Timing—8192K Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

Figure 5-19. SBI Timing—Eight Clock Edge Combinations (Applicable to Any SBI Mode) . . . . . . . . . . 5-22

Figure 5-20. JTAG Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

Figure 5-21. 80-Pin Metric Quad Flat Pack (MQFP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

Figure A-1. T1 Superframe PCM Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Figure A-2. T1 Extended Superframe PCM Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Figure A-3. E1 Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

Fully Integrated T1/E1 Framer and Line Interface

xii

Conexant

N8370DSE

Page 13

Bt8370/8375/8376

List of Tables

Fully Integrated T1/E1 Framer and Line Interface

List of Tables

Table 1-1. Hardware Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Table 2-1. CLAD/JAT Jitter Transfer Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

Table 2-2. Receive Framer Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

Table 2-3. Criteria for Loss/Recovery of Receive Framer Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

Table 2-4. Commonly Used Data Link Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

Table 2-5. RSB Interface Time Slot Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-34

Table 2-6. JCLK/CLADO Timing Reference. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-42

Table 2-7. Jitter Generation Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-42

Table 2-8. CLADO Frequencies Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

Table 2-9. Common CLADI Reference Frequencies and CLAD Configuration Examples. . . . . . . . . . . . 2-44

Table 2-10. Commonly Used Data Link Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-55

Table 2-11. Yellow Alarm Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-61

Table 2-12. Yellow Alarm Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-61

Table 2-13. Multiframe Yellow Alarm Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-62

Table 2-14. Multiframe Yellow Alarm Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-62

Table 2-15. ANSI T1.102, 1993–DS1 Pulse Template Corner Points, Maximum Curve . . . . . . . . . . . . . 2-72

Table 2-16. ANSI T1.102, 1993–DS1 Pulse Template Corner Points, Minimum Curve . . . . . . . . . . . . . 2-72

Table 2-17. ANSI T1.403, 1995–DS1 Pulse Template Corner Points, Maximum Curve . . . . . . . . . . . . . 2-72

Table 2-18. ANSI T1.403, 1995–DS1 Pulse Template Corner Points, Minimum Curve . . . . . . . . . . . . . 2-72

Table 2-19. G.703, 1988–DS1 Pulse Template Corner Points, Maximum Curve . . . . . . . . . . . . . . . . . . 2-72

Table 2-20. G.703, 1988–DS1 Pulse Template Corner Points, Minimum Curve. . . . . . . . . . . . . . . . . . . 2-73

Table 2-21. G.703, 1988–Pulse Template Corner Points, Maximum Curve . . . . . . . . . . . . . . . . . . . . . . 2-73

Table 2-22. G.703, 1988–Pulse Template Corner Points, Minimum Curve. . . . . . . . . . . . . . . . . . . . . . . 2-73

Table 2-23. Transmit Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-75

Table 2-24. Microprocessor Interface Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-84

Table 2-25. JTAG Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-88

Table 2-26. Bt8370/8375/8376 Device Identification JTAG Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-89

Table 2-27. Bt8375 Device Identification JTAG Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-89

Table 2-28. Bt8376 Device Identification JTAG Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-89

Table 3-1. Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Table 3-2. Receive Framer Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Table 3-3. Interrupt Status Register Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-15

Table 3-4. Counter Overflow Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

Table 3-5. Maximum Average Reframe Time (MART) and Framer Timeout. . . . . . . . . . . . . . . . . . . . . 3-30

Table 3-6. System Bus Sync Mode Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-33

Table 3-7. Common TFSYNC and TMSYNC Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-34

Table 3-8. Common RFSYNC and RMSYNC Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-34

Table 3-9. Receive LIU Register Settings versus Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-38

Table 3-10. VGA Maximum Settings for Receive Sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-42

N8370DSE

Conexant

xiii

Page 14

List of Tables

Bt8370/8375/8376

Table 3-11. Receive PRBS Test Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-49

Table 3-12. Receive Yellow Alarm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-53

Table 3-13. Receive Yellow Alarm Set/Clear Criteria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-54

Table 3-14. Return Loss Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-65

Table 3-15. E1 Transmit Framer Modes (T1/E1N = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-68

Table 3-16. T1 Transmit Framer Modes (T1/E1N = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-68

Table 3-17. Criteria for E1 Loss/Recovery of Transmit Frame Alignment. . . . . . . . . . . . . . . . . . . . . . . . 3-69

Table 3-18. Criteria for T1 Loss/Recovery of Transmit Frame Alignment. . . . . . . . . . . . . . . . . . . . . . . . 3-70

Table 3-19. Transmit Framer Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-71

Table 3-20. Transmit Zero Code Suppression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-72

Table 3-21. Transmit PRBS Test Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-78

Table 3-22. (Datalink Configuration Register Description). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-87

Table 3-23. Remote DS0 Channel Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-130

Table 3-24. Global Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-136

Table 3-25. Interrupt Request Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-136

Table 3-26. Interrupt Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-137

Table 3-27. Interrupt Enable Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-137

Table 3-28. Primary Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-138

Table 3-29. Receive LIU Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-138

Table 3-30. Receiver Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-139

Table 3-31. Performance Monitoring Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-140

Table 3-32. Receive Sa-Byte Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-140

Table 3-33. Transmit LIU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-141

Table 3-34. Transmitter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-141

Table 3-35. Transmit Sa-Byte Buffers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-141

Table 3-36. CLAD Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-142

Table 3-37. Bit-Oriented Protocol Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-142

Table 3-38. Data Link Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-142

Table 3-39. System Bus Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-144

Table 4-1. Transformer Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-2. REFCKI (10 MHz) Crystal Oscillator Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Table 5-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Table 5-2. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-3. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-4. Line Interface Unit (RLIU, TLIU) Performance Characteristics . . . . . . . . . . . . . . . . . . . . . . . 5-3

Table 5-5. Input Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Table 5-6. Input Data Setup and Hold Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Table 5-7. Output Data Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Table 5-8. 1-Second Input/Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Table 5-9. Motorola Asynchronous Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Table 5-10. Motorola Asynchronous Write Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Table 5-11. Intel Asynchronous Read Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Table 5-12. Intel Asynchronous Write Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Table 5-13. Motorola Synchronous Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Table 5-14. Motorola Synchronous Write Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

Table 5-15. Intel Synchronous Read Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

Fully Integrated T1/E1 Framer and Line Interface

xiv

Conexant

N8370DSE

Page 15

Bt8370/8375/8376

List of Tables

Fully Integrated T1/E1 Framer and Line Interface

Table 5-16. Intel Synchronous Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

Table 5-17. Test and Diagnostic Interface Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

Table 5-18. Test and Diagnostic Interface Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

Table A-1. Superframe Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Table A-2. T1DM Frame Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Table A-3. SLC-96 Fs Bit Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Table A-4. Extended Superframe Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

Table A-5. Performance Report Message Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

Table A-6. ITU–T CEPT Frame Format Time Slot 0-Bit Allocations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-9

Table A-7. IRSM CEPT Frame Format Time Slot 0-Bit Allocations . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-10

Table A-8. CEPT (ITU–T and IRSM) Frame Format Time Slot 16-Bit Allocations . . . . . . . . . . . . . . . . . A-11

Table B-1. Applicable Standards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

N8370DSE

Conexant

xv

Page 16

List of Tables

Bt8370/8375/8376

Fully Integrated T1/E1 Framer and Line Interface

xvi

Conexant

N8370DSE

Page 17

Bt8370/8375/8376

1.0 Pin Descriptions

Fully Integrated T1/E1 Framer and Line Interface

1

1.0 Pin Descriptions

1.1 Pin Assignments

Bt8370/8375/8376 is packaged in an 80-pin Metric Quad Flat Pack (MQFP). A

pinout diagram of this device is illustrated in Figure 1-1. Figure 1-2 details a

Bt8370/8375/8376 logic diagram. Pin labels, names, I/O functions, and

descriptions are provided in Table 1-1.

The input pins listed below contain an internal pullup resistor (>50 kΩ) and

can remain unconnected if the active-high input state is desired. All other unused

input pins should be either pulled up or grounded.

1 A[7:0] Address lines unused in INTEL bus mode

2 XOE Active-high enables analog bipolar output

3 MOTO* Pullup selects INTEL bus mode if unconnected

1.1 Pin Assignments

4 SYNCMD Pullup selects synchronous processor interface

5 RCKI Receive clock unused if analog inputs enabled

6 TDI Unused if JTAG not connected

7 TMS Disables JTAG if not connected

8 TCK Unused if JTAG not connected

9 RST* Disables hardware reset if not connected

10 TDLI Unused if no external data link

11 TSIGI Unused if signaling data not supported by system

bus

N8370DSE

Conexant

1-1

Page 18

1.0 Pin Descriptions

Bt8370/8375/8376

1.1 Pin Assignments

Figure 1-1. Bt8370/8375/8376 Pinout Diagram

SIGFRZ

XOE

MOTO*

DTACK*

RCKI

80797877767574737271706968676665646362

SYNCMD

CS*

INTR*

DS* (RD*)

AS* (ALE)

R/W*(WR*)

VDD[0]

GND[0]

A[0]

AD[0]

A[1]

AD[1]

A[2]

AD[2]

A[3]

AD[3]

A[4]

AD[4]

A[5]

AD[5]

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

2122232425262728293031323334353637

GND[6]

RRING

RTIP

VDD[6]

RNEGI

RPOSI

VDD[5]

Bt8370/8375/8376

80-Pin MQFP

Fully Integrated T1/E1 Framer and Line Interface

(3)

TCKI

TCKO

GND[5]

GND[4]

38

39

VSET

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

VDD[4]

VDD[3]

XTIP

XRING

GND[3]

TDI

TDO

TCK

TMS

ACKI

VDD[2]

GND[2]

RCKO

RPOSO/RDLO

RNEGO/RDLCKO

RSBCKI

RMSYNC

RFSYNC

RPCMO

TPOSI/TDLI

REFCKI

CLADI

CLADO (NC)

A[6]

A[7]

AD[6]

A[8]

AD[7]

RST*

MCLK

VDD[1]

CLKMD

TPOSO/TNRZO/TINDO

GND[1]

ONESEC

TSIGI

TPCMI

TFSYNC

TMSYNC

NOTE(S):

1. Default pin assignments listed first for pins with multiple modes.

2. Motorola-style processor pin names listed first with Intel pins in parentheses.

3. Pin 66 is not connected for the Bt8376 device.

TSBCKI

TNEGI/TDLCKO

TNEGO/MSYNCO/RINDO

RSIGO

1-2

Conexant

N8370DSE

Page 19

Bt8370/8375/8376

1.0 Pin Descriptions

Fully Integrated T1/E1 Framer and Line Interface

Figure 1-2. Bt8370/8375/8376 Logic Diagram

28

RST*

I/O

I/O

PIO

I

29

I

78

I

I

26

I

(1)

I

(1)

I

I

I

I

79

I

73

I

74

I

61

65

I

51

I

41

I

38

76

I

70

I

71

I

MCLK

MOTO*

1

SYNCMD

CLKMD

A[8:0]

AD[7:0]

5

AS* (ALE)

2

CS*

4

DS* (RD*)

6

R/W*(WR*)

XOE

RTIP

RRING

VSET

TCKI

ACKI

TPOSI/TDLI

TNEGI/TDLCKO

RCKI

RPOSI

RNEGI

Receive, Transmit

Hardware Reset

Processor Clock

Motorola Bus mode

Sync Bus mode

Clock mode

Address Bus

Data Bus or Address/Data

Address Strobe

Chip Select

Read or Data Strobe

Write Strobe or Read/Write

Transmit Output Enable

Receive Tip

Receive Ring

Voltage Reference Set

Tx Clock In

All Ones Clock

Tx Positive In/TDL Data In

Tx Negative In/TDL Clock

Rx Clock In

Rx Positive In

Rx Negative In

Microprocessor

Interface

(MPU)

Line Interface

(RLIU, TLIU)

Digital

Transmitter

(XMTR)

TNEGO/MSYNCO

Digital

Receiver

(RCVR)

RNEGO/RDLCKO

ONESEC

INTR*

DTACK*

XTIP

XRING

TCKO

TPOSO/TNRZO

RCKO

RPOSO/RDLO

1.1 Pin Assignments

PIO

32

3

77

58

57

64

27

39

48

47

46

1-second Timer

O

Interrupt Request

O

Data Transfer Acknowledge

O

Transmit Tip

O

Transmit Ring

Tx Clock Output

O

O

Tx Positive Out/Tx NRZ Data

Tx Negative Out/

O

Tx Multiframe Sync

O

Rx Clock Out

O

Rx Positive Out/RDL Data Out

O

Rx Negative Out/RDL Clock Out

(2)

(2)

37

TSBCKI

TSB Clock

TSB Data

TSB Signaling

RSB Clock

I

34

TPCMI

I

33

TSIGI

I

45

RSBCKI

I

Transmit

System Bus

(TSB)

TFSYNC

TMSYNC

RPCMO

Receive

System Bus

(RSB)

CLADI

CLAD In

Reference Clock

Test Clock I

Test Mode Select I

Test Data In I

NOTE(S):

(1)

Refer to Figure 1-1

(2)

Pins 27 and 39 shown twice for clarity; pin function controlled by PIO (addr 018).

(3)

Pin 66 is not connected for the Bt8376 device.

Bt8370/8375/8376 Pinout Diagram

67

I

REFCKI

68

I

TCK

53

52

TMS

55

TDI

Clock Rate

Adapter (CLAD)

Boundary Scan

(JTAG)

I = Input, O = Output,

PIO = Programmable I/O; controls located at PIO (address 018)

.

RFSYNC

RMSYNC

SIGFRZ

CLADO

TINDO

RSIGO