Page 1

A

Fast Ethernet MAC Controlle

r

A

S

I

X

ASIX AX88140A

100BASE-TX/FX PCI Bus

AX88140

Fast Ethernet MAC Controller

Data Sheet(11/03/’97)

DOCUMENT NO. : AX140D2.DOC

This data sheets contain new products information. ASIX ELECTRONICS reserves the rights to modify the products

specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent

accompany the sale of the product.

ASIX ELECTRONICS CORPORATION

2F, NO.13, Industry East Rd. II, Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C.

TEL: 886-3-579-9500 FAX: 886-3-579-9558

Page 2

AX88140A PRELIMINARY

CONTENTS

1.0 INTRODUCTION ................................................................................................................................................ 6

1.1 GENERAL DESCRIPTION:...................................................................................................................................... 6

1.2 FEATURES............................................................................................................................................................ 7

1.3 BLOCK DIAGRAM: ............................................................................................................................................... 8

1.4 AX88140AQ PIN CONNECTION DIAGRAM FOR 160-PIN...................................................................................... 9

1.5 AX88140AP PIN CONNECTION DIAGRAM FOR 144-PIN .................................................................................... 10

2.0 SIGNAL DESCRIPTION .................................................................................................................................. 11

2.1 SIGNAL DESCRIPTIONS FOR 160-PIN AND 144-PIN.............................................................................................. 11

2.2 PCI INTERFACE GROUP ...................................................................................................................................... 12

2.3 BOOT ROM , SERIAL ROM , GENERAL-PURPOSE SIGNALS GROUP.................................................................... 14

2.4 MII/SYM/SRL INTERFACE SIGNALS GROUP ...................................................................................................... 14

2.5 EXTENDED , NC, POWER PINS GROUP................................................................................................................ 16

3.0 CONFIGURATION OPERATION .................................................................................................................. 17

3.1 CONFIGURATION SPACE MAPPING..................................................................................................................... 17

3.2 CONFIGURATION SPACE..................................................................................................................................... 18

3.2.1 Configuration ID Register (CSID)............................................................................................................ 18

3.2.2 Command and Status Configuration Register (CSCS)............................................................................... 18

3.2.3 Configuration Revision Register (CSRV).................................................................................................. 18

3.2.4 Configuration Latency Timer Register (CSLT)......................................................................................... 18

3.2.5 Configuration Base I/O Address Register (CBIO).................................................................................... 19

3.2.6 Configuration Base Memory Address Register (CBMA) .......................................................................... 19

3.2.7 Expansion ROM Base Address Register (CBER)...................................................................................... 19

3.2.8 Configuration Interrupt Register (CSIT) .................................................................................................. 19

4.0 REGISTERS OPERATION .............................................................................................................................. 20

4.1 REGISTERS MAPPING ......................................................................................................................................... 20

4.2 HOST REGS....................................................................................................................................................... 21

4.2.1 Bus Mode Register (REG0)........................................................................................................................ 21

4.2.2 Transmit Poll Demand (REG1).................................................................................................................21

4.2.3 Receive Poll Demand (REG2)................................................................................................................... 22

4.2.4 Receive List Base Address (REG3)........................................................................................................... 22

4.2.5 Transmit List Base Address (REG4)......................................................................................................... 22

4.2.6 Status Register (REG5)............................................................................................................................. 23

4.2.7 Operation Mode Register (REG6) ............................................................................................................ 24

4.2.8 Interrupt Enable Register (REG7)............................................................................................................ 26

4.2.9 Missed Frame and Overflow Counter (REG8) ........................................................................................ 26

4.2.10 Serial ROM and MII Management Register (REG9).............................................................................. 27

4.2.11 General-Purpose Timer (REG11)........................................................................................................... 27

4.2.12 General-Purpose Port Register (REG12)............................................................................................... 28

4.2.13 Filtering Index (REG13)......................................................................................................................... 28

4.2.14 Filtering data (REG14)........................................................................................................................... 28

5.0 HOST COMMUNICATION.............................................................................................................................. 30

5.1 DESCRIPTOR LISTS AND DATA BUFFERS............................................................................................................ 30

5.2 RECEIVE DESCRIPTORS...................................................................................................................................... 31

5.2.1 Receive Descriptor 0 (RDES0) .................................................................................................................. 31

5.2.2 Receive Descriptor 1 (RDES1) .................................................................................................................. 32

5.2.3 Receive Descriptor 2 (RDES2) .................................................................................................................. 32

5.2.4 Receive Descriptor 3 (RDES3) .................................................................................................................. 32

5.3 TRANSMIT DESCRIPTORS ................................................................................................................................... 33

5.3.1 Transmit Descriptor 0 (TDES0)................................................................................................................. 33

5.3.2 Transmit Descriptor 1 (TDES1)................................................................................................................. 34

5.3.3 Transmit Descriptor 2 (TDES2)................................................................................................................. 34

5.3.4 Transmit Descriptor 3 (TDES3)................................................................................................................. 34

2

ASIX ELECTRONICS CORPORATION

Page 3

AX88140A PRELIMINARY

6.0 ELECTRICAL SPECIFICATION AND TIMINGS...................................................................................... 35

6.1 ABSOLUTE MAXIMUM RATINGS ........................................................................................................................ 35

6.2 GENERAL OPERATION CONDITIONS ................................................................................................................... 35

6.3 DC CHARACTERISTICS ...................................................................................................................................... 35

6.4 A.C. TIMING CHARACTERISTICS........................................................................................................................ 36

6.4.1 PCI CLOCK.............................................................................................................................................. 36

6.4.2 PCI Timings............................................................................................................................................... 36

6.4.3 Reset Timing .............................................................................................................................................. 36

6.4.4 MII/SYM Timing ........................................................................................................................................ 37

6.4.5 10Mbps serial timing ................................................................................................................................. 38

6.4.6 Boot ROM Read Cycles ............................................................................................................................. 39

7.0 PACKAGE INFORMATION............................................................................................................................ 40

APPENDIX A H/W NOTE .................................................................................................................................... 41

A.1 BOOT ROM READ CYCLE.................................................................................................................................. 41

A.2 POWER SUPPLY................................................................................................................................................. 42

A.3 BOUNDARY SCAN TEST PINS ............................................................................................................................ 42

APPENDIX B FUNCTION APPLICATION...................................................................................................... 43

B.1 APPLICATION FOR PCI INTERFACE.................................................................................................................... 43

B.2 APPLICATION FOR BOOT ROM INTERFACE ....................................................................................................... 44

B.3 APPLICATION FOR SERIAL ROM INTERFACE..................................................................................................... 44

B.4 APPLICATION FOR PHY INTERFACE.................................................................................................................. 45

B.4.1 AX88140A, QSI6611, & MTD213 Application ......................................................................................... 45

B.4.2 Application for MII Mode : LEVEL ONE LXT970.................................................................................... 45

B.4.3 Application for MII Mode : MYSON MTD972 + MTD971....................................................................... 46

B.4.4 Application for MII Mode : DAVICOM DM9101 ..................................................................................... 46

3

ASIX ELECTRONICS CORPORATION

Page 4

AX88140A PRELIMINARY

FIGURES

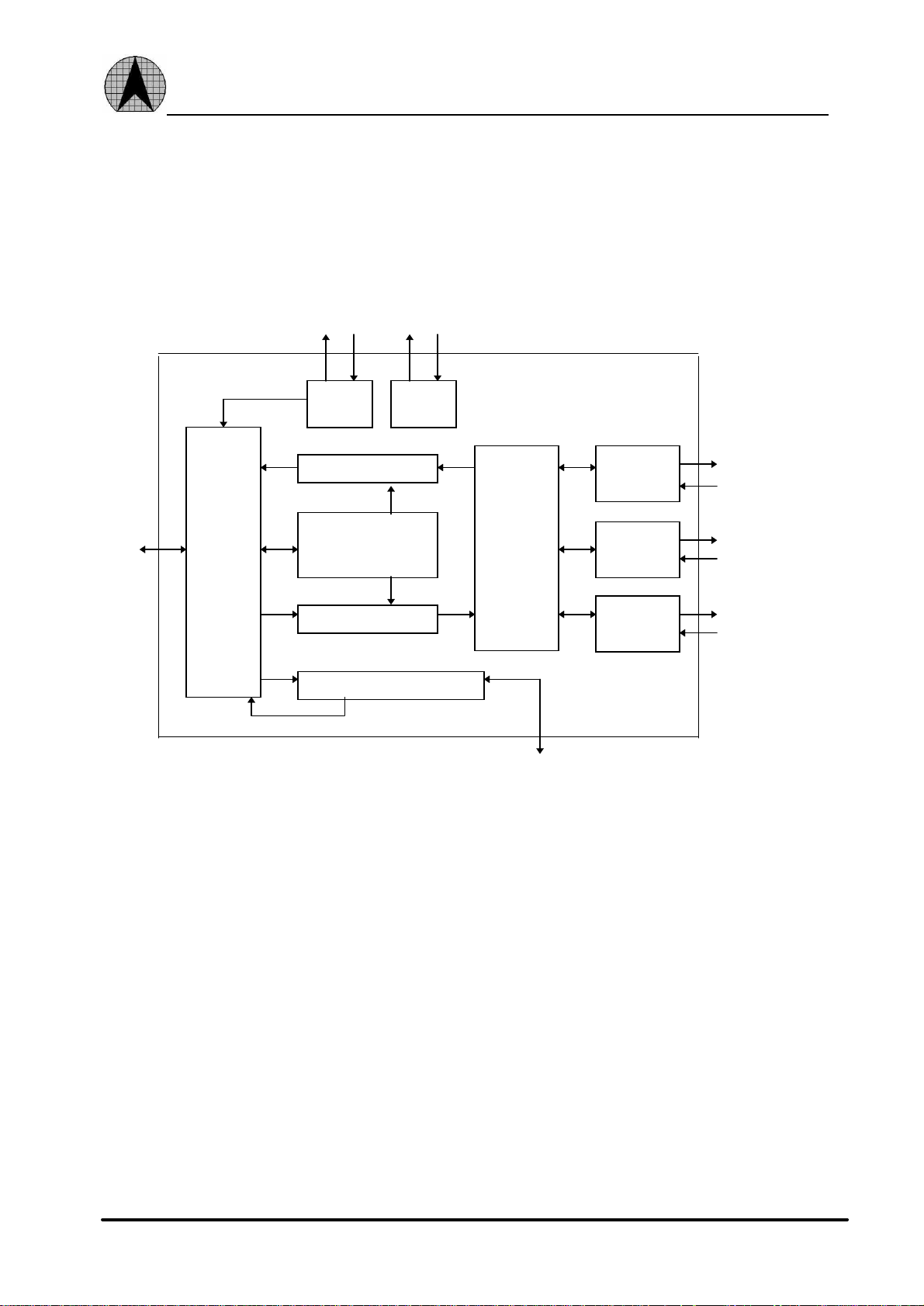

FIG - 1 AX88140A BLOCK DIAGRAM ........................................................................................................................... 8

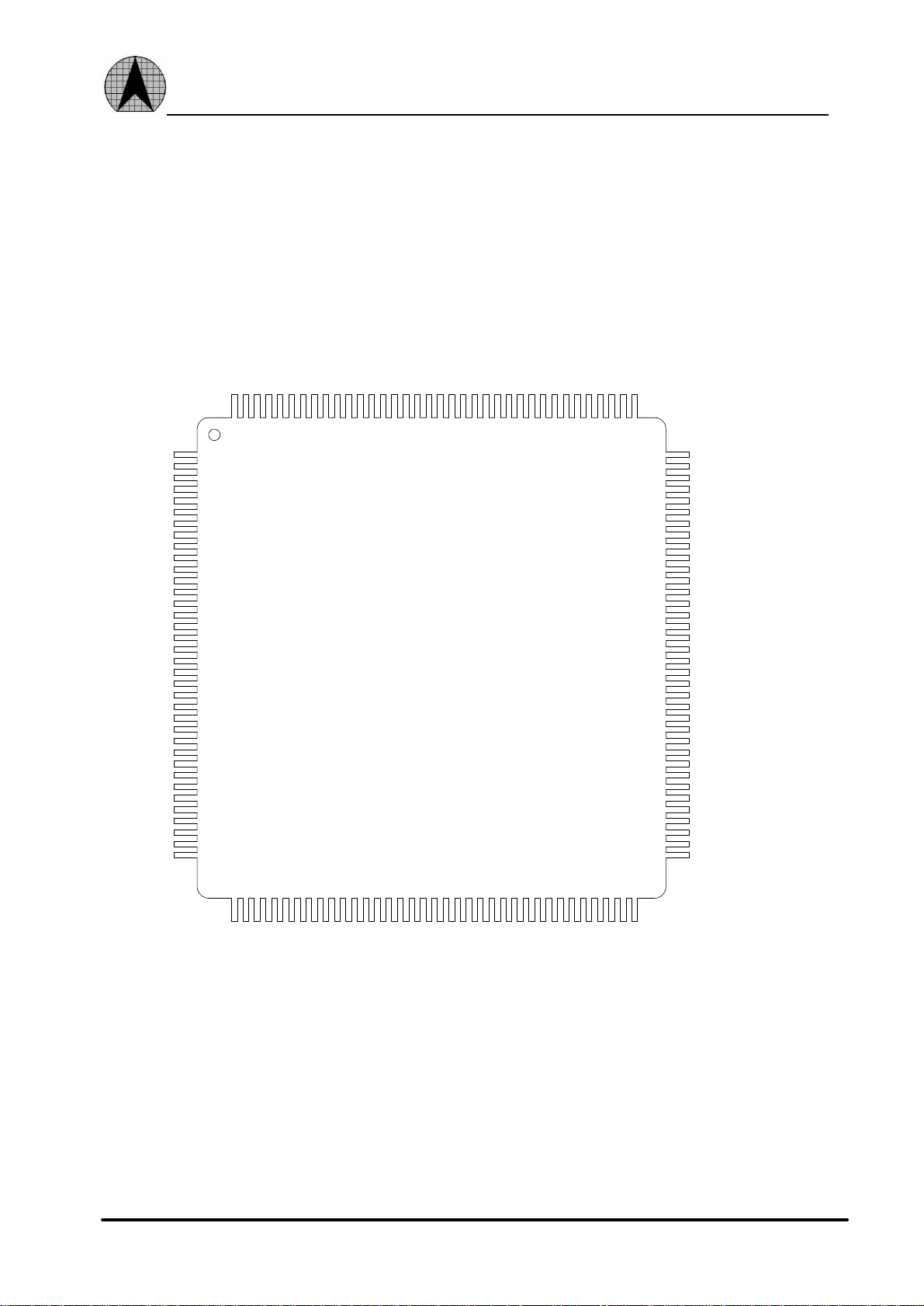

FIG - 2 AX88140AQ PIN CONNECTION DIAGRAM FOR 160-PIN ..................................................................................... 9

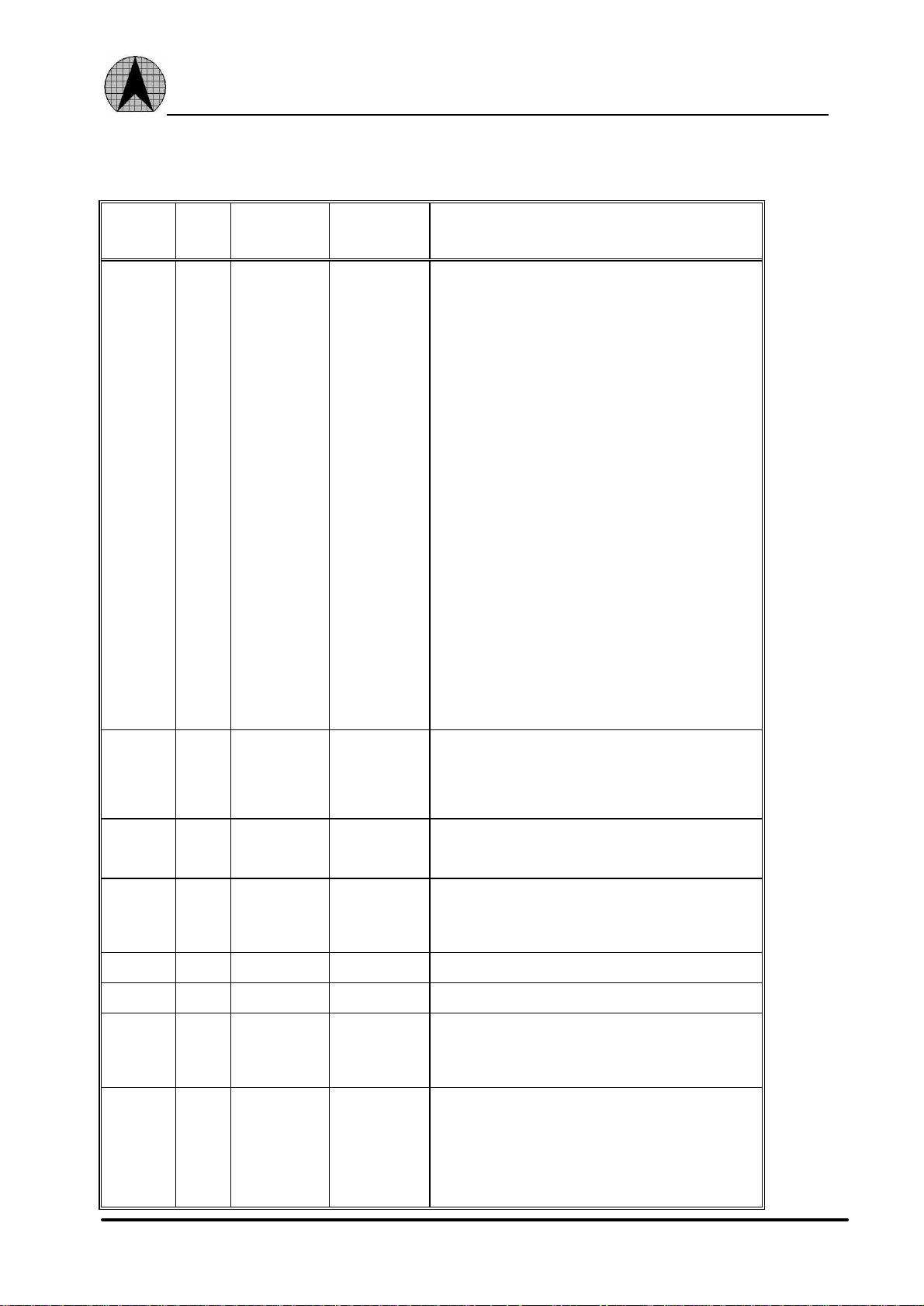

FIG - 3 AX88140AP PIN CONNECTION DIAGRAM FOR 144-PIN.................................................................................... 10

FIG - 4 DESCRIPTOR STRUCTURE EXAMPLE................................................................................................................. 30

FIG - 5 RECEIVE DESCRIPTOR FORMAT........................................................................................................................ 31

FIG - 6 TRANSMIT DESCRIPTOR FORMAT..................................................................................................................... 33

FIG - 7 APPLICATION FOR PCS / SERIAL MODE ........................................................................................................... 45

FIG - 8 APPLICATION FOR MII MODE WITH LXT970................................................................................................... 45

FIG - 9 APPLICATION FOR MII MODE WITH MDT972 + MTD971............................................................................... 46

FIG - 10 APPLICATION FOR MII MODE WITH DM9101................................................................................................ 46

4

ASIX ELECTRONICS CORPORATION

Page 5

AX88140A PRELIMINARY

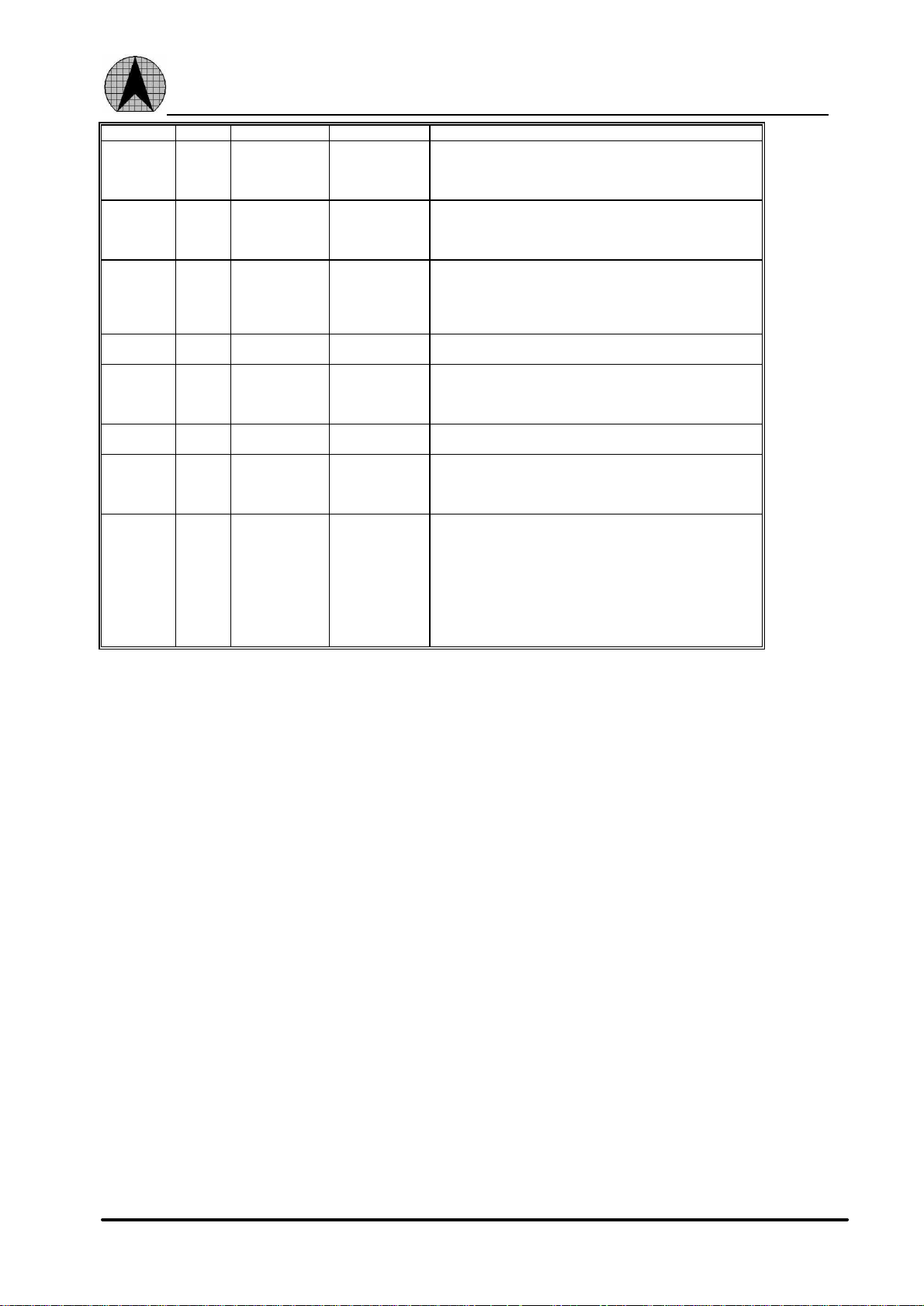

TABLES

TAB - 1 PCI INTERFACE GROUP ................................................................................................................................... 13

TAB - 2 BOOT ROM , SERIAL ROM , GENERAL-PURPOSE SIGNALS GROUP................................................................. 14

TAB - 3 MII/SYM/SRL INTERFACE SIGNALS GROUP................................................................................................... 15

TAB - 4 EXTENDED , NC, POWER PINS GROUP ............................................................................................................. 16

TAB - 5 CONFIGURATION SPACE MAPPING .................................................................................................................. 17

TAB - 6 CSID CONFIGURATION ID REGISTER DESCRIPTION ....................................................................................... 18

TAB - 7 CSCS COMMAND AND STATUS CONFIGURATION REGISTER........................................................................... 18

TAB - 8 CSRV CONFIGURATION REVISION REGISTER DESCRIPTION ........................................................................... 18

TAB - 9 CSLT CONFIGURATION ID REGISTER DESCRIPTION ...................................................................................... 18

TAB - 10 CBIO CONFIGURATION BASE I/O ADDRESS REGISTER DESCRIPTION .......................................................... 19

TAB - 11 CBMA CONFIGURATION BASE MEMORY ADDRESS REGISTER DESCRIPTION............................................... 19

TAB - 12 CBER EXPANSION ROM BASE ADDRESS REGISTER DESCRIPTION .............................................................. 19

TAB - 13 CSIT CONFIGURATION INTERRUPT REGISTER DESCRIPTION ........................................................................ 19

TAB - 14 COMMAND AND STATUS REGISTER MAPPING............................................................................................... 20

TAB - 15 REG0 BUS MODE REGISTER DESCRIPTION................................................................................................... 21

TAB - 16 REG1 TRANSMIT POLL DEMAND REGISTER DESCRIPTION........................................................................... 21

TAB - 17 REG2 RECEIVE POLL DEMAND REGISTER DESCRIPTION.............................................................................. 22

TAB - 18 REG3 RECEIVE LIST BASE ADDRESS REGISTER DESCRIPTION..................................................................... 22

TAB - 19 REG4 TRANSMIT LIST BASE ADDRESS REGISTER DESCRIPTION .................................................................. 22

TAB - 20 REG5 STATUS REGISTER DESCRIPTION........................................................................................................ 24

TAB - 21 REG6 OPERATION MODE REGISTER DESCRIPTION....................................................................................... 25

TAB - 22 PORT AND DATA RATE SELECTION............................................................................................................... 25

TAB - 23 REG7 INTERRUPT ENABLE REGISTER DESCRIPTION..................................................................................... 26

TAB - 24 REG8 MISSED FRAME AND OVERFLOW COUNTER DESCRIPTION ................................................................. 26

TAB - 25 REG9 SERIAL ROM, AND MII MANAGEMENT REGISTER DESCRIPTION ..................................................... 27

TAB - 26 REG11 GENERAL-PURPOSE TIMER REGISTER DESCRIPTION........................................................................ 28

TAB - 27 REG12 GENERAL-PURPOSE PORT REGISTER DESCRIPTION.......................................................................... 28

TAB - 28 REG13 FILTERING INDEX REGISTER DESCRIPTION ...................................................................................... 28

TAB - 29 REG14 FILTERING DATA REGISTER DESCRIPTION ....................................................................................... 28

TAB - 30 DESCRIPTION OF FILTERING BUFFER ............................................................................................................ 28

TAB - 31 LAYOUT OF FILTERING BUFFER.................................................................................................................... 29

TAB - 32 RECEIVE DESCRIPTOR 0................................................................................................................................ 32

TAB - 33 RECEIVE DESCRIPTOR 1................................................................................................................................ 32

TAB - 34 RECEIVE DESCRIPTOR 2................................................................................................................................ 32

TAB - 35 RECEIVE DESCRIPTOR 3................................................................................................................................ 32

TAB - 36 TRANSMIT DESCRIPTOR 0 ............................................................................................................................. 34

TAB - 37 TRANSMIT DESCRIPTOR 1 ............................................................................................................................. 34

TAB - 38 TRANSMIT DESCRIPTOR 2 ............................................................................................................................. 34

TAB - 39 TRANSMIT DESCRIPTOR 3 ............................................................................................................................. 34

5

ASIX ELECTRONICS CORPORATION

Page 6

AX88140A PRELIMINARY

1.0 Introduction

1.1 General Description:

l The AX88140A Fast Ethernet Controller is a high performance and highly integrated PCI Bus Ethernet

Controller chip.

l The AX88140A is cost effective, high performance solution for PCI add-in adapters, PC

motherboards, or bridge/hub applications.

l It implements both 10Mbps and 100Mbps Ethernet function based on IEEE802.3 LAN standard.

l The AX88140A contains a high speed 32 bit PCI Bus master interface to host CPU. Two large

independent transmit and receive FIFO allow the AX88140A to buffer the Ethernet packet efficiently.

l The 10/100Mbps ports can be programmedto support 10Mbps, 100Mbps media-independent interface

(MII), or 100BASE-TX physical coding sub-layer (PCS)mode, For 10Mbps operation AX88140A

provides a standard serial Interface to the external 10Mbps ENDEC chip.

6

ASIX ELECTRONICS CORPORATION

Page 7

AX88140A PRELIMINARY

1.2 Features

l Single chip PCI bus Fast Ethernet Controller.

l Direct interface to PCI bus.

l Support both 10Mbps and 100Mbps data rate.

l Full or Half duplex operation supported for both10Mbps and 100Mbps operation.

l Provides a MII port for both 10/100Mbps operation.

l On chip PCS support for 100BASE-TX symbol mode operation.

l On chip external 10Mbps ENDEC Interface.

l Support 21MHz to 33MHz no wait state PCI Bus Interface.

l Two large Independent FIFO for transmit and receive. no additional On board buffer memory required.

l Interface to serial ROM for Ethernet ID address and jumper-less board design.

l 256KB boot ROM support.

l On chip general purpose, programmable register and I/O pins.

l Unlimited PCI burst.

l external and internal loop-back capability.

l Support early interrupts on transmit.

l Powerful on chip buffer management DMA. And PCI Bus master operation reduce CPU utilization.

l Big and little endian byte ordering supported.

l IEEE 802.3u 100BASE-T, TX, and T4 Compatible.

l 160 pin or 144 pin PQFP package.

l 5V CMOS process.

7

ASIX ELECTRONICS CORPORATION

Page 8

AX88140A PRELIMINARY

1.3 Block Diagram:

SERIAL BOOT ROM

ROOM Interface

Serial

ROM I/F

Receive FIFO

PCI SYM

BUS

PCI

BUS

Interface

Buffer

Management

DMA Engine

Transmit FIFO

General Purpose REG

BOOT

ROM I/F

Interface

MAC

Controller

General purpose I/O pins

Interface

Interface

MII

PCS

10 BT

MII

SRL

Fig - 1 AX88140A Block Diagram

8

ASIX ELECTRONICS CORPORATION

Page 9

AX88140A PRELIMINARY

1.4 AX88140AQ Pin Connection Diagram for 160-pin

The AX88140A is housed in the 160-pin plastic quad flat pack. Fig - 2 shows the AX88140A

pin connection diagram.

nc

nc

nc

int#

rst#

vdd

vss

pci_clk

vdd

gnt#

req#

vss

ad<31>

ad<30>

vss

ad<29>

ad<28>

vss

ad<27>

ad<26>

vdd

ad<25>

ad<24>

c_be#<3>

idsel

vss

ad<23>

ad<22>

ad<21>

ad<20>

vdd

ad<19>

ad<18>

vdd

vss

vss

ad<17>

ad<16>

vss

nc

nc

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

nc

nc

160

159

158

1

2

3

4

5

6

7

8

9

nc

157

nc

156

nc

srl_txen

154

155

srl_tclk

srl_txd

152

153

srl_rclk

srl_rxen

150

151

srl_clsn

srl_rxd

148

149

mii/srl

147

mtxd<3>/symtxd<3>

mtxd<2>/symtxd<2>

145

144

vdd

143

mtxd<1>/symtxd<1>

vss

141

142

symtxd<4>

146

mtclk/symtclk

mtxd<0>/symtxd<0>

mtxen/symtxen

rcv_match

nc

vdd

vss

134

135

136

137

138

139

140

mrxd<2>/symrxd<2>

symrxd<4>

mrxd<3>/symrxd<3>

132

133

131

ASIX

88140AQ

43

45

44

41

42

50

49

48

47

46

55

54

53

52

51

60

59

58

57

56

65

64

63

62

61

70

69

68

67

66

mcol

mcrs

mrxdv

mrxerr

mrclk/symrclk

mrxd<1>/symrxd<1>

mrxd<0>/symrxd<0>

130

128

129

73

72

71

127

74

126

75

125

76

124

77

sd

123

nc

nc

121

122

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

78

79

80

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

nc

nc

vss

vdd

mdc

mdio

nc

br_a<1>

br_a<0>

brce#

br_ad<7>

br_ad<6>

vdd

vss

br_ad<5>

br_ad<4>

br_ad<3>

br_ad<2>

br_ad<1>

br_ad<0>

vss

genp<7>

genp<6>

genp<5>

genp<4>

vdd

vss

genp<3>

genp<2>

genp<1>

genp<0>

sr_cs

sr_ck

sr_di

sr_do

vdd

vss

vdd*

nc

nc

nc

nc

vss

irdy#

trdy#

frame#

devsel#

cbe#<2>

vdd

stop#

serr#

perr#

par

cbe#<1>

vss

ad<15>

ad<14>

vss

ad<13>

ad<12>

ad<11>

vdd

ad<10>

ad<09>

vss

ad<08>

ad<07>

ad<06>

cbe#<0>

vss

ad<05>

ad<04>

vdd

ad<03>

ad<02>

vss

Fig - 2 AX88140AQ Pin connection diagram for 160-pin

9

ASIX ELECTRONICS CORPORATION

ad<00>

ad<01>

nc

nc

Page 10

AX88140A PRELIMINARY

1.5 AX88140AP Pin Connection Diagram for 144-pin

The AX88140A is housed in the 144-pin plastic quad flat pack. Fig - 3 shows the AX88140A

pin connection diagram.

mcol

mii_crs

mrxdv

mrxerr

mrclk/symrclk

110

111

112

113

114

sd

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

vss

vdd

mdc

mdio

nc

br_a<1>

br_a<0>

brce#

br_ad<7>

br_ad<6>

vdd

vss

br_ad<5>

br_ad<4>

br_ad<3>

br_ad<2>

br_ad<1>

br_ad<0>

vss

genp<7>

genp<6>

genp<5>

genp<5>

genp<4>

vdd

vss

genp<3>

genp<2>

genp<1>

genp<0>

sr_cs

sr_ck

sr_di

sr_do

vdd

vss

vdd*

int#

rst#

vdd

vss

pci_clk

vdd

gnt#

req#

vss

ad<31>

ad<30>

vss

ad<29>

ad<28>

vss

ad<27>

ad<26>

vdd

ad<25>

ad<24>

cbe#<3>

idsel

vss

ad<23>

ad<22>

ad<21>

ad<20>

vdd

ad<19>

ad<18>

vdd

vss

vss

ad<17>

ad<16>

vss

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

mii/srl

mtxd<3>/symtxd<3>

mtxd<2>/symtxd<2>

131

130

vdd

129

vss

128

mtxd<1>/symtxd<1>

nc

144

143

1

2

3

4

5

6

7

8

9

142

srl_txen

140

141

139

srl_txd

137

138

srl_tclk

nc

nc

nc

136

srl_rxd

134

135

symtxd<4>

132

133

srl_clsn

srl_rclk

srl_rxen

mtclk/symtclk

mtxd<0>/symtxd<0>

mtxen/symtxen

rcv_match

nc

122

123

124

125

126

127

mrxd<2>/symrxd<2>

symrxd<4>

vdd

vss

mrxd<3>/symrxd<3>

118

119

120

121

117

mrxd<1>/symrxd<1>

mrxd<0>/symrxd<0>

116

115

ASIX

88140AP

37

38

vss

cbe#<2>

40

39

irdy#

frame#

41

trdy#

devsel#

42

44

43

vdd

stop#

45

perr#

46

serr#

48

47

par

cbe#<1>

49

vss

51

50

ad<15>

ad<14>

ad<13>

52

53

vss

ad<12>

54

ad<11>

55

56

vdd

ad<10>

58

57

ad<09>

60

59

vss

ad<08>

63

62

61

ad<07>

ad<06>

cbe#<0>

64

vss

66

65

ad<05>

ad<04>

67

vdd

ad<03>

69

68

ad<02>

70

vss

ad<01>

71

Fig - 3 AX88140AP Pin connection diagram for 144-pin

10

ASIX ELECTRONICS CORPORATION

72

ad<00>

Page 11

AX88140A PRELIMINARY

2.0 Signal Description

2.1 Signal Descriptions for 160-pin and 144-pin

The following terms describe the AX88140A pin-out:

l Address phase

Address and appropriate bus commands are driven during this cycle.

l Data phase

Data and the appropriate byte enable codes are driven during this cycle.

l #

All pin names with the # suffix are asserted low.

The following abbreviations are used in Tab - 1 PCI interface group Tab - 2 Boot ROM , Serial ROM , General-

purpose signals group ,Tab - 3 MII/SYM/SRL interface signals group ,Tab - 4 Extended , NC, Power pins group..

I Input

O Output

I/O Input /Output

O/D Open Drain

11

ASIX ELECTRONICS CORPORATION

Page 12

AX88140A PRELIMINARY

2.2 PCI interface group

SIGNAL TYPE PIN

NUMBER

FOR 160 PIN

AD<31>

AD<30>

AD<29>

AD<28>

AD<27>

AD<26>

AD<25>

AD<24>

AD<23>

AD<22>

AD<21>

AD<20>

AD<19>

AD<18>

AD<17>

AD<16>

AD<15>

AD<14>

AD<13>

AD<12>

AD<11>

AD<10>

AD<9>

AD<8>

AD<7>

AD<6>

AD<5>

AD<4>

AD<3>

AD<2>

AD<1>

AD<0>

CBE#<3>

CBE#<2>

CBE#<1>

CBE#<0>

DEVSEL# I/O 48 42 Device select Is asserted by the target of the current bus access.

FRAME# I/O 45 39 The FRAME# Signal is driven by the AX88140A To indicate the

GNT# I 9 7 BUS GRANT Indicates to the AX88140A That access to the bus is

IDSEL I 24 22 Initialization devise select asserts To indicate that the host is

INT# O/D 3 1 Interrupt request asserts When one of the appropriate bits of reg5

IRDY# I/O 46 40

I/O 12,

13,

15,

16,

18,

19,

21,

22,

26,

27,

28,

29,

31,

32,

36,

37,

56,

57,

58,

60,

61,

63,

64,

66,

68,

69,

71,

72,

74,

75,

77,

78

I/O 23,

44,

54,

67

PIN

NUMBER

FOR 144 PIN

10,

11,

13,

14,

16,

17,

19,

20,

24,

25,

26,

27,

29,

30,

34,

35,

50,

51,

52,

54,

55,

57,

58,

60,

62,

63,

65,

66,

68,

69,

71,

72

21,

38,

48,

61

DESCRIPTION

Address and data bits are multiplexed on the samepins. During the

address phase, the AD<31:0> contain a physical address (32 bits).

During, data phases, AD<31:0> contain 32 bits of data.

The AX88140A supports both read and write bursts (in master

operation only). Little and big endian byte ordering can be used.

BUS COMMAND and BYTE ENABLE Are multiplexed on the

same PCI pins. During the address phase of the transaction,

CBE#<3:0> Provide the BUSCOMMAND.During the data phase,

CBE#<3:0> Provide the BYTE ENABLE. The BYTE ENABLE

determines which byte lines carry valid data., CBE#<0> Applies to

byte 0, and CBE#<3> Applies to byte 3.

When the AX88140A is the master of the current bus access, the

target assert DEVSEL# confirming the access. It is driven by

AX88140A When AX88140A is selected as a slave.

beginning and duration of an access. FRAME# Asserts to indicate

the beginning of a bus transaction. While FRAME# is asserted,

data transfers continue. When FRAME# deasserts the next data

phase is the final data phase transaction.

granted.

issuing a configuration cycle to the AX88140A.

sets and causes an interrupt, provided that the corresponding mask

bit in reg7 is not asserted. interruptrequest deasserts by writing a 1

into the appropriate crs5 bit.

This pin must be pulled up by an external resistor.

Initiator ready Indicates the bus master ability to complete the

current data phase of the transaction.

A data phase is completed on any rising edge of the clock When

both IRDY# and target ready TRDY# are asserted. Waitcycles are

inserted until both IRDY# and TRDY# are asserted together.

When the AX88140A is the bus master, IRDY# is asserted during

write operations to indicate that valid data is present on the

AD<31:0>. During read operations, the AX88140A asserts

12

ASIX ELECTRONICS CORPORATION

Page 13

AX88140A PRELIMINARY

IRDY# to indicate that it is ready to accept data.

PAR I/O 53 47 Parity is an even parity bit for the AD<31:0> AD and CBE#<3:0>.

PCI_CLK I 7 5 The clock provides the timing for the AX88140A related PCI bus

PERR# I/O 51 45 Parity error asserts when a data parity error is detected. When the

REQ# O 10 8 Bus request is asserted by the AX88140A to indicate to the bus

RST# I 4 2 Resets the AX88140A to its initial state. This signal must be

SERR# I/O 52 46 System Error is used by AX88140A to report address parity Error.

STOP# I/O 49 43 Stop indicator indicates that the current target is requesting the bus

TRDY# I/O 47 41 Target ready indicates thetargetability tocompletethe current data

During address and data phases, parity is calculated on all the

AD<31:0> AND CBE#<3:0>lines whether or not any of these

lines carry meaningful information.

transactions. All the bus signals are sampled on the rising edge of

PCI_CLK. The clock frequency range is between 21MHZ and

33MHZ.

AX88140A is the bus master it monitor PERR# to see if the target

report a data parity error., when the AX88140A is the bus target

and a parity error is detected, the AX88140A asserts PERR#. This

pin must be pulled up by an external resistor.

arbiter that it wants to use the bus.

asserted for at least 10 active PCI clock cycles. When is the reset

state, all PCI output pins are put into tri-state and all PCI o/d

signals are floated.

This pin must be pulled up by an external resistor.

master to stop the current transaction. The AX88140A responds to

the assertion of STOP# when it is the bus master, and stop the

current transaction.

phase of the transaction.

A data phase is completed on any clock when both TRDY# and

IRDY# are asserted. Wait cycles are inserted until both IRDY#

and TRDY# are asserted together. When the AX88140A is the bus

master, target ready is asserted by the bus slave on the read

operation, indicating that valid data is present on the ad lines.

During a write cycle, it indicates that the target is prepared to

accept data.

Tab - 1 PCI interface group

13

ASIX ELECTRONICS CORPORATION

Page 14

AX88140A PRELIMINARY

2.3 Boot ROM , Serial ROM , General-purpose signals group

SIGNAL TYPE PIN

NUMBER

FOR 160 PIN

BR_A<0> 0 112 102 Boot ROM address line bit 0.

BR_A<1> 0 113 103 Boot ROM address line bit 1. This pin also latches the boot ROM

BR_AD<7>

BR_AD<6>

BR_AD<5>

BR_AD<4>

BR_AD<3>

BR_AD<2>

BR_AD<1>

BR_AD<0>

BR_CE# O 111 101 Boot ROM chip enable.

SR_CK O 88 78 Serial ROM clock signal.

SR_CS O 89 79 Serial ROM chip-select signal.

SR_DI O 87 77 Serial ROM data-in signal.

SR_DO I 86 76 Serial ROM data-out signal.

GENP<7>

GENP<6>

GENP<5>

GENP<4>

GENP<3>

GENP<2>

GENP<1>

GENP<0>

I/O 110,

109,

106,

105,

104,

103,

102,

101

I/O 99,

98,

97,

96,

93,

92,

91,

90

PIN

NUMBER

FOR 144 PIN

100,

99,

96,

95,

94,

93,

92,

91

89,

88,

87,

86,

83,

82,

81,

80

DESCRIPTION

address and control lines by the two external latches.

Boot ROM address and data multiplexed lines bits 7 through 0. In

the first of two consecutive address cycles, these lines contain the

boot ROM address bits 9 through 2; followed by boot ROM

address bits 17 through 10 in the second cycle. During the data

cycle, bits 7 through 0 contain data.

General-purpose pins can be used by software as either status pins

or control pins. These pins can be configured by software to

perform either input or output functions.

Tab - 2 Boot ROM , Serial ROM , General-purpose signals group

2.4 MII/SYM/SRL interface signals group

SIGNAL TYPE PIN

NUMBER

FOR 160 PIN

MCOL I 126 112 Collision detected is asserted when detected by an

MCRS I 127 113 Carrier sense is asserted by the PHY when the media

MRXDV I 125 111 Data valid is asserted by an external PHY when

MRXERR I 124 110 Receive error asserts when a data decoding error is

MDC O 116 106 MII management data clock is sourced by the

MDIO I/O 115 105 MII management data input/output transfers control

MII/SRL O 147 133 Indicates the selected port: SRL or MII/SYM. When

PIN

NUMBER

FOR 144 PIN

DESCRIPTION

external physical layer protocol(PHY) device.

is active.

receive data is present on the MRXD/SYRXD lines

and is deasserted at the end of the packet. This signal

should be synchronized with the

MRCLK/SYMRCLK signal.

detected by an external PHY device. This signal is

synchronized to MRCLK/SYMRCLK and can be

asserted for a minimum of one receive clock. When

asserted during a packet reception, it sets the cyclic

redundancy check(CRC) error bit in the receive

descriptor (RDESO).

AX88140A to the PHY devices as a timing reference

for the transfer of information on the MII_MDIO

signal.

information and status between the PHY and the

AX88140A.

asserted, the MII/SYM port is active. When

deasserted, the SRL port is active.

14

ASIX ELECTRONICS CORPORATION

Page 15

AX88140A PRELIMINARY

MRCLK/SYMRCLK I 128 114 Supports either the 25-MHZ or 2.5-MHZ receive

MRXD<3>/SYMRXD<3>

MRXD<2>/SYMRXD<2>

MRXD<1>/SYMRXD<1>

MRXD<0>/SYMRXD<0>

MTCLK/SYMTCLK I 137 123 Supports the 25-MHZ or 2.5-MHZ transmit clock

MTXD<3>/SYMTXD<3>

MTXD<2>/SYMTXD<2>

MTXD<1>/SYMTXD<1>

MTXD<0>/SYMTXD<0>

MTXEN/SYMTXEN O 139 125 Transmit enable signals that the transmit is active to

RCV_MATCH O 136 122 Receive match indication is asserted when a received

SD I 123 109 Signal detect indication supplied by an external

SRL_CLSN I 148 134 Collision detect signals a collision occurrence on the

SRL_RCLK I 151 137 Receive clock carries the recovered receive clock

SRL_RXD I 149 135 Receive data carries the input receive data from the

SRL_RXEN I 150 136 Receive enable signals activity on the Ethernet cable

SRL_TCLK I 153 139 Transmit clock carries the transmit clock supplied by

SRL_TXD O 152 138 Transmit data carries the serial output data from the

SRL_TXEN O 154 140 Transmit enable signals an external ENDEC That the

SYMRXD <4> I 133 119 Receive data, together with the four receive lines

SYMTXD<4> O 146 132 Transmit data, together with the our transmit lines

I 132,

131,

130,

129

O 145,

144,

141,

140

118,

117,

116,

115

131,

130,

127,

126

clock. This clock is recovered by the PHY.

Four parallel receive data lines When MII mode is

selected. This data is driven by an external PHY that

attached the media and should be synchronized with

the MRCLK/SYMRCLK signal.

supplied by the external physical layer medium

dependent (PMD) device. This clock should always

be active.

Four parallel transmit data lines. This data is

synchronized to the assertion of the

MTCLK/SYMTCLK signal and is latched by the

external PHY on the rising edge of the

MTCLK/SYMTCLK signal.

an external PHY device. In PCS mode (REG6<23>),

This signal reflects the transmit activity of the MAC

sub-layer.

packet has passed address recognition.

Receive match indication is asserted when a received

packet has passed address recognition.

physical layer medium dependent (PMD) device.

Ethernet cable to the AX88140A. It may be asserted

and deasserted asynchronously by the external

ENDEC to the receive clock.

supplied by an external ENDEC. during idle periods,

SRL_RCLK may be inactive.

external ENDEC. The incoming data should be

synchronous with the SRL_RCLK signal.

to the AX88140A. It is asserted when receive data is

present on the Ethernet cable and is deasserted at the

end of a frame. It may be asserted and deasserted

asynchronously to the receive clock (SRL_RCLK) by

the external ENDEC.

an external ENDEC. This clock must always be

active (even during reset).

AX88140A. This data is synchronized to the

SRL_TCLK signal.

AX88140A transmit is in progress.

MII/SYM_RXD<3:0>, Provide five parallel lines of

data in symbol from for use in PCS mode

(100BASE-T, REG6<23). This data is synchronized

on the rising edge of the MTCLK/SYMTCLK signal.

MII/SYM_TXD<3:0>,provide five parallel lines of

data in symbol form for use in PCS mode

(100BASE-T, REG6<23>). This data is synchronized

on the rising edge of the MII/SYM_TCLK signal.

Tab - 3 MII/SYM/SRL interface signals group

15

ASIX ELECTRONICS CORPORATION

Page 16

AX88140A PRELIMINARY

2.5 Extended , NC, Power pins group

SIGNAL TYPE PIN

NUMBER

FOR 160 PIN

EC<15:0> O 160,159,122,

121,120,119,

82,81,80,79,42,41

,40,39,2,1

NC O 114,138,155,156,

157,158

VDD P 5,8,20,30,33,

50,62,73,85,

95,108,117,

135,143

VDD* P 83 73 5.0-V reference for 5.0-V signaling environments

VSS P 6,11,14,17,25,

34,35,38,43,

55,59,65,70,

76,84,94,100,

107,118,134,

142

PIN

DESCRIPTION

NUMBER

FOR 144 PIN

NONE Expended pins. do not connect.

104,124,141,142,

143,144

3,6,18,28,31,

44,56,67,75,

85,98,107,

121,129

4,9,12,15,23,

32,33,36,37,

49,53,59,64,

70,74,84,90,97,10

8,120,128

No connection.

5-V supply input voltage.

Ground pins.

Tab - 4 Extended , NC, Power pins group

16

ASIX ELECTRONICS CORPORATION

Page 17

AX88140A PRELIMINARY

3.0 Configuration Operation

1. Software reset (REG0<0>) has no effect on the configuration registers.

2. Hardware reset puts the configuration registers in default values.

3. The configuration registers could be accessed in byte, word , and long-word.

3.1 Configuration Space Mapping

CONFIGURATION REGISTER IDENTIFIER I/O ADDRESS OFFSET

DEVICE/VENDOR ID CSID 00H

COMMAND AND STATUS CSCS 04H

REVISION CSRV 08H

LATENCY TIMER CSLT 0CH

BASE I/O ADDRESS CBIO 10H

BASE MEMORY ADDRESS CBMA 14H

RESERVED - 18H-28H

SUBSYSTEM ID - 2CH

EXPANSION ROM BASE ADDRESS CBER 30H

RESERVED - 34H - 38H

INTERRUPT CSIT 3CH

Special Use SUD 40H

Tab - 5 Configuration Space Mapping

17

ASIX ELECTRONICS CORPORATION

Page 18

AX88140A PRELIMINARY

3.2 Configuration Space

3.2.1 Configuration ID Register (CSID)

FIELD R/W DESCRIPTION

31:16 R Device ID :

15:0 R Vender ID :

3.2.2 Command and Status Configuration Register (CSCS)

FIELD R/W TYPE DESCRIPTION

31 R STATUS Detected Parity Error : active high

30 R STATUS Signal System Error : active high

29 R STATUS Received Master Abort : active high

28 R STATUS Received Target Abort : active high

26:25 R STATUS Device Select Timing : fixed at 01 which indicates a medium assertion of DEVSEL#

24 R STATUS Data Parity Report : active high

23 R STATUS Fast Back-to-Back : always set

22:9 - RESERVED

8 R/W COMMAND System Error Enable : active high

6 R/W COMMAND Parity Error Response : active high

2 R/W COMMAND Master Operation : active high

1 R/W COMMAND Memory Space Access : active high

0 R/W COMMAND I/O Space Access : Active high

Provides the unique AX88140A ID number (1400H)

Provides the manufacturer of the AX88140A (125BH)

Tab - 6 CSID Configuration ID Register Description

Tab - 7 CSCS Command and Status Configuration Register

3.2.3 Configuration Revision Register (CSRV)

FIELD R/W DESCRIPTION

31:24 R Base Class : Always equal to 2H that indicates the network controller

23:16 R Subclass : Always equal to 0H that indicates the fast Ethernet controller

7:4 R Revision Number : Indicates the AX88140A revision number and is equal to 0H

3:0 R Step Number : Indicates the AX88140A step number and is referred to current silicon step.

Tab - 8 CSRV Configuration Revision Register Description

3.2.4 Configuration Latency Timer Register (CSLT)

FIELD R/W DESCRIPTION

31:16 R/W Reserved

15:8 R/W Configuration Latency Timer. The value after hardware reset equal to 0h.

7:0 R/W Reserved

Tab - 9 CSLT Configuration ID Register Description

18

ASIX ELECTRONICS CORPORATION

Page 19

AX88140A PRELIMINARY

3.2.5 Configuration Base I/O Address Register (CBIO)

FIELD R/W DESCRIPTION

31:7 R/W Configuration Base I/O Address : Defines the address assignment mapping of AX88140A‘s regs.

6:1 R This field value is 0 when read

0 R I/O Space Indicator : Determines that the register maps into the I/O space. The value in this field is 1.

Tab - 10 CBIO Configuration Base I/O Address Register Description

3.2.6 Configuration Base Memory Address Register (CBMA)

FIELD R/W DESCRIPTION

31:7 R/W Configuration Base Memory Address : Defines the address assignment mapping of AX88140A‘s regs.

6:1 R This field value is 0 when read

0 R Memory Space Indicator : Determines that the register maps into the memory space. The value in this

Tab - 11 CBMA Configuration Base Memory Address Register Description

3.2.7 Expansion ROM Base Address Register (CBER)

FIELD R/W DESCRIPTION

31:10 R/W Expansion ROM Base Address

9:1 R This field value is 0 when read

0 R/W Expansion ROM Enable Bit : Active high

field is 0.

Tab - 12 CBER Expansion ROM Base Address Register Description

3.2.8 Configuration Interrupt Register (CSIT)

FIELD R/W DESCRIPTION

31:24 R MAX_LAT : time unit is equal to 0.25 microsecond.(28H)

23:16 R MIN_GNT : Time unit is equal to 0.25 microsecond.(14H)

15:8 R Interrupt Pin : The AX88140A uses INTA# and the read value is (01H).

7:0 R/W Interrupt Line : The BIOS writes the routing information into this field.

Tab - 13 CSIT Configuration Interrupt Register Description

19

ASIX ELECTRONICS CORPORATION

Page 20

AX88140A PRELIMINARY

4.0 Registers Operation

1. The REGs are quad-word aligned, 32-bits long, and must be accessed using long-word

instruction with quad-word aligned addresses only.

2. Reserved bits should be written with 0.; Reserved bits are UNPREDICTABLE on read

access.

3. Retries on second data transactions occur in response to burst accesses.

4.1 Registers Mapping

REGISTER MEANING OFFSETFROM REG BASE ADDRESS

(CBIO,CBMA)

REG0 BUS MODE 00H

REG1 TRANSMIT POLL DEMAND 08H

REG2 RECEIVE POLL DEMAND 10H

REG3 RECEIVE LIST BASE ADDRESS 18H

REG4 TRANSMIT LIST BASE ADDRESS 20H

REG5 STATUS 28H

REG6 OPERATION MODE 30H

REG7 INTERRUPT ENABLE 38H

REG8 MISSED FRAME AND OVERFLOW COUNTER 40H

REG9 SERIAL ROM, AND MII MANAGEMENT 48H

REG10 - 50H

REG11 GENERAL-PURPOSE TIMER 58H

REG12 GENERAL-PURPOSE PORT 60H

REG13 FILTERING BUFFER INDEX 68H

REG14 FILTERING BUFFER DATA 70H

Tab - 14 Command and Status Register Mapping

20

ASIX ELECTRONICS CORPORATION

Page 21

AX88140A PRELIMINARY

4.2 Host REGs

4.2.1 Bus Mode Register (REG0)

FIELD R/W/C DESCRIPTION

31:22 - RESERVED

21 R/W RML - Read Multiple

20 R/W DBO - Descriptor Byte Ordering Mode

19:14 - Reserved.--Writtenas “0” for future compatibility concern.

13:8 R/W PBL - Programmable Burst Length

7 R/W BLE - Big/Little Endian

6:2 - RESERVED

1 R/W BAR - Bus Arbitration

0 R/W SWR - Software Reset

When set, the AX88140A supports the memory-read-multiple command on the PCI bus. This bus

command is used in memory read bursts with more than one longword. When reset, the AX88140A

uses memory-read command in all its memory read accesses on the PCI bus.

When set, the AX88140A operates in big edian ordering mode for descriptors only.

When reset, the AX88140A operates in little endian mode.

Indicates the maximumnumber of longwords to be transfered in one DMA transaction. If reset, the

ax88140a burst is limited only bytheamount of datastoredinthe receive FIFO(atleast 16 longword),

or by theamountof free space in the transmit FIFO (at least 16longword)beforeissuingabus request.

The PBL can be programmed with permissiblevalues 0,1,2,4,8,16, or 32. After reset, the PBL default

value is 0.

When set, the AX88140A operates in big endian byte ordering mode. When reset, the AX88140A

operates in little endian byte ordering mode. Big endian is applicable only for data buffer

Selects the internal bus arbitration between the receive and transmit processes.

When set, a round robin arbitration scheme is applied resulting in equal sharing between processes.

When reset, thereceiveprocess has priority over the transmit process, unless theax88140aiscurrently

transmitting.

When set, the AX88140A resets all internal hardware with the exception of the configuration area and

also, it does not change the port select setting (REG6<18>).

Software reset does not affect the configuration area.

Tab - 15 REG0 Bus Mode Register Description

4.2.2 Transmit Poll Demand (REG1)

FIELD R/W DESCRIPTION

31:0 W TPD- Transmit Poll Demand

When written with any value, the AX88140A checks for frames to be transmitted. If no descriptor is

available, the transmit process returns to the suspended states and REG5<2> is asserted. If the descriptor

is available the transmit process resumes.

Tab - 16 REG1 Transmit Poll Demand Register Description

21

ASIX ELECTRONICS CORPORATION

Page 22

AX88140A PRELIMINARY

4.2.3 Receive Poll Demand (REG2)

FIELD R/W/C DESCRIPTION

31:0 W RPD - Receive Poll Demand

4.2.4 Receive List Base Address (REG3)

1. The register is used to point the AX88140A to the start of receive descriptors list.

2. The descriptor list resides in physical memory space and must be longword aligned. The

AX88140A behaves UNPREDICTABLY when the list are not longword aligned.

3. Writing to REG3 is permitted only when receive process is in the stopped state. That is, the

REG3 must be written before the receive START command is given .

When written with any value, the AX88140A checks for receive descriptors to be required. If no

descriptor is available, the receive process returns to the suspended states and REG5<7> is not

asserted. If the descriptor is available the receive process resumes.

Tab - 17 REG2 Receive Poll Demand Register Description

REG3 Receive List Base Address Register Description

FIELD R/W/C DESCRIPTION

31:2 R/W Start of receive list

1:0 R/W Must be 00 for longword alignment

Tab - 18 REG3 Receive List Base Address Register Description

4.2.5 Transmit List Base Address (REG4)

1. The register is used to point the AX88140A to the start of transmit descriptors list.

2. The descriptor list resides in physical memory space and must be long-word aligned. The

AX88140A behaves UNPREDICTABLY when the list are not long-word aligned.

3. Writing to REG4 is permitted only when transmit process is in the stopped state. That is, the

REG4 must be written before the transmit START command is given .

FIELD R/W/C DESCRIPTION

31:2 R/W Start of transmit list

1:0 R/W Must be 00 for long-word alignment

Tab - 19 REG4 Transmit List Base Address Register Description

22

ASIX ELECTRONICS CORPORATION

Page 23

AX88140A PRELIMINARY

4.2.6 Status Register (REG5)

1. The status register contains all the status bits that the AX88140A reports to the host.

2. Most of the fields in this register cause the host to be interrupted.

3. REG5 bits are not cleared when read.

4. Writing 1 to these bits clears them; writing 0 has no effect. Each field can be masked.

Field R/W/C Description

31:26 - Reserved

25:23 R EB - Error Bits

22:20 - Reserved.--Written as “0” for future compatibility concern.

19:17 - Reserved.--Written as “0” for future compatibility concern.

16 R

15 R

13 R FBE - Fatal Bus Error

11 R/W/C GTE - General Purpose Timer Expired

10 R/W/C ETI - Early Transmit Interrupt

9 R/W/C RWT - Receive watchdog Time out

8 R/W/C RPS - Receive Process Stopped

7 R/W/C RU - Receive Buffer Unavailable

6 R/W/C RI - Receive Interrupt

5 R/W/C UNF - Transmit Under-flow

(Not generate interrupt)

Indicates the type of error that

caused system error.

Valid only when fatal bus error

REG5<13> is set.

NIS - Normal Interrupt Summary

Only the unmasked bits affect normal interrupt summary REG5<16> bit Normal interrupt

summary bit. Its value is the logical OR of :

CSR5<0> transmit interrupt

CSR5<2> transmit buffer unavailable

CSR5<6> receive interrupt

CSR5<10> Early transmit interrupt

CSR5<11> General-purpose timer expired

AIS - Abnormal Interrupt Summary

Only unmasked bits affect only the abnormal interrupt summary REG5<15> bit.

Abnormal interrupt summary bits. Its value is the logical OR of :

CSR5<1> transmit process stopped

CSR5<3> transmit jabber time out

CSR5<5> transmit under-flow

CSR5<7> receive buffer unavailable

CSR5<8> receive process stopped

CSR5<9> receive watchdog time out

CSR5<13> fatal bus error

Indicates that a system error occurred. If a system error occurs, all bus accesses are disabled

Indicates that the general-purpose timer (REG11) counter has expired. This timer is mainlyused

by the software driver.

Indicates that the packet to be transmitted was fully transferred into the chip‘s internal transmit

FIFOs. Transmit interrupt (REG5<0>) automatically clears this bit.

Indicates that the receive watchdog timerexpiredandanother node is still active onthenetwork.

In case of overflow, the long packets maynot be received.

Asserts when the receive process enters stopped state.

Indicates the next descriptor in the receive list is owned by the host and cannot be acquired by

the AX88140A.The reception process is suspended.

Indicates the completion of a framereception. Specific framestatusinformation has been posted

in the descriptor. The reception process remains in the running state.

Indicates that the transmit FIFO had an under-flow condition during the packet transmission.

The transmit process is placed in the suspended state and under-flow error TDES0<1> is set.

25 24 23 Description

0 0 0 Parity error

0 0 1 Master abort

0 1 0 Target abort

0 1 1 Reserved

1 x x Reserved

4 - Reserved.--Written as “0” for future compatibility concern.

23

ASIX ELECTRONICS CORPORATION

Page 24

AX88140A PRELIMINARY

3 R/W/C TJT - Transmit Jabber Time-out

2 R/W/C TU - Transmit Buffer Unavailable

1 R/W/C TPS - Transmit Process Stopped

0 R/W/C TI - Transmit Interrupt

4.2.7 Operation Mode Register (REG6)

1. REG6 establishes the receive and transmit operating modes and commands.

2. REG6 should be the last REG to be written as part of initialization.

Field R/W/C Description

31 - Reserved

29:25 - Reserved.--Written as “0” for future compatibility concern.

20 - Reserved.--Written as “0” for future compatibility concern.

17:16 - Reserved.--Written as “0” for future compatibility concern.

15:14 R/W

11:10 R/W OM - Operating Mode

9 R/W FD - Full-Duplex Mode 1 Full-Duplex

TR - Threshold Control Bits

The threshold value has a direct impact on the AX88140A bus arbitration scheme . Transmission starts when

the frame size within the transmit FIFO is larger than the threshold. In addition, full frames with a length

less than the threshold are also transmitted. The transmit process must be in the stopped state to change these

bits.

Controls the selected threshold level for the AX88140A transmit FIFO. Four threshold levels are allowed.

REG6<21> REG6<15:14> REG6<22>=X REG6<22>=1 REG6<22>=0

Indicates that the transmit jabber timer expired, meaning that the AX88140A transmitter had

been excessively active. The transmission process is aborted and placed in the stopped state.

This event causes the transmit jabber time-out TDES0<14> is set.

Indicates that the next descriptor on the transmitlist is owned by the host and cannot be acquired

by the AX88140A.The transmission process is suspended. To resume processing transmit

descriptors, the host should change the ownership bit of the descriptor and then issue a transmit

poll demand command.

Asserts when the transmit process enters the stopped state.

Indicates that a frame transmission was completed, while TDES1<31> is asserted in the first

descriptor of the frame.

Tab - 20 REG5 Status Register Description

1 All incoming packets will be received30 R/W RA - Receive All

0 Filtering mode

1 Enable Scrambler24 R/W SCR - Scrambler Mode

0 Disable Scrambler

1 PCS functions are active23 R/W PCS - PCS Mode

0 MII/SYM port is not selected

1 Threshold is 10Mb/s22 R/W TTM - Transmit Threshold Mode

0 Threshold is 100Mb/s

1 Enable Store and Forward21 R/W SF - Store and Forward

0 Disable Store and Forward

1 Heartbeat Disable19 R/W HBD - Heartbeat Disable

0 Heartbeat Enable

1 MII/SYM port is selected.18 R/W PS - Port Select

0 SRL port is selected

REG6<18>=0 REG6<18>=1 REG6<18>=1

0 00 72 72 128

0 01 96 96 256

0 10 128 128 512

0 11 160 160 1024

1 XX Store & Forward Store & Forward Store & Forward

1 Start Transmission13 R/W ST - Start/Stop Transmission

0 Stop Transmission

1 Enable force collision12 R/W FC - Force Collision Mode

0 Disable force collision

00 Normal

01 Internal Loop-back

10 External Loop-back

24

ASIX ELECTRONICS CORPORATION

Page 25

AX88140A PRELIMINARY

0 Half-Duplex

1 Accept broadcast packet8 R/W RB - Receive broadcast packet

0 Reject broadcast packet

1 Enable Pass All Multicast7 R/W PM - Pass All Multicast

0 Disable Pass All Multicast

6 R/W PR - Promiscuous Mode

5:4 - Reserved.--Written as “0” for future compatibility concern.

3 R/W PB - Pass Bad Frames

2 - Reserved.--Written as “0” for future compatibility concern.

0 R PLS - PCS_SYM Link Status : Active high.

Tab - 21 REG6 Operation Mode Register Description

Port and Data Rate Selection

REG6

<18>

0 0 X X SRL 10MB/S Conventional 10MB/S ENDEC interface

1 1 0 0 MII/SYM 10MB/S MII with transmit FIFO thresholds appropriate

1 0 0 0 MII/SYM 100MB/S MII with transmit FIFO thresholds appropriate

1 0 1 0 MII/SYM 100MB/S PCS function for 100BASE-FX

1 0 1 1 MII/SYM 100Mb/s PCS and scrambler functions for 100BASE-T

REG6

<22>

REG6

<23>

REG6

<24>

ACTIVE

PORT

1 Indicates that any incoming valid frame is received,

regardless of its destination address.

0 Disable Promiscuous Mode.

1 All incoming frames that passed the address

filtering are received, including runt frames,

collided fragments, or truncated frames caused by

FIFO over-flow. If any received bad frames are

required, promiscuous mode (REG6<6>) should be

set to 1.

0 Disable pass bad frame.

1 Start Receive1 R/W SR - Start/Stop Receive

0 Stop Receive

DATA

FUNCTION

RATE

for 10MB/S

for 100MB/S

Tab - 22 Port and Data Rate Selection

25

ASIX ELECTRONICS CORPORATION

Page 26

AX88140A PRELIMINARY

4.2.8 Interrupt Enable Register (REG7)

1. The interrupt enable register (REG7) enables the interrupts reported by REG5.

2. Setting bit to 1 enables a corresponding interrupt. After a hardware or software reset, all interrupts are disabled.

Field R/W/C Description

31:17 - Reserved

16 R/W

15 R/W

13 R/W FBE - Fatal Bus Error interrupt enable. Active high.

11 R/W GPT - General purpose Timer interrupt Enable. Active high.

10 R/W ETE - Early Transmit Interrupt Enable. Active high.

9 R/W RW - Receive Watchdog Time out interrupt Enable. Active high

8 R/W RS - Receive Stopped interrupt Enable. Active high.

7 R/W RU - Receive Buffer Unavailable interrupt Enable. Active high.

6 R/W RI - Receive Interrupt Enable. Active high.

5 R/W UN - under-flow interrupt Enable. Active high.

4 - Reserved.--Written as “0” for future compatibility concern.

3 R/W TJ - Transmit Jabber Time out interrupt Enable. Active high.

2 R/W TU - Transmit Buffer Unavailable interrupt Enable. Active high.

1 R/W TS - Transmission Stopped interrupt Enable. Active high.

0 R/W TI - Transmit Interrupt Enable. Active high.

NI - Normal Interrupt Summary Enable

When set, normal interrupt is enabled.

When reset, no normal interrupt is enabled. This bit (REG7<16>) enables the following bits :

CSR5<0> Transmit interrupt

CSR5<2> Transmit buffer unavailable

CSR5<6> Receive interrupt

CSR5<10> Early transmit interrupt

CSR5<11> General-purpose timer expired

AI - Abnormal Interrupt Summary Enable

When set, abnormal interrupt is enabled.

When reset, no abnormal interrupt is enabled. This bit (REG7<15>) enables the following bits :

CSR5<1> transmit process stopped

CSR5<3> transmit jabber time-out

CSR5<5> transmit under-flow

CSR5<7> receive buffer unavailable

CSR5<8> receive process stopped

CSR5<9> receive watchdog time-out

CSR5<11> fatal bus error

Tab - 23 REG7 Interrupt Enable Register Description

4.2.9 Missed Frame and Overflow Counter (REG8)

Field R/W Description

31:29 - Reserved

28 R/C Overflow counter overflow

27:17 R/C Overflow counter

16 R/C Missed frame overflow

15:0 R/C Missed Frame Counter

Tab - 24 REG8 Missed Frame and Overflow Counter Description

Sets When the overflow counter overflows, Resets When REG8 is read.

Indicates the number of frames discarded because of overflow. The counter clears when read.

Sets When the missed frame counter overflows; Resets When reg8 is read.

Indicates the number of frames discarded because no host receive descriptors were available. The counter

clears when read.

26

ASIX ELECTRONICS CORPORATION

Page 27

AX88140A PRELIMINARY

4.2.10 Serial ROM and MII Management Register (REG9)

1. The register provides an interface to the Microwire serial ROM and to the physical layer

protocol (PHY). It selects the device andcontains both the commandsand data to be read from

and stored in the serial ROM.

2. The MII management selects and operation mode for reading and writing the MII.

FIELD R/W/C DESCRIPTION

31:20 - Reserved.--Written as “0” for future compatibility concern.

19 R MDI - MII management data_in

18 R/W MII - MII management operation mode

17 R/W MDO - MII Management write data

16 R/W MDC - MII Management clock

14 R/W RD - Read operation

13:12 - Reserved.--Written as “0” for future compatibility concern.

11 R/W SR - SERIAL ROM select

10:4 - Reserved.--Written as “0” for future compatibility concern.

3 R/W SDO - SERIAL ROM data_out

2 R SDI - SERIAL ROM data_in

Used by the AX88140A to read data from the PHY

Defines the operation mode (read or write) of the PHY.

Specifies the value of the data that AX88140A writes to the PHY

MII management data clock (MII_MDC) is an output signal to the PHY. it is used as a timing

reference.

Read control bit. When set together with REG9<12>, The AX88140A performs read cycles from the

BOOT ROM, and the serial ROM.

When set together with either SERIAL ROM read operation (REG9<14>) or SERIAL ROM Write

operation (REG9<13>), The AX88140A selects the SERIAL ROM.

SERIAL ROM data output(SR_DO) From the SERIAL ROM device to the AX88140A.

SERIAL ROM Data input(SR_DI) To the SERIAL ROM device from the AX88140A.

1 R/W SCLK - SERIAL ROM serial clock

0 R/W SCS - Serial ROM Chip Select

Serial clock (SR_CK) Output to the SERIAL ROM.

Chip select (sr_cs) output to the serial ROM.

Tab - 25 REG9 Serial ROM, and MII Management Register Description

4.2.11 General -Purpose Timer (REG11)

1. This register contains a 16 bit general-purpose timer. It is used mainly by the software driver

for timing functions not supplied by the operating system. After the timer is loaded, it starts

counting down . The expiration of the timer causes an interrupt in REG5<11>.

2. If the timer expires with the CON bit on, the counter will load itself automatically with the last

value. The timer is not active in snooze mode.

Field R/W/C Description

31:17 - Reserved.--Written as “0” for future compatibility concern.

1 Continuous operating mode.16 R/W CON - Continuous Mode

0 One-shot operating mode.

15:0 R/W Timer value

Contains the general-purpose timer value within a N microsecond cycle.

SRL_10M : 204.8us

MII_10M : 819.2us

MII_100M : 81.92us

27

ASIX ELECTRONICS CORPORATION

Page 28

AX88140A PRELIMINARY

Tab - 26 REG11 General -Purpose Timer Register Description

4.2.12 General -Purpose Port Register (REG12)

Field R/W/C Description

31:9 - Reserved.--Written as “0” for future compatibility concern.

8 R/W GPC - General Purpose Control .

When a hardware reset is initiated, all gep pins

become input pins.

7:0 R/W MD - General Purpose Mode and Data

Tab - 27 REG12 General -Purpose Port Register Description

4.2.13 Filtering Index (REG13)

FIELD R/W/C DESCRIPTION

31:6 - Reserved.--Written as “0” for future compatibility concern.

5:0 R/W FI - Filtering Index

When writing data to filtering buffer, uses filtering index register REG13 to point the position (buffer

number) in filtering buffer. The valid value is between 0 and 3.

Tab - 28 REG13 Filtering Index Register Description

1 Indicate next write REG12<7:0> is use

for define General purpose port in/out

direction.

0 Indicate next write REG12<7:0> is use

for read/write general purpose port data.

4.2.14 Filtering data (REG14)

FIELD R/W/C DESCRIPTION

31:0 R/W FD - Filtering Data

By indexed by filtering index register REG13, write the filtering data register REG14 to put filtering

address/hash table into filtering buffer..

Tab - 29 REG14 Filtering Data Register Description

Filtering Buffer

The AX88140A stores one Ethernet address for local physical address and filters the packets

with multicast addresses by 64 bits array. For any incoming frame with a multicast destination

address, the AX88140A applies the standard Ethernet cyclic redundancy check function to the

destination address, then uses the most significant 6 bits of the result as a bit index into the table. If

the indexed bit is set, the frame is accepted. If the bit is reset, the frame is rejected.

Description of Filtering Buffer

BUFFER

NUMBER

0 BYTE 0 - 3 OF LOCAL PHYSICAL ADDRESS

1 BYTE 4 - 5 OF LOCAL PHYSICAL ADDRESS IN THE LEAST SIGNIFICANT WORD

2 BIT 0 - 31 OF MULTICAST ADDRESS FILTERING TABLE

3 Bit 32 - 63 of multicast address filtering table

Tab - 30 Description of Filtering Buffer

DESCRIPTION

Layout of Filtering Buffer

BUFFER

NUMBER

0 PHYSICAL

BYTE 3 BYTE 2 BYTE 1 BYTE 0

ADDRESS BYTE 3

PHYSICAL ADDRESS

BYTE 2

28

PHYSICAL ADDRESS

BYTE 1

ASIX ELECTRONICS CORPORATION

PHYSICAL ADDRESS

BYTE 0

Page 29

AX88140A PRELIMINARY

1 RESERVED RESERVED PHYSICAL ADDRESS

2

3

MULTICAST

ADDRESS

FILTERING TABLE

BIT 24 - 31

multicast address

filtering table bit 56 -

63

MULTICAST

ADDRESS

FILTERING TABLE

BIT 16 - 23

multicast address

filtering table bit 48 - 55

BYTE 5

MULTICAST

ADDRESS FILTERING

TABLE BIT 8 - 15

multicast address filtering

table bit 40 - 47

Tab - 31 Layout of Filtering Buffer

PHYSICAL ADDRESS

BYTE 4

MULTICAST ADDRESS

FILTERING TABLE BIT

0 - 7

multicast address filtering

table bit 32 - 39

29

ASIX ELECTRONICS CORPORATION

Page 30

AX88140A PRELIMINARY

5.0 Host Communication

Descriptor lists and data buffers, collectively called the host communication, reside in the host

memory and manage the actions and status related to buffer management.

5.1 Descriptor Lists and Data Buffers

The AX88140A transfers data frames to the receive buffers and from the transmit buffers in host

memory. Descriptors that reside in the host memory act as pointers to these buffers.

There are two descriptor lists, one for receive and one for transmit. The base address of each list is

written into REG3 and REG4, respectively. A descriptor list is forward-linked (explicitly). The

last descriptor may point back to the first entry to create a ring structure. Explicit chaining of

descriptors is accomplished by setting the address pointer chained in both the receive and transmit

descriptors (RDES3 and TDES3). The descriptor lists reside in the host physical memory address

space.

A data buffer consists of either an entire frame or part of a frame, but it cannot exceed a single

frame. Buffers contain only data; buffer status is maintained in the descriptor. Data chaining refers

to frames that span multiple data buffers.

Descriptor Structure Example

Next Descriptor

Buffer 1

Descriptor 0

Buffer 2

Descriptor 1

Fig - 4 Descriptor Structure Example

30

ASIX ELECTRONICS CORPORATION

Page 31

AX88140A PRELIMINARY

5.2 Receive Descriptors

The receive descriptor provides onebuffer, one byte-count buffer,and one address pointer in

each descriptor. Descriptors and receive buffers addresses must be long-word aligned.

Receive Descriptor Format

31 0

O

RDES0

RDES1 Control bits Byte Count Buffer 2 Byte Count Buffer 1

RDES2 Buffer Address 1

RDES3 Buffer Address 2

W

Status

N

Fig - 5 Receive Descriptor Format

5.2.1 Receive Descriptor 0 (RDES0)

RDES0 contains the received frame status, the frame length, and the descriptor ownership

information.

Field Description

31 OWN - Own Bit

30 FF - Filtering Fail

29:16 FL - Frame Length

15

14 DE - Descriptor Error. The frame is truncated. Active high.

13:12 Reserved.--Written as “0” for future compatibility concern.

11 RF - Runt Frame. Indicates that this frame is a runt frame. Active high.

The AX88140A clears this bit either when it completes

the frame reception or

when the buffers that are associated with this descriptor

are full.

This bit can be set only when receive all (REG6<30>) is

set.

Indicates the length in bytes of the received frame including the cyclic redundancy check (CRC).

This field is valid only when last descriptor (RDES0<8>) is set and descriptor error ( RDES0<14>) is reset.

ES - Error Summary

Indicates the logical OR of the following RDES0 bits :

This field is valid only when last descriptor (RDES0<8>) is set.

RDES0<1> CRC error

RDES0<6> collision seen

RDES0<7> frame too long

RDES0<11> runt frame

RDES0<14> descriptor error

This field is valid only when last descriptor (RDES0<8>) is set.

This field is valid only when last descriptor (RDES0<8>) is set .

1 Indicates that the descriptor is owned by the

AX88140A

0 Indicates that the descriptor is owned by the host

1 Indicates that the frame failed the address

recognition filtering

0 Indicates that the frame passed the address

recognition filtering

31

ASIX ELECTRONICS CORPORATION

Page 32

AX88140A PRELIMINARY

10 MF - Multicast Frame Indicates that this frame is a multicast address.

This field is valid only when last descriptor (RDES0<8>) is set.

9 FS - First Descriptor

8 LS - Last Descriptor

7 TL - Frame Too Long. Frame length grater then 1518 bytes. Active high.

This field is valid only when last descriptor (RDES0<8>) is set.

6 CS - Collision Seen. This is a late collision.

This field is valid only when last descriptor (RDES0<8>) is set.

5 Reserved.--Written as “0” for future compatibility concern.

4 RW - Receive Watchdog time expire. Active high.

This field is valid only when last descriptor (RDES0<8>) is set.

3 RE - Report on MII Error. Active high.

2 DB - Dribbling Bit Active high.

If set, and CRC error (RDES0<1>) is reset, then the packet is valid.

1 CE - CRC Error. Active high.

This field is valid only when last descriptor (RDES0<8>) is set.

0 FIFO Overrun. Active high.

1 Indicates that this descriptor contains the first buffer of a

frame.

0 Indicates that this descriptor is the middle or last buffer of

a frame.

1 Indicates that the buffers pointed to by this descriptor, are

the last buffers

0 Indicates that this descriptor is the middle or first buffer of

a frame.

Tab - 32 Receive Descriptor 0

5.2.2 Receive Descriptor 1 (RDES1)

FIELD DESCRIPTION

31:11 Reserved.--Written as “0” for future compatibility concern.

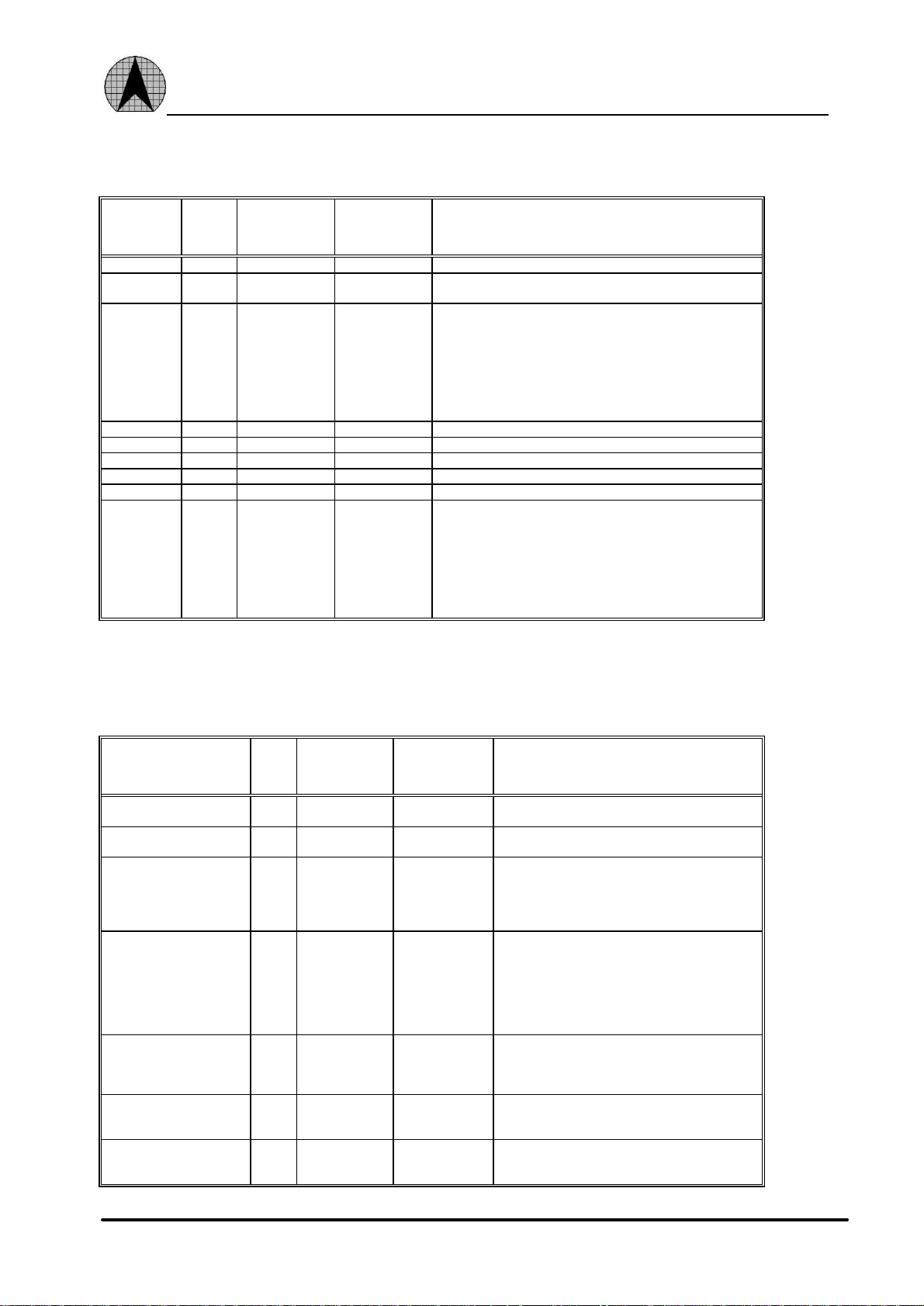

10:0 RBS - Receive Data Buffer Size