Page 1

1

AX84110 L

ASIX Electronics Corp

Preliminary

USB2.0 to Local CPU Bus controller

Document No.: AX84110 / V0.0 / Dec. 16 ’02

Features:

n Compliant with USB specification

1.0, 1.1 and 2.0

n Support both 8 bit and 16 bit local

CPU Interfaces include MCS-51

series, 80186 series, MC68K series

CPU, ISA Bus and PCMCIA Bus

n Capability Full/High Speed USB

Device with bus power

n Support 4 endpoints on USB and 4

General Purpose In/Out pins

n Embedded 2K*16 bit SRAM

n 128-pin LQFP low profile package

n Support suspended mode and

remote wakeup

n Single 12MHz clock input, pure

3.3V operation with 5V I/O

tolerance

n Support (93c56/93c66) 256/512

bytes serial EEPROM (used for

saving USB Descriptors)

n Support 4 set of status change reply

n Support automatic loading of

application device, from

application device USB Descriptors

and Adapter Configuration from

EEPROM when power-on

initialization

Product description

The AX84110 USB2.0 to Local CPU Bus controller is a high performance and with embedded 2K*16

SRAM and compliant with USB Standard V1.0, V1.1 and V2.0. The AX84110 supports Full/High

Speed USB device with bus power capability and supports both 8 bit and 16 bit local CPU interfaces

include MCS-51 series, 80186 series, MC68K series CPU and ISA Bus and PCMCIA Bus.

AX84110

EEPROM

Compliant with CPU Bus application

device as 8051,80186,68K,ISA,PCMCIA

USB bus

Page 2

2

AX84110 L

ASIX Electronics Corp

Preliminary

Always contact ASIX for possible updates before starting a design.

This data sheet contains new products information. ASIX ELECTRONICS reserves the rights to modify the product specification without notice.

No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

Page 3

3

AX84110 L

ASIX Electronics Corp

Preliminary

Contents

1.0Introduction...................................................................................................4

1.1General Description.............................................................................4

1.2AX84110 Block Diagram .....................................................................4

1.3AX84110 Pin Connection Diagram......................................................5

2.0 Signal Description......................................................................................10

3.0 EEPROM Memory Mapping ......................................................................13

4.0 USB Commands.........................................................................................14

4.1 USB standard commands .................................................................14

4.2 USB Vendor commands.................................................................... 15

4.3 USB Vendor and Normal commands format................................... 17

5.0 USB Configuration Structure...................................................................... 18

5.1 USB Configuration............................................................................ 18

5.2 USB Interface.................................................................................... 18

5.3 USB Endpoints..................................................................................18

6.0 Basic Operation.......................................................................................... 19

6.1 Process Flow...................................................................................... 19

6.2 Packet Format Character.................................................................21

7.0 CPU & Device Access Functions ................................................................27

7.1 PCMCIA bus type access functions.................................................. 27

7.2 ISA bus type access functions...........................................................28

7.3 80186 CPU bus type access functions............................................... 29

7.4 68000 CPU bus type access functions............................................... 30

7.5 8051 CPU bus type access functions.................................................31

8.0 Electrical Specification and Timing ............................................................32

8.1 Absolute Maximum Ratings............................................................. 32

8.2 General Operation Conditions .........................................................32

8.3 D.C. Characteristics..........................................................................32

8.4 A.C. Timing Characteristics.............................................................33

9.0 Package information...................................................................................47

10.0 Reference design (PCMCIA to USB)........................................................49

Page 4

4

AX84110 L

ASIX Electronics Corp

Preliminary

1.0Introduction

1.1General Description

The AX84110 USB2.0 to Local CPU Bus controller is a high performance and with embedded 2K*16

SRAM. The AX84110 supported Full/High Speed USB device with bus power capability and supports

both 8 bit and 16bit local CPU interface include MCS-51 series,80186 series,MC68K series CPU and

ISA Bus and PCMCIA Bus. The Chip also support up to 4 additional General Purpose In/Out pins and

receive 4 set of status change from application device.

AX84110 use 128-pin LQFP low profile package, 12MHz operation for USB and CMOS process with

pure 3.3V operation with 5V i/o tolerance.

1.2AX84110 Block Diagram

8 Bit or 16 Bit local

CPU Interface Bus General I/O

EECS

EECK

EEDI

EEDO

DM/DP

Fig-1 AX84110 Block Diagram

USB Core and Interface

SEEPROM

Loader I/F

USB to Local CPU

Bus Bridge

GPIO

2K*16 SRAM

and Memory

Arbiter

Page 5

5

AX84110 L

ASIX Electronics Corp

Preliminary

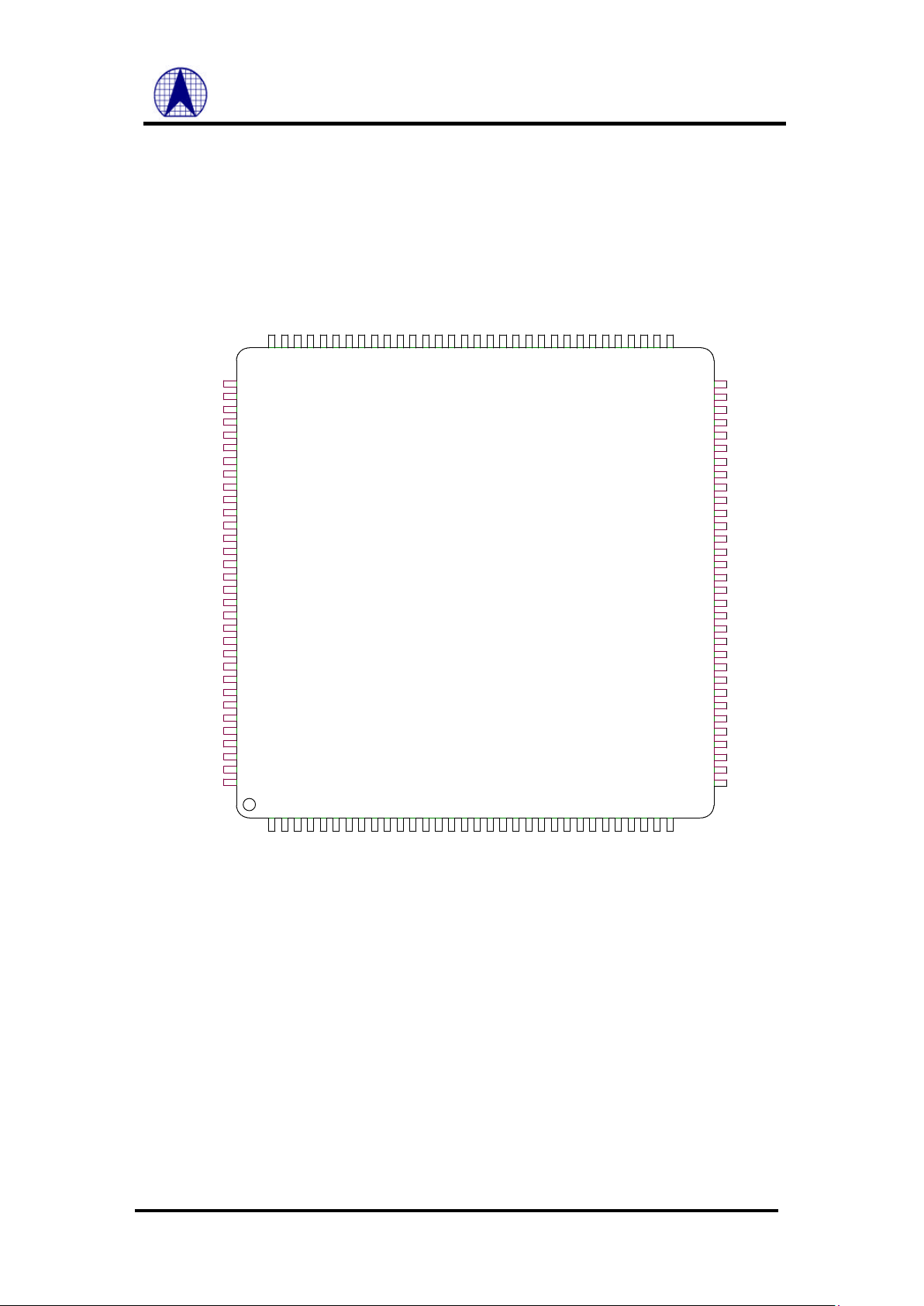

1.3AX84110 Pin Connection Diagram

1.3.1 AX84110 Pin Connection Diagram for PCMCIA Mode

NC

VSS

EECK

EEDO

NC

SD[7]

EEDI

SD[1]

SD[10]

SD[11]

SD[6]

NC

NC

SD[12]

SD[3]

128

SD[0]

NC

VSS

VDD

SD[8]

VDD

19

78

5

18

126

38

89

22

107

65

82

23

10

68

45

13

20

60

SA[0]

103

SA[8]

3

15

SD[15]

SA[4]

VDD

VDD

32

SA[13]

SA[7]

STSCHG3

STSCHG2

8

SA[15]

SA[3]

SA[11]

SA[5]

88

100

WAIT

55

48

SD[13]

REG#

STSCHG1

SA[14]

SA[1]

SA[10]

VSS

SA[2]

RESETP

SD[14]

STSCHG4

NC

17

VDD

SA[6]

VSS

VDD

91

VSS

117

72

SA[9]

59

LED

VDD

VDD

VSS

PVDD

GPIO3

GPIO0

PVSS

PVSS

IOIS16#

NC

ANA_XIQ

VSS

PVDD

VDD

GPIO1

RESET

64

14

21

83

58

25

2

66

43

123

94

27

74

112

40

12

127

102

124

108

46

86

109

36

111

4

56

26

16

69

54

49

114

98

79

90

53

30

75

115

118

47

7

9

95

37

28

67

92

105

101

104

119

29

62

34

71

125

24

11

63

51

97

87

116

76

GPIO2

42

122

110

CLKI

50

TESTMODE

39

44

85

31

41

57

52

93

121

35

106

6

81

33

99

96

73

77

1

80

84

113

120

70

61

SA[12]

IREQ

WE#

IOWR#

OE#

IORD#

VDD

XOUT12M

VSS

CE2#

CE1#

VDD

AX84110

(for PCMCIA Bus I/F)

VDD

DP

FORCEFS

R1

DM

NC

NC

VSS

NC

VBUS

AVDD

NC

TEST1

NC

VSS

NC

AVSS

NC

NC

AVSS

VC

NC

NC

VDD

TEST0

EECS

AVDD

NC

AVSSNCAVSS

NC

EPTEST

XIN12M

VDD

NC

SD[5]

SD[4]

SD[2]

SD[9]

NC

Fig-2 AX84110 Pin Connection Diagram for PCMCIA Bus Mode

* Pin 12 is EXTWAKEUP

Page 6

6

AX84110 L

ASIX Electronics Corp

Preliminary

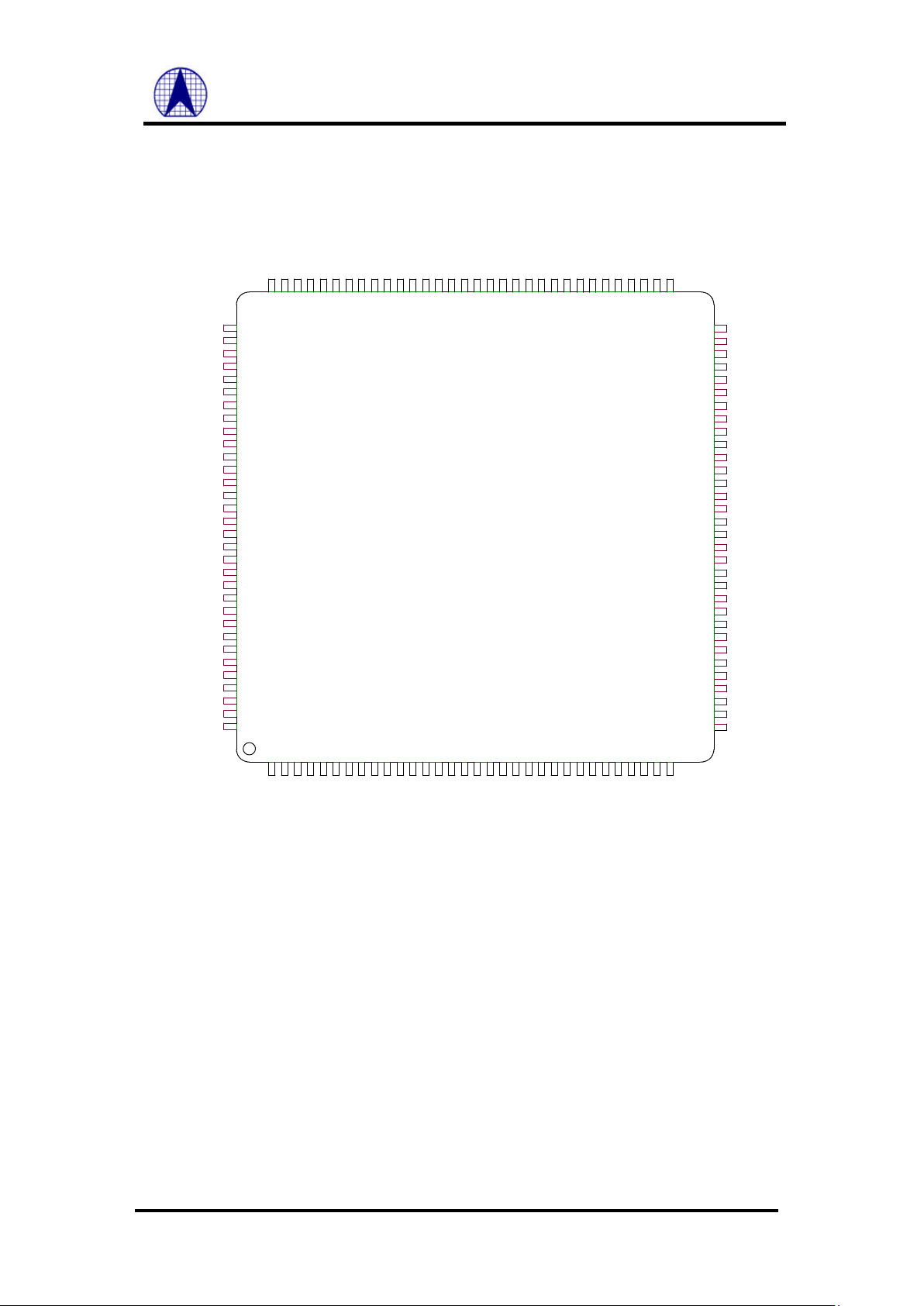

1.3.2 AX84110 Pin Connection Diagram for ISA Mode

VSS

NC

EECK

NC

EEDO

EEDI

SD[7]

SD[1]

SD[11]

SD[10]

SD[6]

NC

NC

128

SD[3]

SD[12]

SD[0]

VDD

VSS

NC

VDD

SD[8]

197818

5

126

89

38

22

65

107

82

10

23

45

68

13

20

60

103

SA[0]

15

3

SA[8]

SD[15]

SA[4]

32

VDD

VDD

SA[13]

SA[7]

STSCHG3

8

STSCHG2

SA[15]

SA[11]

SA[3]

100

88

SA[5]

48

55

RDY

CS#

SD[13]

STSCHG1

SA[14]

SA[10]

SA[1]

SA[2]

VSS

RESETP

STSCHG4

SD[14]

17

AEN

SA[6]

VDD

91

VDD

VSS

72

117

VSS

SA[9]

59

LED

VDD

VDD

PVDD

VSS

GPIO0

GPIO3

PVSS

PVSS

ANA_XIQ

NC

IOIS16#

VSS

VDD

PVDD

GPIO1

64

RESET

14

83

21

58

25

2

43

66

123

94

27

74

112

40

12

127

102

124

108

46

86

36

109

111

56

4

16

26

69

49

54

98

114

79

90

30

53

75

115

118

47

7959

37

28

92

67

105

101

104

29

119

34

62

125

71

11

24

97

51

63

87

116

76

42

GPIO2

122

110

50

CLKI

39

TESTMODE

85

44

31

57

41

93

52

121

35

106

81

6

33

99

96

73

1

77

84

80

113

120

61

70

SA[12]

IREQ

MEMW#

IOWR#

MEMR#

IORD#

VDD

XOUT12M

VSS

NC

BHE#

VDD

AX84110

(for ISA Bus I/F)

VDD

DP

FORCEFS

R1

DM

NC

NC

VSS

VBUS

NC

NC

AVDD

TEST1

NC

VSS

NC

AVSS

NC

NC

AVSS

VC

NC

NC

VDD

TEST0

EECS

NC

AVDD

AVSS

NC

NC

AVSS

EPTEST

XIN12M

VDD

NC

SD[5]

SD[9]

SD[2]

SD[4]

NC

Fig-3 AX84110 Pin Connection Diagram for ISA Bus Mode

* Pin 12 is EXTWAKEUP

Page 7

7

AX84110 L

ASIX Electronics Corp

Preliminary

1.3.3 AX84110 Pin Connection Diagram for 80x86 Mode

NC

VSS

EEDO

NC

EECK

SD[1]

SD[7]

EEDI

SD[10]

SD[11]

NC

NC

SD[6]

SD[12]

SD[3]

128

SD[0]

NC

VSS

VDD

SD[8]

VDD

197818

126

5

38

89

22

65

107

10

82

45

23

13

68

60

20

103

15

SA[0]

3

SA[8]

SA[4]

SD[15]

VDD

32

VDD

SA[13]

SA[7]

STSCHG3

8

STSCHG2

SA[15]

SA[11]

100

SA[3]

88

55

48

SA[5]

RDY

SD[13]

CS#

STSCHG1

SA[14]

SA[1]

SA[10]

VSS

SA[2]

RESETP

STSCHG4

17

SD[14]

NC

SA[6]

VDD

91

VSS

VDD

117

72

VSS

SA[9]

59

LED

VDD

VDD

PVDD

VSS

GPIO3

GPIO0

PVSS

PVSS

NC

ANA_XIQ

NC

VSS

VDD

PVDD

GPIO1

RESET

64

14

21

83

58

25

2

66

43

123

94

74

27

112

40

12

127

102

124

108

46

86

111

109

36

4

56

26

16

69

49

54

98

79

114

90

53

30

75

115

118

7479

95

28

37

92

67

105

101

104

119

29

62

34

125

71

11

24

51

97

63

87

116

76

GPIO2

42

122

110

50

TESTMODE

39

CLKI

44

85

31

57

41

93

121

52

35

106

81

6

33

99

96

73

1

77

84

113

80

61

120

70

SA[12]

IREQ

IOWR#

MEMW#

MEMR#

XOUT12M

VDD

IORD#

VSS

BHE#

NC

(for x86 Interface)

AX84110

VDD

VDD

FORCEFS

DP

DM

R1

NC

VSS

NC

VBUS

NC

NC

TEST1

AVDD

NC

NC

VSS

AVSS

NC

NC

VC

AVSS

NC

NC

VDD

EECS

TEST0

AVDD

NC

NC

AVSS

AVSS

NC

XIN12M

EPTEST

VDD

NC

SD[2]

SD[9]

SD[5]

NC

SD[4]

Fig-4 AX84110 Pin Connection Diagram for 80x86 Mode

* Pin 12 is EXTWAKEUP

Page 8

8

AX84110 L

ASIX Electronics Corp

Preliminary

1.3.4 AX84110 Pin Connection Diagram for MC68K Mode

101

104

119

29

62

34

125

71

11

24

51

97

63

87

116

76

GPIO2

42

122

110

50

TESTMODE

39

CLKI

44

85

31

57

41

93

121

52

35

106

81

6

33

99

96

73

1

77

84

113

80

61

120

70

SA[12]

IREQ

R/W#NCNC

XOUT12M

VDD

NC

VSS

UDS#

NC

(for 68K Interface)

AX84110

VDD

VDD

FORCEFS

DP

DM

R1

NC

VSS

NC

VBUS

NC

NC

TEST1

AVDD

NC

NC

VSS

AVSS

NC

NC

VC

AVSS

NC

NC

VDD

EECS

TEST0

AVDD

NC

NC

AVSS

AVSS

NC

XIN12M

EPTEST

NC

VDD

SD[2]

SD[9]

SD[5]

NC

SD[4]

NC

VSS

EEDO

NC

EECK

SD[1]

SD[7]

EEDI

SD[10]

SD[11]

NC

NC

SD[6]

SD[12]

SD[3]

128

SD[0]

NC

VSS

VDD

SD[8]

VDD

197818

126

5

38

89

22

65

107

10

82

45

23

13

68

60

20

103

15

LDS#

3

SA[8]

SA[4]

SD[15]

VDD

32

VDD

SA[13]

SA[7]

STSCHG3

8

STSCHG2

SA[15]

SA[11]

100

SA[3]

88

55

48

SA[5]

DTACK#

SD[13]

CS#

STSCHG1

SA[14]

SA[1]

SA[10]

VSS

SA[2]

RESETP

STSCHG4

17

SD[14]

NC

SA[6]

VDD

91

VSS

VDD

117

72

VSS

SA[9]

59

LED

VDD

VDD

PVDD

VSS

GPIO3

GPIO0

PVSS

PVSS

NC

ANA_XIQ

NC

VSS

VDD

PVDD

GPIO1

RESET

64

14

21

83

58

25

2

66

43

123

94

74

27

112

40

12

127

102

124

108

46

86

111

109

36

4

56

26

16

69

49

54

98

79

114

90

53

30

75

115

118

7479

95

28

37

92

67

105

Fig-5 AX84110 Pin Connection Diagram for MC68K Mode

* Pin 12 is EXTWAKEUP

Page 9

9

AX84110 L

ASIX Electronics Corp

Preliminary

1.3.5 AX84110 Pin Connection Diagram for MCS-51 Mode

111

109

36

4

56

26

16

69

49

54

98

79

114

90

53

30

75

115

118

7479

95

28

37

92

67

105

101

104

119

29

34

62

125

71

24

11

97

63

51

87

116

76

42

GPIO2

122

110

39

CLKI

50

TESTMODE

44

85

31

41

57

121

52

93

35

106

81

6

33

96

99

73

77

1

84

113

80

120

70

61

IREQ

SA[12]

MEMW#

MEMR#

IOWR#

VDD

IORD#

VSS

XOUT12M

NC

AX84110

VDD

NC

VDD

(for 8051 Interface)

DP

R1

FORCEFS

NC

DM

NC

VBUS

VSS

NC

AVDD

NC

NC

TEST1

VSS

AVSS

NC

NC

AVSS

NC

NC

VC

VDD

NC

EECS

TEST0

NC

AVDD

AVSS

NC

NC

AVSS

EPTEST

VDD

XIN12M

SD[9]

SD[5]

NC

NC

SD[4]

SD[2]

NC

VSS

EEDO

NC

EECK

SD[1]

SD[7]

EEDI

SD[10]

SD[11]

NC

NC

SD[6]

SD[12]

SD[3]

128

SD[0]

NC

VSS

VDD

SD[8]

VDD

197818

126

5

38

89

22

65

107

10

82

45

23

13

68

60

20

103

15

SA[0]

3

SA[8]

SA[4]

SD[15]

VDD

32

VDD

SA[13]

SA[7]

STSCHG3

8

STSCHG2

SA[15]

SA[11]

100

SA[3]

88

55

48

SA[5]

RDY

SD[13]

CS#

STSCHG1

SA[14]

SA[1]

SA[10]

VSS

SA[2]

RESETP

STSCHG4

17

SD[14]

PSEN#

SA[6]

VDD

91

VSS

VDD

117

72

VSS

SA[9]

59

LED

VDD

VDD

PVDD

VSS

GPIO3

GPIO0

PVSS

PVSS

NC

ANA_XIQ

NC

VSS

VDD

PVDD

GPIO1

RESET

64

14

21

83

58

25

2

66

43

123

94

74

27

112

40

12

127

102

124

108

46

86

Fig-6 AX84110 Pin Connection Diagram for MCS-51 Mode

* Pin 12 is EXTWAKEUP

Page 10

10

AX84110 L

ASIX Electronics Corp

Preliminary

2.0 Signal Description

The following terms describe the AX84110 pin-out:

All pin names with the “#” suffix are asserted low.

The following abbreviations are used in following Tables.

I Input PU Internal Pull Up (100K)

O Output PD Internal Pull Down (100K)

I/O Input/Output P Power Pin

OD Open Drain F Failsafe

SIGNAL TYPE PIN NO. DESCRIPTION

NC 1 No Connection

NC 2 No Connection

R1 I 3 Constant-voltage pin

A 6.2K¡Ó

1% resistors is connected to AVSS. Be sure to make

the line between R1 and each resistor as short as possible.

AVDD P 4 Power supply pin for analog circuits +3.3V DC

AVSS P 5 Power supply pin for analog circuits Ground

AVSS P 6 Power supply pin for analog circuits Ground

DP B 7 USB data line Data+

AVSS P 8 Power supply pin for analog circuits Ground

DM B 9

USB data line DataAVSS P 10 Power supply pin for analog circuits Ground

AVDD P 11 Power supply pin for analog circuits +3.3V DC

EXTWAKEUP I/PD 12 Remote-wakeup trigger from external pin. It active high and

should be keep high over 2 clocks (12Mhz).

VBUS I/PD 13 Usb Cable Power supply pin

NC I/PD 14 For testing

VDD P 15 Power supply pin for logic circuits +3.3V DC

NC O 16 For testing

NC O 17 For testing

FORCEFS I/PD 18 When the pin is set, it must be force to work on full speed mode.

NC I/PD 19 For testing

VSS P 20 Power supply +0V DC or Ground Power

TEST1 I/PU 21 Test Pin: This pin for test purpose only

Pull up the pin or keep no connection for normal operation

TEST0 I/PU 22 Test Pin: This pin for test purpose only

Pull up the pin or keep no connection for normal operation

VDD P 23 Power supply pin for logic circuits +3.3V DC

NC O 24 For testing

NC O 25 For testing

NC O 26 For testing

NC O 27 For testing

NC O 28 For testing

NC O 29 For testing

NC O 30 For testing

NC O 31 For testing

VSS P 32 Power supply +0V DC or Ground Power

VDD P 33 Power supply pin for logic circuits +3.3V DC

EECS O 34 EEPROM Chip Select Signal

Page 11

11

AX84110 L

ASIX Electronics Corp

Preliminary

EECK O 35 EEPROM Clock connected to EEPROM clock pin

EEDI O 36 EEPROM Data In :Signal connected EEPROM data input pin

EEDO I/PD 37 EEPROM Data Out :Signal connected EEPROM data output pin

NC I/PD 38 For testing

NC I/PD 39 For testing

NC I/PD 40 For testing

NC I/PD 41 For testing

NC I/PD 42 For testing

NC I/PD 43 For testing

VDD P 44 Power supply pin for logic circuits +3.3V DC

VSS P 45 Power supply +0V DC or Ground Power

SD[15:0] I/O/F 63-56

53-46

System Data Bus: Signal SD[15:0] constitute the bi-directional

data bus.

VDD P 54 Power supply pin for logic circuits +3.3V DC

VSS P 55 Power supply +0V DC or Ground Power

VDD P 64 Power supply pin for logic circuits +3.3V DC

VSS P 65 Power supply +0V DC or Ground Power

CE1# O 66 Card Enable: The CE1# enables even numbered address bytes

CE2# or BHE#

or UDS#

O 67

Card Enable: The CE2# enables odd numbered address bytes for

pcmcia mode.

Bus High Enable: Bus High Enable is active low signal in some

16-bit application mode.

Upper Data Strobe: The signal also name Upper Data Strobe

(/UDS) for 68K application mode.

OE# or MEMR# O 68 Output Enable or Memory Read: The signal is low active for

Memory Read.

IORD# O 69 I/O Read: The signal is low active for I/O Read.

IOWR# O 70 I/O Write: The signal is low active for I/O Write.

WE# or

MEMW#

O 71 Write Enable or Memory Write: The signal is low active for

Memory Write.

IREQ or IREQ# I/PU/F 72 Interrupt Request: IREQ or IREQ# user can define high or low

activ

e. When the IREQ or IREQ# is asserted to indicate the host

system that the application device requires host software service.

VSS P 73 Power supply +0V DC or Ground Power

VDD P 74 Power supply pin for logic circuits +3.3V DC

SA[15:1] ,SA[0]

or LDS#

O 75-82

85-92

System Address: Signal SA[15:0] IO address decoding for up to

64 Kbyte.

SA[0] also means Lower Data Strobe (LDS#) active low signal

in 68K application mode.

VSS P 83 Power supply +0V DC or Ground Power

VDD P 84 Power supply pin for logic circuits +3.3V DC

RESETP or

RESETP#

O 93 RESET: RESETP or RESETP# user can define high or low

active.

WAIT or WAIT#

or RDY or

DTACK#

I/PU/F 94 Wait: WAIT or WAIT # user can define high or low active.

This signal is set active, it insert wait state states

during Remote

DMA transfer.

Ready: as the above same

Dtack#: as above same for Motorola CPU, the pin is active

inform that application device data is accepted.

AEN or PSEN# O 95 Address Enable: The signal is asserted when the address bus is

available for DMA cycle.

PSEN: The signal is active low for 8051program access.

VDD P 96 Power supply pin for logic circuits +3.3V DC

VSS P 97 Power supply +0V DC or Ground Power

REG# or CS# O 98

Attribute Memory and I/O Space Select: When the REG# signal

is asserted, access is limited to Attribute Memory and to the I/O

space (only for PCMCIA mode).

Page 12

12

AX84110 L

ASIX Electronics Corp

Preliminary

Chip Select:When the CS# is asserted, the application is

selected.

STSCHG1 I/PD 99 Status Change: reply application device status to Host

STSCHG2 I/PD 100 Status Change: reply application device status to Host

STSCHG3 I/PD 101 Status Change: reply application device status to Host

STSCHG4 I/PD 102 Status Change: reply application device status to Host

IOIS16# I/PU/F 103 I/O is 16 Bit Port: The IOIS16# is asserted and I/O port

addressed is capable of 16-bit access.

VDD P 104 Power supply pin for logic circuits +3.3V DC

LED O 105 LED indicator: When link FS, drives logic high always. When

link HS, the pin drives logic low and it will drives high/low a

period when line has activity (data transfer).

NC I/PD 106 For testing

GPIO[3:0] I/O/PU 110-107 General Purpose Input / Output Pins.

VDD P 111 Power supply pin for logic circuits +3.3V DC

ANA_XIQ I 112 Sets the IQ mode

This pin is used during testing. It must be set to low in IQ

measurement mode.

0: IQ mode

1: Normal operation mode

VDD P 113 Power supply pin for logic circuits +3.3V DC

CLKI I/PD 114 For testing

TESTMODE I/PD 115 For testing (TESTMODE)

0: Normal operation mode

1: External clock Synchronization mode

RESET I 116

When assert, place AX84110 into reset mode immediately. Reset

complete loads the EEPROM data.

VSS P 117 Power supply +0V DC or Ground Power

VSS P 118 Power supply +0V DC or Ground Power

VDD P 119 Power supply pin for logic circuits +3.3V DC

VDD P 120 Power supply pin for logic circuits +3.3V DC

PVDD P 121 Power supply pin for PLL and oscillator circuits +3.3V DC

PVDD P 122 Power supply pin for PLL and oscillator circuits +3.3V DC

PVSS P 123 Power supply pin for PLL and oscillator circuits +0V DC or

Ground Power

PVSS P 124 Power supply pin for PLL and oscillator circuits +0V DC or

Ground Power

VC I 125 Monitor pin for two PLL charge pumps

Connect to GND on PCB when actually using

PTEST I 126 Charge pump monitor ON/OFF:

Connect to GND on PCB when actually using

XIN12M I 127 12M crystal oscillator input

XOUT12M O 128 12M crystal oscillator output

Tab-1 PIN signals

Page 13

13

AX84110 L

ASIX Electronics Corp

Preliminary

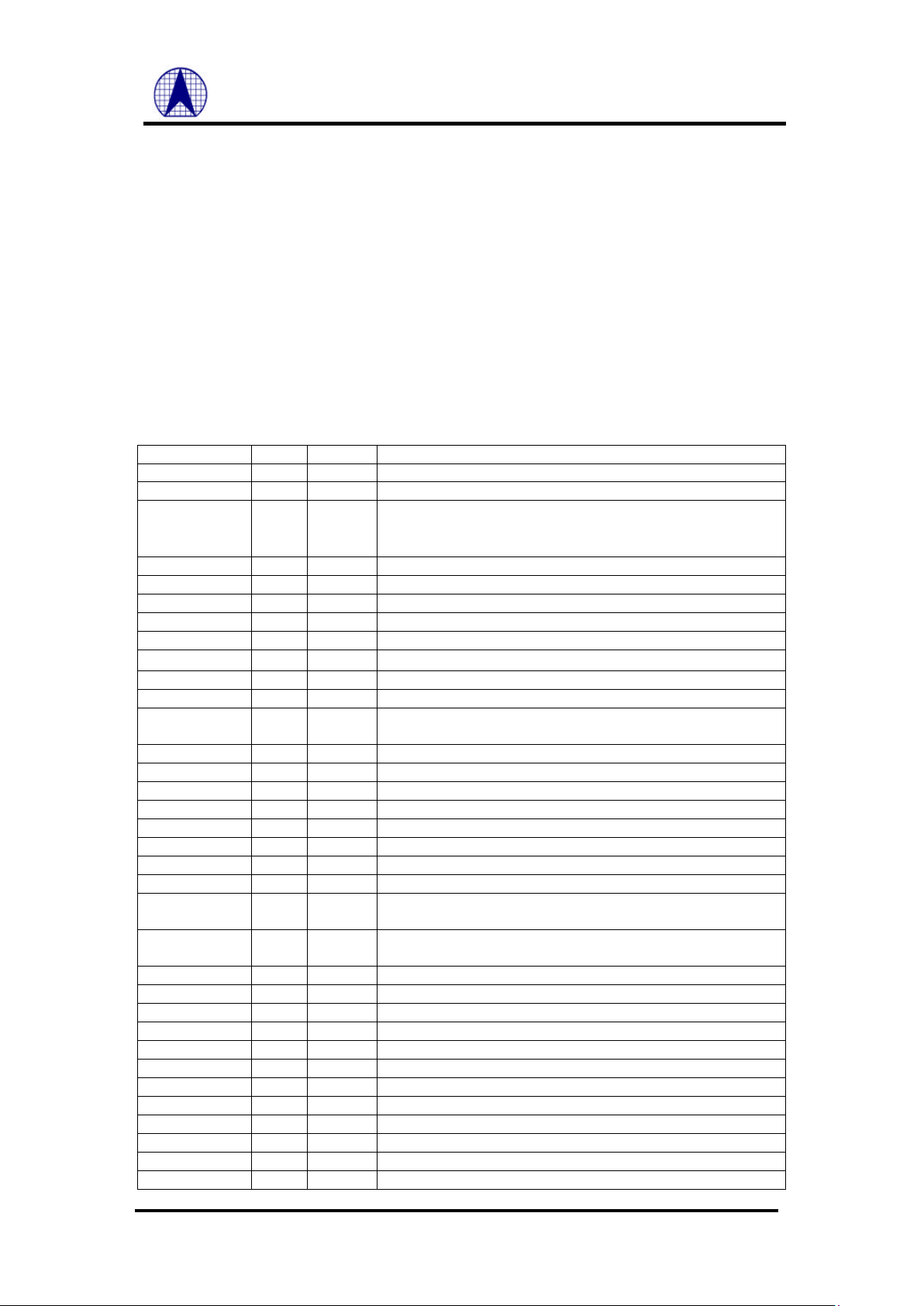

3.0 EEPROM Memory Mapping

EEPROM

OFFSET

HIGH BYTE LOW BYTE

00H RESERVED WORD COUNT FOR PRELOAD

01H *FLAG

02H HIGH-SPEED LENGTH OF DEVICE

DESCRIPTOR(BYTE)

HIGH-SPEED EEPROM OF DEVICE

DESCRIPTOR

03H HIGH-SPEED LENGTH OF

CONFIGURATION

DESCRIPTOR(BYTE)

HIGH-SPEED EEPROM OF

CONFIGURATION DESCRIPTOR

04H RESERVED RESERVED

05H RESERVED RESERVED

06H RESERVED RESERVED

07H LANGUAGE ID HIGH BYTE LANGUAGE ID LOW BYTE

08H LENGTH OF STRING INDEX 1 EEPROM OFFSET OF STRING INDEX 1

09H LENGTH OF STRING INDEX 2 EEPROM OFFSET OF STRING INDEX 2

0AH LENGTH OF STRING INDEX 3 EEPROM OFFSET OF STRING INDEX 3

0BH LENGTH OF STRING INDEX 4 EEPROM OFFSET OF STRING INDEX 4

0CH LENGTH OF STRING INDEX 5 EEPROM OFFSET OF STRING INDEX 5

0DH LENGTH OF STRING INDEX 6 EEPROM OFFSET OF STRING INDEX 6

0EH LENGTH OF STRING INDEX 7 EEPROM OFFSET OF STRING INDEX 7

0FH RESERVED RESERVED

10H RESERVED RESERVED

11H RESERVED RESERVED

12H RESERVED RESERVED

13H FULL-SPEED LENGTH OF DEVICE

DESCRIPTOR(BYTE)

FULL-SPEED EEPROM OF DEVICE

DESCRIPTOR

14H FULL-SPEED LENGTH OF

CONFIGURATION

DESCRIPTOR(BYTE)

FULL-SPEED EEPROM OF

CONFIGURATION DESCRIPTOR

15H-1FH

RESERVED RESERVED

Tab-2 EEPROM Memory Mapping

Note:

*FLAG:

n Bit0 è Self Power (for USB GetStatus) 1:self power ; 0: bus power

n Bit1 è Reserved

n Bit2 è Remote WakeUP support

n Bit3 è 1

n Bit4-6 è Reserved

n Bit7 è Force Full speed enable ; 1:force full speed 0:not enable

n Bit8 è Set Reset active value ; 1:Reset active high ; 0: Reset active low

n Bit9-F è Reserved

Page 14

14

AX84110 L

ASIX Electronics Corp

Preliminary

4.0 USB Commands

There are three command groups for endpoint0 in AX84110

l The USB standard commands

l USB Communication Class commands

l USB vendor commands

4.1 USB standard commands

l The Language ID is 0x0904 for English

l PPLL means buffer length

l CC means configuration number

l I I means Interface number

SETUP COMMAND DATA IN/OUT DESCRIPTION

80 06 00 01 00 00 LL PP Data PPLL bytes Get Device Descriptor

80 06 00 02 00 00 LL PP Data PPLL bytes Get Configuration Descriptor

80 06 00 03 00 00 LL PP Data 2 bytes Get Supported Language ID

80 06 00 03 09 04 LL PP Data PPLL bytes Get Manufacture String

80 06 00 03 09 04 LL PP Data PPLL bytes Get Product String

80 06 00 03 09 04 LL PP Data PPLL bytes Get Serial Number String

80 06 00 03 09 04 LL PP Data PPLL bytes Get Configuration String

80 06 00 03 09 04 LL PP Data PPLL bytes Get Interface 0 String

80 06 00 03 09 04 LL PP Data PPLL bytes Get Interface 1/0 String

80 06 00 03 09 04 LL PP Data PPLL bytes Get Interface 1/1 String

80 08 00 00 00 00 01 00 Data 1 bytes Get Configuration

00 09 CC 00 00 00 00 00 No Data Set Configuration

81 0A 00 00 I I 00 01 00 Data 1 byte Get Interface

01 0B AS 00 00 00 00 00 No Data Set Interface

Tab-3 USB Standard commands

Page 15

15

AX84110 L

ASIX Electronics Corp

Preliminary

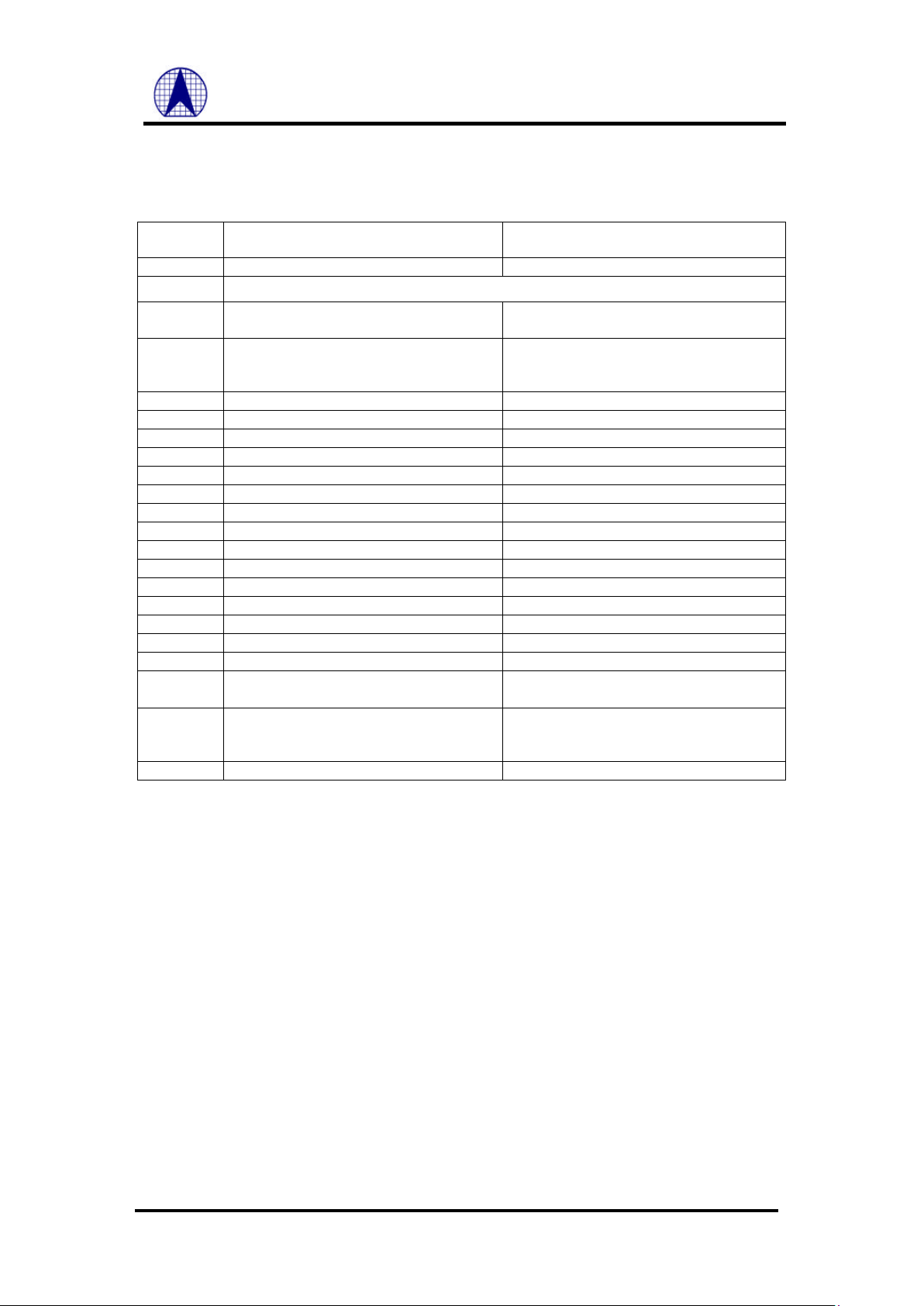

4.2 USB Vendor commands

SETUP COMMAND DATA IN/OUT DESCRIPTOR

40 80 0X 00 RR RR 00 00 No Data Set Interface Register (1)

40 81 0X 00 RR RR 00 00 No Data Set Interface Register (2)

40 82 0X 00 RR RR 00 00 No Data Set Interface Register (3)

40 83 0X 00 RR RR 00 00 No Data Set Interface Register (4)

40 84 IO I I 00 00 00 00 No Data Set IO Data Port for OUT/IN

40 85 GP 00 00 00 00 00 No Data Set Write GPIOs(***)

40 86 BC BC 00 00 00 00 No Data Set Byte Count

40 87 TC 00 00 00 00 00 No Data Set Data Access Timing Cycle

40 89 0Z 00 AA AA 00 00 No Data Set IO or Memory address Function mode

C0 8A 00 00 00 00 01 00 Data 1 Bytes Set Read GPIOs(***)

C0 8B DR 00 00 00 02 00 Data 2 Bytes Read SROM

40 8C DR 00 MM SS 00 00 No Data Write SROM

40 8D 00 00 00 00 00 00 No Data Write SROM Enable

40 8E 00 00 00 00 00 00 No Data Write SROM Disable

40 8F YY 00 00 00 00 00 No Data Set Other Vaule

Tab-4 USB Vendor commands

Page 16

16

AX84110 L

ASIX Electronics Corp

Preliminary

X:

n Bit0 è 1: Service Vaild ; 0: No Service

n Bit1 è 1: Byte Valid ; 0: Word Valid

n Bit2 è 1: Memory Area ; 0: I/O Area

n Bit3 è Reserved

Y:

n Bit0 è 1: Set EEPROM reload trigger

n Bit1 è 1: Wait high active; 0: low active

n Bit2 è 1: Ireq high active; 0: low active

n Bit3 è 1: Set Reset (default Value com from EEPROM Autoload)

n Bit7 Bit6 Bit5 Bit4

x 0 0 0 è PCMCIA BUS mode

x 1 0 0 è ISA BUS mode

T 0 0 1 è 80186 CPU mode

T 0 1 0 è 68000 CPU mode

T 0 1 1 è 8051CPU mode

T: 1: byte mode transmit/receive (only for CPU mode) x: don’t care

0: word mode transmit/receive (only for CPU mode)

Z:

Bit3 Bit2 Bit1 Bit0

x F 0 0 for I/O device

x M 0 1 Attribute memory

x M 1 0 Common memory

F: 1 support fixed port 0: not support x: don’t care

When work on Memory (only for PCMCIA or ISA Bus mode), user can define byte

/word mode transmitting or receiving via set this bit. M:1 byte mode 0:word mode.

In CPU mode (as x86 or 68K or 51) must be set on xx01 (Attribute memory) as work on

Memory mode and this M will be don’t care because set T.

RR Int register offset address (user can set the address and it is absolute address)

I I Set IO Data Port In address (user can set I/O device data port by receiving)

IO Set IO Data Port Out address (user can set I/O device data port by transmitting)

BC Set Byte Count (user can set byte count of byte number for receiving)

TC Set Access Timing Cycle (min 3) (user can set read/write signal active timing of period)

AA Set IO Base or Memory (absolute address)

*** Read / Write GPIO

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

Read GPI3 X GPI2 X GPI1 X GPI0 X

Write GPO3 GPO3EN GPO2 GPO2EN GPO1 GPO1EN GPO0 GPO0EN

Page 17

17

AX84110 L

ASIX Electronics Corp

Preliminary

4.3 USB Vendor and Normal commands format

SETUP COMMAND

DATA IN/OUT DESCRIPTION

Application device internal register Normal Command & USB Vendor Command Register

C0 AD1 DR 00 00 00 02 00 Data 2 Bytes Usb Vendor Command Read

ref Tab-4 Read SROM

40 AD1 DR 00 MM SS 00 00 No Data Usb Vendor Command Write

ref Tab-4 Write SROM

C0 AD1 AD2 AD3 AD4 AD5 wlength No Data Normal Command Read

40 AD1 DL1 DH1 00 00 wlength Variable Normal Command Write

Tab-5 vendor and normal commands format

Notes: wlength must be even numbers

u 40 : Write Command (4,8,C,10…..) for Write Command

u C0: Read Command (0,2,4,6,8…..) for Read Command

AD1 Bit7 = 1 è Vendor Command

0 è Normal Command

AD1 or AD2 or AD3 or AD4 or AD5 or ADL

Bit6 = 1 è D(data) only low byte valid

0 è D(data) low byte & high byte valid

For Normal Command Write:

( low byte) (high byte)

Ex: wlength = 0C 00

Variable : Data OUT 12 Bytes

0C 00 = 12 Bytes

address data

ADL 00h DL DH ADL 00h DL DH ADL 00h DL DH

This space must fix fill with (00h)

L: Low byte H: High Byte

Note: If wlength = 00 00 , it indicate no need other Data OUT .

For Normal Command Read:

If user want to read 3 set application device internal register, you can set this command as below:

C0 AD1AD2 AD3 AD4 AD5 wlength

è C0 02 04 06 x x 06 00 x : don’t care

3x2 = 6 Bytes

Page 18

18

AX84110 L

ASIX Electronics Corp

Preliminary

5.0 USB Configuration Structure

5.1 USB Configuration

The AX84110 supports 1 Configuration only.

5.2 USB Interface

The AX84110 supports 2 interfaces, the interface 0 is Data Interface and interface 1 for

Communication Interface.

5.3 USB Endpoints

The AX84110 supports 4 endpoints.

Endpoint0 è Control endpoint, it is for configuration device.

Endpoint1 è Interrupt endpoint , it is for reporting application device status.

Endpoint2 è Bulk Out endpoint, it is for Transmitting application device Packet.

Buffer is 2k size and have 4 page. Each page have 512byte space.

Endpoint3 è Bulk IN endpoint, it is for Receiving application device Packet.

Buffer is 1k size and have 2 page. Each page have 512 byte space.

Page 19

19

AX84110 L

ASIX Electronics Corp

Preliminary

6.0 Basic Operation

6.1 Process Flow

If need variable vendor command

No need

Fig-7 Basic Process Flow

1. Standard Command (Get USB Standard Command as Get Device Descriptor)

Ex: (ref Tab-3)

80 06 00 01 00 00 LL PP è Get Device Descriptor

2. Vendor Command (Set AX84110 command)

l fixed of vendor command

l variable of vendor command

fixed of vendor command (for initial setup)

Ex: (ref Tab-4)

1.40 (80~83) 0X 00 RR RR 00 00 è Set Interrupt Register4~1 (optional by application)

AX84110 provide 4 set of register about application device for interrupt status reply.

2.40 84 IO I I 00 00 00 00 è Set I/O Data Port (IO:OUT ;I I :IN)

3.40 87 TC 00 00 00 00 00 è Set Data Access Timing Cycle

Data Access Timing Cycle = Control signal read/write active of period

4. 40 8F YY 00 00 00 00 00 è Set Other Value

AX84110 provide variable parameter for variable application device.

It can define some value high or low active and work on selectable mode.

variable of vendor command (depend on application device)

Initial Usb device

attach states

Standard Command

Vendor Command

1. fixed

2. variable

Normal Command

(for device)

Page 20

20

AX84110 L

ASIX Electronics Corp

Preliminary

Ex: (ref Tab-4)

1.40 85 GP 00 00 00 00 00 è Set Write GPIOs

2. C0 8A 00 00 00 00 01 00 èSet Read GPIOs

AX84110 provide optional 4 set General Purpose Pin (IN/OUT) for application device.

3. 40 87 TC 00 00 00 00 00 è Set Byte Count

If want to receive data from application device, it can set this command. When the command is

set , AX84110 will move byte count number from application device.

4. 40 89 0Z 00 AA AA 00 00 è Set I/O or Memory address function mode

AX84110 provide selectable work mode on I/O or Memory (Attribute & Common only for

Pcmcia Bus mode). You can set address by this command .

5. C0 8B DR 00 00 00 02 00 è Set Read SROM

6. 40 8C DR 00 MM SS 00 00 è Set Write SROM

7. 40 8D 00 00 00 00 00 00 è Set SROM Enable

8. 40 8E 00 00 00 00 00 00 è Set SROM Disable

above 4 command about SROM for needed. (ref Tab-2)

AX84110 provide additional space to store some special value. You can write or read DR

(EEPROM offset of address) by used the command.

3. Normal Command (base on application device)

(ref Tab-5)

Page 21

21

AX84110 L

ASIX Electronics Corp

Preliminary

6.2 Packet Format Character

The AX84110 supports 4 endpoints.

l Control endpoint

l Int endpoint

l Bulk Out endpoint

l Bulk In endpoint

6.2.1 Control endpoint

It is for configuration device.

F

Fig-7 Control SEUP Transaction

Fig-8 Control Read and Write Sequences

Example1: I/O single write (ref Tab-5)

1. Host send SETUP token

Page 22

22

AX84110 L

ASIX Electronics Corp

Preliminary

2. Host send DATA frame (40 30 55 AA 00 00 00 00)

3.When the command decode by AX84110 and send appropriate packet to application device.

If finish, AX84110 will reply a ACK to Host.

4. Host Send IN token.

5. AX84110 will send (zero length status stage) to Host.

6. Host reply a ACK. And No-data Control write is end.

Address[15:0] 30

Data[15:0]

AA55

Wait#

Iowr#

Example2: I/O continue write (ref Tab-5)

1. Host send SETUP token

2. Host send DATA frame (40 30 55 AA 00 00 08 00)

3.When the command decode by AX84110 and send appropriate packet to application device.

If finish, AX84110 will reply a ACK to Host.

4. Host send OUT token

5. Host send DATA frame (32 00 BB AA 34 00 DD CC)

6. repeat 3 .

7. Host Send IN token

8. AX84110 will send (zero length status stage) to Host.

9. Host reply a ACK. And Control write is end.

Address[15:0] 30 32 34

Data[15:0]

AA55

AABB

DDCC

Wait#

Iowr#

Example2: I/O continue read (ref Tab-5)

1. Host send SETUP token

2. Host send DATA frame (C0 30 32 34 00 00 06 00)

3.When the command decode by AX84110 and send appropriate packet to application device.

If finish, AX84110 will reply a ACK to Host.

4. Host send IN token

5. AX84110 receive DATA frame (AA BB CC DD EE FF) from application device and

will send to Host.

6. Host receive Data frame and reply a ACK.

7. Host send OUT token

8. Host send zero length Data Frame.(status stage)

9. AX84110 reply a ACK. And Control read is end.

SETUP

Token

DATA0

40 30 55 AA 00 00 00 00

ACK

Handshake

IN

Token

ACK

SETUP

Token

DATA0

40 30 55 AA 00 00 00 00

OUT

Token

ACK

DATA1

32 00 BB AA 34 00 CC DD

ACK

IN

Token

ACK

DATA1

Zero

DATA1

Zero

Page 23

23

AX84110 L

ASIX Electronics Corp

Preliminary

Address[15:0] 30 32 34

Data[15:0]

BBAA

DDCC

FFEE

Wait#

Iord#

6.2.2 INT endpoint

SETUP

Token

DATA0

C0 30 32 34 00 00 06 00

ACK

IN

DATA1

AA BB CC DD EE FF

ACK

OUT

DATA1

Zero

ACK

Page 24

24

AX84110 L

ASIX Electronics Corp

Preliminary

It is for reporting application device status

Fig-9 Interrupt Transaction Format

Example1: interrupt and status report

1. Host send Vendor Command (ref Tab-4) Set Interrupt Register4~1 (optional by application)

2. Host will send INT IN Token in a fixed time.

3. If no interrupt occur, AX84110 will reply a NAK , otherwise AX84110 will receive data base

on Set Interrupt Register4~1 & status4~1(reply from application device) and wait Host send

next IN token. If application reply status (0110 = 6)

4. When IN token occur and have int occur , AX84110 will send data frame to Host.

5. Host reply a ACK. And Int transaction is end.

Address[15:0] 00 02 04

Data[15:0]

A55A

B44B

C33C

Wait#

Iord#

INT

6.2.3 Bulk Out endpoint

It is for Transmitting application device Packet.

IN

Token

DATA0 /

DATA1

ACK

IN

Token

DATA

5A A5 4B B4 3C C3 06

NAK

IN

Token

ACK

Page 25

25

AX84110 L

ASIX Electronics Corp

Preliminary

Fig-10 Bulk Transaction Format

Example1: I/O Bulk Out Transmit Packet

1. Host send Vendor Command (ref Tab-4) Set IO Data Port address.

2. Host send OUT token.(If AX84110 buffer is full, it will reply a NAK to Host)

3. Host send Data Frame(AA BB CC DD ………..). PID (Data 0)

4. When the command decode by AX84110 and send appropriate packet (AA BB CC DD ….) to

application device.

5. AX84110 reply a ACK. And Bulk Out transaction is end.

6. Host send OUT token. AX84110 buffer is full, it reply a NAK to Host.

7. Host send OUT token. (When buffer is not full)

8. Host send Data Frame (12 23 34 56 ………..). PID (Data 1)

9. When the command decode by AX84110 and send appropriate packet (12 23 34 56 ….) to

application device.

10. AX84110 reply a ACK. And Bulk Out transaction is end.

Address[15:0] 10 10

Data[15:0] BBAA 23 12

Wait#

Iowr#

Buffer Full

6.2.4 Bulk In endpoint

It is for Receiving application device Packet.

OUT

Token

DATA0

ACK OUT

Token

DATA1

ACK

IN

Token

DATA0

DATA1

ACK IN

Token

ACK

OUT

Token

DATA0

AA BB CC DD…

ACK

OUT

Token

DATA1

12 23 34 45 56 78

ACK

OUT

Token

NAK

Page 26

26

AX84110 L

ASIX Electronics Corp

Preliminary

Example1: I/O Bulk IN Transmit Packet

1. Host send Vendor Command (ref Tab-4) Set IO Data Port address.

2. Host send Vendor Command (ref Tab-4) Set Byte Count

3.When the set byte count is set, AX84110 will move data from application

device.

4.Host send IN token, but buffer is not ready (buffer is empty) and AX84110 will reply NAK.

5.When buffer is ready and IN token coming, AX84110 will send data to Host.

It base on full/high speed (max 64 / 512 byte). If the set byte count more than

max packet, it will divide a packet into 64 byte or 512 byte. PID (Data 0)

6. Host reply a ACK. And Bulk In transaction is end.

7. Host send IN token, but buffer is not ready (buffer is empty) and AX84110 will reply NAK.

8. When buffer is ready and IN token coming, AX84110 will send data to Host.

It base on full/high speed (max 64 / 512 byte). If the set byte count more than

max packet, it will divide a packet into 64 byte or 512 byte. PID (Data 1)

9. Host reply a ACK. And Bulk In transaction is end.

Address[15:0] 10 10 10 10

Data[15:0]

BB AA

DD CC 23 12 45 34

Wait#

Iord#

Buffer Empty

IN

Token

NAK

IN

Token

DATA0

AA BB CC DD…

ACK IN

Token

DATA1

12 23 34 45 56…

ACK

Page 27

27

AX84110 L

ASIX Electronics Corp

Preliminary

7.0 CPU & Device Access Functions

7.1 PCMCIA bus type access functions

7.1.1 Attribute Memory access function

Attribute Memory Read function

Function Mode REG# CE2# CE1# SA0 OE# WE# SD[15:8] SD[7:0]

Standby Mode X H H X X X High-Z High-Z

Byte Access (8 bits) L H L L L H High-Z Even-Byte

Word Access (16 bits) L L L X L H Not Valid Even-Byte

Attribute Memory Write function

Function Mode REG# CE2# CE1# SA0 OE# WE# SD[15:8] SD[7:0]

Standby Mode X H H X X X X X

Byte Access (8 bits) L H L L H L X Even-Byte

Word Access (16 bits) L L L X H L X Even-Byte

7.1.2 Common Memory access function

Common Memory Read function

Function Mode REG# CE2# CE1# SA0 OE# WE# SD[15:8] SD[7:0]

Standby Mode X H H X X X High-Z High-Z

Byte Access (8 bits) H H H H L

L

L

H

L

L

H

H

High-Z

High-Z

Even-Byte

Odd-Byte

Word Access (16 bits) H L L X L H Odd-Byte Even-Byte

Common Memory Write function

Function Mode REG# CE2# CE1# SA0 OE# WE# SD[15:8] SD[7:0]

Standby Mode X H H X X X X X

Byte Access (8 bits) H H H H L

L

L

H

H H L

L

X

X

Even-Byte

Odd-Byte

Word Access (16 bits) H L L X H L Odd-Byte Even-Byte

7.1.3 I/O access function

I/O Read function

Function Mode REG# CE2# CE1# SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H H X X X High-Z High-Z

Byte Access (8 bits) L

L

H H L

L

L

H

L

L

H

H

High-Z

High-Z

Even-Byte

Odd-Byte

Word Access (16 bits) L L L L L H Odd-Byte Even-Byte

I/O Write function

Function Mode REG# CE2# CE1# SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H H X X X X X

Byte Access (8 bits) L

L

H H L

L

L

H

H H L

L

X

X

Even-Byte

Odd-Byte

Word Access (16 bits) L L L L H L Odd-Byte Even-Byte

Page 28

28

AX84110 L

ASIX Electronics Corp

Preliminary

7.2 ISA bus type access functions

7.2.1 Memory access function

ISA bus Memory Read function

Function Mode CS# BHE# SA0 MEMR# MEMW # SD[15:8] SD[7:0]

Standby Mode X H X X X High-Z High-Z

Byte Access (8 bits) L

L

H H L H L

L

H

H

Not Valid

Not Valid

Even-Byte

Odd-Byte

Word Access (16 bits) L L L L H Odd-Byte Even-Byte

ISA bus Memory Write function

Function Mode CS# BHE# SA0 MEMR# MEMW # SD[15:8] SD[7:0]

Standby Mode X H X X X X X

Byte Access (8 bits) L

L

H H L H H

H

L

L

X

X

Even-Byte

Odd-Byte

Word Access (16 bits) L L L H L Odd-Byte Even-Byte

7.2.2 I/O access function

ISA bus I/O Read function

Function Mode CS# BHE# SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H X X X High-Z High-Z

Byte Access (8 bits) L

L

H H L H L

L

H

H

Not Valid

Not Valid

Even-Byte

Odd-Byte

Word Access (16 bits) L L L L H Odd-Byte Even-Byte

ISA bus I/O Write function

Function Mode CS# BHE# SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H X X X X X

Byte Access (8 bits) L

L

H H L H H

H

L

L

X

X

Even-Byte

Odd-Byte

Word Access (16 bits) L L L H L Odd-Byte Even-Byte

Page 29

29

AX84110 L

ASIX Electronics Corp

Preliminary

7.3 80186 CPU bus type access functions

7.3.1 Memory access function

80186 CPU bus Memory Read function

Function Mode CS# BHE# SA0 MEMR# MEMW # SD[15:8] SD[7:0]

Standby Mode X H X X X High-Z High-Z

Byte Access (8 bits) L

L

H L L H L

L

H

H

Not Valid

Odd-Byte

Even-Byte

Not Valid

Word Access (16 bits) L L L L H Odd-Byte Even-Byte

80186 CPU bus Memory Write function

Function Mode CS# BHE# SA0 MEMR# MEMW # SD[15:8] SD[7:0]

Standby Mode X H X X X X X

Byte Access (8 bits) L

L

H L L H H

H

L

L

X

Odd-Byte

Even-Byte

X

Word Access (16 bits) L L L H L Odd-Byte Even-Byte

7.3.2 I/O access function

80186 CPU bus I/O Read function

Function Mode CS# BHE# SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H X X X High-Z High-Z

Byte Access (8 bits) L

L

H L L H L

L

H

H

Not Valid

Odd-Byte

Even-Byte

Not Valid

Word Access (16 bits) L L L L H Odd-Byte Even-Byte

80186 CPU bus I/O Write function

Function Mode CS# BHE# SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H X X X X X

Byte Access (8 bits) L

L

H L L H H

H

L

L

X

Odd-Byte

Even-Byte

Odd-Byte

Word Access (16 bits) L L L H L Odd-Byte Even-Byte

Page 30

30

AX84110 L

ASIX Electronics Corp

Preliminary

7.4 68000 CPU bus type access functions

7.4.1 68000 CPU Bus access function

68000 CPU bus Read function

Function Mode CS# UDS# LDS# R/W# SD[15:8] SD[7:0]

Standby Mode X H X X High-Z High-Z

Byte Access (8 bits) L

L

H L L

H

H

H

Not Valid

Even-Byte

Odd-Byte

Not Valid

Word Access (16 bits) L L L H Even-Byte Odd-Byte

68000 CPU bus Write function

Function Mode CS# UDS# LDS# R/W# SD[15:8] SD[7:0]

Standby Mode X H X X X X

Byte Access (8 bits) L

L

H L L

H

L

L

X

Even-Byte

Odd-Byte

X

Word Access (16 bits) L L L L Even-Byte Odd-Byte

Page 31

31

AX84110 L

ASIX Electronics Corp

Preliminary

7.5 8051 CPU bus type access functions

7.5.1 Memory access function

8051 CPU bus Memory Read function

Function Mode CS# PSEN SA0 MEMR# MEMW # SD[15:8] SD[7:0]

Standby Mode X H X X X High-Z High-Z

Byte Access (8 bits) L

L

H H L H L

L

H

H

Not Valid

Not Valid

Even-Byte

Odd-Byte

8051 CPU bus Memory Write function

Function Mode CS# PSEN SA0 MEMR# MEMW # SD[15:8] SD[7:0]

Standby Mode X H X X X X X

Byte Access (8 bits) L

L

H H L H H

H

L

L

X

X

Even-Byte

Odd-Byte

7.3.2 I/O access function

8051 CPU bus I/O Read function

Function Mode CS# PSEN SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H X X X High-Z High-Z

Byte Access (8 bits) L

L

H H L H L

L

H

H

Not Valid

Not Valid

Even-Byte

Odd-Byte

8051 CPU bus I/O Write function

Function Mode CS# PSEN SA0 IORD# IOWR# SD[15:8] SD[7:0]

Standby Mode X H X X X X X

Byte Access (8 bits) L

L

H H L H H

H

L

L

X

X

Even-Byte

Odd-Byte

Page 32

32

AX84110 L

ASIX Electronics Corp

Preliminary

8.0 Electrical Specification and Timing

8.1 Absolute Maximum Ratings

Description SYM Min Max Units

Operating Temperature Ta 0 +85

¢J

Storage Temperature Ts -65 +150

¢J

Supply Voltage Vdd -0.3 +3.6 V

Input Voltage Vin -0.3 Vdd+0.3 V

Output Voltage Vout -0.3 Vdd+0.3 V

Lead Temperature (soldering 10 seconds maximum) Tl 55 +240

¢J

Note: Stress above those listed under Absolute Maximum Rating may cause permanent damage to the

device. Exposure to Absolute Maximum Ratings condition for extended period, adversely affect device

life and reliability.

8.2 General Operation Conditions

Description

SYM Min Tpy Max Units

Operating Temperature Ta 0 25 +70

¢J

Supply Voltage Vdd +3.0 +3.30 +3.6 V

8.3 D.C. Characteristics

(Vdd = 3.0 to 3.6v , Vss = 0V , Ta = 0¢J to 70¢J)

Description SYM Min Tpy Max Units

Low Input Voltage Vil - 0.7*Vdd

V

High Input Voltage Vih 0.7*Vdd

- V

Low Output Voltage Vol - 0.4 V

High Output Voltage Voh 2.4 - V

Input Leakage Current Iil -1 +1 uA

Output Leakage Current Iol -10 +10 uA

Input Pull-up / down resistance Ri 75 K ohm

Description SYM Min Tpy Max Units

Power Consumption (3.3V) SPt3v 150 mA

Page 33

33

AX84110 L

ASIX Electronics Corp

Preliminary

8.4 A.C. Timing Characteristics

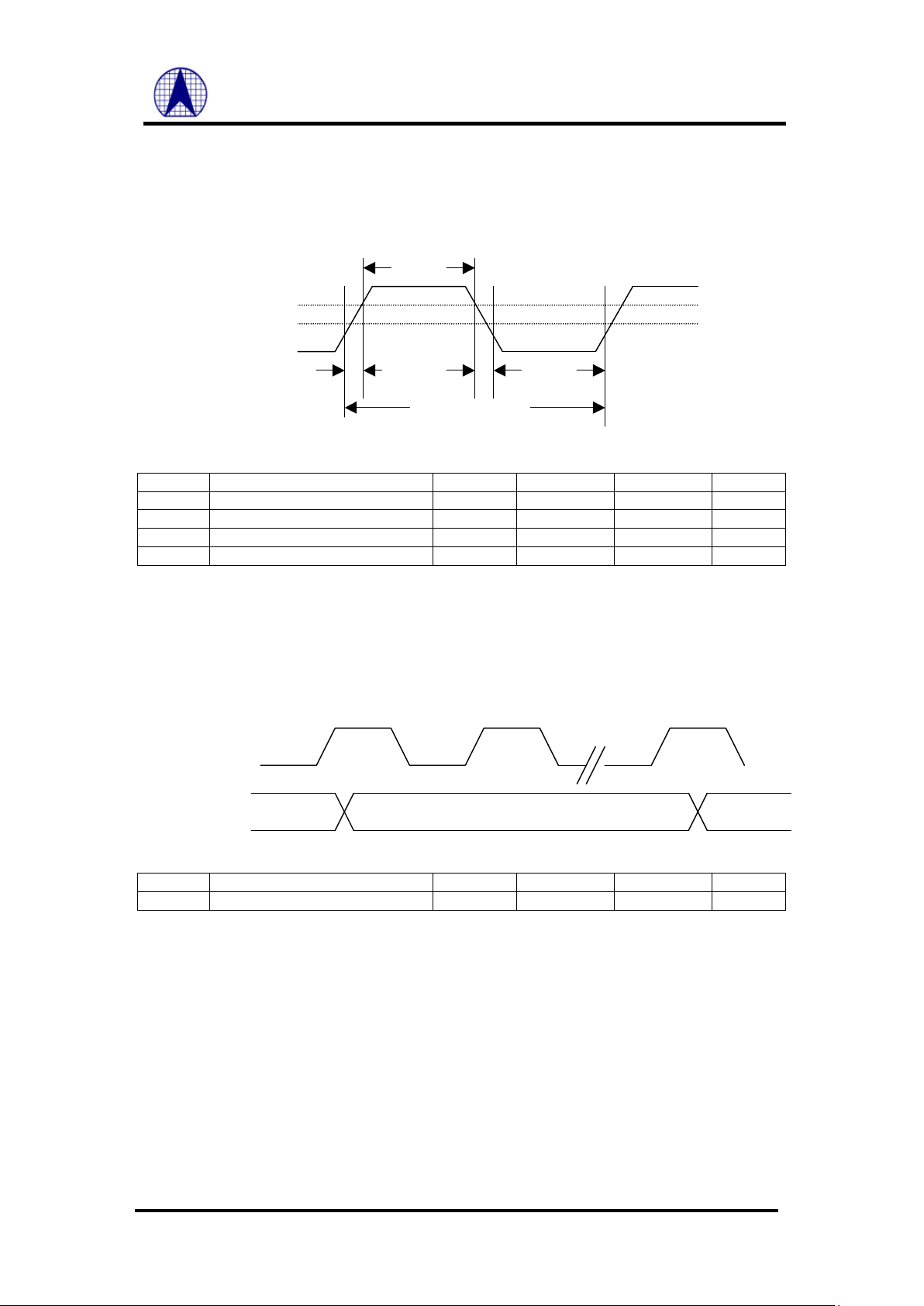

8.4.1 12M_XIN

Symbol

Description Min Typ Max Units

Tcyc CYCLE TIME 83.33 ns

Thigh CLK HIGH TIME 34.71 41.66 49.99 ns

Tlow CLK LOW TIME 34.71 41.66 49.99 ns

Tr / Tf CLK SKEW RATE 1 - 4 ns

8.4.2 Reset Timing

Symbol

Description Min Typ Max Units

Trst Reset pulse width (6ms ~ 10 ms)

100 - - 12M_XIN

Thigh

Tr

Tcyc

Page 34

34

AX84110 L

ASIX Electronics Corp

Preliminary

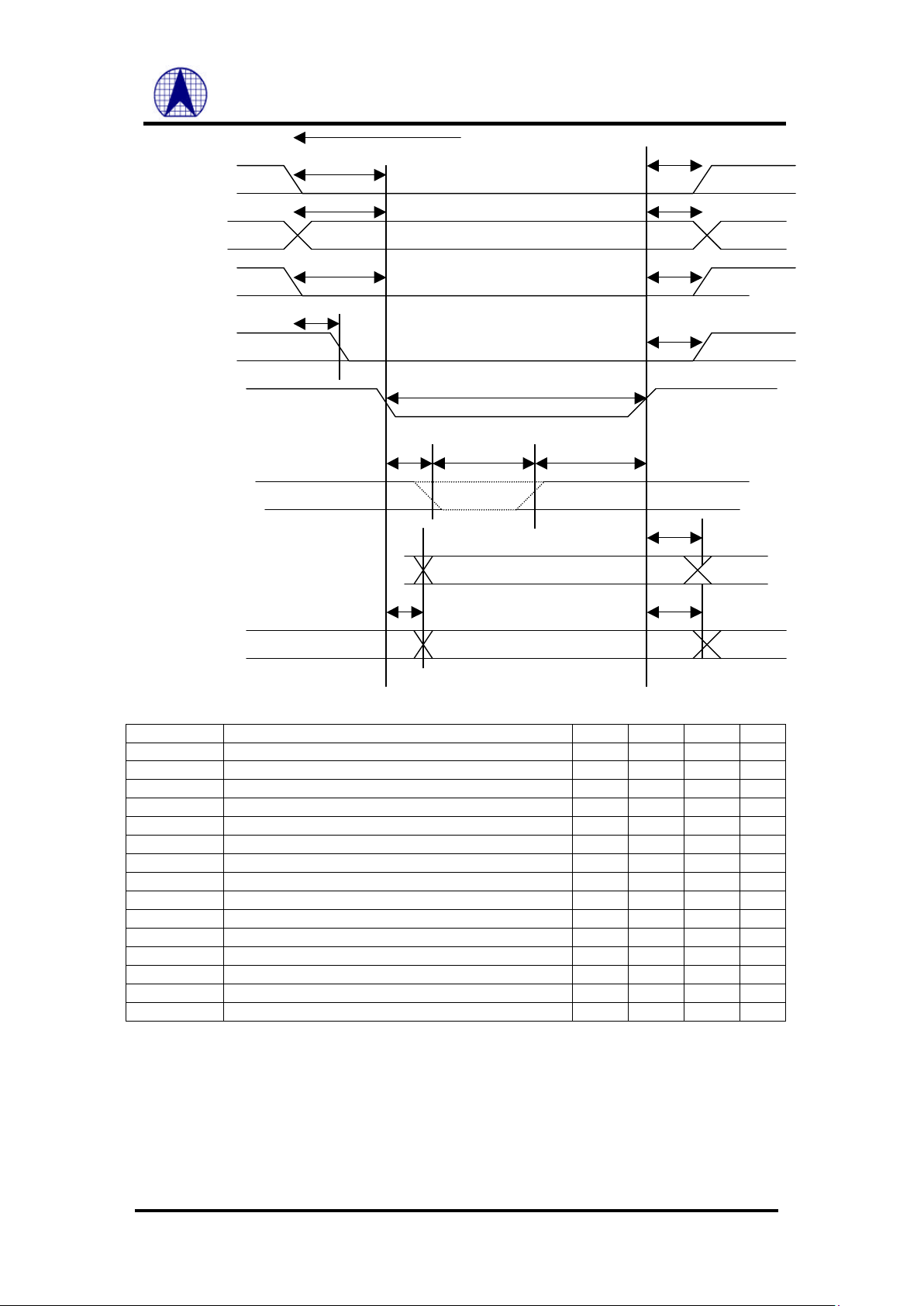

8.4.3 Serial EEprom Timing

Symbol

Description Min Typ Max Units

Tclk EECK Clock Cycle Time 187.5 KHZ

Tch EECK Clock High Time 2666 ns

Tcl EECK Clock Low Time 2666 ns

Tdv EEDI Data Valid Output to EECK High Time 2666 ns

Tod EECK High to EEDI Data Output Delay Time 2666 ns

Tscs EECS Valid to EECK High Time 2666 ns

Thcs EECK Low to EECS Invalid Time 0 ns

Tlcs Minimum EECS Low Time 23904 ns

Ts Data Input Setup Time 10 ns

Th Data Input Hold Time 100 ns

Tdv

VALID

VALID

DATA VALID

EEDI

(output)

EEDO

(input)

Page 35

35

AX84110 L

ASIX Electronics Corp

Preliminary

8.4.4 Pcmcia Attribute Memory Read Timing

Symbol Description Min Typ Max Units

TcR READ CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CE) CARD ENABLE SETUP TIME (CE1) 60 - - ns

Tsu(CE2) CARD ENABLE SETUP TIME (CE2) 30 - - ns

Tsu(REG) REGISTER SELECT SETUP TIME 60 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CE) CARD ENABLE HOLD TIME (CE1) 30 - - ns

Th(CE2) CARD ENABLE HOLD TIME (CE2) 30 - - ns

Th(REG) REGISTER SELECT HOLD TIME 30 - - ns

Tv(WT) WAIT VALID FROM OE# - - 20 ns

Tw(WT) WAIT# PULSE WIDTH 0 - - ns

Tdis(WT) OE# HIGH FROM WAIT# DISABLE 30 - - ns

Ten(OE) DATA ENABLE TIME FROM OE# 0 - - ns

Tdis(OE) DATA DISABLE TIME FROM OE# 30 - - ns

Tw(OE) OE# PULSE WIDTH ** - - ns

* TcR = Tsu(A) + Tw(OE) + Th(A)

** Tw(OE) = Base on Tab-4 Set Data Access Timing Cycle (TC) è No wait condition (Tw(WT) = 0)

= Tv(WT) + Tw(WT) + Tdis (WT) è wait condition (Tw(WT) != 0)

1. No wait condition

If you set TC = 06

Tw(OE) = TC * 30 = 6*30 = 180ns TcR = 270 ns

2. wait condition

If you set TC = 06

Tv(WT) = 20ns, Tw(WT) = 40ns, Tdis (WT) = 30ns

Tw(OE) = 90ns TcR = 180 ns

SA[15:0]

SD[15:0]

REG#

CE1#

CE2#

OE#

WAIT#

Tsu(A)

TcR

Tdis(OE)

Ten(OE)

Th(A)

Th(CE)

Tv(WT) Tw(WT)

Tsu(CE)

DATA Valid

Tsu(CE2)

Tw(OE)

Tsu(REG)

Tdis (WT)

Th(CE2)

Th(REG)

Page 36

36

AX84110 L

ASIX Electronics Corp

Preliminary

8.4.5 Pcmcia Attribute Memory Write Timing

Symbol Description Min Typ Max Units

TcW WRITE CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CE) CARD ENABLE SETUP TIME (CE1) 60 - - ns

Tsu(CE2) CARD ENABLE SETUP TIME (CE2) 30 - - ns

Tsu(REG) REGISTER SELECT SETUP TIME 60 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CE) CARD ENABLE HOLD TIME (CE1) 30 - - ns

Th(CE2) CARD ENABLE HOLD TIME (CE2) 30 - - ns

Th(REG) REGISTER SELECT HOLD TIME 30 - - ns

Tv(WT) WAIT VALID FROM WE# - - 20 ns

Tw(WT) WAIT# PULSE WIDTH 0 - - ns

Tdis(WT) WE# HIGH FROM WAIT# DISABLE 30 - - ns

Ten(WE) DATA ENABLE TIME FROM WE# 30 - - ns

Th(WE) DATA DISABLE TIME FROM WE# 30 - - ns

Tw(WE) WE# PULSE WIDTH ** - - ns

* TcW = Tsu(A) + Tw(WE) + Th(A)

** Tw(WE) = Base on Tab-4 Set Data Access Timing Cycle (TC) è No wait condition (Tw(WT) = 0)

= Tv(WT) + Tw(WT) + Tdis (WT) è wait condition (Tw(WT) != 0)

1. No wait condition

If you set TC = 06

Tw(WE) = TC * 30 = 6*30 = 180ns TcW = 270 ns

2. wait condition

If you set TC = 06

Tv(WT) = 20ns, Tw(WT) = 40ns, Tdis (WT) = 30ns

Tw(WE) = 90ns TcW = 180 ns

SA[15:0]

SD[15:0]

REG#

CE1#

CE2#

WE#

WAIT#

TcW

Tw(WE)

Tsu(A)

Tw(WT)

DATA Valid

Th(WE)

Th(CE)

Tdis(WT)

Tv(WT)

Tsu(CE)

Tsu(CE2)

Tsu(REG)

Ten(WE)

Th(A)

Th(REG)

Th(CE2)

Page 37

37

AX84110 L

ASIX Electronics Corp

Preliminary

8.4.6 Pcmcia Common Memory Read Timing

Symbol Description Min Typ Max Units

TcR READ CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CE) CARD ENABLE SETUP TIME (CE1) 60 - - ns

Tsu(CE2) CARD ENABLE SETUP TIME (CE2) 30 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CE) CARD ENABLE HOLD TIME (CE1) 30 - - ns

Th(CE2) CARD ENABLE HOLD TIME (CE2) 30 - - ns

Tv(WT) WAIT VALID FROM OE# - - 20 ns

Tw(WT) WAIT# PULSE WIDTH 0 - - ns

Tdis(WT) OE# HIGH FROM WAIT# DISABLE 30 - - ns

Ten(OE) DATA ENABLE TIME FROM OE# 0 - - ns

Tdis(OE) DATA DISABLE TIME FROM OE# 30 - - ns

Tw(OE) OE# PULSE WIDTH ** - - ns

* TcR = Tsu(A) + Tw(OE) + Th(A)

** Tw(OE) = Base on Tab-4 Set Data Access Timing Cycle (TC) è No wait condition (Tw(WT) = 0)

= Tv(WT) + Tw(WT) + Tdis (WT) è wait condition (Tw(WT) != 0)

1. No wait condition

If you set TC = 06

Tw(OE) = TC * 30 = 6*30 = 180ns TcR = 270 ns

2. wait condition

If you set TC = 06

Tv(WT) = 20ns, Tw(WT) = 40ns, Tdis (WT) = 30ns

Tw(OE) = 90ns TcR = 180 ns

SA[15:0]

SD[15:0]

REG#

CE1#

CE2#

OE#

WAIT#

Tsu(A)

Tdis(OE)

Ten(OE)

Th(A)

Th(CE)

Tv(WT) Tw(WT)

Tsu(CE)

DATA Valid

Tsu(CE2)

Tw(OE)

Tdis(WT)

Th(CE2)

Page 38

38

AX84110 L

ASIX Electronics Corp

Preliminary

8.4.7 Pcmcia Common Memory Write Timing

Symbol Description Min Typ Max Units

TcW WRITE CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CE) CARD ENABLE SETUP TIME (CE1) 60 - - ns

Tsu(CE2) CARD ENABLE SETUP TIME (CE2) 30 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CE) CARD ENABLE HOLD TIME (CE1) 30 - - ns

Th(CE2) CARD ENABLE HOLD TIME (CE2) 30 - - ns

Tv(WT) WAIT VALID FROM WE# - - 20 ns

Tw(WT) WAIT# PULSE WIDTH 0 - - ns

Tdis(WT) WE# HIGH FROM WAIT# DISABLE 30 - - ns

Ten(WE) DATA ENABLE TIME FROM WE# 30 - - ns

Th(WE) DATA DISABLE TIME FROM WE# 30 - - ns

Tw(WE) WE# PULSE WIDTH ** - - ns

* TcW = Tsu(A) + Tw(WE) + Th(A)

** Tw(WE) = Base on Tab-4 Set Data Access Timing Cycle (TC) è No wait condition (Tw(WT) = 0)

= Tv(WT) + Tw(WT) + Tdis (WT) è wait condition (Tw(WT) != 0)

1. No wait condition

If you set TC = 06

Tw(WE) = TC * 30 = 6*30 = 180ns TcW = 270 ns

2. wait condition

If you set TC = 06

Tv(WT) = 20ns, Tw(WT) = 40ns, Tdis (WT) = 30ns

SA[15:0]

SD[15:0]

REG#

CE1#

CE2#

WE#

WAIT#

TcW

Tw(WE)

Tsu(A)

Tw(WT)

DATA Valid

Tdis(WE)

Th(CE)

Tdis(WT)

Tv(WT)

Tsu(CE)

Tsu(CE2)

Ten(WE)

Th(A)

Th(CE2)

Page 39

39

AX84110 L

ASIX Electronics Corp

Preliminary

Tw(WE) = 90ns TcW = 180 ns

8.4.8 Pcmcia I/O Read Timing

Page 40

40

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

TcR READ CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CE) CARD ENABLE SETUP TIME (CE1) 60 - - ns

Tsu(CE2) CARD ENABLE SETUP TIME (CE2) 30 - - ns

Tsu(REG) REGISTER SELECT SETUP TIME 60 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CE) CARD ENABLE HOLD TIME (CE1) 30 - - ns

Th(CE2) CARD ENABLE HOLD TIME (CE2) 30 - - ns

Th(REG) REGISTER SELECT HOLD TIME 30 - - ns

Tv(WT) WAIT VALID FROM IORD# - - 20 ns

Tw(WT) WAIT# PULSE WIDTH 0 - - ns

Tdis(WT) IORD# HIGH FROM WAIT# DISABLE 30 - - ns

Ten(IORD) DATA ENABLE TIME FROM IORD# 0 - - ns

Tdis(IORD) DATA DISABLE TIME FROM IORD# 30 - - ns

Tw(IORD) IORD# PULSE WIDTH ** - - ns

TdfIOIS16 IOIS16# DELAY FALLING FROM ADDRESS

- - 10 ns

TdrIOIS16 IOIS16# DELAY RISING FROM ADDRESS 0 - - ns

* TcR = Tsu(A) + Tw(IORD) + Th(A)

** Tw(IORD) = Base on Tab-4 Set Data Access Timing Cycle (TC) è No wait condition

= Tv(WT) + Tw(WT) + Tdis (WT) è wait condition

8.4.9 Pcmcia I/O Write Timing

SA[15:0]

SD[15:0]

REG#

CE1#

CE2#

IORD#

WAIT#

IOIS16#

Tdis(IORD)

DATA Valid

Tw(WT)

Tsu(REG)

Tsu(CE)

Tw(IORD)

TdfIOIS16

Tv(WT)

TdrIOIS16

Th(CE)

Th(REG)

Th(A)

TcR

Tsu(A)

Tsu(CE2)

Ten(IORD)

Tdis(WT)

Th(CE2)

Page 41

41

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

TcW WRITE CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CE) CARD ENABLE SETUP TIME (CE1) 60 - - ns

Tsu(CE2) CARD ENABLE SETUP TIME (CE2) 30 - - ns

Tsu(REG) REGISTER SELECT SETUP TIME 60 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CE) CARD ENABLE HOLD TIME (CE1) 30 - - ns

Th(CE2) CARD ENABLE HOLD TIME (CE2) 30 - - ns

Th(REG) REGISTER SELECT HOLD TIME 30 - - ns

Tv(WT) WAIT VALID FROM IOWR# - - 20 ns

Tw(WT) WAIT# PULSE WIDTH 0 - - ns

Tdis(WT) IOWR# HIGH FROM WAIT# DISABLE 30 - - ns

Ten(IOWR) DATA ENABLE TIME FROM IOWR# 30 - - ns

Th(IOWR) DATA DISABLE TIME FROM IOWR# 30 - - ns

Tw(IOWR) IOWR# PULSE WIDTH ** - - ns

TdfIOIS16 IOIS16# DELAY FALLING FROM ADDRESS

- - 10 ns

TdrIOIS16 IOIS16# DELAY RISING FROM ADDRESS 0 - - ns

* TcW = Tsu(A) + Tw(IOWR) + Th(A)

** Tw(IOWR) = Base on Tab-4 Set Data Access Cycle (TC) è No wait condition (Tw(WT) = 0)

= Tv(WT) + Tw(WT) + Tdis (WT) è wait condition (Tw(WT) != 0)

8.4.9 ISA Bus Access I/O Timing

SA[15:0]

SD[15:0]

REG#

CE1#

CE2#

IOWR#

WAIT#

IOIS16#

Ten(IOWR)

Th(IOWR)

DATA Valid

Tw(WT)

Tsu(REG)

Tw(IOWR)

Tsu(A)

TdfIOIS16

Tv(WT)

TdrIOIS16

Th(CE)

Th(REG)

Th(A)

Tdis(WT)

TcW

Tsu(CE2)

Th(CE2)

Tc

Page 42

42

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

Tc CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CS) CHIP SELECT SETUP TIME 60 - - ns

Tsu(BHE) BYTE HIGH ENABLE SETUP TIME 30 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CS) CHIP SELECT HOLD TIME 30 - - ns

Th(BHE) BYTE HIGH ENABLE HOLD TIME 30 - - ns

Tv(RDY) RDY VALID FROM IO# - - 20 ns

Tw(RDY) RDY# PULSE WIDTH 0 - - ns

Tdis(RDY) IO# HIGH FROM RDY# DISABLE 30 - - ns

Ten(IORD) DATA ENABLE TIME FROM IORD# 0 - - ns

Tdis(IORD) DATA DISABLE TIME FROM IORD# 30 - - ns

Ten(IOWR) DATA ENABLE TIME FROM IOWR# 30 - - ns

Th(IOWR) DATA DISABLE TIME FROM IOWR# 30 - - ns

Tw(IO) IO# PULSE WIDTH ** - - ns

Tv(CS16-A) IOIS16# VALID FROM ADDRESS CHANGE - - 10 ns

Tdis(CS16-A) IOIS16# DISABLE FROM ADDRESS CHANGE 0 - - ns

* Tc = Tsu(A) + Tw(IO) + Th(A) IO: include (IOWR & IORD)

** Tw(IO) = Base on Tab-4 Set Data Access Cycle (TC) è No wait condition (Tw(RDY) = 0)

= Tv(RDY) + Tw(RDY) + Tdis (RDY) è wait condition (Tw(RDY) != 0)

SA[15:0]

SD[15:0]

AEN#

RDY

IOIS16#

DATA Valid

DATA Valid

SD[15:0]

BHE#

CS#

Tsu(AEN)

Tsu(A)

Tsu(BHE)

Tsu(CS)

Tv(CS16-A)

Tv(RDY)

Tdis(CS16-A)

Th(A)

Th(CS)

Th(BHE)

Ten(IOWR)

Ten(IORD)

Tw(RDY) Tdis(RDY)

Th(IOWR)

Tdis(IORD)

Tw(IO)

Page 43

43

AX84110 L

ASIX Electronics Corp

Preliminary

8.4.10 ISA Bus Access MEM Timing

Tc

Page 44

44

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

Tc CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CS) CHIP SELECT SETUP TIME 60 - - ns

Tsu(BHE) BYTE HIGH ENABLE SETUP TIME 30 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CS) CHIP SELECT HOLD TIME 30 - - ns

Th(BHE) BYTE HIGH ENABLE HOLD TIME 30 - - ns

Tv(RDY) RDY VALID FROM MEM# - - 20 ns

Tw(RDY) RDY# PULSE WIDTH 0 - - ns

Tdis(RDY) MEM# HIGH FROM RDY# DISABLE 30 - - ns

Ten(MEMR) DATA ENABLE TIME FROM MEMR# 0 - - ns

Tdis(MEMR) DATA DISABLE TIME FROM MEMR# 30 - - ns

Ten(MEMW) DATA ENABLE TIME FROM MEMW # 30 - - ns

Th(MEMW) DATA DISABLE TIME FROM MEMW # 30 - - ns

Tw(MEM) MEM# PULSE WIDTH ** - - ns

* Tc = Tsu(A) + Tw(MEM) + Th(A) MEM: include (MEMR & MEMW)

** Tw(MEM) = Base on Tab-4 Set Data Access Cycle (TC) è No wait condition (Tw(RDY) = 0)

= Tv(RDY) + Tw(RDY) + Tdis (RDY) è wait condition (Tw(RDY) != 0)

8.4.11 80186 Type Access Timing

SA[15:0]

SD[15:0](WRITE)

AEN

MEMR#

RDY

DATA Valid

DATA Valid

MEMW#

SD[15:0](READ)

BHE#

CS#

Tsu(AEN)

Tsu(A)

Tsu(BHE)

Tsu(CS)

Tv(RDY)

Th(AEN)

Th(A)

Th(CS)

Th(BHE)

Ten(IOWR)

Ten(IORD)

Tw(RDY) Tdis(RDY)

Th(IOWR)

Tdis(IORD)

Tw(MEM)

Page 45

45

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

Tc CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CS) CHIP SELECT SETUP TIME 60 - - ns

Tsu(BHE) BYTE HIGH ENABLE SETUP TIME 30 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CS) CHIP SELECT HOLD TIME 30 - - ns

Th(BHE) BYTE HIGH ENABLE HOLD TIME 30 - - ns

Tv(RDY) RDY VALID FROM MEM# - - 20 ns

Tdis(RDY) OP# HIGH FROM RDY# DISABLE 0 - - ns

Ten(RD) DATA ENABLE TIME FROM OP# 0 - - ns

Tdis(RD) DATA DISABLE TIME FROM OP# 30 - - ns

Ten(WR) DATA ENABLE TIME FROM OP# 30 - - ns

Th(WR) DATA DISABLE TIME FROM OP# 30 - - ns

Tw(OP) OP# PULSE WIDTH ** - - ns

* Tc = Tsu(A) + Tw(OP) + Th(A) OP: include (MEMR & MEMW & IOWR & IORD)

** Tw(OP) = Base on Tab-4 Set Data Access Cycle (TC)

8.4.12 68K Type Access Timing

SA[15:0]

SD[15:0](WRITE)

RDY

DATA Valid

IORD#

SD[15:0](READ)

BHE#

CS#

MEMR#

MEMW#

Tc

Tsu(BHE)

Tv(RDY)

Tdis(RDY)

Tdis(RD)

Th(WR) Ten(WR)

Ten(RD)

Th(BHE)

Tsu(CS)

Tsu(A) Th(A)

Th(CS)

Tw(OP)

Tc

Tsu(A) Th(A)

Page 46

46

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

Tc CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CS) CHIP SELECT SETUP TIME 60 - - ns

Tsu(UDS) UPPER DATA STROBE SETUP TIME 60 - - ns

Tsu(LDS) LOWER DATA STROBE SETUP TIME 60 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CS) CHIP SELECT HOLD TIME 30 - - ns

Th(UDS) UPPER DATA STROBE HOLD TIME 30 - - ns

Th(LDS) LOWER DATA STROBE HOLD TIME 30 - - ns

Tv(DTACK) DTACK VALID FROM UDS# OR LDS# - - 20 ns

Tdis(DTACK) DTACK DISABLE FROM UDS# OR LDS# 0 - - ns

Ten(RD) DATA ENABLE TIME FROM UDS# OR LDS# 0 - - ns

Tdis(RD) DATA DISABLE TIME FROM UDS# OR LDS# 30 - - ns

Ten(WR) DATA ENABLE TIME FROM R/W (WRITE) 30 - - ns

Th(WR) DATA DISABLE TIME FROM R/W (WRITE) 30 - - ns

Tw(WR) WR# PULSE WIDTH ** - - ns

* Tc = Tsu(A) + Tw(WR) + Th(A)

** Tw(WR) = Base on Tab-4 Set Data Access Cycle (TC)

8.4.12 8051 Bus Access Timing

Tc

SA[15:1]

SD[15:0](WRITE)

DTACK#

SD[15:0](READ)

UDS#

(Read)

R/W

(Write)

R/W

CS#

Tsu(CS)

Tw(WR)

Ten(WR)

Ten(RD)

Tv(DTACK)

Tdis(DTACK)

Th(CS)

Tdis(RD)

Th(WR)

Tsu(UDS)

Th(UDS)

LDS#

Tsu(LDS) Th(LDS)

Page 47

47

AX84110 L

ASIX Electronics Corp

Preliminary

Symbol Description Min Typ Max Units

Tc CYCLE TIME * - - ns

Tsu(A) ADDRESS SETUP TIME 60 - - ns

Tsu(CS) CHIP SELECT SETUP TIME 60 - - ns

Tsu(PSEN) PSEN SETUP TIME 60 - - ns

Th(A) ADDRESS HOLD TIME 30 - - ns

Th(CS) CHIP SELECT HOLD TIME 30 - - ns

Th(PSEN) PSEN HOLD TIME 30 - - ns

Tv(RDY) RDY VALID FROM OP# - - 20 ns

Tdis(RDY) OP# HIGH FROM RDY# DISABLE 0 - - ns

Ten(RD) DATA ENABLE TIME FROM OP# 0 - - ns

Tdis(RD) DATA DISABLE TIME FROM OP# 30 - - ns

Ten(WR) DATA ENABLE TIME FROM OP# 30 - - ns

Th(WR) DATA DISABLE TIME FROM OP# 30 - - ns

Tw(OP) OP# PULSE WIDTH ** - - ns

* Tc = Tsu(A) + Tw(OP) + Th(A) OP: include (MEMR & MEMW & IOWR & IORD)

** Tw(OP) = Base on Tab-4 Set Data Access Cycle (TC)

9.0 Package information

SA[15:0]

CS#

PSEN

SD[15:0](WRITE)

DATA Valid

DATA Valid

SD[15:0](READ)

Tsu(PSEN)

Tsu(A)

Tsu(CS)

Tw(OP)

Th(A)

Th(CS)

Ten(WR)

Ten(RD)

Tv(RDY) Tdis(RDY)

Th(WR)

Tdis(RD)

Th(PSEN)

Page 48

48

AX84110 L

ASIX Electronics Corp

Preliminary

b

e

D

Hd

E

He

pin 1

A2 A1

L

L1

θ

A

MILIMETER SYMBOL

MIN. NOM MAX

A1 0.05 0.1 0.15

A2 1.39 1.40 1.41

A 1.70

b 0.155 0.16 0.26

D 13.9 14.00 14.1

E 13.9 14.00 14.1

e 0.5

Hd 15.6 16.00 16.4

He 15.6 16.00 16.4

L 0.3 0.50 0.7

L1 1.00

θ

0° 10°

Page 49

49

AX84110

USB2.0 to Local Bus

ASIX electronics Corp

10.0 Reference design (PCMCIA to USB)

USB TO PCMCIA

1.0

AX84110 DEM0 Board

C

1 1Wednesday, December 11, 2002

Title

Size Document Number Rev

Date: Sheet of

VDD5

VDD33L

VDD33L

VDD33L

VDD33L

VDD33L

RESET

WAIT

SD14

IORD#

SD15

IOWR#

SD13

SD12

CE2#

SD11

GND

SD4

SA0

SA4

SD7

SD1

SA6

WE#

SA7

SA2

GND

CE1#

SA3

OE#

SA10

SA11

SA1

IREQ#

SA14

SA8

SA12

SD5

SA5

SA13

SD0

SD3

SA15

SD2

GND

SA9

SD6

IOIS16#

GND

SD9

REG#

SD8

SD10

STSCHG#

DM

DP

VBUS

STSCHG#

VDD5

VDD33

VCC

VDD33L VDD33L

VDD5

VDD33

12M_XIN

EEDO

EECS VDD33

EEDI

EECK

VCC

VCC

VDD33L

EECK

SA0

SD5

VDD33L

VBUS

STSCHG2

SD12

IOWR#

SA12

VDD33L

CE1#

SA7

GND

STSCHG1

VDD33L

SA4

GND

SD9

GND

IORD#

IREQ#

VDD33L

VDD33L

REG#

VDD33L

SD6

SD0

SD13

SA13

VDD33L

SD7

12M_XOUT

12M_XOUT

IOIS16#

CE2#

GND

SA6

AVDD33

GND

GND

OE#

VDD33L

SA5

SA10

SD3

EEDI

RST

VDD33PLL

RST

SD10

EECS

GND

SA9

VDD33PLL

GND

SA1

SA8

SD1

VDD33PLL

STSCHG3

SD14

SA14

VDD33L

GND EEDO

RESET

SD4

AVDD33

GND

GND

GND

SD15

SD11

WE#

SA11

GND

AVDD33

VDD33L

DP

VDD33L

GND

VDD33L

GND

DM

GND

12M_XIN

STSCHG4

WAIT

SA2

SA3

SD2

GND

SD8

VDD33L

SA15

VDD33L

C20

0.1u

C21

0.1u

C11

22P

JP2

HEADER 4X2

1 2

3 4

5 6

7 8

C13

0.47uF

C23

0.1u

Y1

CRYSTAL 12.000MHz

R6 1M

R8

0

C17

0.1u

U3

93C56

1

2

3

4 5

6

7

8

CS

SK

DI

DO GND

NC

NC

VCC

C25

0.1u

C6

0.1u

+

C4

22u/16V

C29

0.1u

C19

0.1u

C9

0.1u

R7

15K

C31

0.1u

D3

DIODE

C12

22P

R5

6.2K 1%

+

C15

22u/16V

C35

0.1u

S2

SW PUSHBUTTON

TP1

TEST POINT1

TP2

TEST POINT1

AX84110

ASIX

USB 2.0 to Local Bus/PCMCIA

U1

AX84110

12345678910121913141516171811

202122232425262728

36

45

46

47

48

49

50

51

52

53

54

7374757677787980818283848586878889909192939495

96

293031

32

33

34

35

37

38

39

40

41

42

43

44

55

56

72717069686766

65

62

61

60

59

58

57

64

63

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115