Page 1

AT91SAM9261-EK Evaluation Board

..............................................................................................

User Guide

Page 2

6198C–ATARM–15-Dec-06

AT91SAM9261-EK Evaluation Board User Guide

Page 3

Table of Contents

Section 1

Overview...............................................................................................1-1

1.1 Scope........................................................................................................1-1

1.2 Deliverables ..............................................................................................1-1

1.3 The AT91SAM9261-EK Evaluation Board................................................1-1

Section 2

Setting Up the AT91SAM9261-EK

Evaluation Board ..................................................................................2-1

2.1 Electrostatic Warning ................................................................................2-1

2.2 Requirements............................................................................................2-1

2.3 Layout .......................................................................................................2-2

2.4 Powering Up the Board.............................................................................2-4

2.5 Backup Power Supply...............................................................................2-4

2.6 Getting Started..........................................................................................2-4

2.7 AT91SAM9261-EK Block Diagram ...........................................................2-5

Section 3

Board Description ................................................................................. 3-1

3.1 AT91SAM9261 Microcontroller .................................................................3-1

3.2 AT91SAM9261 Block Diagram .................................................................3-4

3.3 Memory .....................................................................................................3-5

3.4 Clock Circuitry...........................................................................................3-5

3.5 Reset Circuitry ..........................................................................................3-5

3.6 Shutdown Controller .................................................................................3-5

3.7 Power Supply Circuitry..............................................................................3-5

3.8 Remote Communication ...........................................................................3-5

3.9 Audio Stereo Interface ..............................................................................3-5

3.10 User Interface ...........................................................................................3-5

3.11 Debug Interface ........................................................................................3-6

3.12 Expansion Slot ..........................................................................................3-6

3.13 PIO Usage ...............................................................................................3-7

Section 4

Configuration Straps .............................................................................4-1

4.1 Configuration Straps .................................................................................4-1

Section 5

Schematics ........................................................................................... 5-1

5.1 Schematics ...............................................................................................5-1

AT91SAM9261-EK Evaluation Board User Guide i

6198C–ATARM–15-Dec-06

Page 4

Section 6

Errata....................................................................................................6-1

6.1 JTAGSEL S5 Footprint Selector ...............................................................6-1

Section 7

Revision History....................................................................................7-1

7.1 Revision History ........................................................................................7-1

-ii AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 5

Section 1

Overview

1.1 Scope The AT91SAM9261-EK evaluation kit is an effective platform for evaluating chip perfor-

mance and developing code for applications based on the AT91SAM9261.

This guide is a description of the hardware included in the AT91SAM9261-EK evaluation

kit. Software files are available on the DVD-ROM included in the kit and described in

“Deliverables” below.

1.2 Deliverables The AT91SAM9261-EK package contains the following items:

! an AT91SAM9261-EK board

! one A/B-type USB cable

! one serial RS232 cable

! one RJ45 crossed Ethernet cable

1.3 The

AT91SAM9261EK Evaluation

Board

! universal input AC/DC power supply with US and EU plug adapter

! one DVD-ROM containing summary and full datasheets, datasheets with electrical

and mechanical characteristics, application notes and getting started documents for

all development boards and AT91 microcontrollers. An AT91 software package with C

and assembly listings is also provided. This allows the user to begin evaluating the

AT91 A R M

The board is equipped with an AT91SAM9261 (217-ball LFBGA package) together with

the following:

! 64 Mbytes of SDRAM memory

! 256 Mbytes of NAND Flash memory

! one Atmel

! one USB device port interface

! two USB host port interfaces

! one DBGU serial communication port

! JTAG/ICE debug interface

®

Thumb® 32-bit microcontroller quickly.

®

serial DataFlash

®

AT91SAM9261-EK Evaluation Board User Guide 1-1

6198C–ATARM–15-Dec-06

Page 6

Overview

! one Ethernet 100-base TX with three status LEDs

! one Atmel AT73C213 Audio DAC

! one 3.5" 1/4 VGA TFT LCD Module with TouchScreen and backlight

! one Power LED and two general-purpose LEDs

! four user input pushbuttons

! one wakeup input pushbutton

! one reset pushbutton

! one DataFlash SD/MMC card slot

! two expansion footprint connectors (solder side)

! one Lithium Coin Cell Battery Retainer for 12 mm cell size

! dual pitch prototyping area

1-2 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 7

Section 2

Setting Up the AT91SAM9261-EK

Evaluation Board

2.1 Electrostatic Warning

2.2 Requirements In order to set up the AT91SAM9261-EK evaluation board, the following items are

The AT91SAM9261-EK evaluation board is shipped in a protective anti-static package.

The board must not be subjected to high electrostatic potentials. A grounding strap or

similar protective device should be worn when handling the board. Avoid touching the

component pins or any other metallic element.

required:

! the AT91SAM9261-EK evaluation board itself

! AC/DC power adapter (5V at 2A), 2.1 mm by 5.5 mm

AT91SAM9261-EK Evaluation Board User Guide 2-1

6198C–ATARM–15-Dec-06

Page 8

Setting Up the AT91SAM9261-EK Evaluation Board

2.3 Layout

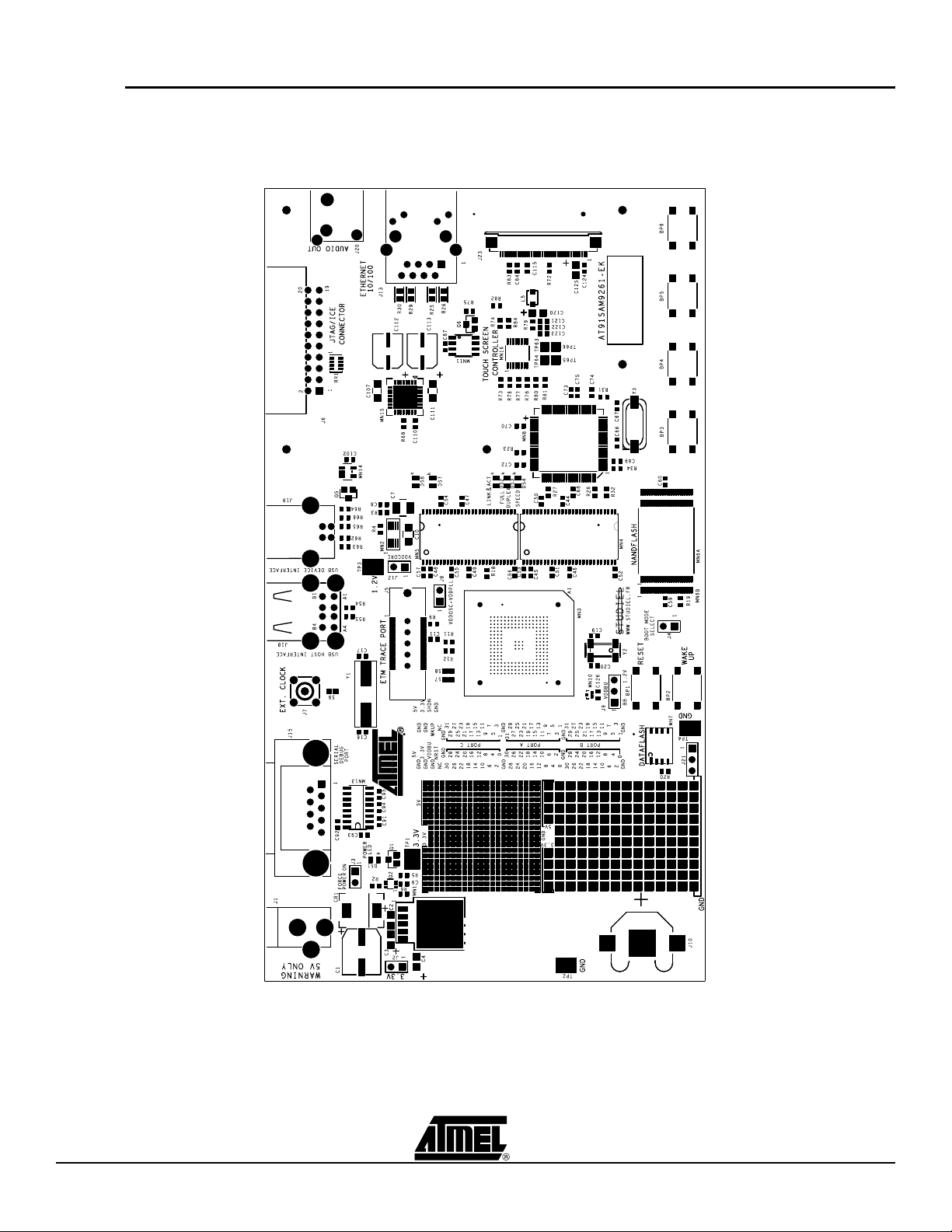

Figure 2-1. AT91SAM9261-EK Layout - Top View

2-2 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 9

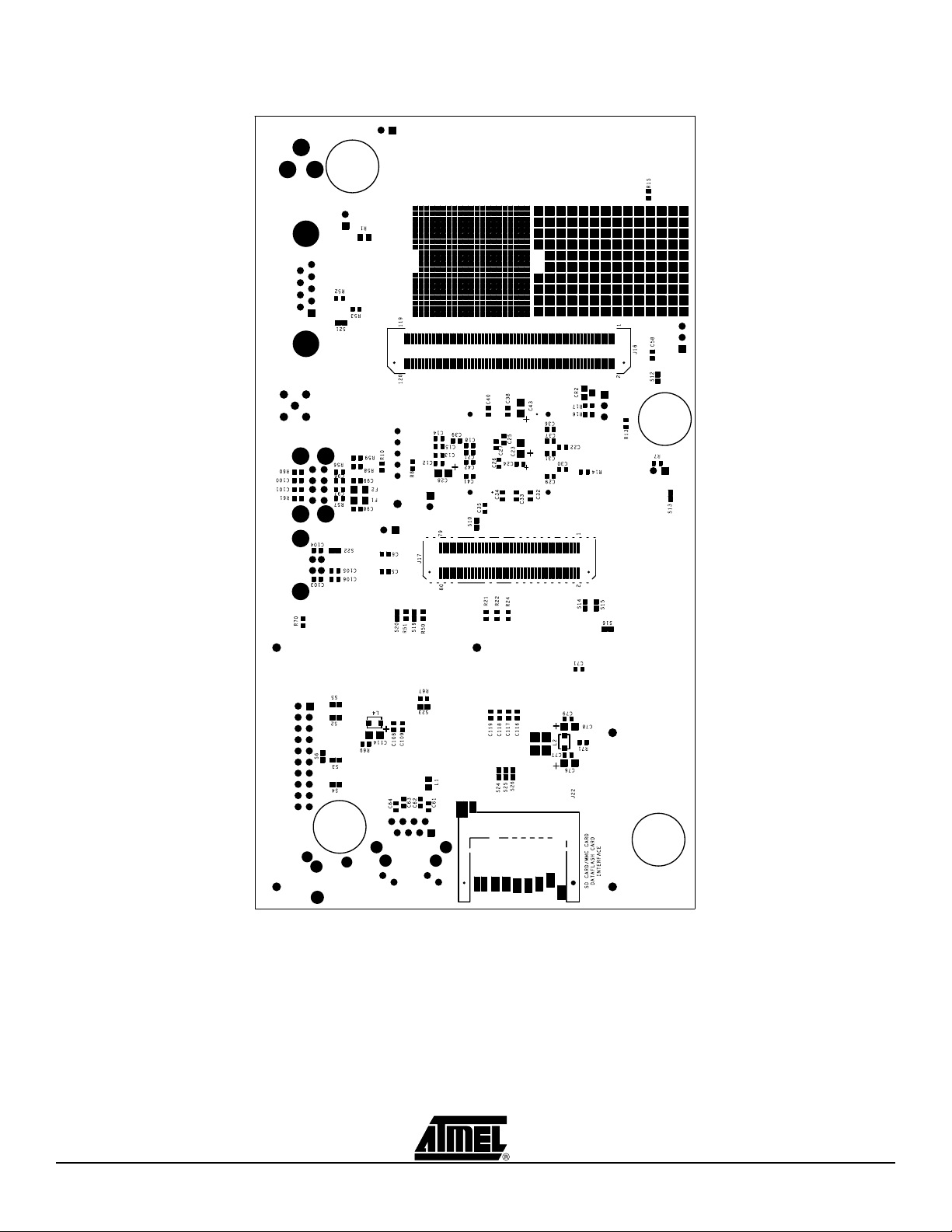

Figure 2-2. AT91SAM9261-EK Layout - Bottom View

Setting Up the AT91SAM9261-EK Evaluation Board

AT91SAM9261-EK Evaluation Board User Guide 2-3

6198C–ATARM–15-Dec-06

Page 10

Setting Up the AT91SAM9261-EK Evaluation Board

2.4 Powering Up the Board

2.5 Backup Power Supply

AT91SAM9261-EK requires 5V DC (±5%). DC power is supplied to the board via the 2.1

mm by 5.5 mm socket (J1). The coaxial power plug center pin is positive polarity .

The user has the possibility to add a battery (3V Lithium Battery CR1225 or equivalent)

in order to permanently power the backup part of the device. In this case, J9 configuration must to be set in position 1, 2.

Refer to Table 4-1, “Configuration Jumpers and Straps”.

2.6 Getting Started The AT91SAM9261-EK evaluation board is delivered with one CD-ROM allowing the

user to begin evaluating the AT91 ARM Thumb 32-bit microcontroller quickly. Please

refer to the AT91 web site, www.atmel.com/products/AT91/, for the most up-to-date infor-

mation on getting started with the AT91SAM9261-EK.

2-4 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 11

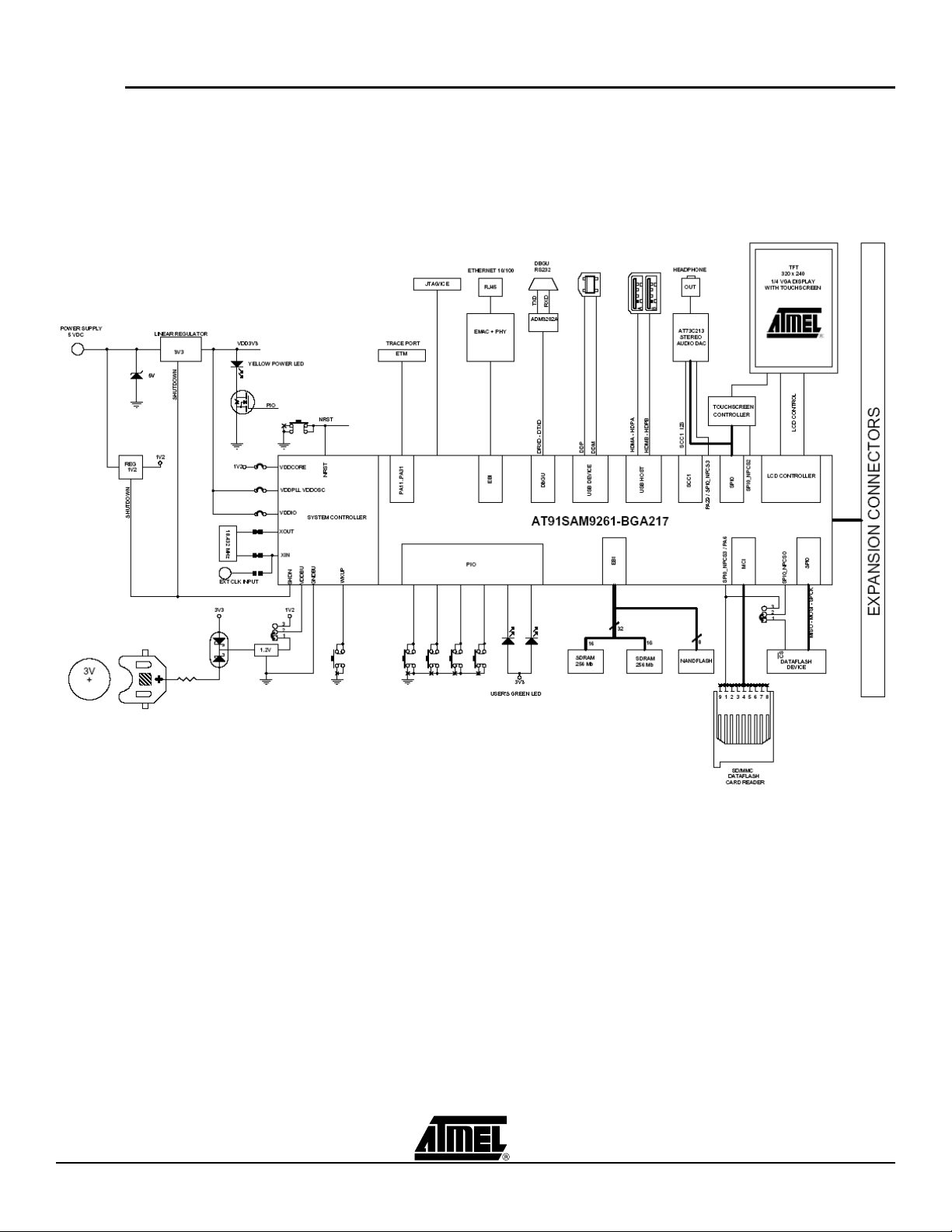

2.7 AT91SAM9261EK Block

Diagram

Figure 2-3. Block Diagram

Setting Up the AT91SAM9261-EK Evaluation Board

AT91SAM9261-EK Evaluation Board User Guide 2-5

6198C–ATARM–15-Dec-06

Page 12

Setting Up the AT91SAM9261-EK Evaluation Board

2-6 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 13

Section 3

Board Description

3.1 AT91SAM9261 Microcontroller

! Incorporates the ARM926EJ-S™ ARM Thumb Processor

– DSP Instruction Extensions

– ARM Jazelle

– 16-KByte Data Cache, 16-KByte Instruction Cache, Write Buffer

– 200 MIPS at 180 MHz

– Memory Management Unit

– EmbeddedICE

– Mid-level implementation Embedded Trace Macrocell

! Additional Embedded Memories

– 32K Bytes of Internal ROM, Single-cycle Access at Maximum Bus Speed

– 160K Bytes of Internal SRAM, Single-cycle Access at Maximum Processor or

Bus Speed

! External Bus Interface (EBI)

– Supports SDRAM, Static Memory, NAND Flash and CompactFlash

! LCD Controller

– Supports Passive or Active Displays

– Up to 16-bits per Pixel in STN Color Mode

– Up to 16M Colors in TFT Mode (24-bit per Pixel), Resolution up to 2048 x

2048

®

Tech n o l ogy for Java® Acceleration

™

In-circuit Emulation, Debug Communication Channel Support

™

®

! USB

– USB 2.0 Full Speed (12 Mbits per second) Host Double Port

Dual On-chip Transceivers

Integrated FIFOs and Dedicated DMA Channels

– USB 2.0 Full Speed (12 Mbits per second) Device Port

On-chip Transceiver, 2-Kbyte Configurable Integrated FIFOs

! Bus Matrix

– Handles Five Masters and Five Slaves

– Boot Mode Select Option

AT91SAM9261-EK Evaluation Board User Guide 3-1

6198C–ATARM–15-Dec-06

Page 14

Board Description

– Remap Command

! Fully Featured System Controller (SYSC) for Efficient System Management, including

– Reset Controller, Shutdown Controller, Four 32-bit Battery Backup Registers

for a Total of 16 Bytes

– Clock Generator and Power Management Controller

– Advanced Interrupt Controller and Debug Unit

– Periodic Interval Timer, Watchdog Timer and Real-time Timer

– Three 32-bit PIO Controllers

! Reset Controller (RSTC)

– Based on Power-on Reset Cells, Reset Source Identification and Reset

Output Control

! Shutdown Controller (SHDWC)

– Programmable Shutdown Pin Control and Wake-up Circuitry

! Clock Generator (CKGR)

– 32.768 kHz Low-power Oscillator on Battery Backup Power Supply, Providing

a Permanent Slow Clock

– 3 to 20 MHz On-chip Oscillator and two PLLs

! Power Management Controller (PMC)

– Very Slow Clock Operating Mode, Software Programmable Power

Optimization Capabilities

– Four Programmable External Clock Signals

! Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Three External Interrupt Sources and One Fast Interrupt Source, Spurious

Interrupt Protected

! Debug Unit (DBGU)

– 2-wire USART and Support for Debug Communication Channel,

Programmable ICE Access Prevention

! Periodic Interval Timer (PIT)

– 20-bit Interval Timer plus 12-bit Interval Counter

! Watchdog Timer (WDT)

– Key Protected, Programmable Only Once, Windowed 12-bit Counter, Running

at Slow Clock

! Real-Time Timer (RTT)

– 32-bit Free-running Backup Counter Running at Slow Clock

! Three 32-bit Parallel Input/Output Controllers (PIO) PIOA, PIOB and PIOC

– 96 Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up Resistor and Synchronous

Output

! Nineteen Peripheral DMA (PDC) Channels

3-2 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 15

Board Description

! Multimedia Card Interface (MCI)

– Compliant with Multimedia Cards and SDCards

– Automatic Protocol Control and Fast Automatic Data Transfers with PDC,

MMC and SDCard Compliant

! Three Synchronous Serial Controllers (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and

Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

! Three Universal Synchronous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA

®

Infrared Modulation/Demodulation

– Support for ISO7816 T0/T1 Smart Card, Hardware and Software

Handshaking, RS485 Support

! Two Master/Slave Serial Peripheral Interface (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

! One Three-channel 16-bit Timer/Counters (TC)

– Three External Clock Inputs, Two multi-purpose I/O Pins per Channel

– Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

! Two-wire Interface (TWI)

– Master Mode Support, All Two-wire Atmel EEPROMs Supported

! IEEE

®

1149.1 JTAG Boundary Scan on All Digital Pins

! Required Power Supplies:

– 1.08V to 1.32V for VDDCORE and VDDBU

– 3.0V to 3.6V for VDDOSC and for VDDPLL

– 2.7V to 3.6V for VDDIOP (Peripheral I/Os)

– 1.65V to 1.95V and 3.0V to 3.6V for VDDIOM (Memory I/Os)

! Available in a 217-ball LFBGA RoHS-compliant Package

AT91SAM9261-EK Evaluation Board User Guide 3-3

6198C–ATARM–15-Dec-06

Page 16

Board Description

3.2 AT91SAM9261 Block Diagram

JTAGSEL

TDI

TDO

TMS

TCK

NTRST

RTCK

TST

FIQ

IRQ0-IRQ2

DRXD

DTXD

PCK0-PCK3

PLLRCA

PLLRCB

XIN

XOUT

XIN32

XOUT32

SHDN

WKUP

VDDBU

GNDBU

VDDCORE

NRST

MCCK

MCCDA

MCDA0-MCDA3

RXD0

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

RXD2

TXD2

SCK2

RTS2

CTS2

SPI0_NPCS0

SPI0_NPCS1

SPI0_NPCS2

SPI0_NPCS3

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

SPI1_NPCS10

SPI1_NPCS1

SPI1_NPCS12

SPI1_NPCS3

SPI1_MISO

SPI1_MOSI

SPI1_SPCK

JTAG

Boundary Scan

System Controller

PIO

DBGU

PLLA

PLLB

OSC

WDT

GPBREG

OSC

SHDWC

POR

PIO

PIO

RSTC

POR

PIOA PIOB PIOC

Figure 3-1. Block Diagram

ICE

AIC

ITCM DTCM

PDC

PDC

PDC

PDC

PDC

PDC

Fast SRAM

160K bytes

Fast ROM

32K bytes

PDC

PMC

PIT

RTT

MCI

USART0

USART1

USART2

SPI0

SPI1

Instruction Cache

16K bytes

TCM

Interface

ID

Peripheral

Bridge

Peripheral

DMA

Controller

APB

ARM926EJ-S Core

MMU

ID

5-layer

Matrix

Data Cache

16K bytes

BIU

DMA FIFO

FIFO

DMA

FIFO

LUT

LCD Controller

PDC

PDC

PDC

Timer Counter

ETM

EBI

CompactFlash

NAND Flash

SDRAM

Controller

Static

Memory

Controller

USB Host

USB Device

SSC0

SSC1

SSC2

TC0

TC1

TC2

TWI

TSYNC

TCLK

PIO

TPS0-TPS2

TPK0-TPK15

BMS

D0-D15

A0/NBS0

A1/NBS2/NWR2

A2-A15/A18-A21

A22/REG

A16/BA0

A17/BA1

NCS0

NCS1/SDCS

NCS2

NCS3/NANDCS

NRD/CFOE

NWR0/NWE/CFWE

NWR1/NBS1/CFIOR

NWR3/NBS3/CFIOW

SDCK

SDCKE

RAS-CAS

SDWE

SDA10

NWAIT

A23-A24

A25/CFRNW

NCS4/CFCS0

NCS5/CFCS1

PIO

Transceiver

Transceiver

PIO

CFCE1

CFCE2

NCS6/NANDOE

NCS7/NANDWE

D16-D31

HDMA

HDPA

HDMB

HDPB

DDM

DDP

LCDD0-LCDD23

LCDVSYNC

LCDHSYNC

LCDDOTCK

LCDDEN

LCDCC

TF0

TK0

TD0

RD0

RK0

RF0

TF1

TK1

TD1

RD1

RK1

RF1

TF2

TK2

TD2

RD2

RK2

RF2

TCLK0

TCLK1

TCLK2

TIOA0

TIOB0

TIOA1

TIOB1

TIOA2

TIOB2

TWD

TWCK

3-4 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 17

3.3 Memory ! 32 Kbytes of Internal ROM

! 160 Kbytes of Internal High-speed SRAM

! Atmel serial DataFlash

! 64 Mbytes of SDRAM memory

! 256 Mbytes of NAND Flash memory

3.4 Clock Circuitry ! 18.432 MHz standard crystal for the embedded oscillator

! 32.768 kHz standard crystal for the slow clock oscillator

3.5 Reset Circuitry ! Internal reset controller with a bi-directional reset pin

! External reset push button

Board Description

3.6 Shutdown Controller

3.7 Power Supply Circuitry

3.8 Remote Communication

3.9 Audio Stereo Interface

! Programmable shutdown and Wake-Up

! Wake-up push button

! For dynamic power consumption, the AT91SAM9261 consumes a maximum of 50 mA

on VDDCORE at maximum speed in typical conditions (1.2V, 25°C), processor

running full-performance algorithm

! On-board 1.2V high efficiency step-down charge pump regulator with shutdown

control

! On-board 3.3V linear regulator with shutdown control

! One Serial interface (DBGU COM Port) via RS-232 DB9 male socket

! USB V2.0 Full-speed Compliant, 12 Mbits per second (UDP)

! Two USB Host port V2.0 Full-speed Compliant, 12 Mbits per second (UHP)

! One Ethernet 100-base TX with three status LEDs

! One Atmel stereo audio DAC AT73C213

! One 32 Ohm/20 mW Stereo Headset output (J20) with Master Volume and Mute

Controls

3.10 User Interface ! Four user input pushbuttons

! Two user green LEDs

! One yellow power LED (can be also software controlled)

AT91SAM9261-EK Evaluation Board User Guide 3-5

6198C–ATARM–15-Dec-06

Page 18

Board Description

! One ¼ VGA display LCD with Touchscreen and white LED backlight

3.11 Debug Interface ! 20-pin JTAG/ICE interface connector

! DBGU COM Port

3.12 Expansion Slot ! One DataFlash, SD/MMC card slot

! All I/Os of the AT91SAM9261 are routed to peripheral extension footprint connectors

(J16 and J17). This allows the developer to check the integrity of the components and

to extend the features of the board by adding external hardware components or

boards.

3-6 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 19

Board Description

3.13 PIO Usage

Table 3-1. PIO Controller A

I/O Line Peripheral A Peripheral B Comments

PA0 SPI0_MISO MCDA0 SD/MMC/DATAFLASH SOCKET (J9) & DATAFLASH DEVICE &

TOUCH SCREEN CONTROLLER & AUDIO DAC

PA1 SPI0_MOSI MCCDA SD/MMC/DATAFLASH SOCKET (J9) & DATAFLASH DEVICE &

TOUCH SCREEN CONTROLLER & AUDIO DAC

PA2 SPI0_SPCK MCCK SD/MMC/DATAFLASH SOCKET (J9) & DATAFLASH DEVICE &

TOUCH SCREEN CONTROLLER & AUDIO DAC

PA3 SPI0_NPCS0 DATAFLASH DEVICE or DATAFLASH SOCKET (J9) SPI0_NPCS0

PA4 SPI0_NPCS1 MCDA1 SD/MMC/DATAFLASH SOCKET (J9) MCDA1

PA5 SPI0_NPCS2 MCDA2 SD/MMC/DATAFLASH SOCKET (J9) MCDA2

PA6 SPI0_NPCS3 MCDA3 SD/MMC/DATAFLASH SOCKET (J9) SPI0_NPCS3 or

PA7 TWD PCK0

PA 8 T WCK P CK1

PA9 DRXD PCK2 SERIAL DEBUG PORT (J15) DRXD

PA10 DTXD PCK3 SERIAL DEBUG PORT (J15) DTXD

PA11 TSYNC SCK1 TOUCH SCREEN CONTROLLER (MN16) BUSY PA11

PA12 TCLK RTS1 TFT PANEL CONTROL (J23) POWER CONTROL IN PA12

PA13 TPS0 CTS1 GREEN USER'S LED 1 (DS8) PA13

PA14 TPS1 SCK2 GREEN USER'S LED 2 (DS7) PA14

PA15 TPS2 RTS2

PA16 TPK0 CTS2

PA17 TPK1 TF1 I2S AUDIO DAC AT73C213 (MN15) LRFS TF1

PA18 TPK2 TK1 I2S AUDIO DAC AT73C213 (MN15) BCLK TK1

PA19 TPK3 TD1 I2S AUDIO DAC AT73C213 (MN15) SDIN TD1

PA20 TPK4 RD1

PA21 TPK5 RK1

PA22 TPK6 RF1

PA23 TPK7 RTS0 YELLOW POWER LED CONTROL (DS1) PA23

PA24 TPK8 SPI1_NPCS1 USER'S PUSH BUTTON INPUT (BP6) PA24

PA25 TPK9 SPI1_NPCS2 USER'S PUSH BUTTON INPUT (BP5) PA25

PA26 TPK10 SPI1_NPCS3 USER'S PUSH BUTTON INPUT (BP4) PA26

PA27 TPK11 SPI0_NPCS1 USER'S PUSH BUTTON INPUT (BP3) PA27

PA28 TPK12 SPI0_NPCS2 TOUCH SCREEN CONTROLLER (MN16) SPI0_NPCS2

PA29 TPK13 SPI0_NPCS3 I2S AUDIO DAC AT73C213 (MN15) SPI0_NPCS3

PA30 TPK14 A23

PA31 TPK15 A24

SPI0_MISO or

MCI0_DA0

SPI0_MOSI or

MCI0_CDA

SPI0_SPCK or

MCCK

MCDA3

AT91SAM9261-EK Evaluation Board User Guide 3-7

6198C–ATARM–15-Dec-06

Page 20

Board Description

Table 3-2. PIO Controller B

I/O Line Peripheral A Peripheral B Comments

PB0 LCDVSYNC

PB1 LCDHSYNC TFT PANEL CONTROL (J23) LCDHSYNC

PB2 LCDDOTCK PCK0 TFT PANEL CONTROL (J23) LCDDOTCK

PB3 LCDDEN TFT PANEL CONTROL (J23) LCDDEN

PB4 LCDCC LCDD2 TFT PANEL CONTROL (J23) BACKLIGHT LCDCC

PB5 LCDD0 LCDD3

PB6 LCDD1 LCDD4

PB7 LCDD2 LCDD5 TFT PANEL CONTROL (J23) LCDD2 RED

PB8 LCDD3 LCDD6 TFT PANEL CONTROL (J23) LCDD3 RED

PB9 LCDD4 LCDD7 TFT PANEL CONTROL (J23) LCDD4 RED

PB10 LCDD5 LCDD10 TFT PANEL CONTROL (J23) LCDD5 RED

PB11 LCDD6 LCDD11 TFT PANEL CONTROL (J23) LCDD6 RED

PB12 LCDD7 LCDD12 TFT PANEL CONTROL (J23) LCDD7 RED

PB13 LCDD8 LCDD13

PB14 LCDD9 LCDD14

PB15 LCDD10 LCDD15 TFT PANEL CONTROL (J23) LCDD10 GREEN

PB16 LCDD11 LCDD19 TFT PANEL CONTROL (J23) LCDD11 GREEN

PB17 LCDD12 LCDD20 TFT PANEL CONTROL (J23) LCDD12 GREEN

PB18 LCDD13 LCDD21 TFT PANEL CONTROL (J23) LCDD13 GREEN

PB19 LCDD14 LCDD22 TFT PANEL CONTROL (J23) LCDD14 GREEN

PB20 LCDD15 LCDD23 TFT PANEL CONTROL (J23) LCDD15 GREEN

PB21 TF0 LCDD16

PB22 TK0 LCDD17

PB23 TD0 LCDD18 TFT PANEL CONTROL (J23) LCDD18 BLUE

PB24 RD0 LCDD19 TFT PANEL CONTROL (J23) LCDD19 BLUE

PB25 RK0 LCDD20 TFT PANEL CONTROL (J23) LCDD20 BLUE

PB26 RF0 LCDD21 TFT PANEL CONTROL (J23) LCDD21 BLUE

PB27 SPI1_NPCS1 LCDD22 TFT PANEL CONTROL (J23) LCDD22 BLUE

PB28 SPI1_NPCS0 LCDD23 TFT PANEL CONTROL (J23) LCDD23 BLUE

PB29 SPI1_SPCK IRQ2 USB DEVICE INTERFACE (J19) USB_CNX PB29

PB30 SPI1_MISO IRQ1

PB31 SPI1_MOSI PCK2 I2S AUDIO DAC AT73C213 (MN15) MCLK PCK2

3-8 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 21

Board Description

Table 3-3. PIO Controller C

I/O Line Peripheral A Peripheral B Comments

PC0 NANDOE NCS6 NAND FLASH DEVICE (MN6x) NANDOE

PC1 NANDWE NCS7 NAND FLASH DEVICE (MN6x) NANDWE

PC2 NWAIT IRQ0 TOUCH SCREEN CONTROLLER (MN16) PENIRQ IRQ0

PC3 A25/CFRNW

PC4 NCS4/CFCS0

PC5 NCS5/CFCS1

PC6 CFCE1

PC7 CFCE2

PC8 TXD0 PCK2

PC9 RXD0 PCK3

PC10 RTS0 SCK0 ETHERNET CONTROLLER (MN8) RST PC10

PC11 CTS0 FIQ ETHERNET CONTROLLER (MN8) IRQ PC11

PC12 TXD1 NCS6

PC13 RXD1 NCS7

PC14 TXD2 SPI1_NPCS2 NAND FLASH DEVICE (MN6x) CHIP ENABLE (CE) PC14

PC15 RXD2 SPI1_NPCS3 NAND FLASH DEVICE (MN6x) READY/BUSY (R/B) PC15

PC16 D16 TCLK0 EBI DATA BUS D16 D16

PC17 D17 TCLK1 EBI DATA BUS D17 D17

PC18 D18 TCLK2 EBI DATA BUS D18 D18

PC19 D19 TIOA0 EBI DATA BUS D19 D19

PC20 D20 TIOB0 EBI DATA BUS D20 D20

PC21 D21 TIOA1 EBI DATA BUS D21 D21

PC22 D22 TIOB1 EBI DATA BUS D22 D22

PC23 D23 TIOA2 EBI DATA BUS D23 D23

PC24 D24 TIOB2 EBI DATA BUS D24 D24

PC25 D25 TF2 EBI DATA BUS D25 D25

PC26 D26 TK2 EBI DATA BUS D26 D26

PC27 D27 TD2 EBI DATA BUS D27 D27

PC28 D28 RD2 EBI DATA BUS D28 D28

PC29 D29 RK2 EBI DATA BUS D29 D29

PC30 D30 RF2 EBI DATA BUS D30 D30

PC31 D31 PCK1 EBI DATA BUS D31 D31

AT91SAM9261-EK Evaluation Board User Guide 3-9

6198C–ATARM–15-Dec-06

Page 22

Board Description

3-10 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 23

Section 4

Configuration Straps

4.1 Configuration Straps

Table 4-1 gives details on configuration straps on the AT91SAM9261-EK evaluation

board and their default settings.

Table 4-1. Configuration Jumpers and Straps

Default

Designation

J2 Closed 3.3V Jumper

J3 Closed Forces power on. To use the software shutdown control, J3

J4 Opened Enables Boot on the internal ROM

J8 Closed VDDPLL Jumper

J9 2-3 VDDBU Jumper select

J12 Closed VDDCORE Jumper

J21 1-2 NPCS0 select

Setting Feature

(1)

This jumper footprint is provided for 3.3V power consumption

measurement use. By default, it is closed. To use this feature,

the user has to open the strap by cutting it before soldering a

jumper.

must be opened.

Closed Enables Boot on the NCS0

(1)

(1)

1-2 : Lithium 3V Battery

2-3 : 1.2V from VDDCORE

(1)

1-2: DataFlash device (MN7)

2-3: DataFlash card interface (J22)

Warning: In this case NPCS03 must be configured as

input.

S2 Opened Disables the ICE NTRST input

S3 Closed Enables the ICE RTCK return. S6 must be opened

S4 Closed Enables the ICE NRST input

S5 Opened Selects ICE mode or JTAG mode (See Section 6, Errata )

S6 Opened Disables TCK <-> RTCK local loop. If S6 is closed, S3 must be

opened.

AT91SAM9261-EK Evaluation Board User Guide 4-1

6198C–ATARM–15-Dec-06

Page 24

Configuration Straps

Table 4-1. Configuration Jumpers and Straps

Default

Designation

S7-S8

S9

S10 Closed Enables the use of SDRAM (NCS1_SDCS)

S12 Opened Disables Serial DataFlash write protect.

S13 Closed Disables NAND FLASH write protect.

S14 Closed Enables the use of interrupt ETHERNET MAC (PC11_FIQ).

S15 Closed Enables the use of ETHERNET MAC (NCS2).

S16 Opened Disables the use of NWAIT ETHERNET MAC signal

S19 Closed Enables the use of the User LED DS7 (PA14)

S20 Closed Enables the use of the User LED DS8 (PA13)

S21 Closed Enables the use of the DBGU RXD signal (PA9)

S22 Closed Enables the use of the USB CNX detection (PB29)

S23 Closed Enables the use of AUDIO DAC INTERFACE (NPCS03)

S24 Closed Enables the use of TOUCH SCEEN CONTROLLER (NPCS02)

Setting Feature

Closed Enables the use of 18.432 MHz crystal. If external clock used,

Opened

S7-S8 must be opened and S9 closed.

(PC2_NWAIT)

S25 Closed Enables the use of TOUCH SCEEN CONTROLLER BUSY

signal (PA11)

S26 Closed Enables the use of TOUCH SCEEN CONTROLLER PENIRQ

(PC2_IRQ0)

TP1 N.A 3.3V Test point.

TP2 N.A GND Test point.

TP3 N.A 1.2V Test point.

TP4 N.A GND Test point.

TP63 N.A 0 to 3.3V analog user's input

TP64 N.A 0 to 3.3V analog user's input

TP65 N.A AGND of TP63

TP66 N.A AGND of TP64

Note: 1. These jumpers are provided for measuring power consumption. By default, they are

closed. To use this feature, the user has to open the strap and insert an ammeter.

4-2 AT91SAM9261-EK Evaluation Board User Guide

6198C–ATARM–15-Dec-06

Page 25

5.1 Schematics This section contains the following schematics:

! Power Supply and Audio

! AT91SAM9261

! SDRAM and NAND Flash

! Ethernet

! LCD and User Interface

! Serial and I/O Expansion

Section 5

Schematics

AT91SAM9261-EK Evaluation Board User Guide 5-1

6198C–ATARM–15-Dec-06

Page 26

8

D D

7

6

5

4

3

2

1

3V3

10 SQUARE CM COPPER AREA FOR HEAT SINKING

REGULATED

5V ONLY

J1J1

3

C C

1

2

C1

C1

330µF

330µF

Q2

Q2

Si1563EDH

Si1563EDH

5V

+

+

CR15VCR1

5V

R2

100KR2100K

J3J3

FORCE

POWER

ON

C9

15PFC915PF

1 32

R5

10KR510K

SHDN

WITH NO SOLDER MASK

LT1963AEQ-3.3

LT1963AEQ-3.3

C2

C2

MN1

MN1

10µF

10µF

10V

10V

2

VIN

SD

1

456

R6

10KR610K

GND

GND

6

3

VOUT

FB

R1

120RR1120R

3V3

POWER LED

J2J2

4

5

C3

10µFC310µF

M5V

C5

1µFC51µF

8

5V

C1M

5

VIN

C10

C10

4.7µF

4.7µF

1

EN

MN2

MN2

TP1TP1

3.3V

C4

10µFC410µF

TP2TP2

GND

C6

1µFC61µF

C1P6C2M3C2P

VOUT

TPS60500

TPS60500

GND

9

FB

PG

DS1

DS1

YELLOW

YELLOW

PA[0..31]

3

Q1

Q1

IRLML2402

IRLML2402

PA23

1

2

4

C7

22µFC722µF

7

R3

100KR3100K

1V2

C8

10PFC810PF

TP3TP3

1.2V

10

R4

2

200KR4200K

TP4TP4

GND

AUDIO DAC INTERFACE

J20

J20

3.5 PHONEJACK STEREO

3.5 PHONEJACK STEREO

3

1

4

2

C112 6V3

C112 6V3

+

+

+

+

C113

C113

100µF

100µF

100µF

100µF

6V3

6V3

MN15 AT73C213

MN15 AT73C213

PAINN

PAINN

15

VBAT

VBAT

12

CBP

CBP

14

HPP

HPP

13

HPN

HPN

11

LPHN

LPHN

10

PAINP

PAINP

16

MONOP

MONOP

30

MONON

MONON

29

LINER

LINER

7

LINEL

LINEL

6

AUXP

AUXP

31

AUXN

AUXN

32

HSR

HSR

4

HSL

HSL

3

INGND GNDD

INGND GNDD

8

GNDB

GNDB

33

DOUT

DOUT

DIN

DIN

CLK

CLK

CS

CS

SMODE

SMODE

RSTB

RSTB

VDIG

VDIG

AVDD

AVDD

AVDDHS

AVDDHS

VCM

VCM

VREF

VREF

MCLK

MCLK

SDIN

SDIN

LRFS

LRFS

BCLK

BCLK

23

SPI0_MISO

25

SPI0_MOSI

26

SPI0_SPCK

27

SPI0_NPCS3

28

22

21

24

2

5

C107 10µFC107 10µF

9

C111 10µFC111 10µF

1

20

17

19

18

R68

R68

47R

47R

3V3

R67

R67

100K

100K

NRST

C108

C108

100NF

100NF

GND_DAC

PCK2

TD1

TF1

TK1

S23S23

C109

C109

100NF

100NF

PA0

PA1

PA2

PA29

C110

C110

100NF

100NF

PB31

PA19

PA17

PA18

PA[0..31]

3V3

VCC_DAC

PB[0..31]

PA[0..31]

ADHESIVE FEET

Z3

Z4

11.1Z311.1

11.1Z411.1

B B

Z7

Z8

11.1Z711.1

11.1Z811.1

GND_DAC

VCC_DAC

C114

C114

10µF

10µF

10V

10V

L4

4.7µHL44.7µH

3V3

R69 0RR69 0R

GND_DAC

A A

JPGD01/18/06

JPGD01/18/06

JPGD01/18/06

JPG 14/09/05C

JPG 14/09/05C

JPG 14/09/05C

04/20/05JPGB

04/20/05JPGB

INIT EDIT

INIT EDIT

INIT EDIT

A

A

A

REV

REV

REV

SCALE

SCALE

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261-EK

POWER SUPPLY & AUDIO

POWER SUPPLY & AUDIO

POWER SUPPLY & AUDIO

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

8

7

6

5

4

3

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

SCALE

1/1

1/1

1/1

DES.

DES.

DES.

04/20/05JPGB

02/23/05

02/23/05

02/23/05

DATE

DATE

DATE

1

XX/XX/05JPG XXX

XX/XX/05JPG XXX

XX/XX/05JPG XXX

VER.

VER.

VER.

DATEMODIF.

DATEMODIF.

DATEMODIF.

REV. SHEET

REV. SHEET

REV. SHEET

1

1

1

D

D

D

6

6

6

Page 27

BOOT MODE SELECT

J4J4

8

PC[0..15]

PB[0..31]

PB3

BMS

R7 1KR7 1K

PA[0..31]

7

MN3

MN3

6

PB2

PB1

PB5

PB4

PB3

PB0

K17

L17

K16

PB7

PB8

PB6

J17

K15

H17

J16

H16

G17

5

PB13

PB12

PB9

PB10

PB11

H14

G16

G15

J15

PB17

PB16

PB15

PB14

E16

F14

H15

G14

PB21

PB19

PB22

PB20

PB18

D16

E15

B17

D15

E14

C16

PB27

PB29

PB26

PB25

PB28

PB24

PB23

A15

D13

D14

A17

D12

B15

B16

4

PC5

PC6

PC2

PC3

PC0

PC4

PB30

C13

PC1

PB31

B13

P6

U3

U2

T4

PC9

PC8

PC7

PC10

PC11

T8

T7

T6

P7

R7

P8

D16

PC15

PC14

PC12

PC13

T9

R9

U8

R8

3

D20

D19

D23

D22

D21

D17

D18

M3

D28

D29

D30

D26

D24

D25

T3

U1

P4

D31

D27

N3

P5

R5

R4

P2

2

D[0..31]

A[0..22]

1

ETM

D D

PA13

PIPESTAT[0]

PA14

PIPESTAT[1]

PA15

PIPESTAT[2]

PA11

TRACESYNC

PA16

TRACEPKT[0]

PA17

TRACEPKT[1]

PA18

TRACEPKT[2]

PA19

TRACEPKT[3]

PA20

TRACEPKT[4]

PA21

TRACEPKT[5]

PA22

TRACEPKT[6]

PA23

TRACEPKT[7]

PA12

3V3

14

16

18

20

J10J10

VSUPPLY

EXTTRIG

TRACECLK

R90RR9

0R

C11

C11

100NF

100NF

J6J6

12

34

56

78

910

1112

13

15

17

19

Z14

Z14

CR1225

CR1225

+

+

3V

3V

8

3V3

R8

10KR810K

C C

B B

A A

TRACE PORT

38

36

34

32

30

28

26

24

22

20

18

16

14

12

10

8

6

4

2

G1G2G3G4G5

NOT POPULATED

678

RR1

RR1

100K

100K

ICE INTERFACE

15234

ICE_NTRST

TDI

TMS

TCK

ICE_RTCK

ICE_NRST

MMBD1704A

MMBD1704A

R15 1KR15 1K

TDO

NOT POPULATED

3V3

VDDOSC + VDDPLL

CURRENT MEASURE

CR2

CR2

3V3

J7

J7

J8J8

2

1

37

35

33

31

29

27

25

23

21

19

17

15

13

11

9

7

5

3

1

J5J5

S4S4

S6S6

2 3

SMB MALE

SMB MALE

3

C126

C126

100NF

100NF

TRACEPKT[8]

TRACEPKT[9]

TRACEPKT[10]

TRACEPKT[11]

TRACEPKT[12]

TRACEPKT[13]

TRACEPKT[14]

TRACEPKT[15]

ICE_NTRST

TDI

TMS

TCK

ICE_RTCK

TDO

ICE_NRST

DBGRQ

GND

S2S2

S3S3

NRST

C14

C14

4.7NF

4.7NF

C16

C16

10PF

10PF

1

54

C19

C19

10PF

10PF

C20

C20

10PF

10PF

3

VDD

2

R10

R10

10K

10K

C12

C12

4.7NF

4.7NF

C17

C17

10PF

10PF

MN10

MN10

R1100D121C

R1100D121C

GND

OUT

1

WAKE UP

BP2BP2

7

PA24

PA25

PA26

PA27

PA28

PA29

PA30

PA31

3V3

R11 1,96K

R11 1,96K

C13

C13

C15

C15

J9J9

VDDBU

SHDN

WKUP

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PA8

PA9

PA10

PA11

PA12

PA13

PA14

PA15 D10

PA16

PA17

PA18

PA19

PA20

PA21

PA22

PA23

PA24

PA25

PA26

PA27

PA28

PA29

PA30

PA31

DDP

DDM

HDPA

HDMA

HDPB

HDMB

470pF

470pF

R12 1,5K

R12 1,5K

470pF

470pF

Y1

Y1

18.4320MHz

18.4320MHz

1 2

32.768 kHz

32.768 kHz

Y2

Y2

1 4

1V2

3

2

1

R11

T12

U13

P10

T13

U14

T14

R12

T15

U16

R13

T16

U15

R14

T17

P13

P14

R15

R17

P16

P17

N15

N14

N16

N17

M14

M15

L15

M16

M17

L14

L16

A12

B12

C12

B14

A13

A14

E17

C17

D17

U17

F16

S5S5

B10

F17

1%

1%

U9

1%

1%

U10

S7S7

U12

S8S8

U11

S9S9

T10

C18

C18

100NF

100NF

T11

A10

A11

R10

C21

C21

100NF

100NF

P9

NOT POPULATED

PA0/SPI0_MISO/MCDA0

PA1/SPI0_MOSI/MCCDA

PA2/SPI0_SPCK/MCCK

PA3/SPI0_NPCS0

PA4/SPI0_NPCS1/MCDA1

PA5/SPI0_NPCS2/MCDA2

PA6/SPI0_NPCS3/MCDA3

PA7/TWD/PCK0

PA8/TWCK/PCK1

PA9/DRXD/PCK2

PA10/DTXD/PCK3

PA11/TSYNK/SCK1

PA12/TCLK/RTS1

PA13/TPS0/CTS1

PA14/TPS1/SCK2

PA15/TPS2/RTS2

PA16/TPK0/CTS2

PA17/TPK1/TF1

PA18/TPK2/TK1

PA19/TPK3/TD1

PA20/TPK4/RD1

PA21/TPK5/RK1

PA22/TPK6/RF1

PA23/TPK7/RTS0

PA24/TPK8/SPI1_NPCS1

PA25/TPK9/SPI1_NPCS2

PA26/TPK10/SPI1_NPCS3

PA27/TPK11/SPI0_NPCS1

PA28/TPK12/SPI0_NPCS2

PA29/TPK13/SPI0_NPCS3

PA30/TPK14/A23

PA31/TPK15/A24

DDP

DDM

HDPA

HDMA

HDPB

HDMB

TDI

TMS

TCK

RTCK

TDO

JTAGSEL

NTRST

PLLRCB

PLLRCA

XOUT

XIN

VDDOSC

GNDOSC

XOUT32

XIN32

VDDPLL

GNDPLL

WKUP

R16R16

R17

R17

100K

100K

B11

6

D9

SHDN

C22

C22

100NF

100NF

CFCE1/PC6U5CFCE2/PC7

LCDVSYNC/PB0

LCDHSYNK/PB1

BMS/LCDDEN/PB3

LCDD0/LCDD3/PB5

LCDD1/LCDD4/PB6

LCDD2/LCDD5/PB7

LCDD3/LCDD6/PB8

LCDCC/LCDD2/PB4

LCDDOTCK/PCK0/PB2

GNDBU

VDDBU

B9

C9

C24

C24

100NF

100NF

C23

C23

10µF

10µF

10V

10V

LCDD4/LCDD7/PB9

LCDD5/LCDD10/PB10

LCDD6/LCDD11/PB11

LCDD7/LCDD12/PB12

LCDD8/LCDD13/PB13

LCDD9/LCDD14/PB14

LCDD10/LCDD15/PB15

LCDD11/LCDD19/PB16

AT91SAM9261

AT91SAM9261

VDDCORE

VDDCORE

VDDCORED5VDDCORE

C25

C25

100NF

100NF

K14

C26

C26

100NF

100NF

M4

P12

C27

C27

100NF

100NF

GND

GNDC7GND

A16

C11

J12J12

VDDCORE CURRENT MEASURE

5

LCDD12/LCDD20/PB17

LCDD13/LCDD21/PB18

GNDD3GNDH8GNDH9GND

TF0/LCDD16/PB21

TK0/LCDD17/PB22

TD0/LCDD18/PB23

RF0/LCDD21/PB26

RK0/LCDD20/PB25

RD0/LCDD19/PB24

SPI1_NPCS1/LCDD22/PB27

GNDK8GNDK9GND

SPI1_MISO/IRQ1/PB30

SPI1_SPCK/IRQ2/PB29

SPI1_MOSI/PCK2/PB31

SPI1_NPCS0/LCDD23/PB28

GNDR3GND

GNDU4GND

U7

K10

R16

C28

C28

10µF

10µF

10V

10V

LCDD14/LCDD22/PB19

LCDD15/LCDD23/PB20

GNDJ3GNDJ8GNDJ9GND

J10

H10

1V2

A25/CFRNW/PC3

NWAIT/IRQ0/PC2

NCS4/CFCS0/PC4R6NCS5/CFCS1/PC5

NANDOE/NCS6/PC0

NANDWE/NCS7/PC1

VDDIOMC3VDDIOMC5VDDIOMC8VDDIOMD4VDDIOMH3VDDIOML4VDDIOM

C31

C31

C29

C29

100NF

100NF

100NF

100NF

C30

C30

C32

C32

100NF

100NF

100NF

100NF

4

TXD0/PCK2/PC8

C33

C33

100NF

100NF

CTS0/FIQ/PC11

RXD0/PCK3/PC9

RTS0/SCK0/PC10

TXD1/NCS6/PC12

RXD1/NCS7/PC13

TXD2/SPI1_NPCS2/PC14

N4

C35

C35

100NF

100NF

C34

C34

100NF

100NF

RXD2/SPI1_NPCS3/PC15

D16/TCLK0/PC16P1D17/TCLK1/PC17N2D18/TCLK2/PC18

C36

C36

100NF

100NF

D19/TIOA0/PC19R1D20/TIOB0/PC20T1D21/TIOA1/PC21R2D22/TIOB1/PC22P3D23/TIOA2/PC23T2D24/TIOB2/PC24

VDDIOP

VDDIOP

C15

D11

C37

C37

100NF

100NF

3

C38

C38

100NF

100NF

VDDIOP

J14

VDDIOP

P11

C39

C39

100NF

100NF

D25/TF2/PC25

D26/TK2/PC26

VDDIOP

P15

C40

C40

100NF

100NF

D27/TD2/PC27

D30/RF2/PC30

D29/RK2/PC29

D28/RD2/PC28

D31/PCK1/PC31

D10

D11

D12

D13

D14

D15

NBS0/A0

NWR2/NBS2/A1

A10

A11

A12

A13

A14

A15

BA0/A16

BA1/A17

A18

A19

A20

A21

A22

RAS

CAS

SDWE

SDA10

SDCKE

SDCK

NCS0

SDCS/NCS1

NCS2

NANDCS/NCS3

CFOE/NRD

CFWE/NWE/NWR0

CFIOR/NBS1/NWR1

CFIOW/NBS3/NWR3

NRST

TST

NC

NC

NC

VDDIOPT5VDDIOP

3V3

U6

C43

C43

10µF

10µF

10V

10V

C42

C42

100NF

100NF

C41

C41

100NF

100NF

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

A2

A3

A4

A5

A6

A7

A8

A9

G2

H1

H2

J1

J2

K1

K4

K2

L1

K3

L2

L3

M1

N1

M2

D8

B8

A8

A7

B7

D7

A6

B6

C6

A5

D6

B5

A4

B4

A3

B3

A2

C4

B2

A1

B1

C2

C1

F2

J4

G3

E4

F1

H4

F4

D2

D1

G4

E3

E2

E1

F3

F15

C10

A9

C14

D10

D1

D2

D3

D4

D5

D6

D7

D8

D9

D11

D12

D13

D14

D15

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

RAS

CAS

SDWE

SDA10

SDCKE

SDCK

NCS0

SDCS_NCS1

NCS2

SMCS_NCS3

CFOE_NOE_NRD

CFWE_NWE_NWR0

CFIOR_NBS1_NWR1

CFIOW_NBS3_NWR3

3V3

R131KR13

1K

R141KR14

1K

NRST

BP1BP1

D0

G1

RESET

INIT EDIT

INIT EDIT

INIT EDIT

A

A

A

REV

REV

REV

SCALE

SCALE

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261

AT91SAM9261

AT91SAM9261

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

SCALE

1/1

1/1

1/1

JPGD01/18/06

JPGD01/18/06

JPGD01/18/06

JPG 14/09/05C

JPG 14/09/05C

JPG 14/09/05C

04/20/05JPGB

04/20/05JPGB

04/20/05JPGB

02/23/05

02/23/05

02/23/05

DES.

DES.

DES.

DATE

DATE

DATE

1

XX/XX/05JPG XXX

XX/XX/05JPG XXX

XX/XX/05JPG XXX

VER.

VER.

VER.

DATEMODIF.

DATEMODIF.

DATEMODIF.

REV. SHEET

REV. SHEET

REV. SHEET

2

2

2

D

D

D

6

6

6

Page 28

8

7

6

5

4

3

2

1

EBI SDRAM INTERFACE

A[0..22]

D[0..31]

RAS

CAS

D D

CFIOR_NBS1_NWR1

CFIOW_NBS3_NWR3

C C

SDWE

SDA10

SDCKE

SDCK

SDCS_NCS1

R18

R18

100K

100K

3V3

MN4

A2

A4

A5

A6

A7

A8

A9

A10

A11

SDA10

A13

A16

BA0

A17

BA1

A14

SDCKE

SDCK

NBS0 NBS2

A0

CFIOR_NBS1_NWR1

CAS

RAS

SDWE

23

24

25

26

29

30

31

32

33

34

22

35

20

21

36

40

37

38

15

39

17

18

16

19

MN4

A0

MT48LC16M16A2

MT48LC16M16A2

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

BA0

BA1

A12

N.C

CKE

CLK

DQML

DQMH

CAS

RAS

WE

CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

D0

2

D1

4

D2

5

D3

7

D4

8

D5

10

D6

11

D7

13

D8

42

D9

44

D10

45

D11

47

D12

48

D13

50

D14

51

D15

53

1

14

27

3

9

43

49

28

41

54

C50

C50

C51

100NF

100NF

C44

C44

100NF

100NF

C51

100NF

100NF

C45

C45

100NF

100NF

6

12

46

52

C52

C52

100NF

100NF

C46

C46

100NF

100NF

C53

C53

100NF

100NF

A2

A3A3

A4

A5

A6

A7

A8

A9

A10

A11

SDA10

A13

A16

BA0

A17

BA1

A14

SDCKE

SDCK

A1

CFIOW_NBS3_NWR3

CAS

RAS

SDWE

23

24

25

26

29

30

31

32

33

34

22

35

20

21

36

40

37

38

15

39

17

18

16

19

MN5

MN5

A0

MT48LC16M16A2

MT48LC16M16A2

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

BA0

BA1

A12

N.C

CKE

CLK

DQML

DQMH

CAS

RAS

WE

CS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

1

14

27

3

9

43

49

28

41

54

6

12

46

52

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

3V33V3

C54

C54

100NF

100NF

C47

C47

100NF

100NF

C55

C55

100NF

100NF

C48

C48

100NF

100NF

C56

C56

100NF

100NF

C49

C49

100NF

100NF

C57

C57

100NF

100NF

S10S10

256 Mbits 256 Mbits

PA[0..31]

DUAL FOOTPRINT

D[0..31]

PC[0..15]

3V3

B B

A A

R19

R19

100K

100K

S13S13

A21

A22

PC0

PC1

PC14

PC15

WP

16

17

8

18

9

7

19

1

2

3

4

5

6

10

11

14

15

20

21

22

23

24

34

35

16-bit bus width 8-bit bus width

MN6AMN6A

CLE

ALE

RE

WE

CE

R/B

WP

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

I/O9

I/O10

I/O11

I/O12

I/O13

I/O14

I/O15

N.C

PRE

N.C

VCC

VCC

VSS

VSS

VSS

D0

26

D1

28

D2

30

D3

32

D4

40

D5

42

D6

44

D7

46

D8

27

D9

29

D10

31

D11

33

D12

41

D13

43

D14

45

D15

47

39

38

36

3V3

37

12

48

25

13

C59

C59

100NF

100NF

C60

C60

100NF

100NF

A21

A22

PC0

PC1

PC14

PC15

WP

MN6BMN6B

16

CLE

17

ALE

8

RE

18

WE

9

CE

7

R/B

19

WP

1

N.C

2

N.C

3

N.C

4

N.C

5

N.C

6

N.C

10

N.C

11

N.C

14

N.C

15

N.C

20

N.C

21

N.C

22

N.C

23

N.C

24

N.C

25

N.C

26

N.C

NOT POPULATED

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

N.C

N.C

N.C

N.C

N.C

N.C

PRE

N.C

N.C

N.C

N.C

N.C

VCC

VCC

VSS

VSS

PA0

D0

29

D1

30

D2

31

D3

32

D4

41

D5

42

D6

43

D7

44

48

47

46

45

40

39

38

35

34

33

28

27

37

12

36

13

3V3

PA1

PA2

3V3

1

PA3

2

3

PA4

PA0

SPI0_MISO MCDA0

PA2

SPI0_SPCK MCCK

PA1

SPI0_MOSI MCCDA

PA6

SPI0_NPCS3 MCDA3

PA5

J21J21

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

SPI0_NPCS0

R20 100KR20 100K

NRST

MCDA1

3V3

MCDA2

3V3

R72

R72

10K

10K

C115

C115

100NF

100NF

MN7MN7

8

1

2

4

3

VCC

SO

SI

SCK

GND

CS

RESET

WP

WRITE PROTECT

NORMALLY OPEN

SD CARD / MMC CARD

DATAFLASH CARD

INTERFACE

J22

J22

8

7

6

5

4

3

2

1

9

FPS009

FPS009

3V3

6

C58

C58

100NF

100NF

7

5

S12S12

JPGD01/18/06

JPGD01/18/06

JPGD01/18/06

JPG 14/09/05C

JPG 14/09/05C

JPG 14/09/05C

04/20/05JPGB

04/20/05JPGB

INIT EDIT

INIT EDIT

INIT EDIT

A

A

A

REV

REV

REV

SCALE

SCALE

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261-EK

SDRAM & NANDFLASH

SDRAM & NANDFLASH

SDRAM & NANDFLASH

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

8

7

6

5

4

3

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

SCALE

1/1

1/1

1/1

DES.

DES.

DES.

04/20/05JPGB

02/23/05

02/23/05

02/23/05

DATE

DATE

DATE

1

VER.

VER.

VER.

REV.

REV.

REV.

D

D

D

XX/XX/05JPG XXX

XX/XX/05JPG XXX

XX/XX/05JPG XXX

DATEMODIF.

DATEMODIF.

DATEMODIF.

SHEET

SHEET

SHEET

3

3

3

6

6

6

Page 29

8

7

6

5

4

3

2

1

DS2

D D

3V3

R23

R23

4,7K

4,7K

DS2

DS3

DS3

DS4

DS4

GREEN

GREEN

YELLOW

YELLOW

GREEN

GREEN

LINK&ACT

FULL DUPLEX

SPEED 100

3V3

R21 1KR21 1K

R22 1KR22 1K

R24 1KR24 1K

Note1: 8/16 bit DataBus

selection; Removed R27

when using 16-bit mode;

otherwise is 8-bit mode.

61

71

73

3V3

MN8

MN8

NOT POPULATED

R27

R27

4,7K

4,7K

D[0..15]

A[0..22]

PC[0..15]

C C

D15

D14

D13

D12

D11

D10

D9

D8

A2

PC11

FIQ

NRST

S14S14

3V3

3V3

R28

R28

4,7K

4,7K

100

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

DGND

NC

LINK_O

WAKEUP

PW_RST#

DGND

SD15

SD14

SD13

SD12

SD11

SD10

SD9

SD8

DVDD

IO16

CMD

SA4

SA5

SA6

SA7

SA8

SA9

DGND

INT

75

NC74NC

DVDD72DVDD

GPIO068GPIO169GPIO270GPIO3

IOR#1IOW#2AEN3IOWAIT4DVDD5SD06SD17SD28SD39SD410SD511SD612SD713RST14DGND15TEST116TEST217TEST318TEST419DVDD20X2_25M21X1_25M22DGND23SD24AGND

3V3

63

65

62

66

64

67

EEDI

EECK

EEDO

DGND

EECS/LED

DM9000

DM9000

LINKACT#

57

58

59

60

DUP#

DGND

SPEED#

CLK20MO

53

55

54

56

MDC

MDIO

DVDD

TX_EN

25

TXD151TXD252TXD3

3V3

TXD0

TX_CLK

TEST5

RX_CLK

RX_ER

RX_DV

COL

CRS

DGND

RXD3

RXD2

RXD1

RXD0

LINK_I

DVDD

AVDD

TXO-

TXO+

AGND

AGND

RXI-

RXI+

AVDD

AVDD

BGRES

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

R31

R31

6,80K

6,80K

1%

1%

3V3

VCCA

VCCA

L1 742792093L1 742792093

R25

R25

49R9

49R9

1%

1%

R29

R29

49R9

49R9

1%

1%

C61

C61

100NF

100NF

C64

C64

100NF

100NF

R26

R26

49R9

49R9

1%

1%

C62 100NFC62 100NF

R30

R30

49R9

49R9

1%

1%

C63

C63

100NF

100NF

15

J13 J0026D21

J13 J0026D21

TD+

TD+

1

CT

CT

3

TD-

TD-

2

RD+

RD+

7

CT

CT

6

RD-

RD-

8

4

1nF

5

1nF

16

7575

7575

75

75

75

75

TX+

TX+

TX-

TX-

RX+

RX+

RX-

RX-

1

1

2

2

3

3

6

6

4

4

5

5

7

7

8

8

R32

3V3

6

R32

100K

100K

R34

R34

4,7K

4,7K

Y3

Y3

25MHz

1 2

C66

C66

22PF

22PF

5

25MHz

C67

C67

22PF

22PF

R70 0RR70 0R

4

3V3 VCCA

C76

C76

10µF

10µF

10V

10V

C77

C77

100NF

100NF

L2

4.7µHL24.7µH

R71 0RR71 0R

C78

C78

10µF

10µF

10V

10V

C79

C79

100NF

100NF

3

C68

C68

100NF

100NF

3V33V3

C69

C69

100NF

100NF

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261-EK

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

3V3 3V3 3V33V3

C70

C70

100NF

100NF

ETHERNET

ETHERNET

ETHERNET

2

C71

C71

100NF

100NF

C72

C72

100NF

100NF

A

A

A

REV

REV

REV

SCALE

SCALE

SCALE

C73

C73

100NF

100NF

INIT EDIT

INIT EDIT

INIT EDIT

1/1

1/1

1/1

JPGD01/18/06

JPGD01/18/06

JPGD01/18/06

JPG 14/09/05C

JPG 14/09/05C

JPG 14/09/05C

DES.

DES.

DES.

VCCA VCCA

C74

C74

100NF

100NF

04/20/05JPGB

04/20/05JPGB

04/20/05JPGB

02/23/05

02/23/05

02/23/05

DATE

DATE

DATE

1

C75

C75

100NF

100NF

VER.

VER.

VER.

REV.

REV.

REV.

D

D

D

XX/XX/05JPG XXX

XX/XX/05JPG XXX

XX/XX/05JPG XXX

DATEMODIF.

DATEMODIF.

DATEMODIF.

SHEET

SHEET

SHEET

4

4

4

6

6

6

B B

CFOE_NOE_NRD

CFWE_NWE_NWR0

D0

D1

D2

D3

D4

D5

D6

D7

PC10

RST

PC2

NWAIT

NOT USED

A A

8

NCS2

S15S15

S16S16

7

Page 30

8

7

6

5

4

3

3V3

2

1

3V3

54132-4097

54132-4097

40

39

D D

Z17 TX09D71VM1CCAZ17 TX09D71VM1CCA

C C

J23

J23

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

C124

C124

100NF

100NF

X_RIGHT

Y_LOW

X_LEFT

Y_UP

Vctrl

PCI

B0

B1

B2

B3

B4

B5

G0

G1

G2

G3

G4

G5

R0

R1

R2

R3

R4

R5

DTMG

HSYNC

DCLK

VCTRL

LCDD18

LCDD19

LCDD20

LCDD21

LCDD22

LCDD23

LCDD10

LCDD11

LCDD12

LCDD13

LCDD14

LCDD15

LCDD2

LCDD3

LCDD4

LCDD5

LCDD6

LCDD7

LCDDEN

LCDHSYNC

LCDDDOTCK

3V3

C125

C125

10V

10V

10µF

10µF

PB23

PB24

PB25

PB26

PB27

PB28

PB15

PB16

PB17

PB18

PB19

PB20

PB7

PB8

PB9

PB10

PB11

PB12

PB3

PB1

PB2

LCDCC

R75

R75

10K

10K

C87

C87

4.7NF

4.7NF

3

2

Q6

Q6

IRLML2402

IRLML2402

R83 10KR83 10K

C84

C84

100NF

100NF

1

MN11

MN11

1

RST

2

IN

3

N.C

4

GND

MC34064D

MC34064D

PA12

VCTRLPB4

PB[0..31]

M5V

8

N.C

7

N.C

6

N.C

5

N.C

POWER CONTROL IN

X_LEFT

Y_UP

X_RIGHT

Y_LOW

R73 0RR73 0R

R76 0RR76 0R

R77 0RR77 0R

R78 0RR78 0R

NOT POPULATED

C116

C116

10NF

10NF

C117

C117

10NF

10NF

C118

C118

10NF

10NF

TOUCH SCREEN CONTROLLER

MN16

MN16

2

XP

3

YP

4

XM

5

YM

C119

C119

10NF

10NF

R80

R80

100K

100K

R81 100KR81 100K

TP63TP63

AGND

TP65TP65

TWO USER'S ANALOG INPUTS

Full-Scale Input Span 0 to VREF

TP64TP64

TP66TP66

7

IN3

8

IN4

ADS7843E

ADS7843E

DCLK

DIN

DOUT

CS

BUSY

PENIRQ

VREF

VCC

VCC

GND

R84

R84

100K

100K

C122

C122

100NF

100NF

C121

C121

100NF

100NF

R74 47RR74 47R

C123

C123

100NF

100NF

16

14

12

15

13

11

9

1

10

6

S24S24

S25S25

S26S26

R79 0RR79 0R

PA12

PA2

PA1

PA0

PA28

PA11

PC2

SPI0_SPCK

SPI0_MOSI

SPI0_MISO

SPI0_NPCS2

BUSY

IRQ0

L5 4.7µHL5 4.7µH

C120

C120

10µF

10µF

10V

10V

R82 0RR82 0R

3V3

PA[0..31]

PC[0..15]

PA[0..31]

B B

3V3

GREEN

GREEN

DS7

DS7

GREEN

GREEN

DS8

DS8

A A

R50 220RR50 220R

R51 220RR51 220R

S19S19

S20S20

PA14

PA13

PA27

PA26

PA25

PA24

BP3BP3

BP4BP4

BP5BP5

BP6BP6

USER INTERFACE

JPGD01/18/06

JPGD01/18/06

JPGD01/18/06

JPG 14/09/05C

JPG 14/09/05C

JPG 14/09/05C

04/20/05JPGB

04/20/05JPGB

INIT EDIT

INIT EDIT

INIT EDIT

A

A

A

REV

REV

REV

SCALE

SCALE

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261-EK

LCD & USER'S INTERFACE

LCD & USER'S INTERFACE

LCD & USER'S INTERFACE

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

8

7

6

5

4

3

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

SCALE

1/1

1/1

1/1

DES.

DES.

DES.

04/20/05JPGB

02/23/05

02/23/05

02/23/05

DATE

DATE

DATE

1

VER.

VER.

VER.

REV.

REV.

REV.

D

D

D

XX/XX/05JPG XXX

XX/XX/05JPG XXX

XX/XX/05JPG XXX

DATEMODIF.

DATEMODIF.

DATEMODIF.

SHEET

SHEET

SHEET

5

5

5

6

6

6

Page 31

8

7

6

5

4

3

2

1

MN13

MN13

1 16

C1+V+VCC

C91

C91

100NF

100NF

C94

C94

100NF

100NF

R52 0RR52 0R

D D

C C

B B

A A

EXPANSION CONNECTORS

PA[0..31] PB[0..31] PC[0..15]

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PA8

PA9

PA10

PA11

PA12

PA13

PA14

PA15

PA16

PA17

PA18

PA19

PA20

PA21

PA22

PA23

PA24

PA25

PA26

PA27

PA28

PA29

PA30

PA31

A[0..22] D[0..31]

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PB8

PB9

PB10

PB11

PB12

PB13

PB14

PB15

PB16

PB17

PB18

PB19

PB20

PB21

PB22

PB23

PB24

PB25

PB26

PB27

PB28

PB29

PB30

PB31

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

PC8

PC9

PC10

PC11

PC12

PC13

PC14

PC15

NRST

VDDBU

NOT POPULATED NOT POPULATED

PB0

PB2

PB4

PB6

PB8

PB10

PB12

PB14

PB16

PB18

PB20

PB22

PB24

PB26

PB28

PB30

PA0

PA2

PA4

PA6

PA8

PA10

PA12

PA14

PA16

PA18

PA20

PA22

PA24

PA26

PA28

PA30

PC0

PC2

PC4

PC6

PC8

PC10

PC12

PC14

D16

D18

D20

D22

D24

D26

D28

D30

3V3

5V

101

103

105

107

109

111

113

115

117

119

J16J16

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

PB1

PB3

PB5

PB7

PB9

PB11

PB13

PB15

PB17

PB19

PB21

PB23

PB25

PB27

PB29

PB31

PA1

PA3

PA5

PA7

PA9

PA11

PA13

PA15

PA17

PA19

PA21

PA23

PA25

PA27

PA29

PA31

PC1

PC3

PC5

PC7

PC9

PC11

PC13

PC15

D17

D19

D21

D23

D25

D27

D29

D31

3V3

5V

SDCS_NCS1

CFIOR_NBS1_NWR1

CFOE_NOE_NRD

CFIOW_NBS3_NWR3

SDWE

WKUP

SHDN

A1

A4

A7

A11

A13

A15

A18

A0

A10

A17

A21

A22

RAS

CAS

D2

D3

D10

D8

D12

D11

D6

3V3

3V3

5V

USER'S GRID AERA

3V3 5V

J17J17

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

2

A2

4

A3

6

A6

8

A9

10

A12

12

A14

14

A16

16

A19

18

A5

20

A8

22

A20

24

26

28

30

32

34

36

38

40

42

44

46

D1

48

D0

50

D5

52

D7

54

D4

56

D15

58

D13

60

D14D9

62

64

66

68

70

72

74

76

78

80

5V

1.27 PITCH

2.54 PITCH

3V3

3V3

SDCKE

NCS2

CFWE_NWE_NWR0

SDA10

NCS0

SDCK

SMCS_NCS3

5V3V3

HDMA

HDPA

HDMB

HDPB

NRST

DDM

DDP

PA10

PA9

S21S21

DBGU_TXD

DBGU_RXD

USB HOST INTERFACE

PB29

PB30

S22S22

USB_CNX

USB_DP_PUP

USB DEVICE INTERFACE

C1+V+VCC

3

C1-

C1-

4

C2+

C2+

5

C2- V-

C2- V-

11

T

T

10

T

T

12

9 8

ADM3202ARN

ADM3202ARN

R54

R54

R55 39RR55 39R

R58

R58

R59 39RR59 39R

R63

R63

22K

22K

GND

GND

R

R

R

R

R62 15KR62 15K

C105

C105

15PF

15PF

15

2

6

14

7

13

39R

39R

R56

R56

15K

15K

39R

39R

R60

R60

15K

15K

MN14

MN14

1

2

3

GND

GND

SN74LVC1G00DBV

SN74LVC1G00DBV

3V3

C92

C92

100NF

100NF

R53 0RR53 0R

R57

R57

15K

15K

R61

R61

15K

15K

VCC

VCC

R65

R65

R66

R66

C106

C106

15PF

15PF

C93

C93

100NF

100NF

C95

C95

100NF

100NF

SERIAL DEBUG PORT

C96

C96

47pF

47pF

C100

C100

47pF

47pF

NOT POPULATED

3V3

5

4

C102

C102

100NF

100NF

39R

39R

39R

39R

5V

C97

C97

47pF

47pF

C101

C101

47pF

47pF

Q5

Q5

IRLML6302

IRLML6302

1

R64

R64

1,5K

1,5K

3 2

C98

C98

100NF

100NF

C103

C103

33PF

33PF

F1

F1

500 mA

500 mA

J18

J18

CCUSBA-32002-30X

CCUSBA-32002-30X

A1

A

A

A2

A3

A4

B

B

1 2

2

3

MALE RIGHT ANGLED

MALE RIGHT ANGLED

1

3 4

J19J19

5 6

6

2

7

3

8

4

9

5

B1

B2

B3

B4

RXD

TXD

J15

J15

10

11

F2

F2

500 mA

500 mA

C99

C99

100NF

100NF

1

4

C104

C104

100NF

100NF

JPGD01/18/06

JPGD01/18/06

JPGD01/18/06

JPG 14/09/05C

JPG 14/09/05C

JPG 14/09/05C

04/20/05JPGB

04/20/05JPGB

INIT EDIT

INIT EDIT

INIT EDIT

A

A

A

REV

REV

REV

SCALE

SCALE

AT91SAM9261-EK

AT91SAM9261-EK

AT91SAM9261-EK

SERIAL & I/O EXPANSION

SERIAL & I/O EXPANSION

SERIAL & I/O EXPANSION

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

8

7

6

5

4

3

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

SCALE

1/1

1/1

1/1

DES.

DES.

DES.

04/20/05JPGB

02/23/05

02/23/05

02/23/05

DATE

DATE

DATE

1

XX/XX/05JPG XXX

XX/XX/05JPG XXX

XX/XX/05JPG XXX

VER.

VER.

VER.

DATEMODIF.

DATEMODIF.

DATEMODIF.

REV. SHEET