Page 1

Tj

-30 /

standard specification

ANSALDO

Ansaldo Trasporti s.p.a.

Unita' Semiconduttori

PHASE CONTROL THYRISTOR AT604

Repetitive voltage up to 1600 V

Mean on-state current 605 A

Surge current 8.4 kA

FINAL SPECIFICATION

feb 97 - ISSUE : 03

Via N. Lorenzi 8 - I 16152 GENOVA - ITALY

Tel. int. +39/(0)10 6556549 - (0)10 6556488

Fax Int. +39/(0)10 6442510

Tx 270318 ANSUSE I -

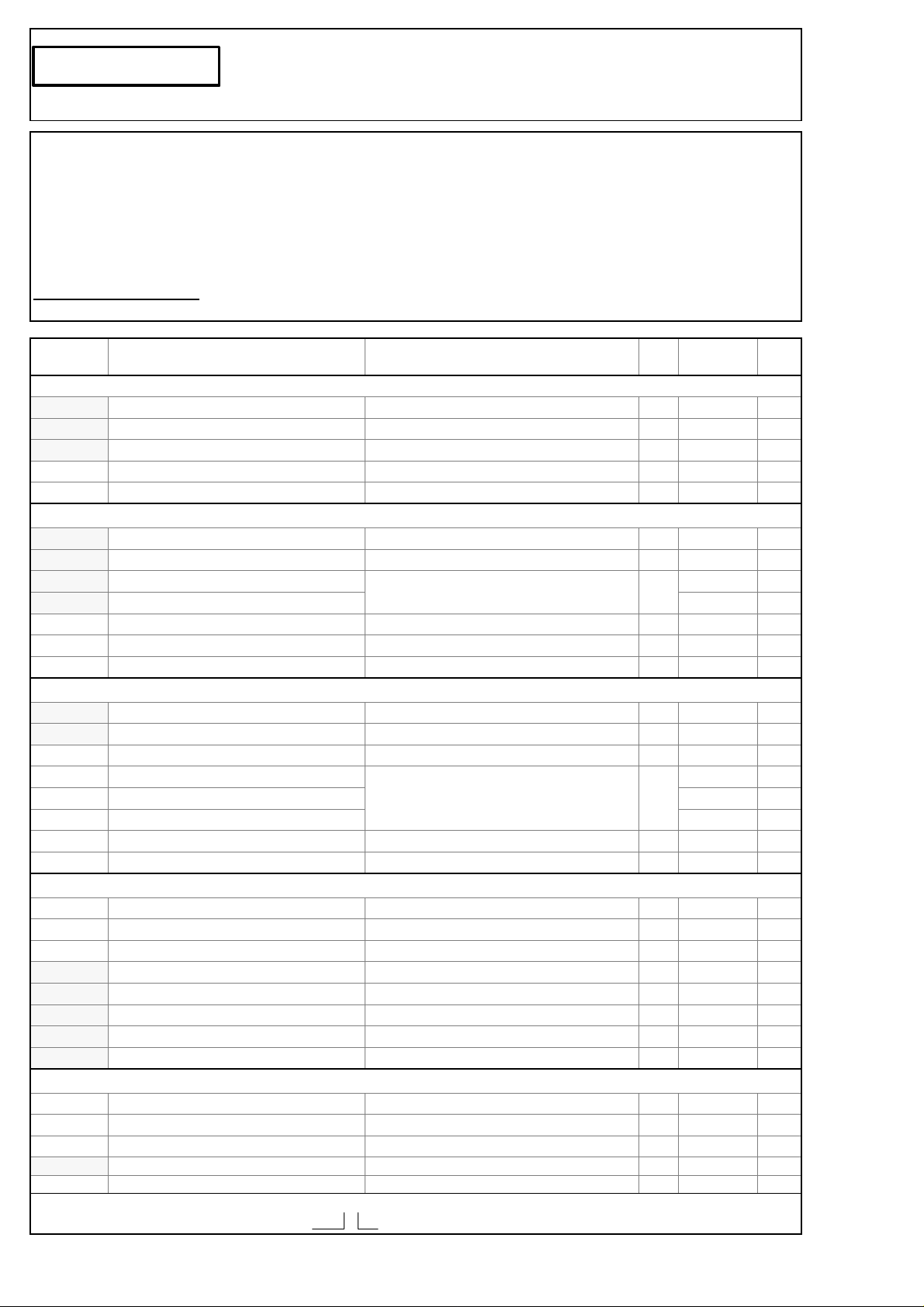

Symbol Characteristic Conditions

[°C]

Value Unit

BLOCKING

V RRM Repetitive peak reverse voltage 125 1600 V

V RSM Non-repetitive peak reverse voltage 125 1700 V

V DRM Repetitive peak off-state voltage 125 1600 V

I RRM Repetitive peak reverse current V=VRRM 125 50 mA

I DRM Repetitive peak off-state current V=VDRM 125 50 mA

CONDUCTING

I T (AV) Mean on-state current 180° sin, 50 Hz, Th=55°C, double side cooled 605 A

I T (AV) Mean on-state current 180° sin, 50 Hz, Tc=85°C, double side cooled 530 A

I TSM Surge on-state current sine wave, 10 ms 125 8.4 kA

I² t I² t without reverse voltage 353 x1E3 A²s

V T On-state voltage On-state current = 1000 A 25 1.6 V

V T(TO) Threshold voltage 125 1.05 V

r T On-state slope resistance 125 0.850 mohm

SWITCHING

di/dt Critical rate of rise of on-state current, min. From 75% VDRM up to 660A, gate 10V 5ohm 125 200 A/µs

dv/dt Critical rate of rise of off-state voltage, min. Linear ramp up to 70% of VDRM 125 500 V/µs

td Gate controlled delay time, typical VD=100V, gate source 10V, 10 ohm , tr=.5 µs 25 1.3 µs

tq Circuit commutated turn-off time, typical dV/dt = 20 V/µs linear up to 75% VDRM 200 µs

Q rr Reverse recovery charge di/dt=-20 A/µs, I= 450A 125 µC

I rr Peak reverse recovery current VR= 50 V A

I H Holding current, typical VD=5V, gate open circuit 25 300 mA

I L Latching current, typical VD=5V, tp=30µs 25 700 mA

GATE

V GT Gate trigger voltage VD=5V 25 3.5 V

I GT Gate trigger current VD=5V 25 200 mA

V GD Non-trigger gate voltage, min. VD=VDRM 125 0.25 V

V FGM Peak gate voltage (forward) 30 V

I FGM Peak gate current 10 A

V RGM Peak gate voltage (reverse) 5 V

P GM Peak gate power dissipation Pulse width 100 µs 150 W

P G Average gate power dissipation 2 W

MOUNTING

R th(j-h) Thermal impedance, DC Junction to heatsink, double side cooled 50 °C/kW

R th(c-h) Thermal impedance Case to heatsink, double side cooled 15 °C/kW

T j Operating junction temperature

F Mounting force 8.0 / 9.0 kN

Mass 85 g

ORDERING INFORMATION : AT604 S 16

VDRM&VRRM/100

125 °C

Page 2

AT604 PHASE CONTROL THYRISTOR

ANSALDO

FINAL SPECIFICATION feb 97 - ISSUE : 03

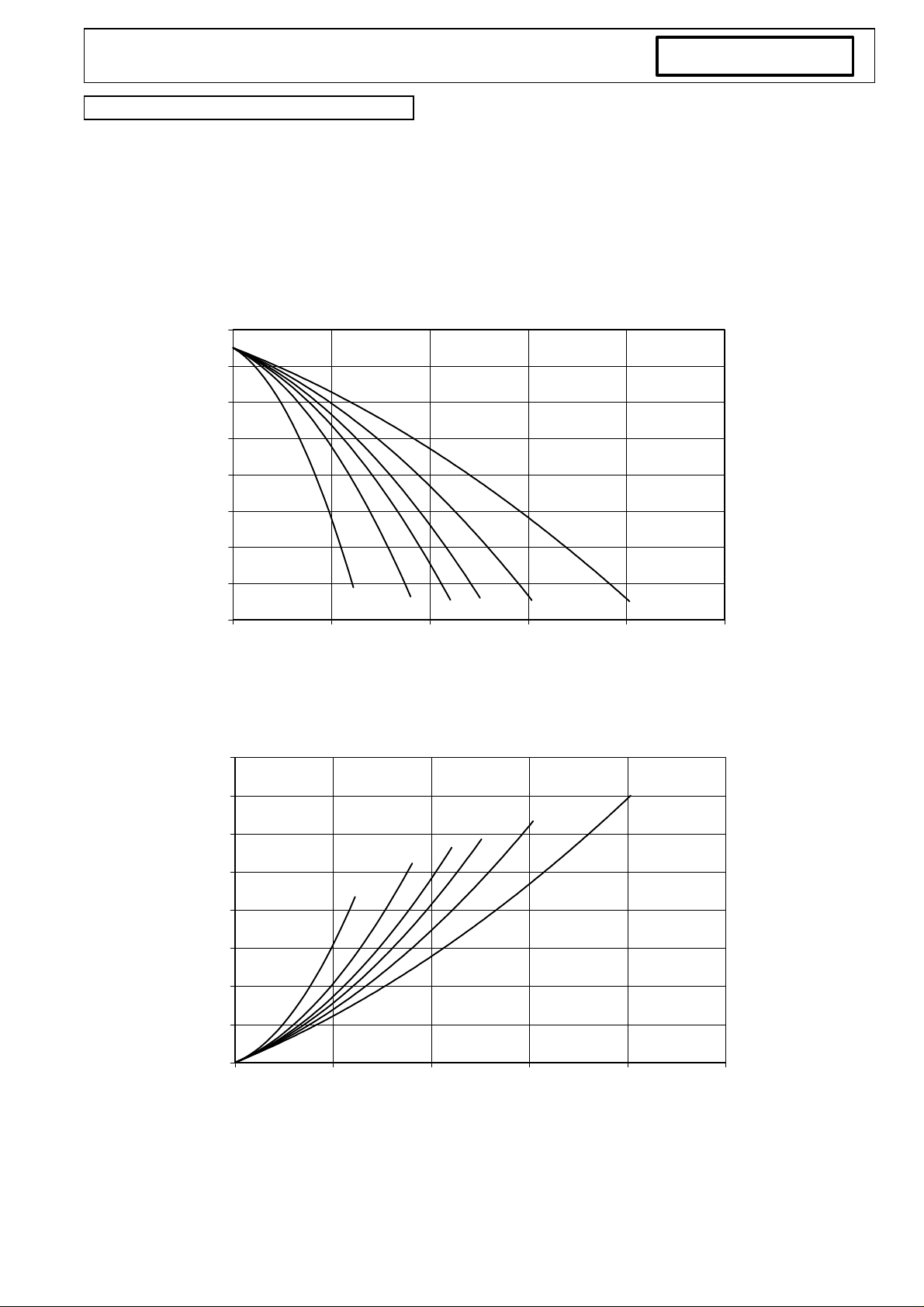

DISSIPATION CHARACTERISTICS

SQUARE WAVE

Th [°C]

130

120

110

100

90

30°

80

60°

70

90°

60

50

0 200 400 600 800 1000

120°

180°

DC

PF(AV) [W]

1600

1400

1200

1000

800

600

400

200

0

IF(AV) [A]

DC

180°

120°

90°

60°

30°

0 200 400 600 800 1000

IF(AV) [A]

Page 3

AT604 PHASE CONTROL THYRISTOR

ANSALDO

ANSALDO

FINAL SPECIFICATION feb 97 - ISSUE : 03

DISSIPATION CHARACTERISTICS

SINE WAVE

Th [°C]

130

120

110

100

90

80

70

60

50

PF(AV) [W]

1400

1200

1000

800

600

30°

60°

90°

120°

180°

0 200 400 600 800 1000

IF(AV) [A]

180°

120°

90°

60°

30°

400

200

0

0 200 400 600 800 1000

IF(AV) [A]

Page 4

AT604 PHASE CONTROL THYRISTOR

ON-STATE CHARACTERISTIC

On-state Current [A]

Zth j-h [°C/kW]

SURGE CHARACTERISTIC

ITSM [kA]

ANSALDO

FINAL SPECIFICATION feb 97 - ISSUE : 03

Tj = 125 °C

2000

1800

1600

1400

1200

1000

800

600

400

200

0

0.6 1.1 1.6 2.1 2.6

On-state Voltage [V]

Tj = 125 °C

9

8

7

6

5

4

3

2

1

0

1 10 100

n° cycles

TRANSIENT THERMAL IMPEDANCE

DOUBLE SIDE COOLED

50.0

45.0

40.0

35.0

30.0

25.0

20.0

15.0

10.0

5.0

0.0

0.001 0.01 0.1 1 10 100

t[s]

Cathode terminal type DIN 46244 - A 4.8 - 0.8

Gate terminal type AMP 60598 - 1

All the characteristics given in this data sheet are guaranteed only with uniform

clamping force, cleaned and lubricated heatsink, surfaces with flatness < .03

mm and roughness < 2 µm.

In the interest of product improvement ANSALDO reserves the right to change

any data given in this data sheet at any time without previous notice.

If not stated otherwise the maximum value of ratings (simbols over shaded

background) and characteristics is reported.

Distributed by

Loading...

Loading...