Datasheet AT25640T2-10TI, AT25640T2-10TC-2.7, AT25640T2-10TC-1.8, AT25640T2-10TC, AT25640T1-10TI-2.7 Datasheet (ATMEL)

...Page 1

Features

•

Serial Peripheral Interface (SPI) Compatible

•

Supports SPI Modes 0 (0,0) and 3 (1,1)

•

Low Voltage and Standard Voltage Operation

– 5.0 (VCC = 4.5V to 5.5V)

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 3.6V)

•

2.1 MHz Clock Rate

•

32-Byte Page Mode

•

Block Write Protection

– Protect 1/4, 1/2, or Entire Array

•

Write Protect (WP) Pin and Write Disable Instructions for

Both Hardware and Software Data Protection

•

Self-Timed Write Cycle (5 ms Typical)

•

High Reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

– ESD Protection: >4000V

•

Automotive Grade and Extended Temperature Devices Available

•

8-Pin PDIP, JEDEC SOIC, and 14-Pin and 20-Pin TSSOP Packages

SPI Serial

EEPROMs

8K (1024 x 8)

16K (2048 x 8)

32K (4096 x 8)

Description

The AT25080/160/320/640 provides 8192/16384/32768/65536 bits of serial electrically erasable programmable read only memory (EEPROM) organized as

1024/2048/4096/8192 words of 8 bits each. The device is optimized for use in many

industrial and commercial applications where low power and low voltage operation

(continued)

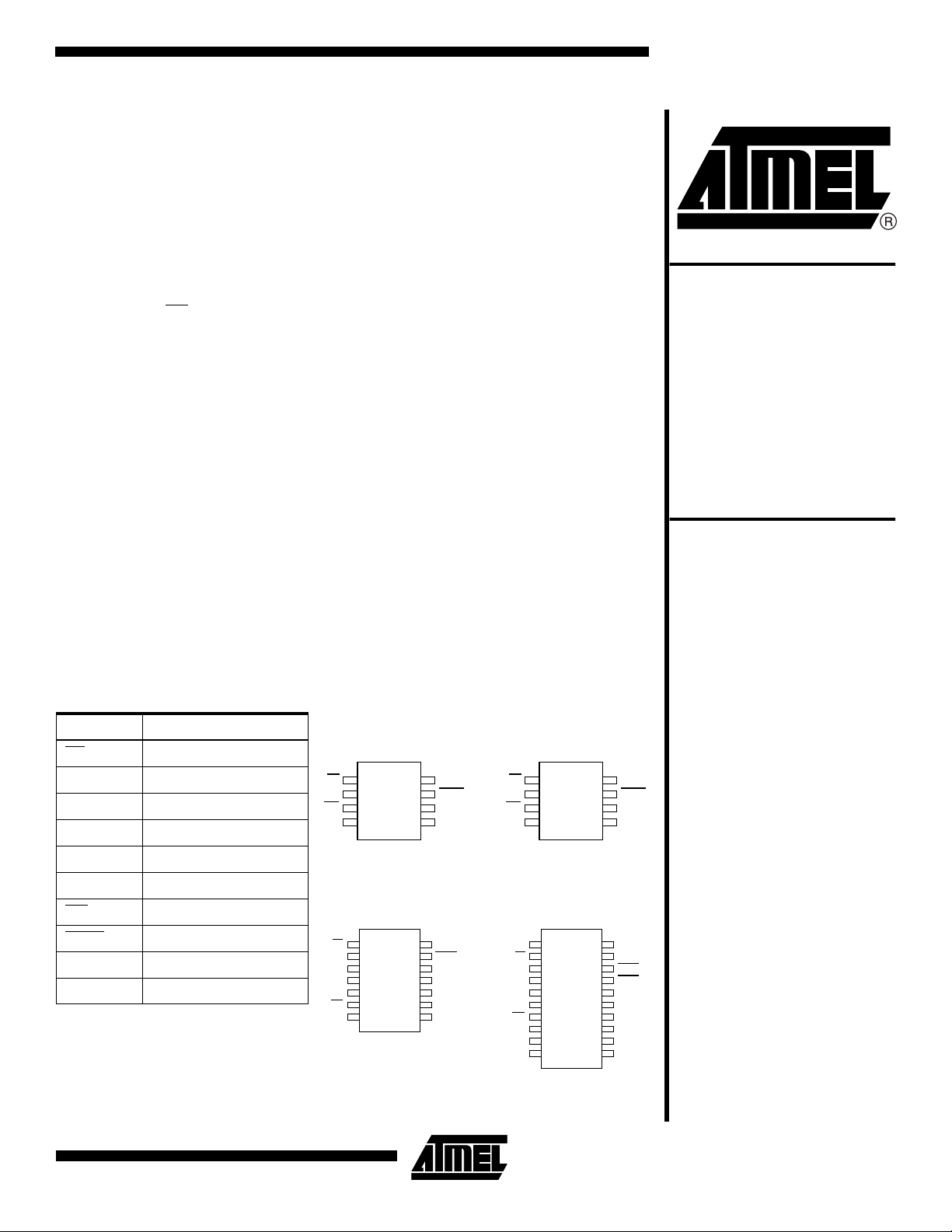

Pin Configuration

Pin Name Function

CS

Chip Select

SCK Serial Data Clock

SI Serial Data Input

SO Serial Data Output

GND Ground

V

CC

WP

Power Supply

Write Protect

HOLD Suspends Serial Input

NC No Connect

DC Don’t Connect

8-Pin PDIP

1

CS

2

SO

3

WP

4

GND

14-Lead TSSOP

CS

1

SO

2

NC

3

NC

4

NC

5

WP

6

GND

7

VCC

8

HOLD

7

SCK

6

SI

5

14

VCC

13

HOLD

12

NC

11

NC

10

NC

9

SCK

8

SI

8-Pin SOIC

1

CS

2

SO

3

WP

4

GND

20-Lead TSSOP*

1

NC

2

CS

3

SO

4

SO

5

NC

6

NC

7

WP

8

GND

9

DC

10

NC

VCC

8

HOLD

7

SCK

6

SI

5

20

NC

19

VCC

18

HOLD

17

HOLD

16

NC

15

NC

14

SCK

13

SI

12

DC

11

NC

64K (8192 x 8)

AT25080

AT25160

AT25320

AT25640

*Pins 3, 4 and 17, 18 are internally connected for 14-lead TSSOP socket compatibility.

Rev. 0675C–08/98

1

Page 2

are essential. The AT25080/160/320/640 is available in

space saving 8-pin PDIP, JE DEC SOIC, and 14-pin and

20-pin TSSOP packages.

The AT25080/160/320/640 is enabled through the Chip

Select pin (CS

sisting of Serial Data Input (SI), Serial Data Output (SO),

and Serial Clock (SCK). All programmi ng cycles are c ompletely self-timed, and no separate E RASE cycle is

required before WRITE.

) and accessed via a 3-wire interface con-

Absolute Maximum Ratings*

Operating Temperature.................................. -55°C to +125°C

Storage Temperature..................................... -65°C to +150°C

Voltage on Any Pin

with Respect to Ground.....................................-1.0V to +7.0V

Maximum Operating Voltage........................................... 6.25V

DC Output Current........................................................5 .0 mA

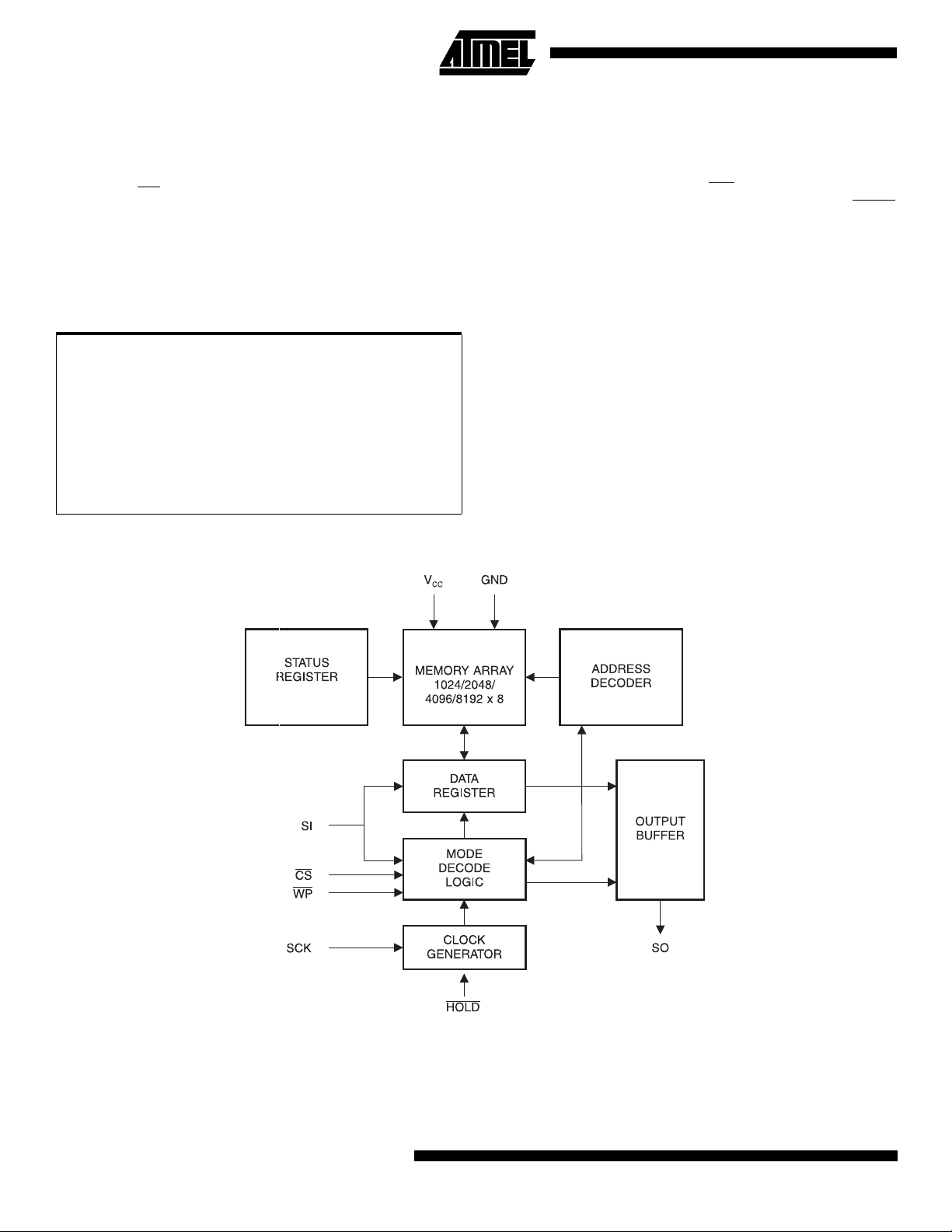

Block Diagram

BLOCK WRITE protection is enabled by programming the

status register with one of four blocks of write protection.

Separate program ena ble and p rogr am di sabl e in str uc tions

are provided for additional data protection. Hardware data

protection is provided via the WP

inadvertent write attempts to the status register. The HOLD

pin may be used to suspend an y serial communi cation

without resetting the serial sequence.

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to the dev ice . This is a s tress rating only an d

functional oper ation of the de vi ce at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or e xtended periods ma y af fect de vice

reliability .

pin to protect against

2

AT25080/160/320/640

Page 3

AT25080/160/320/640

Pin Capacitance

(1)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +5.0V (unless otherwise noted).

Test Conditions Max Units Conditions

C

OUT

C

IN

Output Capacitance (SO) 8 pF V

Input Capacitance(CS, SCK, SI, WP, HOLD)6pFV

OUT

IN

= 0V

= 0V

Note: 1. This parameter is characterized and is not 100% tested.

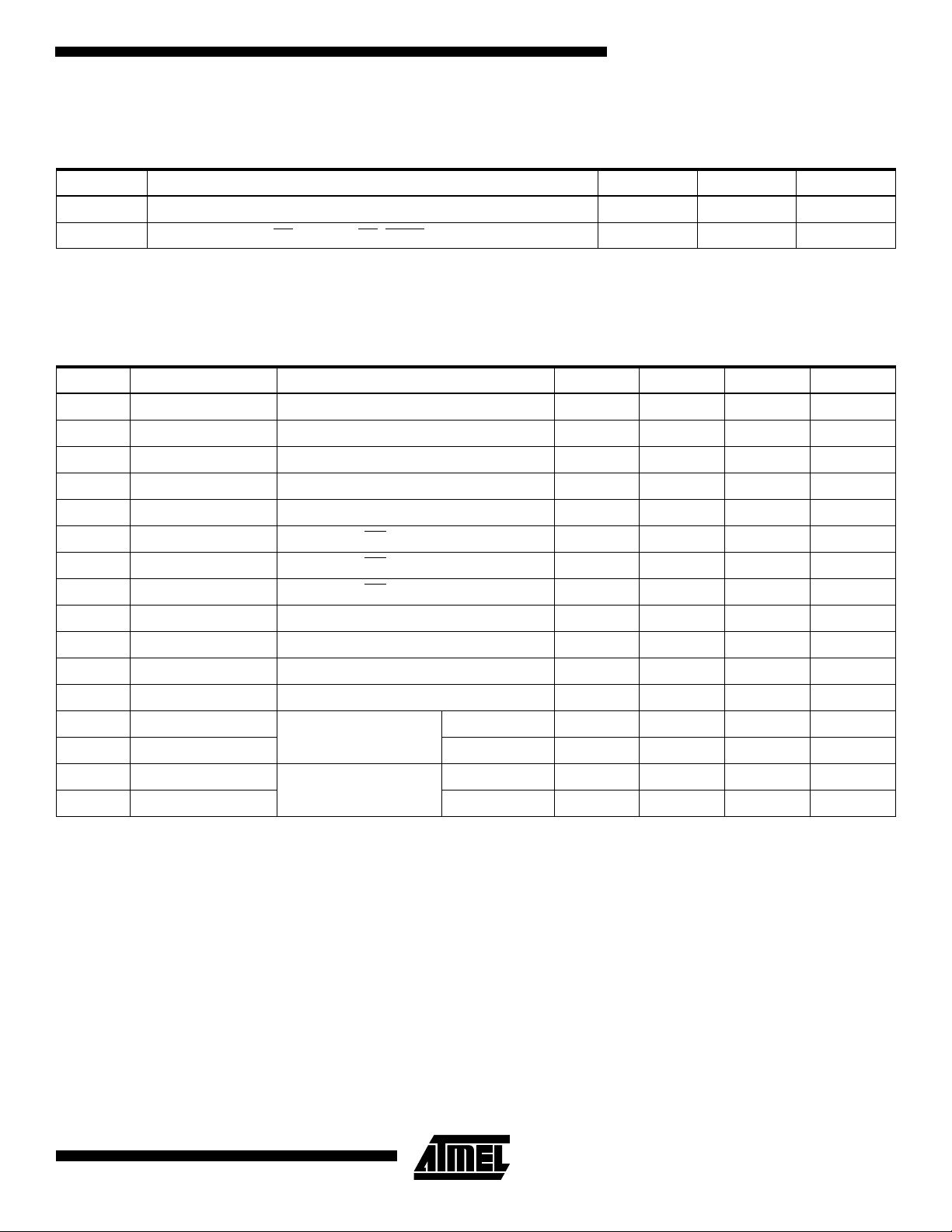

DC Characteristics

Applicable over recommended operating range from: TAI = -40°C to +85°C, VCC = +1.8V to +5.5V, TAC = 0°C to +70°C,

= +1.8V to +5.5V (unless otherwise noted).

V

CC

Symbol Parameter Test Condition Min Typ Max Units

V

CC1

V

CC2

V

CC3

I

CC1

I

CC2

I

SB1

I

SB2

I

SB3

I

IL

I

OL

(1)

V

IL

(1)

V

IH

V

OL1

V

OH1

V

OL2

V

OH2

Note: 1. V

Supply Voltage 1.8 3.6 V

Supply Voltage 2.7 5.5 V

Supply Voltage 4.5 5.5 V

Supply Current

Supply Current

Standby Current

Standby Current

Standby Current

Input Leakage

Output Leakage

Input Low Voltage -0.6

Input High Voltage

Output Low Voltage

Output High Voltage

Output Low Voltage

Output High Voltage I

min and VIH max are reference only and are not tested.

IL

V

= 5.0V at 1 MHz, SO = Open

CC

V

= 5.0V at 2 MHz, SO = Open

CC

V

= 1.8V, CS = V

CC

V

= 2.7V, CS = V

CC

V

= 5.0V, CS = V

CC

V

= 0V to V

IN

V

= 0V to V

IN

4.5V ≤ V

1.8V ≤ V

CC

CC

≤

≤

CC

,

T

CC

5.5V

3.6V

AC

CC

CC

CC

= 0°C to 70°C

= 3.0 mA

I

OL

I

= -1.6 mA V

OH

= 0.15 mA

I

OL

= -100 µAV

OH

0.2 0.5

0.5 2.0

-3.0 3.0

-3.0 3.0

V

CC

V

x 0.7 V

CC

- 0.8

CC

- 0.2 V

CC

CC

3.0 mA

5.0 mA

0.1

µ

µ

µ

µ

µ

x 0.3

+ 0.5

V

V

0.4 V

V

0.2 V

A

A

A

A

A

3

Page 4

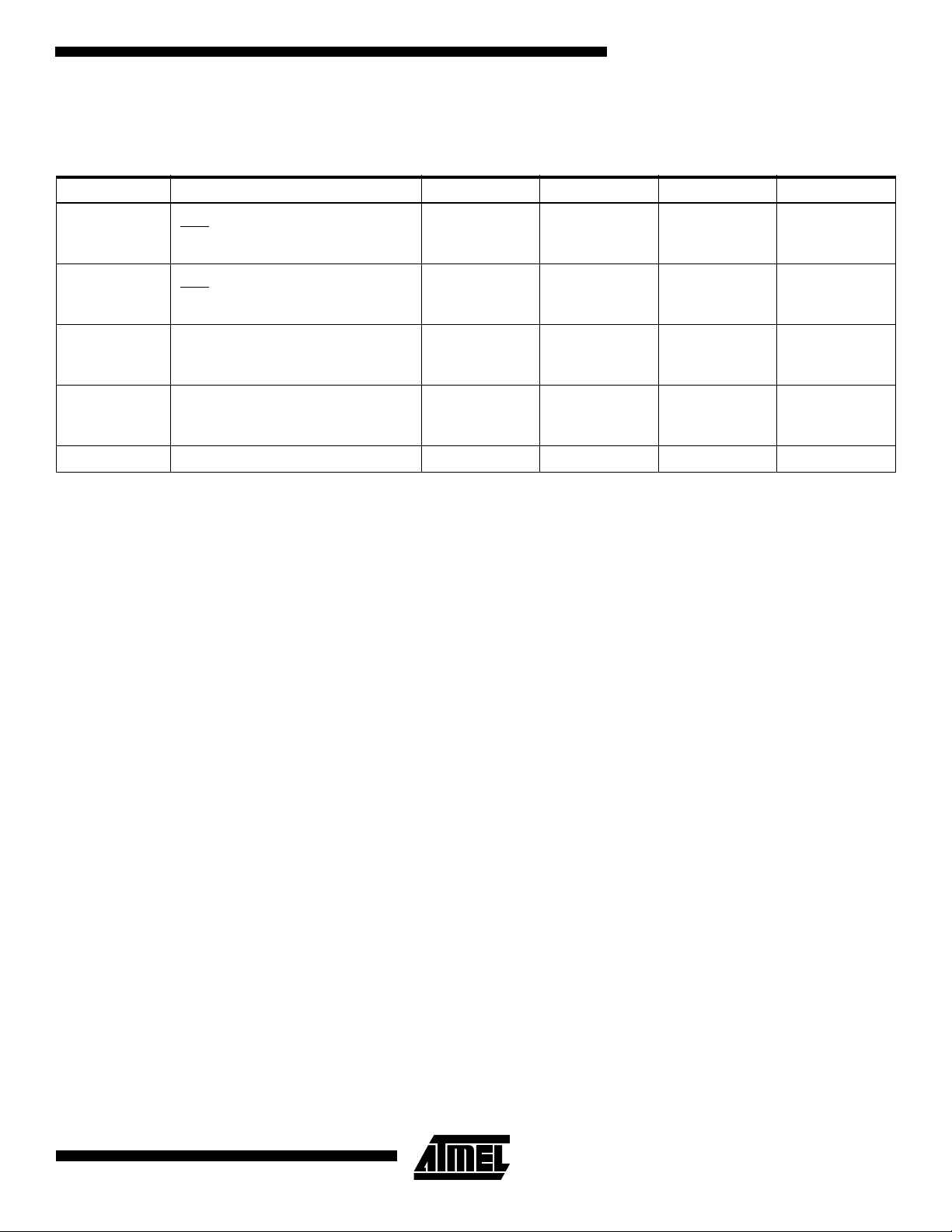

AC Characteristics

Applicable over recommended operating range from TA = -40°C to +85°C, VCC = As Specified,

CL = 1 TTL Gate and 100 pF (unless otherwise noted).

Symbol Parameter Voltage Min Max Units

f

SCK

SCK Clock Frequency

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

2.1

2.1

0.5

MHz

t

RI

t

FI

t

WH

t

WL

t

CS

t

CSS

t

CSH

t

SU

Input Rise Time

Input Fall Time

SCK High Time

SCK Low Time

CS High Time

CS Setup Time

CS Hold Time

Data In Setup Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

200

200

800

200

200

800

250

250

1000

250

250

1000

250

250

1000

50

50

100

2

2

2

2

2

2

ns

µ

µ

ns

ns

ns

ns

ns

s

s

4.5 - 5.5

t

H

Data In Hold Time

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

HD

Hold Setup Time

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

CD

Hold Hold Time

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

V

Output Valid

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

HO

Output Hold Time

2.7 - 5.5

1.8 - 3.6

4

AT25080/160/320/640

50

50

100

100

100

400

200

200

400

0

0

0

0

0

0

200

200

800

ns

ns

ns

ns

Page 5

AT25080/160/320/640

AC Characteristics (Continued)

Applicable over recommended operating range from TA = -40°C to +85°C, VCC = As Specified,

CL = 1 TTL Gate and 100 pF (unless otherwise noted).

Symbol Parameter Voltage Min Max Units

4.5 - 5.5

t

LZ

t

HZ

t

DIS

t

WC

Endurance

Note: 1. This parameter is characterized and is not 100% tested.

(1)

Hold to Output Low Z

Hold to Output High Z

Output Disable Time

Write Cycle Time

5.0V, 25°C, Page Mode 1M Write Cycles

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

100

100

100

100

100

100

250

250

1000

5

10

20

ns

ns

ns

ms

5

Page 6

Serial Interface Description

MASTER:

SLAVE:

input, the AT25080/160/320/640 always operates as a

slave.

TRANSMITTER/RECEIVER:

has separate pins designated for data transmission (SO)

and reception (SI).

MSB:

mitted and received.

SERIAL OP-CODE:

going low, the first byte will be receiv ed. This byte co ntains

the op-code that defines the operations to be performed.

INVA LID OP-CODE:

data will be shifted into the AT25080/16 0/320/640 , and the

serial output pin (SO) will remain in a high impedance state

until the falling edge of CS

tialize the serial communication.

CHIP SELECT:

when the CS

data will not be accepte d via th e SI pin, and the ser ial output pin (SO) will remain in a high impedance state.

HOLD:

pin to select the AT25080/160/320/640. When the device is

selected and a se ri al se que nce is un derwa y, HOLD

used to pause the se rial communica tion with the master

device without resetting the serial sequence. To pause, the

HOLD

resume serial communication, the HOLD

high while the SCK pin is low (SCK may still toggle during

HOLD

is in the high impedance state.

WRITE PROTECT:

normal read/ write opera tions when he ld high. Wh en the

WP pin is brought low an d WPE N bit is “1”, al l write o pera-

The device that generates the serial clock.

Because the Serial Clock pi n (SCK) is always a n

The AT25080/160/320/640

The Most Significant Bit (M SB) is th e first bi t trans-

After the device is selected with CS

If an invalid op-code is received, no

is detected again. This will reini-

The AT25080/160/320/640 is selected

pin is low . When the de vice is no t sele cted,

The HOLD

pin must be brought low while the SCK pin is low. To

). Inputs to the SI pin will be ignored while the SO pin

pin is us ed in conju nctio n wit h the CS

can be

pin is brought

The write protect pi n (WP

) will allow

tions to the sta tus register are inhibited . WP

while CS

ter. If the internal write cycle has already been initiated, WP

going low will have no effect on any write operation to the

status register. The WP

WPEN bit in the status r egister is "0". T his will allow t he

user to ins tall t he AT25 080/16 0/320/6 40 in a sy stem w ith

the WP

status regi ste r. All WP

WPEN bit is set to “1”.

is still low will interrupt a wr ite to the status r egis-

pin function is blocked when the

pin tied to ground and still be able to write to the

pin functions are enabled when the

going low

SPI Serial Interface

6

AT25080/160/320/640

Page 7

AT25080/160/320/640

Functional Description

The AT25080/160/32 0/640 is desi gned to i nterfac e di rectly

with the synchronous serial peripheral interface (SPI) of the

6805 and 68HC11 series of microcontrollers.

The AT25080/160/320/640 utilizes an 8 bit instruction register. The list of instructions and their operation codes are

contained in Table 1. All instructions, addresses, and data

are transferred with the MSB first and start with a high-tolow CS transition.

Table 1.

Instruction

Name

WREN 0000 X110 Set Write Enable Latch

WRDI 0000 X100 Reset Write Enable Latch

RDSR 0000 X101 Read Status Register

WRSR 0000 X001 Write Status Register

READ 0000 X011 Read Data from Memory Array

WRITE 0000 X010 Write Data to Memory Array

WRITE ENABLE (WREN):

write disable state when V

instructions mus t t here fo re be p reced ed b y a Wr ite Enab le

instruction.

WRITE DISABLE (WRDI):

inadvertent writes, the Wr it e Dis able i nst ru cti on disabl es all

programming modes. The WRDI ins tructio n is ind ependen t

of the status of the WP

READ STATUS REGISTER (RDSR):

Register instruction provides access to the status register.

The READY/BUSY an d Write Enable sta tus of th e devic e

can be determined by the RDSR instruction. Similarly, the

Block Write Pr otec tion bits i ndic ate th e exten t o f prote ctio n

employed. These bits are set by using the WRSR instru ction.

Table 2.

WPEN X X X BP1 BP0 WEN RDY

Instruction Set for the AT25080/160/320/640

Instruction

Format Operation

The device will power u p in th e

is applied. All programming

CC

To protect the device against

pin.

The Read Status

Status Register Format

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bi t 2 Bit 1 Bit 0

Table 3.

Bit Definition

Bit 0 (RDY

Bit 1 (WEN)

Bit 2 (BP0) See Table 3.

Bit 3 (BP1) See Table 3.

Bits 4-6 are 0s when device is not in an internal write cycle.

Bit 7 (WPEN) See Table 4.

Bits 0-7 are 1s during an internal write cycle.

WRITE STATUS REGISTER (WRSR):

Read Status Register Bit Definition

)

Bit 0 = 0 (RDY

0 = 1 indicates the write cycle is in progress.

Bit 1= 0 indicates the device is not WRITE

ENABLED. Bit 1 = 1 indicates the de vice is WRITE

ENABLED.

) indicates the device is READY. Bit

The WRSR instruction allows the user to select one of four levels of protection. The AT25080/160/320/640 is divided into four array

segments. One quarter ( 1/4), one half ( 1/2), or all of the

memory segments can be protected. Any of the data within

any selected segment will therefore be READ only. The

block write prot ection le vels and corr espondi ng stat us register control bits are shown in Table 4.

The three bits, BP0, BP1, and WPEN are nonvolatile cells

that have the same pro perties and functi ons as the regul ar

memory cells (e.g. WREN, t

Table 4.

Level

0 0 0 None None None None

1(1/4) 0 1

2(1/2) 1 0

3(All) 1 1

Block Write Protect Bits

Status

Register

Bits Arra y Addresses Protected

BP1 BP0 AT25080 AT25160 AT25320 AT25640

0300

-03FF

0200

-03FF

0000

-03FF

, RDSR).

WC

-07FF

-07FF

-07FF

0600

0400

0000

0C00

-0FFF

0800

-0FFF

0000

-0FFF

1800

-1FFF

1000

-1FFF

0000

-1FFF

The WRSR instruction also allows the user to enable or

disable the write protect (WP

) pin through the use of the

Write Protect Enable (WPEN) bit. Hardware write protection is ena bl e d wh en t h e W P

pin is low and the WPEN bit is

“1”. Hardware write protection is disabled when either the

pin is high or the WPEN bit is “0”. When the device is

WP

hardware write protected, writes to the Status Register,

including the Bloc k Protec t bits and the WPEN bi t, and the

block-protected sec tions in the memor y arra y are disab led.

7

Page 8

Writes are only allowed to sections of the memory which

are not block-protected.

NOTE:

cannot be changed back to “0”, as long as the WP

When the WPEN bit is hardware write protected, it

pin is

held low.

Table 5.

WPEN WP WEN

READ SEQUENCE (READ):

WPEN Operation

Protected

Blocks

0 X 0 Protected Protected Protected

0 X 1 Protected Writable Writable

1 Low 0 Protected Protected Protected

1 Low 1 Protected Writable Protected

X High 0 Protected Protected Protected

X High 1 Protected Writable Writable

Unprotected

Blocks

Status

Register

Reading the

AT25080/160/320/640 via the SO (Serial Output) pin

requires the follo win g seque nce. After the CS

line is pulled

low to select a device, the READ op-code is transmitted via

the SI line followed by the byte address to be read (A15-A0,

Refer to Table 6). Upon completion, any data on the SI line

will be ignored. The data (D7-D0) at the specified address

is then shifted out onto the SO line. If only one byte is to be

read, the CS

line should be driven high after the da ta

comes out. The READ sequence can be continued since

the byte address is automatically incremented and data will

continue to be shifted out. When the highest address is

reached, the addr ess counter will roll over to th e lowest

address allowing the ent ire memo ry to be read in one co ntinuous READ cycle.

WRITE SEQUENCE (WRITE):

In order to program the

AT25080/160/320/640, t wo sep arate instr uctions m ust be

executed. First, the device

must be write enabled

via the

Write Enable (WREN) Instruction. Then a Write (WRITE)

Instruction may be executed. Also, the address of the

memory location(s) to be p rogramm ed must be out side th e

protected address field location selected by the Block Write

Protection Level. During an internal write c ycle, all commands will be ignored except the RDSR instruction.

A Write Instruc tion r equires the foll owing s equence. After

the CS

line is pulled low to select the device, the WRITE

op-code is transmitted via the S I line follo wed by the byte

address (A15-A0) and the data (D7- D0) to be pr ogramme d

(Refer to Table 6). Programming will start after the CS

is brought high. (The LOW to High transition of the CS

pin

pin

must occur during the SCK low time immediately after

clocking in the D0 (LSB) data bit.

The READY/BUSY status of the devic e can be determine d

by initiating a READ STATUS REGISTER (RDSR) Instruction. If Bit 0 = 1, the WRITE cycle is still in progress. If Bit 0

= 0, the WRITE cycle has ended. Only the READ STATUS

REGISTER instruction is enabled during the WRITE programming cycle.

The AT25080/160/ 320/640 i s capable of a 32 -byte P AGE

WRITE operation. After each by te of data is receiv ed, the

five low order address bits are internally incremented by

one; the high order bits of the address will remain constant.

If more than 32-bytes of data are transmitted, the address

counter will roll over and the previously written data will be

overwritten. The AT25080/160/320/640 is automatically

returned to the write disable state at the completion o f a

WRITE cycle.

NOTE:

If the device is not Write enabled (WREN), the

device will igno re the Wr it e instruction and wil l r etu rn to th e

standby state, when CS

is brought high. A new CS falli ng

edge is required to re-initiate the serial communication.

Table 6.

Address AT25080 AT25160 AT25320 AT25640

Care Bits

A

N

Don't

Address Key

A9 - A

0

- A

A

15

10

A10 - A

A15 - A

A11 - A

0

A

11

15

- A

A12 - A

0

12

A15 - A

0

13

8

AT25080/160/320/640

Page 9

Timing Diagrams

Synchronous Data Timing (for Mode 0)

V

IH

CS

V

IL

t

CSS

V

SO

IH

V

IL

t

SU

V

IH

SI

V

IL

V

OH

HI-Z

V

OL

SCK

WREN Timing

VALID IN

AT25080/160/320/

t

CS

t

CSH

t

WH

t

H

t

WL

t

V

t

HO

t

DIS

HI-Z

WRDI Timing

9

Page 10

RDST Timing

CS

01234567891011121314

SCK

WRSR Timing

READ Timing

CS

SCK

SI

SO

SI

SO

HIGH IMPEDANCE

HIGH IMPEDANCE

INSTRUCTION

DATA OUT

76543210

MSB

00112233445566778 9 10 11 12 13 14 15

DATA IN

INSTRUCTION

10

CS

0

1

2

3

445566778910

SCK

SI

SO

INSTRUCTION

HIGH IMPEDANCE

AT25080/160/320/

11 20 21 22 23 24 25 26 27 28 29 30

BYTE ADDRESS

15 14 13

...

0

1

2

3

DATA OUT

0

1

2

3

MSB

Page 11

WRITE Timing

CS

SCK

SI

0

1

2

3

INSTRUCTION

445566778910

BYTE ADDRESS DATA IN

15 14 13

AT25080/160/320/640

11 20 21 22 23 24 25 26 27 28 29 30 31

...

2

3

0

1

3

1

2

0

HOLD

SO

Timing

CS

SCK

HOLD

SO

HIGH IMPEDANCE

t

CD

t

HD

t

HD

t

HZ

t

CD

t

LZ

11

Page 12

AT25080 Ordering Info rmation

t

(max)

WC

(ms)

5 5000 2.0 2100 AT25080-10PC

10 3000 0.5 2100 AT25080-10PC-2.7

20 3000 0.2 500 AT25080-10PC-1.8

5 5000 2.0 2100 AT25080-10PI

10 3000 0.5 2100 AT25080-10PI-2.7

20 3000 0.2 500 AT25080-10PI-1.8

I

CC

(max)

(

A)

µµµµ

I

SB

(max)

(

A)

µµµµ

f

MAX

(kHz)

Ordering Code Package Operation Range

AT25080N-10SC

AT25080T1-10TC

AT25080N-10SC-2.7

AT25080T1-10TC-2.7

AT25080N-10SC-1.8

AT25080T1-10TC-1.8

AT25080N-10SI

AT25080T1-10TI

AT25080N-10SI-2.7

AT25080T1-10TI-2.7

AT25080N-10SI-1.8

AT25080T1-10TI-1.8

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Package Type

8P3 8-Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

8S1 8-Lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)

14T 14-Lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)

Options

Blank Standard Device (4.5V to 5.5V)

-2.7 Low Voltage (2.7V to 5.5V)

-1.8 Low Voltage (1.8V to 3.6V)

12

AT25080/160/320/640

Page 13

AT25160 Ordering Info rmation

t

(max)

WC

(ms)

5 5000 2.0 2100 AT25160-10PC

10 3000 0.5 2100 AT25160-10PC-2.7

20 3000 0.2 500 AT25160-10PC-1.8

5 5000 2.0 2100 AT25160-10PI

10 3000 0.5 2100 AT25160-10PI-2.7

20 3000 0.2 500 AT25160-10PI-1.8

I

CC

(max)

(

A)

µµµµ

I

SB

(max)

(

A)

µµµµ

f

MAX

(kHz)

Ordering Code Package Operation Range

AT25160N-10SC

AT25160T1-10TC

AT25160N-10SC-2.7

AT25160T1-10TC-2.7

AT25160N-10SC-1.8

AT25160T1-10TC-1.8

AT25160N-10SI

AT25160T1-10TI

AT25160N-10SI-2.7

AT25160T1-10TI-2.7

AT25160N-10SI-1.8

AT25160T1-10TI-1.8

AT25080/160/320/640

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

8P3

8S1

14T

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Package Type

8P3 8-Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

8S1 8-Lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)

14T 14-Lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)

Options

Blank Standard Device (4.5V to 5.5V)

-2.7 Low Voltage (2.7V to 5.5V)

-1.8 Low Voltage (1.8V to 3.6V)

13

Page 14

AT25320 Ordering Info rmation

t

(max)

WC

(ms)

5 5000 2.0 2100 AT25320-10PC

10 3000 0.5 2100 AT25320-10PC-2.7

20 3000 0.2 500 AT25320-10PC-1.8

5 5000 2.0 2100 AT25320-10PI

10 3000 0.5 2100 AT25320-10PI-2.7

20 3000 0.2 500 AT25320-10PI-1.8

I

CC

(max)

(µµµµA)

I

SB

(max)

(µµµµA)

f

MAX

(kHz) Ordering Code Package Operation Range

AT25320N-10SC

AT25320T1-10TC

AT25320T2-10TC

AT25320N-10SC-2.7

AT25320T1-10TC-2.7

AT25320T2-10TC-2.7

AT25320N-10SC-1.8

AT25320T1-10TC-1.8

AT25320T2-10TC-1.8

AT25320N-10SI

AT25320T1-10TI

AT25320T2-10TI

AT25320N-10SI-2.7

AT25320T1-10TI-2.7

AT25320T2-10TI-2.7

AT25320N-10SI-1.8

AT25320T1-10TI-1.8

AT25320T2-10TI-1.8

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S

14T

20T

8P3

8S1

14T

20T

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Package Type

8P3 8-Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

8S1 8-Lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)

14T 14-Lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)

20T 20-Lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)

Options

Blank Standard Device (4.5V to 5.5V)

-2.7 Low Voltage (2.7V to 5.5V)

-1.8 Low Voltage (1.8V to 3.6V)

14

AT25080/160/320/640

Page 15

AT25640 Ordering Info rmation

t

(max)

WC

(ms)

5 5000 2.0 2100 AT25640-10PC

10 3000 0.5 2100 AT25640-10PC-2.7

20 3000 0.2 500 AT25640-10PC-1.8

5 5000 2.0 2100 AT25640-10PI

10 3000 0.5 2100 AT25640-10PI-2.7

20 3000 0.2 500 AT25640-10PI-1.8

I

CC

(max)

(

A)

µµµµ

I

SB

(max)

(

A)

µµµµ

f

MAX

(kHz)

Ordering Code Package Operation Range

AT25640N-10SC

AT25640T1-10TC

AT25640T2-10TC

AT25640N-10SC-2.7

AT25640T1-10TC-2.7

AT25640T2-10TC-2.7

AT25640N-10SC-1.8

AT25640T1-10TC-1.8

AT25640T2-10TC-1.8

AT25640N-10SI

AT25640T1-10TI

AT25640T2-10TI

AT25640N-10SI-2.7

AT25640T1-10TI-2.7

AT25640T2-10TI-2.7

AT25640N-10SI-1.8

AT25640T1-10TI-1.8

AT25640T2-10TI-1.8

AT25080/160/320/640

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S1

14T

20T

8P3

8S1

14T

20T

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Industrial

(-40°C to 85°C)

Package Type

8P3 8-Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

8S1 8-Lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)

14T 14-Lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)

20T 20-Lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)

Options

Blank Standard Device (4.5V to 5.5V)

-2.7 Low Voltage (2.7V to 5.5V)

-1.8 Low Voltage (1.8V to 3.6V)

15

Page 16

Packaging Information

8P3,

8-Lead, 0.300" Wide,

Plastic Dual Inline Package (PDIP)

Dimensions in Inches and (Millimeters)

JEDEC STANDARD MS-001 BA

.400 (10.16)

.355 (9.02)

PIN

1

.280 (7.11)

.240 (6.10)

.037 (.940)

.300 (7.62) REF

.210 (5.33) MAX

SEATING

PLANE

.150 (3.81)

.115 (2.92)

.012 (.305)

.008 (.203)

.070 (1.78)

.045 (1.14)

.027 (.690)

.100 (2.54) BSC

.015 (.380) MIN

.022 (.559)

.014 (.356)

.325 (8.26)

.300 (7.62)

0

REF

15

.430 (10.9) MAX

8S1,

8-Lead, 0.150" Wide,

Plastic Gull Wing Small Outline (JEDEC SOIC)

Dimensions in Inches and (Millimeters)

.020 (.508)

.013 (.330)

.244 (6.20)

.228 (5.79)

.068 (1.73)

.053 (1.35)

.010 (.254)

.007 (.203)

PIN 1

0

8

.157 (3.99)

.150 (3.81)

.050 (1.27) BSC

.196 (4.98)

.189 (4.80)

.010 (.254)

.004 (.102)

REF

.050 (1.27)

.016 (.406)

14T,

14-Lead, 0.170" Wide,

Thin Super Small Outline Package (TSSOP)

Dimensions in Inches and (Millimeters)

4.50 (.177)

4.30 (.169)

1.20 (.047) MAX

0.20 (.008)

0.09 (.004)

INDEX MARK

6.50 (.256)

6.25 (.246)

SEATING

PLANE

.650 (.026) BSC

0

REF

8

5.10 (.201)

4.90 (.193)

0.30 (.012)

0.19 (.007)

0.75 (.030)

0.45 (.018)

PIN

1

0.15 (.006)

0.05 (.002)

20T,

20-Lead, 0.170" Wide,

Thin Super Small Outline Package (TSSOP)

Dimensions in Inches and (Millimeters)

4.50 (.177)

4.30 (.169)

1.20 (.047) MAX

0.20 (.008)

0.09 (.004)

INDEX MARK

6.50 (.256)

6.25 (.246)

SEATING

PLANE

.650 (.026) BSC

0

REF

8

6.60 (.260)

6.40 (.252)

0.30 (.012)

0.19 (.007)

0.75 (.030)

0.45 (.018)

PIN

1

0.15 (.006)

0.05 (.002)

16

AT25080/160/320/640

Loading...

Loading...