Datasheet AS5SS128K36DQ-12-XT, AS5SS128K36DQ-12-IT, AS5SS128K36DQ-11-XT, AS5SS128K36DQ-11-IT Datasheet (AUSTN)

Page 1

Austin Semiconductor, Inc.

SRAM

AS5SS128K36

128K x 36 SSRAM

SYNCHRONOUS ZBL SRAM

FLOW-THRU OUTPUT

FEATURES

• High frequency and 100% bus utilization

• Fast cycle times: 11ns & 12ns

• Single +3.3V +5% power supply (VDD)

• Advanced control logic for minimum control signal interface

• Individual BYTE WRITE controls may be tied LOW

• Single R/W\ (READ/WRITE) control pin

• CKE\ pin to enable clock and suspend operations

• Three chip enables for simple depth expansion

• Clock-controlled and registered addresses, data I/Os and

control signals

• Internally self-timed, fully coherent WRITE

• Internally self-timed, registered outputs to eliminate the

need to control OE\

• SNOOZE MODE for reduced-power standby

• Common data inputs and data outputs

• Linear or Interleaved Burst Modes

• Burst feature (optional)

• Pin/function compatibility with 2Mb, 8Mb, and 16Mb ZBL

SRAM

• Automatic power-down

OPTIONS MARKING

• Timing (Access/Cycle/MHz)

8.5ns/11ns/90 MHz -1 1

9ns/12ns/83 MHz -1 2

• Packages

100-pin TQFP DQ No. 1001

• Operating T emperature Ranges

Military (-55oC to +125oC) XT

Industrial (-40oC to +85oC) IT

GENERAL DESCRIPTION

The Austin Semiconductor, Inc. Zero Bus Latency SRAM

family employs high-speed, low-power CMOS designs using an advanced CMOS process.

ASI’s 4Mb ZBL SRAMs integrate a 128K x 36 SRAM core

with advanced synchronous peripheral circuitry and a 2-bit burst

counter. These SRAMS are optimized for 100 percent bus utilization,

eliminating any turnaround cycles for READ to WRITE, or WRITE

to READ, transitions. All synchronous inputs pass through registers

controlled by a positive-edge-triggered single clock input (CLK). The

synchronous inputs include all addresses, all data inputs, chip enable

(CE\), two additional chip enables for easy depth expansion (CE2,

CE2\), cycle start input (ADV/LD\), synchronous clock enable (CKE\),

byte write enables (BW a\, BWb\, BWc\, and BWd\) and read/write (R/

W\).

Asynchronous inputs include the output enable (OE\, which

may be tied LOW for control signal minimization), clock (CLK) and

snooze enable (ZZ, which may be tied LOW if unused). There is also

a burst mode pin (MODE) that selects between interleaved and linear

burst modes. MODE may be tied HIGH, LOW or left unconnected if

burst is unused. The flow-through data-out (Q) is enabled by OE\.

WRITE cycles can be from one to four bytes wide as controlled by the

write control inputs.

All READ, WRITE and DESELECT cycles are initiated by

the ADV/LD\ input. Subsequent burst addresses can be internally

generated as controlled by the burst advance pin (ADV/LD\). Use of

burst mode is optional. It is allowable to give an address for each

individual READ and WRITE cycle. BURST cycles wrap around

after the fourth access from a base address.

To allow for continuous, 100 percent use of the data bus,

the flow-through ZBL SRAM uses a LATE WRITE cycle. For example, if a WRITE cycle begins in clock cycle one, the address is

present on rising edge one. BYTE WRITEs need to be asserted on the

same cycle as the address. The write data associated with the address

is required one cycle later, or on the rising edge of clock cycle two.

Address and write control are registered on-chip to simplify

WRITE cycles. This allows self-timed WRITE cycles. Individual

byte enables allow individual bytes to be written. During a BYTE

WRITE cycle, BWa\ controls DQa pins; BWb\ controls DQb pins;

BWc\ controls DQc pins; and BWd\ controls DQd pins. Cycle types

can only be defined when an address is loaded, i.e., when ADV/LD\ is

LOW . Parity/ECC bits are available on this device.

Austin’s 4Mb ZBL SRAMs operate from a +3.3V V

power supply, and all inputs and outputs are LVTTL-compatible.

The device is ideally suited for systems requiring high bandwidth and

zero bus turnaround delays.

DD

AS5SS128K36

Rev. 2.0 12/00

For more products and information

please visit our web site at

www.austinsemiconductor .com

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

1

Page 2

Austin Semiconductor, Inc.

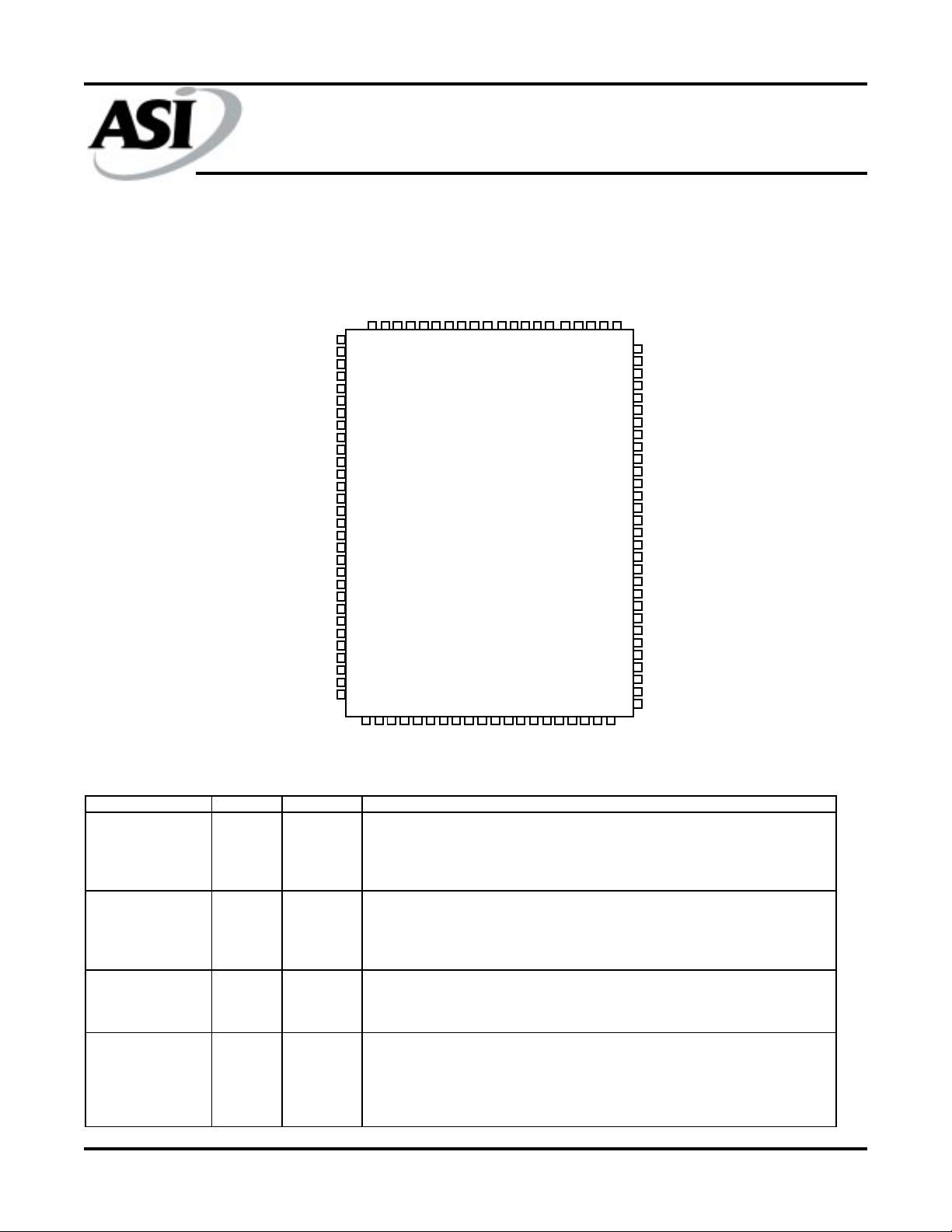

PIN ASSIGNMENT

(T op Vie w)

100-pin TQFP (DQ)

SS

DD

R/W\

CLK

V

V

CE2\

BWa\

BWb\

BWc\

BWd\

CE2

CE\

SA

SA

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

DQc

1

DQc

2

DQc

3

VDDQ

4

V

5

SS

DQc

6

DQc

7

DQc

8

DQc

9

10

V

SS

11

VDDQ

12

DQc

13

DQc

14

V

SS

15

V

DD

16

V

DD

17

V

SS

18

DQd

19

DQd

20

VDDQ

21

V

SS

22

DQd

23

DQd

24

DQd

25

DQd

26

V

SS

27

VDDQ

28

DQd

29

DQd

30

DQd

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

SS

DD

SA

SA

SA

SA

SA1

SA0

DNU

DNU

V

SA

V

DNU

DNU

CKE\

SA

ADV/LD\

OE\ (G\)

SA

SA

NF

SRAM

AS5SS128K36

SA

SA

NF

DQb

80

DQb

79

DQb

78

VDDQ

77

V

76

SS

DQb

75

DQb

74

DQb

73

DQb

72

V

71

SS

VDDQ

70

69

DQb

68

DQb

67

V

SS

66

V

SS

65

V

DD

64

ZZ

63

DQa

62

DQa

61

VDDQ

60

V

SS

59

DQa

58

DQa

57

DQa

56

DQa

55

V

SS

54

VDDQ

53

DQa

52

DQa

51

DQa

SA

SA

SA

PIN DESCRIPTIONS

MODE (LBO\)

TQFP PINS SYMBOL TYPE DESCRIPTION

37

36

32-35, 44-50,

81, 82, 99, 100

93

94

95

96

87 CKE\ Input Synchronous Clock Enable: This active LOW input permits CLK to propagate

88 R/W\ Input Read/Write: This input determines the cycle type when ADV/LD\ is LOW and is the

AS5SS128K36

Rev. 2.0 12/00

SA0

SA1

SA

BWa\

BWb\

BWc\

BWd\

Input Synchronous Address Inputs: These inputs are registered and must meet the setup

and hold times around the rising edge of CLK. Pins 83 and 84 are reserved as

address bits for the higher-density 8Mb and 16Mb ZBL SRAMs, respectively. SA0 and

SA1 are the two least significant bits (LSB) of the address field and set the internal

burst counter if burst is desired.

Input Synchronous Byte Write Enables: These active LOW inputs allow individual bytes to

be written when a WRITE cycle is active and must meet the setup and hold times

around the rising edge of CLK. BYTE WRITEs need to be asserted on the same cycle

as the address. BWa\ controls DQa pins; BWb\ controls DQb pins; BWc\ controls

DQc pins; BWd\ controls DQd pins.

throughout the device. When CKE is HIGH, the device ignores the CLK input and

effectively internally extends the previous CLK cycle. This input must meet setup and

hold times around the rising edge of CLK.

only means for determining READs and WRITEs. READ cycles may not be converted

into WRITEs (and vice versa) other than by loading a new address. A LOW on this pin

permits BYTE WRITE operations and must meet the setup and hold times around the

rising edge of CLK. Full bus-width WRITEs occur if all byte write enables are LOW.

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

2

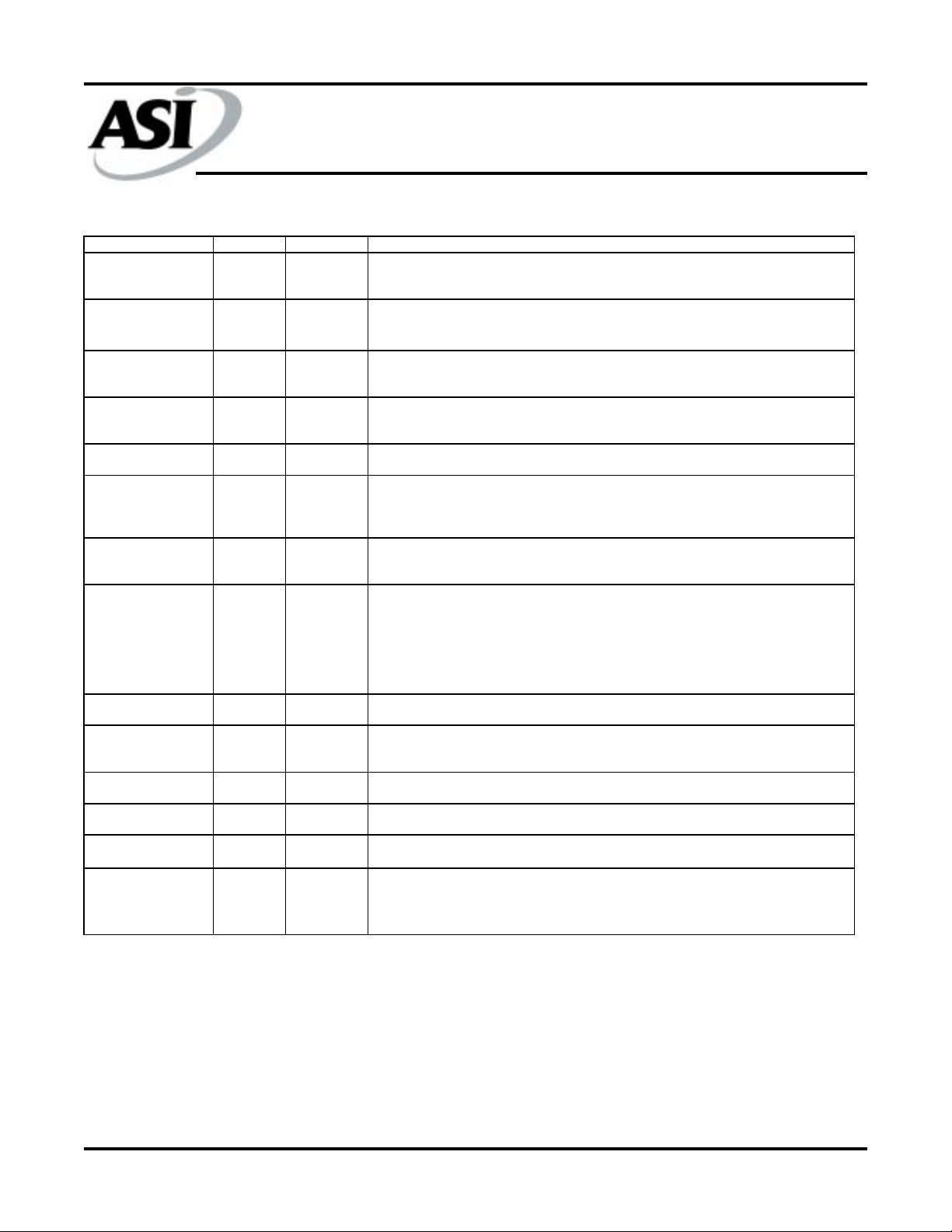

Page 3

SRAM

AS5SS128K36

Austin Semiconductor, Inc.

PIN DESCRIPTIONS (continued)

TQFP PINS SYMBOL TYPE DESCRIPTION

64 ZZ Input Snooze Enable: This active HIGH, asynchronous input causes the device to enter a

89 CLK Input Clock: This signal registers the address, data, chip enables, byte write enables and

98, 92 CE\, CE2\ Input Synchronous Chip Enable: These active LOW inputs are used to enable the device

97 CE2 Input Synchronous Enable: This active HIGH input is used to enable the device and is

86 OE\

85 ADV/LD\ Input Synchronous Address Advance/Load: When HIGH, this input is used to advance the

31 MODE

(a) 51, 52, 53, 56-59,

62, 63

(b) 68, 69, 72-75, 78,

79, 80

(c)1, 2, 3, 6-9, 12, 13

(d) 18, 19, 22-25, 28,

29, 30

15, 16, 41, 65, 91

5, 10, 14, 17, 21, 26

40, 55, 60, 66, 67, 71

76, 90

4, 11, 20, 27, 54, 61

70, 77

38, 39, 42, 43, 83, 84 64NC ---- No Connect: These pins can be left floating or connected to GND to minimize thermal

(G\)

(LBO\)

DQa

DQb

DQc

DQd

V

DD

Vss Ground Ground: GND

Q

V

DD

38, 39, 42, 43 DNU

83, 84 NF

Input Output Enable: This active LOW, asynchronous inputs enables the data I/O output

Input Mode: This inputs selects the burst sequence. A LO W on this pin selects linear burst.

Input/Output SRAM Data I/Os: Byte "a" is DQa pins; Byte "b" is DQb pins; Byte "c" is DQc pins;

Supply Power Supply: See DC Electrical Characteristics and Operating Conditions for range.

Supply Isolated Output Buffer Supply: See DC Electrical Characteristics and Operating

----

----

low-power standby mode in which all data in the memory array is retained. When ZZ

is active, all other inputs are ignored.

burst control inputs on its rising edge. All synchronous inputs must meet setup and

hold times around the clock's rising edge.

and are sampled only when a new external address is loaded (ADV/LD\ LOW). CE2\

can be used for memory depth expansion.

sampled only when a new external address is loaded (ADV/LD\ LOW). This input can

be used for memory depth expansion.

drivers. G\ is the JEDEC-standard term for OE\.

internal burst counter, controlling burst access after the external address is loaded.

When ADV/LD\ is HIGH, R/W\ is ignored. A LOW on ADV/LD\ clocks a new address

at the CLK rising edge.

NC or HIGH on this pin selects interleaved burst. Do not alter input state while device

is operating. LBO\ is the JEDEC-standard term for MODE.

Byte "d" is DQd pins. Input data must meet setup and hold times around the rising

edge CLK.

Conditions for range.

impedance.

Do Not Use: These signals may with be unconnected or wired to GND to

minimize thermal impedance.

No Function: These pins are internally connected to the die and will have the

capacitance of an input pin. It is allowable to leave these pins unconnected or

driven by signals. Pins 83 and 84 are reserved for address expansion.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

Page 4

Austin Semiconductor, Inc.

INTERLEAVED BURST ADDRESS TABLE (MODE = NC OR HIGH)

SRAM

AS5SS128K36

First Address

(external)

X...X00 X...X01 X...X10 X...X11

X...X01 X...X00 X...X11 X...X10

X...X10 X...X11 X...X00 X...X01

X...X11 X...X10 X...X01 X...X00

Second Address

(internal)

Third Address

(internal)

Fourth Address

(internal)

LINEAR BURST ADDRESS TABLE (MODE = LOW)

First Address

(external)

X...X00 X...X01 X...X10 X...X11

X...X01 X...X10 X...X11 X...X00

X...X10 X...X11 X...X00 X...X01

X...X11 X...X00 X...X01 X...X10

Second Address

(internal)

Third Address

(internal)

Fourth Address

(internal)

PARTIAL TRUTH TABLE FOR READ/WRITE COMMANDS*

FUNCTION R/W\ BWa\ BWb\ BWc\ BWd\

READ H XXXX

Write Abort/NOP L HHHH

Write Byte a (DQa, DQPa)

Write Byte b (DQb, DQPb)

Write Byte c (DQc, DQPc)

Write Byte d (DQd, DQPd)

2

2

2

2

LLHHH

LHLHH

LHHLH

LHHHL

Write all bytes LLLLL

* NOTE: Using R/W\ and byte write(s), any one or more bytes may be written.

AS5SS128K36

Rev. 2.0 12/00

4

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

Page 5

Austin Semiconductor, Inc.

17

FUNCTIONAL BLOCK DIA GRAM

SRAM

AS5SS128K36

SA0, SA1, SA

CLK

CKE\

17 17 15 17

ADDRESS

REGISTER

MODE

K

WRITE ADDRESS

REGISTER

ADV/LD\

BWa\

BWb\ DQs

BWc\

BWd\

R/W\

OE\

CE\

CE2

CE2\

WRITE REGISTRY AND

DATA COHERENCY

CONTROL LOGIC

READ

LOGIC

ADV/LD\

SA1

SA0

K

D1

D0

BURST

LOGIC

SA1'

Q1

SA0'

Q0

17

WRITE

DRIVERS

128K X 9 X 4

MEMORY

ARRAY

INPUT

REGISTER

O

D

S

E

N

S

E

A

M

P

S

E

A

T

A

S

T

E

E

R

I

N

G

U

T

P

U

T

B

U

F

F

E

R

S

E

NOTE: The Functional Block Diagram illustrates simplified device operation. See Truth Table, pin descriptions and timing diagrams for detailed

information.

AS5SS128K36

Rev. 2.0 12/00

5

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

Page 6

Austin Semiconductor, Inc.

STATE DIAGRAM FOR ZBL SRAM

SRAM

AS5SS128K36

READ

BURST

DS

BURST

DS DS

DESELECT

WRITE

BEGIN

READ

READ

DS

WRITE

DS

BEGIN

WRITE

READ

READ BURST BURST WRITE

READ

BURST

READ

WRITE

BURST

WRITE

WRITE

BURST

KEY:

NOTE: 1. A ST ALL or IGNORE CLOCK EDGE cycle is not shown in the above diagram. This is because CKE\ HIGH only

AS5SS128K36

Rev. 2.0 12/00

COMMAND ACTION

DS DESELECT

READ New READ

WRITE New WRITE

BURST READ,

BURST

blocks the clock (CLK) input and does not change the state of the device.

2. States change on the rising edge of the clock (CLK).

BURST WRITE or

CONTINUE DESELECT

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

6

Page 7

Austin Semiconductor, Inc.

SRAM

AS5SS128K36

TRUTH TABLE

OPERATION

DESELECT CYCLE None H X X L L X X X L L H High-Z

DESELECT CYCLE None X H X L L X X X L L H High-Z

DESELECT CYCLE None X X L L L X X X L L H High-Z

CONTINUE DESELECT CYCLE None X X X L H X X X L L H High-Z 1

READ CYCLE

(Begin Burst)

READ CYCLE

(Continue Burst)

NOP/DUMMY READ

(Begin Burst)

DUMMY READ

(Continue Burst)

WRITE CYCLE

(Begin Burst)

WRITE CYCLE

(Continue Burst)

NOP/WRITE ABORT

(Begin Burst)

WRITE ABORT

(Continue Burst)

IGNORE CLOCK EDGE

(Stall)

SNOOZE MODE None X X X H X X X X X X High-Z

(5-10)

ADDRESS

USED

External L L H L L H X L L L HQ

Next X X X L H X X L L L H Q 1, 11

External L L H L L H X H L L H High-Z 2

Next X X X L H X X H L L H High-Z 1, 2, 11

External L L H L L L L X L L HD 3

Next X X X L H X L X L L H D 1, 3, 11

None L L H L L L H X L L H High-Z 2, 3

Next X X X L H X H X L L H High-Z

Current X X X L X X X X H L H --- 4

CE\ CE2\ CE2 ZZ ADV/LD\ R/W\ BWx OE\ CKE\ CLK DQ NOTES

1, 2, 3,

11

NOTE:

1 . CONTINUE BURST cycles, whether READ or WRITE, use the same control inputs. The type of cycle performed (READ

or WRITE) is chosen in the initial BEGIN BURST cycle. A CONTINUE DESELECT cycle can only be entered if a

DESELECT cycle is first executed.

2 . DUMMY READ and WRITE ABOR T cycles can be considered NOPs because the device performs no external operation.

A WRITE ABOR T means a WRITE command is given, but no operation is performed.

3 . OE\ may be wired LOW to minimize the number of control signals to the SRAM. The device will automatically turn off the

output drivers during a WRITE cycle. OE\ may be used when the bus turn-on and turn-off times do not meet an applications

requirements.

4. If an IGNORE CLOCK EDGE command occurs during a READ operation, the DQ bus will remain active (Low-Z). If it occurs

during a WRITE cycle, the bus will remain in High-Z. No WRITE operations will be performed during the IGNORE CLOCK

EDGE cycle.

5. X means “Don’t Care.” H means logic HIGH. L means logic LOW . BWx = H means all byte write signals (BW a\, BWb\, BWc\,

BWd\) are HIGH. BWx = L means all byte write signals are LOW .

6 . BW a\ enables WRITES to Byte “a” (DQa pins); BWb\ enables WRITES to Byte “b” (DQb pins); BWc\ enables WRITES to

Byte “c” (DQc pins); BWd\ enables WRITES to Byte “d” (DQd pins).

7 . All inputs except OE\ and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

8 . Wait states are inserted by setting CKE\ HIGH.

9 . This device contains circuitry that will ensure that the outputs will be in the High-Z during power-up.

10. The device incorporates a 2-bit burst counter . Address wraps to the initial address every fourth BURST cycle.

11 . The address counter is incremented for all CONTINUE BURST cycles.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

7

Page 8

Austin Semiconductor, Inc.

SRAM

AS5SS128K36

ABSOLUTE MAXIMUM RATINGS*

V oltage on VDD Supply Relative to VSS.................-0.5V to +4.6V

V oltage on VDDQ Supply Relative to VSS.................-0.5V to V

VIN.................................................................. -0.5V to VDDQ +0.5V

Storage T emperature (Plastics) ..........................-55°C to +150°C

Short Circuit Output Current ........................…..................100mA

Max. Junction Temperature*.............................................+150 °C

*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operation section of this speci-

DD

fication is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability .

**Junction T emperature depends upon package type, cycle time, loading, ambient temperture and airflow.

DC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS

(-55oC < TA < +125oC; V

DD, VDD

DESCRIPTION CONDITIONS SYMBOL MIN MAX UNITS NOTES

Input High (Logic 1) Voltage

Input High (Logic 1) Voltage DQ Pins

Input Low (Logic 0) Voltage

Input Leakage Current

Output Leakage Current

Output High Voltage

Output Low Voltage

Supply Voltage

Isolated Output Buffer Supply

Q = +3.3V +0.165V unless otherwise noted)

2.0

2.0

V

DD

V

DD

-0.3 0.8 V 1, 2

-1.0 1.0 µA3

-1.0 1.0 µA

2.4 --- V 1, 4

--- 0.4 V 1, 4

3.135 3.465 V 1

3.135

V

VIN < V

0V <

DD

Output(s) Disabled,

VIN < V

0V <

I

= -4.0mA V

OH

= 8.0mA V

I

OL

DD

V

IH

V

IH

V

IL

IL

I

IL

O

OH

OL

V

DD

V

Q

DD

+ 0.3

+ 0.3

DD

V 1, 2

V 1, 2

V 1, 5

CAPACITANCE

DESCRIPTION CONDITIONS SYMBOL TYP MAX UNITS NOTES

Control Input Capacitance

Input/Output Capacitance (DQ)

Address Capacitance

Clock Capacitance

NOTE:

1. All voltages referenced to V

2. Overshoot: V

Undershoot: V

Power-up: V

3. MODE pin has an internal pull-up, and input leakage =

4. The load used for V

are available upon request.

5. V

6. This parameter is sampled.

AS5SS128K36

Rev. 2.0 12/00

Q should never exceed VDD. VDD and VDDQ should be externally wired together to the same power supply.

DD

< +4.6V for t < t

IH

< -0.7V for t < t

IL

< +3.465V and VDD < 3.135V for t < 200ms.

IH

OH

(GND).

SS

, VOL testing is shown in Figure 2. AC load current is higher than the shown DC values. AC I/O curvers

T

= 25oC; f = 1 MHz

A

= 3.3V

V

DD

/2 for I < 20mA.

KHKH

/2 for I < 20mA.

KHKH

+ 10µA.

C

I

C

O

C

A

C

CK

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3 4 pF 6

4 5 pF 6

3 3.5 pF 6

3 3.5 pF 6

8

Page 9

AS5SS128K36

Austin Semiconductor, Inc.

IDD OPERATING CONDITIONS AND MAXIMUM LIMITS

(-55oC < TA < +125oC; V

DD, VDD

DESCRIPTION CONDITIONS SYM -11 -12 UNITS NOTES

Q = +3.3V +0.165V unless otherwise noted)

MAX

SRAM

Power Supply

Current: Operating

Power Supply

Current: Idle

CMOS Standby

TTL Standby

Clock Running

Device selected; All inputs < V

or > VIH; Cycle time > tKC (MIN)

V

= MAX; Outputs open

DD

Device selected; V

CKE\ >

All inputs <

VSS + 0.2 or > VDD -0.2;

Cycle time >

Device selected; V

All inputs <

VSS + 0.2 or > VDD -0.2;

= MAX;

DD

VIH;

tKC (MIN)

= MAX;

DD

All inputs static; CLK frequency = 0

Device selected; V

All inputs <

VIL or > VIH;

= MAX;

DD

All inputs static; CLK frequency = 0

Device selected; V

ADV/LD\ >

or >

VDD - 0.2; Cycle time > tKC (MIN)

VIH; All inputs < VSS + 0.2

= MAX;

DD

IL

I

DD

I

DD1

I

SB2

I

SB3

I

SB4

275 250 mA 1, 2

22 20 mA 1, 2

10 10 mA 2

25 25 mA 2

65 60 mA 2

Snooze Mode

ZZ >

V

IH

I

SB2Z

10 10 mA 2

THERMAL RESISTANCE

DESCRIPTION CONDITIONS SYM TYP UNITS NOTES

Thermal Resistance

(Junction to Ambient)

Test conditions follow standard test

θ

JA

46

methods and procedures for measuring

Thermal Resistance

(Junction to Top of Case)

thermal impedance, per EIA/JESD51

θ

JC

2.8

NOTE:

1. IDD is specified with no output current and increases with faster cycle times. IDDQ increases with faster cycle times and

greater output loading.

2. “Device deselected” means device is in a deselected cycle as defined in the truth table. “Device selected” means device

is active (not in deselected mode).

3 . This parameter is sampled.

AS5SS128K36

Rev. 2.0 12/00

9

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

o

C/W

o

C/W

3

3

Page 10

Austin Semiconductor, Inc.

SRAM

AS5SS128K36

AC ELECTRICAL CHARACTERISTICS

(-55oC < TA < +125oC; V

DESCRIPTION

CLOCK

Clock cycle time

Clock frequency

Clock HIGH time

Clock LOW time

OUTPUT TIMES

Clock to output valid

Clock to output invalid

Clock to output in Low-Z

Clock to output in High-Z

OE\ to output valid

OE\ to output in Low-Z

DD, VDD

Q = +3.3V +0.165V)

SYM MIN MAX MIN MAX UNITS NOTES

t

KHKH

t

KF

t

KHKL

t

KLKH

t

KHQV

t

KHQX

t

KHQX1

t

KHQZ

t

GLQV

t

GLQX

6, 8, 9

-11 -12

11 12 ns

90 83 MHz

3.0 3.0 ns 1

3.0 3.0 ns 1

8.5 9.0 ns

3.0 3.0 ns 2

3.0 3.0 ns 2, 3, 4, 5

5.0 5.0 ns 2, 3, 4, 5

5.0 5.0 ns 6

0 0 ns 2, 3, 4, 5

OE\ to output in High-Z

t

GHQZ

5.0 5.0 ns 2, 3, 4, 5

SETUP TIMES

Address

Clock enable (CKE\)

Control signals

Data-in

t

AVKH

t

EVKH

t

CVKH

t

DVKH

2.2 2.5 ns 7

2.2 2.5 ns 7

2.2 2.5 ns 7

2.2 2.5 ns 7

HOLD TIMES

Address

Clock enable (CKE\)

Control signals

Data-in

NOTE:

1 . Measured as HIGH above VIH and LOW below VIL.

2. Contact ASI for more information on these parameters.

3. This parameter is sampled.

4. This parameter is measured with the output loading shown in Figure 2.

5. Transistion is measured +200mV from steady state voltage.

6. OE\ can be considerted a “Don’t Care” during WRITEs; however, controlling OE\ can help fine-tune a system for ZBL timing.

7 . This is a synchrnous device. All addresses must meet the specified setup and hold times for all rising edgges o CLK when they are being

registered into the device. All other synchronous inputs must meet the setup and hold times with stable logic levels for all rising edges of

clock (CLK) when the chip is enabled. Chip enable must be valid at each rising edge of CLK when ADV/LD\ is LOW to remain enabled.

8. Test conditions as specified with the output loading shown in Figure 1, unless otherwise noted.

9 . A WRITE cycle is defined by R/W\ LOW having been registered into the device at ADV/LD\ LOW. A READ cycle is defined by R/W\

HIGH with ADV/LD\ LOW. Both cases must meet setup and hold times.

AS5SS128K36

Rev. 2.0 12/00

t

KHAX

t

KHEX

t

KHCX

t

KHDX

0.5 0.5 ns 7

0.5 0.5 ns 7

0.5 0.5 ns 7

0.5 0.5 ns 7

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

10

Page 11

Austin Semiconductor, Inc.

AC TEST CONDITIONS

SRAM

AS5SS128K36

Input pulse levels

Input slew rate

Input timing reference levels

Output reference levels

Output load

Q

Z0=50Ω

VT = 1.5V

Vss to 3.3V

See Figures 1 and 2

OUTPUT LOADS

50Ω

1 ns

1.5V

1.5V

3.3v

317Ω

Q

351Ω

5 pF

Fig. 2 OUTPUT LOAD EQUIVALENTFig. 1 OUTPUT LOAD EQUIVALENT

LOAD DERA TING CUR VES

The ASI 128K x 36 ZBL SRAM timing is dependent upon

the capacitive loading on the outputs.

Consult the factory for copies of I/O current versus

voltage curves.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

11

Page 12

Austin Semiconductor, Inc.

0

0

0

0

0

1

1

1

1

1

5

5

5

SRAM

AS5SS128K36

SNOOZE MODE

SNOOZE MODE is a low-current, “power-down” mode

in which the device is deselected and current is reduced to

I

. The duration of SNOOZE MODE is dictated by the

SB2Z

length of time the ZZ pin is in a HIGH state. After the device

enters SNOOZE MODE, all inputs except ZZ become disabled and all outputs go to High-Z.

becomes a logic HIGH, I

is met. Any READ or WRITE operation pending when the

device enters SNOOZE MODE is not guaranteed to complete

sucessfully. Therefore, SNOOZE MODE must not be initiated

until valid pending operations are completed. Similarly, when

exiting SNOOZE MODE during t

cycle should be given.

The ZZ pin is an asynchronous, active HIGH input that

causes the device to enter SNOOZE MODE. When the ZZ pin

SNOOZE MODE ELECTRICAL CHARACTERISTICS

DESCRIPTION CONDITIONS SYM MIN MAX UNITS NOTES

Current during SNOOZE MODE

ZZ active to input ignored

ZZ inactive to input sampled

ZZ active to snooze current

ZZ inactive to exit snooze current

ZZ >

V

IH

I

SB2Z

t

ZZ

t

RZZ

t

ZZI

t

RZZI

is guaranteed after the time t

SB2Z

, only a DESELECT or READ

RZZ

10 mA

0

t

KHKH

0

t

KHKH

t

KHKH

ns 1

ns 1

ns 1

0ns1

ZZI

SNOOZE MODE WAVEFORM

CLK

t

ZZ

ZZ

t

ZZI

I

SUPPLY

ALL INPUTS

(except ZZ)

234567890123456789

Outputs (Q)

AS5SS128K36

Rev. 2.0 12/00

234567890123456789

I

ISB2Z

2345678901234567890

2345678901234567890

2345678901234567890

High-Z

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

12

t

RZZ

t

RZZI

DESELECT

or READ Only

234567890123456789

234567890123456789

234567890123456789

234

234

234

Don’t Care

Page 13

MIN

MAX

123

123

123

9

8

123456789012345678901

1

1

123456789012345678901

8

7

123

123

123

7

7

3

4

4

CLK

CLE\

CE\

ADV/LD\

AS5SS128K36

Austin Semiconductor, Inc.

READ/WRITE TIMING

t

KHKH

1 2 3 4 5 6 7 8 9 10

t

t

EVKH

t

CVKH

t

KHEX

t

KHCX

KHKL

t

KLKH

2345678

234567

SRAM

R/W\

2345678901234567890

BWx\

ADDRESS

DQ

t

AVKH

A1

t

KHAX

t

DVKH

A2

D(A1)

t

KHDX

23456

D(A2)

A3

t

t

KHQX1

D(A2+1)

KHQV

OE\

COMMAND

WRITE

D(A1)

WRITE

D(A2)

BURST

WRITE

D(A2+1)

READ

Q(A3)

READ/WRITE TIMING P ARAMETERS

SYMBOL

t

KHKH

t

KF

t

KHKL

t

KLKH

t

KHQV

t

KHQX

t

KHQX1

t

KHQZ

t

GLQV

t

GLQX

MIN MAX MIN MAX

11 12

90 83

3.0 3.0

3.0 3.0

8.5 9.0

3.0 3.0

3.0 3.0

5.0 5.0

5.0 5.0

00

-12-11

A4

t

Q(A3)

READ

Q(A4)

KHQX

23456

Q(A4)

t

GHQZ

BURST

READ

Q(A4 +1)

SYMBOL

t

GHQZ

t

AVKH

t

EVKH

t

CVKH

t

DVKH

t

KHAX

t

KHEX

t

KHCX

t

GLDX

t

GLQV

t

234567

A5

Q(A4+1)

GLQX

WRITE

D(A5)

t

KHQZ

t

KHQX

READ

Q(A6)

2

Don’t Care

A6

2.2 2.5

2.2 2.5

2.2 2.5

2.2 2.5

0.5 0.5

0.5 0.5

0.5 0.5

0.5 0.5

A7

D(A5)

Q(A6)

WRITE

DESELECT

D(A7)

23

23

Undefined

MIN MAX

5.0 5.0

23456

D(A7)

-12-11

NOTE:

1. For this waveform, ZZ is tied LOW .

2. Burst sequence order is determined by MODE (0=linear, 1=interleaved). BURST operations are optional.

3. CE\ represents three signals. When CE\ = 0, it represents CE\ = 0, CE2\ = 0, CE2 = 1.

4. Data coherency is provided for all possible operations. If a READ is initiated, the most current data is used. The most

recent data may be from the input data register.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

13

Page 14

2

4

4

123

123

123

123

3

4

4

CLK

123

123

123

123

12345678

1

8

12345678

8

9

123

123

123

123

8

8

1

1

1

9

1

1

1

1234567890

1234567890

1234567890

CKE\

CE\

ADV/LD\

R/W\

BWx\

ADDRESS

AS5SS128K36

Austin Semiconductor, Inc.

NOP, ST ALL AND DESELECT CYCLES

1 2 3 4 5 6 7 8 9 10

234567

234567

234567

23456789012345678901

A1 A2

A3

234567

2345678

2345678

234567890123

A4

234567890123

A5

t

SRAM

KHQZ

DQ

COMMAND

WRITE

D(A1)

D(A1)

READ

Q(A2)

Q(A2)

ST A L L READ

Q(A3)

Q(A3)

WRITE

D(A4)

STALL NOP

NOP, STALL AND DESELECT TIMING PARAMETERS

-12-11

SYMBOL

t

KHQX

t

KHQZ

MIN MAX MIN MAX

3.0 3.0

5.0 5.0

D(A4)

2

READ

Q(A5)

Don’t Care

Q(A5)

t

KHQX

DESELECT CONTINUE

23

23

Undefined

DESELECT

NOTE:

1. The IGNORE CLOCK EDGE or STALL cycle (clock 3) illustrates CKE\ being used to create a “pause”. A WRITE is not performed

during this cycle.

2. For this waveform, ZZ and OE\ are tied LOW.

3. CE\ represents three signals. When CE\ = 0, it represents CE\ = 0, CE2\ = 0, CE2 = 1.

4. Data coherency is provided for all possible operations. If a READ is initiated, the most current data is used. The most recent data

may be from the input data register.

AS5SS128K36

Rev. 2.0 12/00

14

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

Page 15

AS5SS128K36

Austin Semiconductor, Inc.

ASI Case # 1001 (Package Designator DQ)

16.00 +0.20/-0.05

14.00 + 0.10

SRAM

1.50 + 0.10

0.65 Basic

See Detail A

0.32+0.06/-0.10

0.60 + 0.15

0.15 +0.03/-0.02

22.10 +0.10/-0.15

20.10 + 0.10

1.40 + 0.05

Detail A

0.10+0.10/-0.05

1.00 TYP

NOTE: All dimensions in Millimeters.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

15

Page 16

Austin Semiconductor, Inc.

ORDERING INFORMATION

EXAMPLE: AS5SS128K36DQ-11/IT

SRAM

AS5SS128K36

Device Number

AS5SS128K36 DQ -11 /*

AS5SS128K36 DQ -12 /*

Package

Type

Speed ns Process

*AVAILABLE PROCESSES

IT = Industrial T emperature Range -40oC to +85oC

XT = Extended T emperature Range -55oC to +125oC

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

16

Loading...

Loading...