Page 1

ICs for Mobile Communication

AN8538SH

Single PLL IC for cellular phone

■ Overview

The AN8538SH is a single PLL IC with a fixed

frequency dividing ratio for IF local oscillation of

a cellular phone. You can generate a local signal of

260.76 MHz by using a reference signal of 19.68

MHz or 19.8 MHz.

■ Features

• Two reference frequencies of 19.68 MHz and 19.8

MHz are available. (Select by SELECT pin.)

• Power saving operation (V

= 2.7 V, 0.9 mA typ.)

CC

• Power saving function (10 µA max.)

• Two systems of charge pump output (one of them

can be switched to on/off with SW pin.)

• Lock detection function

• SSONF-10D small package

■ Applications

• IF local oscillation for cellular phone terminal

(CDMA for North America)

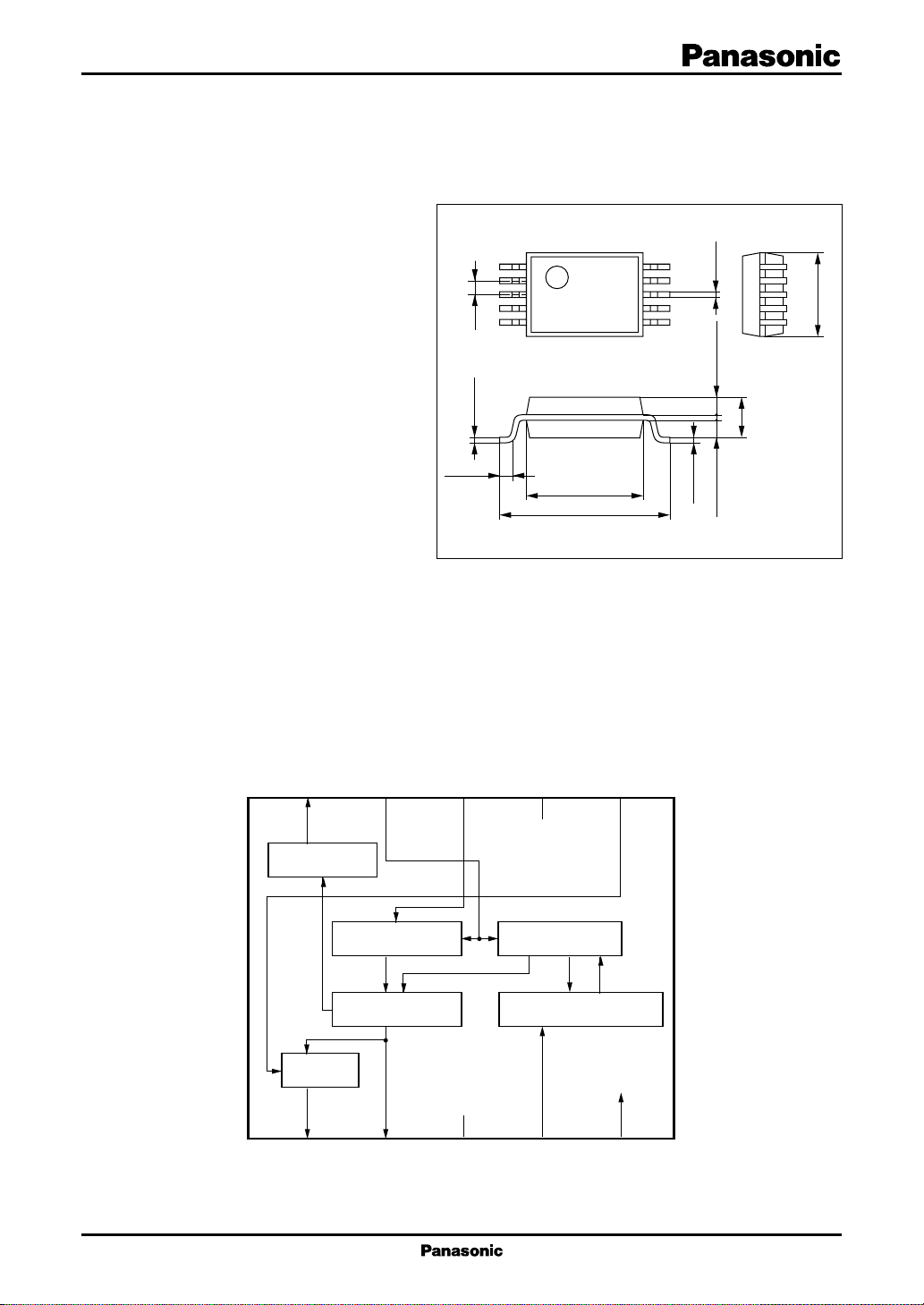

■ Block Diagram

0.5

0.1±0.1

0.5±0.2

Unit: mm

1

5

4.3±0.30

6.3±0.30

SSOP010-P-0225

10

6

+0.1

0.2±0.1

3.0±0.30

0.625±0.100.625±0.10

1.5±0.2

–0.05

0.15

LD

10

Lock detection

14-bit R counter

Phase comparator

Selector

1

CPSUB

SELECT

9

2

CP

REF

8

3

GND

CC

V

7

15-bit N counter

1/16, 1/17 prescaler

4

IFIN

SW

6

5

PS

1

Page 2

AN8538SH ICs for Mobile Communication

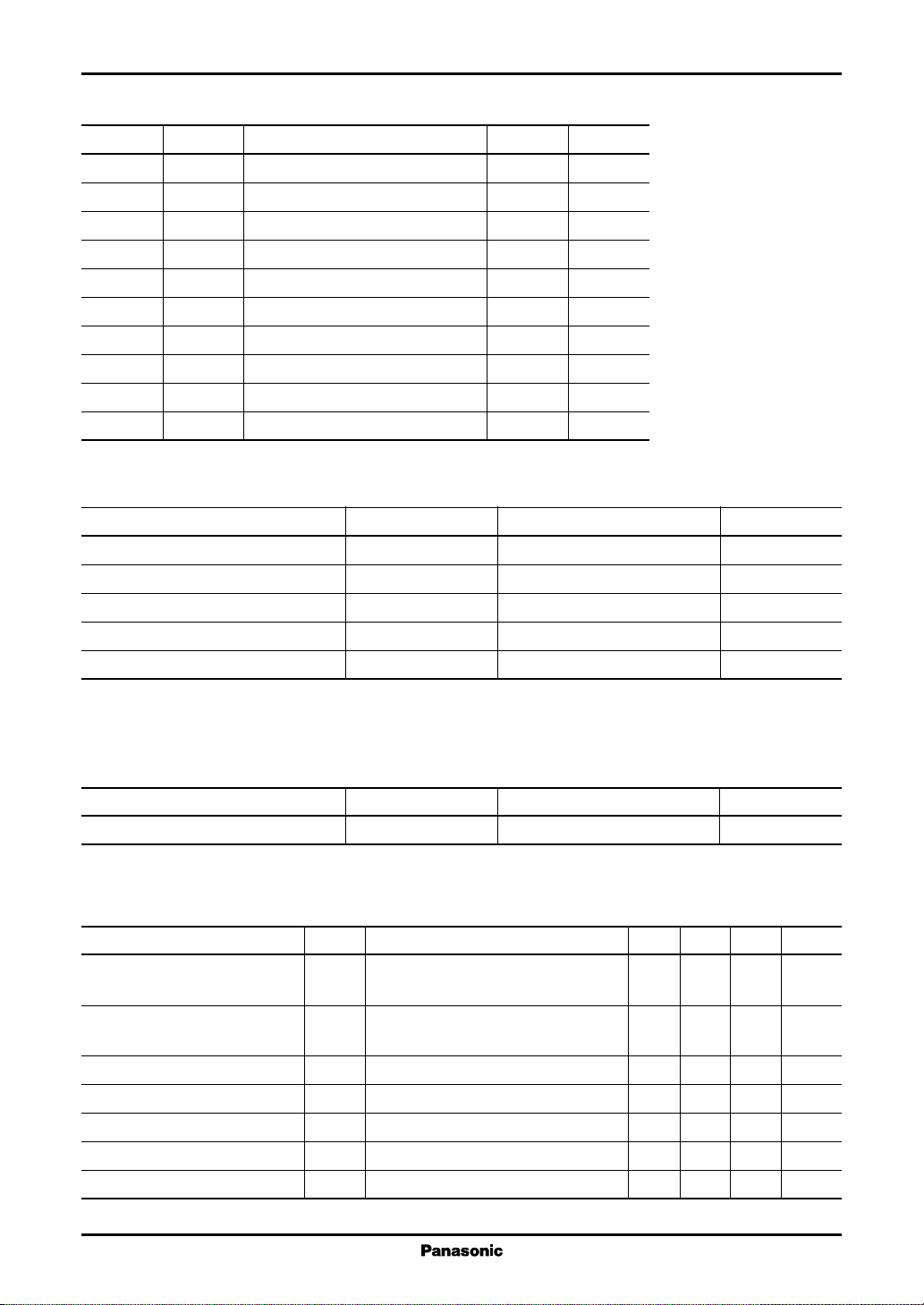

■ Pin Descriptions

Pin No. Symbol Description I/O Level

1 CPSUB Sub charge pump output O CMOS

2 CP Charge pump output O CMOS

3 GND GND pin

4 IFIN IF input I ECL

5 PS Power save control I CMOS

6 SW Sub charge pump control I CMOS

7VCCPower supply pin

8 REF Reference frequency input I ECL

9 SELECT IF frequency changeover control I CMOS

10 LD Lock detection output O CMOS

■ Absolute Maximum Ratings

Parameter Symbol Rating Unit

Supply voltage V

Supply current I

2

Power dissipation

Operating ambient temperature

Storage temperature

Note)*1: Except for the operating ambient temperature and storage temperature, all ratings are for Ta = 25°C.

2: Ta = 85°C

*

*

1

*

1

*

CC

CC

P

D

T

opr

T

stg

3.6 V

3.5 mA

12.6 mW

−30 to +85 °C

−55 to +125 °C

■ Recommended Operating Range

Parameter Symbol Range Unit

Supply voltage V

CC

■ Electrical Characteristics at VCC = 2.7 V, f

Parameter Symbol Conditions Min Typ Max Unit

Consumption current 1 I

Consumption current 2 I

Reference signal input level V

High-level input voltage V

Low-level input voltage V

High-level input current I

Low-level input current I

2

SELECT = low 0.90 1.21 mA

CC1

At 260.76 MHz lock

Power save mode 010µA

CC2

At PS = low setting

REFINfREFIN

IH

IL

IH

IL

= 19.68 MHz 0.5 1.2 V[p-p]

At VIH = 2.16 V applied − 10 1 µA

At VIL = 0 V applied − 10 1 µA

= 19.68 MHz, V

REFIN

2.55 to 3.3 V

= 0.6 V[p-p], Ta = 25°C

REFIN

2.16 3.30 V

0 0.4 V

Page 3

ICs for Mobile Communication AN8538SH

■ Electrical Characteristics at VCC = 2.7 V, f

= 19.68 MHz, V

REFIN

= 0.6 V[p-p], Ta = 25°C

REFIN

(continued)

• Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

Parameter Symbol Conditions Min Typ Max Unit

Consumption current 1 I

SELECT = low 0.90 1.34 mA

CC1

At 260.76 MHz lock

Consumption current 2 I

SELECT = high 0.90 1.34 mA

CC2

At 260.76 MHz lock

IF input level V

Reference signal input level V

Output leak current I

IFINfIFIN

REFINfREFIN

OZ

= 100 MHz to 350 MHz − 10 +2dBm

= 10 MHz to 25 MHz 0.5 1.2 V[p-p]

At VOZ = 0 V, 2.7 V applied − 1.0 +1.0 µA

■ Terminal Equivalent Circuits

Pin No. Equivalent circuit Description

1 Pin 1: CPSUB

2 Pin 2: CP

2

1

SW

3 GND

4 IFIN

4

4.5 kΩ

4.5 kΩ

5PS

Pin 5

9

6SW

6

3

Page 4

AN8538SH ICs for Mobile Communication

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description

7 V

8 REF

10 kΩ 10 kΩ

8

9 Refer to pin 5 SELECT

10 LD

10

CC

■ Application Notes

1. Input level characteristics

1) IF input level characteristics

V

Upper limit

10

Ta = −30°C, 25°C, 85°C

0

(dBm)

−10

Lower limit

Input level

−20

Ta = −30°C

−30

−40

75 100 150 200 250 300 350

Input frequency (MHz

Ta = 85°C

= 2.55 V to 3.3V

CC

Ta = 25°C

)

4

Page 5

ICs for Mobile Communication AN8538SH

■ Application Notes (continued)

1. Input level characteristics (continued)

2) REF input level characteristics

= 2.55 V to 3.3V

V

CC

Upper limit

20

Ta = −30°C, 25°C, 85°C

10

(dBm)

0

Lower limit

Input level

−10

−20

−30

0 5 10 15 20 25 30

Ta = −30°C

Ta = 85°C

Input frequency (MHz

Ta = 25°C

)

2. Characteristics specification

1) IF select specification

SELECT pin control enables you to switch IF as below:

SELECT = low → f

SELECT = high→ f

= 260.76 MHz, fR = 60 kHz (P = 16, N = 271, A = 10, R = 328)

OUT

= 260.76 MHz, fR = 60 kHz (P = 16, N = 271, A = 10, R = 330)

OUT

2) Unlock detection and LD output specification

LD output is high in a lock mode and low in an unlock mode. Lock signal is outputted in a power save mode.

SELECT = high: Detection time is 16 µs. About detection accuracy, when a dividing output shifts

by ±(51 × 3) ns for f

= 60 kHz, it generates an unlock output.

REF

SELECT = low : Detection time is 16 µs. About detection accuracy, when a dividing output shifts

by ±(51 × 3) ns for f

= 60 kHz, it generates an unlock output.

REF

3) Power save control specification

When power save control pin (PS) is high, it is set to an operating mode. When it is low, it is set to power save mode.

4) Analog SW control specification

CPSUB is controlled by SW pin.

SW = low : CPSUB open

SW = high : CPSUB operation

5) Other specification

Set CMOS input pins, such as PS pin, SW pin, SELECT pin, etc., normally to VCC or GND.

5

Loading...

Loading...