Page 1

ICs for TV

AN5491K

Synchronous signal and deflection distortion correction processing IC

2

supporting I

■ Overview

The AN5491K is a deflection processor IC for synchronous signal processing and screen distortion correction. It synchronizes with the input signal of High-vision,

wide television, NTSC, PAL and VGA by the external

binary input signal of them so that a multimedia television

can be realized easily.

■ Features

• Supports the multiple-point horizontal frequency

(15.7 kHz to 62.7 kHz)

• Horizontal duty is controllable by external voltage.

• Built-in full functions for correction

(Horizontal and vertical: 16 items)

• Over-current detection, shut-down and hold-down

C bus for HD, wide television

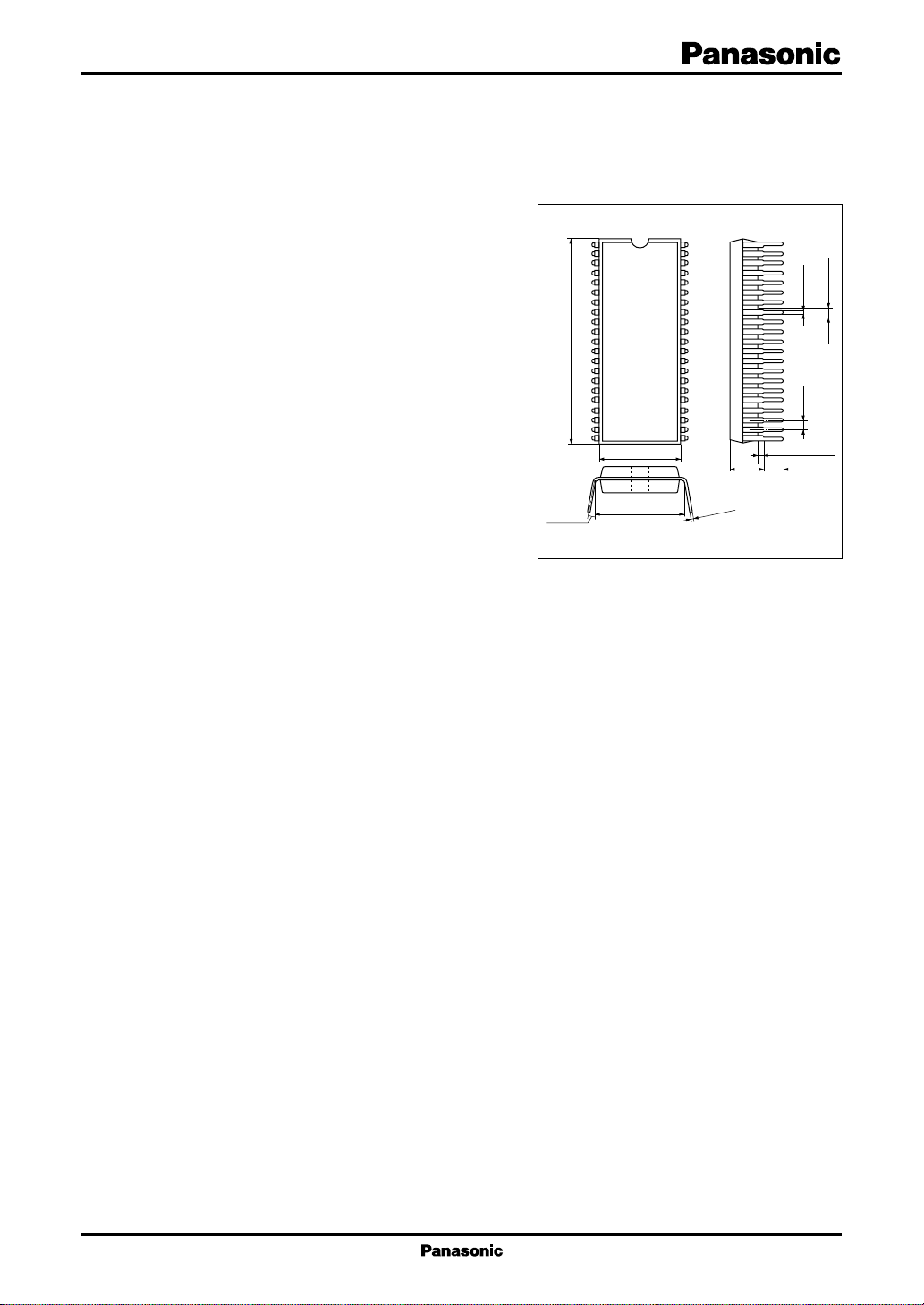

36.8±0.3

3° to 15°

Unit: mm

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

13.7±0.3

15.3±0.25

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

4.76±0.25

0.1

+

–0.05

0.3

0.5±0.1

1.778

0.96±0.25

3.3±0.25

0.9±0.25

SDIP042-P-0600A

■ Applications

• High-vision televisions, Wide screen televisions and

Projection televisions

1

Page 2

AN5491K ICs for T V

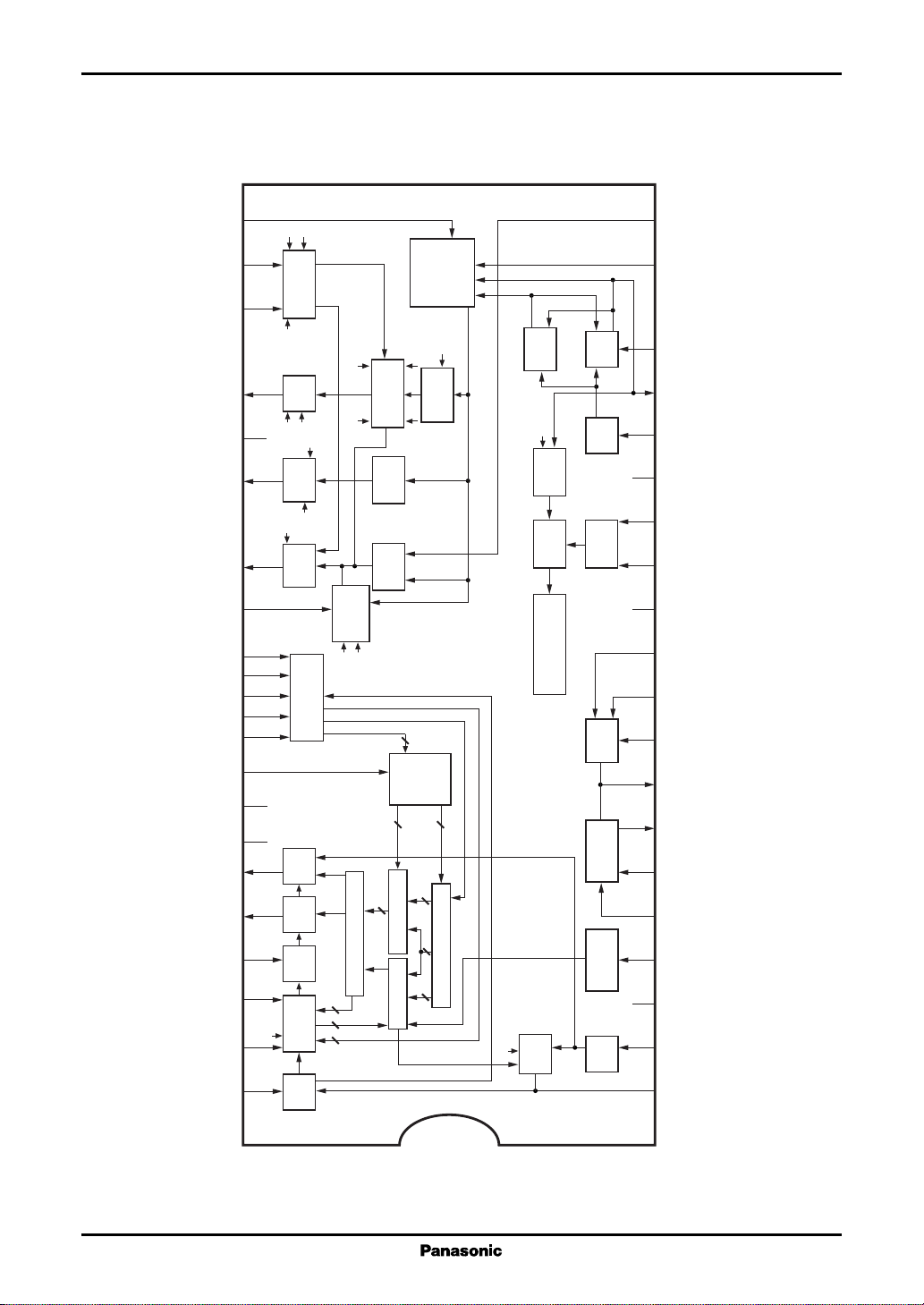

■ Block Diagram

22 21

AGC

EHT-DC

EHT-AC

V- EHT

H- EHT

23 20

/AGC

24

EHT

correction

Ramp

Trapezoid

Ramp

V-out

DEF GND

Phase out

EW out

Corner level

× 32

× 8

× 4

× 2

× 1

VGA

2

L GND

I

H-GND

Lock det.

H-out

V

VP

18

OSC

17

16

slice

15

28

29

30

EHT-AC

V

out

POL

V-POS

out

Phase

Trape

V-SAW

correction

Phase

crrection

H-parabola

V/I

converter

V-amp.

V-S

V-LIN

BOW

timing

V-AGC

Latch-SW

pulse

V-latch

14

Parallel

32

H-WID

out

EW

crrection

Trapezoid

Data

latch

2

C

I

decode

13

33 12

Corner

19

correction

11

25

Upper

H

Lower

input

5

26

31

35

switch

f

27

34

36

37 6

38 5

Lock

H

det.

out

input

Counter

2

6

7

4

Sync. DEF DAC

gen.

V-BLK

det.

X-ray

10

V-OSC

VS2

VP in

DEF V

SCL

SDA

2

I

L V

CC

V-SAW in

V-SAW lower

9

V-SAW upper

8

BLK out

7

Comparator out

Comparator in

Comparator ref.

CC

H-duty adj.

H-AFC2

FBP in

H-OSC

39 4

H

duty

Counter BF

40

H

H-POS

H

AFC2

VCO

2 2 2

41 2

42

2

Counter

7

Counter PG Counter decode

Gain-SW

H

AFC1

Shut down

HP

det.

slice

Shut down

3

H-V

H-pulse in

1

H-AFC1

CC

2

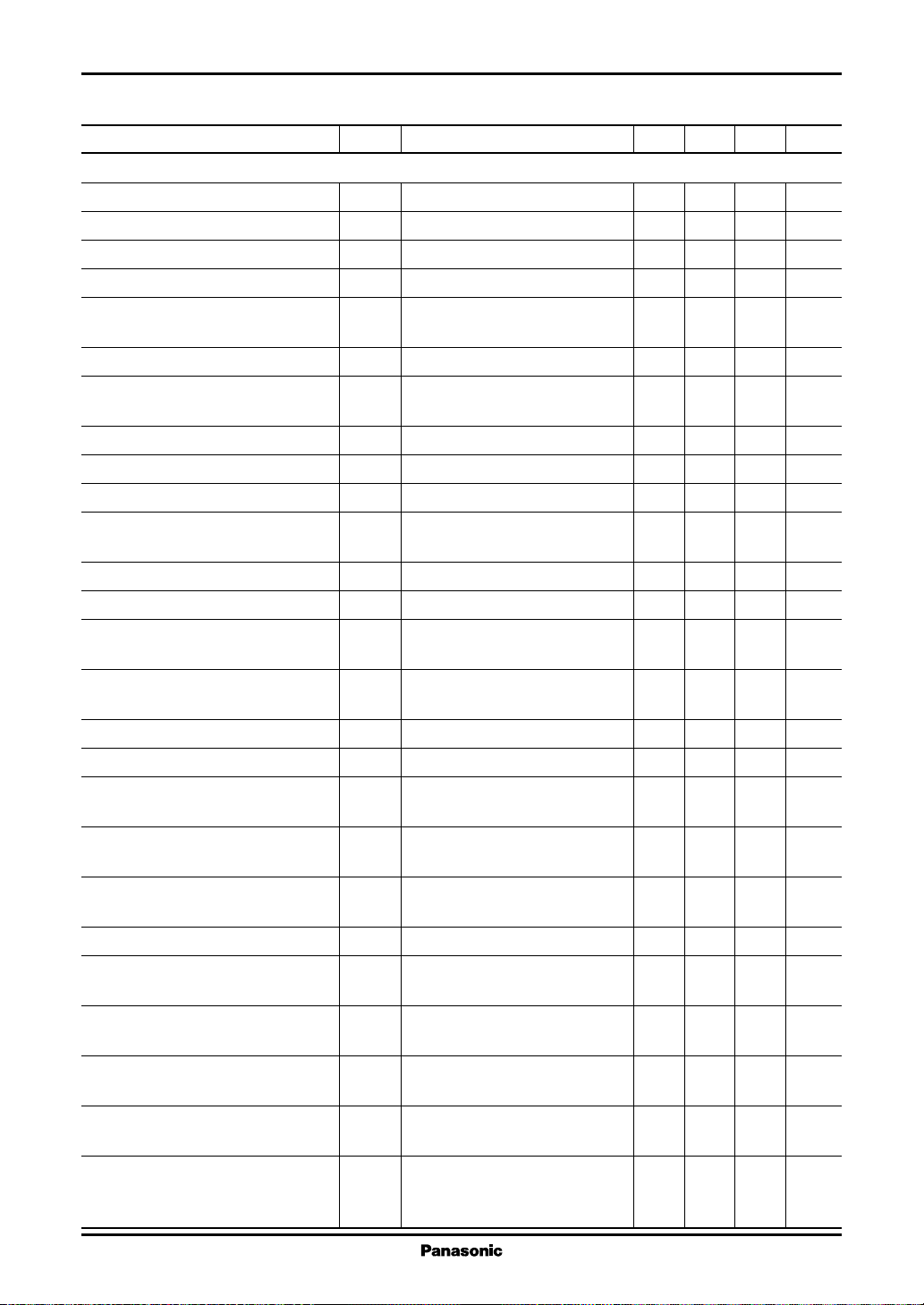

Page 3

ICs for TV AN5491K

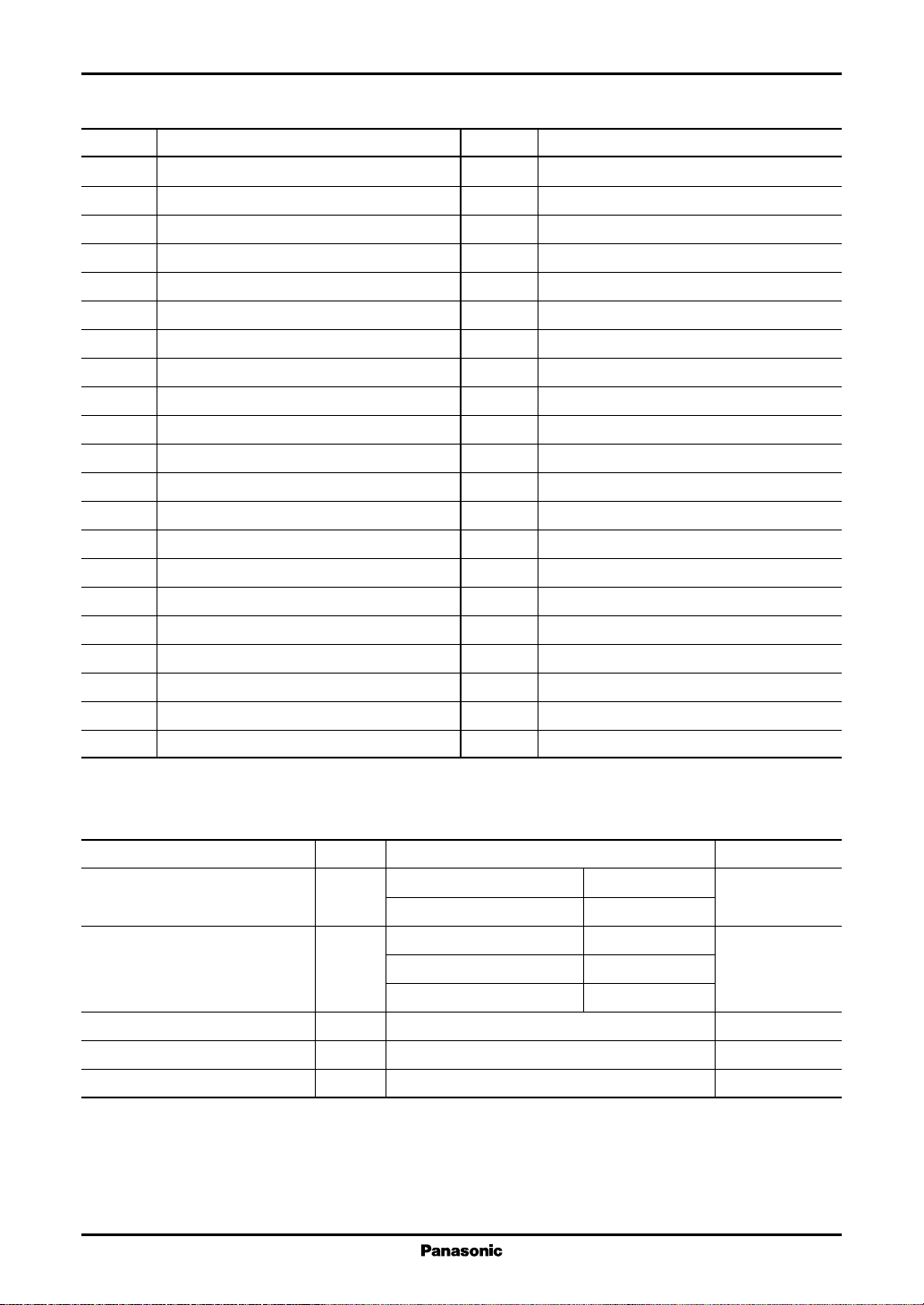

■ Pin Descriptions

Pin No. Description Pin No. Description

1 H-AFC1 22 V- AGC

2 H-pulse input 23 EHT-DC input

3H-V

4 Shut down SW 25 × 8

5 Comparator ref. (6.5 V) 26 × 4

6 Comparator 27 VGA

7 Comparator output 28 V-output

8 BLK output 29 DEF GND

9 V-SAW slice voltage (High) 30 Phase output

10 V-SAW slice voltage (Low) 31 × 2

11 V-SAW input 32 EW output

12 I2L VCC (5 V) 33 Corner slice voltage

13 I2C SDA input 34 I2L GND

14 I2C SCL input 35 × 1

15 DEF VCC (9 V) 36 H-GND

16 V-pulse input 37 Lock det.

17 V-pulse output 38 H-output

18 V-OSC 39 H-duty

19 × 32 40 H-AFC2

20 V-ramp 41 FBP input

21 Trapezoid correction voltage 42 H-OSC

(6.2 V) 24 EHT-AC input

CC

■ Absolute Maximum Ratings

Parameter Symbol Rating Unit

Supply voltage V

Supply current I

2

Power dissipation

*

Operating ambient temperature

1

Storage temperature

Note)*1: Except for the operating ambient temperature and storage temperature, all ratings are for Ta = 25°C.

2: The power dissipation shown is for the independent IC without a heat sink in free air at Ta = 70°C.

*

*

CC

CC

P

D

1

*

T

opr

T

stg

V

CC1

V

CC2

I

CC1

I

CC2

I

3

5.6 V

10

24 mA

29

14

600 mW

−20 to +70 °C

−55 to +150 °C

3

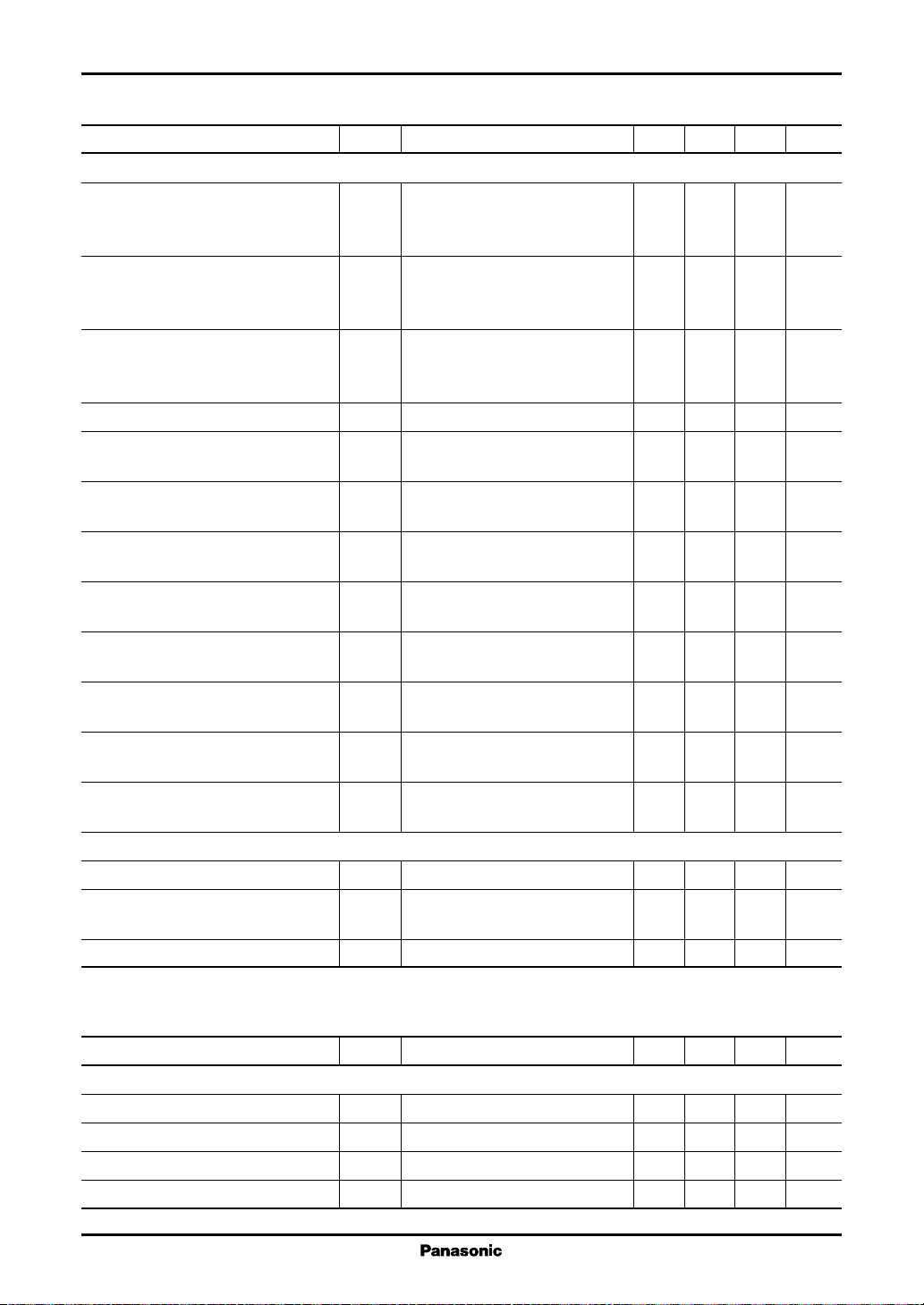

Page 4

AN5491K ICs for T V

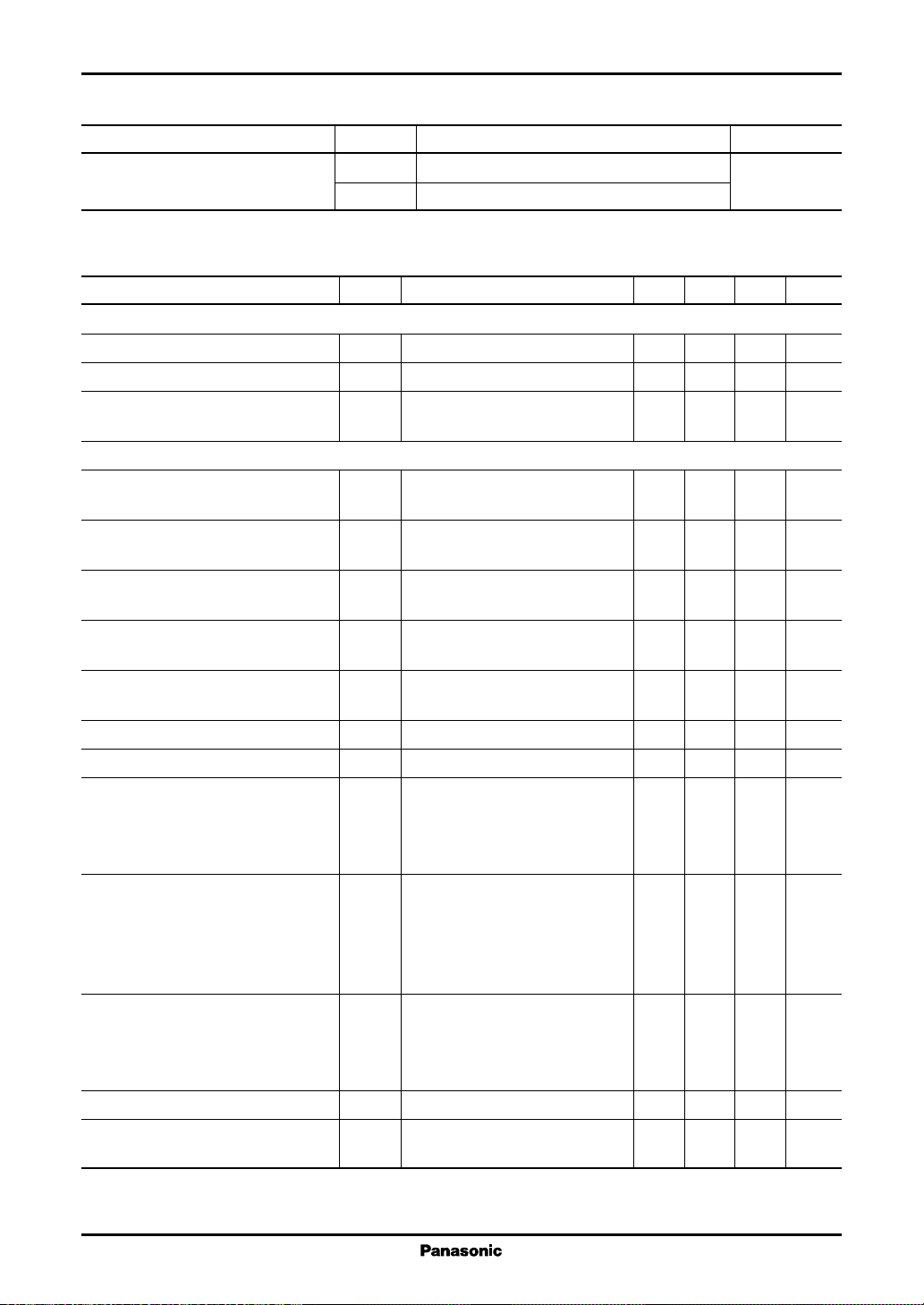

■ Recommended Operating Range

Parameter Symbol Range Unit

Supply voltage V

CC1

V

CC2

■ Electrical Characteristics at Ta = 25°C

Parameter Symbol Conditions Min Typ Max Unit

DC characteristics

Circuit current I

Circuit current I

Circuit current I

CC1

CC2

CC3

Synchronizing signal processing

Horizontal free-running oscillation f

frequency 1 [Divide-by-8] Pins 19, 26, 31, 35: Low

Horizontal free-running oscillation f

frequency 2 [Divide-by-16] Pins 19, 25, 26, 31, 35: Low

Horizontal free-running oscillation f

frequency 3 [Divide-by-32] Pin 19: High

Horizontal output pulse duty cycle 1 τ

[Divide-by-32] Pin 19: High

Horizontal output pulse duty cycle 2 τ

[Divide-by-32] Pin 19: High

Horizontal high-level output voltage V

Horizontal low-level output voltage V

Horizontal output start voltage V

Screen center variable range 1 t

[Divide-by-16] Pins 19, 26, 31, 35: High

Screen center variable range 2 t

[Divide-by-32] Change amount of phase difference

Horizontal input pulse threshold voltage

Over-voltage protective operation V

voltage

I

V

12

I

15

I

3

HO8

HO16

HO32

HO1

HO2

FHH

FHL

FHS

= 5 V, V

CC1

V

= 5 V, V

CC1

V

= 5 V, V

CC1

V

= 6.5 V

CC3

Pin 2: Without input, Pin 25: High 61.5 62.7 63.9 kHz

Pin 2: Without input 30.8 31.4 32.0 kHz

Pin 2: Without input 15.4 15.7 16.0 kHz

Pin 2: Without input, Pin 39: 2 V 11.7 14.0 16.6 µs

Pin 2: Without input, Pin 39: 5 V 23.9 28.5 33.7 µs

DC voltage for pin 38 high-level 2.8 3.5 4.2 V

DC voltage for pin 38 low-level 0 0.3 V

Minimum voltage of pin 3 to bec- 4.2 5.0 V

ome f > 10 kHz when horizontal

oscillation output is 1 V[p-p] or

more in divide-by-32 mode.

Pin 25: Low, 2.16 2.70 3.24 µs

DH16

Change amount of phase difference

between H

[00] to [1F]

Pin 19: Low, 3.8 4.8 5.8 µs

DH32

between HP and H out of Data 08:

[00] to [1F]

V

Slice level of pin 2 0.9 1.5 2.1 V

T2

Pin 4 voltage at I4 = 50 µA 0.60 0.75 0.90 V

4

4.5 to 5.0 to 5.5 V

8.1 to 9.0 to 9.9

= 9 V 13.6 17.0 20.4 mA

CC2

= 9 V 16.8 21.0 25.2 mA

CC2

= 9 V, 6.0 7.5 9.0 mA

CC2

and H-out of Data 08:

P

4

Page 5

ICs for TV AN5491K

■ Electrical Characteristics at Ta = 25°C (continued)

Parameter Symbol Conditions Min Typ Max Unit

Deflection correction processing

VP pulse for OSD low-level V

VP pulse for OSD high-level V

EHT-AC input pin voltage V

Vertical input signal threshold voltage V

Vertical free-running oscillation f

LOSDVCC1

HOSDVCC1

24

TFV

VO

frequency external R = 10 kΩ, C = 3.3 µF

Typical vertical output amplitude V

Typical EW output amplitude V

Phase out amplitude V

Ramp waveform amplitude V

AGC input and output current I

Service SW: ON time V

V

EW

PHASE

RAMPfV

AGC

28SW

Vertical output DC

BLK pulse high-level V

BLK pulse low-level V

Vertical output amplitude

∆V

HBLK

LBLK

AMPmax

variable ratio (max.) typ. → max.

Vertical output amplitude

∆V

AMPmin

variable ratio (min.) typ. → max.

Vertical output DC variable amount (min.)

Vertical output DC variable amount (max.)

Vertical output trapezoidal waveform

∆V

∆V

∆V

SHIFTmin

SHIFTmax

TRAPmin

correction variable amount (min.) Typ. → min.

Vertical output trapezoidal waveform

∆V

TRAPmin

correction variable amount (max.) Typ. → max.

External trapezoidal waveform V

21

center voltage

Vertical output center DC level V

EW output (min.) to parabolic V

28

EWmin

amplitude change

EW output (max.) to parabolic V

EWmax

amplitude change

EW output (min.) (DC) ∆V

EWmin

to horizontal amplitude change

EW output (max.) (DC) ∆V

EWmax

to horizontal amplitude change

EW output (bottom voltage) 1 ∆V

EDC1

to EHT-DC change Horizontal EHT: Max.

= 5 V, V

= 5 V, V

= 9 V 0 0.4 V

CC2

= 9 V 2.2 2.75 3.3 V

CC2

Pin 24: Open 2.00 2.45 2.90 V

Pin 16: Input 0.9 1.5 2.1 V

Pin 16: Without input 35 44 53 Hz

V amplitude DAC: Typ. 0.88 1.10 1.32 V[p-p]

EW output amplitude for typical ver- 0.8 1.0 1.2 V[p-p]

tical output amplitude = 1.25 V[p-p]

Side pin parallel, DAC: Typ. − 0.1 0 0.1 V[p-p]

= 50 Hz to 120 Hz 2.15 2.45 2.75 V[p-p]

1.6 2.0 2.4 mA

3.1 3.5 3.9 V

4.5 5.0 5.5 V

0 0.4 V

V amplitude ratio between +40 +50 +60 %

V amplitude ratio between −40 −50 −60 %

Vertical DC: Typ. → min. − 0.28 − 0.38 − 0.48 V

Vertical DC: Typ. → max. +0.28 +0.38 +0.48 V

Trapezoidal waveform correction: − 0.28 − 0.38 − 0.48 V

Trapezoidal waveform correction: +0.28 +0.38 +0.48 V

2.4 3.0 3.6 V

2.8 3.5 4.2 V

Parabolic amplitude: Min. − 0.1 0 0.1 V[p-p]

Parabolic amplitude: Max. 1.4 1.8 2.2 V[p-p]

Horizontal amplitude: Min. − 0.95 −1.15 −1.35 V

Horizontal amplitude: Max. +0.95 +1.15 +1.35 V

EHT-DC: 5.0 V → 3.8 V +1.04 +1.30 +1.56 V

EHT-AC gain: Min.

5

Page 6

AN5491K ICs for T V

■ Electrical Characteristics at Ta = 25°C (continued)

Parameter Symbol Conditions Min Typ Max Unit

Deflection correction processing (continued)

EW output (bottom voltage) 2 ∆V

to EHT-DC change Horizontal EHT: Max.

EW output (bottom voltage) 1 ∆V

to EHT-AC change Horizontal EHT: Max.

EW output (bottom voltage) 2 ∆V

to EHT-AC change Horizontal EHT: Max.

EW output parabolic DC level V

Parallelogram correction fluctuation 1 ∆V

(upper side) Typ. → min.

Parallelogram correction fluctuation 2 ∆V

(upper side) Typ. → max.

Parallelogram correction fluctuation 3 ∆V

(lower side) Typ. → min.

Parallelogram correction fluctuation 4 ∆V

(lower side) Typ. → max.

Bow shape correction fluctuation 1 ∆V

(upper side) Typ. → min.

Bow shape correction fluctuation 2 ∆V

(upper side) Typ. → max.

Bow shape correction fluctuation 3 ∆V

(lower side) Typ. → min.

Bow shape correction fluctuation 4 ∆V

(lower side) Typ. → max.

I2C interface

SCL, SDA input threshold voltage V

Sink capacity at ACK V

Maximum clock frequency f

EHT-DC: 5.0 V → 6.2 V −1.04 −1.30 −1.56 V

EDC2

EHT-AC gain: Min.

EHT-AC: 2.35 V → 1.35 V +0.25 +0.35 +0.45 V

EAC1

EHT-AC gain: Max.

EHT-AC: 2.35 V → 3.35 V − 0.25 − 0.35 − 0.45 V

EAC2

EHT-AC gain: Max.

Typ. 2.2 2.7 3.4 V

32

Parallelogram correction: +0.16 +0.26 +0.36 V

UPH1

Parallelogram correction: − 0.16 − 0.26 − 0.36 V

UPH2

Parallelogram correction: − 0.25 − 0.35 − 0.45 V

BPH1

Parallelogram correction: +0.16 +0.26 +0.36 V

BPH2

Bow shape correction: − 0.24 − 0.34 − 0.44 V

USD1

Bow shape correction: +0.12 +0.22 +0.32 V

USD2

Bow shape correction: − 0.17 − 0.27 − 0.37 V

BSD1

Bow shape correction: +0.12 +0.22 +0.32 V

BSD2

V

TH

ACK

= 5 V 1.5 3.0 dB

CC1

I = 3 mA in case of pull-up resistor 0.4 V

1.6 Ω

SCL

100 kHz

• Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

Parameter Symbol Conditions Min Typ Max Unit

DC characteristics

AGC pulse width τ

Ramp discharge current I

Ramp charge current 1 I

Ramp charge current 2 I

AGC

RAMP1

RAMP2

RAMP3

f = 120 Hz, Pin 4: 5.7 V 138 µA

f = 30 Hz, Pin 4: 7.5 V 32.9 µA

95 µs

3.6 mA

6

Page 7

ICs for TV AN5491K

■ Electrical Characteristics at Ta = 25°C (continued)

• Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

Parameter Symbol Conditions Min Typ Max Unit

DC characteristics (continued)

BLK output amplitude V

Vertical output drive current I

Vertical output amplitude fluctuation

with supply voltage ∆V

Vertical output DC fluctuation V

with supply voltage ∆V

EW output amplitude fluctuation V

with supply voltage ∆V

EW output DC fluctuation V

with supply voltage ∆V

V

BLK

28

V

CC

28

CC

EW

CC

32

CC

Difference of V

Difference of V

Difference of V

Difference of V

CCmax

CCmax

CCmax

CCmax

− V

− V

− V

− V

CCmin

CCmin

CCmin

CCmin

Synchronizing signal processing

Horizontal free-running oscillation f

Pin 2: Without input, Pin 19: Low 32.9 33.5 34.1 kHz

HO15

frequency [Divide-by-15] Pins 25, 26, 31, 35: High

Horizontal output pull-in range f

Pin 2: Without input, Pin 25: High ±2 000 ±2 600 Hz

HP8

[Divide-by-8] Pins 19, 26, 31, 35: Low

Comparator detection operation voltage

V

Pin 6: Minimum voltage to become

6

high, Pin 5: 6.2 V

Lock detection output voltage V

Lock detection charge and discharge I

V37 in horizontal AFC lock mode 5.7 6.3 6.9 V

37

DC measurement in divide-by-32 ±0.8 mA

LOCK

current

FBP (AFC2) slice level V

Minimum voltage of pin 41 at 1.5 1.9 2.3 V

TFBP

which AFC operates.

Horizontal AFC µµDC measurement in divide-by-32 37 µA/µs

Horizontal VCO ββSlant of β curve near f = 15.7 kHz 1.9 Hz/mV

FBP allowable range 1 t

Time from H-out rise to FBP 3 9 µs

FBP8

[Divide-by-8] center

FBP allowable range 2 t

FBP16

Time from H-out rise to FBP 4 13 µs

[Divide-by-16] center

FBP allowable range 3 t

FBP32

Time from H-out rise to FBP 6 20 µs

[Divide-by-32] center

AFC1 reference current 1 I

AFC1 reference current 2 I

AFC1 reference current 3 I

AFC1 reference current 4 I

Horizontal output pull-in range 1 f

Data 0C = "11" (D1, D0) 0.82 mA

AFC1

Data 0C = "01" (D1, D0) 1.1 mA

AFC2

Data 0C = "10" (D1, D0) 1.5 mA

AFC3

Data 0C = "00" (D1, D0) 2.0 mA

AFC4

Pin 2: Without input ±1 000 ±1 300 Hz

HP16

[Divide-by-16] Pins 19, 25, 26, 31, 35: Low

Horizontal output pull-in range 2 f

Pin 2: Without input ±500 ±650 Hz

HP32

[Divide-by-32] Pin 19: High

456V

−2 mA

0.1 V

1.0 V

0.1 V

1.0 V

5.7 6.3 6.9 V

7

Page 8

AN5491K ICs for T V

■ Electrical Characteristics at Ta = 25°C (continued)

• Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

Parameter Symbol Conditions Min Typ Max Unit

Deflection correction processing

Vertical output S-shape variable ∆V

ratio 1 Ratio of min.→max.

Vertical output S-shape variable ∆V

ratio 2 max. (Change of V-out 40% to

Vertical output (upper side) ∆V

linearity variable ratio 1 Typ.→max.

Vertical output (upper side) ∆V

linearity variable ratio 2 Typ.→min.

Vertical output (lower side) ∆V

linearity variable ratio 1 Typ.→max.

Vertical output (lower side) ∆V

linearity variable ratio 2 Typ.→min.

Vertical output ∆V

EHT-DC change 1

Vertical output ∆V

EHT-DC change 2

Vertical output ∆V

EHT-AC change 1 EHT: Max., EHT gain: Max.

Vertical output ∆V

EHT-AC change 2 EHT: Max., EHT gain: Max.

EW output (min.)

∆V

to trapezoidal waveform change Trapezoidal: Typ. → min.

EW output (max.)

∆V

to trapezoidal waveform change Trapezoidal: Typ. → max.

EW output (min.) to upper corner ∆V

trapezoidal waveform change Corner slice voltage: 1 V

EW output (max.) to upper corner ∆V

trapezoidal waveform change Corner slice voltage: 1 V

EW output (min.) to lower corner ∆V

trapezoidal waveform change Corner slice voltage: 1 V

EW output (max.) to lower corner ∆V

trapezoidal waveform change Corner slice voltage: 1 V

External trapezoidal waveform correction

∆V

fluctuation 1 (Parabolic amplitude) 3 V → 2 V

External trapezoidal waveform correction

∆V

fluctuation 2 (Parabolic amplitude) 3 V → 4 V

Vertical S-shape: −28 %

SC1

Vertical S-shape: Ratio of min.→ 1.5 %

SC2

60% point)

Vertical linearity (upper side): +12 %

ULIN1

Vertical linearity (upper side): −10 %

ULIN2

Vertical linearity (lower side): +9 %

BLIN1

Vertical linearity (lower side): −11 %

BLIN2

EHT-DC = 5.0 V → 3.8 V −30 %

EDC1

Vertical EHT: Max., EHT gain: Max.

EHT-DC = 5.0 V → 6.2 V +25 %

EDC2

Vertical EHT: Max., EHT gain: Max.

EHT-AC = 2.35 V → 1.35 V −12 %

EAC1

EHT-AC = 2.35 V → 3.35 V +12 %

EAC2

Trapezoidal SW: On, −40 %

TRAPmin

Trapezoidal SW: On, +40 %

TRAPmax

Upper corner: Typ. → min. −45 %

UCmin

Upper corner: Typ. → max. +45 %

UCmax

Lower corner: Typ. → min. −45 %

BCmin

Lower corner: Typ. → max. +45 %

BCmax

External trapezoidal correction: −40 %

ETR1

External trapezoidal correction: +40 %

ETR2

8

Page 9

ICs for TV AN5491K

■ Electrical Characteristics at Ta = 25°C (continued)

• Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

Parameter Symbol Conditions Min Typ Max Unit

I2C interface

3, 4, 5, 6-bit DAC DNLE L1 1LSB = 0.1 1.0 1.9 LSB/step

{Data(max.) − Data(00)}/7,15,31,63

7-bit DAC DNLE (Except for 40) L2

7-bit DAC DNLE (40 only) L3

■ Terminal Equivalent Circuits

Pin No. Equivalent circuit Description Voltage

1 AFC1:

6.5 V

3.15 V

1

1LSB = {Data(max.) − Data(00)}/127

1LSB = {Data(max.) − Data(00)}/127

Horizontal frequency detection pin

4.3 V

27 kΩ

• Pin for adjusting the frequency of horizontal input pulse and the internal refere- DC

nce pulse. approx. 4.3 V

• Connect a lag lead filter.

0.1 1.0 1.9 LSB/step

−1.0 1.0 2.0 LSB/step

5.3 V

2 H-pulse in: AC

3 V

100 kΩ

2

1 kΩ

3V

4 Shut down: DC

4

12 V

330 Ω

3

28 kΩ 28 kΩ

9 V

1.5 V

6.5 V

Horizontal synchronizing signal input pin

• Polarity is as shown in the right figure

(Negative).

• Slice level is 1.5 V.

• Input polarity is one polarity only

(not corresponding to both polarities).

:DC

CC

Horizontal system power supply (6.5 V) pin 6.5 V

• Connect an external zener

Control pin for shut-down Normal: GND

•

Horizontal output stops (GND) if a voltage

1 VBE and over (more than approx. 0.75 V)

is applied to the pin.

1.5 V

H rate

9

Page 10

AN5491K ICs for T V

Upper side

BLK

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

5 Comparator ref.: DC

5

6.5 V

1 kΩ

Reference voltage input pin for comparator

•

Attach zener diode externally (approx. 6.2 V)

(Usable as reference voltage for hold-down)

6 Comparator: DC

7 Comparator out: DC

8 BLK out: DC

6

7

6.5 V

1 kΩ

20 kΩ

1 kΩ

5

9 V

25 kΩ

48.3 kΩ

20 kΩ

9 V

Input pin for comparator detection

• (Usable as pin for hold-down detection)

Comparator detection output pin Normally:

• Connect pull-up resistors outside the IC. High

(usable as hold-down control pin)

Note) Use under 400 µA or less.

Blanking pulse output pin At BLK: High

• Normally: Low

At BLK: High (5 V)

8

99.8 kΩ

9 Upper side slice: DC

10

9 V

9

20 kΩ

145 Ω145 Ω

Upper side slice voltage input pin for BLK

pulse generation

Page 11

ICs for TV AN5491K

Lower side

BLK

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

10 Lower side slice: DC

9 V

Lower side slice voltage input pin for BLK

Pulse generation

10

20 kΩ

145 Ω

11 V-SAW in: AC

9 V

V-SAW input pin for BLK pulse generation

25 µA

11

20 kΩ

145 Ω

12 VCC:DC

Power supply (5 V) pin for DAC/I2L5 V

• Connect a pass capacitor (0.01 µF) between

pin 12 and GND (pin 19).

13 SDA:

5 V

2

I

C data input pin

5 V

20 µA

13

14 SCL:

1 kΩ

5 V

2

I

C clock input pin

GND

5 V

20 µA

14

1 kΩ

GND

15 VCC:DC

Pin for deflection system power supply (9 V) 9 V

• Connect a pass capacitor between the pin

and GND.

11

Page 12

AN5491K ICs for T V

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

16 V-pulse in: AC

290 Ω

16

30 kΩ

290 Ω

25 µA

9 V

1.5 V

Vertical sync. signal input pin (Pulse)

• Polarity is as shown in the right figure

(Negative)

• Slice level is 1.5 V.

• Input polarity is only one polarity

(Not correspond to both polarities)

1.5 V

0 V

V rate

17 V-pulse out: AC

17

18 V-OSC: AC

19 × 32: DC

9 V

18

1 kΩ

150 kΩ

19

55 kΩ

5 V

30 kΩ

9 V

36 kΩ

50 µA

6.5V

Vertical sync. signal output pin (Pulse)

• If vertical sync. signal input is present:

Outputs the pulse synchronized with input V.

Not present: Outputs free-running V pulse.

(Usable for microcomputer OSD control)

Vertical oscillation pin

• Connect CR.

• Free-running oscillation when there is no

input.

Horizontal free-running oscillation frequency

control pin

• To be used by high/low control.

• Input is controlled by open collector output.

2.5 V

V rate

V rate

0 V

5.8 V

3.1 V

30 kΩ

30 kΩ

20 V-ramp pin: AC

1kΩ

20

12

9V

• The pin for generating reference V sawtooth

waveform for IC inside.

• Connect an 0.22 µF mylar capacitor.

2.5V

V rate

2.5 V

0 V

Page 13

ICs for TV AN5491K

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

21 External trapezoidal waveform: DC

21

25 µA

145 Ω

9 V

The pin for controlling trapezoidal wavefo- 2 V to 4 V

rm compensation from outside.

• Used by linking to V-position shift (at AC coupling). typ. 3.0 V

22 V-AGC: DC

500 Ω

22

500 Ω

23 EHT-DC: DC

23

20 kΩ

24 EHT-AC AC

25 µA

20 kΩ 20 kΩ

24

145 Ω

9 V

25 µA

145 Ω

9 V

145 Ω

9 V

3.8 V

5.45 V

Vertical AGC pin

• AGC pin to make a vertical output amplitude constant.

• Connect 3.3 µF tantalum capacitor.

Pin for extremely high-tension compensation

(EHT)

• DC-coupled to pin.

Pin for extremely high-tension compensation

• AC-coupled to pin.

Operating range:

3.8 V to 6.2 V

2.35 V in an

open mode

Operating range:

1.35 V to 3.35 V

25 × 8: DC

150 kΩ

25

20 kΩ

20 kΩ

6.5 V

Horizontal free-running oscillation frequency

control pin

• To be used by high/low control.

• Input is controlled by open collector output.

13

Page 14

AN5491K ICs for T V

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

26 × 4: DC

150 kΩ

26

20 kΩ

20 kΩ

6.5 V

Horizontal free-running oscillation frequency

control pin

• To be used by high/low control.

• Input is controlled by open collector output.

27 V-FB: DC

28 V-out: A C

29 GND: DC

30 Phase out: AC

30

28

27

6.5 V

300 Ω

100 Ω

60 kΩ

290 Ω

× 5

× 5

290 Ω

9 V

9 V

Forced progressive mode pin

• To be used by high/low control.

• At high: Multi-point mode

At low: Progressive mode

V sawtooth waveform output pin

• Typ. 1.25 V[p-p]

GND pin for deflection-system circuit (9 V) GND

Pin for side pin (Bow shape) correction, parallelogram correction and control pulse output. DC

• Connect to H-AFC2 pin via 1 µF (non- approx. 3.7 V

polarity) capacitor.

9 V

0 V

14

290 Ω

Max.

300 mV[p-p]

Page 15

ICs for TV AN5491K

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

31 × 2: DC

150 kΩ

31

20 kΩ

20 kΩ

6.5 V

Horizontal free-running oscillation frequency

control pin

• To be used by high/low control.

• Input is controlled by open collector output.

32 EW out: AC

500 Ω

32

33 Corner slice: DC

50 µA 50 µA

33

34 GND: GND pin for 5 V system (I2C/I2L) DC

35 × 1: DC

150 kΩ

35

10 kΩ

40 kΩ

300 Ω

6.5 V

9 V

10 kΩ

1.5 V

Parabolic waveform output pin

9 V

The voltage to set a slice point of upper and

lower corner correction.

• The correction gain can be controlled inde- Externally set

pendently by I

respectively. 1.25 VDC

Horizontal free-running oscillation frequency

control pin

• To be used by high/low control.

2

C bus for upper and lower, at 0 VDC to

GND

9 V

36 GND: GND pin for 6.5 V system DC

(Horizontal system) GND

37 Lock det.: DC

200 Ω

820 µA

37

880 µA

6.5 V

Horizontal lock detection pin

• Connect 0.022 µF and 1 MΩ between the At lock mode:

pin and GND. 6 V

At unlocked

mode: GND

15

Page 16

AN5491K ICs for T V

■ Terminal Equivalent Circuits (continued)

Pin No. Equivalent circuit Description Voltage

38 H-out: AC

3.2 mA

38

40 kΩ

15 kΩ

6.5 V

Horizontal output pin

• The length of high-period can be adjusted

by a separate pin.

2.9 V

GND

H rate

39 H-duty: DC

124 kΩ

39

10 kΩ

124 kΩ

40 AFC2: DC

40

3.9 V

41 FBP input pin: AC

2.7 kΩ

41

100 kΩ

6.5 V

1.9 V

50 µA

6.5 V

6.5 V

1.9 V

Pin for controlling the length of high-period 1 V to 5 V

of horizontal output pulse.

• Apply DC voltage from the outside.

Horizontal phase detection pin 1.5 V to 4.5 V

• Pin for controlling phase difference bet-

ween horizontal output pulse and FBP.

• Phase out waveform is also connected to

this pin via capacitor.

• Connect 0.015 µF between this pin and

GND.

• Slices at 1.9 V (in the IC) and then uses

as AFC2 control pulse.

• Do not input any signal under GND insi-

de the IC.

1.9 V

GND

42 H-OSC: AC

270 Ω

42

100 µA

16

300 Ω

200 µA

270 Ω

10 kΩ

6.5 V

Reference oscillation pin (500 kHz)

• Connect CERALOCK (CSB500F48), and

temperature guaranteed (N750) 220 pF

capacitor in series between this pin and

GND.

3.0 V

2.25 V

0.5 V[p-p]

Page 17

ICs for TV AN5491K

■ Application Circuit Example

9 V

AGC

3.3 µF

22 21

Trapezoid

EHT DC

EHT AC

V-out

DEF GND

Phase out

EW out

Corner level

VGA

2

I

L GND

H-GND

Lock det.

23 20

Ramp

0.22 µF

24

18

9 V

28

29

30

17

16

15

14

32

33

13

12

V

× 32

× 8

× 4

× 2

× 1

19

25

26

31

35

27

11

10

9

8

34

7

1 MΩ

36

37 6

10 kΩ

4.7 kΩ

4.7 kΩ

3.3 µF

9 V

5 V

V-OSC

VS2

VP in

DEF V

CC

SCL

SDA

2

L V

I

CC

V-SAW in

V-SAW lower

V-SAW upper

BLK out

Comparator out

Comparator in

H-out

H-duty adj.

H-AFC2

FBP in

0.22 µF

6.5V

1 µF

6.5 V

220 pF

H-OSC

1: Horizontal oscillator

*

TAFCSB500F48

[Murata Manufacturing Co. Ltd.]

38

39 4

10 kΩ

40

41

1

*

42

5

3

2

1

6.5 V

22 µF

6.5 V

330 Ω

620 Ω

0.033 µF

Comparator ref.

Shut down

H-V

CC

12 V

H-pulse in

H-AFC1

17

Loading...

Loading...