Page 1

AN2566

Application note

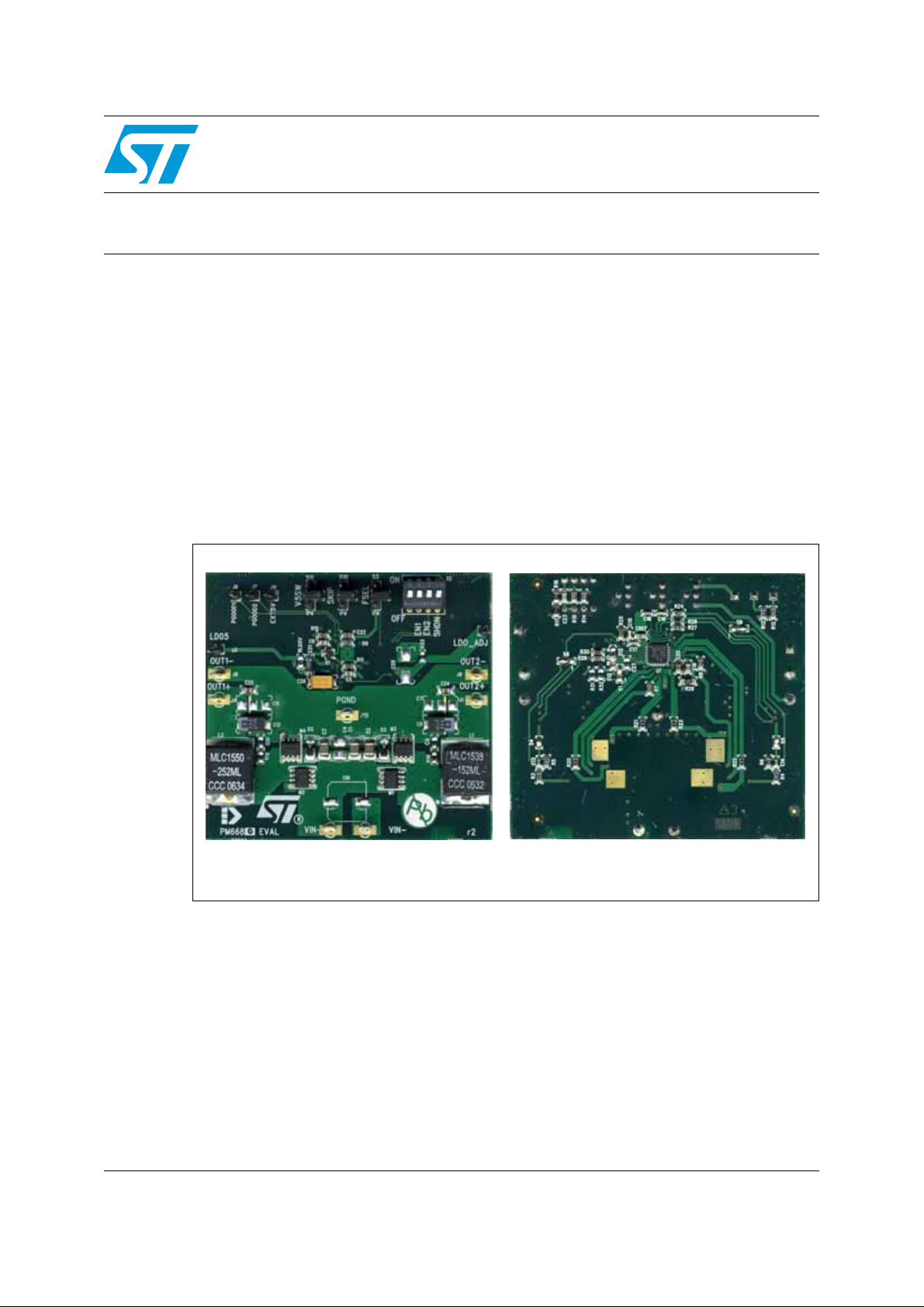

PM6680 evaluation kit dual step-down controller

with auxiliary voltages for notebook power system

Introduction

PM6680A evaluation kit order code: STEVAL-ISA053V1.

The PM6680 is a dual step-down controller with adju stable output voltages for notebook

computer power systems . The PM66 80 e valuation kit is designed to test the performance of

the PM6680 by employing a typical application circuit that allows testing of all PM6680

device functions. The kit features two switching sections, with (typically) 1.5 V and 1.05 V

outputs, from a 6 V to 28 V input battery voltage. The operating switching frequency of the

two switching sections is 200 kHz / 300 kHz, respectively. Each switching section delivers

more than 5 A output current. Moreover, an internal linear regulator can provide 5 V @ 100

mA peak current.

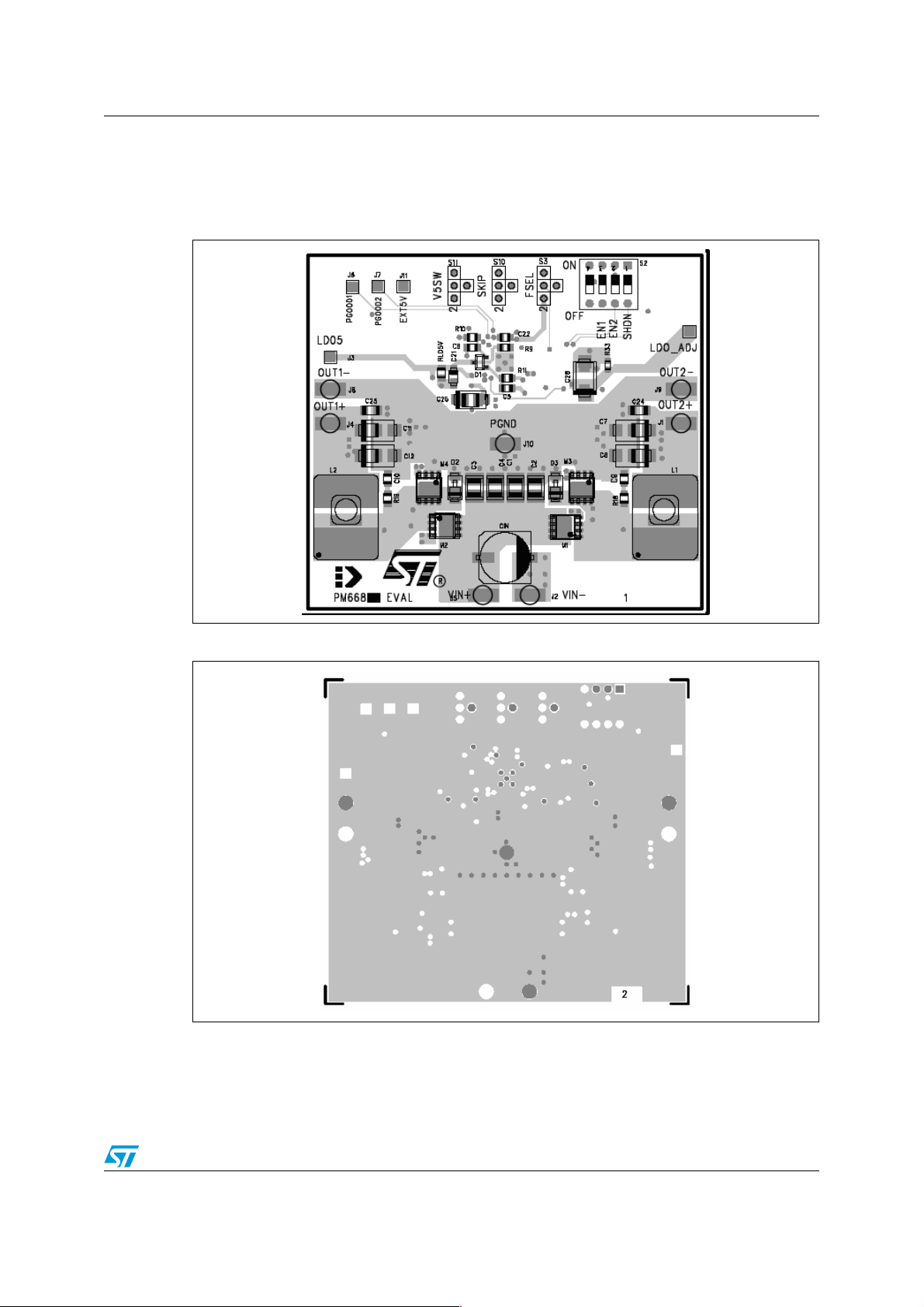

Figure 1. PM6680 evaluation kit

Top

April 2008 Rev 3 1/29

Bottom

www.st.com

Page 2

Contents AN2566

Contents

1 Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Evaluation kit schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Component list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4 Evaluation board layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5 I/O interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

6 Recommended equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

7 Quick start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

8 Jumper settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

9 Feedback output connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

10 Test setup and performance summary . . . . . . . . . . . . . . . . . . . . . . . . . 17

10.1 Test setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

10.2 Power-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

10.3 Soft-start and shutdown waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

10.4 1.5 V and 1.05 V output efficiency vs. load current . . . . . . . . . . . . . . . . . 19

10.5 Power consumption analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

10.6 Switching frequency vs. load current . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

10.7 Linear regulator output voltages vs. output current . . . . . . . . . . . . . . . . . 24

10.8 Load transient responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

11 Representatives waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

12 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2/29

Page 3

AN2566 List of figures

List of figures

Figure 1. PM6680 evaluation kit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 2. Evaluation kit schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. PM6680 evaluation board layout - top layer (PGND plain and component side) . . . . . . . . . 9

Figure 4. PM6680 evaluation board layout - inner layer 1 (SGND layer and V

Figure 5. PM6680 evaluation board layout - inner layer 2 (SGND layer and signals) . . . . . . . . . . . . 10

Figure 6. PM6680 evaluation board layout - bottom layer (PM6680 and component side). . . . . . . . 10

Figure 7. REF and LDO5 power-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 8. Section 1 soft-start waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 9. Section 2 soft-start waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 10. Section 1 shutdown waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 11. Section 2 shutdown waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 12. 1.5 V SMPS efficiency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 13. 1.05 V SMPS efficiency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 14. Input current vs. input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 15. Input current vs. input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 16. Input current vs. input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 17. Device current consumption vs. input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 18. Device current consumption vs. input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 19. 1.5 V output switching frequency vs. load current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 20. 1.05 V output switching frequency vs. load current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 21. LDO5 output vs. load current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 22. SMPS 1.5 V load transient response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 23. SMPS 1.05 V load transient response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 24. SMPS pulse skip mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 25. SMPS no-audible skip mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 26. SMPS PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

plane) . . . . . . . . . . . 9

IN

3/29

Page 4

List of tables AN2566

List of tables

Table 1. Component list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. The test points of the evaluation board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 3. Jumper S11 - V5SW pin connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 4. Jumper S3 - FSEL pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 5. Jumper S10 - SKIP pin connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 6. Jumper S4, S5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 7. Jumper S8, S9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 8. Jumper S4, S5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 9. Jumper S8, S9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 10. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4/29

Page 5

AN2566 Main features

1 Main features

● Constant on-time control allows very fast load transients

● 6 V to 28 V input voltage range

● 5 V auxiliary output voltage

● Adjustable switching outputs

● Lossless current sensing using lo w side MOSFET R

●

Negative current limit

● Soft-start internally fixed at 2.8 ms

● Soft-end for output discharge

● 200 kHz / 300 kHz, 300 kHz / 400 kHz, 400 kHz / 500 kHz (5 V / 3 V selectable

switching frequency)

● Selectable pulse skip and no-audible skip modes at light loads

● Independent power good signals

DS(on)

5/29

Page 6

Evaluation kit schematic AN2566

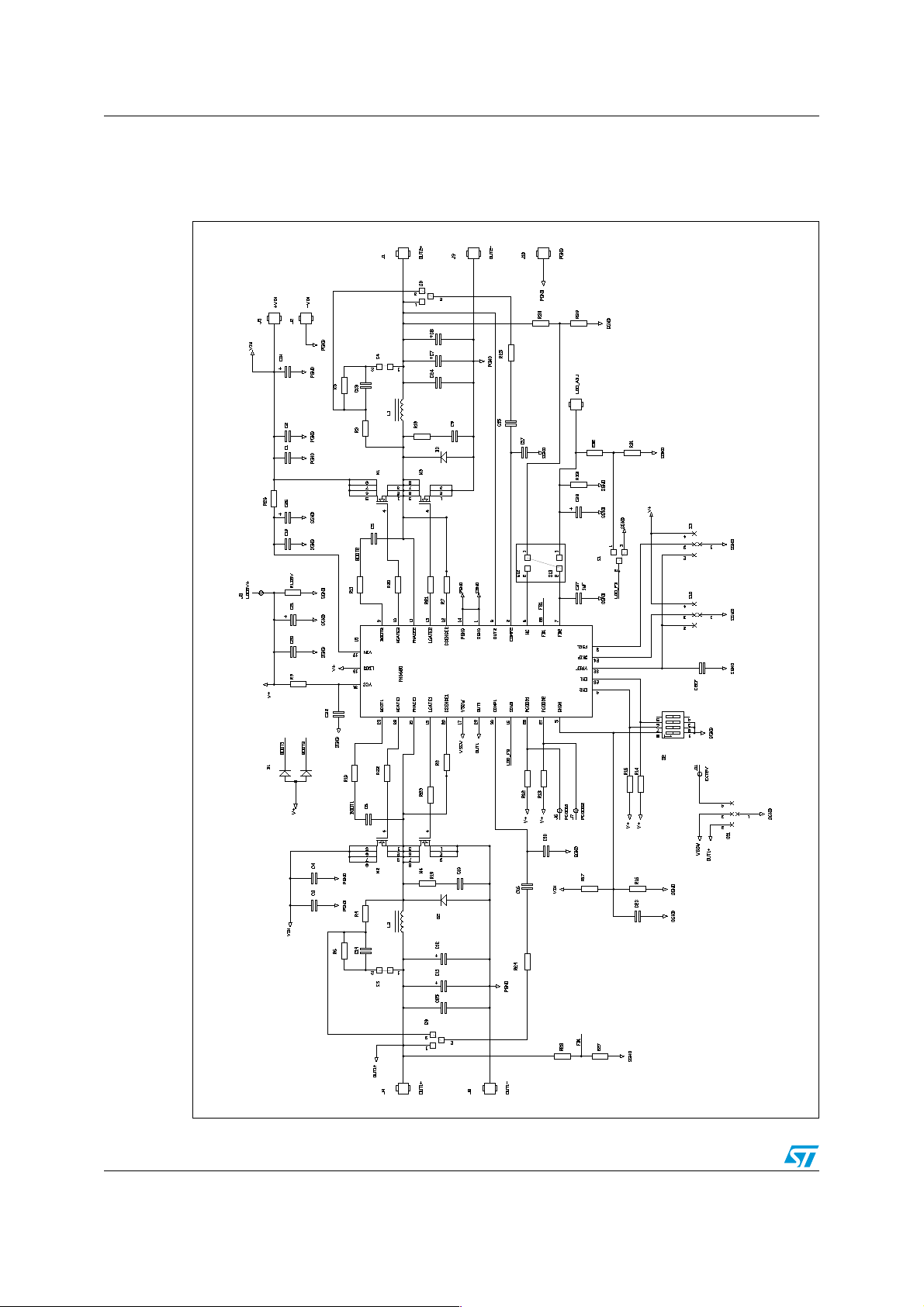

2 Evaluation kit schematic

Figure 2. Evaluation kit schematic

6/29

Page 7

AN2566 Component list

3 Component list

Table 1. Component list

Name Description Size Value Supplier Part number

C1, C2,

C3

C4

C5, C6 Ceramic capacitor 0805 0,1 µF Standard

C7 Low ESR capacitor D case Not installed Standard

C8

C11 Low ESR capacitor D case Not installed Standard

C12

C13, C14 Ceramic capacitor 0805 5.6 nF Standard

C15, C16 Ceramic capacitor 0603 1 nF Standard

C17, C18 Ceramic capacitor 0603 47 pF Standard

C19

C26

C20 Ceramic capacitor 0603 1 µF Standard

C21

C22 Ceramic capacitor 0805 220 nF Standard

Ceramic capacitor

50 V

Ceramic capacitor

50 V

Low ESR capacitor

4 V, 12 mΩ ESR

Low ESR capacitor

4 V, 12 mΩ ESR

Ceramic capacitor

50 V

Tantalum capacitor

35 V

Tantalum capacitor

package A, 16 V

1210 10 µF Taiyo Yuden UMK325BJ106KM

1210 Not installed

D case 330 µF POSCAP - Sanyo 4TPD33OM

D case 330 µF POSCAP - Sanyo 4TPD33OM

0805 0.1 µF Standard B37941K5104K62

C case 4.7 µF AVX TPS TPSC475*035#0600

B case 4.7 µF AVX THJ THJB475*016#JN

C9, C10 Ceramic capacitor 0805 Not installed Standard

C23 Ceramic capacitor 0603 10 pF Standard

CIN

CREF Ceramic capacitor 0603 100 nF Standard

C24,C25 Ceramic capacitor 0805 10 µF Standard

C27 Ceramic capacitor 0805 Not installed Standard

C28 Tantalum capacitor 3216 Not installed Standard

D1 Dual Schottky diode SOT23 STMicroelectronics BA T54A

D2,D3 Diode 1 A, 30 V DO216-AA STMicroelectronics STPS1L30M

IC1 PM6680 device

Electrolytic capacitor

39 µF, 25 V

D 10 mm Not installed Sanyo 25SVPD39M

VFQFPN-32

5 mm x 5 mm

STMicroelectronics PM6680

7/29

Page 8

Component list AN2566

Table 1. Component list (continued)

Name Description Size Value Supplier Part number

L1

L2

M1

M2

M3

M4

R7,R8 Resistor 0805 680 Ω Standard

R3 Resistor 0805 22 kΩ Standard

R4 Resistor 0805 36 kΩ Standard

R5 Resistor 0805 3.3 kΩ Standard

R6 Resistor 0805 3 kΩ Standard

R24 Resistor 0805 1.1 kΩ Standard

R25 Resistor 0805 820 Ω Standard

R9 Resistor 0805 47 Ω Standard

R10,R11 Resistor 0805 10 Ω Standard

1.5 µH inductor, 12 A

sat.

2.5 µH inductor, 8 A

sat.

MOSFET control FET

SO-8

MOSFET control FET

SO-8

MOSFET Sync FET

SO-8

MOSFET Sync FET

SO-8

13 mm x

13 mm

13 mm x

13 mm

SO-8 STMicroelectronics STS12NH3LL

SO-8 STMicroelectronics STS12NH3LL

SO-8 STMicroelectronics STS12NH3LL

SO-8 STMicroelectronics STS12NH3LL

1.5 µH Coilcraft MLC1538-152ML

2.5 µH Coilcraft MLC1550-252ML

R12,R13,

R14,R15

R16 Resistor 0603 150 kΩ Standard

R18,R19 Resistor 0603 Not installed

R17 Resistor 0603 560 kΩ Standard

R26 Resistor 1206 3.9 Ω Standard

R20, R21,

R22, R23

R27 Resistor 0805 10 kΩ Standard

R28 Resistor 0805 6.8 kΩ Standard

R29 Resistor 0805 11 kΩ Standard

R30 Resistor 0805 1.8 kΩ Standard

R31 Resistor 0805 Not installed Standard

R32 Resistor 0805 Not installed Standard

RLD5V,

RLD3V

Resistor 0603 100 kΩ Standard

Resistor 0805 0 Ω Standard

Resistor 0805 Not installed Standard

8/29

Page 9

AN2566 Evaluation board layout

4 Evaluation board layout

Figure 3. PM6680 evaluation board layout - top layer (PGND plain and component

side)

Figure 4. PM6680 evaluation boar d la y out - inner la y er 1 (SGND la y er and V

plane)

IN

9/29

Page 10

Evaluation board layout AN2566

Figure 5. PM6680 evaluation board layout - inner layer 2 (SGND layer and signals)

Figure 6. PM6680 evaluation board layout - bottom layer (PM6680 and component

side)

10/29

Page 11

AN2566 I/O interface

5 I/O interface

The evaluation board has the following test points.

Table 2. The test points of the evaluation board

Test point Description

V

+ Input voltage

IN

- Input voltage ground

V

IN

LDO5 5 V linear regulator output

LDO_ADJ Not used for this device

EXT5V 5 V external input

OUT1+ OUT1 switching section output

OUT1- OUT1 switching section output ground

PGOOD1 OUT1 switching section power good

OUT2+ OUT2 switching section output

OUT2+ OUT2 switching section output ground

PGOOD2 OUT2 switching section power good

J10 Junction pin between PGND and SGND planes

11/29

Page 12

Recommended equipment AN2566

6 Recommended equipment

● 6 V to 28 V power supply, notebook computer battery or AC adapter

● Active loads

● Digital multimeter

● 500 MHz four-trace oscilloscope

12/29

Page 13

AN2566 Quick start

7 Quick start

1. Connect the VIN+ and VIN- test points of the evaluation board to an external power

supply.

2. Ensure that all DIP switches (S2) are in the "OFF" position. In this condition all outputs

are disabled (shutdown mode).

3. Turn S2

(standby-mode).

4. Turn S2

regulation of the output. PGOOD1 pin goes high after soft-start.

5. Turn S2

regulation of the output. PGOOD2 pin goes high after soft-start.

6. In order to load the switching ou tputs, the loads must be connected between the "+"

and the "-" output test points, respectively.

7. In order to load the linear outputs, the loads must be connected between J10 and

LDO5 or alternative RLD5V resistors can be used on the evaluation board.

to the “ON” position (SHDN pin high). This turns on the LDO5 output

1

to the “ON” position (EN1 pin high). The 1.5 V switching controller begins

2

to the “ON” position (EN2 pin high). The 1.05 V switching controller begins

3

13/29

Page 14

Jumper settings AN2566

8 Jumper settings

It is possible to select different working conditions by using the jumpers on the board.

Note: Jumpers S1,S6, S7, S12 and S13 are alread y soldere d on the evaluation board and it is not

necessary to change them. Please refer to the schemat ic to verify their proper connection.

The external bypass connections for the linear regulator LDO5 are set by connecting the

V5SW pin to jumper S11 as indicated in Table 3 below.

Table 3. Jumper S11 - V5SW pin connections

Position LDO5 working conditions

OUT5V

SGND

EXT5V

When the main output voltage is greater than the boostrap-switchover

threshold, an internal 3 Ω (max) P-chann el MOSFET switch connects the

V5SW pin to the LDO5 pin shutting down the LDO5 internal linear

regulator. If not used, it must be tied to ground.

The internal linear regulator LDO5 is always on. In this case LDO5

supplies all gate drivers and the internal circuitry. It can provide an output

peak current of 100 mA.

The internal linear regulator LDO5 remains off if an alternative 5V external

voltage is applied to the EXT5V test-point. An internal 3 Ω (max) P-

channel MOSFET switch connects V5SW pin to LDO5 output. The gate

drivers and internal circuitry are supplied by the same 5 V external voltage

applied.

The FSEL pin is connected to jumper S3 to select the SMPS frequency. The jumper

positions and corresponding frequencies are shown in Table 4 below.

Table 4. Jumper S3 - FSEL pin connections

Position SMPS OUT1 SMPS OUT2

SGND

200 kHz 300 kHz

VREF

LDO5

14/29

300 kHz 400 kHz

400 kHz 500 kHz

Page 15

AN2566 Jumper settings

To select the switching operation mod e of the SMPS , connect the SKIP pin to jumper S10 as

described in Table 5.

Table 5. Jumper S10 - SKIP pin connections

Position Switching operating mode

GND

VREF

LDO5

If the SKIP pin is tied to ground, a pulse skip mode takes place at light

loads. A zero crossing comparator prev ents the in ductor current fr om going

negative.

if the SKIP pin is tied to VREF pin enables a pulse skip mode with a

minimum switching frequency about 25 kHz (ultrasonic mode).

If the SKIP pin is tied to 5 V, The fixed PWM mode takes place. The

switching output is in a position to sink and source current from the load.

15/29

Page 16

Feedback output connections AN2566

9 Feedback output connections

Table 6 and Table 7 below illustrate jumper settings for a loop compensation network for

very low output voltage ripple.

Table 6. Jumper S4, S5

Position Output ripple compensation

Short

Virtual ESR output ripple is generated by using a compensation network connected

between the output and PHASE pin of the switching section.

Table 7. Jumper S8, S9

Position Feedback connection

Controller feedback signal connected to the compensation network

Table 8 and Table 9 describe the settings for a loop compensation network for high output

voltage ripple.

Table 8. Jumper S4, S5

Position Output ripple compensation

Open ESR output ripple is used.

Table 9. Jumper S8, S9

Position Feedback connection

Controller feedback signal connected directly to the output capacitor.

16/29

Page 17

AN2566 Test setup and performance summary

10 Test setup and performance summary

10.1 Test setup

The PM6680 ev aluation board has the following input/output connections:

– 12 V input through J5-J2 (V

– 1.5 V SMPS output through J4-J13 (OUT1+ and OUT1-)

– 1.05 V SMPS output through J1-J12 (OUT2+ and OUT2-)

– 5 V linear regulator output through J3 (LDO5)

+ and VIN-)

IN

A power supply capable of supplying at least 6 A should be connected to V

active loads should be connected respectively to OUT1+, OUT1- and OUT2+, OUT2-.

10.2 Power-up

As shown in Figure 7, the power-up starts when the input voltage is applied and the voltage

on the SHDN pin is above the de vice “on” threshold. First, the LDO5 goes up wit h a masking

time of about 4 ms.

Figure 7. REF and LDO5 power -up

SHDN

LDO5

VREF

+, VIN- and two

IN

10.3 Soft-start and shutdown waveforms

Figure 8 and 9 show the soft-start waveforms.

Figure 10 and 11 show the shut down waveforms.

The PM6680 has an independent internal digital soft-start for each s witching section. During

the soft-start phase the internal current limit increases from 25% to 100%, in increments of

25%, to avoid the inductor current reaching too high a value.

17/29

Page 18

Test setup and performance summary AN2566

Figure 8. Section 1 soft-start waveforms

OUT1

I_L

EN1

Figure 9. Section 2 soft-start waveforms

OUT2

I_L

EN2

Driving the SHDN pin below the SHDN device “off” threshold will cause the device to enter

shutdown mode. In this case the switching outputs are connected to ground through an

internal 12

Ω power MOSFET and are discharged softly, (discharge mode). When the output

voltages reach 0.3 V, the low side MOSFETs are t urned on, quickly discharging them to

ground.

18/29

Page 19

AN2566 Test setup and performance summary

Figure 10. Section 1 shutdown waveforms

OUT1

Lgate1

EN1

Figure 11. Section 2 shutdown waveforms

OUT2

Lgate2

EN2EN2

10.4 1.5 V and 1.05 V output efficiency vs. load current

Figure 12 and Figure 13 show the efficiency versus load current for different input voltage

values in PWM mode, skip mo de and no-audible skip mode.

19/29

Page 20

Test setup and performance summary AN2566

%

%

Figure 12. 1.5 V SMPS efficiency

1. 5 V OUTPUT EFFI CIENCY

100

90

80

70

60

50

40

EFFICIENCY [

30

20

10

0

0.01 0.1 1 10

vs LOAD CURRENT

A: SKIP, VIN=10.8V

B: SKIP, VIN=14.4V

C: PWM, VIN=10.8V

D: PWM, VIN=14.4V

E: NO AUD., VIN=10.8V

LOAD CURRENT [A]

Figure 13. 1.05 V SMPS efficiency

1.05 V OUTPUT EFFICI ENCY

100

90

80

70

60

50

40

EFFICIE NCY [

30

20

10

0

0.01 0.1 1 10

vs LOAD CURRENT

A: SKIP, VIN=10.8V

B: SKIP, VIN=14.4V

C: PWM, VIN=10.8V

D: PWM, VIN=14.4V

E: NO AUD., VIN=10.8V

LOAD CURRENT [A]

10.5 Power consumption analysis

To measure the device consumption under real working conditions, an external power

supply of +5 V is connected to EXT5V.

The two traces on figures that f ollo w show the dif f erentiation bet ween the tw o input currents .

Once the internal linear regulator is turned on, device consumption will increase as a

consequence.

Figure 14 shows the input current consumption measured at V

input device current consumption measured at the VCC pin. Both switching sections are

working in forced PWM mode. No load is applied on the outputs.

20/29

+ (includes ISHDN) and the

IN

Page 21

AN2566 Test setup and performance summary

Figure 14. Input current vs. input voltage

Figure 15 shows the input current consumption measured at V

+ (includes ISHDN) and the

IN

input device current consumption measured at the VCC pin(IEXT5V). Both switching

sections are working in SKIP mode. No load is applied.

Figure 15. Input current vs. input voltage

21/29

Page 22

Test setup and performance summary AN2566

Figure 16 shows the input current consumption measured at VIN+ (includes ISHDN) and the

input device current consumption measured at the VCC pin(IEXT5V). Both switching

sections are working in NO-AUDIBLE SKIP mode. No load is applied.

Figure 16. Input current vs. input voltage

In the following il lustr ations , the device current consumption is measured in shutdown mode

and standby mode. In shutdown mode all outputs are off (SHDN pin low). In standby mode

only the linear regulator output is on (V5SW = SGND, SHDN pin high, EN5 and EN3 pins

low).

Figure 17. Device current consumption vs. input voltage

SHUTDO WN M ODE INPU T BAT TE RY CU RRENT

25.00

20.00

15.00

10.00

5.00

INPUT CURRENT [uA]

0.00

8 10121416182022242628

vs INPUT VOLT AGE

INPUT VOLTA GE [V]

22/29

Page 23

AN2566 Test setup and performance summary

Figure 18. Device current consumption vs. input voltage

STANDBY MO DE INPUT BATTERY CURRENT

184

182

180

178

176

174

INPUT CURRENT [uA]

172

8 10121416182022242628

vs INPUT VOLTAGE

INPUT VOLTAGE [V]

10.6 Switching frequency vs. load current

Figure 19 and Figure 20 show the switching frequency variation with the load current in

PWM mode, skip mode and no-audible skip mode. 12 V is applied at the V

points.

+ and VIN- test

IN

Figure 19. 1.5 V output switching frequency vs. load current

1. 5V SW ITCHING FREQ UENCY

250

PWM

200

150

100

50

FREQUENCY [kHz]

NO AUD. SKIP

SKIP

0

0.01 0.1 1 10

vs LOAD CURRENT

LOAD CURRENT [A ]

23/29

Page 24

Test setup and performance summary AN2566

Figure 20. 1.05 V output switching frequenc y vs. load current

1.05V SWITCHING FREQUENCY

350

300

PWM

250

200

150

100

FREQUENCY [kHz]

50

NO AUD. SKIP

SKIP

0

0.01 0.1 1 10

vs LOAD CURRENT

LOAD CURRENT [A]

10.7 Linear regulator output voltages vs. output current

Figure 21 shows the load regulation for the internal linear regulator LDO5. Both switching

sections are disabled and 12 V is applied at V

+ and VIN- test points.

IN

Figure 21. LDO5 output vs. load current

LDO5 vs . O UTPUT CURRENT

4.9890

4.9880

4.9870

4.9860

4.9850

4.9840

[V]

4.9830

4.9820

4.9810

4.9800

LIN E AR OU P UT VOLTA GE

4.9790

0 102030405060708090100

10.8 Load transient responses

The following figures show the load transient response from 1 A to 4 A for both switching

outputs. In each of these cases the PM6680 w orks in forced PWM mode (the SKIP pin is

high).

LOAD CURRENT [m A]

24/29

Page 25

AN2566 Test setup and performance summary

Figure 22. SMPS 1.5 V load transient response

OUT1

I_L

Vphase

Figure 23. SMPS 1.05 V load transient response

Vphase

OUT2

I_L

25/29

Page 26

Representatives waveforms AN2566

11 Representatives waveforms

The following illustrations show the relevant waveforms of a switching section and are

provided to underline the behavior of the device in pulse skip mode, no-audible skip mode

and forced PWM mode working conditions.

Figure 24. SMPS pulse skip mode

Figure 25. SMPS no-audible skip mode

26/29

Page 27

AN2566 Representatives waveforms

Figure 26. SMPS PWM mode

27/29

Page 28

Revision history AN2566

12 Revision history

Table 10. Document revision history

Date Revision Changes

20-Aug-2007 1 Initial release

– Changed: Figure 1, 2, 3, 14, and 16

05-Mar-2008 2

07-Apr-2008 3 – Modified: Introduction

– Modified: Table 1

– Minor text changes

28/29

Page 29

AN2566

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely res ponsibl e fo r the c hoic e, se lecti on an d use o f the S T prod ucts and s ervi ces d escr ibed he rein , and ST as sumes no

liability whatsoever relati ng to the choice, selection or use o f the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third pa rty p ro duc ts or se rv ices it sh all n ot be deem ed a lice ns e gr ant by ST fo r t he use of su ch thi r d party products

or services, or any intellectua l property c ontained the rein or consi dered as a warr anty coverin g the use in any manner whats oever of suc h

third party products or servi ces or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICUL AR PURPOS E (AND THEIR EQUIVALE NTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJ URY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST fo r the ST pro duct or serv ice describe d herein and shall not cr eate or exten d in any manne r whatsoever , any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document su persedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of compan ie s

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - I taly - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

29/29

Loading...

Loading...