Page 1

高速差動

R

+

+

高速差動 ADC

高速差動高速差動

ADC ドライバの設計についての考察

ドライバの設計についての考察

ADCADC

ドライバの設計についての考察ドライバの設計についての考察

by John Ardizzoni and Jonathan Pearson

はじめに

はじめに

はじめにはじめに

ほとんどの最新の高性能 ADC は差動入力を使用して、同

相ノイズと干渉を除去し、ダイナミック・レンジをファク

タ 2 増大し、平衡した信号送信により全体の性能を改善し

ています。差動入力 ADC はシングル・エンド入力信号も

入力可能ですが、やはり入力信号が差動の時に最適な特性

が得られます。ADCドライバ(このような信号を出力す

るためにしばしば特別に開発された回路。)は振幅スケー

リング、シングル・エンド to差動入力変換、バッファ・

アンプ、同相オフセット調整、フィルタを含む多数の重要

な機能を実行します。 AD8138の紹介以来、差動 ADC

ドライバはデータ・アクウィジション・システムで必要不

可欠な信号処理部品になりました。

F1

R

G1

V

V

+

IP

V

IN, dm

V

–

IN

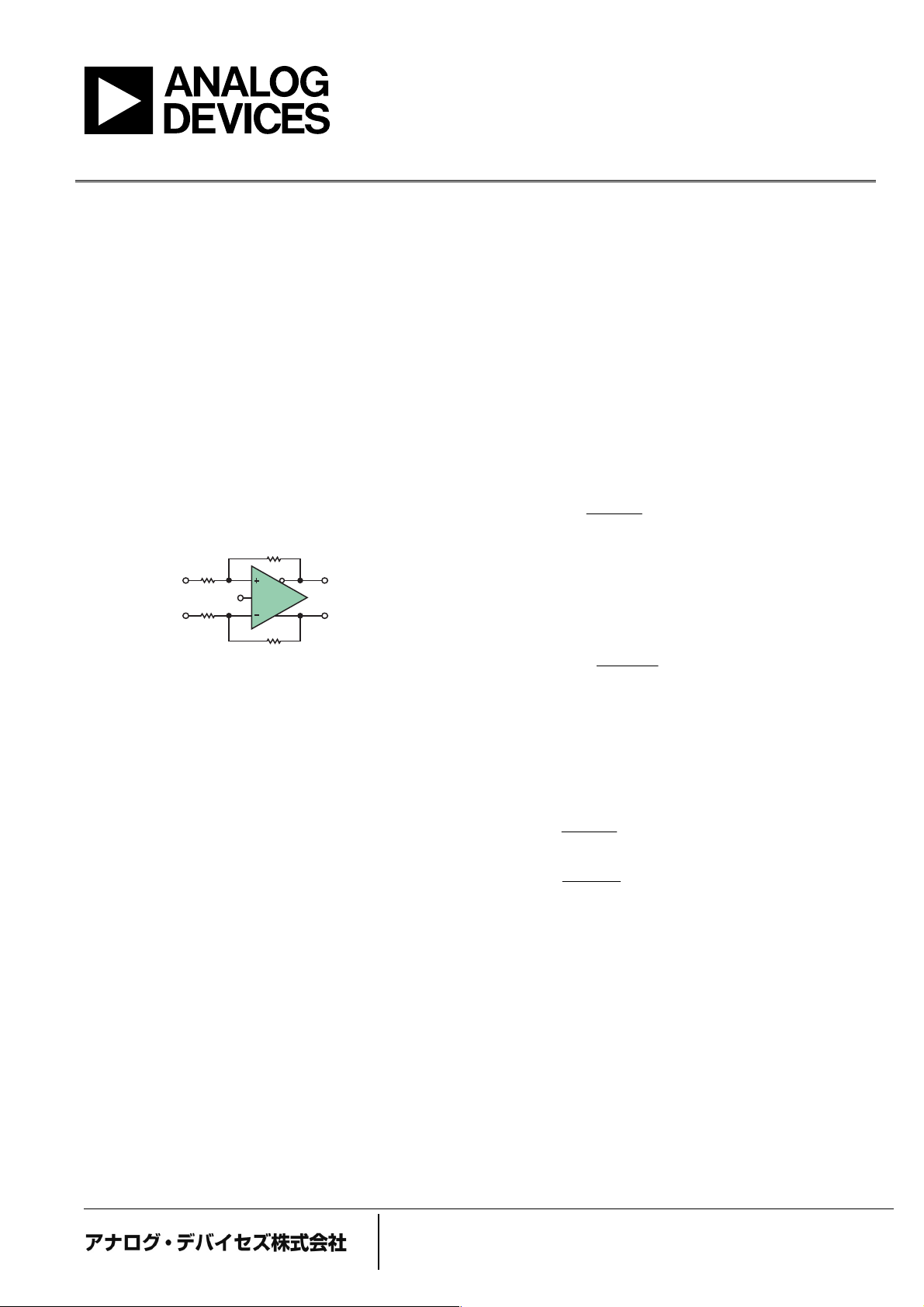

基本的な完璧に差動の電圧フィードバック ADC ドライバ

を図 1 に示します。従来のオペアンプ帰還回路とは 2 つの

点で違いがある事がわかります。差動 ADCドライバには

新たに出力端子(VON) と入力端子(V

これらの端子は差動入力の ADCに信号をインターフェー

スする時非常に便利です。

差動 ADC ドライバはシングル・エンド出力の代わりに、

V

基準に VOP と VON.の間で平衡な差動出力を生じます。

OCM

(P は正を、N は負を表します。)V

電圧をコントロールします。入出力信号が規定範囲内であ

る限り、出力同相電圧は V

しくなります。負帰還と高オープンループ・ゲインにより、

アンプ入力端子電圧の VA+ と VA–は基本的に等しくなり

ます。

A

V

OCM

V

R

A

G2

図 1.差動アンプ

OCM

V

–

ON

V

OUT, dm

V

+

R

F2

OP

08263-001

)が追加されています。

OCM

入力は出力同相

OCM

入力に印加された電圧に等

AN-1026

APPLICATION NOTE

今後の説明のために、いくつかの定義を順に説明します。

入力信号が平衡であれば、VIP と VINは通常 同相基準電圧

を基準にして振幅は同じで位相が反対になります。入力が

シングル・エンドの場合は、一方の入力が固定電圧で他方

がその電圧を基準に変化します。いずれの場合も、入力信

号は VIP – VINとして規定されます。

差動モード入力電圧、V

1 と式 2 で規定されます。

V

= VIP – VIN (1)

IN, dm

VV

V

IN, cm

=

INIP

2

この同相の定義は入力が平衡の時には直感的に理解できま

すが、入力がシングル・エンドでも有効です。

出力も又差動モードと同相モードがあり、式 3 と式 4 で規

定されます。

V

= VOP – VON (3)

OUT, dm

V

OUT, cm

=

VV

2

実際の出力同相モード電圧 V

設定する)V

入力端子との間の差に注意してください。

OCM

差動 ADC ドライバの解析は従来のオペアンプの解析より

もかなり複雑です。代数を簡略化するために式 5、式 6 で

与えられたように 2 つの帰還係数 β1 、β

利です。

R

β

1

β

G1

=

F1

=

2

F

(5)

RR

+

G1

R

2

G

(6)

RR

+

2

2

G

と同相入力電圧、V

IN, dm

(2)

ONOP

(4)

,と(出力同相レベルを

OUT, cm

を定義すると便

2

IN, cm

, は式

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって

生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示

的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属

します。※日本語資料は REVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2010 Analog Devices, Inc. All rights reserved.

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー

電話 03(5402)8200

電話 06(6350)6868

Page 2

AN-1026 APPLICATION NOTE

目次

目次

目次目次

はじめに

改定履歴 .......................................................................... 2

改訂履歴

改訂履歴

改訂履歴改訂履歴

11/09—Revision 0:初版

........................................................................... 1

ADC ドライバに対する入力の終端 .............................. 3

入力同相電圧範囲(ICMVR)

入力結合および出力結合:AC又は DC ....................... 6

出力振幅 ....................................................................... 7

.............................................. 5

ノイズ ...........................................................................7

電源電圧 ........................................................................9

高調波歪み ..................................................................10

帯域とスルーレート .................................................... 11

安定性 ......................................................................... 11

PC 基板レイアウト .....................................................12

Rev. 0 | Page 2 of 16

Page 3

APPLICATION NOTE

R

200Ω

R

ほとんどの ADCドライバでは β1 = β

タのミスマッチが性能にどのように影響するかついて理解

するのに、VIP, VIN, V

, β1, β2の項をもつ V

OCM

的な閉ループ公式は役に立ちます。図 7 に示す V

式にはアンプの有限で周波数に依存するオープンループ電

圧ゲイン、A(s)が含まれています。

V

β

OUT,dm

1

≠ β2の時、差動出力電圧は V

=

2

+

ββ

21

( ) ( ) ( )

OCM

21

+

1

OCM

差動出力にオフセットと余分なノイズを生じるので、望ま

しくない結果になります。 電圧帰還回路のゲイン帯域幅

積(GB 積)は一定です。興味ある事に、ゲイン帯域幅積

(GB 積)のゲインは 2 つの帰還率の平均の逆数です。

β

= β2 ≡ ≡β の時、式 7 は式 8 のように短縮されます。

1

V

,

dmOUT

V

=

,

dmIN

R

F

R

G

1

1

+

1

( )

β

)(

sA

これはよく知られている式です;理想的な閉ループゲイン

は、A(s) → ∞の時単純な RF/RGになります。 ゲイン帯

域幅積(GB 積)も又、ノイズゲインが 1/β になるので、

ちょうど従来のオペアンプの場合のようによく知られた形

になります。

帰還率がマッチングしている差動 ADC ドライバの理想的

な閉ループゲインは式 9 になります。

A ==

V

V

V

R

dmOUT

,

F

(9)

R

G

dmIN

,

差動 ADC ドライバの重要な性能基準である出力平衡には、

振幅平衡と位相平衡の 2 つの要素があります。 振幅平衡

は 2 つの出力の振幅がどのくらい一致しているかを表す尺

度です;理想的なアンプではそれらは正確に一致していま

す。出力位相平衡は 2 つの出力間の位相差がどのくらい

180°に近いかを表す尺度です。出力振幅又は出力位相のど

のような不平衡も出力に好ましくない同相成分を生じます。

出力平衡誤差(式 10)は差動入力信号によって生成される

出力同相電圧の、(同じ入力信号によって生成される)出

力差動モード電圧に対する対数比で、デシベルで表されま

す。

=

ErrorBalanceOutput

内部の同相帰還ループにより V

log20

OUT, cm

される電圧に等しくなり、優れた出力平衡を生みます。

です。しかしベー

2

の一般

OUT, dm

の

OUT, dm

−−−+−

βVβVββV

11

IP

( )

( )

1

2

+

ββsA

21

2

IN

に依存します。これは

(8)

∆

V

10

∆

V

が V

cmOUT

,

dmOUT

,

入力に印加

OCM

(10)

(7)

AN-1026

ADC

ADC ドライバ

ドライバに対する

ADCADC

ドライバドライバ

ADC ドライバは高速信号を処理するシステムで頻繁に使

用されます。信号波長の小片以上に分離されたデバイスは

信号のもとの波形を損なわないようにインピーダンス整合

された電気伝送ラインで接続されなければなりません。伝

送ラインの両端を特性インピーダンスで終端した時、最適

の性能が得られます。ドライバは一般的に ADC の近くに

配置されるのでそれらの間にインピーダンス整合した接続

の必要はありませんが、しばしば ADC ドライバ入力まで

の信号経路が長いことがあるので、その場合適切な抵抗で

終端してインピーダンス整合した接続をする必要がありま

す。

終端抵抗 R

抗値にできるように、(差動であろうとシングル・エンド

であろうと)ADCドライバの入力抵抗は、所望の終端抵

抗より大きいか等しくなければなりません。ここで検討す

る例に出てくるすべての ADC ドライバは

たようにバランスのとれたフィードバック比を持つように

設計されています。

アンプの 2 つの入力間電圧は負帰還によりゼロになるよう

に動作するので、これらは仮想的に接続され、差動入力抵

抗 RIN,は単純な 2 × RGになります。伝送ライン抵抗 R

整合させるために、差動入力の間に式 11で計算した値の

RTを接続します。図 3.図 3 に標準的な抵抗 RF = RG = 200

Ω, 要求される抵抗 R

ます。

R

=

T

に対する入力の終端

に対するに対する

をアンプ入力と並列に追加して要求される抵

T

入力の終端

入力の終端入力の終端

図 2.

F

R

G

R

IN, dm

図 2.差動アンプ入力インピーダンス

1

−

= 100Ω V

L, dm

V

OCM

R

G

L, dm

11

RR

INL

R

T

R

T

図 3.100Ω ラインに整合

R

= 100 Ω, と RT = 133 Ω.を示し

200Ω

OCM

200Ω

1

=

1

−

100Ω

F

200Ω

1

400Ω

= 133Ω

図 2 に示し

L

に

(11)

Rev. 0 | Page 3 of 16

Page 4

AN-1026 APPLICATION NOTE

–2V

3.5V

200Ω

2V p-p

R

1.1V p-p

R

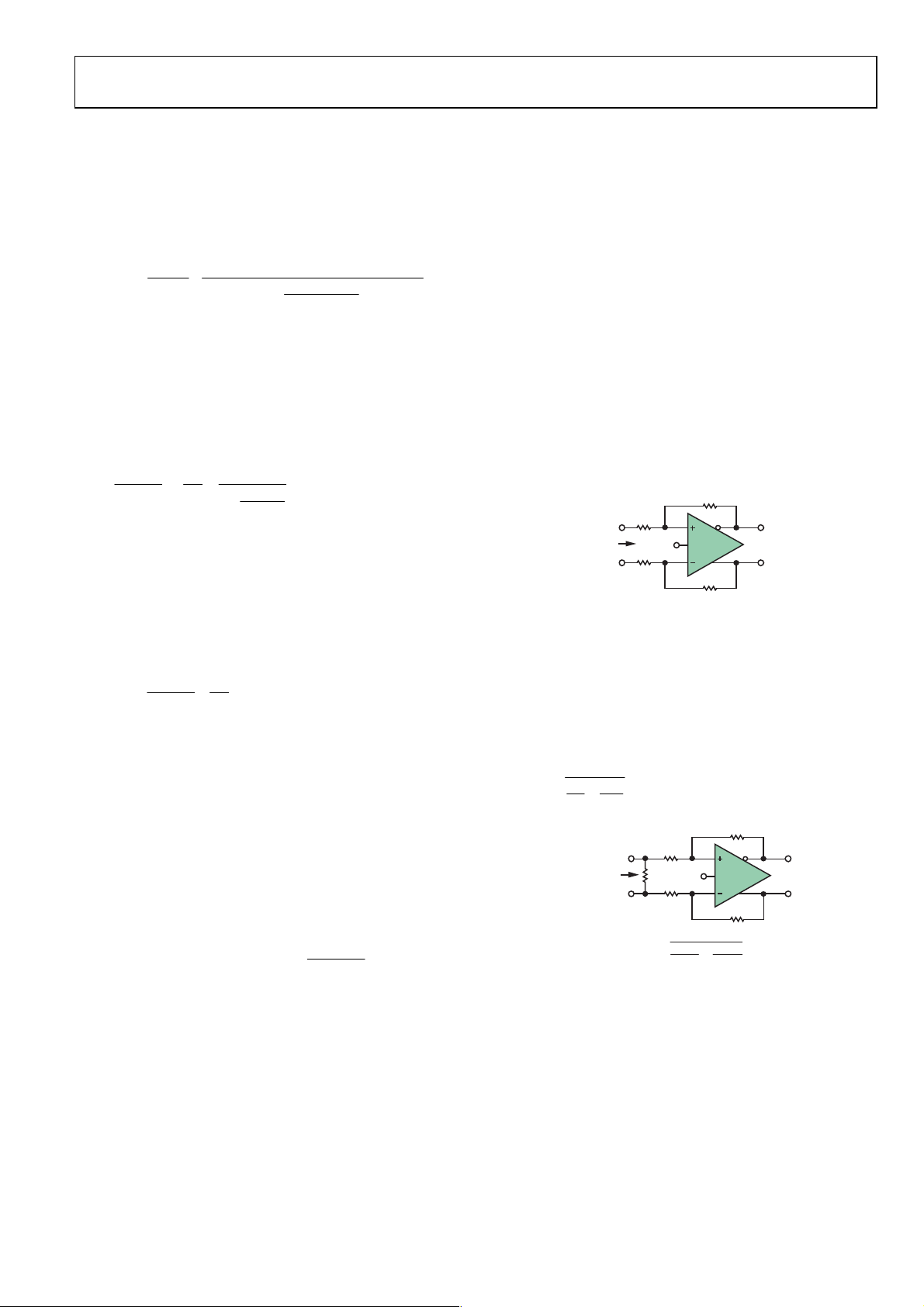

シングル・エンド入力を終端する事はより多くの努力を必

要とします。図 4 はシングル・エンド入力、差動出力回路

の ADC ドライバがどのように動作するかを示しています。

2.5V

1.5V

R

F

V

500Ω

OCM

R

500Ω

V

ON

–

V

OUT, dm

+

V

OP

F

3.5V

2.5V

1.5V

2V

V

0V

IN

1.75V

1.25V

0.75V

R

500Ω

2.5V

R

500Ω

G

G

図 4.ADC ドライバへのシングル・エンド入力の例

入力はシングル・エンドですが、V

ります。抵抗 RF と R

は等しくバランスがとれているの

G

IN, dm

は V

に等しくな

IN

で、ゲインは1で、差動出力、VOP − VON,は入力電圧、す

なわち、4Vp-p に等しくなります。V

V に等しく、又入力電圧 VA+ と V

は、下側の帰還回路の

A−

OUT, cm

は V

OCM

= 2.5

フィードバックにより、 VOP/2に等しくなります。

式 3 と 式 4を使うと、VOP = V

に±1 V同相スウィングします。又 VON = V

+ VIN/2となり 2.5 V基準

OCM

– VIN/2とな

OCM

り 2.5 V.基準に±1 V逆相スウィングします。 従って VA+

と VA− は 1.25 V基準に±0.5 Vスウィングします。 VIN か

ら供給しなければならない電流の AC成分は(2 V – 0.5

V)/500 Ω = 3 mAです。従って VIN から見て整合をとらなけ

ればならないグラウンドに対する抵抗は、667 Ω です。

各々のループの帰還率がマッチングしている時、このシン

グル・エンド入力抵抗を計算する一般的な公式は式 12 で

表せます。ここで RIN, seはシングル・エンド入力抵抗です。

=

R

seIN

,

1

−

2

R

G

R

( )

F

+×

RR

F

G

(12)

これは終端抵抗を計算するスタート点です。ここで、アン

プ・ゲインの式は入力源インピーダンスをゼロと仮定して

いる事に注意する事が重要です。本質的にシングル・エン

ド入力のために生ずる不平衡の状態で、信号源インピーダ

ンスを整合させなければならないので、上側の R

を追加します。 平衡を保つために、これを下側の R

に抵抗

G

G

に抵

抗を追加してマッチングさせなければなりませんが、それ

はゲインに影響します。

シングル・エンド信号を終端する事の問題に対して閉形式

解を決めることは可能かもしれませんが、再計算法が一般

的に使用されます。その必要性は次の例で明らかです。

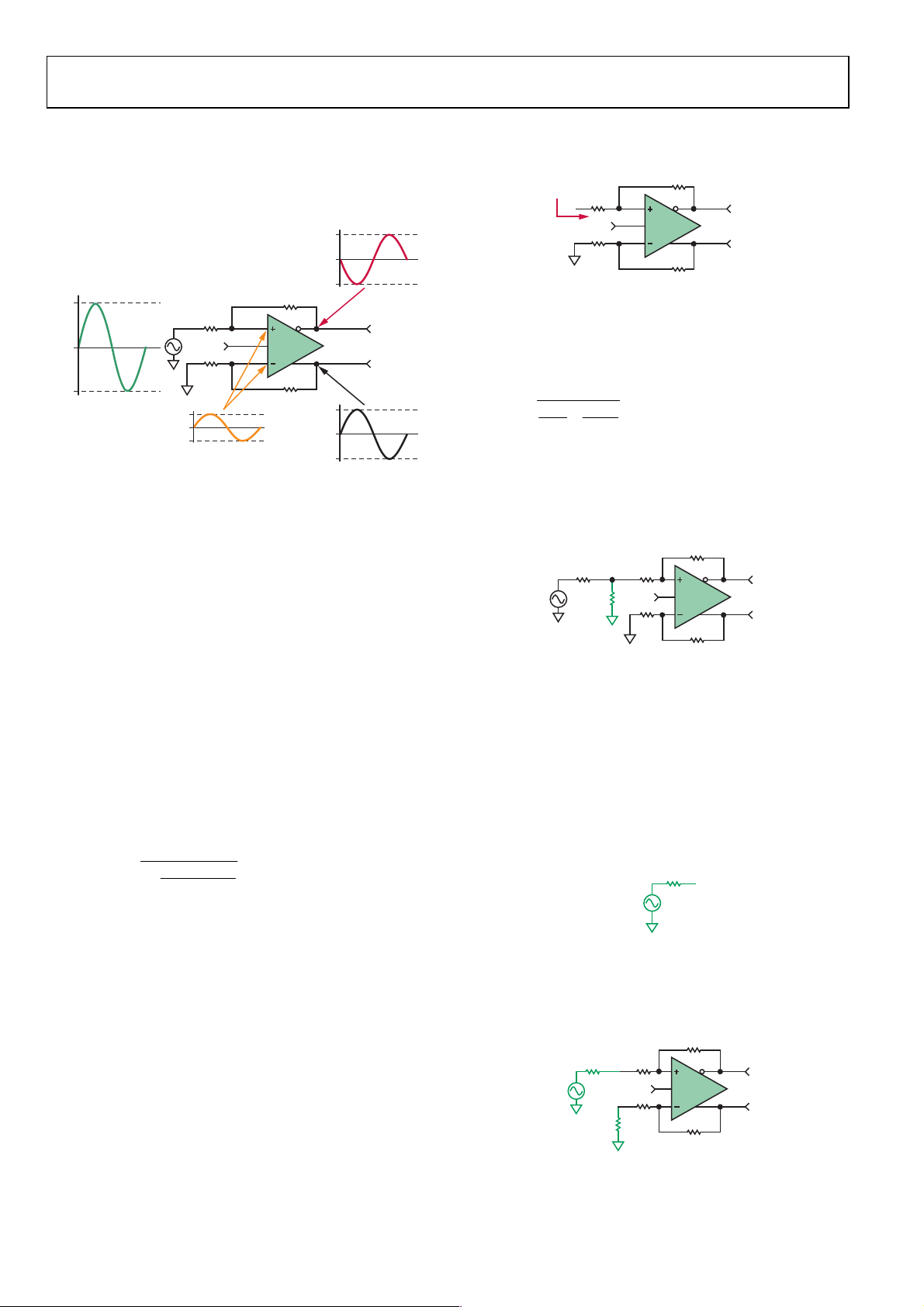

図 5 は、シングル・エンド to 差動のゲインが 1, 入力終端

抵抗が 50Ω、そしてノイズを低く保つために、フィード

バック抵抗とゲイン抵抗を約 200Ω 付近の値にしています。

267Ω

200Ω

2.5V

200Ω

図 5.シングル・エンド入力インピーダンス

200Ω

V

OCM

200Ω

–

V

OUT, dm

+

V

ON

V

OP

式 12 からシングル・エンド入力抵抗は 267 Ω になります。

式 13 から入力抵抗 267 Ω を 50 Ω に落とすためには、並

列抵抗、R

61.5Ω にしなければならないことがわかり

Tを

ます。

=TR

図 6 は信号源抵抗と終端抵抗を示した回路です。 信号源

08263-004

1

1

−

Ω50

61.5

=

1

(13)

Ω267

の解放回路電圧は 2 V p-p で、信号源抵抗は 50 Ω です。

信号源が 50 Ω に終端されると、入力電圧は 1 V p-p に減

少します。これは又ユニティゲイン・ドライバの差動出力

電圧になります。

200Ω50Ω

R

61.5Ω

T

2.5V

200Ω

V

OCM

200Ω

図 6.信号源と終端抵抗を加えたシングル・エンド回路

–

V

OUT, dm

+

V

V

この回路は一見完全に見えますが、50 Ω と並行にミスマ

ッチした抵抗 61.5 Ω が上側の R

のみに追加されていま

G

す。これはゲインとシングル・エンド入力抵抗を変え、帰

還率をミスマッチさせます。ゲインが小さいので、入力抵

抗の変化は小さくしばらく無視されます、しかし帰還率は

マッチングしていなければなりません。これを可能するも

っとも簡単な方法は下側の R

に抵抗を加えることです。

G

図 7 はテブナン等価回路を示しますが、ここで前述した並

列組み合わせ回路が信号源抵抗として働きます。

V

TH

27.6Ω

TH

08263-007

図 7.入力信号源のテブナン等価回路

図 8 に示すように、ループ帰還率をマッチングさせるため

に、この置き換え回路に合わせて下側ループに 27.6 Ω 抵

抗, R

を追加します。

TS

V

1.1V p-p

TH

R

TH

27.6Ω

27.6Ω

F

200Ω

R

G

200Ω

V

2.5V

R

TS

200Ω

OCM

R

G

R

F

200Ω

–

V

OUT, dm

+

V

V

図 8.平衡シングル・エンド終端回路

ON

OP

ON

OP

08263-008

Rev. 0 | Page 4 of 16

Page 5

APPLICATION NOTE

R

2V p-p

+

(

)

+

(

)

−+−

+

(

)

−+=

1.1 V p-p のテブナン電圧は適切に終端された電圧 1 V p-p

よりも大きくなり、ゲイン抵抗はそれぞれ 27.6 Ω 増える

ので、閉ループゲインが減少する事に注意してください。

これら出力電圧に対して相反する影響は抵抗が大きく (>1

kΩ) 、ゲインが小さい(1 又は 2)場合は,互いに相殺する傾

向にありますが、抵抗が小さくゲインが高い場合には完全

には相殺されません。

図 8 の回路は簡単に解析する事ができ、差動出力電圧は式

14 で計算する事ができます。

V

=

dmOUT,

p-pV 1.1 =

差動出力電圧は所望の電圧 1 V p-pより多少小さくなりま

すが、式 15 に示したようにフィードバック抵抗を変更す

ることにより最終的な独立したゲイン調整が可能です。

Ω227.6

=

R

F

Ω27.62

p-pV 0.1

p-pV 1.1

図 9 に完成した回路を示します。ここで使用する抵抗の値

は標準 1%です。

R

R

S

50Ω

R

T

61.9Ω

R

TS

28Ω

図 1.完全シングル・エンド終端回路

図 9 の回路に関して、ドライバのシングル・エンド入力抵

抗 RIN, seは RFと R

の変更により変わります。ドライバ

G

の上側ループのゲイン抵抗は 200 Ω で、下側ループのゲ

イン抵抗は 200 Ω + 28 Ω = 228 Ω です。ゲイン抵抗が違

う場合は、R

の計算を行う前に式 16 と式 17 に示すよ

IN, se

うに 2 つベータ値を計算する必要があります。

R

G

=

β

1

β

2

入力抵抗 R

R

+

RR

GF

RR

=

IN, se

=

,

seIN

TSG

++

RRR

TSGF

は式 18 に示すように計算します。

ββR

( )

1

+

ββ

21

21

G

この値は始めに計算した値 267 Ω とほとんど変わらず、

RTの計算に大きな影響はありません。なぜなら R

RTとは並列だからです。

もしもっと正確な全体のゲインが必要であれば、より高精

度な抵抗又は直列トリム抵抗を使用する事ができます。

IN, se

=

Ω200

Ω227.6

,

dmOUT

=

p-pV 1.1

Ω206.9

F

205Ω

G

V

OCM

G

R

F

205Ω

(16)

494.0

==

Ω228

527.0

==

Ω433

Ω271

(18)

=

200Ω

2.5V

200Ω

Ω200

Ω405

VDesired

R

R

p-p V 0.97

(15)

V

ON

–

V

OUT, dm

+

V

OP

(17)

は

IN, se

(14)

AN-1026

ここで述べた1度の再計算方法は閉ループゲインが 1 又は

2 の時はよく当てはまります。ゲインがさらに高い場合、

RTSの値は RGの値に近くなり、式 18 で計算した R

値と式 12で計算した値の差は大きくなります。このよう

な場合には何回かの再計算が必要です。

これは困難ではありません:最近リリースされた差動アン

プ計算ツール、ADIsimDiffAmp™ と ADI Diff Amp

Calculator™はすべての厄介な仕事を行います;それらは

前述の計算を数秒で行います。詳細については、

www.analog.comを参照してください。

入力同相電圧範囲

入力同相電圧範囲(ICMVR)

入力同相電圧範囲入力同相電圧範囲

ICMVR は通常動作で差動アンプ入力に加える事のできる

電圧範囲を規定します。差動アンプ入力に現れる電圧は

ICMV, V

, 又は V

acm

と呼ばれています。この仕様はしばし

A±

ば誤解されます。差動アンプ入力での実際の電圧を(得に

入力電圧基準に)決めるのはかなり困難です。アンプ入力

電圧(VA±)は変数 V

IN, cm

、 β、 V

が既知の時、βsが異な

OCM

る場合は一般的な式 19 を使い、βsが同じ場合は簡略化し

た式 20 を使って計算することができます。

V

V

ββ

VorV

acm

A

±

acm

A

V

は常に入力信号のスケールを小さくしたバージョンで

A

21

=

VVorV

cmIN

,

±

OCM

IP

β

ββ

ββ

+

21

VV

(20)

ICMOCM

ある(図 4 に示すように)事に注意してください。入力同

相電圧範囲はアンプのタイプによって異なります。アナロ

グ・デバイセズ(株)の高速差動 ADC ドライバには

ICMVR が電源の中点を中心に設定されているもの

(centered)と ICMVR の中点が電源の中点からシフトされ

たもの(shifted)の 2 種類の入力段構成があります。ICMVR

が電源の中点を中心に設定されている ADC ドライバは

各々の電源レールから約1V のヘッドルームがあります。

(それ故”centered”と呼ばれます)ICMVR の中点がシフト

された入力段には2つのトランジスタが追加されており、

入力が–V

レールにより近くスウィングできるようになっ

S

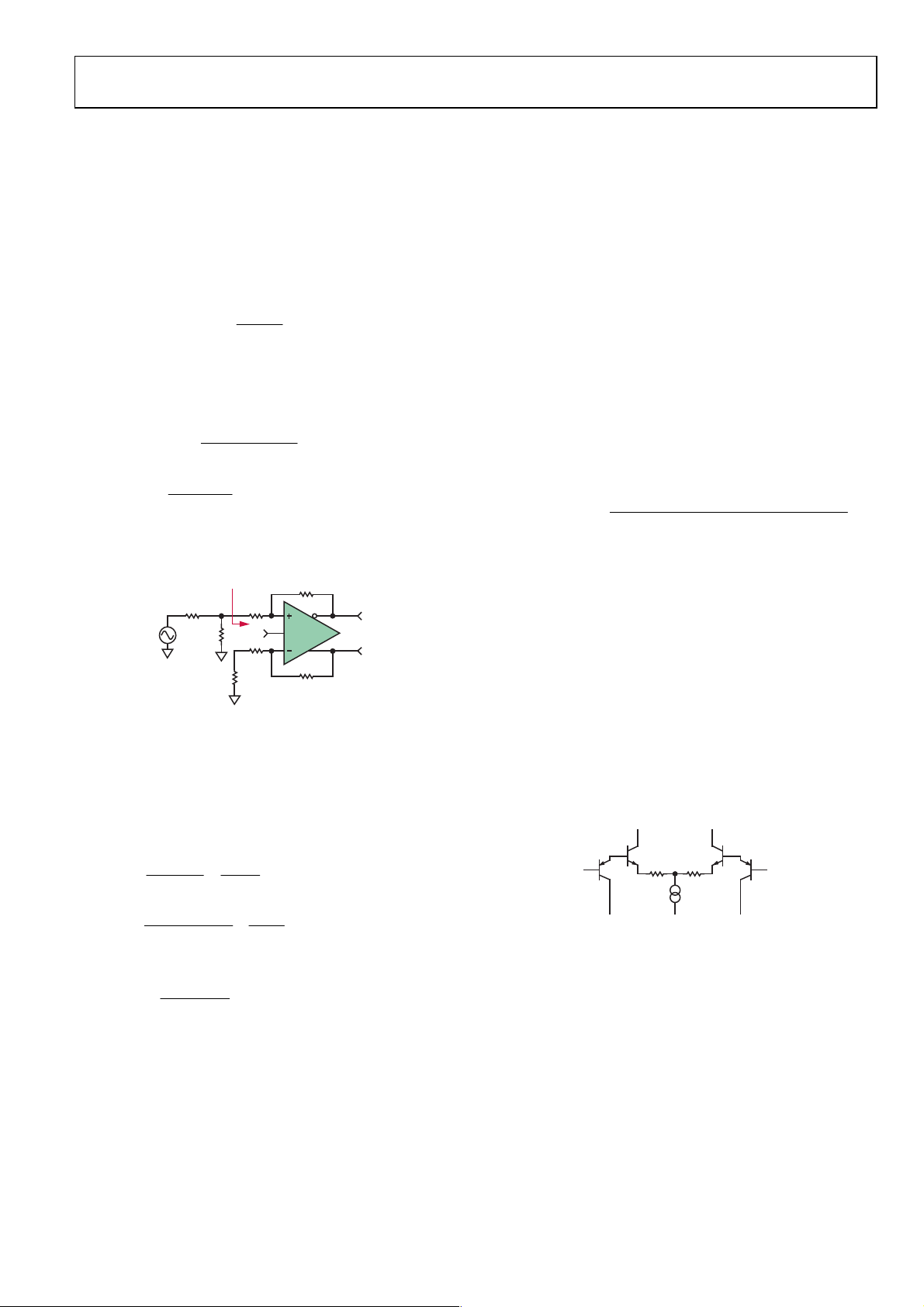

ています。図 10 は代表的な差動アンプの簡略化した入力

回路を示します。 (Q2 と Q3)。

A

–IN +IN

Q2 Q3

Q1 Q4

図 10.シフトされた ICMVRの簡略化した差動アンプ

ICMVR をシフトした入力回路構成の差動アンプは、例え

単電源駆動でもバイポーラ入力信号の処理が可能で、入力

がグラウンド又はそれ以下になる単電源アプリケーション

に十分対応できます。 入力に追加した PNP トランジス

タ(Q1 と Q4)により、差動ペアへ入力する入力電圧が1ト

ランジスタ Vbe分上にシフトします。 例えば –IN に–0.3 V

を印加した時、A点は 0.7 V になり差動ペアが正常に動作

します。PNP(入力段)が無い場合は、A点が–0.3 V とな

り NPN 差動ペアが逆バイアスとなり通常動作が停止しま

す。

IN, se

ββ

21IN12

の

)1(1V2

(19)

Rev. 0 | Page 5 of 16

Page 6

AN-1026 APPLICATION NOTE

R

R

表

表 1.高速

高速 ADC ドライバの仕様

表表

高速高速

製品

製品型番

型番

製品製品

型番型番

AD8132 350 1200 8 –4.7 to +3 0.3 to 3 0.3 to 1.3 0.3 to 1 ±3.6 1 to 3.7 ― 0.3 to 1 ±1 12

AD8137 76 450 8.25 –4 to +4 1 to 4 1 to 2.3 1 to 2 ±4 1 to 4 1 to 2.3 1 to 2 Rail to

AD8138 320 1150 5 –4.7 to

AD8139 410 800 2.25 –4 to +4 1 to 4 ― ― ±3.8 1 to 3.8 ― ― Rail to

ADA4927-1/

ADA4927-2

ADA4932-1/

ADA4932-2

ADA4937-1/

ADA4937-2

ADA4938-1/

ADA4938-2

ADA4939-1/

ADA4939-2

ドライバの仕様

ドライバの仕様ドライバの仕様

ADC Driver ICMVR V

BW

(MHz)

2300 5000 1.4 –3.5 to

1000 2800 3.6 –4.8 to

1900 6000 2.2 ― 0.3 to 3 0.3 to 1.2 ― ― 1.2 to 3.8 1.2 to 2.1 ― ±0.9 40

1000 4700 2.6 –4.7 to

1400 6800 2.3

Slew

Rate

(V/µs)

Noise

(nV) ±5 V +5 V +3.3 V +3 V ±5 V +5 V +3.3 V +3 V

0.3 to 3.2 ― ― ±3.8 1 to 3.8 ― ― ±1.4 20

+3.4

1.3 to 3.7 ― ― ±3.5 1.5 to 3.5 ― ― ±1.2 20

+3.5

0.2 to 3.2 ― ― ±3.8 1.2 to 3.2 ― ― ±1 9

+3.2

0.3 to 3.4 ― ― ±3.7 1.3 to 3.7 ― ― ±1.2 37

+3.4

― 1.1 to 3.9 0.9 to 2.4 ― ― 1.3 to 3.5 1.3 to 1.9 ― ±0.8 37

電源電圧

電源電圧(V)

電源電圧電源電圧

OCM

Output

Swing

from

Rails

(V)

rail

rail

I

SUPPLY

(mA)

3.2

25

表 1 はアナログ・デバイセズ社 ADC ドライバの多くの仕

様の早見表で、どのドライバが ICMVR をシフトしたもの

か、どのドライバがそうでないかの特徴も含まれています。

入力結合および出力結合:

入力結合および出力結合:AC

入力結合および出力結合:入力結合および出力結合:

AC 又は

又は DC

ACAC

又は又は

DC

DCDC

AC 結合又は DC結合する必要が有る場合には、差動 ADC

ドライバの選び方が大きく違ってくる可能性があります。

入力結合と出力結合では検討方法が異なります。

AC 結合入力段を図 11に示します。

C

IN

R

G

V

OCM

R

G

C

IN

図 11.AC 結合 ADCドライバ

F

R

F

AC 結合の差動 to 差動アプリケーションの場合、DC帰還

電流が入力コンデンサによって阻止されるので、アンプ入

力端子に現れる DC 同相電圧は DC 出力同相電圧に等しく

なります。又、DC の帰還率はマッチングしており正確に

1に等しくなります。V

すなわち DC入力同相電圧はほ

OCM

とんどの場合 電源電圧の中点近くに設定されます。電源の

中点を中心とする入力同相範囲の ADC ドライバは、入力

同相電圧がその規定された範囲の中心近くになり、これら

のタイプのアプリケーションで良好に動作します。

AC 結合したシングル・エンド to 差動回路はそれに相当す

る差動入力の回路に似ていますが、アンプ入力端子に、同

相リップル、入力信号の大きさが小さくなった信号が観測

されます。 電源の中点を中心とする入力同相範囲

(centered)の ADC ドライバは、平均入力同相電圧が規

定された範囲の中間近くとなり、ほとんどのアプリケーシ

ョンでリップルに必要な十分なマージンがとれます。

入力結合が選択できる場合、AC 結合入力の ADC ドライ

バの方が DC 同相電流がどちらの帰還ループにも流れない

ので、DC 結合入力の類似したドライバよりも消費電力が

小さくなることに注目する価値があります。

駆動ドライバの出力可能範囲を大幅に超えるような入力同

相電圧を ADC に印加しなければならない時、ADCドライ

バ出力を AC 結合する事は有効です。V

が電源中点近

OCM

くに設定された時、ドライバは最大の出力振幅になりま

す; しかしこの場合低電圧 ADC を非常に低い入力同相

電圧の条件下で駆動する時、問題が現れます。この問題の

簡単な解決方法はドライバ出力と ADC 入力間の接続を

AC 結合して(図 12)、ドライバ出力から ADC の DC 同相

電圧を取り除き、AC 結合の ADC側に ADC に合った同相

レベルを供給できるようにする事です。 例えば、ドライ

バが電源 5V、V

= 2.5 V で動作している場合もありま

OCM

すし、ADC が電源 1.8 V で、要求される入力同相電圧

0.9V を ADC CMV に印加して動作している場合もあり

ます。

F

C

R

G

V

OCM

R

G

R

図 12.DC 結合入力、AC 結合出力接続

OUT

R

OUT

ADC

CMVTOADC

R

OUT

OUT

08263-012

C

F

Rev. 0 | Page 6 of 16

Page 7

APPLICATION NOTE

–20

HARMONIC DISTORTION (dBc)

入力同相範囲がシフトしているドライバは、一般的に単電

源駆動の DC 結合システムで最適に動作します。なぜなら

出力同相電圧が帰還ループを通して分圧降下され、その変

動成分がグラウンドつまり負レールに近づく可能性がある

からです。シングル・エンド入力の場合、入力同相電圧は

入力に関連したリップルによりさらに負のレール近くにな

ります。両電源動作のシステムの場合は、シングル・エン

ド又は差動入力、AC 結合又は DC 結合のいずれの場合で

も、ヘッドルームが増えるので一般的にはどちらのタイプ

の入力段でも良好に動作します。

表 1

表 2 に入力結合、電源電圧の各種組み合わせに使わ

れるもっとも一般的な ADC ドライバ入力段タイプをまと

めてあります。しかし、これらの選択は必ずしも最適では

ないかもしれません。各々のシステムはケース・バイ・ケ

ースで解析する必要があります。

表

表 1.Coupling and Input Stage Options

表表

Input

Coupling

任意 任意 デュアル

AC

DC

AC

DC

出力振幅

出力振幅

出力振幅出力振幅

入力信号

入力信号 電源

入力信号入力信号

Singleended

Singleended

差動 シングル

差動 シングル

電源

電源電源

シングル

シングル

ADC のダイナミック・レンジを最大にするには、ADC を

その全入力範囲に渡って駆動する必要があります。しかし

ADC を駆動するには注意が必要です。ADCをあまり大き

く駆動すると、入力が破損する可能性があります; 一方駆

動電圧が小さいと分解能が悪くなります。ADC をその全

入力範囲駆動する事は、アンプの出力がその全範囲振れな

ければならない事を意味しません。差動出力の主な利点は

各出力の振れ幅が、従来のシングル・エンド出力の振れ幅

の半分だけでよい事です。ドライバ出力を各電源レールか

ら離れた電圧に保つ事がでるので歪みを低減できます。し

かしシングル・エンド・ドライバの場合は事情が違います。

ドライバの出力電圧が電源レールに近づくと、アンプは直

線性を失ない歪みを招きます。

mV 単位の出力電圧が要求されるようなアプリケーション

に適した ADC ドライバについては表1を参照してくださ

い。この表にある ADC ドライバは標準ヘッドルーム範囲

が(負荷により)数 mV から数百 mV のレール to レール

出力です。

表 1

Input

Type

Either

Centered

Shifted

Centered

Centered

Rev. 0 | Page 7 of 16

AN-1026

V

= 2V p-p

OUT

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

1.4 1.6 2.01.8 2.2 2.4 2.6 2.8 3.0 3.2 3.4

図 13. 5V 電源駆動の ADA4932 の各種周波数における

図 13 は ADA4932 の各種周波数における高調波歪み対

V

を示します。ADA4932の標準的な出力振幅は各々の

OCM

電源レールから 1.2 V 以内と規定されています。出力振幅

は V

と 信号 (1 V)の V

OCM

(3.8 V

, 又は 5V レールの下 1.2 V)を超えると加速度的

PEAK

に大きくなります。低電圧の方を見ると、2.2V(–1 V

では歪みはまだ小さいです。同じタイプの現象が帯域とス

ルーレートについての議論で現れます。

ノイズ

ノイズ

ノイズノイズ

ADC の不完全な部分として量子化ノイズ、電子(又はラ

ンダム)ノイズ、高調波歪みがあります。ノイズはほとん

どのアプリケーションで重要な項目ですが、一般的に広帯

域システムでもっとも重要な性能基準です。

すべての ADC は本質的にビット数(n)に依存する量子化

ノイズがあります;量子化ノイズはビット数を増やすごと

に低減します。理想的なコンバータでも量子化ノイズは存

在するので、量子化ノイズはランダムノイズ、高調波歪み

を比較する時対象となるベンチマークとして使用されます。

ADC ドライバからの出力ノイズは ADC のランダムノイズ、

高調波歪みと同等かより低いはずです。ADC のノイズと

歪みの特性評価を見直してみる事から、ADC の性能に対

する ADC ドライバのノイズの評価方法を示します。

ADC は無限の分解能をもつアナログ信号を有限の数のデ

スクリート・レベルに量子化するので量子化ノイズは生じ

ます。 n ビット ADCには 2n バイナリの数のレベルがあり

ます。1つのレベルと次のレベルとの間の差が分解可能な

最小な差を表します;これは最下位ビット(LSB)、又は

量子レベル q と呼ばれています。それ故1量子レベルはコ

ンバータの範囲の 1/2

完璧な n ビット ADC で変換され、それを逆に変換してア

ナログに戻し ADC の入力信号から減算すれば、その差は

ノイズになるでしょう。それは次の rms 値になります。

HD2 @ 10MHz

HD3 @ 10MHz

HD2 @ 30MHz

HD3 @ 30MHz

V

(V)

OCM

高調波歪み対 V

との合計です。歪みは 2.8 V

PEAK

n

になります。もし変化する電圧が

NoiseonQuantizatiRMS ==

q

12

OCM

1

(21)

n

122

PEAK

)

Page 8

AN-1026 APPLICATION NOTE

=

+

−

V

V

v

2

(

)

−

(

)

−

(

)

−

(

)

(

)

(

)

(

)

この値から、そのナイキスト帯域の n ビット ADC の信号

対量子化ノイズ比の対数式(dB)を導く事ができます(式

22); これは n ビットコンバータの得られる最大の SNR で

す。

信号対 量子化ノイズ比(dB)=6.02n + 1.76 dB (22)

ADC の中のランダムノイズ(熱ノイズ、ショットノイズ、

フリッカノイズの組み合わせ)は一般的に量子化ノイズよ

りも大きくなります。ADC の非直線性の結果生ずる高調

波歪みは(高調波的に入力信号に関係した)望ましくない

信号を出力に生じます。全高調波歪みとノイズ((THD +

N)は電子ノイズと高調波歪みを ADC のフルスケール入力

レンジに近いアナログ入力と比較する重要な ADCの性能

指標です。電子ノイズは対象とする最後の高調波周波数ま

での帯域全体に渡って積分されます。式 23 で全 THD は

始めの5つの高調波歪みを含みます。これはノイズととも

に2乗和の平方根です。

NoiseTHD

[ ]

2

2

[ ]

4

[ ]

v

1

2

[ ] [ ]

2

)rms(

2

3

[ ]

2

5

v1は入力信号、v2 から v6,までは 5 つの高調波歪み積、v

2

2

)rms()rms()rms()rms()rms(

vvvvvv

6

+++++

n

(23)

n

は ADC 電子ノイズです。

THD+ノイズの逆数の信号対ノイズ+歪み比(SINAD)は通

常デシベルで表します(式 24)。

SINAD

log20)dB(

10

(式 22)で信号対量子化ノイズ比を SINAD に置き換えれ

ば、その信号対量子化ノイズ比がその SINAD と同じとす

ればコンバータがもつ事ができる有効ビッ数(ENOB)を

規定する事ができます(式 25)。

SINAD(dB)= 6.02(ENOB) +1.76dB (25)

ENOB は又式 26に示すように SINAD に関する式で表せ

ます。

ENOB

02.6

SINAD

=

ENOB は ADC ドライバのノイズ性能を ADC のノイズ性

能と比べて、ADCドライバがその ADC を駆動するのに適

しているかどうかを決めるために使用する事ができます。

図 14に差動 ADCノイズモデルを示します。

nRG1

R

G1

i

nIN+

i

nIN–

R

G2

V

nRG2

図 14. 差動 ADC ドライバのノイズモデル

R

F1

+

V

nIN

R

F2

1

(24)

+=NTHD

dB 76.1)dB(

nRF1

V

OCM

V

nRF2

V

no, dm

(26)

V

nCM

08263-014

8 つのノイズ源各々の全出力ノイズ密度への寄与度を

一般的な場合と β1 = β2 ≡β の場合について式 27 に示し

ています。

v

vv

todue

dmno

,

dmno

,

dmno

,

dmno

,

dmno

,

dmno

,

dmno

,

nIN

vv

todue

nCM

iv

todue

nIN

iv

todue

nIN

vv

todue

nRG

vv

todue

nRG

vv

todue

nRF

nIN

= for

+

2

nCM

= for0

nIN

=

+

nIN

=

−

= for4

1

= for4

2

1

= for4

1

nIN

β

ββ

21

ββv

21

ββ

+

21

12

+

12

−

kTRβ

42

+

Rβi

1

G

1

ββ

+

21

Rβi

2

G

2

ββ

+

21

βkTR

−

142

G

+

G

+

ββ

21

1

1

ββ

2

ββ

F

1

=

21

βkTR

−

142

2

21

( )

( )

=

F

1

21

kTR

kTR

===

+

−

βββ

===

21

( )

( )

G

1

G

2

βββ

βββRi

for

1

for

2

R

F

1

R

G

1

R

F

2

R

G

2

βββkTR

===

21

===

21FnIN

βββRi

===

21FnIN

βββ

==

21

βββ

==

21

kTRβ

42

vv

todue

dmno

,

nRF

1

= for4

2

F

2

ββ

+

21

F

2

Rev. 0 | Page 8 of 16

βββkTR

===

21

(27)

Page 9

APPLICATION NOTE

V+

全出力ノイズ電圧密度 v

方根を計算することにより計算されます。全出力ノイズ電

圧密度を計算するには、各式をスプレッドシートに入力す

るのがもっともよい方法です。ノイズ、ゲイン、その他差

動 ADC ドライバの現象を速く計算する ADI Diff Amp

Calculator は www.analog.comで提供されています。

ここで ADCドライバのノイズ性能は ADC の ENOB と比

較することができます。5V 電源、2Vフルスケール入力で

動作する ADC の AD9445を駆動するゲイン 2 の差動ドラ

イバを例にとります;AD9445 は 50 MHz (−3 dB) 帯域

(1極フィルタで制限)を占有した直結の広帯域信号を処

理します。 各種条件の ENOB 仕様をリストしてあるデー

タシートを参照すると、ナイキスト周波数 50MHz では

ENOB=12 ビットです。

ADA4939は直結可能な高性能、広帯域差動 ADC ドライバ

です。 ADA4939はノイズに関しては AD9445 を駆動する

のに適した ADC ドライバです。差動ゲインが約 2 の場合、

データシートでは RF = 402 Ω と RG=200Ω が推奨されてい

ます。 この回路構成での全出力電圧ノイズ密度は 9.7

nV√Hz. です。

初めに、システムノイズ帯域 BN,を計算します。システム

ノイズ帯域 BN,は与えられた一定の入力ノイズ電力スペク

トル密度のシステム帯域を決める実際のフィルタと同じノ

イズ電力を出力する等価長方形ローパス・フィルタの帯域

です。1 極フィルタの場合、BN は式 28 に示すように 3dB

帯域の π/2 倍に等しくなります。

π

=NB

2

次に出力 rmsノイズを得るためにシステム帯域の平方根全

体に渡ってノイズ密度を積算します。(式 29を参照)

v

(rms) = (9.7 nV/√Hz)(√78.5 MHz)= 86 µV rms (29)

no, dm

ノイズの振幅はガウス分布とします;従って、ピーク to

ピーク・ノイズを得るのに一般的な±3σ リミット(ノイズ

電圧は約 99.7%の間これらのリミット内でスウィングし

ます。)を使用すると、ピーク to ピーク出力ノイズは次

のように計算できます。

v

(p-p) ≈ 6(86 µV rms) = 516 µV p-p (30)

no, dm

ここで ADCドライバのピーク to ピーク出力ノイズを、、

ENOB12 ビット、フルスケール入力範囲 2V を基準とした

AD9445LSB の1LSB 電圧(図 31 で計算してるように)

とを比較します。

1 LSB = 2 V/2

12

= 488 µV (31)

ドライバからのピーク to ピーク出力ノイズは ENOB 12 ビ

ットを基準とした ADC の LSB に匹敵します;従ってこの

アプリケーションでは ADC ドライバはノイズの観点から

は検討する良い候補です。最終決定はドライバと ADC の

組み合わせ回路を組み立て、テストする事によりされなけ

ればなりません。

はこれらの成分の二乗和の平

no, dm

MHz5.78MHz50

=

(28)

AN-1026

電源電圧

電源電圧

電源電圧電源電圧

電源電圧と電源電流を調べる事は ADC ドライバの選択を

絞る早い方法です。表 1 は電源を基準にした ADC ドライ

バ性能の簡単なレファランスです。電源電圧は帯域、信号

振幅、ICMVR に影響します。差動アンプの選択には、そ

れぞれの仕様を比べ、トレード・オフを検討する事が重要

です。電源電圧除去(PSR)はもう一つの重要な仕様です。

アンプに対する入力として電源端子の役割はしばしば無視

されます。電源ライン又はそれらに結合されるどのような

ノイズも基本的に出力信号を壊す可能性があります。

例えば、ADA4947-1 の電源ラインに 60MHz で 50 mV p-p

のノイズが載っている場合を考えます。 その PSR は

50MHZ で−70 dB です。これは電源ラインに載ったノイズ

がアンプ出力で約 16 µV に減衰する事を意味します。1 V

フルスケール入力で 16 ビットシステムの場合 1 LSB は

15.3 µV です; 従って電源ラインからのノイズは LSB を妨

害します。

この状況を改善するためには、直列に SMT フェライト・

ビーズ L1と L2 と、シャント・バイパス・コンデンサ C1

と C2、(図 15 参照)を接続してください。

L1

U1

AD8138AR

8

2

1

図 15.電源のバイパス

50MHzでフェライト・ビーズのインピーダンスは 60 Ω

で、10 nF (0.01 µF) コンデンサのインピーダンスは 0.32

Ω です。この 2 つの素子によって構成される減衰回路によ

り 45.5 dB の減衰度が得られます。(式 32 を参照)

デバイダ減衰度= 20log

デバイダ減衰度と PSR –70 dB との組み合わせで約 115

dB の除去が得られます。これによりノイズは 1LSB より

十分小さな約 90 nV p-p に減少します。

C1

10nF

3

54–OUT

V

OCM

+OUT

6

C2

10nF

L2

V–

0.32

+600.32

08263-015

= −45.5 dB (32)

Rev. 0 | Page 9 of 16

Page 10

AN-1026 APPLICATION NOTE

–60

HARMONIC DISTORTION (dBc)

高調波歪み

高調波歪み

高調波歪み高調波歪み

周波数領域での低高調波歪みは狭帯域と広帯域システムの

両方で重要です。ドライバの非直線性はアンプ出力でシン

グル・トーンの高調波歪みと複数トーンの相互変調歪み積

を生じます。

ノイズ解析例に使用された同じアプローチが歪み解析に適

応できます。ADA4939の高調波歪みをフルスケール出力

2V で ENOB12 ビットの AD9445 の 1LSB と比較 します。

1 ENOB LSB はノイズ解析すると 488µV になります。

ADA4939 の仕様表の歪みデータはゲイン 2 とした時の値

で、各種周波数での 2 次高調波と 3 次高調波を比較してい

ます。

表 2

表 3 はゲイン 2、差動出力スウィング 2 V p-p

の条件での高調波歪みを示します。

表

表 2. ADA4943のののの 2 次および

表表

次および 3 次高調波歪み

次および次および

次高調波歪み

次高調波歪み次高調波歪み

Parameter Harmonic Distortion (dBc)

HD2 @ 10 MHz -102

HD2 @ 70 MHz -83

HD2 @ 100 MHz -77

HD3 @ 10 MHz -101

HD3 @ 70 MHz -97

HD3 @ 100 MHz -91

データは周波数が高くなるとともに高調波歪みが増える事

と、対象の周波数(50MHz)では HD2 が HD3 より悪い事を

示しています。高調波歪み積は対象の周波数よりも周波数

が高いのでそれらの振幅はシステム帯域制限により低減す

ることができます。もしシステムに 50 MHz でブリックウ

ォール・フィルタがあれば 25 MHz以上の周波数のみ対

象になります。なぜならばより高い周波数の全高調波はフ

ィルタで減衰されるからです。それでもシステムを

50 MHz まで評価しました。なぜなら存在するどのフィル

タも高調波を十分に減衰する事は難しく、歪み積が信号帯

域内に折り返される可能性があるからです。図 16は 2 V

p-p 出力として各種電源電圧について ADA4939 の高調波

歪み対周波数を示しています。

V

= 2V p-p

OUT, dm

–65

–70

–75

–80

–85

–90

–95

–100

–105

–110

HD2, VS (SPLIT SUPPLY) = ±2.5V

HD3, VS (SPLIT SUPPLY) = ±2.5V

HD2, VS (SPLIT SUPPLY) = ±1.65V

HD3, VS (SPLIT SUPPLY) = ±1.65V

HD2 ≈ –88dBc @ 50MHz

1 10 100

図 16.高調波歪みの周波数特性

FREQUENCY (MHz)

08263-016

50 MHzでの HD2 は入力信号 2 V p-p に対して約−88 dBc

です。高調波歪みのレベルを 1 ENOB LSB と比較するた

めに、式 33 に示したようにこのレベルを電圧に変換する

必要があります。

88

−

20

HD2

( )

=

≈

p-pµV 8010p-pV 2

(33)

この歪み積はわずか 80 µV p-p、又は 1 ENOB LSB の

16%です。このように歪みの点から ADA4939 は AD9445

ADC を駆動するドライバとして検討する適正な選択にな

ります。

ADC ドライバは負帰還型アンプなので、出力歪みはアン

プ回路のループゲインの大きさに依存します。負帰還アン

プのもともとのオープンループ歪みは ファクタ 1/(1 + LG)

分縮小します。ここで LG はアンプのループゲインです。

アンプの入力(誤差電圧)は大きな順電圧ゲイン A(s)と

乗算され、帰還率 β を通して入力にフィードバックされ

ますが、ここで誤差が最小限になるように出力電圧が調整

されます。 それ故、このタイプのアンプのループゲイン

は A(s) × β です;ループゲイン(A(s), β, 又は両方)が減少

すると、高調波歪みが増します。 積分器のような電圧帰

還アンプは DC と低周波数で大きな A(s)を持ち、規定され

た高周波でゲインが 1 になるまで 1/f でロールオフするよ

うに設計されています。A(s)はロールオフすると、ループ

ゲインが減少し、歪みが増大します。それ故、高調波歪み

特性は A(s)の逆になります。

電流帰還型オペアンプは誤差電流を帰還信号として使いま

す。誤差電流は大きなトランスインピーダンス、 T(s)、に

乗算され、出力電圧に変換されます。それから帰還率

1/RF を経由して出力電圧を帰還電流に変換します。その

帰還電流は入力誤差電流を最小限にするように働きます。

それ故理想電流帰還アンプのループゲインは T(s) × (1/RF)

= T(s)/RFになります。A(s)と同じように T(s) は大きな DC

値を持っており、周波数が高くなるとロールオフし、ルー

プゲインが低減してきて高調波歪みが増大します。

ループゲインは又直接帰還率 1/R

に依存します。理想的

F

、

な電流帰還アンプのループゲインは閉ループゲインに依存

しません;それ故高調波歪み特性は閉ループゲインが増し

ても悪くなりません。しかし実際の電流帰還型アンプでは

ループゲインは閉ループゲインの大きさに多少影響されま

す。しかしその影響度は電圧帰還型アンプよりはるかに少

なくなっております。この理由により高閉ループゲインと

低歪みを要求するアプリケーションには電圧帰還型アンプ

よりも ADA4927のような電流帰還型アンプの方を選択す

る方がよいことがわかります。

Rev. 0 | Page 10 of 16

Page 11

APPLICATION NOTE

–40

SPURIOUS-FREE DYNAMIC RANGE (dBc)

–50

DISTORTION (dBc)

(

)

+

図 17 は ADA4927 について閉ループゲインが大きくなっ

ても、歪み特性がどのように良好に維持されているかを示

しています。

V

= 2V p-p

OUT, dm

–50

–60

–70

–80

–90

–100

–110

–120

–130

1 10 100 1k

図 17.高調波歪み対周波数特性およびゲイン

帯域とスルーレート

帯域とスルーレート

帯域とスルーレート帯域とスルーレート

FREQUENCY (MHz)

帯域とスルーレートは ADC ドライバアプリケーションで

特に重要です。一般的にデバイスの帯域は小信号帯域です。

一方スルーレートはアンプ出力での大信号振幅の最大変化

率です。

ENOB に似ている用語で有効使用可能帯域(EUBW)があり

ますが、これは帯域の事を述べています。多数の ADC ド

ライバとオペアンプは帯域の仕様を誇示していますが、実

際に使用可能な帯域は限られています。例えば −3 dB 帯

域は帯域を評価する従来の方法ですが、すべての帯域が使

用可能という意味ではありません。−3 dB 帯域の振幅誤差

と位相誤差は実際のカットオフ周波数よりも 1 デケード早

く観測されます。使用可能な帯域を決定するよい方法はデ

ータシートの歪みに関するグラフを参照する事です。

図 18 は 2 次、3 次高調波歪みを−80 dBc 以上に保つには、

ADC ドライバを 60 MHz.以上の周波数で使用するべきで

はないことを示しています。

図 18.

各アプリケーション

は違うので、システム条件がそのアプリケーションに対し

て十分な帯域と十分な歪み特性を持った適切なドライバか

どうかの案内になります。

HD2, G = 1, RF = 200Ω

HD3, G = 1, RF = 200Ω

–60

–70

–80

–90

–100

–110

–120

図 18.2 電流帰還 ADC ドライバ ADA4937 の歪み曲線

HD2, G = 2, RF = 402Ω

HD3, G = 2, RF = 402Ω

1 10 100

FREQUENCY (MHz)

G = 1

G = 10

G = 20

08263-017

08263-018

AN-1026

スルーレート(大信号パラメータ)はアンプ出力が大きな

歪みを伴わないで入力に追従することのできる最大の変化

率です。 サイン波出力のスルーレートについて考えてみま

しょう。

VO = VP sin 2πft (34)

式 34 のゼロ交差での導関数(変化率)、最大変化率は次

のとうりです。

dv

dt

ここで、

dv/dt maxはスルーレートです。

VPはピーク電圧です。

f はフルパワー帯域幅(FPBW)です。FPBW について解く

と下記の式になります、

FPBWπ=

それ故、ADC ドライバを選ぶ時にはアンプが対象アプリ

ケーションで十分使用可能か判断するためにゲイン、帯域、

スルーレート(FPBW)を確認する事が重要です。

安定性

安定性

安定性安定性

差動 ADC ドライバの安定性に関する評価はオペアンプと

同じです。主な仕様は位相余裕です。特定のアンプ回路の

位相余裕はデータシートから決定されます;しかしそれは

実際のシステムでは PC 基板レイアウトの寄生的な影響に

より大きく低減します。

負電圧帰還オペアンプの安定性はループゲイン A(s) × β の

大きさと符号に依存します。 差動 ADC ドライバには 2 つ

の帰還率があるので標準的なオペアンプ回路よりも多少複

雑です。 ループゲインは式 7と式 8 の分母の中にありま

す。式 37は帰還率がマッチングしてない (β1 ≠ β2)場合の

ループゲインです。

帰還率がマッチングしてない場合、有効な帰還率は単に 2

つの帰還率の平均です。それらがマッチングしていて β と

規定した時、ループゲインは A(s) × β に簡略化できます。

帰還アンプを安定させるには、ループゲインが−1 又はそ

れと等価ですが−180°の位相シフトでループゲイン+1 にな

ることを避けなければなりません。電圧帰還アンプの場合、

オープン・ループ・ゲイン周波数曲線でループゲインの大

きさが 1(すなわち、 0 dB)に等しい点で A(s)の大きさ

が帰還率の逆数に等しくなります。基本的なアンプのアプ

リケーションでは帰還は純粋に抵抗性なので帰還ループ周

辺で位相シフトは生じません。帰還率がマッチングしてい

る場合、周波数依存性のない帰還率の逆数、1 + RF/R

ノイズゲインと呼ばれる事があります。デシベル表示の一

定のノイズゲインをオープン・ループ・ゲイン、A(s)と同

じグラフに描いた時、2 つの曲線が交差する周波数がルー

プゲイン 1、又は 0dBになる周波数です。その周波数での

A(s)の位相と−180°との間の差が位相余裕と定義されま

す;安定動作のためには、位相余裕は 45°に等しいか大き

くなければなりません。

図 3.

max

fV

π= 2

(35)

P

RateSlew

(36)

Vp

2

)(

ββ

GainLoop

sA

=

21

(37)

2

は

G

Rev. 0 | Page 11 of 16

Page 12

AN-1026 APPLICATION NOTE

80

90

GAIN (dB)

1k

50

IMPEDANCE MAGNITUDE (kΩ)

図 19 は RF/RG = 1 (ノイズゲイン = 2)に設定した

ADA4932 のユニティループ・ゲイン点と位相余裕につい

て説明しています。

GAIN

60

PHASE

40

20

6

0

–20

–40

–60

–80

1k 10k 100k 1M 10M 100M 1G 10G

PHASE

MARGIN ≈ 70°

FREQUENCY (Hz)

図 3. ADA4932 のオープン・ループ・ゲインの大きさ

および位相対周波数

R

F

R

(6dB)1 + = 2

G

LOOP

GAIN = 0dB

45

0

–45

–90

–135

–180

–225

–270

PHASE (Degrees)

図 19 をさらに詳しく調べると ADA4932 はノイズゲイン

1(各ループで 100%帰還) で約 50° の位相余裕があります。

ADC ドライバをゼロ・ゲインで動作させる事は現実的で

はありませんが、この事は ADA4932が整数でない差動ゲ

イン(たとえば RF/RG = 0.25, ノイズゲイン = 1.25)で安定動

作する事を示しています。この事は全部の差動 A/Dコン

バータ ドライバには適用されません。安定動作する最小

ゲインはすべての ADC ドライバのデータシートに記述さ

れています。

電流帰還形 ADC ドライバの位相余裕も又オープンループ

応答特性から決定されます。電流帰還型アンプの場合はフ

ォワード・ゲインの代わりにフォワード・トランスインピ

ーダンス T(s)を使用し、誤差電流がフィードバック信号と

なります。フィードバック抵抗がマッチングしている電流

帰還型ドライバのループゲインは T(s)/R

です;従って電

F

流帰還型アンプのループゲインは T(s) = RFの時 1(すなわ

ち、0dB)に等しくなります。この点はオープンループ・

トランスインピーダンスと位相のグラフで(電圧帰還型ア

ンプの場合と同じ方法で)簡単に探し出す事ができます。

抵抗の 1 kΩ に対する比率をプロットする事により抵抗を

対数グラフで表せます。

図 4.

図 20 は RF = 300とした場

合の電流帰還型差動 ADC ドライバ ADA4927 のユニティ

ループ・ゲイン点と位相余裕について説明しています。

MAGNITUDE

PHASE

100

10

1

0.3

0.1

10 100 1k 10k 100k 1M 10M 100M 1G 10G

FREQUENCY (Hz)

図 4.ADA4927のオープン・ループ・ゲインおよび位相対周波数

0

–50

–100

–135

–150

–180

–200

IMPEDANCE PHASE (Degrees)

PHASE

MARGIN ≈ 45°

08263-019

300 Ω フィードバック抵抗の水平線がトランスインピーダ

ンス曲線と交差する所でループゲインが 0dB になります。

この周波数では T(s) の位相が約−135°となりますので、位

相余裕が+45°になります。位相余裕と安定性は、R

きくなると増し、R

が小さくなると低減します。電流帰

F

F

還型アンプにはいつも純粋な抵抗性フィードバックを用い、

十分な位相余裕をもつ必要があります。

PC

PC ボードのレイアウト

ボードのレイアウト

PCPC

ボードのレイアウトボードのレイアウト

安定した ADC ドライバの設計は PC 基板で実現されなけ

ればなりません。基板の寄生要素(最小限に保たなければ

なりません)により位相余裕が多少失われます。特に懸念

されるのが負荷容量、帰還ループ・インダクタンス、加算

ノード容量です。 これら各々の寄生リアクタンスにより

遅延する位相シフトが帰還ループに加わり、位相マージン

が低減します。PC基板レイアウトの設計が悪いと位相マ

ージンが 20° 又はそれ以上失われます。

電圧帰還型アンプで R

と加算点容量で形成される極によ

F

る位相シフトを最小限にするために、できるだけ小さな

RFを使うのがベストです。もし大きな R

小さな容量 C

を各帰還抵抗間に接続する事によりその加

F

が必要な場合、

F

算点容量を補償する事ができます。この場合 CFは RFCF

が加算ノード容量の R

倍に等しくなるような値に設定し

G

ます。

PC 基板レイアウトは必要な設計の最後のステップの一つ

です。高速回路の性能はレイアウトに大きく依存しますが、

あいにく PC 基板レイアウトは設計でもっとも見落としが

ちなステップの一つです。不注意な又は貧弱なレイアウト

によって高性能設計の性能低下を余儀なくさせられたり、

場合によっては使用を諦めさせられる事になります。ここ

では適切な高速 PC 基板設計のすべての面をカバーできま

せんが、いくつかの主なトピックスについて述べます。

寄生成分は高速回路の性能を低下させます。寄生容量は部

品のパッド、パターン、グラウンド・プレーン又は電源プ

レーンによって生じます。グラウンド・プレーンのない長

いパターンは寄生インダクタンスが生じ、過度応答にリン

ギングを生じたり、他の不安定な現象をもたらします。得

にアンプの加算ノードで生ずる寄生容量は大きな影響があ

ります。なぜならそれはフィードバック応答に極をつくり、

ピーキングを生じたり不安定になるからです。一つの解決

方法は基板全部の層において、ADCドライバの搭載部分

とフィードバック部品のパッドの下の領域にはグラウン

ド・プレーンや電源プレーンを設けないようにする事です。

望ましくない寄生リアクタンスを最小限にするためにすべ

てのパターンをできるだけ短く保ってください。FR-4PC

基板の外側層の 50 Ω パターンはおおよそ 2.8 pF/インチ

と 7 nH/インチあります。内側層の 50 Ω パターンの場合

これらの寄生リアクタンスは約 30% 増えます。さらにパ

ターン・インダクタンスを最小限にするために長いパター

ンの下にグラウンド・プレーンが有ることを確認してくだ

さい。パターンを短く、小さく保つことは寄生容量と寄生

インダクタンスを最小限にし、設計の完全性を維持するの

に役立ちます。

08263-020

が大

Rev. 0 | Page 12 of 16

Page 13

APPLICATION NOTE

R4

電源バイパスはレイアウトを行うに際し問題となるもう

一つの主な分野です;(V

様に)電源バイパス・コンデンサをアンプのピンのできる

だけ近くに配置する事を確実に行ってください。さらに複

数のバイパス・コンデンサを電源ラインに使う事は、広帯

域ノイズに対して低インピーダンス・パスにする事を確実

にする助けになります。図 21は電源バイパスと出力にロ

ーパス・フィルタを接続した標準的な差動アンプ回路です。

図 21.

ローパス・フィルタは帯域と ADC に入るノイズを

制限します。理想的には電源バイパス・コンデンサのリタ

ーンは負荷リターンの近くにあることです;これはグラウ

ンド・プレーンの中の還流電流を減らし ADC ドライバ性

能を改善する助けになります。(図 22 参照)

R

S

R

図 21.電源バイパスと出力ローパス・フィルタを接続した

R2

V

OCM

T

R1

C1

R3

バイパス・コンデンサと同

OCM

+V

S

C2

C3

R6

U1

C4

C5

–V

S

R5

R7

ADCドライバ

C6

C7

TO

ADC

AN-1026

グラウンド・プレーンの使用や一般的な接地方法は複雑で

内容が深いテーマなのでこのアプリケーション・ノートの

範囲外です。しかし、いくつかの主なポイントを次に述べ

ます。(図 22 参照)

• アナログ・グラウンドとデジタル・グラウンドとを共

に 1 点で接続してください。そのようにすればグラウ

ンド・プレーンを流れるアナログ電流とデジタル電流

の相互作用(これがシステムにノイズを招きます。)

を最小限にする事ができます。

• アナログ電源をアナログ電源プレーンに終端し、デジ

タル電源をデジタル電源プレーンに終端してください。

• ミックスド・シグナル IC の場合、デジタル電流とア

ナログ電流が混じ合わないように、アナログ・グラウ

ンド・リターンをアナログ・グラウンド・プレーンに

終端し、デジタル・グラウンド・リターンをデジタ

ル・グラウンド・プレーンに終端し、2つのプレーン

を共に1つの小さな接続だけで接続してください。

(図 23 参照)

高速プリント基板(PCB)レイアウトについての詳細な説明

は www.analog.comの”A Practical Guide to High-Speed

Printed-Circuit-Board Layout ”を参照してください。

このアプリケーション・ノートの情報は ADC ドライバを

使って回路設計をする時、考慮しなければならない多数の

課題について考えるお手伝いをするのが目的です。プロジ

ェクトの初めに差動アンプについて理解し、ADC ドライ

バの設計の詳細に注意を払う事は将来の問題を最小限に抑

え、リスクを減らし、堅牢な設計を確かなものとします。

R2

R4

R

T

U1

R1 R3 R5

(a)

R6

R7

C2

C3

C4

C1

C5

(b)

C6

C7

図 22.部品側(a), 回路側(b)

SYSTEM

STAR

GROUND

V

A

ANALOG

CIRCUITS

A A D

ANALOG

CIRCUITS

V

AGND DGND

A D

図 23.ミックスド・シグナルの接地

A

MIXED

SIGNALS

V

D

V

D

DIGITAL

CIRCUITS

D

DIGITAL

CIRCUITS

DIGITAL SUPPLYANALOG SUPPLY

Rev. 0 | Page 13 of 16

Page 14

AN-1026 APPLICATION NOTE

ノート

ノート

ノートノート

Rev. 0 | Page 14 of 16

Page 15

APPLICATION NOTE

ノート

ノート

ノートノート

AN-1026

Rev. 0 | Page 15 of 16

Page 16

AN-1026 APPLICATION NOTE

2008

ノート

ノート

ノートノート

Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

©

Rev. 0 | Page 16 of 16

Loading...

Loading...