Datasheet AMP04GBC, AMP04FS-REEL7, AMP04FS-REEL, AMP04FS, AMP04FP Datasheet (Analog Devices)

...Page 1

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AMP04*

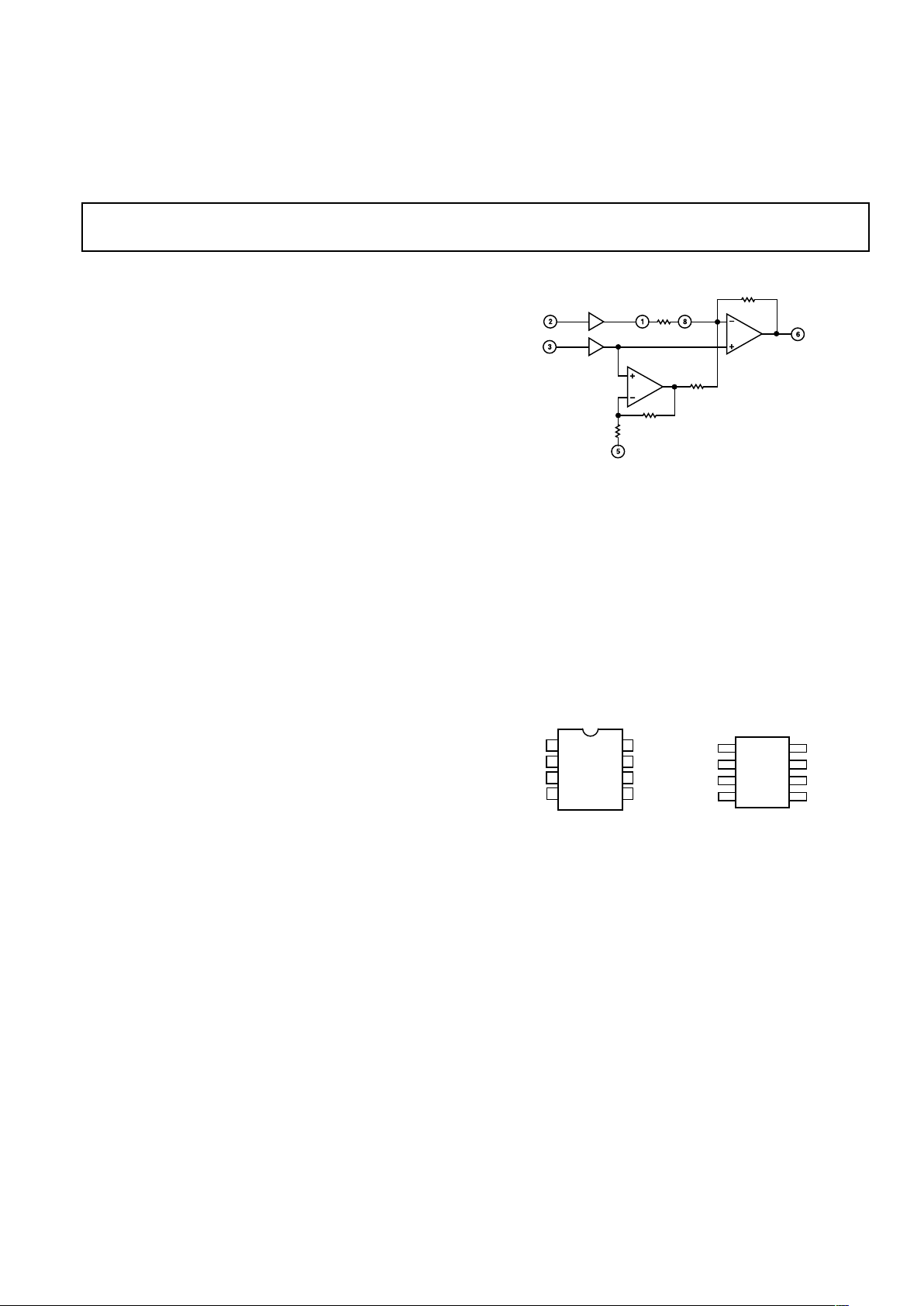

FUNCTIONAL BLOCK DIAGRAM

IN(–)

IN(+)

INPUT BUFFERS

REF

100k

11k

11k

R

GAIN

V

OUT

100k

FEATURES

Single Supply Operation

Low Supply Current: 700 A Max

Wide Gain Range: 1 to 1000

Low Offset Voltage: 150 V Max

Zero-In/Zero-Out

Single-Resistor Gain Set

8-Lead Mini-DIP and SO Packages

APPLICATIONS

Strain Gages

Thermocouples

RTDs

Battery-Powered Equipment

Medical Instrumentation

Data Acquisition Systems

PC-Based Instruments

Portable Instrumentation

Precision Single Supply

Instrumentation Amplifier

GENERAL DESCRIPTION

The AMP04 is a single-supply instrumentation amplifier

designed to work over a +5 volt to ±15 volt supply range. It

offers an excellent combination of accuracy, low power consumption, wide input voltage range, and excellent gain

performance.

Gain is set by a single external resistor and can be from 1 to

1000. Input common-mode voltage range allows the AMP04 to

handle signals with full accuracy from ground to within 1 volt of

the positive supply. And the output can swing to within 1 volt of

the positive supply. Gain bandwidth is over 700 kHz. In addition to being easy to use, the AMP04 draws only 700 µA of

supply current.

For high resolution data acquisition systems, laser trimming of

low drift thin-film resistors limits the input offset voltage to

under 150 µV, and allows the AMP04 to offer gain nonlinearity

of 0.005% and a gain tempco of 30 ppm/°C.

A proprietary input structure limits input offset currents to

less than 5 nA with drift of only 8 pA/°C, allowing direct connection of the AMP04 to high impedance transducers and

other signal sources.

The AMP04 is specified over the extended industrial (–40°C to

+85°C) temperature range. AMP04s are available in plastic and

ceramic DIP plus SO-8 surface mount packages.

Contact your local sales office for MIL-STD-883 data sheet

and availability.

PIN CONNECTIONS

8-Lead Epoxy DIP

(P Suffix)

8-Lead Narrow-Body SO

(S Suffix)

*Protected by U.S. Patent No. 5,075,633.

1

2

3

4

8

7

6

5

AMP04

R

GAIN

V+

V

OUT

REF

R

GAIN

–IN

+IN

V–

AMP04

V+

R

GAIN

V

OUT

REF

R

GAIN

–IN

+IN

V–

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

Page 2

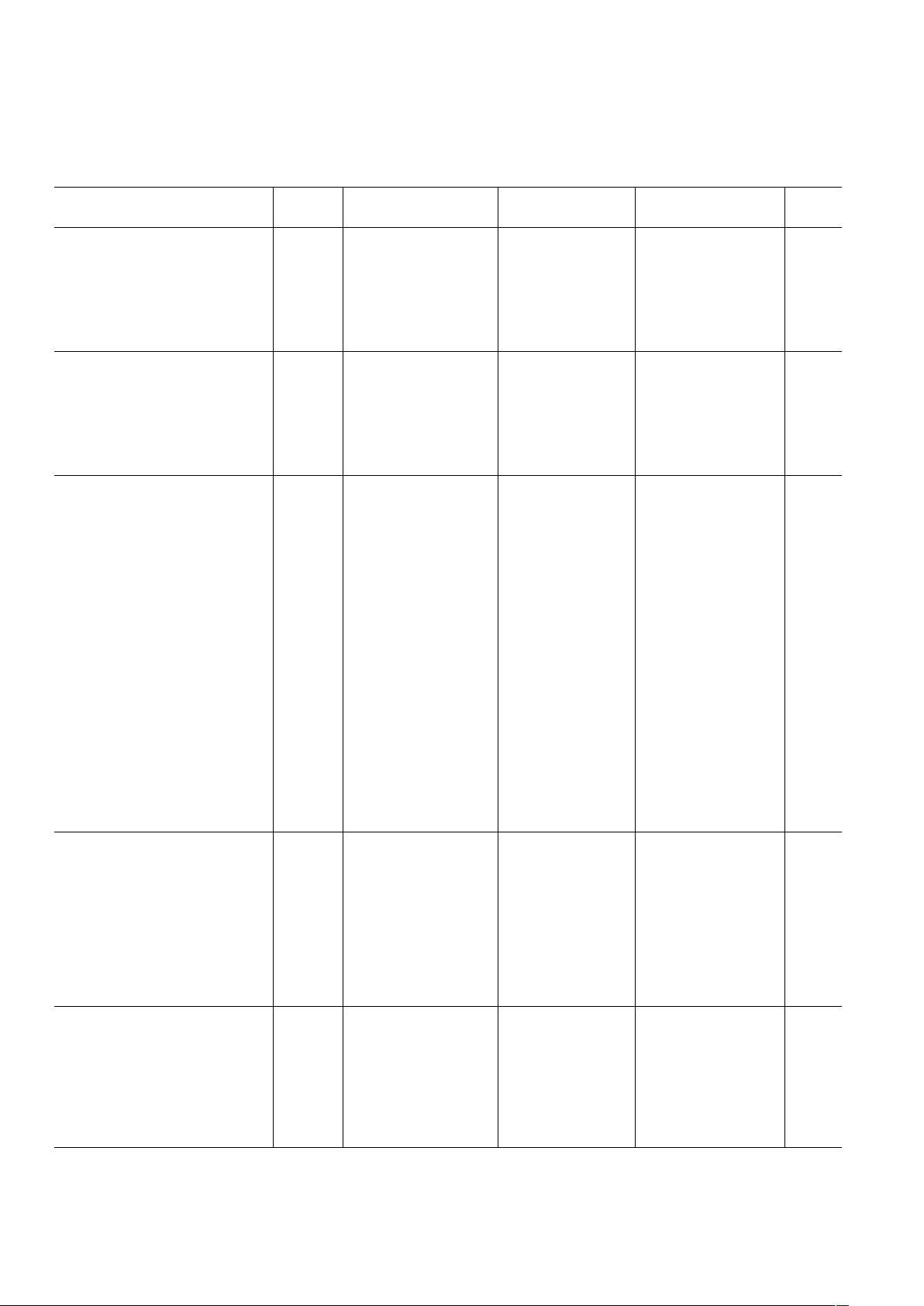

AMP04–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

AMP04E AMP04F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

OFFSET VOLTAGE

Input Offset Voltage V

IOS

30 150 300 µV

–40°C ≤ T

A

≤ +85°C 300 600 µV

Input Offset Voltage Drift TCV

IOS

36µV/°C

Output Offset Voltage V

OOS

0.5 1.5 3 mV

–40°C ≤ T

A

≤ +85°C3 6mV

Output Offset Voltage Drift TCV

OOS

30 50 µV/°C

INPUT CURRENT

Input Bias Current I

B

22 30 40 nA

–40°C ≤ T

A

≤ +85°C50 60nA

Input Bias Current Drift TCI

B

65 65 pA/°C

Input Offset Current I

OS

15 10nA

–40°C ≤ T

A

≤ +85°C10 15nA

Input Offset Current Drift TCI

OS

8 8 pA/°C

INPUT

Common-Mode Input Resistance 4 4 GΩ

Differential Input Resistance 4 4 GΩ

Input Voltage Range V

IN

0 3.0 0 3.0 V

Common-Mode Rejection CMR 0 V ≤ V

CM

≤ 3.0 V

G = 1 60 80 55 dB

G = 10 80 100 75 dB

G = 100 90 105 80 dB

G = 1000 90 105 80 dB

Common-Mode Rejection CMR 0 V ≤ V

CM

≤ 2.5 V

–40°C ≤ T

A

≤ +85°C

G = 1 55 50 dB

G = 10 75 70 dB

G = 100 85 75 dB

G = 1000 85 75 dB

Power Supply Rejection PSRR 4.0 V ≤ V

S

≤ 12 V

–40°C ≤ T

A

≤ +85°C

G = 1 95 85 dB

G = 10 105 95 dB

G = 100 105 95 dB

G = 1000 105 95 dB

GAIN (G = 100 K/R

GAIN

)

Gain Equation Accuracy G = 1 to 100 0.2 0.5 0.75 %

G = 1 to 100

–40°C ≤ T

A

≤ +85°C 0.8 1.0 %

G = 1000 0.4 0.75 %

Gain Range G 1 1000 1 1000 V/V

Nonlinearity G = 1, R

L

= 5 kΩ 0.005 %

G = 10, R

L

= 5 kΩ 0.015 %

G = 100, R

L

= 5 kΩ 0.025 %

Gain Temperature Coefficient ∆G/∆T 30 50 ppm/°C

OUTPUT

Output Voltage Swing High V

OH

RL = 2 kΩ 4.0 4.2 4.0 V

R

L

= 2 kΩ

–40°C ≤ T

A

≤ +85°C 3.8 3.8 V

Output Voltage Swing Low V

OL

RL = 2 kΩ

–40°C ≤ T

A

≤ +85°C 2.0 2.5 mV

Output Current Limit Sink 30 30 mA

Source 15 15 mA

REV. B

–2–

(VS = 5 V, VCM = 2.5 V, TA = 25C unless otherwise noted)

Page 3

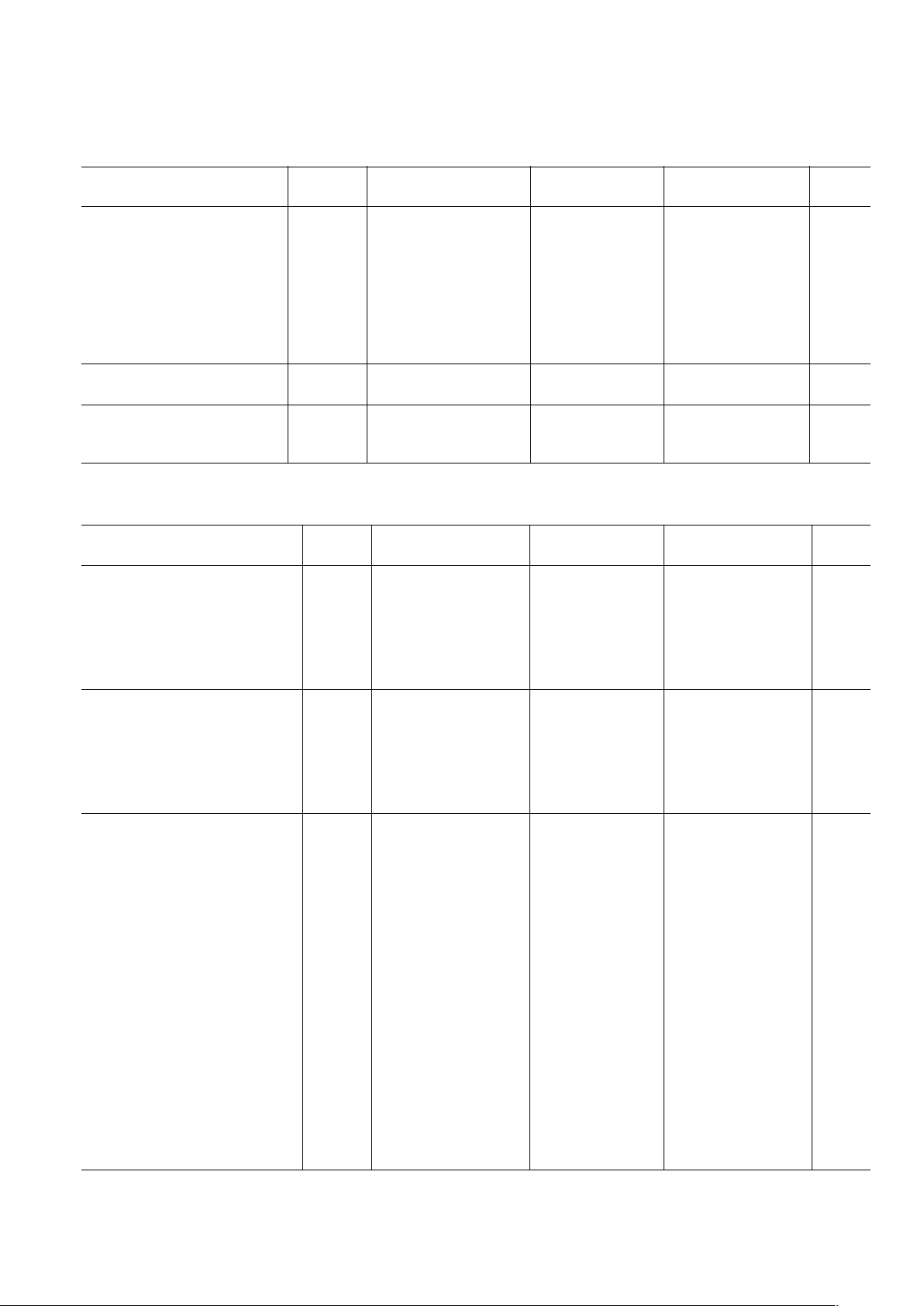

AMP04

REV. B

–3–

AMP04E AMP04F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

NOISE

Noise Voltage Density, RTI e

N

f = 1 kHz, G = 1 270 270 nV/√Hz

f = 1 kHz, G = 10 45 45 nV/√Hz

f = 100 Hz, G = 100 30 30 nV/√Hz

f = 100 Hz, G = 1000 25 25 nV/√Hz

Noise Current Density, RTI i

N

f = 100 Hz, G = 100 4 4 pA/√Hz

Input Noise Voltage e

N

p-p 0.1 Hz to 10 Hz, G = 1 7 7 µV p-p

0.1 Hz to 10 Hz, G = 10 1.5 1.5 µV p-p

0.1 Hz to 10 Hz, G = 100 0.7 0.7 µV p-p

DYNAMIC RESPONSE

Small Signal Bandwidth BW G = 1, –3 dB 300 300 kHz

POWER SUPPLY

Supply Current I

SY

550 700 700 µA

–40°C ≤ TA ≤ +85°C 850 850 µA

Specifications subject to change without notice.

ELECTRICAL CHARACTERISTICS

AMP04E AMP04F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

OFFSET VOLTAGE

Input Offset Voltage V

IOS

80 400 600 µV

–40°C ≤ T

A

≤ +85°C 600 900 µV

Input Offset Voltage Drift TCV

IOS

36µV/°C

Output Offset Voltage V

OOS

13 6 mV

–40°C ≤ T

A

≤ +85°C6 9mV

Output Offset Voltage Drift TCV

OOS

30 50 µV/°C

INPUT CURRENT

Input Bias Current I

B

17 30 40 nA

–40°C ≤ T

A

≤ +85°C50 60nA

Input Bias Current Drift TCI

B

65 65 pA/°C

Input Offset Current I

OS

25 10nA

–40°C ≤ T

A

≤ +85°C15 20nA

Input Offset Current Drift TCI

OS

28 28 pA/°C

INPUT

Common-Mode Input Resistance 4 4 GΩ

Differential Input Resistance 4 4 GΩ

Input Voltage Range V

IN

–12 +12 –12 +12 V

Common-Mode Rejection CMR –12 V ≤ V

CM

≤ +12 V

G = 1 60 80 55 dB

G = 10 80 100 75 dB

G = 100 90 105 80 dB

G = 1000 90 105 80 dB

Common-Mode Rejection CMR –11 V ≤ V

CM

≤ +11 V

–40°C ≤ T

A

≤ +85°C

G = 1 55 50 dB

G = 10 75 70 dB

G = 100 85 75 dB

G = 1000 85 75 dB

Power Supply Rejection PSRR ± 2.5 V ≤ V

S

≤ ± 18 V

–40°C ≤ T

A

≤ +85°C

G = 1 75 70 dB

G = 10 90 80 dB

G = 100 95 85 dB

G = 1000 95 85 dB

(VS = 15 V, VCM = 0 V, TA = 25C unless otherwise noted)

Page 4

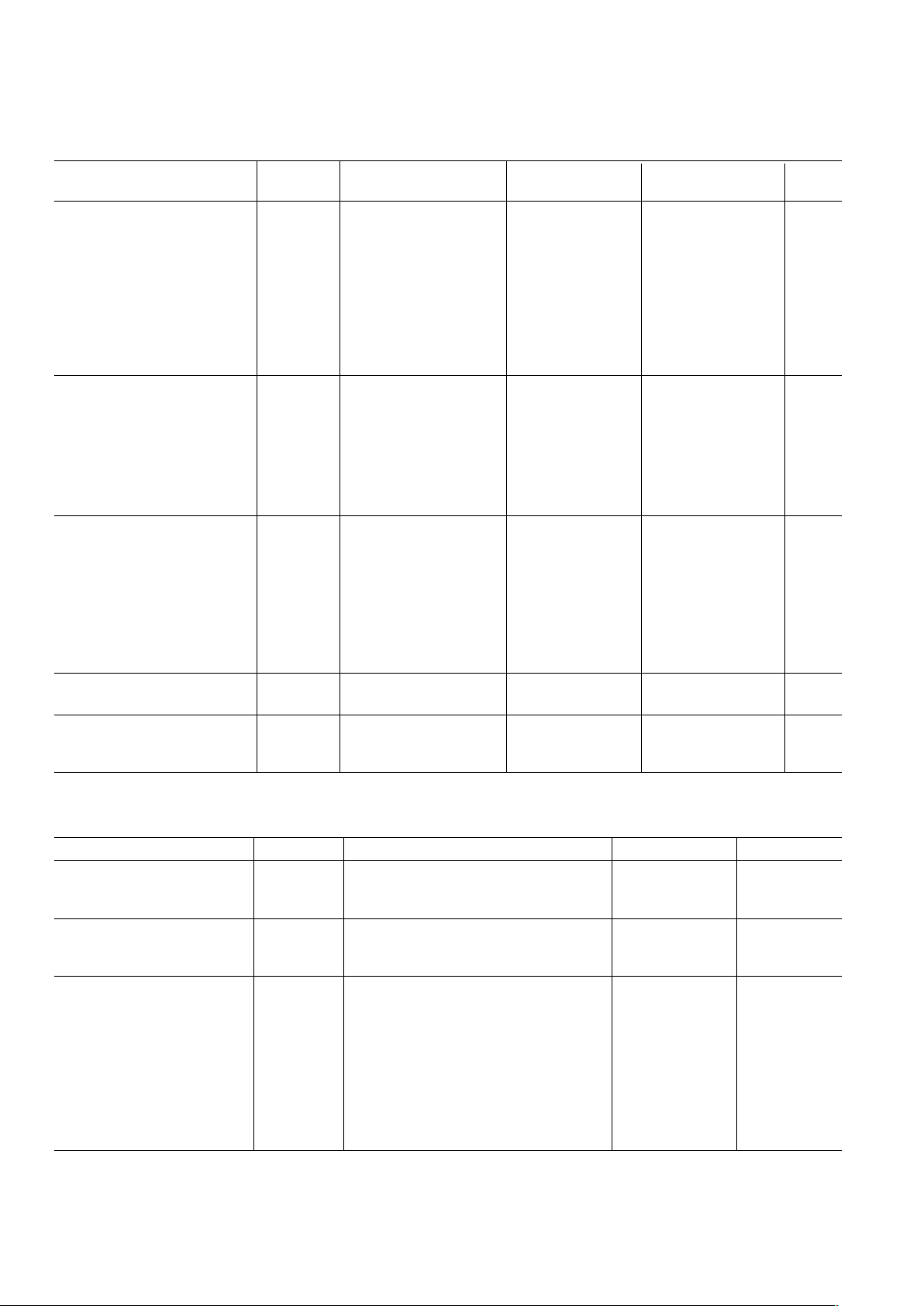

AMP04

REV. B

–4–

AMP04E AMP04F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

GAIN (G = 100 K/R

GAIN

)

Gain Equation Accuracy G = 1 to 100 0.2 0.5 0.75 %

G = 1000 0.4 0.75 %

G = 1 to 100

–40°C ≤ T

A

≤ +85°C 0.8 1.0 %

Gain Range G 1 1000 1 1000 V/V

Nonlinearity G = 1, R

L

= 5 kΩ 0.005 0.005 %

G = 10, R

L

= 5 kΩ 0.015 0.015 %

G = 100, R

L

= 5 kΩ 0.025 0.025 %

Gain Temperature Coefficient ∆G/∆T 30 50 ppm/°C

OUTPUT

Output Voltage Swing High V

OH

RL = 2 kΩ 13 13.4 13 V

R

L

= 2 kΩ

–40°C ≤ T

A

≤ +85°C 12.5 12.5 V

Output Voltage Swing Low V

OL

RL = 2 kΩ

–40°C ≤ T

A

≤ +85°C –14.5 –14.5 V

Output Current Limit Sink 30 30 mA

Source 15 15 mA

NOISE

Noise Voltage Density, RTI e

N

f = 1 kHz, G = 1 270 270 nV/√Hz

f = 1 kHz, G = 10 45 45 nV/√Hz

f = 100 Hz, G = 100 30 30 nV/√Hz

f = 100 Hz, G = 1000 25 25 nV/√Hz

Noise Current Density, RTI i

N

f = 100 Hz, G = 100 4 4 pA/√Hz

Input Noise Voltage e

N

p-p 0.1 Hz to 10 Hz, G = 1 5 5 µV p-p

0.1 Hz to 10 Hz, G = 10 1 1 µV p-p

0.1 Hz to 10 Hz, G = 100 0.5 0.5 µV p-p

DYNAMIC RESPONSE

Small Signal Bandwidth BW G = 1, –3 dB 700 700 kHz

POWER SUPPLY

Supply Current I

SY

750 900 900 µA

–40°C ≤ TA ≤ +85°C 1100 1100 µA

Specifications subject to change without notice.

WAFER TEST LIMITS

Parameter Symbol Conditions Limit Unit

OFFSET VOLTAGE

Input Offset Voltage V

IOS

300 µV max

Output Offset Voltage V

OOS

3mV max

INPUT CURRENT

Input Bias Current I

B

40 nA max

Input Offset Current I

OS

10 nA max

INPUT

Common-Mode Rejection CMR 0 V ≤ VCM ≤ 3.0 V

G = 1 55 dB min

G = 10 75 dB min

G = 100 80 dB min

G = 1000 80 dB min

Common-Mode Rejection CMR V

S

= ±15 V, –12 V ≤ VCM ≤ +12 V

G = 1 55 dB min

G = 10 75 dB min

G = 100 80 dB min

(VS = 5 V, VCM = 2.5 V, TA = 25C unless otherwise noted)

Page 5

AMP04

REV. B

–5–

Parameter Symbol Conditions Limit Unit

G = 1000 80 dB min

Power Supply Rejection PSRR 4.0 V ≤ V

S

≤ 12 V

G = 1 85 dB min

G = 10 95 dB min

G = 100 95 dB min

G = 1000 95 dB min

GAIN (G = 100 K/R

GAIN

)

Gain Equation Accuracy G = 1 to 100 0.75 % max

OUTPUT

Output Voltage Swing High V

OH

RL = 2 kΩ 4.0 V min

Output Voltage Swing Low V

OL

RL = 2 kΩ 2.5 mV max

POWER SUPPLY

Supply Current I

SY

VS = ±15 900 µA max

700 µA max

NOTE

Electrical tests and wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard

product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

ABSOLUTE MAXIMUM RATINGS

1

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±18 V

Common-Mode Input Voltage

2

. . . . . . . . . . . . . . . . . . . ± 18 V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . 36 V

Output Short-Circuit Duration to GND . . . . . . . . . . Indefinite

Storage Temperature Range

Z Package . . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +175°C

P, S Package . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

AMP04A . . . . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

AMP04E, F . . . . . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

Junction Temperature Range

Z Package . . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +175°C

P, S Package . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . . 300°C

Package Type

JA

3

JC

Unit

8-Lead Cerdip (Z) 148 16 °C/W

8-Lead Plastic DIP (P) 103 43 °C/W

8-Lead SOIC (S) 158 43 °C/W

NOTES

1

Absolute maximum ratings apply to both DICE and packaged parts, unless

otherwise noted.

2

For supply voltages less than ± 18 V, the absolute maximum input voltage is

equal to the supply voltage.

3

θJA is specified for the worst case conditions, i.e., θJA is specified for device in

socket for cerdip, P-DIP, and LCC packages; θJA is specified for device

soldered in circuit board for SOIC package.

ORDERING GUIDE

Temperature VOS @ 5 V Package Package

Model Range TA = 25C Description Option

AMP04EP XIND 150 µV Plastic DIP N-8

AMP04ES XIND 150 µV SOIC SO-8

AMP04ES-REEL7 XIND 150 µV SOIC SO-8

AMP04FP XIND 300 µV Plastic DIP N-8

AMP04FS XIND 300 µV SOIC SO-8

AMP04FS-REEL XIND 150 µV SOIC SO-8

AMP04FS-REEL7 XIND 150 µV SOIC SO-8

AMP04GBC 25°C 300 µV

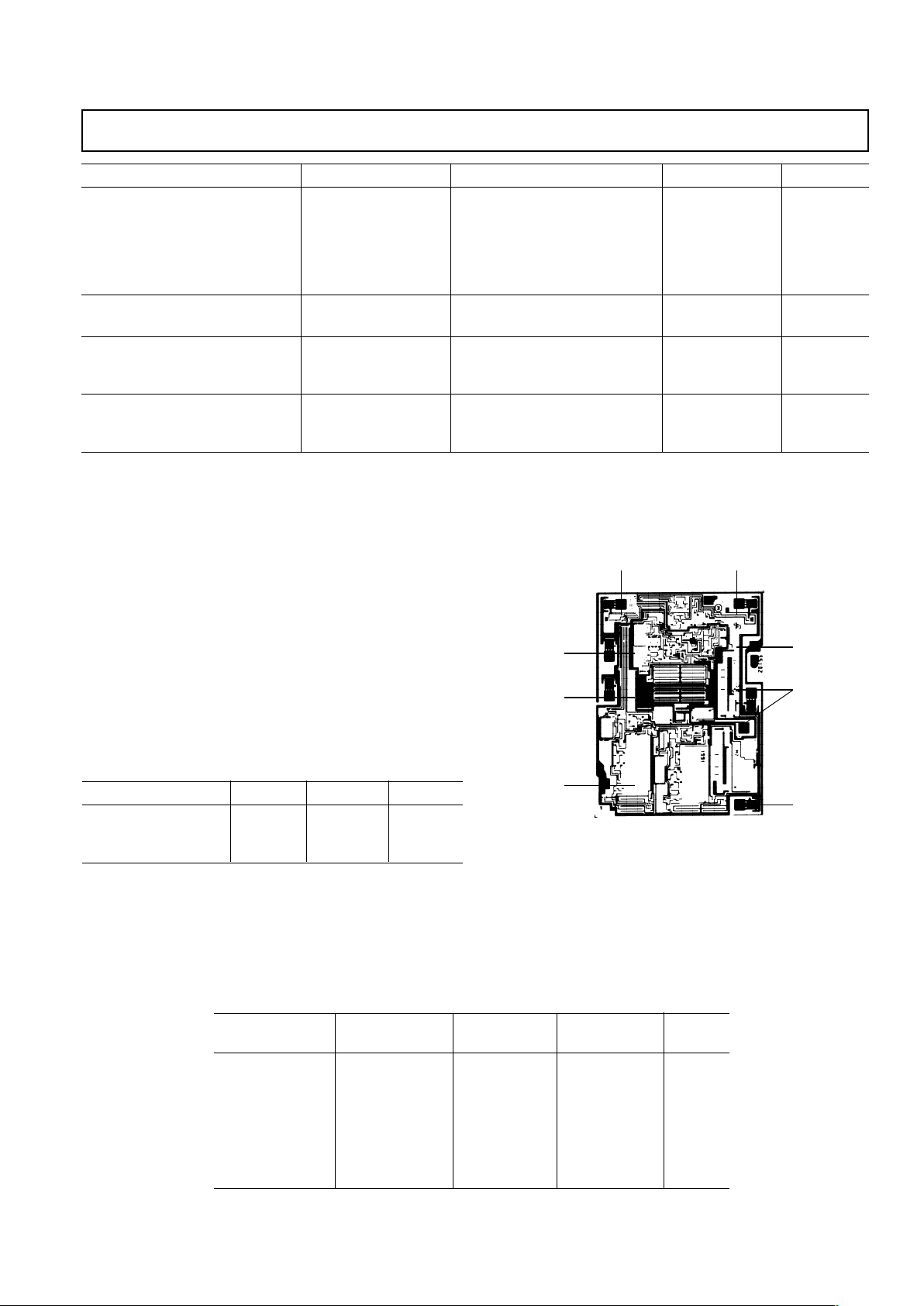

DICE CHARACTERISTICS

R

GAIN

1

R

GAIN

8

7 V+

6 V

OUT

5 REF

–IN 2

+IN 3

V– 4

AMP04 Die Size 0.075 × 0.99 inch, 7,425 sq. mils.

Substrate (Die Backside) Is Connected to V+.

Transistor Count, 81.

Page 6

AMP04

REV. B

–6–

APPLICATIONS

Common-Mode Rejection

The purpose of the instrumentation amplifier is to amplify the

difference between the two input signals while ignoring offset

and noise voltages common to both inputs. One way of judging

the device’s ability to reject this offset is the common-mode

gain, which is the ratio between a change in the common-mode

voltage and the resulting output voltage change. Instrumentation amplifiers are often judged by the common-mode rejection

ratio, which is equal to 20 × log

10

of the ratio of the user-selected

differential signal gain to the common-mode gain, commonly

called the CMRR. The AMP04 offers excellent CMRR, guaranteed to be greater than 90 dB at gains of 100 or greater. Input

offsets attain very low temperature drift by proprietary lasertrimmed thin-film resistors and high gain amplifiers.

Input Common-Mode Range Includes Ground

The AMP04 employs a patented topology (Figure 1) that uniquely

allows the common-mode input voltage to truly extend to zero

volts where other instrumentation amplifiers fail. To illustrate,

take for example the single supply, gain of 100 instrumentation

amplifier as in Figure 2. As the inputs approach zero volts, in

order for the output to go positive, amplifier A’s output (V

OA

)

must be allowed to go below ground, to –0.094 volts. Clearly

this is not possible in a single supply environment. Consequently

this instrumentation amplifier configuration’s input common-mode

voltage cannot go below about 0.4 volts. In comparison, the

AMP04 has no such restriction. Its inputs will function with a

zero-volt common-mode voltage.

IN(–)

IN(+)

INPUT BUFFERS

REF

100k

11k

11k

R

GAIN

V

OUT

100k

Figure 1. Functional Block Diagram

0.01V

+

20k

V

OUT

100k

–

4.7A

4.7A

20k

0.01V

5.2A

2127

100k

V

OB

V

OA

0V

B

A

V

IN

–0.094V

0V

Figure 2. Gain = 100 Instrumentation Amplifier

Input Common-Mode Voltage Below Ground

Although not tested and guaranteed, the AMP04 inputs are

biased in a way that they can amplify signals linearly with commonmode voltage as low as –0.25 volts below ground. This holds

true over the industrial temperature range from –40°C to +85°C.

Extended Positive Common-Mode Range

On the high side, other instrumentation amplifier configurations,

such as the three op amp instrumentation amplifier, can have

severe positive common-mode range limitations. Figure 3 shows

an example of a gain of 1001 amplifier, with an input commonmode voltage of 10 volts. For this circuit to function, V

OB

must

swing to 15.01 volts in order for the output to go to 10.01 volts.

Clearly no op amp can handle this swing range (given a 15 V

supply) as the output will saturate long before it reaches the

supply rails. Again the AMP04’s topology does not have this

limitation. Figure 4 illustrates the AMP04 operating at the same

common-mode conditions as in Figure 3. None of the internal

nodes has a signal high enough to cause amplifier saturation. As

a result, the AMP04 can accommodate much wider commonmode range than most instrumentation amplifiers.

100k

R

V

OB

V

OA

10.00V

A

10.01V

15.01V

5V

R

R

R

50A

100k

10.01V

200

B

Figure 3. Gain = 1001, Three Op Amp Instrumentation

Amplifier

+15V

–15V

100k

11k

V

OUT

100k

+15V

–15V

11k

100.1A

11.111V

10.01V

10.00V

100

10.01V

0.1A

10V

100A

Figure 4. Gain = 1000, AMP04

Page 7

AMP04

REV. B

–7–

Programming the Gain

The gain of the AMP04 is programmed by the user by selecting

a single external resistor—R

GAIN

:

Gain = 100 kΩ/R

GAIN

The output voltage is then defined as the differential input

voltage times the gain.

V

OUT

= (V

IN+

– V

IN–

) × Gain

In single supply systems, offsetting the ground is often desired

for several reasons. Ground may be offset from zero to provide

a quieter signal reference point, or to offset “zero” to allow a

unipolar signal range to represent both positive and negative

values.

In noisy environments such as those having digital switching,

switching power supplies or externally generated noise, ground

may not be the ideal place to reference a signal in a high accuracy system.

Often, real world signals such as temperature or pressure may

generate voltages that are represented by changes in polarity. In

a single supply system the signal input cannot be allowed to go

below ground, and therefore the signal must be offset to accommodate this change in polarity. On the AMP04, a reference

input pin is provided to allow offsetting of the input range.

The gain equation is more accurately represented by including

this reference input.

V

OUT

= (V

IN+

– V

IN–

) × Gain + V

REF

Grounding

The most common problems encountered in high performance

analog instrumentation and data acquisition system designs are

found in the management of offset errors and ground noise.

Primarily, the designer must consider temperature differentials

and thermocouple effects due to dissimilar metals, IR voltage drops, and the effects of stray capacitance. The problem

is greatly compounded when high speed digital circuitry, such

as that accompanying data conversion components, is brought

into the proximity of the analog section. Considerable noise and

error contributions such as fast-moving logic signals that easily

propagate into sensitive analog lines, and the unavoidable noise

common to digital supply lines must all be dealt with if the accuracy of the carefully designed analog section is to be preserved.

Besides the temperature drift errors encountered in the amplifier, thermal errors due to the supporting discrete components

should be evaluated. The use of high quality, low-TC components where appropriate is encouraged. What is more important,

large thermal gradients can create not only unexpected changes

in component values, but also generate significant thermoelectric voltages due to the interface between dissimilar metals such

as lead solder, copper wire, gold socket contacts, Kovar lead

frames, etc. Thermocouple voltages developed at these junctions

commonly exceed the TCV

OS

contribution of the AMP04.

Component layout that takes into account the power dissipation

at critical locations in the circuit and minimizes gradient effects

and differential common-mode voltages by taking advantage of

input symmetry will minimize many of these errors.

High accuracy circuitry can experience considerable error contributions due to the coupling of stray voltages into sensitive

areas, including high impedance amplifier inputs which benefit

from such techniques as ground planes, guard rings, and shields.

Careful circuit layout, including good grounding and signal

routing practice to minimize stray coupling and ground loops is

recommended. Leakage currents can be minimized by using

high quality socket and circuit board materials, and by carefully

cleaning and coating complete board assemblies.

As mentioned above, the high speed transition noise found in

logic circuitry is the sworn enemy of the analog circuit designer.

Great care must be taken to maintain separation between them

to minimize coupling. A major path for these error voltages will

be found in the power supply lines. Low impedance, load related

variations and noise levels that are completely acceptable in the

high thresholds of the digital domain make the digital supply

unusable in nearly all high performance analog applications.

The user is encouraged to maintain separate power and ground

between the analog and digital systems wherever possible,

joining only at the supply itself if necessary, and to observe

careful grounding layout and bypass capacitor scheduling in

sensitive areas.

Input Shield Drivers

High impedance sources and long cable runs from remote transducers in noisy industrial environments commonly experience

significant amounts of noise coupled to the inputs. Both stray

capacitance errors and noise coupling from external sources can

be minimized by running the input signal through shielded

cable. The cable shield is often grounded at the analog input

common, however improved dynamic noise rejection and a

reduction in effective cable capacitance is achieved by driving

the shield with a buffer amplifier at a potential equal to the

voltage seen at the input. Driven shields are easily realized with

the AMP04. Examination of the simplified schematic shows that

the potentials at the gain set resistor pins of the AMP04 follow

the inputs precisely. As shown in Figure 5, shield drivers are

easily realized by buffering the potential at these pins by a dual,

single supply op amp such as the OP213. Alternatively, applications with single-ended sources or that use twisted-pair cable

could drive a single shield. To minimize error contributions due

to this additional circuitry, all components and wiring should

remain in proximity to the AMP04 and careful grounding and

bypassing techniques should be observed.

V

OUT

1/2 OP213

1/2 OP213

Figure 5. Cable Shield Drivers

Page 8

AMP04

REV. B

–8–

Compensating for Input and Output Errors

To achieve optimal performance, the user needs to take into

account a number of error sources found in instrumentation

amplifiers. These consist primarily of input and output offset

voltages and leakage currents.

The input and output offset voltages are independent from one

another, and must be considered separately. The input offset

component will of course be directly multiplied by the gain of

the amplifier, in contrast to the output offset voltage that is

independent of gain. Therefore, the output error is the dominant factor at low gains, and the input error grows to become

the greater problem as gain is increased. The overall equation

for offset voltage error referred to the output (RTO) is:

V

OS

(RTO) = (V

IOS

× G) + V

OOS

where V

IOS

is the input offset voltage and V

OOS

the output offset

voltage, and G is the programmed amplifier gain.

The change in these error voltages with temperature must also

be taken into account. The specification TCV

OS

, referred to the

output, is a combination of the input and output drift specifications. Again, the gain influences the input error but not the

output, and the equation is:

TCV

OS

(RTO) = (TCV

IOS

× G) + TCV

OOS

In some applications the user may wish to define the error contribution as referred to the input, and treat it as an input error.

The relationship is:

TCV

OS

(RTI) = TCV

IOS

+ (TCV

OOS

/ G)

The bias and offset currents of the input transistors also have an

impact on the overall accuracy of the input signal. The input

leakage, or bias currents of both inputs will generate an additional offset voltage when flowing through the signal source

resistance. Changes in this error component due to variations

with signal voltage and temperature can be minimized if both

input source resistances are equal, reducing the error to a

common-mode voltage which can be rejected. The difference in

bias current between the inputs, the offset current, generates a

differential error voltage across the source resistance that should

be taken into account in the user’s design.

In applications utilizing floating sources such as thermocouples,

transformers, and some photo detectors, the user must take

care to provide some current path between the high impedance inputs and analog ground. The input bias currents of

the AMP04, although extremely low, will charge the stray

capacitance found in nearby circuit traces, cables, etc., and

cause the input to drift erratically or to saturate unless given a

bleed path to the analog common. Again, the use of equal resistance values will create a common input error voltage that is

rejected by the amplifier.

Reference Input

The V

REF

input is used to set the system ground. For dual supply operation it can be connected to ground to give zero volts

out with zero volts differential input. In single supply systems it

could be connected either to the negative supply or to a pseudoground between the supplies. In any case, the REF input must

be driven with low impedance.

Noise Filtering

Unlike most previous instrumentation amplifiers, the output

stage’s inverting input (Pin 8) is accessible. By placing a capacitor across the AMP04’s feedback path (Figure 6, Pins 6 and 8)

IN(–)

IN(+)

INPUT BUFFERS

REF

100k

LP

=

1

2 (100k) C

EXT

11k

11k

R

GAIN

V

OUT

100k

C

EXT

Figure 6. Noise Band Limiting

a single-pole low-pass filter is produced. The cutoff frequency

(f

LP

) follows the relationship:

fLP=

1

2π (100 kΩ) C

EXT

Filtering can be applied to reduce wide band noise. Figure 7a

shows a 10 Hz low-pass filter, gain of 1000 for the AMP04.

Figures 7b and 7c illustrate the effect of filtering on noise. The

photo in Figure 7b shows the output noise before filtering. By

adding a 0.15 µF capacitor, the noise is reduced by about a

factor of 4 as shown in Figure 7c.

100k

+15V

–15V

0.15F

Figure 7a. 10 Hz Low-Pass Filter

10

90

100

0%

5mV

10ms

Figure 7b. Unfiltered AMP04 Output

Page 9

AMP04

REV. B

–9–

10

90

100

0%

1mV

2s

Figure 7c. 10 Hz Low-Pass Filtered Output

Power Supply Considerations

In dual supply applications (for example ±15 V) if the input is

connected to a low resistance source less than 100 Ω, a large

current may flow in the input leads if the positive supply is

applied before the negative supply during power-up. A similar

condition may also result upon a loss of the negative supply. If

these conditions could be present in you system, it is recommended that a series resistor up to 1 kΩ be added to the input

leads to limit the input current.

This condition can not occur in a single supply environment

as losing the negative supply effectively removes any current

return path.

Offset Nulling in Dual Supply

Offset may be nulled by feeding a correcting voltage at the V

REF

pin (Pin 5). However, it is important that the pin be driven with

a low impedance source. Any measurable resistance will degrade

the amplifier’s common-mode rejection performance as well as

its gain accuracy. An op amp may be used to buffer the offset

null circuit as in Figure 8.

8

7

6

5

1

2

3

4

AMP04

REF

V+

V–

5V–

+

INPUT

+5V

–5V

50k

100

50k

5mV

ADJ

RANGE

*

*OP90 FOR LOW POWER

OP113 FOR LOW DRIFT

–5V

OUTPUT

R

G

+5V

–5V

Figure 8. Offset Adjust for Dual Supply Applications

Offset Nulling in Single Supply

Nulling the offset in single supply systems is difficult because

the adjustment is made to try to attain zero volts. At zero volts

out, the output is in saturation (to the negative rail) and the

output voltage is indistinguishable from the normal offset error.

Consequently the offset nulling circuit in Figure 9 must be used

with caution.

First, the potentiometer should be adjusted to cause the output

to swing in the positive direction; then adjust it in the reverse

direction, causing the output to swing toward ground, until

the output just stops changing. At that point the output is at

the saturation limit.

8

7

6

5

1

2

3

4

AMP04

5V

INPUT

100

OUTPUT

R

G

OP113

50k

5V

Figure 9. Offset Adjust for Single Supply Applications

Alternative Nulling Method

An alternative null correction technique is to inject an offset

current into the summing node of the output amplifier as in

Figure 10. This method does not require an external op amp.

However, the drawback is that the amplifier will move off its

null as the input common-mode voltage changes. It is a less

desirable nulling circuit than the previous method.

IN(–)

IN(+)

INPUT BUFFERS

REF

100k

11k

11k

R

GAIN

V

OUT

100k

V–

V+

Figure 10. Current Injection Offsetting Is Not

Recommended

Page 10

AMP04

REV. B

–10–

APPLICATION CIRCUITS

Low Power Precision Single Supply RTD Amplifier

Figure 11 shows a linearized RTD amplifier that is powered

from a single 5 volt supply. However, the circuit will work up to

36 volts without modification. The RTD is excited by a 100 µA

constant current that is regulated by amplifier A (OP295). The

0.202 volts reference voltage used to generate the constant current

is divided down from the 2.500 volt reference. The AMP04 amplifies the bridge output to a 10 mV/°C output coefficient.

R10

100

R2

26.7k

R

SENSE

1k

V

OUT

FULL-SCALE

ADJ

0 4.00V

(0C TO 400C)

LINEARITY

ADJ.

(@1/2 FS)

NOTES: ALL RESISTORS 0.5%, 25 PPM/ C

ALL POTENTIOMETERS 25 PPM/ C

AMP04

R8

383

R9

50

C1

0.47F

1

7

3

2

4

5

8

6

1/2

OP295

1/2

OP295

R1

26.7k

500

R4

100

R6

11.5k

R5

1.02k

OUT

REF43 IN

GND

2.5V

R7

121k

50k

4

5

6

8

7

5V

2

5V

C2

0.1F

C3

0.1F

RTD

100

0.202V

6

4

1

2

3

R3

BALANCE

5V

A

B

Figure 11. Precision Single Supply RTD Thermometer

Amplifier

The RTD is linearized by feeding a portion of the signal back to

the reference circuit, increasing the reference voltage as the

temperature increases. When calibrated properly, the RTD’s

nonlinearity error will be canceled.

To calibrate, either immerse the RTD into a zero-degree ice

bath or substitute an exact 100 Ω resistor in place of the RTD.

Then adjust bridge BALANCE potentiometer R3 for a 0 volt

output. Note that a 0 volt output is also the negative output swing

limit of the AMP04 powered with a single supply. Therefore, be

sure to adjust R3 to first cause the output to swing positive and

then back off until the output just stops swinging negatively.

Next, set the LINEARITY ADJ potentiometer to the midrange.

Substitute an exact 247.04 Ω resistor (equivalent to 400°C

temperature) in place of the RTD. Adjust the FULL-SCALE

potentiometer for a 4.000 volts output.

Finally substitute a 175.84 Ω resistor (equivalent to 200°C

temperature), and adjust the LINEARITY ADJ potentiometer

for a 2.000 volts at the output. Repeat the full-scale and the

half-scale adjustments as needed.

When properly calibrated, the circuit achieves better than

±0.5°C accuracy within a temperature measurement range

from 0°C to 400°C.

Precision 4-20 mA Loop Transmitter with Noninteractive Trim

Figure 12 shows a full bridge strain gage transducer amplifier

circuit that is powered off the 4-20 mA current loop. The AMP04

amplifies the bridge signal differentially and is converted to a

current by the output amplifier. The total quiescent current

drawn by the circuit, which includes the bridge, the amplifiers,

and the resistor biasing, is only a fraction of the 4 mA null

current that flows through the current-sense resistor R

SENSE

.

The voltage across R

SENSE

feeds back to the OP90’s input,

whose common-mode is fixed at the current summing reference

voltage, thus regulating the output current.

With no bridge signal, the 4 mA null is simply set up by the

50 kΩ NULL potentiometer plus the 976 kΩ resistors that

inject an offset that forces an 80 mV drop across R

SENSE

. At a

50 mV full-scale bridge voltage, the AMP04 amplifies the

voltage-to-current converter for a full-scale of 20 mA at the

output. Since the OP90’s input operates at a constant 0 volt

common-mode voltage, the null and the span adjustments do

not interact with one another. Calibration is simple and easy

with the NULL adjusted first, followed by SPAN adjust. The

entire circuit can be remotely placed, and powered from the

4-20 mA 2-wire loop.

R

SENSE

20

U1

AMP04

5k

10-TURN

2.49k

1

7

3

2

4

5

8

6

U2

OP90

50mV

FS

0.22F

97.6k

3

2

B

976k

50k

HP

5082-2810

220pF

4

6

100k

5%

2k

5%

T1P29A

0.1F

5.00V

OUT

REF02

N

GND

U3

1N4002

4mA NULL

13.3k

15.8k

3500 STRAIN

GAGE BRIDGE

7

20mA

SPAN

6

2

4

+V

S

12V TO 36V

R

LOAD

100

4-20mA

I

NULL

+ I

SPAN

UNLESS OTHERWISE SPECIFIED, ALL RESISTORS 1%

OR BETTER POTENTIOMETER < 50 PPM/C

Figure 12. Precision 4-20 mA Loop Transmitter Features Noninteractive Trims

Page 11

AMP04

REV. B

–11–

4-20 mA Loop Receiver

At the receiving end of a 4-20 mA loop, the AMP04 makes a

convenient differential receiver to convert the current back to

a usable voltage (Figure 13). The 4-20 mA signal current passes

through a 100 Ω sense resistor. The voltage drop is differentially

amplified by the AMP04. The 4 mA offset is removed by the

offset correction circuit.

AMP04

1k

3

2

4

6

V

OUT

7

+15V

–15V

100

1%

1N4002

WIRE

RESISTANCE

1k

4–20mA

4–20mA

TRANSMITTER

100k

POWER

SUPPLY

0.15F

4–20mA

0–1.6V FS

5

8

1

OP177

2

3

AD589

–15V

6

27k

10k

–0.400V

Figure 13. 4-to-20 mA Line Receiver

Low Power, Pulsed Load-Cell Amplifier

Figure 14 shows a 350 Ω load cell that is pulsed with a low duty

cycle to conserve power. The OP295’s rail-to-rail output capability allows a maximum voltage of 10 volts to be applied to the

bridge. The bridge voltage is selectively pulsed on when a measurement is made. A negative-going pulse lasting 200 ms should

be applied to the MEASURE input. The long pulsewidth is

necessary to allow ample settling time for the long time constant

of the low-pass filter around the AMP04. A much faster settling

time can be achieved by omitting the filter capacitor.

AMP04

3

2

V

OUT

7

6

IN

GND

OUT

REF01

1/2

OP295

MEASURE

1N4148

10k1k

50k

12V

5

4

330

0.22F

8

1

2N3904

12V

350

Figure 14. Pulsed Load Cell Bridge Amplifier

Single Supply Programmable Gain Instrumentation Amplifier

Combining with the single supply ADG221 quad analog switch,

the AMP04 makes a useful programmable gain amplifier that

can handle input and output signals at zero volts. Figure 15

shows the implementation. A logic low input to any of the gain

control ports will cause the gain to change by shorting a gainset resistor across AMP04’s Pins 1 and 8. Trimming is required

at higher gains to improve accuracy because the switch ONresistance becomes a more significant part of the gain-set

resistance. The gain of 500 setting has two switches connected

in parallel to reduce the switch resistance.

8

7

6

5

1

2

3

4

V–

REF

V+

R

G

R

G

AMP04

ADG221

13

10

9

7

8

15

16

2

1

12

5V TO

30V

V

OUT

0.22F

5

4

11

6

14

3

715

10.9k

200

200

0.1F10F

5V TO 30V

GAIN OF 500

GAIN OF 100

GAIN OF 10

WR

GAIN

CONTROL

0.1F

INPUT

100k

Figure 15. Single Supply Programmable Gain Instrumentation Amplifier

The switch ON resistance is lower if the supply voltage is 12 volts

or higher. Additionally, the overall amplifier’s temperature coefficient also improves with higher supply voltage.

Page 12

AMP04

REV. B

–12–

120

0

200

60

20

–160

40

–200

100

80

16080400 120–40–80–120

NUMBER OF UNITS

INPUT OFFSET VOLTAGE – V

TA = 25C

V

S

= 5V

V

CM

= 2.5V

BASED ON 300 UNITS

3 RUNS

Figure 16. Input Offset (V

IOS

) Distribution @ 5 V

2.500.250 2.251.751.501.25 2.001.000.750.50

TCV

IOS

– V/C

120

0

60

20

40

100

80

NUMBER OF UNITS

300 UNITS

V

S

= 5V

V

CM

= 2.5V

Figure 17. Input Offset Drift (TCV

IOS

) Distribution @ 5 V

2.0–1.6–2.0 1.60.80.40 1.2–0.4–0.8–1.2

OUTPUT OFFSET – mV

120

0

60

20

40

100

80

NUMBER OF UNITS

TA = 25C

V

S

= 5V

V

CM

= 2.5V

BASED ON 300 UNITS

3 RUNS

Figure 18. Output Offset (V

OOS

) Distribution @ 5 V

0.5–0.4–0.5 0.40.20.10 0.3–0.1–0.2–0.3

INPUT OFFSET VOLTAGE – mV

120

0

60

20

40

100

80

NUMBER OF UNITS

TA = 25C

V

S

= 15V

V

CM

= 0V

BASED ON 300 UNITS

3 RUNS

Figure 19. Input Offset (V

IOS

) Distribution @ ±15 V

2.500.250 2.251.751.501.25 2.001.000.750.50

TCV

IOS

–

V/C

120

0

60

20

40

100

80

NUMBER OF UNITS

300 UNITS

V

S

= 15V

V

CM

= 0V

Figure 20. Input Offset Drift (TCV

IOS

) Distribution @ ±15 V

5–4–542103–1–2–3

OUTPUT OFFSET – mV

120

0

60

20

40

100

80

NUMBER OF UNITS

TA = 25C

V

S

= 15V

V

CM

= 0V

BASED ON 300 UNITS

3 RUNS

Figure 21. Output Offset (V

OOS

) Distribution @ ±15 V

Page 13

AMP04

REV. B

–13–

202018141210 16864

TCV

OOS

– V/C

120

0

60

20

40

100

80

NUMBER OF UNITS

300 UNITS

V

S

= 5V

V

CM

= 0V

Figure 22. Output Offset Drift (TCV

OOS

) Distribution

@ 5 V

TEMPERATURE – C

5.0

3.8

100

4.4

4.0

–25

4.2

–50

4.8

4.6

7550250

OUTPUT VOLTAGE SWING – Volts

VS = 5V

RL = 100k

RL = 2k

RL = 10k

Figure 23. Output Voltage Swing vs. Temperature

@ 5 V

40

0

100

10

5

–25–50

20

15

25

30

35

7550250

INPUT BIAS CURRENT – nA

TEMPERATURE – C

VS = 5V

VS = 15V

VS = 5V, V

CM

= 2.5V

V

S

= 15V, V

CM

= 0V

Figure 24. Input Bias Current vs. Temperature

120

0

60

20

40

100

80

NUMBER OF UNITS

300 UNITS

V

S

= 15V

V

CM

= 0V

20218141210 16864

TCV

OOS

– V/C

22 24

Figure 25. Output Offset Drift (TCV

OOS

) Distribution

@

±

15 V

15.0

–15.1

100

–14.8

–15.0

–25

–14.9

–50

12.5

–14.7

–14.6

13.0

13.5

14.0

14.5

7550250

TEMPERATURE – C

+OUTPUT SWING – Volts

VS = 5V

RL = 100k

RL = 2k

RL = 10k

–OUTPUT SWING – Volts

RL = 2k

RL = 10k

RL = 100k

Figure 26. Output Voltage Swing vs. Temperature

@

+15 V

8

6

0

4

2

100–25–50 7550250

INPUT OFFSET CURRENT – nA

TEMPERATURE – C

VS = 5V

VS = 15V

VS = 5V, V

CM

= 2.5V

V

S

= 15V, V

CM

= 0V

Figure 27. Input Offset Current vs. Temperature

Page 14

AMP04

REV. B

–14–

50

30

–20

1k 1M100k10k100

40

10

20

–10

0

FREQUENCY – Hz

VOLTAGE GAIN – dB

G = 1

G = 100

G = 10

TA = 25C

V

S

= 15V

Figure 28. Closed-Loop Voltage Gain vs. Frequency

1 10 100k10k1k100

FREQUENCY – Hz

100

–20

60

80

0

40

COMMON-MODE REJECTION – dB

20

120

TA = 25C

V

S

= 15V

V

CM

= 2V p-p

G = 100

G = 10

G = 1

Figure 29. Common-Mode Rejection vs. Frequency

10 100k10k1k100

FREQUENCY – Hz

100

60

80

0

40

POWER SUPPLY REJECTION – dB

20

120

TA = 25C

VS = 15V

VS = 1V

G = 100

G = 10

G = 1

140

1M

Figure 30. Positive Power Supply Rejection vs. Frequency

100

–20

1k 100k10k100

60

80

0

40

FREQUENCY – Hz

OUTPUT IMPEDANCE –

10

20

120

VS = 15V

VS = 5V

TA = 25C

G = 1

Figure 31. Closed-Loop Output Impedance vs. Frequency

COMMON-MODE REJECTION – dB

120

70

50

110 1k100

100

60

80

90

110

VOLTAGE GAIN – G

TA = 25C

V

S

= 15V

V

CM

= 2V p-p

Figure 32. Common-Mode Rejection vs. Voltage Gain

10 100k10k1k100

FREQUENCY – Hz

100

60

80

0

40

POWER SUPPLY REJECTION – dB

20

120

TA = 25C

VS = 15V

VS = 1V

G = 100

G = 10

G = 1

140

1M

Figure 33. Negative Power Supply Rejection vs. Frequency

Page 15

AMP04

REV. B

–15–

VOLTAGE GAIN – G

1

110

TA = 25C

VS = 15V

= 100Hz

VOLTAGE NOISE – nV/ Hz

10

100

1k

100 1k

Figure 34. Voltage Noise Density vs. Gain

100

100 10k10

60

80

0

40

FREQUENCY – Hz

1

20

120

TA = 25C

VS = 15V

G = 100

140

VOLTAGE NOISE DENSITY – nV/ Hz

1k

Figure 35. Voltage Noise Density vs. Frequency

1200

0

100

600

200

–25

400

–50

1000

800

7550250

TEMPERATURE – C

SUPPLY CURRENT – A

VS = 15V

V

S

= 5V

Figure 36. Supply Current vs. Temperature

VOLTAGE GAIN – G

1

110

TA = 25C

V

S

= 15V

= 1kHz

VOLTAGE NOISE – nV/ Hz

10

100

1k

100 1k

Figure 37. Voltage Noise Density vs. Gain, f = 1 kHz

10

90

100

0%

20mV

1s

VS = 15V, GAIN = 1000, 0.1 TO 10 Hz BANDPASS

Figure 38. Input Noise Voltage

1k 100k10k100

0

LOAD RESISTANCE –

OUTPUT VOLTAGE – V

10

TA = 25C

V

S

= 15V

2

4

6

8

10

12

14

16

Figure 39. Maximum Output Voltage vs. Load Resistance

Page 16

AMP04

REV. B

–16–

C00250–0–11/00 (rev. B)

PRINTED IN U.S.A.

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

8-Lead Plastic DIP (N-8)

SEATING

PLANE

0.060 (1.52)

0.015 (0.38)

0.210

(5.33)

MAX

0.022 (0.558)

0.014 (0.356)

0.160 (4.06)

0.115 (2.93)

0.070 (1.77)

0.045 (1.15)

0.130

(3.30)

MIN

8

14

5

PIN 1

0.280 (7.11)

0.240 (6.10)

0.100 (2.54)

BSC

0.430 (10.92)

0.348 (8.84)

0.195 (4.95)

0.115 (2.93)

0.015 (0.381)

0.008 (0.204)

0.325 (8.25)

0.300 (7.62)

8-Lead Cerdip (Q-8)

1

4

85

0.310 (7.87)

0.220 (5.59)

PIN 1

0.005 (0.13)

MIN

0.055 (1.4)

MAX

0.100 (2.54) BSC

15°

0°

0.320 (8.13)

0.290 (7.37)

0.015 (0.38)

0.008 (0.20)

SEATING

PLANE

0.200 (5.08)

MAX

0.405 (10.29) MAX

0.150

(3.81)

MIN

0.200 (5.08)

0.125 (3.18)

0.023 (0.58)

0.014 (0.36)

0.070 (1.78)

0.030 (0.76)

0.060 (1.52)

0.015 (0.38)

8-Lead Narrow-Body SO (SO-8)

85

41

0.1968 (5.00)

0.1890 (4.80)

0.2440 (6.20)

0.2284 (5.80)

PIN 1

0.1574 (4.00)

0.1497 (3.80)

0.0500 (1.27)

BSC

0.0688 (1.75)

0.0532 (1.35)

SEATING

PLANE

0.0098 (0.25)

0.0040 (0.10)

0.0192 (0.49)

0.0138 (0.35)

0.0098 (0.25)

0.0075 (0.19)

0.0500 (1.27)

0.0160 (0.41)

8

0

0.0196 (0.50)

0.0099 (0.25)

45

Loading...

Loading...