Page 1

PRELIMINARY

Am79C973/Am79C975

PCnet™-FAST III

Single-Chip 10/100 Mbps PCI Ethernet Controller wi th Integrated PHY

DISTINCTIVE CHARACTERISTICS

■ Single-chip PCI-to-Wire Fast Ethernet controller

— 32-bit glueless PCI host interface

— Supports PCI clock frequency fr om DC to

33 MHz independent of network clock

— Supports network operation with PCI clock

from 15 MHz to 33 MHz

— High performance bus mastering

architecture with integrated Direct Memory

Access (DMA) Buffer Management Unit for

low CPU and bus utilization

— PCI specification revision 2.2 compliant

— Supports PCI Subsystem/Subvendor ID/

Vendor ID pr ogramming through the

EEPROM interface

— Supports both PCI 5.0 V and 3.3 V signaling

environments

— Plug and Play compatible

— Big endian and little endian byte alignments

supported

■ Fully Integrated 10/100 Mbps Physical Layer

Interface (PHY)

— Conforms to IEEE 802.3 standard for

10BASE-T, 100BASE-TX, and 100BASE-FX

interfaces

— Integrated 10BASE-T transceiver with on-

chip filtering

— Fully integrated MLT-3 encoder/decoder for

100BASE-TX

— Provides a PECL interface for 100BASE-FX

fiber implementations

— Full-duplex capability for 10BASE-T and

100BASE-TX

— IEEE 802.3u Auto-Negotiation between 10

Mbps and 100 Mbps, half- and full-duplex operation

■ Dual-speed CSMA/CD (10 Mbps and 100 Mbps)

Media Access Controller (MAC) compliant with

IEEE/ANSI 802.3 and Blue Book Ethernet

standards

■ Supports PC98/PC99 and Wired for

Management baseline specifications

— Full OnNow support including pattern

matching and link status wake-up events

— Implements AMD’s patented Magic Packet™

technology for remote wake-up & power-on

— Magic Packet mode and the physical address

loaded from EEPROM at power up without

requiring PCI clock

— Supports PCI Bus Power Management

Interface Specification Revision 1.1

— Supports Advanced Configuration and

Power Interface (ACPI) Specification Version

1.0

— Supports Network Device Class Power

Management Specification Version 1.0a

■ Serial Management Interface enables remote

alerting of system management events

2

— Inter-IC (I

— System Management Bus (SMBus)

compliant signaling interface and register

access protocol

— Optional interrupt pin simplifies software

interface

■ Large independent internal TX and RX FIFOs

— Programmable FIFO watermarks fo r both TX

and RX operations

— RX frame queuing for high latency PCI bus

host operation

— Programmable allocation of buffer space

between RX and TX queues

■ EEPROM interface supports jumperless design

and provides through-chip programming

— Supports extensive programmability of

device operation through EEPROM mapping

■ Supports up to 1 megabyte (Mbyte) optional

Boot PROM and Flash for diskless node

application

■ Extensive programmable internal/external

loopback capabilities

■ Extensive programmable LED status support

C) compliant electrical interface

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate thi s product. AMD reserves t he right to chan ge or discontinue work o n this proposed

product without notice.

i

Publication# 21510 Rev: E Amendment/0

Issue Date: August 2000

i

i

Page 2

PRELIMINARY

■ Look-Ahead Packet Processing (LAPP) data

handling technique reduces system overhead

by allowing protocol analysis to begin before

the end of a receive frame

■ Includes Programmable Inter Packet Gap (IPG)

to address less network aggressive MAC

controllers

■ Offers the Modified Back-Off algorithm to

address the Ethernet Capture Effect

■ IEEE 1149.1-compliant JTAG Boundary Scan

test access port interface and NAND tree test

GENERAL DESCRIPTION

The Am79C973 and Am79C975 controllers are singlechip 32-bit full- duplex, 10/100-Megabit per second

(Mbps) fully integrated PCI-to -Wire Fast Ethernet system solution, designed to address high-performanc e

system application requirements. They are flexible bus

mastering device that can be used in any applic ation,

including network-ready PCs and bridge/router designs. The bus master archi tecture pr ovides high dat a

throughput and low CPU and system bus utilization.

The Am79C973 and Am79C975 controllers are fabricated with advanced low-power 3.3-V CMOS process

to provide low operating current for power sensitive applications.

The third generation Am 79C973 and A m79C975 Fast

Ethernet controll ers also have several enhance ments

over their predecessors, the Am79C971 and

Am79C972 devices. Besides integrating the comp lete

10/100 Physical Layer (PHY) interface, they further reduce system implementation cost by integrating the

SRAM buffers on chip.

The Am79C973 and Am79C975 controllers contain 12kilobyte (Kbyte) buffers, the largest of their class in 10/

100 Mbps Ethernet controllers. The large internal buffers are fully programmable between t he RX and TX

queues for optimal performance.

The Am79C973 an d Am79C975 contr ollers are also

compliant with PC98/PC99 and Wired for Management

specifications. They fully suppor t Microsoft’s OnNow

and ACPI specifications, which are backward compatible with Magic Packet technology and compliant with

the PCI Bus Power Management Interface Specification by supporting th e four power management states

(D0, D1, D2, and D3), the optional PME

necessary configuration and data registers.

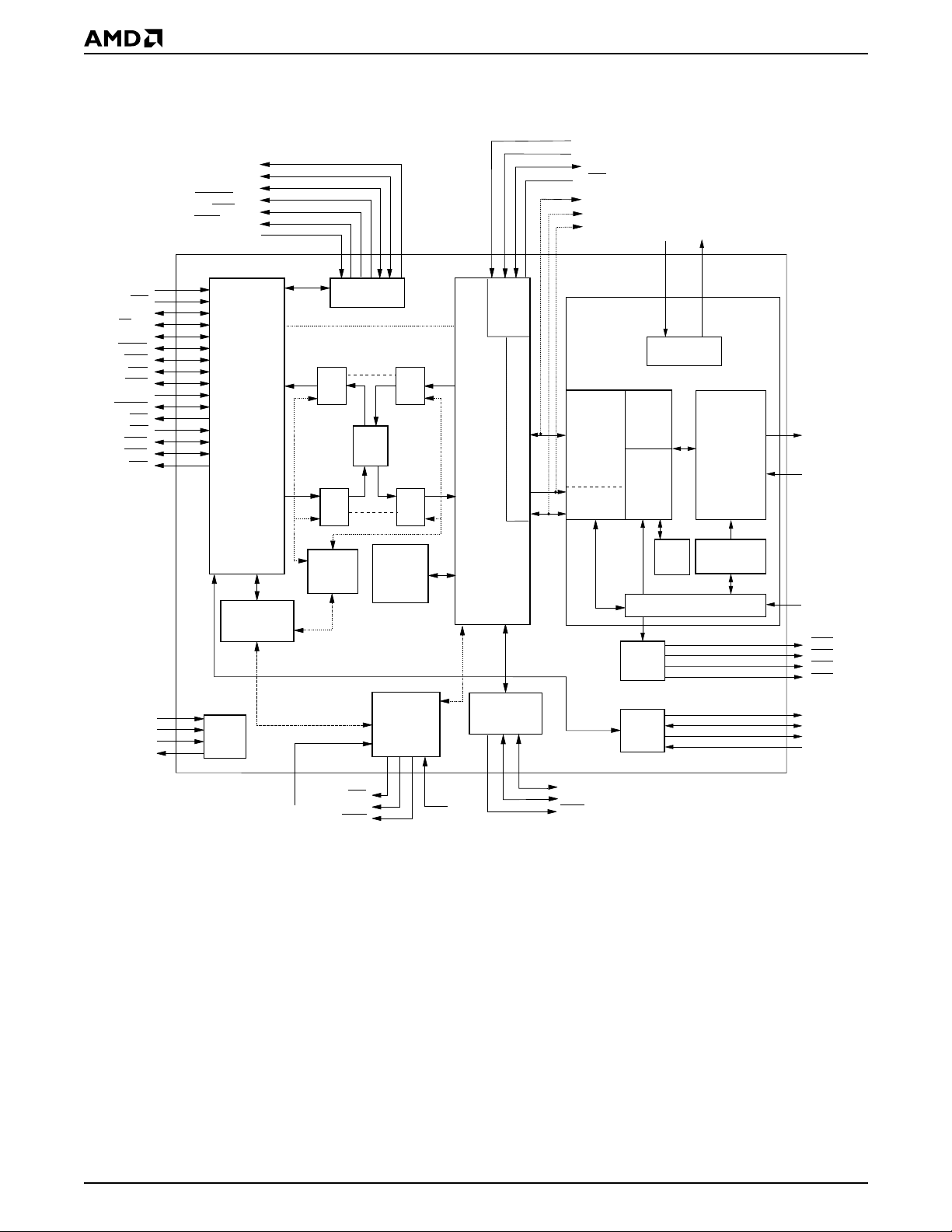

The Am79C973 and Am79C975 controllers are complete Ethernet nod es integrated into a s ingle VLSI device. It contains a bus interface unit, a Direct Mem ory

Access (DMA) Buffer Management Unit, an ISO/IEC

8802-3 (IEEE 802.3)- compliant Media Access Control-

pin, and the

mode for board-level production connectivity

test

■ Compatible with the existing PCnet Family

driver/diagnostic software

■ Software compatible with AMD PCnet Family

and LANCE™/C-LANCE™ register and

descriptor architecture

■ Available in 160-pin PQFP and 176-pin TQFP

packages

■ Advanced +3.3 V CMOS process technology for

low power operation

ler (MAC), a large Transmit FIFO and a large Receive

FIFO, and an IEEE 802.3-compliant 10/100 Mbps PHY .

The integrated 10/100 PHY unit of the Am79C973 and

Am79C975 controll ers implement the c omplete physical layer for 10BASE-T and the Physical Codin g Sublayer (PCS), Physical Medium Attachment (PMA), and

Physical Medium Dependent (PMD) functionality for

100BASE-TX, incl uding MLT-3 encoding/ decoding. It

also supports 100BAS E-FX operation by providing a

Pseudo-ECL (PECL) interface for direct connection to

a fiber optic transceiver module. The internal 10/100

PHY implemen ts Auto-Negotiation for twisted-pa ir

(10T/100TX) operation by using a modified 10BASE-T

link integrity test pulse sequence as defined in the

IEEE 802.3u specifi catio n. The Auto-Negotiat ion fun ction automatically configures the controller to operate

at the maximum performance level supported across

the network link.

The Am79C975 controller also implements a Serial

Management Interface in addition to the advanced

management features offered with the Am79C973 controller. The Serial Management Interface is based on

the industry standard Inter-IC (I

agement Bus (SMBus) specifications and enables a

system to communicate with another network station

for remote monitoring and alerting of local system management parameters and events. This simple yet powerful Serial Management Interface is capable of

communicating within the system and over the network

during normal operation or in low-power modes, even if

the device is not initialized or set up for transmit or receive operation by the network software driver.

The 32-bit multiplexed bus interface unit provides a direct interface to the PCI loc al bus, simplifying the

design of an Ethernet node in a PC system. The

Am79C973 and Am79C975 controllers provide the

complete interface to an Ex pansi on ROM or F lash device allowing add-on card desig ns with only a single

load per PCI bus interface pin. With their built-in s upport for both little and big endian byte alignment, the

2

C) and System Man-

2 Am79C973/Am79C975

Page 3

PRELIMINARY

controllers also address non-PC applications. The

Am79C973 and Am79C975 controllers’ advanced

CMOS design allows the bus interface to be connected

to either a +5-V or a + 3.3-V signaling environment. A

compliant IEEE 1149.1 JTAG test interface for boardlevel testing is also provided, as well as a NAND tree

test structure for those systems that cannot support the

JTAG interface.

The Am79C973 and Am79C975 controllers support

auto-configuration in the PCI co nfiguration spac e. Additional Am79C973 and Am 79C975 controll er co nfiguration parameters, including the un ique IEEE physical

address, can be rea d from an external non -volatile

memory ( EEPROM) immediately following system reset.

In addition, the Am79C973 an d Am7 9C97 5 co ntr oller s

provide programmable on-chip LED drivers for transmit, receive, collision, link integrity, Magic Packet status, activity, link active, address match, full-duplex, 10

Mbps or 100 Mbps, or jabber status.

The Am79C973 and Am79C975 co ntrollers are register compatible with the LANCE™ (Am7990) Ethernet

controlle r, the C-LANCE™ (Am79C90) Ethernet controller, and all Ethernet controllers in the PCnet™ Family, except ILACC™ (Am79C900), including the PCnetISA™ (Am79C960), PCnet-ISA+™ (Am79C961),

PCnet-ISA II™ (Am79C961A), PCnet-32™

(Am79C965), PCnet-PCI™ (Am79C970),

PCnet-PCI II™ (Am79C970A), PCnet-FAST™

(Am79C971), and PCnet-FAST+™ (Am79C972). The

Buffer Management Unit supports the LANCE and

PCnet descriptor software models.

The Am79C973 and Am79C 975 c ont ro ller s ar e id eal ly

suited for LAN on the motherboard, network adapter

card, and embedded designs. It is available in a 160pin Plastic Quad Flat Pack (PQFP) package and also in

a 176-pin Thin Quad Flat Pack (TQFP) package for

form factor sensitive designs.

Am79C973/Am79C975 3

Page 4

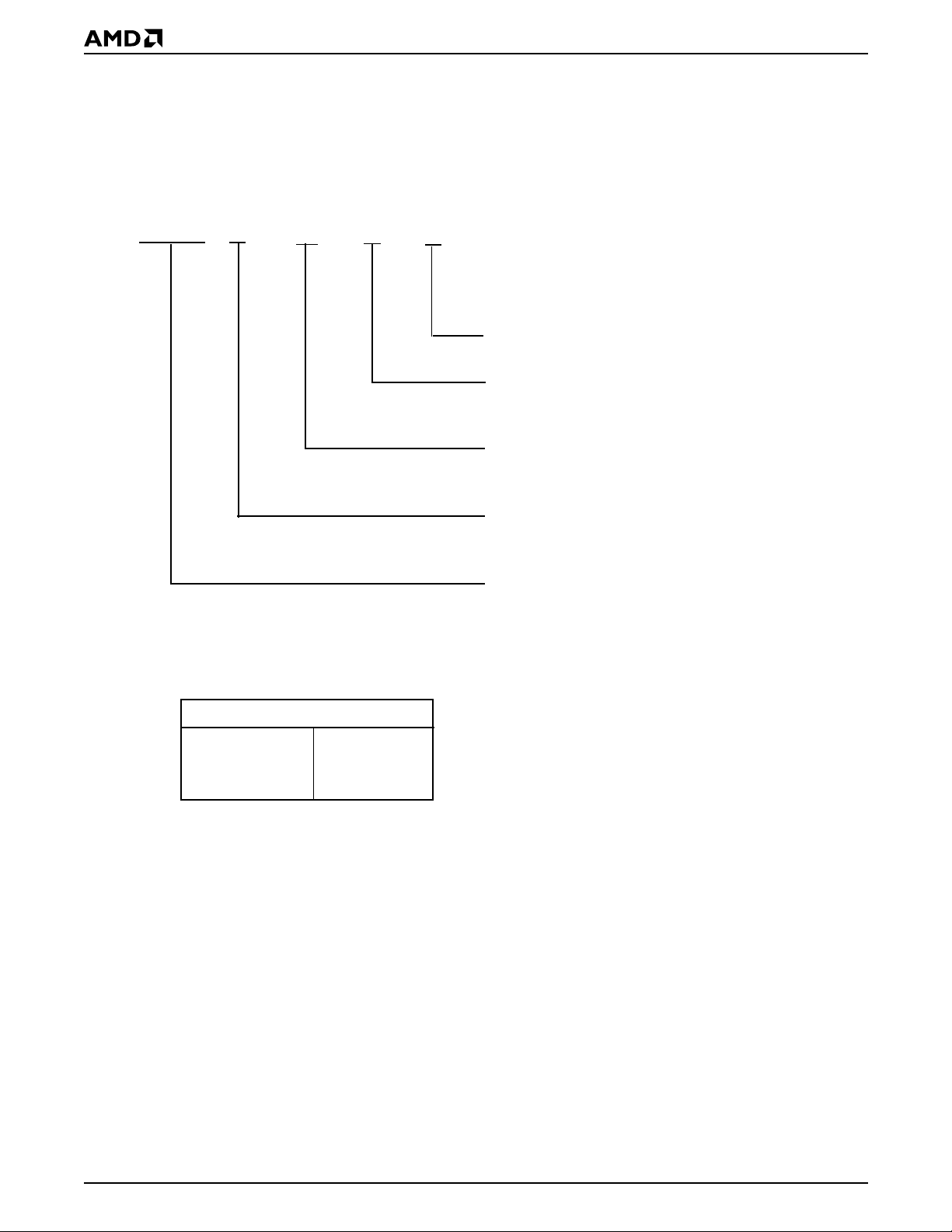

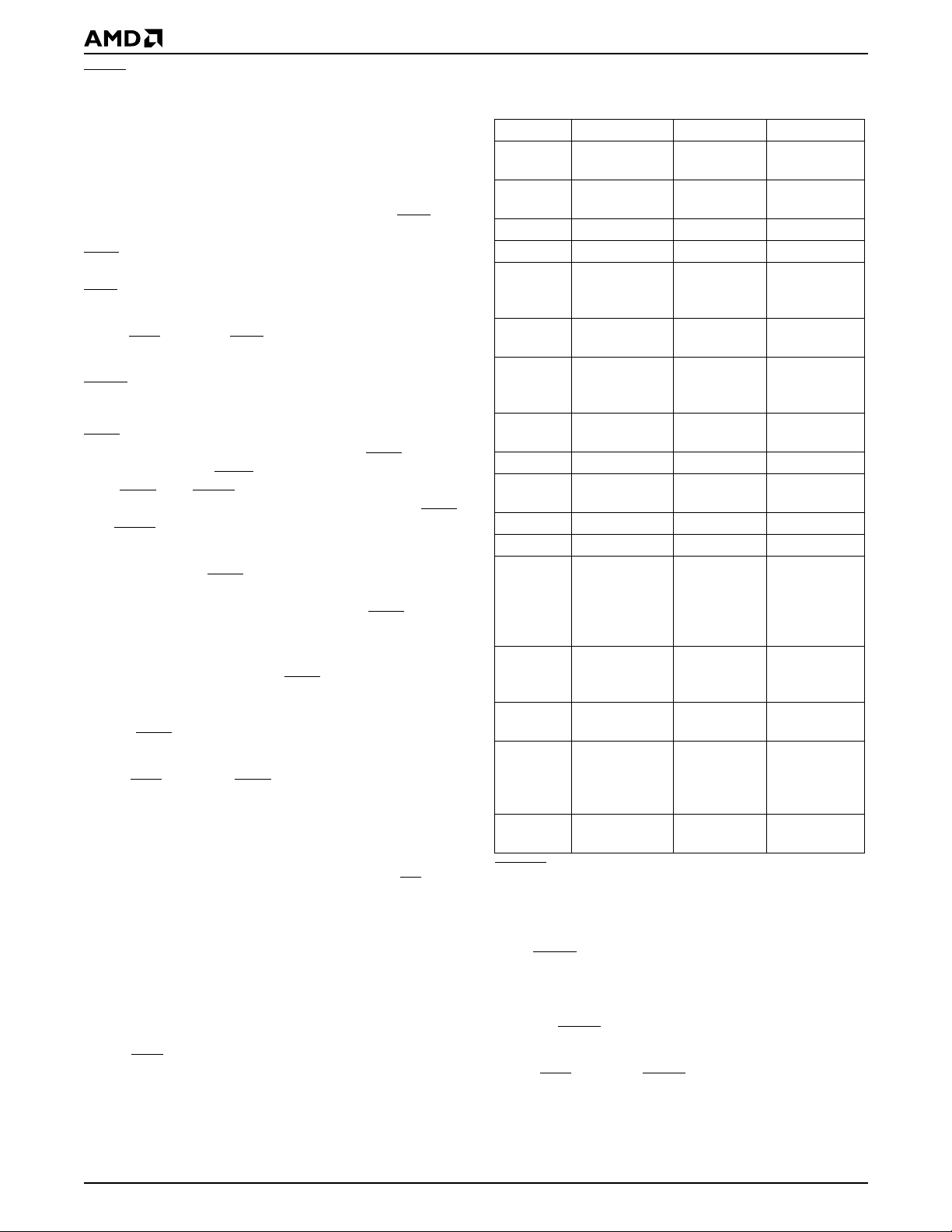

BLOCK DIAGRAM

EBUA_EBA[7:0]

EBDA[15:8]

EBD[7:0]

EROMCS

AS_EBOE

EBWE

EBCLK

PRELIMINARY

MIIRXFRTGE

MIIRXFRTGD

SFBD

EAR

RXD[3:0],TXD[3:0]

MDIO

MDC

XTAL1 XTAL2

CLK

RST

AD[31:0]

C/BE[3:0]

PAR

FRAME

TRDY

IRDY

STOP

IDSEL

DEVSEL

REQ

GNT

PERR

SERR

INTA

TCK

TMS

TDI

TDO

PCI Bus

Interface

Management

JTAG

Port

Control

Unit

Buffer

Unit

Expansion Bus

Bus

Rcv

FIFO

Bus

Xmt

FIFO

FIFO

Control

Interface

12K

SRAM

MAC

Rcv

FIFO

MAC

Xmt

FIFO

Network

Port

Manager

OnNow

Power

Management

Unit

EADI

MII

802.3

MAC

Core

Serial

Management

Interface Unit

MDC

MDIO

MII

Interface

MII

Management

Transmit

Block

Receive

Block

LED

Control

93C46

EEPROM

Interface

Clock

Reference

10/100 PHY Core

(100 BASE-TX)

(100 BASE-FX)

10 BASE-T

Link

Monitor

Negotiation

PHY Control

MLT3

PECL

Auto

TX±

RX±

SDI±

LED0

LED1

LED2

LED3

EECS

EESK

EEDI

EEDO

VAUXDET

PME

RWU

WUMI

PG

4 Am79C973/Am79C975

MCLOCK

MDATA

MIRQ

21510D-1

Page 5

PRELIMINARY

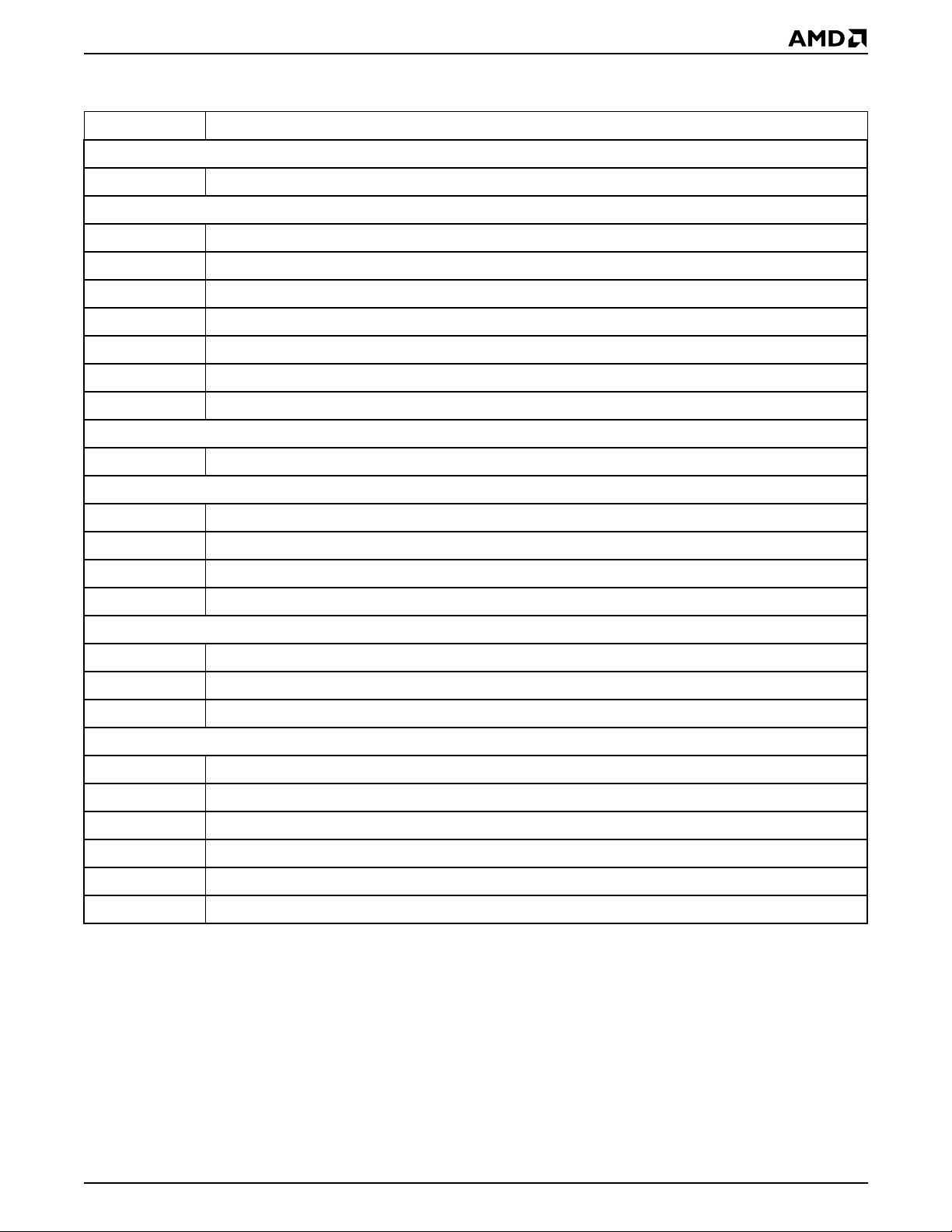

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

TABLE OF CONTENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

LIST OF FIGURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

LIST OF TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

RELATED AMD PRODUCTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

CONNECTION DIAGRAM (PQR160) - AM79C973 . . . . . . . . . . . . . . . . . . . . . . . . . . 18

CONNECTION DIAGRAM (PQL176) AM79C973 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

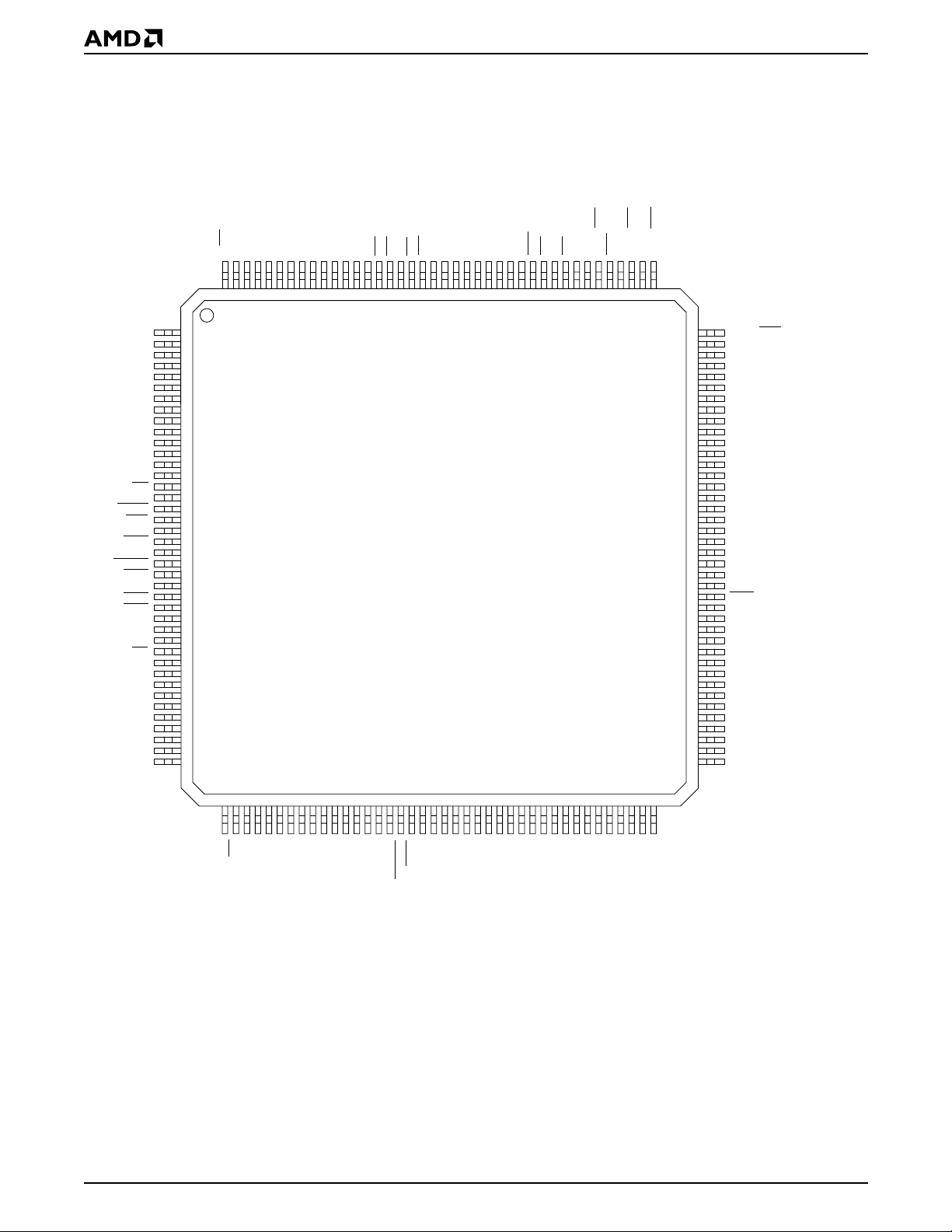

CONNECTION DIAGRAM (PQR160) - AM79C975 . . . . . . . . . . . . . . . . . . . . . . . . . . 20

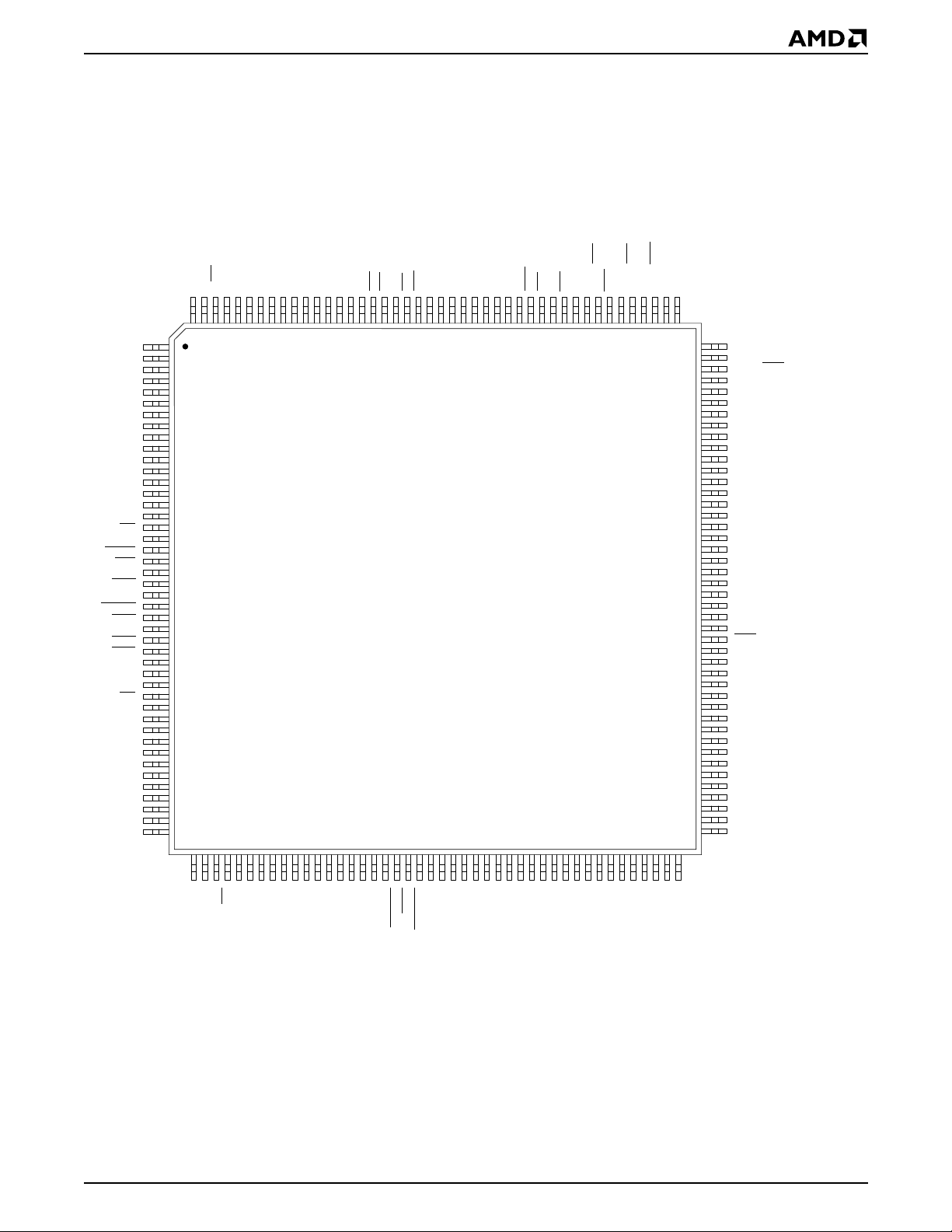

CONNECTION DIAGRAM (PQL176) - AM79C975 . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

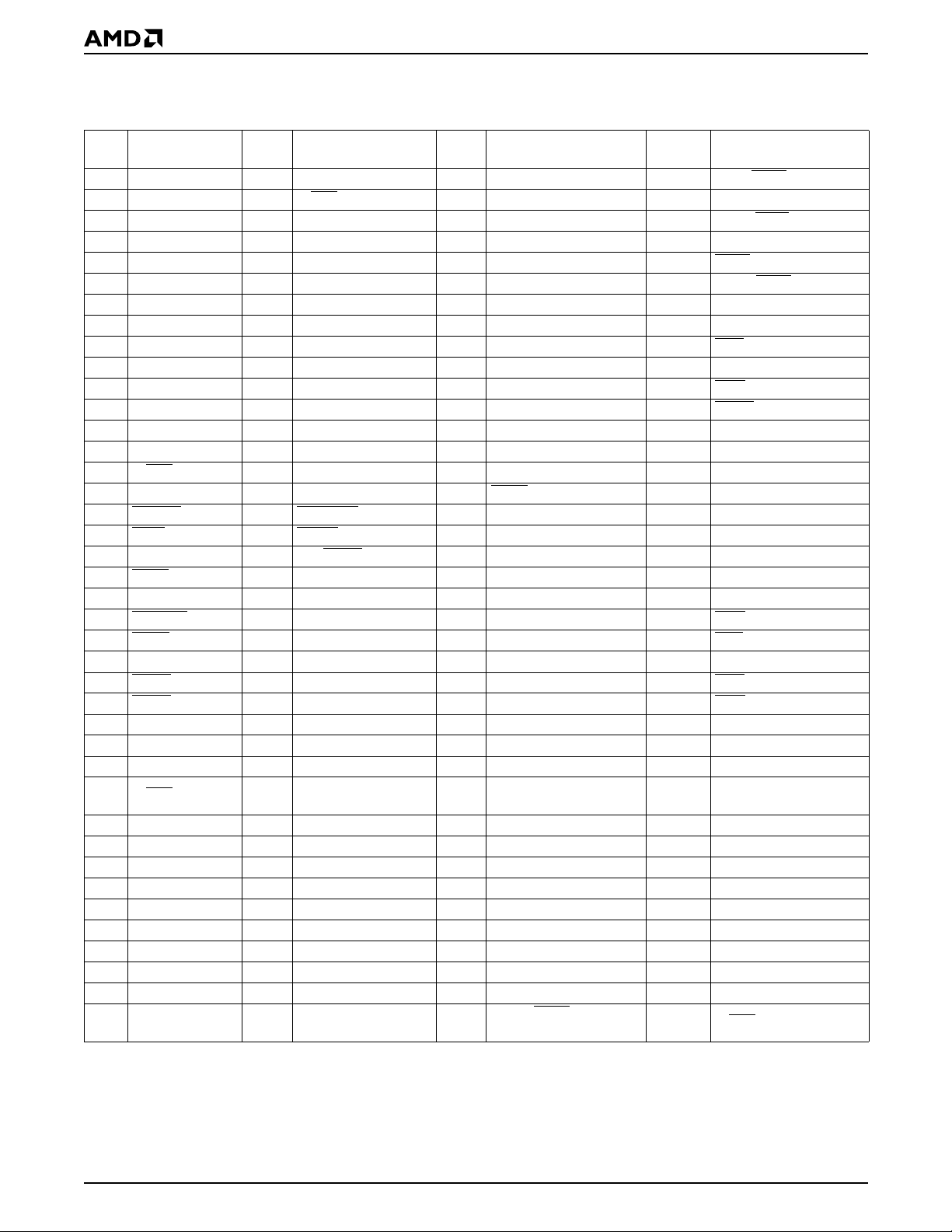

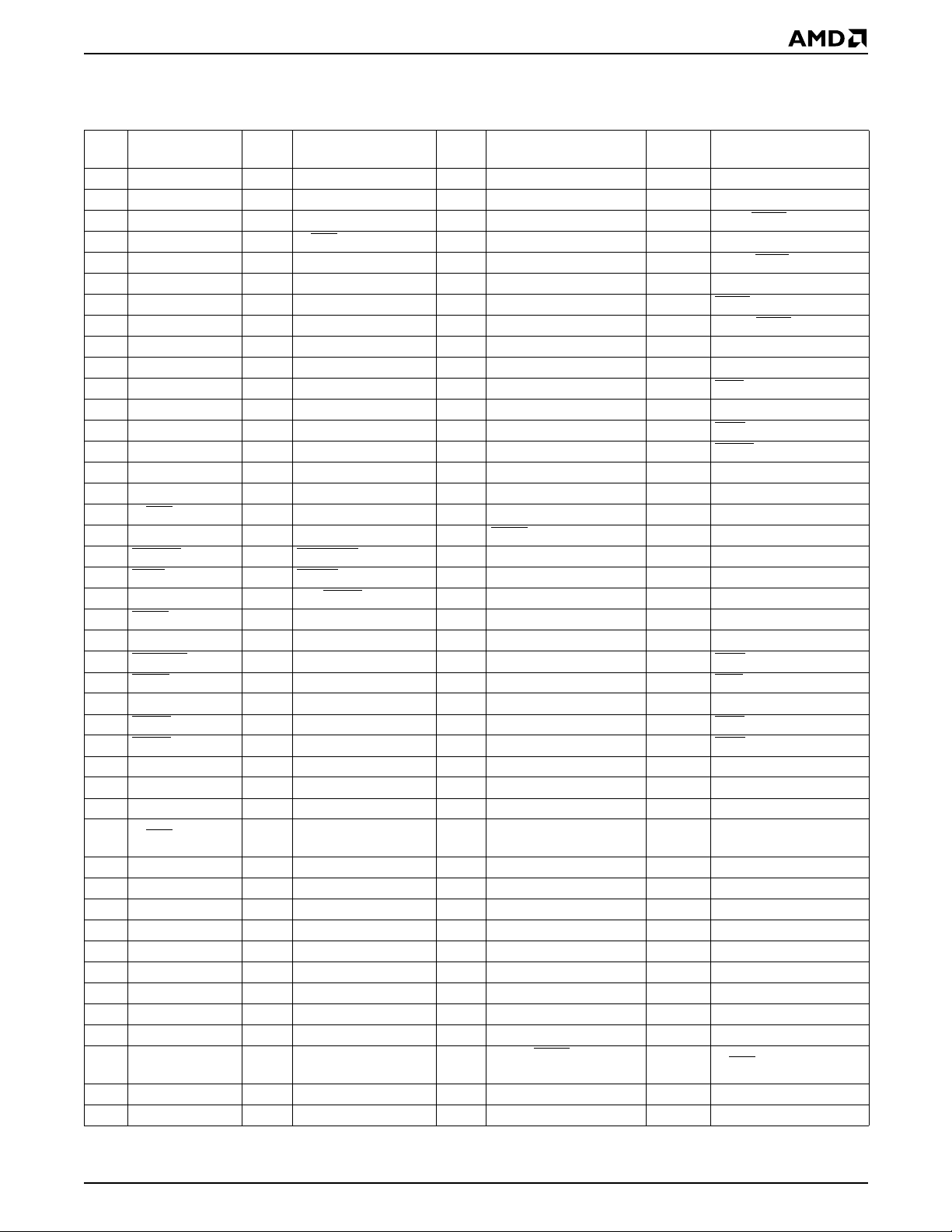

PIN DESIGNATIONS (PQR160) (Am79C973/Am79C975) . . . . . . . . . . . . . . . . . . . . 22

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

PIN DESIGNATIONS (PQL176) (Am79C973/Am79C975) . . . . . . . . . . . . . . . . . . . . . 23

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

PIN DESIGNATIONS (PQR160, PQL176) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Listed By Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

PIN DESIGNATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Listed By Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

PIN DESIGNATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Listed By Driver Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Board Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Expansion Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Media Independent Interface (MII) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

IEEE 1149.1 (1990) Test Access Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Network Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Serial Management Interface (SMI) (Am79C975 only) . . . . . . . . . . . . . . . . . . . . . . 37

Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

BASIC FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

System Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Software Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Network Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Serial Management Interface (Am79C975) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

DETAILED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Slave Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Slave Configuration Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Slave I/O Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Expansion ROM Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Slave Cycle Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Master Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Am79C973/Am79C975 5

Page 6

PRELIMINARY

Bus Acquisition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Bus Master DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Target Initiated Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Master Initiated Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Master Abort. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Initialization Block DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Descriptor DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

FIFO DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Buffer Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Re-Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Suspend. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Buffer Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Descriptor Rings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Polling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Transmit Descriptor Table Entry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Receive Descriptor Table Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Receive Frame Queuing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Software Interrupt Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

10/100 Media Access Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Transmit and Receive Message Data Encapsulation. . . . . . . . . . . . . . . . . . . . . 70

Destination Address Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Media Access Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Transmit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Transmit Function Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Automatic Pad Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Transmit FCS Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Transmit Exception Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Receive Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Receive Function Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Address Matching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Automatic Pad Stripping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Receive FCS Checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Receive Exception Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Loopback Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Miscellaneous Loopback Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Full-Duplex Link Status LED Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

10/100 PHY Unit Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

100BASE-TX Physical Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

100BASE-FX (Fiber Interface) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

10BASE-T Physical Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

PHY/MAC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Transmit Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Receive Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Internal PHY Loopback Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Encoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6 Am79C973/Am79C975

Page 7

PRELIMINARY

Scrambler/Descrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Link Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Far End Fault Generation and Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

MLT-3 and Adaptive Equalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Serializer/Deserializer and Clock Recovery. . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Medium Dependent Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

10BASE-T Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Twisted Pair Transmit Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Twisted Pair Receive Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Twisted Pair Interface Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Collision Detect Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Jabber Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Reverse Polarity Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Soft Reset Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

External Address Detection Interface: MII Snoop Mode . . . . . . . . . . . . . . . . . . 89

External Address Detection Interface: Receive Frame Tagging . . . . . . . . . . . . 89

Expansion Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Expansion ROM - Boot Device Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Direct Flash Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

AMD Flash Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Direct SRAM Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Automatic EEPROM Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

LED Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Power Savings Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Power Management Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Magic Packet Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

IEEE 1149.1 (1990) Test Access Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Boundary Scan Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

TAP Finite State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Supported Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Other Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

H_RESET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

S_RESET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Power on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Software Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

PCI Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

I/O Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

USER ACCESSIBLE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

PCI Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

PCI Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

PCI Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

PCI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Am79C973/Am79C975 7

Page 8

PRELIMINARY

PCI Revision ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

PCI Programming Interface Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

PCI Sub-Class Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

PCI Base-Class Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

PCI Latency Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

PCI Header Type Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

PCI I/O Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

PCI Memory Mapped I/O Base Address Register . . . . . . . . . . . . . . . . . . . . . . 118

PCI Subsystem Vendor ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

PCI Subsystem ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

PCI Expansion ROM Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . 119

PCI Capabilities Pointer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI Interrupt Line Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI Interrupt Pin Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI MIN_GNT Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI MAX_LAT Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI Capability Identifier Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI Next Item Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PCI Power Management Capabilities Register (PMC). . . . . . . . . . . . . . . . . . . 121

PCI Power Management Control/Status Register (PMCSR) . . . . . . . . . . . . . . 121

PCI PMCSR Bridge Support Extensions Register . . . . . . . . . . . . . . . . . . . . . . 122

PCI Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

RAP Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

RAP: Register Address Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

CSR0: Am79C973/Am79C975 Controller Status and Control Register. . . . . . 123

CSR1: Initialization Block Address 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

CSR2: Initialization Block Address 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

CSR3: Interrupt Masks and Deferral Control . . . . . . . . . . . . . . . . . . . . . . . . . . 126

CSR4: Test and Features Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

CSR5: Extended Control and Interrupt 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

CSR6: RX/TX Descriptor Table Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

CSR7: Extended Control and Interrupt 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

CSR8: Logical Address Filter 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

CSR9: Logical Address Filter 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

CSR10: Logical Address Filter 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

CSR11: Logical Address Filter 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

CSR12: Physical Address Register 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

CSR13: Physical Address Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

CSR14: Physical Address Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

CSR15: Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

CSR16: Initialization Block Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

CSR17: Initialization Block Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

CSR18: Current Receive Buffer Address Lower . . . . . . . . . . . . . . . . . . . . . . . 140

CSR19: Current Receive Buffer Address Upper . . . . . . . . . . . . . . . . . . . . . . . 140

CSR20: Current Transmit Buffer Address Lower. . . . . . . . . . . . . . . . . . . . . . . 140

CSR21: Current Transmit Buffer Address Upper. . . . . . . . . . . . . . . . . . . . . . . 140

CSR22: Next Receive Buffer Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . 140

CSR23: Next Receive Buffer Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . 140

8 Am79C973/Am79C975

Page 9

PRELIMINARY

CSR24: Base Address of Receive Ring Lower . . . . . . . . . . . . . . . . . . . . . . . . 141

CSR25: Base Address of Receive Ring Upper . . . . . . . . . . . . . . . . . . . . . . . . 141

CSR26: Next Receive Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . . . 141

CSR27: Next Receive Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . . . 141

CSR28: Current Receive Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . 141

CSR29: Current Receive Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . 141

CSR30: Base Address of Transmit Ring Lower. . . . . . . . . . . . . . . . . . . . . . . . 141

CSR31: Base Address of Transmit Ring Upper. . . . . . . . . . . . . . . . . . . . . . . . 142

CSR32: Next Transmit Descriptor Address Lower. . . . . . . . . . . . . . . . . . . . . . 142

CSR33: Next Transmit Descriptor Address Upper. . . . . . . . . . . . . . . . . . . . . . 142

CSR34: Current Transmit Descriptor Address Lower . . . . . . . . . . . . . . . . . . . 142

CSR35: Current Transmit Descriptor Address Upper . . . . . . . . . . . . . . . . . . . 142

CSR36: Next Next Receive Descriptor Address Lower . . . . . . . . . . . . . . . . . . 142

CSR37: Next Next Receive Descriptor Address Upper . . . . . . . . . . . . . . . . . . 142

CSR38: Next Next Transmit Descriptor Address Lower. . . . . . . . . . . . . . . . . . 143

CSR39: Next Next Transmit Descriptor Address Uper. . . . . . . . . . . . . . . . . . . 143

CSR40: Current Receive Byte Count. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

CSR41: Current Receive Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

CSR42: Current Transmit Byte Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

CSR43: Current Transmit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

CSR44: Next Receive Byte Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

CSR45: Next Receive Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

CSR46: Transmit Poll Time Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

CSR47: Transmit Polling Interval. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

CSR48: Receive Poll Time Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

CSR49: Receive Polling Interval . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

CSR58: Software Style. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

CSR60: Previous Transmit Descriptor Address Lower . . . . . . . . . . . . . . . . . . 147

CSR61: Previous Transmit Descriptor Address Upper . . . . . . . . . . . . . . . . . . 148

CSR62: Previous Transmit Byte Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

CSR63: Previous Transmit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

CSR64: Next Transmit Buffer Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . 148

CSR65: Next Transmit Buffer Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . 148

CSR66: Next Transmit Byte Count. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

CSR67: Next Transmit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

CSR72: Receive Ring Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

CSR74: Transmit Ring Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

CSR76: Receive Ring Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

CSR78: Transmit Ring Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

CSR80: DMA Transfer Counter and FIFO Threshold Control . . . . . . . . . . . . . 150

CSR82: Transmit Descriptor Address Pointer Lower. . . . . . . . . . . . . . . . . . . . 152

CSR84: DMA Address Register Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

CSR85: DMA Address Register Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

CSR86: Buffer Byte Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

CSR88: Chip ID Register Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

CSR89: Chip ID Register Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

CSR92: Ring Length Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

CSR100: Bus Timeout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

CSR112: Missed Frame Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Am79C973/Am79C975 9

Page 10

PRELIMINARY

CSR114: Receive Collision Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

CSR116: OnNow Power Mode Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

CSR122: Advanced Feature Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

CSR124: Test Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

CSR125: MAC Enhanced Configuration Control . . . . . . . . . . . . . . . . . . . . . . . 156

Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

BCR0: Master Mode Read Active . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

BCR1: Master Mode Write Active. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

BCR2: Miscellaneous Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

BCR4: LED 0 Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

BCR5: LED1 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

BCR6: LED2 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

BCR7: LED3 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

BCR9: Full-Duplex Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

BCR16: I/O Base Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

BCR17: I/O Base Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

BCR18: Burst and Bus Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

BCR19: EEPROM Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

BCR20: Software Style. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

BCR22: PCI Latency Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

BCR23: PCI Subsystem Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . 180

BCR24: PCI Subsystem ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

BCR25: SRAM Size Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

BCR26: SRAM Boundary Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

BCR27: SRAM Interface Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

BCR28: Expansion Bus Port Address Lower

(Used for Flash/EPROM and SRAM Accesses) . . . . . . . . . . . . . . . . . . . . . 183

BCR29: Expansion Port Address Upper

(Used for Flash/EPROM Accesses) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

BCR30: Expansion Bus Data Port Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 184

BCR31: Software Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

BCR32: PHY Control and Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

BCR33: PHY Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

BCR34: PHY Management Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

BCR35: PCI Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

BCR36: PCI Power Management Capabilities (PMC) Alias Register . . . . . . . 188

BCR37: PCI DATA Register Zero (DATA0) Alias Register . . . . . . . . . . . . . . . 188

BCR38: PCI DATA Register One (DATA1) Alias Register. . . . . . . . . . . . . . . . 188

BCR39: PCI DATA Register Two (DATA2) Alias Register. . . . . . . . . . . . . . . . 189

BCR40: PCI DATA Register Three (DATA3) Alias Register . . . . . . . . . . . . . . 189

BCR41: PCI DATA Register Four (DATA4) Alias Register . . . . . . . . . . . . . . . 189

BCR42: PCI DATA Register Five (DATA5) Alias Register. . . . . . . . . . . . . . . . 190

BCR43: PCI DATA Register Six (DATA6) Alias Register. . . . . . . . . . . . . . . . . 190

BCR44: PCI DATA Register Seven (DATA7) Alias Register . . . . . . . . . . . . . . 191

BCR45: OnNow Pattern Matching Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . 191

BCR46: OnNow Pattern Matching Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . 191

BCR47: OnNow Pattern Matching Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . 192

BCR48-BCR55: Reserved Locations for Am79C975. . . . . . . . . . . . . . . . . . . . 192

PHY Management Registers (ANRs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

10 Am79C973/Am79C975

Page 11

PRELIMINARY

ANR1: Status Register (Register 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

ANR2 and ANR3: PHY Identifier (Registers 2 and 3) . . . . . . . . . . . . . . . . . . . 196

ANR4: Auto-Negotiation Advertisement Register (Register 4). . . . . . . . . . . . . 197

ANR5: Auto-Negotiation Link Partner Ability Register (Register 5) . . . . . . . . . 198

ANR6: Auto-Negotiation Expansion Register (Register 6). . . . . . . . . . . . . . . . 199

ANR7: Auto-Negotiation Next Page Register (Register 7). . . . . . . . . . . . . . . . 199

Reserved Registers (Registers 8-15, 20-23, and 25-31) . . . . . . . . . . . . . . . . . 199

ANR16: INTERRUPT Status and Enable Register (Register 16). . . . . . . . . . . 200

ANR17: PHY Control/Status Register (Register 17) . . . . . . . . . . . . . . . . . . . . 200

ANR18: Descrambler Resynchronization Timer Register (Register 18) . . . . . 202

ANR19: PHY Management Extension Register (Register 19) . . . . . . . . . . . . . 202

ANR24: Summary Status Register (Register 24). . . . . . . . . . . . . . . . . . . . . . . 202

Initialization Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Receive Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Transmit Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

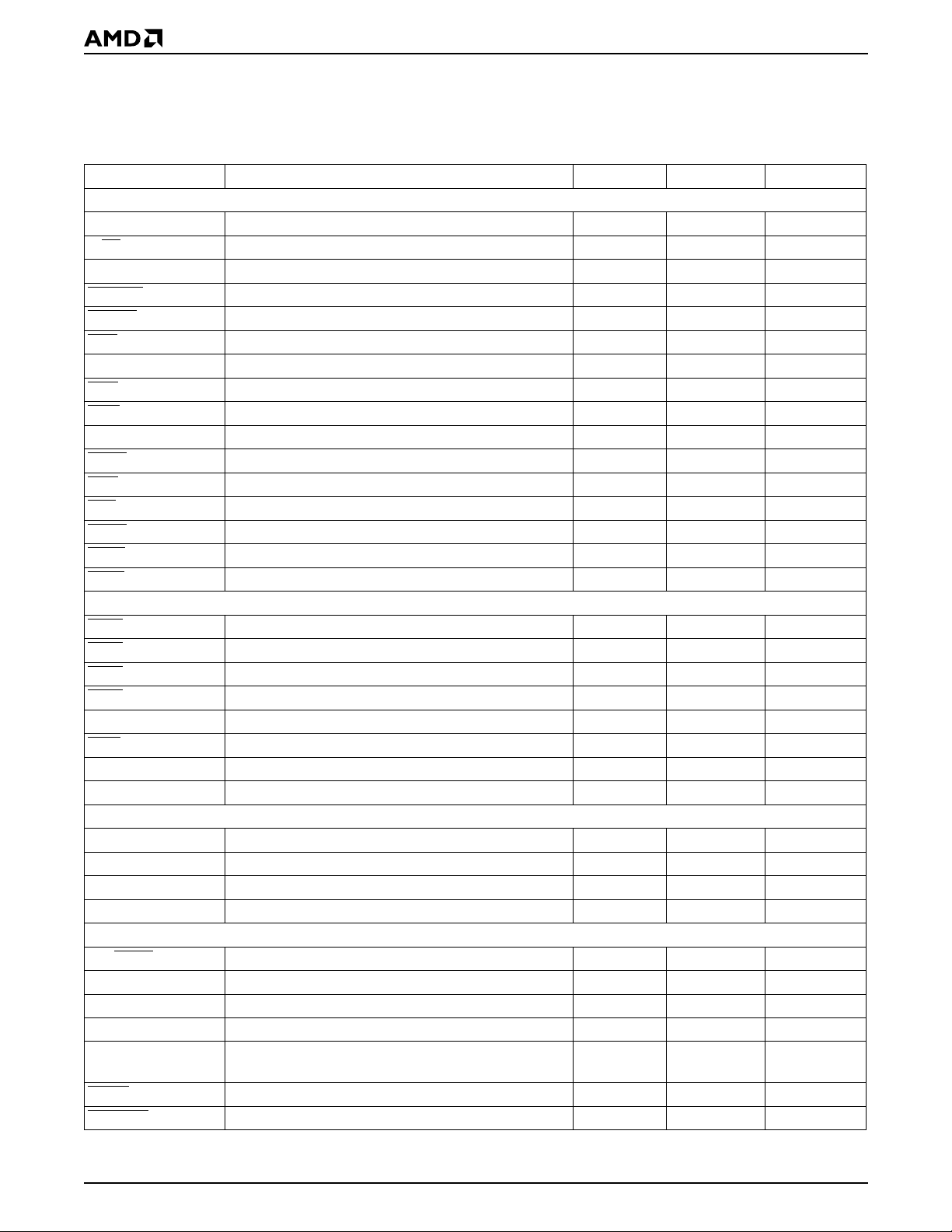

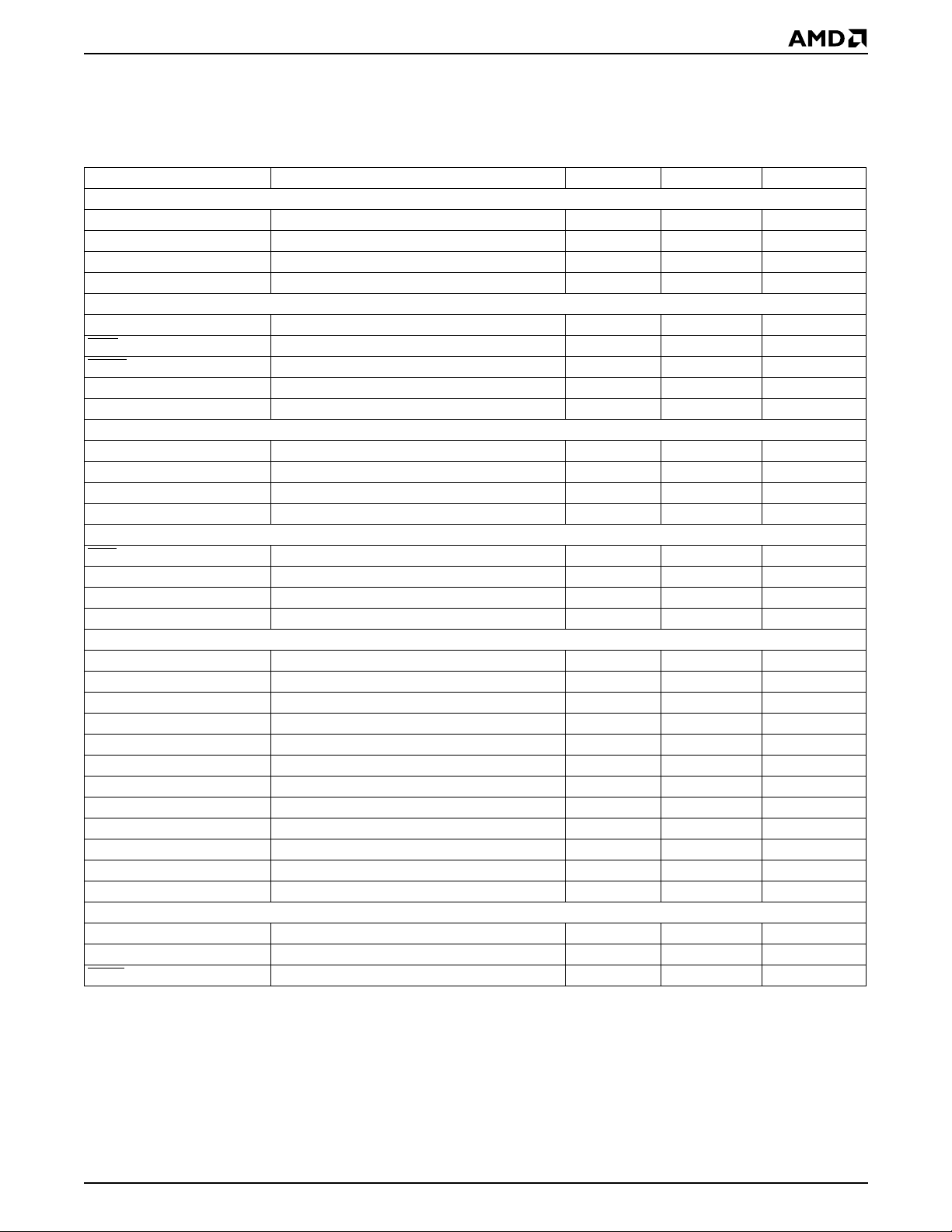

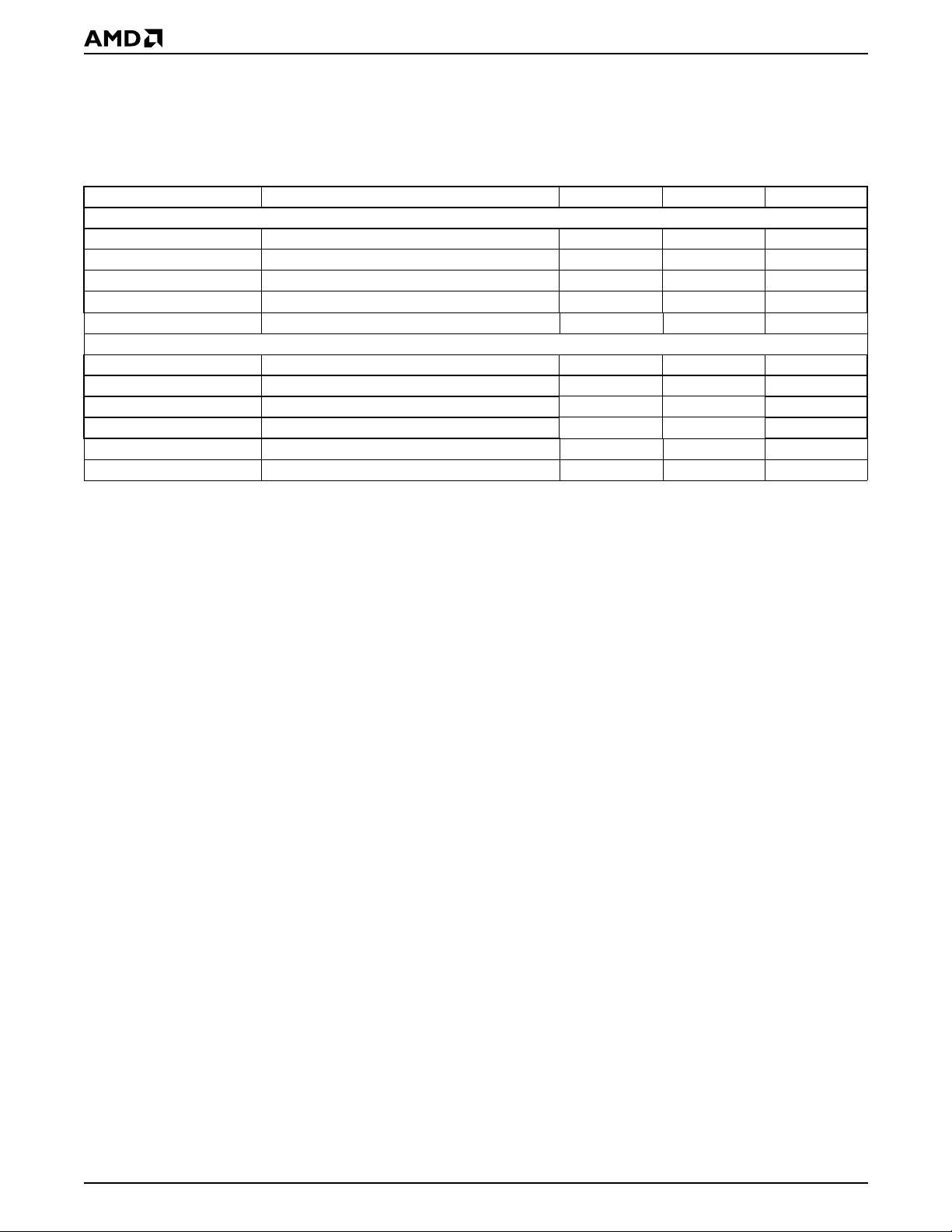

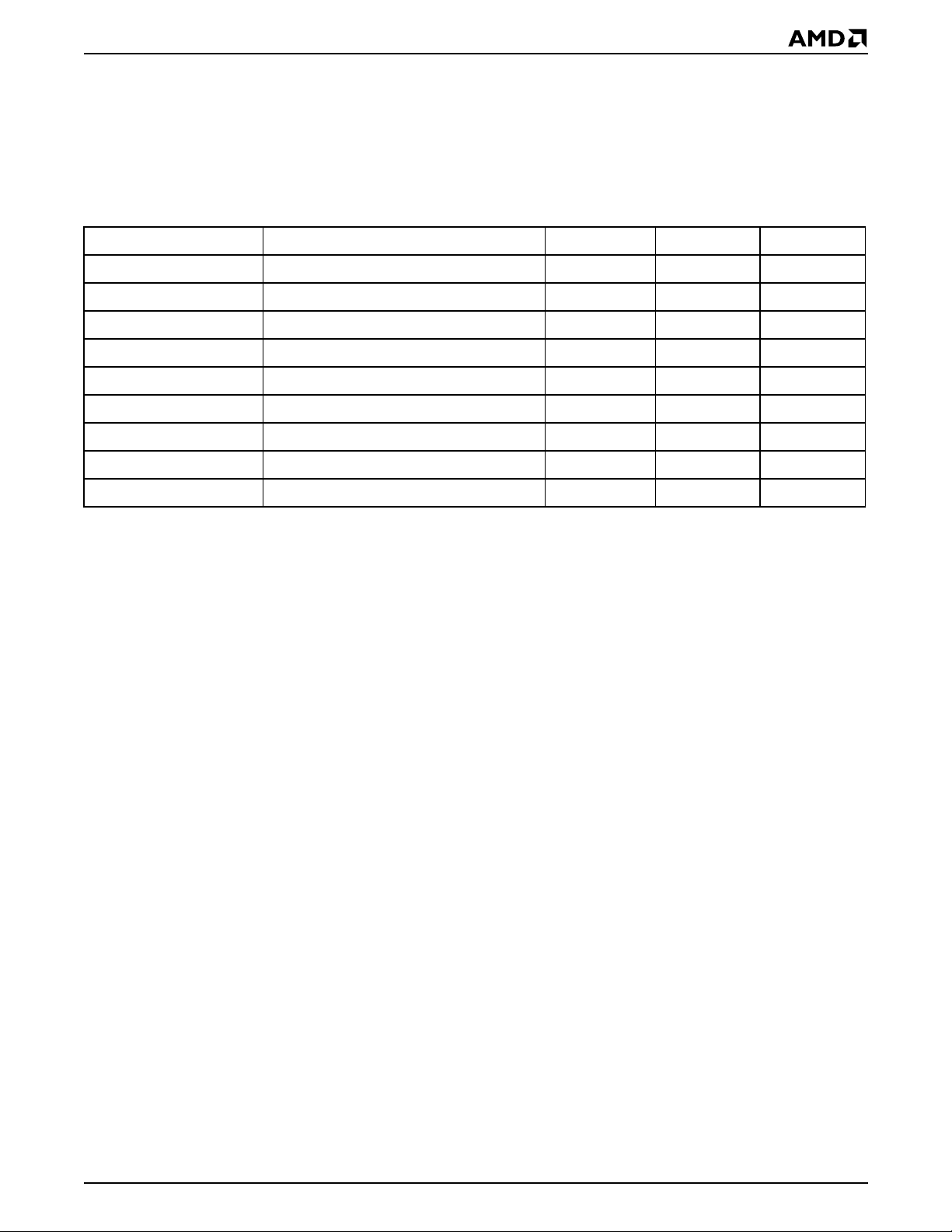

REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

PHY Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

PROGRAMMABLE REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Am79C973/Am79C975 Control and Status Registers . . . . . . . . . . . . . . . . . . . . . 220

Am79C973/Am79C975 Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . 222

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

SWITCHING CHARACTERISTICS: BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . 227

SWITCHING CHARACTERISTICS: EXTERNAL ADDRESS

DETECTION INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

EXTERNAL CLOCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

SWITCHING WAVEFORMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

SWITCHING TEST CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

SWITCHING WAVEFORMS: SYSTEM BUS INTERFACE . . . . . . . . . . . . . . . . . . . . 236

SWITCHING WAVEFORMS: EXPANSION BUS INTERFACE . . . . . . . . . . . . . . . . 240

PHYSICAL DIMENSIONS* . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

PQR160 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

PQL176 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

APPENDIX A: PCnet™-FAST III Recommended Magnetics . . . . . . . . . . . . . . . . 244

APPENDIX B: SERIAL MANAGEMENT INTERFACE UNIT

(AM79C975 ONLY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Am79C975 PIN DESIGNATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Am79C975 Slave Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Register Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Detailed Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Transmit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Receive Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

Loopback Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

User Accessible Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Device ID Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Am79C973/Am79C975 11

Page 12

PRELIMINARY

Node ID Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Device Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

Am79C975 EEPROM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

Am79C975 EEPROM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Switching Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

APPENDIX C: MEDIA INDEPENDENT INTERFACE (MII) . . . . . . . . . . . . . . . . . . . . 268

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

Automatic Network Port Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

MII management registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Control Register (Register 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Status Register (Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

Auto-Negotiation Advertisement Register (Register 4) . . . . . . . . . . . . . . . . . . . . . 276

Auto-Negotiation Link Partner Ability Register (Register 5) . . . . . . . . . . . . . . . . . 277

Switching Characteristics: Media Independent Interface . . . . . . . . . . . . . . . . . . . 278

Switching Waveforms: Media Independent Interface . . . . . . . . . . . . . . . . . . . . . . 279

Switching Waveforms: External Address Detection Interface . . . . . . . . . . . . . . . . 281

Switching Waveforms: Receive Frame Tag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

APPENDIX D: ALTERNATIVE METHOD FOR INITIALIZATION . . . . . . . . . . . . . . . 283

APPENDIX E: LOOK-AHEAD PACKET PROCESSING (LAPP) CONCEPT . . . . . 284

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Outline of LAPP Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

LAPP Software Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

LAPP Rules for Parsing Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Some Examples of LAPP Descriptor Interaction . . . . . . . . . . . . . . . . . . . . . . . . . 289

Buffer Size Tuning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

An Alternative LAPP Flow: Two-Interrupt Method . . . . . . . . . . . . . . . . . . . . . . . . 291

INDEX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

12 Am79C973/Am79C975

Page 13

PRELIMINARY

LIST OF FIGURES

Figure 1. Slave Configuration Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 2. Slave Configuration Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 3. Slave Read Using I/O Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 4. Slave Write Using Memory Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 5. Expansion ROM Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 6. Disconnect Of Slave Cycle When Busy . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 7. Disconnect Of Slave Burst Transfer - No Host Wait States . . . . . . . . . . . . . 44

Figure 8. Disconnect Of Slave Burst Transfer - Host Inserts Wait States . . . . . . . . . . 45

Figure 9. Address Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 10. Slave Cycle Data Parity Error Response 46

Figure 11. Bus Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 12. Non-Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 13. Burst Read Transfer (EXTREQ = 0, MEMCMD = 0) . . . . . . . . . . . . . . . . . . 48

Figure 14. Non-Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 15. Burst Write Transfer (EXTREQ = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 16. Disconnect With Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 17. Disconnect Without Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 18. Target Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 19. Preemption During Non-Burst Transaction . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 20. Preemption During Burst Transaction 54

Figure 21. Master Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 22. Master Cycle Data Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 23. Initialization Block Read In Non-Burst Mode 57

Figure 24. Initialization Block Read In Burst Mode 57

Figure 25. Descriptor Ring Read In Non-Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 26. Descriptor Ring Read In Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 27. Descriptor Ring Write In Non-Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 28. Descriptor Ring Write In Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 29. FIFO Burst Write At Start Of Unaligned Buffer . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 30. FIFO Burst Write At End Of Unaligned Buffer . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 31. 16-Bit Software Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 32. 32-Bit Software Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 33. ISO 8802-3 (IEEE/ANSI 802.3) Data Frame . . . . . . . . . . . . . . . . . . . . . . . .74

Figure 34. IEEE 802.3 Frame And Length Field Transmission Order . . . . . . . . . . . . . . 77

Figure 35. 100BASE-X Transmit and Receive Data Paths of the Internal PHY . . . . . . 81

Figure 36. MLT-3 Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 37. TX± and RX± Termination 86

Figure 38. 10BASE-T Transmit and Receive Data Paths . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 39. Receive Frame Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 40. Flash Configuration for the Expansion Bus . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 41. EPROM Only Configuration for the Expansion Bus (64K EPROM) . . . . . . . 92

Figure 42. EPROM Only Configuration for the Expansion Bus (64K EPROM) 93

Figure 43. Expansion ROM Bus Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 44. Flash Read from Expansion Bus Data Port . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 45. Flash Write from Expansion Bus Data Port . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 46. Block Diagram No SRAM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 47. Block Diagram Low Latency Receive Configuration . . . . . . . . . . . . . . . . . . 97

Figure 48. LED Control Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Am79C973/Am79C975 13

Page 14

PRELIMINARY

Figure 49. OnNow Functional Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 50. Pattern Match RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 51. Address Match Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 52. External Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Figure 53. PMD Interface Timing (PECL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Figure 54. PMD Interface Timing (MLT-3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Figure 55. 10 Mbps Transmit (TX±) Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . 233

Figure 56. 10 Mbps Receive (RX±) Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Figure 57. Normal and Tri-State Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Figure 58. CLK Waveform for 5 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Figure 59. CLK Waveform for 3.3 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Figure 60. Input Setup and Hold Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Figure 61. Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

Figure 62. Output Tri-state Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

Figure 63. EEPROM Read Functional Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 37

Figure 64. Automatic PREAD EEPROM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Figure 65. JTAG (IEEE 1149.1) TCK Waveform for 5 V Signaling . . . . . . . . . . . . . . . 238

Figure 66. JTAG (IEEE 1149.1) Test Signal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Figure 67. EBCLK Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Figure 68. Expansion Bus Read Timing 240

Figure 69. Expansion Bus Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

Figure 70. Standard Data Transfer on the Serial Management Interface . . . . . . . . . . 247

Figure 71. Data Transfer with Change in Direction (with wait state) . . . . . . . . . . . . . . 247

Figure 72. Write Byte Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

Figure 73. Read Byte Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 48

Figure 74. Block Write Command 249

Figure 75. Block Read Command 250

Figure 76. System Management Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

Figure 77. Media Independent Interface 268

Figure 78. Frame Format at the MII Interface Connection . . . . . . . . . . . . . . . . . . . . . 270

Figure 79. MII Receive Frame Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .273

Figure 80. Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Figure 81. Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Figure 82. MDC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Figure 83. Management Data Setup and Hold Timing . . . . . . . . . . . . . . . . . . . . . . . . 280

Figure 84. Management Data Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . . 280

Figure 85. Reject Timing - External PHY MII @ 25 MHz . . . . . . . . . . . . . . . . . . . . . . . 281

Figure 86. Reject Timing - External PHY MII @ 2.5 MHz 281

Figure 87. Receive Frame Tag Timing with Media Independent Interface . . . . . . . . . 282

Figure 88. LAPP Timeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

Figure 89. LAPP 3 Buffer Grouping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Figure 90. LAPP Timeline for Two-Interrupt Method . . . . . . . . . . . . . . . . . . . . . . . . . .292

Figure 91. LAPP 3 Buffer Grouping for Two-interrupt Method . . . . . . . . . . . . . . . . . . 293

14 Am79C973/Am79C975

Page 15

PRELIMINARY

LIST OF TABLES

Table 1. Interrupt Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 2. SDI± Settings for Transceiver Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 3. Slave Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 4. Master Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 5. Descriptor Read Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 6. Descriptor Write Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 7. Receive Address Match . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 8. Encoder Code-Group Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 9. Decoder Code-Group Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 10. Auto-Negotiation Capabilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 11. EADI Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 12. Am29Fxxx Flash Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 13. Am79C973 EEPROM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 14. Am79C975 EEPROM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 15. LED Default Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 16. IEEE 1149.1 Supported Instruction Summary . . . . . . . . . . . . . . . . . . . . . . 106

Table 17. BSR Mode Of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 18. Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 19. PCI Configuration Space Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 20. I/O Map In Word I/O Mode (DWIO = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 21. Legal I/O Accesses in Word I/O Mode (DWIO = 0) . . . . . . . . . . . . . . . . . . .111

Table 22. I/O Map In DWord I/O Mode (DWIO =1). . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 23. Legal I/O Accesses in Double Word I/O Mode (DWIO =1). . . . . . . . . . . . . 111

Table 24. Loopback Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Table 25. Software Styles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 26. Receive Watermark Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 27. Transmit Start Point Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 28. Transmit Watermark Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 29. BCR Registers (Am79C973) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Table 30. BCR Registers (Am79C975) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 31. ROMTNG Programming Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Table 32. Interface Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Table 33. Software Styles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Table 34. SRAM_BND Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

Table 35. EBCS Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Table 36. CLK_FAC Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 37. FMDC Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Table 38. APDW Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 39. Am79C973/Am79C975 Internal PHY Management Register Set . . . . . . . 193

Table 40. ANR0: PHY Control Register (Register 0) . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 41. ANR1: PHY Status Register (Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Table 42. ANR2: PHY Identifier (Register 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Table 43. ANR3: PHY Identifier (Register 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Table 44. ANR4: Auto-Negotiation Advertisement Register (Register 4) . . . . . . . . . . 197

Table 45. ANR5: Auto-Negotiation Link Partner Ability Register (Register 5)

- Base Page Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Table 46. ANR5: Auto-Negotiation Link Partner Ability Register (Register 5)

- Next Page Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Am79C973/Am79C975 15

Page 16

PRELIMINARY

Table 47. ANR6: Auto-Negotiation Expansion Register (Register 6) . . . . . . . . . . . . . 199

Table 48. ANR7: Auto-Negotiation Next Page Register (Register 7) . . . . . . . . . . . . . 199

Table 49. ANR16: INTERRUPT Status and Enable Register (Register 16) . . . . . . . . 200

Table 50. ANR17: PHY Control/Status Register (Register 17) . . . . . . . . . . . . . . . . . . 201

Table 51. ANR18: Descrambler Resynchronization Timer (Register 18) . . . . . . . . . . 202

Table 52. ANR19: PHY Management Extension Register (Register 19) . . . . . . . . . . . 202

Table 53. ANR24: Summary Status Register (Register 24) . . . . . . . . . . . . . . . . . . . . 203

Table 54. Initialization Block (SSIZE32 = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Table 55. Initialization Block (SSIZE32 = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Table 56. R/TLEN Decoding (SSIZE32 = 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Table 57. R/TLEN Decoding (SSIZE32 = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Table 58. Receive Descriptor (SWSTYLE = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Table 59. Receive Descriptor (SWSTYLE = 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Table 60. Receive Descriptor (SWSTYLE = 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Table 61. Transmit Descriptor (SWSTYLE = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 62. Transmit Descriptor (SWSTYLE = 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 63. Transmit Descriptor (SWSTYLE = 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 64. Clock (XTAL1, XCLK = 1) Switching Characteristics . . . . . . . . . . . . . . . . . 231

Table 65. Crystal (XTAL1, XTAL2, XCLK = 0) Requirements . . . . . . . . . . . . . . . . . . 231

Table 66. Crystal (XTAL1, XTAL2, XCLK = 0) Requirements . . . . . . . . . . . . . . . . . . 231

Table 67. Recommended Magnetics Vendors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

Table 68. Auto-Negotiation Capabilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

Table 69. EADI Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Table 70. MII Management Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Table 71. MII Management Control Register (Register 0) . . . . . . . . . . . . . . . . . . . . . .274

Table 72. MII Management Status Register (Register 1) . . . . . . . . . . . . . . . . . . . . . . 275

Table 73. Auto-Negotiation Advertisement Register (Register 4) . . . . . . . . . . . . . . . . 276

Table 74. Technology Ability Field Bit Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Table 75. Auto-Negotiation Link Partner Ability Register (Register 5)

- Base Page Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

Table 76. Registers for Alternative Initialization Method (Note 1) . . . . . . . . . . . . . . . . 283

16 Am79C973/Am79C975

Page 17

PRELIMINARY

RELATED AMD PRODUCTS

Part No. Description

Controllers

Am79C90 CMOS Local Area Network Controller for Ethernet (C-LANCE™)

Integrated Controllers

Am79C930 PCnet™-Mobile Single Chip Wireless LAN Media Access Controller

Am79C940 Media Access Controller for Ethernet (MACE™)

Am79C961A PCnet-ISA II Full Duplex Single-Chip Ethernet Controller for ISA Bus

Am79C965 PCnet-32 Single-Chip 32-Bit Ethernet Controller for 486 and VL Buses

Am79C970A PCnet-PCI II Full Duplex Single-Chip Ethernet Controller for PCI Local Bus

Am79C971 PCnet-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus

Am79C972 PCnet-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support

Manchester Encoder/Decoder

Am7992B Serial Interface Adapter (SIA)

Physical Layer Devices (Single-Port)

Am7996 IEEE 802.3/Ethernet/Cheapernet Transceiver

Am79761 Physical Layer 10-Bit Transceiver for Gigabit Ethernet (GigaPHY™-SD)

Am79C98 Twisted Pair Ethernet Transceiver (TPEX)

Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX+)

Physical Layer Devices (Multi-Port)

Am79C871 Quad Fast Ethernet Transceiver for 100BASE-X Repeaters (QFEXr™)

Am79C988A Quad Integrated Ether net Transceiver (QuIET™)

Am79C989 Quad Ethernet Switching Transceiver (QuEST™)

Integrated Repeater/Hub Devices

Am79C981 Integrated Multiport Repeater Plus (IMR+)

Am79C982 Basic Integrated Multiport Repeater (bIMR)

Am79C983 Integrated Multiport Repeater 2 (IMR2™)

Am79C984A Enhanced Integrated Multiport Repeater (eIMR™)

Am79C985 Enhanced Integrated Multiport Repeater Plus (eIMR+™)

Am79C987 Hardware Implemented Management Information Base (HIMIB™)

Am79C973/Am79C975 17

Page 18

PRELIMINARY

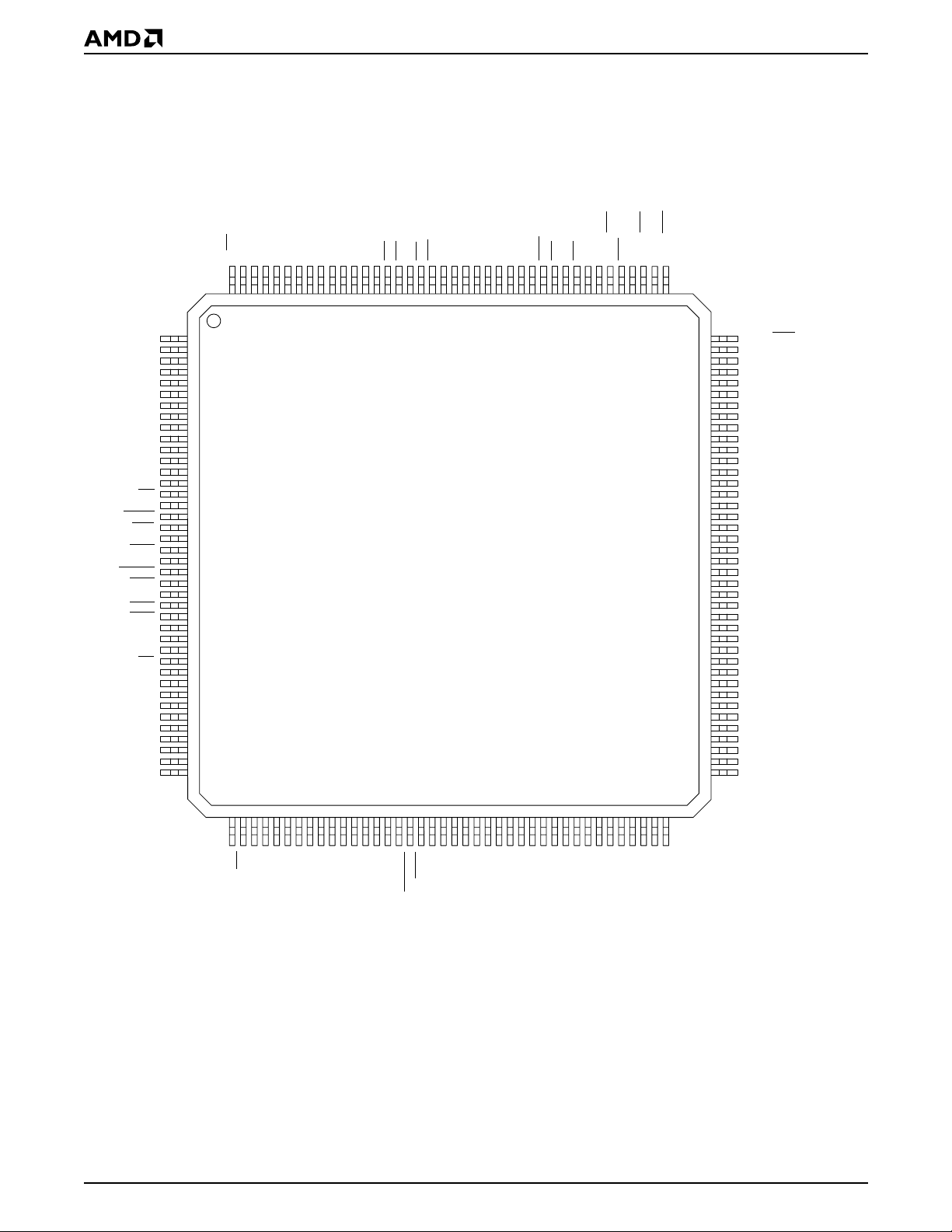

CONNECTION DIAGRAM (PQR160) - Am79C973

C/BE3

AD24

AD25

VSSB

AD26

VDD_PCI

AD27

AD28

AD29

AD30

VSS

VSSB

AD31

VDD_PCI

REQ

GNT

CLK

RST

INTAPGVDD

TDI

VSSB

TDO

VDDB

TMS

TCK

RWU

WUMI

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

IDSEL

AD23

VSSB

AD22

VDD_PCI

AD21

AD20

VDD

AD19

AD18

VSSB

AD17

VDD_PCI

AD16

C/BE2

VSS

FRAME

IRDY

VSSB

TRDY

VDD_PCI

DEVSEL

STOP

VDD

PERR

SERR

VSSB

PAR

VDD_PCI

C/BE1

AD15

VSS

AD14

AD13

VSSB

AD12

AD11

VDD_PCI

AD10

AD9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

Am79C973

PQR160

414243444546474849505152535455565758596061626364656667686970717273747576777879

132

PME

131

VSS

130

EAR

129

EECS

VSSB

EESK/LED1/SFBD

LED2/MIIRXFRTGE

128

127

126

125

VDDB

XCLK/XTAL

VSSB

124

123

122

EED1/LED0

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

EEDO/LED3/MIIRXFRTGD

DVSSP

DVDDP

RXDVDDRX

RX+

SDIDVSSX

SDI+

TXDVDDTX

TX+

DVDDD

IREF

DVSSD

DVDDA

DVDDCO

XTAL1

XTAL2

VDDB

NC

VSSB

NC

VDD

NC

VSSB

VAUXDET

EBD0/RXD0

EBD1/RXD1

EBD2/RXD2

VSS

EBD3/RXD3

VDDB

EBD4/RX_DV

EBD5/RX_CLK

EBD6/RX_ER

VSSB

EBD7/TX_CLK

EBDA15/COL

EBDA14/CRS

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

VSSB

C/BE0

VDD_PCI

VDD

VSSB

VDD_PCI

VSS

EROMCS

EBWE

AS_EBOE

VSSB

EBCLK

EBUA_EBA0

VDD

VDDB

EBUA_EBA1

EBUA_EBA2

EBUA_EBA3

EBUA_EBA4

Pin 1 is marked for orientation.

18 Am79C973/Am79C975

VSS

VSSB

EBDA8/TXD0

EBDA9/TXD1

EBUA_EBA5/MDC

EBUA_EBA7/TX_ER

EBUA_EBA6/PHY_RST

VDDB

EBDA10/TXD2

EBDA11/TXD3

EBDA13/MDIO

EBDA12/TX_EN

21510D-2

Page 19

PRELIMINARY

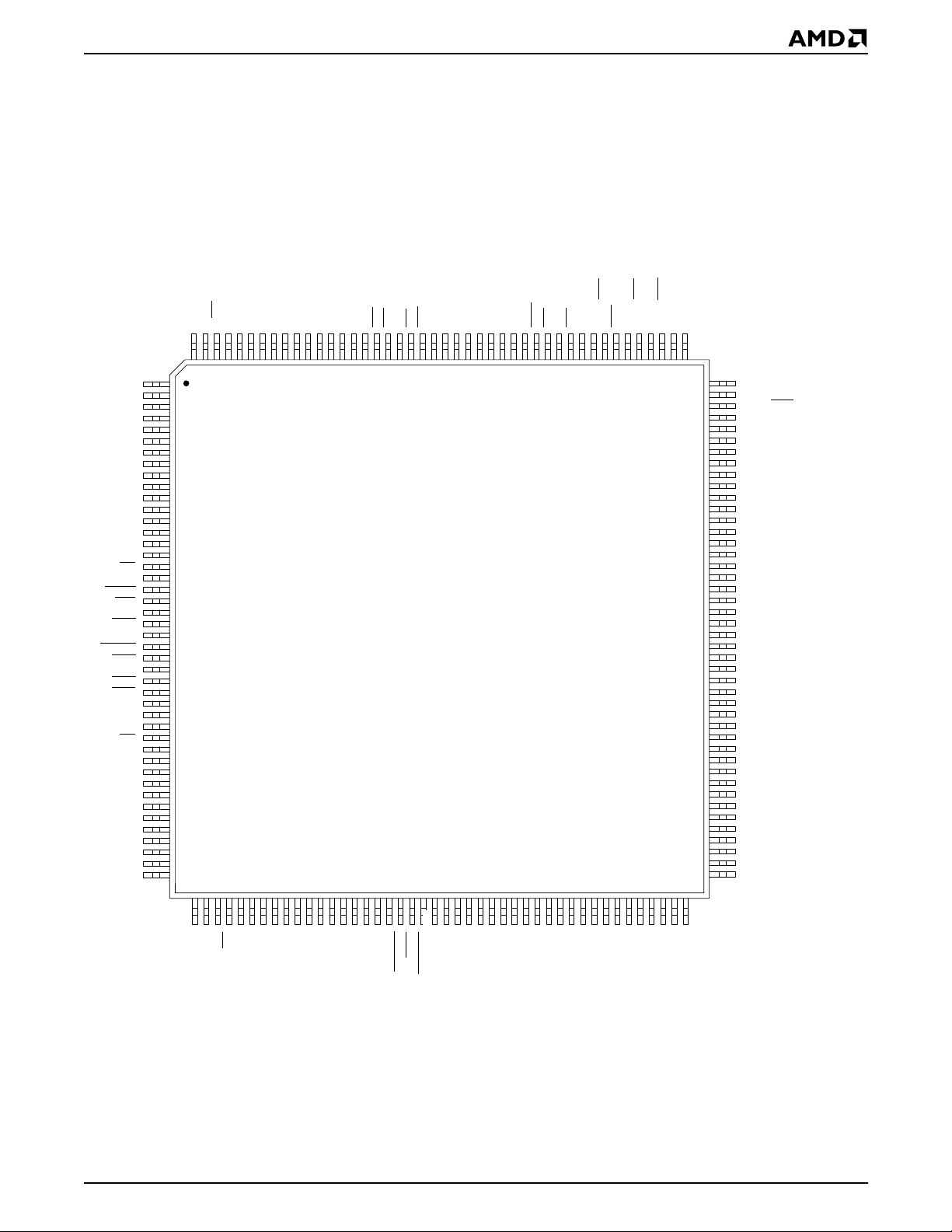

CONNECTION DIAGRAM (PQL176) Am79C973

NCNCC/BE3

AD24

AD25

VSSB

AD26

VDD_PCI

AD27

AD28

AD29

AD30

VSS

VSSB

AD31

VDD_PCI

REQ

GNT

CLK

RST

INTAPGVDD

TDI

VSSB

TDO

VDDB

TMS

TCK

RWU

176

175