Page 1

Am79C971

PCnet™-FAST

Single-Chip Full-Duplex 10/100 Mbps Ethernet Contr oller for PCI Local Bus

DISTINCTIVE CHARACTERISTICS

■ Single-chip Fast Ethernet controller for the

Peripheral Component Interconnect (PCI) local

bus

— 32-bit glueless PCI host interface

— Supports PCI clock frequency fr om DC to

33 MHz independent of network clock

— Supports network operation with PCI clock

from 15 MHz to 33 MHz

— High performance bus mastering

architecture with integrated Direct Memory

Access (DMA) Buffer Management Unit for

low CPU and bus utilization

— PCI specification revision 2.1 compliant

— Supports PCI Subsystem/Subvendor ID/

Vendor ID pr ogramming through the

EEPROM interface

— Supports both PCI 5.0-V and 3.3-V signaling

environments

— Plug and Play compatible

— Supports an unlimited PCI burst length

— Big endian and little endian byte alignments

supported

■ Integrated 10BASE-T and 10BASE-2/5 (AUI)

Physical Layer Interface

— Single-chip IEEE/ANSI 802.3, IEC/ISO 8802-3

and Blue Book Ethernet-compliant solution

— Automatic Twisted-Pair receive polarity

detection and correction

— Internal 10BASE-T transceiver with Smart

Squelch to Twisted-Pair medium

— IEEE 802.3-compliant auto-negotiable

10BASE-T interface

■ Supports General Purpose Serial Interface

(GPSI)

■ Media Independent Interface (MII) for

connecting external 10- or 100-Megabit per

second (Mbps) transceivers

— IEEE 802.3-compliant MII

— Intelligent Auto-Poll™ external PHY status

monitor and interrupt

— Includes intelligent on-chip Network Port

Manager that provides auto-port selection

between MII, on-chip 10BASE-T port, and A UI

without software support

— Supports both auto-negotiable and non

auto-negotiable external PHYs

— Supports 10BASE-T, 100BASE-TX/FX,

100BASE-T4, and 100BASE-T2 IEEE 802.3compliant MII PHYs at full- or half-duplex

■ Internal/external loopback capabilities on all

ports

■ Supports patented External Address Detection

Interface (EADI)

— Receive frame tagging support for inter-

networking applications

■ Dual-speed CSMA/CD (10 Mbps and 100 Mbps)

Media Access Controller (MAC) compliant with

IEEE/ANSI 802.3 and Blue Book Ethernet

standards

■ Full-duplex operation supported in AUI,

10BASE-T, MII, and GPSI ports with

independent Transmit (TX) and Receive (RX)

channels

■ Flexible buffer architecture

— Large independent internal TX and RX FIFOs

— SRAM-based FIFO buffer extension

supporting up to 128 kilobytes (Kbytes)

— 1/2 Gigabit per second (Gbps) internal data

bandwidth

— Programmable FIFO watermarks fo r both TX

and RX operations

— RX frame queuing for high latency PCI bus

host operation

— Programmable allocation of buffer space

between RX and TX queues

■ EEPROM interface supports jumperless design

and provides through-chip programming

— Supports full programmability of half-/full-

duplex operation f or external 100 Mbps PHYs

through EEPR OM mapping

■ Extensive LED status support

Publication# 20550 Rev: E Amendment: /0

Issue Date: May 2000

Page 2

■ Supports up to 1 Megabyte (Mbyte) optional

Boot PROM and Flash for diskless node

application

■ Look-Ahead Packet Processing (LAPP) data

handling technique reduces system overhead

by allowing protocol analysis to begin before

the end of a receive frame

■ Includes Programma ble Inter Packet Gap (IPG)

to address less network aggressive MAC

controllers

■ Offers the Modified Back-Off algorithm to

address the Ethernet Capture Effect

■ IEEE 1149.1-compliant JTAG Boundary Scan

test access port interface and NAND tree test

GENERAL DESCRIPTION

The Am79C971 controller is a single-chip 32-bit full-duplex, 10/100-Megabit per second (Mbps) highlyintegrated Etherne t system solution, designed to

address high-perfor mance syst em applicat ion requirements. It is a flexible bus mastering dev ice that can be

used in any application, including network-ready PCs

and bridge/router designs. The bus master architecture

provides high data throughput in the system and low

CPU and system bus utiliza tion. The Am79C971 co ntroller is fabricated with AMD’s advanced low-power

Complementary Metal Oxide Semiconductor (CMOS)

process to provide l ow operating and stand by current

for power sensitive applications.

The Am79C971 controller is a complete Ethernet node

integrated into a sin gle VLSI device. It contain s a bus

interface unit, a Direct Memory Access (DMA) Buffer

Management Unit, an ISO/IEC 8802-3 (IEEE 802.3)compliant Media Access Controller (MAC), a large

Transmit FIFO and a large Receive FIFO, SRAMbased FIFO extension with support for up to 128K

bytes of external frame buffering, an IEEE 802.3u-compliant MII, an IEEE 802.3-compliant Twisted-P air T r ansceiver Media Attachment Unit (10BASE-T MAU), and

an IEEE 802.3-compliant Attachment Unit Interface

(AUI). Both proprietary full-duplex and IEEE 802.3

compliant half-duplex operation are supported on the

MII, AUI, GPSI, and 10BASE-T MAU interfaces. 10Mbps operation is supported through the MII, AUI, and

10BASE-T MAU interfaces, and 100 Mbps operation is

supported th rough the MII. The 10BASE-T MAU interface includes an IEEE 802.3-compliant auto-negotiation implementation , whic h wi ll auto mati ca lly ne got iate

between half- and full-duplex with another IEEE 802.3compliant auto-negotiation 10BASE-T device.

The Am79C971 controller is register compatible with

the LANCE (Am7990) E thernet controller, the C-

mode for board-level production connectivity

test

■ Implements low-power management for critical

battery powered application and green PCs

— Includes two power-saving sleep modes

(sleep and snooze)

— Integrated Magic Packet™ technology

support for remote power of networked PCs

■ Software compatible with AMD PCnet Family

and LANCE/C-LANCE register and descriptor

architecture

■ Compatible with the existing PCnet Family

driver/diagnostic software

■ Available in 160-pin TQFP and 176-pin TQFP

packages

LANCE (Am79C90) Ether net controlle r, and all Ethernet controllers in the PCnet Family except ILACC

(Am79C900), including the PCnet-ISA controller

(Am79C960),PCnet-ISA+ controller (Am79C961) ,

PCnet-ISA II con troller (Am79C9 61A), PCnet- 32 controller (Am79C965), PCnet-PCI controller

(Am79C970), and PCnet-PCI II controller

(Am79C970A). The B uffer Management Unit supp orts

the LANCE and PCnet descriptor software models.

The 32-bit multiplexed bus interface unit provides a

direct interface to the PCI local bus, simplifying the

design of an Ethernet node in a PC system. The

Am79C971 controller provides the complete interface

to an Expansion ROM or Flash device allowing add-on

card designs with only a singl e load per PCI bus interface pin. With its built-in suppor t for both little and bi g

endian byte alignment, this controller also addresses

non-PC applications. The Am79C971 controller’s advanced CMOS design allows the bus interface to be

connected to eithe r a +5-V or a +3.3-V s ignalin g environment. A compliant IEEE 1149.1 JTAG test interface

for board-level testing is also provided, as well as a

NAND tree test structure for those systems that cannot

support the JTAG interface.

The Am79C971 controll er suppor ts au to-configuratio n

in the PCI configu ration space. Additional Am79C971

controller configuration parameters, including the

unique IEEE physical address, can be read from an external non-volatile memory (EEPROM) immediately following system reset.

The integrated Manchester encoder/decoder (MENDEC) eliminates the need for an external Serial Interface Adapter (SIA) in the system. The built-in GPSI

allows the MENDEC to be bypassed.

2 Am79C971

Page 3

In addition, the device provides programmable on-chip

LED drivers for trans mit , re ce ive, collis ion, r ecei ve polarity, link integrity, activity, link active, address match,

full-duplex, MII select, 100 Mbps, or jabber status. The

Am79C971 controller also provides an EADI to allow

external hardware address filtering in internetworking

applications and a receive frame tagging feature.

For power sensitive applications where low standby

current is desired, the device incorporates two sleep

functions to reduce overall system power consumption,

excellent for notebooks and green PCs. In conjunctio n

with these low power modes, the PCnet-FAST controller also has integrated functions to suppor t Magic

Packet technology, an inexpensive technology that allows remote wake up of networked PCs.

The controller has the capability to automatically select

either the MII, AUI, or Twisted-Pair transceiver. Only

one interface is active at any one time. Any of the n etwork interfaces can be programmed to operate in either

half-duplex or full-duplex mode (AUI full-duplex only

supports the 10BASE-F standard).

The dual T ransmit and Receive FIFOs optimize system

overhead, providing sufficient latency tolerance at 10

Mbps and for 100-Mbps sys tems where low laten cies

can be guaranteed during frame transmission and

reception.

In highly loaded 10-M bps sys tems, suc h as se r vers or

when using the controll er in a 100-Mbp s environment,

the additional frame buffering capabili ty provided by a

16-bit wide SRAM interface provides high performance

and high latency tolerance on the system bus and network.

The Am79C971 controller can use up to 128 Kbytes of

SRAM as an extension of its dual Transmit and Receive

FIFOs. When no SRAM is used, the Am7 9C971 con-

troller’s FIFOs are programmed to bypass the SRAM

interface.

IMPORT ANT NOTE: A “No SRAM configuration” is only

valid for 10Mb mode. In 100Mb mode, SRAM is mandatory and must always be used.

ISO/IEC 8802-3 and IEEE 802.3 will be used interchangeably when referring to half-duplex 10 Mbps networks. IEEE 802.3 or IE EE 802.3u will be used

interchangeably only when referring to half-duplex 100Mbps Ethernet networks, since the IEEE standard is

not ISO approved yet. Full-duplex is a proprietary standard and is not approved by IEEE or ISO.

Am79C971 3

Page 4

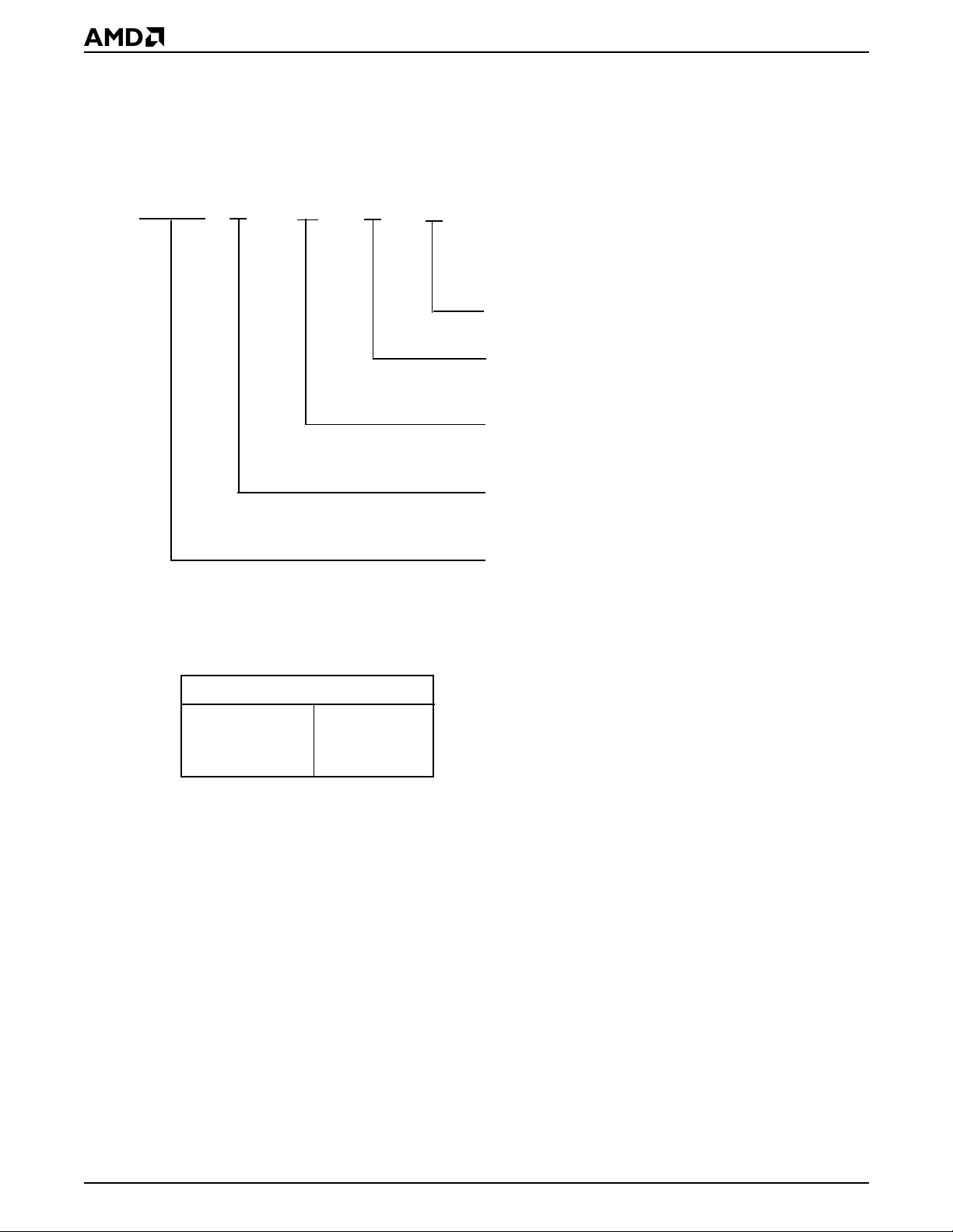

ORDERING INFORMATION

Standard Products

AMD standard produc ts are av ailable in sev eral pac kages and operating r anges. T he order number (Valid Combination) is f ormed

by a combination of the elements below.

Am79C971

K\V

C

\W

ALTERNATE PACKAGING OPTION

\W = Trimmed and formed in a tray

TEMPERATURE RANGE

C = Commercial (0° C to +70° C)

PACKAGE TYPE

K = Plastic Quad Flat Pack (PQR160)

V = Thin Quad Flat Pack (PQL176)

SPEED OPTION

Not applicable

DEVICE NUMBER/DESCRIPTION

Am79C971

Single-Chip Full-Duplex 10/100 Mbps Ethernet

Controller for PCI Local Bus

Valid Combinations

Am79C971

KC\W,

VC\W

Valid Combinations

Valid Combinations list configurations planned to be

supported in volume for this device. Consult the local

AMD sales office to confirm availability of specific

valid combinations and to check on newly released

combinations.

4 Am79C971

Page 5

BLOCK DIAGRAM

CLK

RST

AD[31:00]

C/BE[3:0]

PAR

FRAME

TRDY

IRDY

STOP

IDSEL

DEVSEL

REQ

GNT

PERR

SERR

INTA

SLEEP

PCI Bus

Interface

Unit

Buffer

Management

Unit

Expansion Bus Interface

Bus

Rcv

FIFO

Bus

Xmt

FIFO

FIFO

Control

MAC

Rcv

FIFO

MAC

Xmt

FIFO

Network

Port

Manager

Auto

Negotiation

EBUA_EBA[7:0]

EBDA[15:8]

EBD[7:0]

EROMCS

ERAMCS

AS_EBOE

EBWE

EBCLK

802.3

MAC

Core

Manchester

Encoder/

Decoder

(PLS) &

AUI Port

10BASE-T

MAU

GPSI

Port

MII

Port

EADI

Port

TXEN

TXCLK

TXDAT

RXEN

RXCLK

RXDAT

CLSN

TX_E

TXD[3:0]

TX_EN

TX_CLK

COL

RXD[3:0]

RX_ER

RX_CLK

RX_DV

CRS

MDC

MDIO

SRDCLK

SRD

SF/BD

EAR

RXFRTGD/MIIRXFRTGD

RXFRTGE/MIIRXFRTGE

XTAL1

XTAL2

DO+/DI+/CI+/-

TXD+/TXP+/RXD+/-

TCK

TMS

TDI

TDO

JTAG

Port

Control

93C46

EEPROM

Interface

LED

Control

EECS

EESK

EEDI

EEDO

LED0

LED1

LED2

LED3

20550D-1

Am79C971 5

Page 6

TABLE OF CONTENTS

AM79C971 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Standard Products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

BLOCK DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

RELATED AMD PRODUCTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0

CONNECTION DIAGRAM (PQR160) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

CONNECTION DIAGRAM (PQL176) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

PIN DESIGNATIONS (PQR160) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

PIN DESIGNATIONS (PQL176). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

PIN DESIGNATIONS (PQR160, PQL176). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Listed By Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

PIN DESIGNATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Listed By Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

PIN DESIGNATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Listed By Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Listed By Driver Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

AD[31:0]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

C/BE[3:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

CLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

DEVSEL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

FRAME . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

GNT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

IDSEL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

INTA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

IRDY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

PAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

PERR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Board Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

LED0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

LED1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

LED2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

LED3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

SLEEP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

XTAL1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

XTAL2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EECS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EEDI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EEDO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EESK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Expansion Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EBUA_EBA[7:0]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

EBDA[15:8] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

EBD[7:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

EROMCS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

ERAMCS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

AS_EBOE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

EBWE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

EBCLK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Media Independent Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

6 Am79C971

Page 7

TX_CLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

TXD[3:0]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

TX_EN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

TX_ER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

COL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

CRS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

RX_CLK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

RXD[3:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

RX_DV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

RX_ER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

MDC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

MDIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Attachment Unit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

±. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

CI

DI±. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

DO±. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

10BASE-T Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

± . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

RXD

TXD±. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

TXP±. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

General Purpose Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 5

CLSN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

RXCLK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

RXDAT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

RXEN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

TXCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

TXDAT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

TXEN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

EAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

SFBD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

SRD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

SRDCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

RXFRTGD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

RXFRTGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

MIIRXFRTGD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

MIIRXFRTGE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

IEEE 1149.1 (1990) Test Access Port Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

TCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

TDI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

TDO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

TMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Power Supply Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

AV DDB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

AV SSB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VDD_PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VSS_PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VDDB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VSSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VDD_PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

BASIC FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

System Bus Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Software Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Network Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

DETAILED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Slave Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Am79C971 7

Page 8

Slave Configuration Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Slave I/O Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Master Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Buffer Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Software Interrupt Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Media Access Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Transmit Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Receive Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Loopback Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Manchester Encoder/Decoder. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Attachment Unit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Twisted-Pair Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

General Purpose Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 5

Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Media Independent Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Automatic Network Port Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

External Address Detection Interface (EADI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Expansion Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

LED Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

Power Savings Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

IEEE 1149.1 (1990) Test Access Port Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

The contents of the Device ID register is the same as the contents of CSR88. . . . . . . . . . . . . .100

NAND Tree Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Software Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

USER ACCESSIBLE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

RAP Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

Initialization Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

Receive Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183

Transmit Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

REGISTER PROGRAMMING SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

Am79C971 Programmable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

OPERATING RANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

DC CHARACTERISTICS OV ER COMMERCIAL OPERATING RANGES UNLESS OTHERWISE

SPECIFIED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

SWITCHING CHARACTERISTICS: BUS INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

SWITCHING CHARACTERISTICS: 10BASE-T INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206

SWITCHING CHARACTERISTICS: ATTACHMENT UNIT INTERFACE. . . . . . . . . . . . . . . . . . . . . .207

SWITCHING CHARACTERISTICS: MEDIA INDEPENDENT INTERFACE . . . . . . . . . . . . . . . . . . .208

SWITCHING CHARACTERISTICS: GENERAL-PURPOSE SERIAL INTERFACE . . . . . . . . . . . . .209

SWITCHING CHARACTERISTICS: EXTERNAL ADDRESS DETECTION INTERFACE . . . . . . . .210

KEY TO SWITCHING WAVEFORMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .211

SWITCHING TEST CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .211

SWITCHING WAVEFORMS: SYSTEM BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

SWITCHING WAVEFORMS: EXPANSION BUS INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

SWITCHING WAVEFORMS: 10BASE-T INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .219

SWITCHING WAVEFORMS: ATTACHMENT UNIT INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . .221

SWITCHING WAVEFORMS: MEDIA INDEPENDENT INTERFACE . . . . . . . . . . . . . . . . . . . . . . . .224

8 Am79C971

Page 9

SWITCHING WAVEFORMS: GENERAL-PURPOSE SERIAL INTERFACE . . . . . . . . . . . . . . . . . .226

SWITCHING WAVEFORMS: EXTERNAL ADDRESS DETECTION INTERFACE. . . . . . . . . . . . . .227

SWITCHING WAVEFORMS: RECEIVE FRAME TAG. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .228

PHYSICAL DIMENSIONS* . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

PQR160. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

PQL176 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .230

AM79C971 COMPATIBLE MEDIA INTERFACE MODULES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-1

RECOMMENDATION FOR POWER AND GROUND DECOUPLING. . . . . . . . . . . . . . . . . . . . . . . .B-1

ALTERNATIVE METHOD FOR INITIALIZATION* . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .C-1

LOOK-AHEAD PACKET PROCESSING (LAPP) CONCEPT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .D-1

AUTO-NEGOTIATION REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .E-1

AM79C971A PCNET-FAST 10/100 MBPS PCI ETHERNET CONTROLLER REV A.6 ERRATA . . F-1

Am79C971 9

Page 10

RELATED AMD PRODUCTS

Part No. Description

Am79C90 CMOS Local Area Network Controller for Ethernet (C-LANCE)

Am7996 IEEE 802.3/Ethernet/Cheapernet Tap Transceiver

Am79C98 Twisted Pair Ethernet Transceiver (TPEX)

Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX+)

Am79865 100 Mbps Physical Data Transmitter (PDT)

An79866A 100 Mbps Physical Data Receiver (PDR)

Am79C870 Quad 100BASE-X Transceiver

Am79C871 Quad 100BASE-X Repeater Transceiver

Am79C940 Media Access Controller for Ethernet (MACE™)

Am79C960 PCnet-ISA Single-Chip Ethernet Controller (for ISA bus)

Am79C961 PCnet-ISA+ Single-Chip Ethernet Controller (with Microsoft® Plug n' Play support)

Am79C961A PCnet-ISA II Single-Chip Full-Duplex Ethernet Controller (with Microsoft® Plug n' Play support)

Am79C965 PCnet-32 Single-Chip 32-Bit Ethernet Controller (for 486 and VL buses)

Am79C970A PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus

Am79C981 Integrated Multiport R epeater Plus™ (IMR+™)

Am79C987 Hardware Implemented Management Information Base™ (HIMIB™)

10 Am79C971

Page 11

CONNECTION DIAGRAM (PQR160)

D

IDSEL

VDD

AD23

AD22

VSS

AD21

AD20

VDD_PCI

AD19

AD18

VSSB

AD17

AD16

C/BE2

FRAME

IRDY

TRDY

DEVSEL

STOP

VSSB

PERR

SERR

VDD_PCI

PAR

C/BE1

AD15

AD14

AD13

AD12

VSSB

AD11

AD10

VDD

AD9

AD8

VSS

C/BE0

AD7

AD6

VSSB

AD27

AD26

VDD_PCI

AD25

AD24

C/BE3

VSSB

160

159

158

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

157

414243444546474849505152535455565758596061626364656667687071727374757677787980

156

155

154

AD29

AD28

153

152

AD30

VDD

151

150

AD31

CLK

VSSB

REQ

GNT

149

148

147

146

145

PCnet™-

Am79C971 KC/W

Am79C971

VSS

144

RST

143

INTA

142

TDI

VDD_PCI

141

140

FAST

TDO

TMS

139

138

TCK

137

VSSB

EECS

136

135

VDDB

VDD_PLL

LED2/SRDCLK/MIIRXFRTGE

EESK/LED1/SFBD

EEDI/LED0

EEDO/LED3/SRD/MIIRXFRTG

CI+

CI-

DI+

134

133

131

130

129

128

127

132

69

126

AVDDB

DI-

125

124

DO+

DO-

123

122

AVSSB

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

XTAL2

VSS_PLL

XTAL1

AVDDB

TXD+

TXP+

TXDTXPAVDDB

RXD+

RXDVSS

MDIO

MDC

SLEEP/EAR

RXD3

RXD2

RXD1

RXD0/RXFRTGD

VDDB

RX_DV/RXFRTGE

RX_CLK/RXCLK

RX_ER/RXDAT

VSSB

TX_ER

TX_CLK/TXCLK

TX_EN/TXEN

VDDB

TXD0/TXDAT

TXD1

TXD2

TXD3

COL/CLSN

CRS/RXEN

VSSB

EBD0

EBD1

EBD2

EBD3

EBD4

AD5

AD4

AD3

Pin 1 is marked for orientation.

AD1

AD2

VDD_PCI

AD0

VSSB

EBWE

ERAMCS

AS_EBOE

EBROMCS

2055A-2

VSS

EBCLK

EBUA_EBA0

EBUA_EBA1

VSSB

VDDB

EBUA_EBA2

EBUA_EBA3

EBUA_EBA4

VDDB

EBDA8

EBUA_EBA5

EBUA_EBA6

EBUA_EBA7

EBDA9

EBDA10

EBDA11

VSSB

EBDA12

VDD

EBDA13

EBDA14

EBDA15

EBD6

EBD7

EBD5

VSSB

VSS

Am79C971 11

20550D-2

Page 12

CONNECTION DIAGRAM (PQL176)

NCNCAD24

C/BE3

VSSB

AD25

VDD_PCI

AD26

AD27

AD28

AD29

AD30

VDD

AD31

176

175

174

173

172

171

170

169

168

167

166

165

164

NC

NC

IDSEL

VDD

AD23

AD22

VSS

AD21

AD20

VDD_PCI

AD19

AD18

VSSB

AD17

AD16

C/BE2

FRAME

IRDY

TRDY

DEVSEL

STOP

VSSB

PERR

SERR

VDD_PCI

PAR

C/BE1

AD15

AD14

AD13

AD12

VSSB

AD11

AD10

VDD

AD9

AD8

VSS

C/BE0

AD7

AD6

VSSB

NC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45464748495051525354555657585960616263646566676869707172737475767778798081828384858687

163

REQ

GNT

VSSB

CLK

VSS

RST

162

161

160

159

158

157

PCnetª-

Am79C971 VC/W

Am79C971

INTA

VDD_PCI

156

155

TDI

154

TDO

TMS

153

152

FAST

VC/W

TCK

EECS

VSSB

EESK/LED1/SFBD

LED2/SRDCLK/MIIRXFRTGE

EEDI/LED0

151

150

149

148

147

146

EEDO/LED3/SRD/MIIRXFRTGD

VDDB

VDD_PLL

CI+

CI-

DI+

DI-

AVDDB

DO+

DO-

AVSSBNCNC

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

NC

NC

XTAL2

VSS_PLL

XTAL1

AVDDB

TXD+

TXP+

TXDTXPAVDDB

RXD+

RXDVSS

MDIO

MDC

SLEEP/EAR

RXD3

RXD2

RXD1

RXD0/RXFRTGD

VDDB

RX_DV/RXFRTGE

RX_CLK/RXCLK

RX_ER/RXDAT

VSSB

TX_ER

TX_CLTXCLK

TX_EN/TXEN

VDDB

TXD0/TXDAT

TXD1

TXD2/RXEN

TXD3

99

COL/CLSN

98

CRS/RXEN

97

VSSB

96

EBD0

95

EBD1

94

EBD2

93

EBD3

92

EBD4

91

NC

90

NC

89

88

NC

NC

AD5

AD4

AD3

AD2

AD1

AD0

VDD_PCI

VSSB

ERAMCS

EBWE

AS_EBOE

EBROMCS

VSS

EBCLK

EBUA_EBA0

EBUA_EBA1

EBUA_EBA2

EBUA_EBA3

VSSB

VDDB

EBUA_EBA4

EBUA_EBA5

EBUA_EBA6

EBUA_EBA7

Pin 1 is marked for orientation.

12 Am79C971

VDDB

EBDA8

EBDA9

EBDA10

VSSB

EBDA11

EBDA12

EBDA13

VDD

EBDA14

EBDA15

EBD7

EBD6

VSSB

EBD5

VSS

NC

NC

20550D-3

Page 13

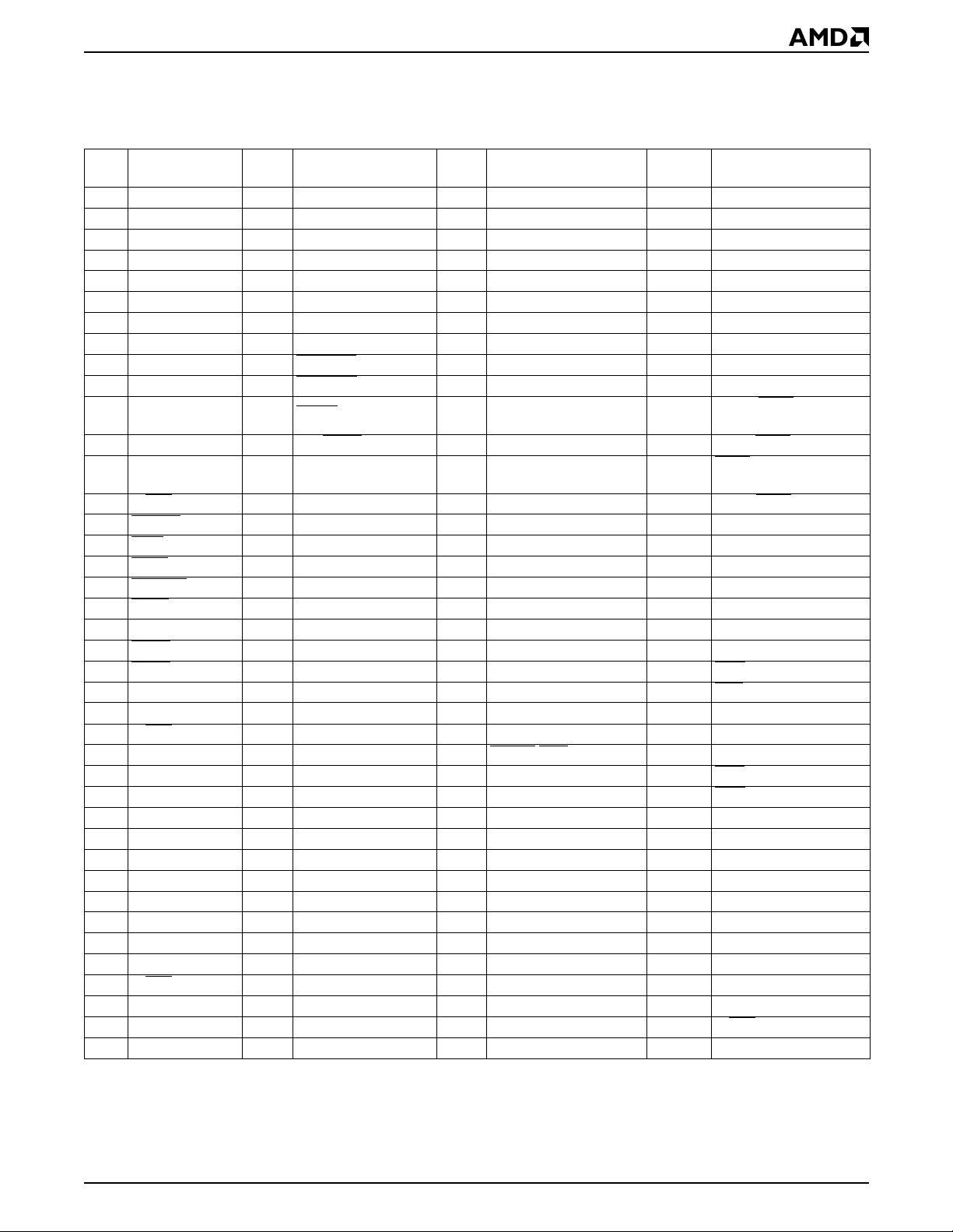

PIN DESIGNATIONS (PQR16 0)

Listed By Pin Number

Pin

Pin

No.

Name

1 IDSEL 41 AD5 81 EBD4 121 AVSSB

2 VDD 42 AD4 82 EBD3 122 DO3 AD23 43 AD3 83 EBD2 123 DO+

4 AD22 44 AD2 84 EBD1 124 AVDDB

5 VSS 45 VDD_PCI 85 EBD0 125 DI6 AD21 46 AD1 86 VSSB 126 DI+

7 AD20 47 AD0 87 CRS/RXEN 127 CI8 VDD_PCI 48 VSSB 88 COL/CLSN 128 CI+

9 AD19 49 ERAMCS 89 TXD3 129 VDD_PLL

10 AD18 50 EROMCS 90 TXD2 130 VDDB

11 VSSB 51 EBWE 91 TXD1 131

12 AD17 52 AS_EBOE 92 TXD0/TXDAT 132 EED1/LED0

13 AD16 53 EBCLK 93 VDDB 133

14 C/BE2 54 VSS 94 TX_EN/TXEN 134 EESK/LED1/SFBD

15 FRAME 55 EBUA_EBA0 95 TX_CLK/TXCLK 135 VSSB

16 IRDY 56 EBUA_EBA1 96 TX_ER 136 EECS

17 TRDY 57 EBUA_EBA2 97 VSSB 137 TCK

18 DEVSEL 58 EBUA_EBA3 98 RX_ER/RXDAT 138 TMS

19 STOP 59 VSSB 99 RX_CLK/RXCLK 139 TDO

20 VSSB 60 EBUA_EBA4 100 RX_DV/RXFRTGE 140 TDI

21 PERR 61 VDDB 101 VDDB 141 VDD_PCI

22 SERR 62 EBUA_EBA5 102 RXD0/RXFRTGD 142 INTA

23 VDD_PCI 63 EBUA_EBA6 103 RXD1 143 RST

24 PAR 64 EBUA_EBA7 104 RXD2 144 VSS

25 C/BE1 65 VDDB 105 RXD3 145 CLK

26 AD15 66 EBDA8 106 SLEEP/EAR 146 VSSB

27 AD14 67 EBDA9 107 MDC 147 GNT

28 AD13 68 EBDA10 108 MDIO 148 REQ

29 AD12 69 EBDA11 109 VSS 149 AD31

30 VSSB 70 VSSB 110 RXD- 150 VDD

31 AD11 71 EBDA12 111 RXD+ 151 AD30

32 AD10 72 EBDA13 112 AVDDB 152 AD29

33 VDD 73 VDD 113 TXP- 153 AD28

34 AD9 74 EBDA14 114 TXD- 154 AD27

35 AD8 75 EBDA15 115 TXP+ 155 AD26

36 VSS 76 EBD7 116 TXD+ 156 VDD_PCI

37 C/BE0 77 EBD6 117 AVDDB 157 AD25

38 AD7 78 VSSB 118 XTAL1 158 VSSB

39 AD6 79 EBD5 119 VSS_PLL 159 C/BE3

40 VSSB 80 VSS 120 XTAL2 160 AD24

Pin

No.

Pin

Name

Pin

No.

Pin

Name

Pin No.

Pin

Name

EEDO/LED3/SRD/

MIIRXFRTGD

LED2/SRDCLK/

MIIRXFRTGE

Am79C971 13

Page 14

PIN DESIGNATIONS (PQL176)

Listed By Pin Number

Pin

Pin

No.

Name

1 NC 45 NC 89 NC 133 NC

2 NC 46 NC 90 NC 134 NC

3 IDSEL 47 AD5 91 EBD4 135 AVSSB

4 VDD 48 AD4 92 EBD3 136 DO5 AD23 49 AD3 93 EBD2 137 DO+

6 AD22 50 AD2 94 EBD1 138 AVDDB

7 VSS 51 VDD_PCI 95 EBD0 139 DI8 AD21 52 AD1 96 VSSB 140 DI+

9 AD20 53 AD0 97 CRS/RXEN 141 CI10 VDD_PCI 54 VSSB 98 COL/CLSN 142 CI+

11 AD19 55 ERAMCS 99 TXD3 143 VDD_PLL

12 AD18 56 EROMCS 100 TXD2/RXEN 144 VDDB

13 VSSB 57 EBWE 101 TXD1 145

14 AD17 58 AS_EBOE 102 TXD0/TXDAT 146 EED1/LED0

15 AD16 59 EBCLK 103 VDDB 147

16 C/BE2 60 VSS 104 TX_EN/TXEN 148 EESK/LED1/SFBD

17 FRAME 61 EBUA_EBA0 105 TX_CLK/TXCLK 149 VSSB

18 IRDY 62 EBUA_EBA1 106 TX_ER 150 EECS

19 TRDY 63 EBUA_EBA2 107 VSSB 151 TCK

20 DEVSEL 64 EBUA_EBA3 108 RX_ER/RXDAT 152 TMS

21 STOP 65 VSSB 109 RX_CLK/RXCLK 153 TDO

22 VSSB 66 EBUA_EBA4 110 RX_DV/RXFRTGE 154 TDI

23 PERR 67 VDDB 111 VDDB 155 VDD_PCI

24 SERR 68 EBUA_EBA5 112 RXD0/RXFRTGD 156 INTA

25 VDD_PCI 69 EBUA_EBA6 113 RXD1 157 RST

26 PAR 70 EBUA_EBA7 114 RXD2 158 VSS

27 C/BE1 71 VDDB 115 RXD3 159 CLK

28 AD15 72 EBDA8 116 SLEEP/EAR 160 VSSB

29 AD14 73 EBDA9 117 MDC 161 GNT

30 AD13 74 EBDA10 118 MDIO 162 REQ

31 AD12 75 EBDA11 119 VSS 163 AD31

32 VSSB 76 VSSB 120 RXD- 164 VDD

33 AD11 77 EBDA12 121 RXD+ 165 AD30

34 AD10 78 EBDA13 122 AVDDB 166 AD29

35 VDD 79 VDD 123 TXP- 167 AD28

36 AD9 80 EBDA14 124 TXD- 168 AD27

37 AD8 81 EBDA15 125 TXP+ 169 AD26

38 VSS 82 EBD7 126 TXD+ 170 VDD_PCI

39 C/BE0 83 EBD6 127 AVDDB 171 AD25

40 AD7 84 VSSB 128 XTAL1 172 VSSB

41 AD6 85 EBD5 129 VSS_PLL 173 C/BE3

42 VSSB 86 VSS 130 XTAL2 174 AD24

43 NC 87 NC 131 NC 175 NC

44 NC 88 NC 132 NC 176 NC

Pin

No.

Pin

Name

Pin

No.

Pin

Name

Pin No.

Pin

Name

EEDO/LED3/SRD/

MIIRXFRTGD

LED2/SRDCLK/

MIIRXFRTGE

14 Am79C971

Page 15

PIN DESIGNATIONS (PQR160, PQL176)

Listed By Group

Pin Name Pin Function Type

PCI Bus Interface

AD[31:0] Address/Data Bus IO TS3 32

C/BE[3:0] Bus Command/Byte Enable IO TS3 4

CLK Bus Clock I NA 1

DEVSEL Device Select IO STS6 1

FRAME Cycle Fram e IO STS6 1

GNT Bus Grant I NA 1

IDSEL Initialization Device Select I NA 1

INTA Interrupt O OD6 1

IRDY Initiator Ready IO STS6 1

PAR Parity IO TS3 1

PERR Parity Error IO STS6 1

REQ Bus Request O TS3 1

RST Reset I NA 1

SERR System Error IO OD6 1

STOP Stop IO STS6 1

TRDY Target Ready IO STS6 1

Board Interface

LED0 LED0 O LED 1

LED1 LED1 O LED 1

LED2 LED2 O LED 1

LED3 LED3 O LED 1

SLEEP Sleep Mode I NA 1

XTAL1 Crystal Input I NA 1

XTAL2 Crystal Output O XTAL 1

EEPROM Interface

EECS Serial EEPROM Chip Select O O6 1

EEDI Serial EEPROM Data In O LED 1

EEDO Serial EEPROM Data Out I NA 1

EESK Serial EEPROM Clock IO LED 1

Expansion ROM Interface

AS_EBOE Address Strobe/Expansion Bus Output Enable O O6 1

EBCLK Expansion Bus Clock I NA 1

EBD[7:0] Expansion Bus Data [7:0] IO TS6 8

EBDA[15:8] Expansion Bus Data/Address [15:8] IO TS6 8

EBUA_EBA[7:0]

EBWE Expansion Bus Write Enable O O6 1

ERAMCS Expansion Bus RAM Chip Select O O6 1

EROMCS Expansion Bus ROM Chip Select O O6 1

Note:

1. Not including test features

Expansion Bus Upper Addres s /Expansion Bus Addres s

[7:0]

1

O O6 8

Driver No. of Pins

Am79C971 15

Page 16

PIN DESIGNATIONS

Listed By Group

Pin Name Pin Function Type

Media Independent Interface (MII)

COL Collision I NA 1

CRS Carrier Sense I NA 1

MDC Management Data Clock O OMII2 1

MDIO Management Data I/O IO TSMII 1

RX_CLK Receive Clock I NA 1

RXD[3:0] Receive Data I NA 4

RX_DV Receive Data Valid I NA 1

RX_ER Receive Error I NA 1

TX_CLK Transmit Clock I NA 1

TXD[3:0] Transmit Data O OMII1 4

TX_EN Transmit Data Enable O OMII1 1

TX_ER Transmit Error O OMII1 1

Attachment Unit Interface (A UI)

CI± AUI Collis ion I NA 1

DI± AUI Data In I NA 1

DO± AUI Data Out O DO 1

10BASE-T Interface

RXD+/RXD- Receive Differential Pair I NA 2

TXD+/TXD- Transmit Differential Pair O TDO 2

TXP+/TXP- Transmit Pre-distortion Differential Pair O TPO 2

General Purpose Serial Interface (GPSI)

CLSN Collision IO NA 1

RXCLK Receive Clock I NA 1

RXDAT Receive Data I NA 1

RXEN Receive Enable I NA 1

TXCLK Transmit Clock I NA 1

TXDAT Transmit Data O O6 1

TXEN Transmit Enable O O6 1

External Address Detection Interface (EADI)

EAR External Address Reject Low I NA 1

SFBD Start Frame Byte Delimiter O LED 1

SRD Serial Receive Data IO LED 1

SRDCLK Serial Receive Data Clock IO LED 1

RXFRTGD/MIIRXFRTGD

RXFRTGE/MIIRXFRTGE

IEEE 1149.1 Test Access Port Interface (JTAG)

TCK Test Clock I NA 1

TDI Test Data In I NA 1

TDO Test Data Out O TS6 1

TMS Test Mode Sele ct I NA 1

Note:

1. Not including test features.

Receive Frame Tag Data/MII Receive Frame

Tag Data

Receive Frame T ag Enable/MII Receive Fr ame

Tag Enable

1

I NA 1

I NA 1

Driver No. of Pins

16 Am79C971

Page 17

PIN DESIGNATIONS

Listed By Group

Pin Name Pin Function Type

Power Suppli es

AVDDB Analog I/O Buffer Power P NA 3

AVSSB Analog I/O Buffer Ground P NA 1

VDD_PLL Analog PLL Power P NA 1

VSS_PLL Analog PLL Ground P NA 1

VDD Digital Power P NA 4

VSS Digital Ground P NA 6

VDDB I/O Buffer Power P NA 5

VSSB I/O Buffer Ground P NA 13

VDD_PCI PCI I/O Buffer Power P NA 5

Note:

1. Not including test features.

1

Driver No. of Pins

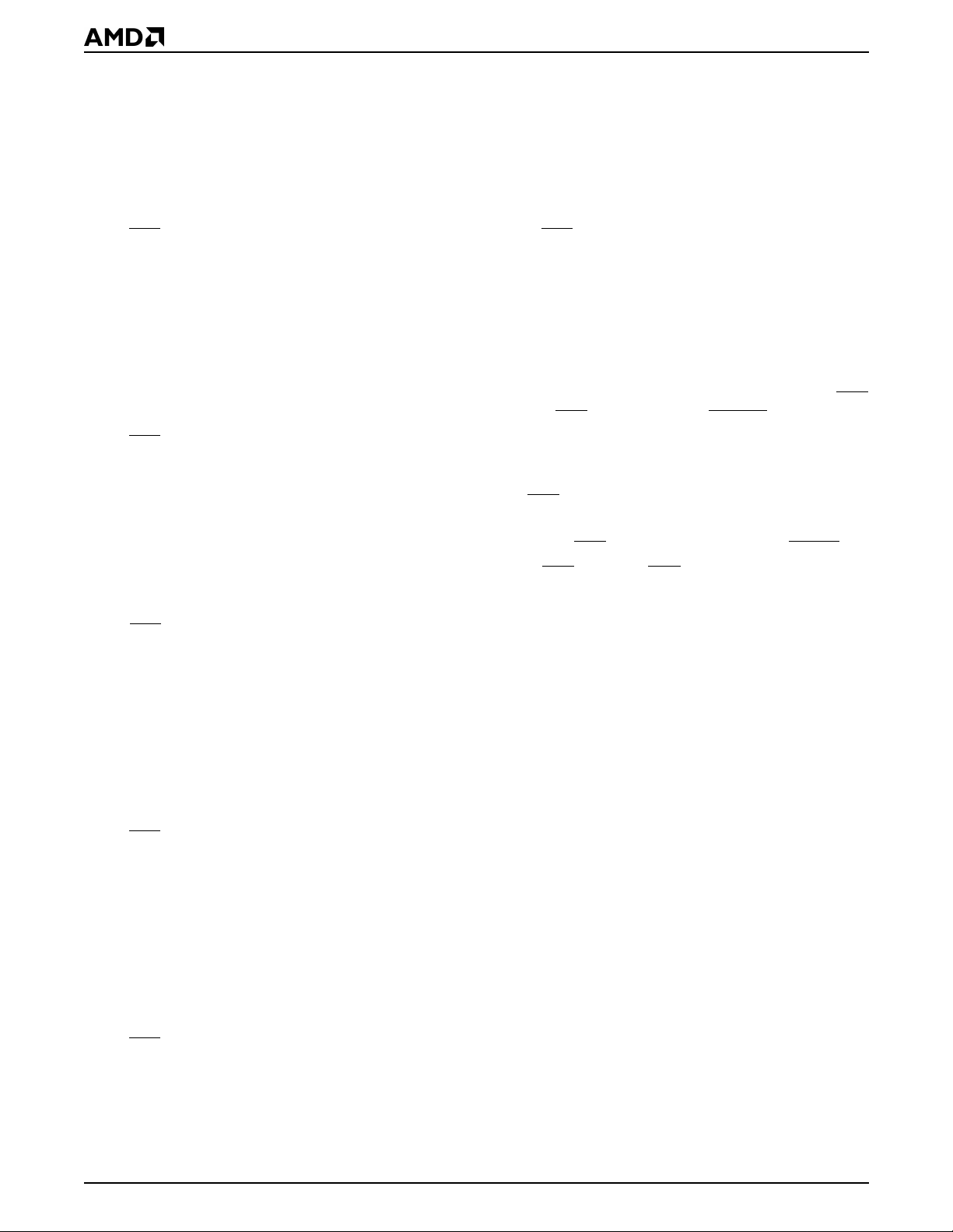

Listed By Driver Type

The following table describes th e various type s of o utput drive rs used i n the Am79C9 71 contro ller . All I

values shown in the table apply to 5 V signaling.

I

OH

See the DC Characteristics section for the values ap-

OL

and

A sustained tri-state signal is a low active signal that is

driven high for one clock period before it is left floating.

DO, TDO, and TPO are differential output drivers. Their

characteristics and t he o ne of the XTAL output a re described in the DC Characteristics section.

plying to 3.3 V signaling.

Name Type IOL (mA) IOH (mA) Load (pF)

LED LED 12 -0.4 50

OMII1 Totem Pole 4 -4 50

OMII2 Totem Pole 4 -4 390

O6 Totem Pole 6 -0.4 50

OD6 Open Drain 6 NA 50

STS6 Sustained Tri-State 6 -2 50

TS3 Tri-State 3 -2 50

TS6 Tri-State 6 -2 50

TSMII Tri-State 4 -4 470

Am79C971 17

Page 18

PIN DESCRIPTIONS

PCI Interfa ce

AD[31:0]

Address and Data Input/Output

Address and data ar e multi pl exed on the same bus in terface pins. During the fir st clock of a transaction,

AD[31:0] contain a physical address (32 bits). During

the subsequent clocks, AD[31:0] contain data. Byte ordering is littl e endian by default. AD[07:0] are define d

as the least significant byte (LSB) and AD[31:24] are

defined as the most significant byte (MSB). For FIFO

data transfers, the Am79C971 controller can be programmed for big endian byte ordering. See CSR3, bit 2

(BSWP) for more details.

eration section for details. The Am79C971 controller

will support a clock frequency of 0 MHz after certain

precautions are taken to ensure data integrity. This

clock or a derivation i s not used to dr ive any network

functions.

When RST

testing.

is active, CLK is an inp ut for NAND tree

DEVSEL

Device Select Input/Output

The Am79C971 controller dr ives DEVSEL when it detects a transaction that selects the device as a target.

The device samples DEVSEL

claims a transaction that the Am79C971 controller has

initiated.

to detect if a target

During the address phase of the transaction, when the

Am79C971 controller is a bus master , AD[31:2] will address the active Double Word (DWord). The

Am79C971 controller alwa ys drives AD[1:0] to ’00’ dur-

ing the address phase indicating linear burst order.

When the Am79C971 controller is not a bus master, the

AD[31:0] lines are continuously monitored to determine

if an address match exists for slave transfers.

During the data phase of the transacti on, AD[31: 0] are

driven by the Am79C971 controller wh en performing

bus master write and slave read operations. Data on

AD[31:0] is latched by the Am79C971 co ntroller when

performing bus master read and slave write operations.

When RST

testing.

is active, AD[31:0] are inputs for NAND tree

C/BE[3:0]

Bus Command and Byte Enables Input/Output

Bus command and byte enables are multiplexed on the

same bus interface pins. During the a ddress phase o f

the transaction, C /BE

During the data phase, C/BE

ables. The byte enables define which physical byte

lanes carry meaningful data. C/BE

(AD[07:0]) and C/BE

The function of the byte enables is ind ependen t of th e

byte ordering mode (BSWP, CSR3, bit 2).

When RST

tree testing.

is active, C/BE[3:0] are inputs for NAND

[3:0] define th e bus command.

[3:0] are used as byte en -

0 applies to byte 0

3 applies to byte 3 (AD[31:24 ]).

CLK

Clock Input

This clock is used to drive the system bus interface and

the internal buffer management unit. All bus signals are

sampled on the rising edge of CLK and all parameters

are defined with resp ect to this edge. The A m79C971

controller normally operates over a frequency range of

10 to 33 MHz on the PCI bus due to networking demands. See the Frequency Demands for Networ k Op-

When RST

testing.

is activ e, DEVS EL is an inp ut f or NAND tr ee

FRAME

Cycle Frame Input/Output

FRAME is driven by the Am79 C971 controll er when it

is the bus master to indicate the beginning and duration

of a transaction. FRAME

transaction is beginning. FRAME

data transfers continue. FRAME

the final data phase o f a transaction. When the

Am79C971 controller is in slave mode, it samples

FRAME

tion.

When RST is active, FRAME is an input f or NAND tree

testing.

to determ ine the ad dress phas e of a tran sac-

is asser ted to indica te a bus

is asserted while

is deasserted before

GNT

Bus Grant Input

This signal indicates that the access to the bus has

been granted to the Am79C971 controller.

The Am79C971 controller supports bus parking. When

the PCI bus is idle and the system arbiter asserts GNT

without an active REQ from the Am79C971 controller,

the device will drive the AD[31:0], C/BE

lines.

When RST is active, GNT is an input for NAND tree

testing.

[3:0] and PAR

IDSEL

Initialization Device Select Input

This signal is used as a c hip sele ct for the Am79C97 1

controller duri ng configura tion read a nd write transactions.

When RST

testing.

1. Not including test features.

is active, IDSEL is an input for NAND tree

18 Am79C971

Page 19

INTA

Interrupt Request Output

An attention signal which indicates that one or more of

the following status flags is set: BABL, EXDINT, IDON,

JAB, MERR, MISS, MFCO, MPINT, RCVCCO, RINT,

SINT, SLPINT, TINT, TXSTRT, UINT, MCCIINT, MCCINT, MPDTINT, MAPINT, MREINT, and STINT. Each

status flag has either a mask or an enable bit which allows for suppression of INTA

the flag meanings.

Table 1. Interrupt Flags

Name Description Mask Bit Interrupt Bit

BABL Babble CSR3, bit 14 CSR0, bit 14

EXDINT

IDON

JAB Jabber CSR4, bit 0 CSR4, bit 1

MERR Memory Error CSR3, bit 11 CSR0, bit 11

MISS Missed Frame CSR3, bit 12 CSR0, bit 12

MFCO

MPINT

RCVCCO

RINT

SLPINT Sleep Interrupt CSR5, bit 8 CSR5, bit 9

SINT System Error CSR5, bit 10 CSR5, bit 11

TINT

TXSTRT Transmit Start CSR4, bit 2 CSR4, bit 3

UINT User Interrupt CSR4, bit 7 CSR4, bit 6

MCCIINT

MCCINT

MPDTINT

Excessive

Deferral

Initialization

Done

Missed Frame

Count Overflow

Magic Packet

Interrupt

Receive

Collision Count

Overflow

Receive

Interrupt

Transmit

Interrupt

Internal MII

Management

Command

Complete

Interrupt

MII

Management

Command

Complete

Interrupt

MII PHY Detect

Transition

Interrupt

assertio n. Table 1 shows

CSR5, bit 6 CSR5, bit 7

CSR3, bit 8 CSR0, bit 8

CSR4, bit 8 CSR4, bit 9

CSR5, bit 3 CSR5, bit 4

CSR4, bit 4 CSR4, bit 5

CSR3, bit 10 CSR0, bit 10

CSR3, bit 9 CSR0, bit 9

CSR7, bit 2 CSR7, bit 3

CSR7, bit 4 CSR7, bit 5

CSR7, bit 0 CSR7, bit 1

Table 1. Interrupt Flags

Name Description Mask Bit Interrupt Bit

MAPINT

MREINT

STINT

By default INTA

MII Auto-Poll

Interrupt

MII

Management

Frame Read

Error Interrupt

Software Timer

Interrupt

CSR7, bit 6 CSR7, bit 7

CSR7, bit 8 CSR7, bit 9

CSR7, bit 10 CSR7, bit 11

is an open-drain output. For applications that need a high-active edge-sensitive interrupt

signal, the INTA

pin can be configured f or this mode by

setting INTLEVEL (BCR2, bit 7) to 1.

When RST is active, INTA is the outp ut for NAND tree

testing.

IRDY

Initiator Ready Input/Output

IRDY indicates the ability of the initiator of the transaction to complete the current data phase. IRDY

in conjunct i on wi t h T RDY

both IRDY

and TRDY are asser ted simultaneously. A

. Wait states are inserted until

is used

data phase is completed on any clock when both IRDY

and TRDY are asserted.

When the Am79C971 c ontroll er is a bus mas ter, it asserts IRDY during all write data phases to indicate that

valid data is present on AD[31:0]. Durin g all read dat a

phases, the device asserts IRDY

to indicate that it is

ready to accept the data.

When the Am79C971 controller is the target of a trans-

action, it checks IRDY

during all write data phases to

determine if valid data is presen t on AD[31:0]. During

all read data phases, the device checks IRDY

to deter-

mine if the initiator is ready to accept the data.

When RST is active, IRDY is an input for NAND tree

testing.

PAR

Parity Input/Output

Parity is even parity across AD[31:0] a nd C/BE[3:0].

When the Am79C971 controller is a bus master , it generates parity during the address and write data phases.

It checks parity during read data phases. When the

Am79C971 controller operates in slave mode, it checks

parity during ev ery address phase. When it is the target

of a cycle, it checks parity during write data phases and

it generates parity during read data phases.

When RST

testing.

is active, PA R is an input for NAND tree

Am79C971 19

Page 20

PERR

Parity Error Input/Output

During any slave write transaction and any master read

transaction, the Am79C971 contro ller asserts PE RR

when it detects a dat a pa rity error and reporting of the

error is enabled by setting PERREN (PCI Command

register, bit 6) to 1. During any master write transaction,

the Am79C971 control ler monit ors PERR

target reports a data parity error.

When RST is active, PERR is an in put for NAND tree

testing.

to see if the

REQ

Bus Request Input/Output

The Am79C971 controller asserts REQ pin as a signal

that it wishes to become a bus mas ter. REQ

high when the Am79C971 control ler does not request

the bus. During M a gi c Packet

not be driven.

When RST is active, REQ is an input for NAND tree

testing.

mode, the REQ pin will

is driven

RST

Reset

Input

When RST

troller performs an internal system reset of the type

H_RESET (HARDWARE_RESET, see section on RESET). RST

riods. While in the H_RESET state, the Am79C971

controller will disable or deassert all outputs. RST

be asynchronous to clock when asser ted or deasserted.

When RST

is asserte d low, then the Am79C971 con-

must be held for a minimum of 30 clock pe-

may

is active, NAND tree testing is enabled.

SERR

System Error Input/Output

During any slave transaction, the Am79C971 controller

asserts S ERR

and reporting of the error is enabled by setting PERREN (PCI Command register, bit 6) and SERREN (PCI

Command register, bit 8) to 1.

By default SERR

nent test, it can be programmed to be an active-high

totem-pole output.

When RST

testing.

when it detects a n add re ss p ar i ty er r or,

is an open-drain out put. For compo-

is active, SERR is an input for NAND tree

STOP

Stop Input/Output

In slave mode, the Am79C971 controller drives the

signal to inform the bus master to stop the cur-

STOP

rent transaction. In bus mas ter mode, the Am79C97 1

controller checks STOP

to disconnect the current transaction.

When RST is active, STOP is an input for NAND tree

testing.

to determine if the target wants

TRDY

Target Ready Input/Output

TRDY indicates the ability of the target of the transa ction to complete the current data phase. Wait states are

inserted until both IRDY

taneously. A data phase is completed on any clock

when both IRDY

When the Am79C971 controller is a bus master, it

checks TRD Y during all read data phases to determine

if vali d data is present on AD[31: 0]. Duri ng all write data

phases, the device checks TRDY

target is ready to accept the data.

When the Am79C971 controller is the target of a transaction, it asser ts TRDY

indicate that valid data is present on AD[31 :0]. Durin g

all write data phases, the device ass erts TRDY

cate that it is ready to accept the data.

When RST is active, TRDY is an input for NAND tree

testing.

and TRDY are asserted.

and TRDY are asserted simul-

to determine if th e

during all read data phases to

to indi-

Board Interface

Note: Before programming the LED pins, see the

description of LEDPE in BCR2, bit 12 first.

LED0

LED0 Output

This output is designed to directly drive an LED. By defaul t, LED 0

10BASE-T interface. This pin can also be programmed

to indicate other network status (see BCR4). The LED0

pin polarity is programmable, but by default it is active

LOW. Whe n the LED0

active LOW, the output is an open d rain driver. When

the LED0

the output is a totem pole driver.

Note: The LED0 pin is multiplexed with the EEDI pin.

When RST

testing.

indicates an ac tive link connection on the

pin polarity is programmed to

pin polar ity is progra mmed to act ive HIGH,

is active, LED0 is an input for NAND tree

LED1

LED1 Output

This output is designed to directly drive an LED. By default, LED1

This pin can also be programmed to indicate other network status (see BCR5). T he LED1

grammable, but by default, it is active LOW. When the

LED1

output is an open drain driver. When the LED1

indicates receive activity on the network.

pin polarity is pro-

pin polarity is programmed to active LOW, the

pin po-

20 Am79C971

Page 21

larity is pr ogrammed to active HIGH, th e output is a

totem pole driver.

Note: The LED1 pin is multiplexed with the EESK and

SFBD pins.

The LED1

Detection to deter mine whe ther or not an EE PROM is

present at the Am79C971 controller interface. At the

last rising edge of CLK while RST

is sampled to determine the value of the EEDET bit i n

BCR19. It is important to maintain ad equate hold time

around the rising edge of the CLK at this time to ensure

a correctly sampled value. A sampled HIGH value

means that an EEPROM is present, and EEDET will be

set to 1. A sampled LOW value means that an EEPROM is not present, and EEDET will be set to 0. See

the EEPROM Auto-Detection section for more details.

If no LED circuit is to be attached to this pin, then a pull

up or pull down resistor must be attached instead i n

order to resolve the EEDET setting.

When RST

testing.

WARNING: The input signal level of LED1 must b e

insured for correct EEPROM detection before the

deassertion of RST

pin is also used dur ing EEPROM Auto-

is active LOW , LED1

is active, LED1 is an input for NAND tree

.

LED2

LED2 Output

This output is designed to directly drive an LED. By default, LED2

10BASE-T interface. This pin can also be programmed

to indicate other network status (see BCR6). The LED2

pin polarity is programmable, but by default it is active

LOW. Whe n the LED2

active LOW, the output is an open drain driver. When

the LED2

the output is a totem pole driver.

indicates correct receive polarity on the

pin polarity is programmed to

pin polar ity is progra mmed to act ive HIGH,

LED while an EEPROM is used in the system, then

buffering is required between the LED3

LED circuit. If an LED c ircuit were directl y attached t o

this pin, it would crea te an I

not be met by the serial EEPROM attached to this pin.

If no EEPROM is inclu ded in the system design, then

the LED3

without buffering. For more details regarding LED connection, see the section on LED Support.

Note: The LED3

SRD, MIIRXFRTGD pins.

When RST

testing.

signal may be directly connected to an LED

pin is multiplexed with the EEDO,

is active, LED3 is an input for NAND tree

OL requirement that could

pin and the

SLEEP

Sleep Input

When SLEEP is asser ted, the Am79C9 71 controller

performs an internal system reset of the H_RESET

type and then proceeds into a power savings mode. All

Am79C971 controller outputs will be placed in their

normal reset condition. All Am79C971 controller inputs

will be ignored except for the SLEEP

tem must refrain from star ting th e network operations

of the Am79C971 controller for 0.5 se conds following

the deasser tion o f the SLEEP

ternal analog circuits to stabilize.

For effects with the Magic Packet™ modes, se e the

Magic Packet section.

Both CLK and XTAL1 inputs must have valid clock signals present in order for the SLEEP

effect.

The SLEEP pin should not be asserted during power

supply ramp up. If it is desired that SLEEP

at power supply ramp up, then the system must delay

the assertion of SLEEP

completion of hardware reset.

until three clock cycles after the

pin itself . The sys-

pin in order to allow in-

command to take

be asserted

Note: The LED2 pin is multiplexed with the SRDCLK

pin and the MIIRXFRTGE pins.

When RST

testing.

is active, LED2 is an input for NAND tree

LED3

LED3 Output

This output is designed to directly drive an LED. By default, LED3

This pin can also be programmed to indicate other network status (see BCR7). T he LED3

gramma ble, but by defaul t it is active LOW. When th e

LED3

output is an open d rain driver. When the LED3

larity is pr ogrammed to active HIGH, th e output is a

totem pole driver.

Special attention must be given to the external circuitry

attached to this pin. Whe n this pin is used to dri ve an

indicates tran smit activity on the network .

pin polarity is pro-

pin polarity is programmed to active LOW, the

pin po-

Am79C971 21

WARNING: The SLEEP pin must not be left unconnected. It should be tied to VDD if the power saving

mode is not used.

Note: The SLEEP

When RST

testing.

is active, SLEEP is an input for NAND tree

pin is multiplexed with the EAR pin.

XTAL1

Crystal Oscillator In Input

The internal clock generator uses a 20-MHz crystal that

is attached to the pins XTAL1 and XTAL2. The network

data rate is one-half of the cr ystal frequency. XTAL1

may alternatively be driven using an external 20- MHz

CMOS level clock signal. Refer to the section on Exter-

nal Crystal Characte ristic s for more details. This clock

is always required whether or not the internal

10BASE-T/AUI ports are enabled. If the internal PHY is

Page 22

not used, ±10% accuracy is sufficient for the clock

source.

Note: When the Am79C971 controller is in coma

mode, t here is an i nternal 2 2 k

ground. If an external source drives XTAL1, some

power consumption will be consumed driving this resistor. If XTAL1 is driven LOW at this time, power consumption will be minimized. In this case, XTAL1 must

remain active for at least 30 cycles after the as ser tion

of SLEEP

and deassertion of REQ.

Ω resistor fr om X TAL1 to

XTAL2

Crystal Oscillator Out Output

The internal clock generator uses a 20-MHz crystal that

is attached to the pins XT AL1 and XTAL2. The network

data rate is one-half of the cry stal frequenc y. If an external clock source is used on XTAL1, then XTAL2

should be left unconnected.

EEPROM Interface

EECS

EEPROM Chip Select Output

This pin is designed to directly interface to a serial EEPROM that uses the 93C46 EEPROM interface protocol. EECS is connected to the EEPROM ’s chip select

pin. It is controll ed by either the Am 79C971 controll er

during command portions of a read of the entire EEPROM, or indirectly by the host system by writing to

BCR19, bit 2.

When RST

testing.

is active, EECS is an input for NAND tree

EEDI

EEPROM Data In Output

This pin is designed to directly interface to a serial

EEPROM that uses the 93C46 EEPROM interface protocol. EEDI is connecte d to the EEPROM’s data input

pin. It is controll ed by either the Am 79C971 controll er

during command portions of a read of the entire

EEPROM, or indirectly by the host system by writing to

BCR19, bit 0.

Note: The EEDI pin is multiplexed with the LED0

When RST

testing.

is active, EEDI is an input for NAND tree

pin.

EEDO

EEPROM Data Out Input

This pin is designed to di rectly interface to a serial

EEPROM that uses the 93C46 EEPROM interface protocol. EEDO is connecte d to the EEPROM’s data output pin. It is controlled by either the Am79C971

controller during command portions of a read of the entire EEPROM, or indirectly by the host system by reading from BCR19, bit 0.

Note: The EEDO pin is multiplexed with the LED3,

MIIRXFRTGD, and SRD pins.

When RST

testing.

is active, EEDO is an input for NAND tree

EESK

EEPROM Serial clock Input/Output