Page 1

■

■

■

■

■

■

■

■

■

PRELIMINARY

Am79C90

CMOS Local Area Network Controller for Ethernet

(C-LANCE)

DISTINCTIVE CHARACTERISTICS

Compatible with Ethernet and IEEE 802.3

10BASE-5 Type A, and 10BASE-2 Type B,

“Cheapernet,” 10BASE-T

Easily interfaced with 80x86, 680x0, Am29000

™

Z8000

microprocessors

On-board DMA and buffer management, 64-byte

Receive, 48-byte Transmit FIFOs

24-bit-wide linear addressing (Bus Master Mode)

Network and packet error reporting

,

Back-to-back packet reception with as little as

0.5 µ s interframe spacing

Diagnostic Routines

—Internal/external loopback

—CRC logic check

—Time domain reflectometer

Low power consumption for power-sensitive

applications

Completely software- and hardware-compatible with

AMD’s LANCE device (Am7990) (see Appendix A)

GENERAL DESCRIPTION

The Am79C90 CMOS Local Area Network Controller

for Ethernet (C-LANCE) is a 48-pin VLSI device designed to greatly simplify interfacing a microcomputer or

minicomputer to an IEEE 802.3/Ethernet Local Area

Network. The C-LANCE, in conjunction with the

Am7992B Serial Interface Adapter (SIA), Am7996 or

Am79C98 and Am79C100 Transceiver, and closely

coupled local memory and microprocessor, is intended

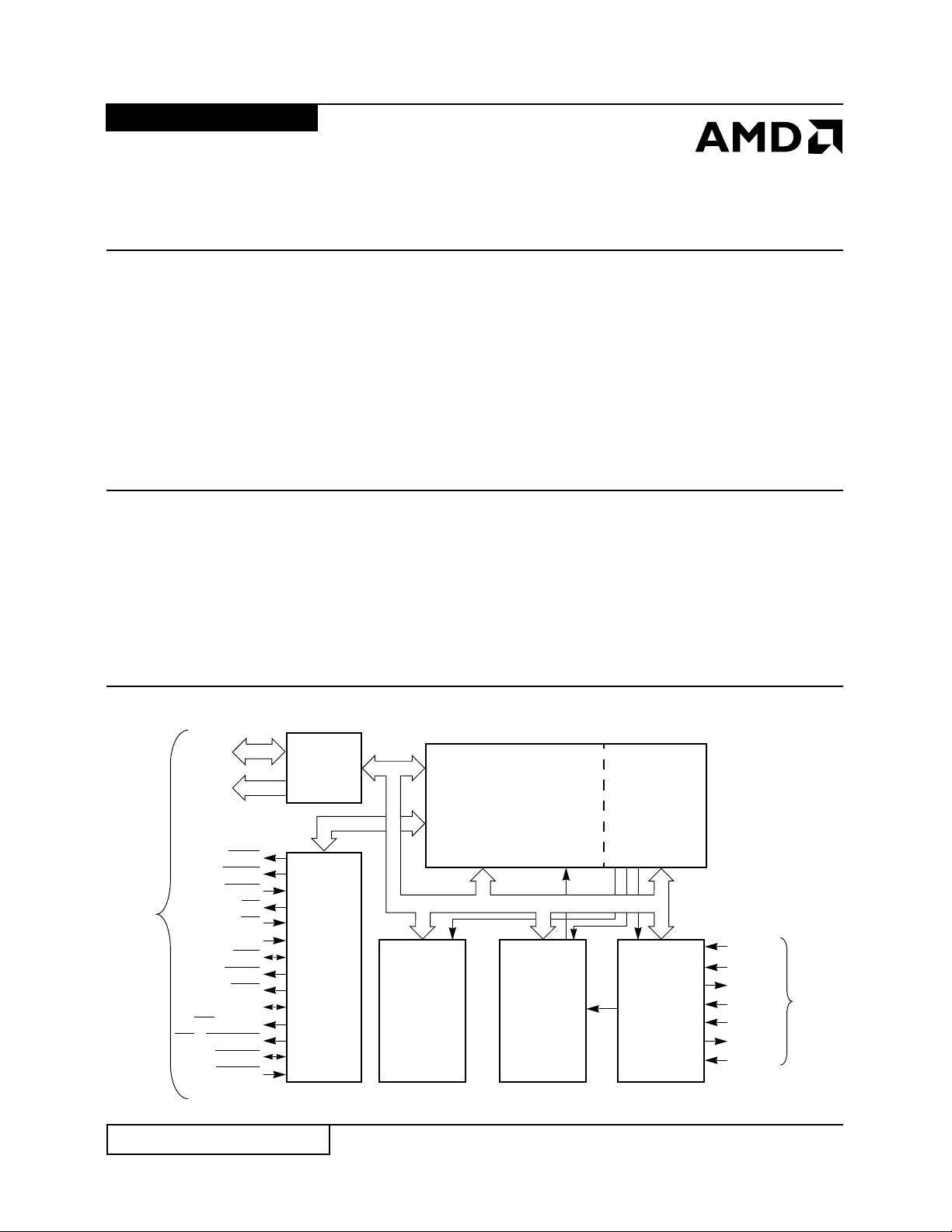

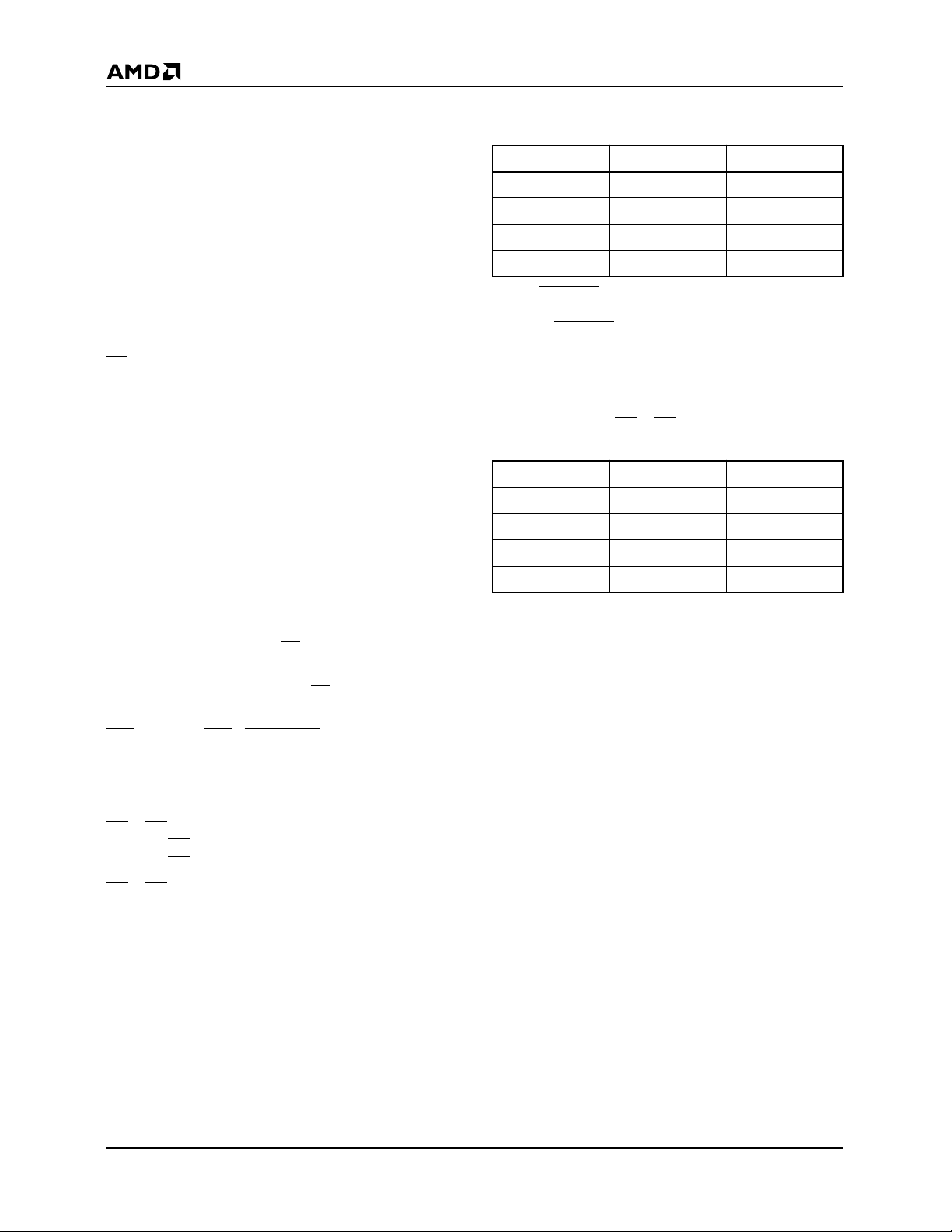

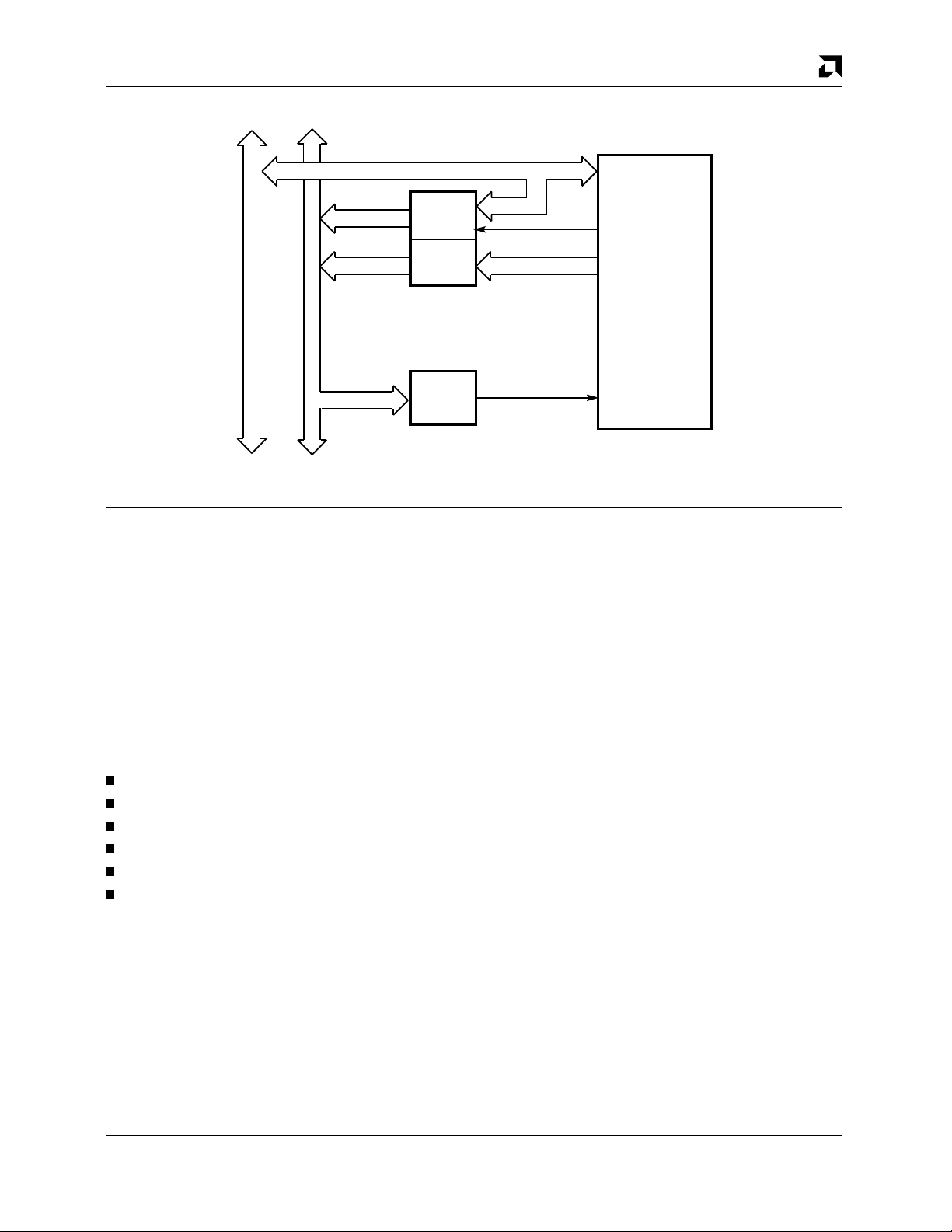

BLOCK DIAGRAM

Parallel

Bus

Interface

C-LANCE/

CPU

Control

Bus

Interface

Station

Address

Detection

Local CPU Interface

DAL15:0

A23:16

BM

1/BUSAKO

BM

INTR

HOLD

HLDA

ALE/AS

CS

ADR

AS

D

DALO

DALI

READ

0/BYTE

READY

RESET

to provide the user with a complete interface module for

an Ethernet network. The Am79C90 is designed using

a scalable CMOS technology and is compatible with a

variety of microprocessors. On-board DMA, advanced

buffer management, and extensive error reporting and

diagnostics facilitate design and improve system

performance.

DMA/Data

Path Control

Retry

Logic

Microprogram

Store

Serial I/O

Interface

RX

RCLK

TX

TCLK

CLSN

TENA

RENA

17881C-1

Am7992B SIA Interface

Publication# 17881 Rev: CAmendment/0

Issue Date: January 1998

This document contains information on a product under development at Advanced Micro Devices. The

information is intended to help you evaluate this product. AMD reserves the right to change or discontinue

work on this proposed product without notice.

1

Page 2

AMD

P R E L I M I N A R Y

RELATED AMD PRODUCTS

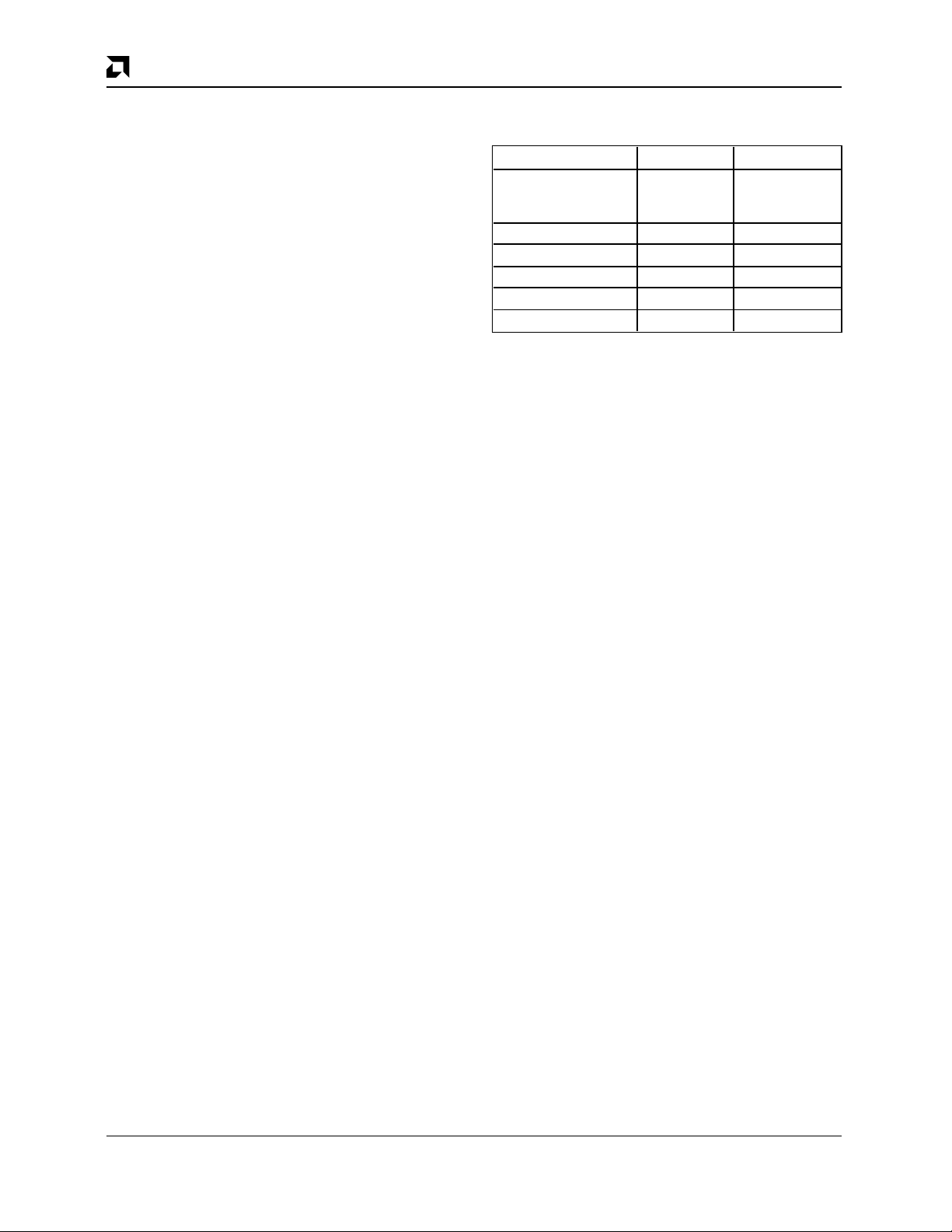

Part No. Description

Am7996 IEEE 802.3/Ethernet/Cheapernet Tap Transceiver

Am79C100 Twisted-Pair Ethernet Transceiver Plus (TPEX+)

TM

TM

(ILACCTM)

)

Am79C900 Integrated Local Area Communications Controller

Am79C940 Media Access Controller for Ethernet (MACE

Am79C960 PCnet-ISA Single-Chip Ethernet Controller (for ISA bus)

Am79C961 PCnet-ISA Single-Chip Ethernet Controller (with Microsoft

Plug n’ Play support)

Am79C965 PCnet-32 Single-Chip 32-Bit Ethernet Controller (for 386DX, 486 and VL buses)

Am79C970 PCnet-PCI Single-Chip Ethernet Controller (for PCI bus)

Am79C974 PCnet-SCSI Combination Ethernet and SCSI Controller for PCI Systems

Am79C98 Twisted-Pair Ethernet Transceiver (TPEX)

TM

Am79C981 Integrated Multiport Repeater Plus

Am79C987 Hardware Implemented Management Information Base

(IMR+TM)

TM

(HIMIBTM)

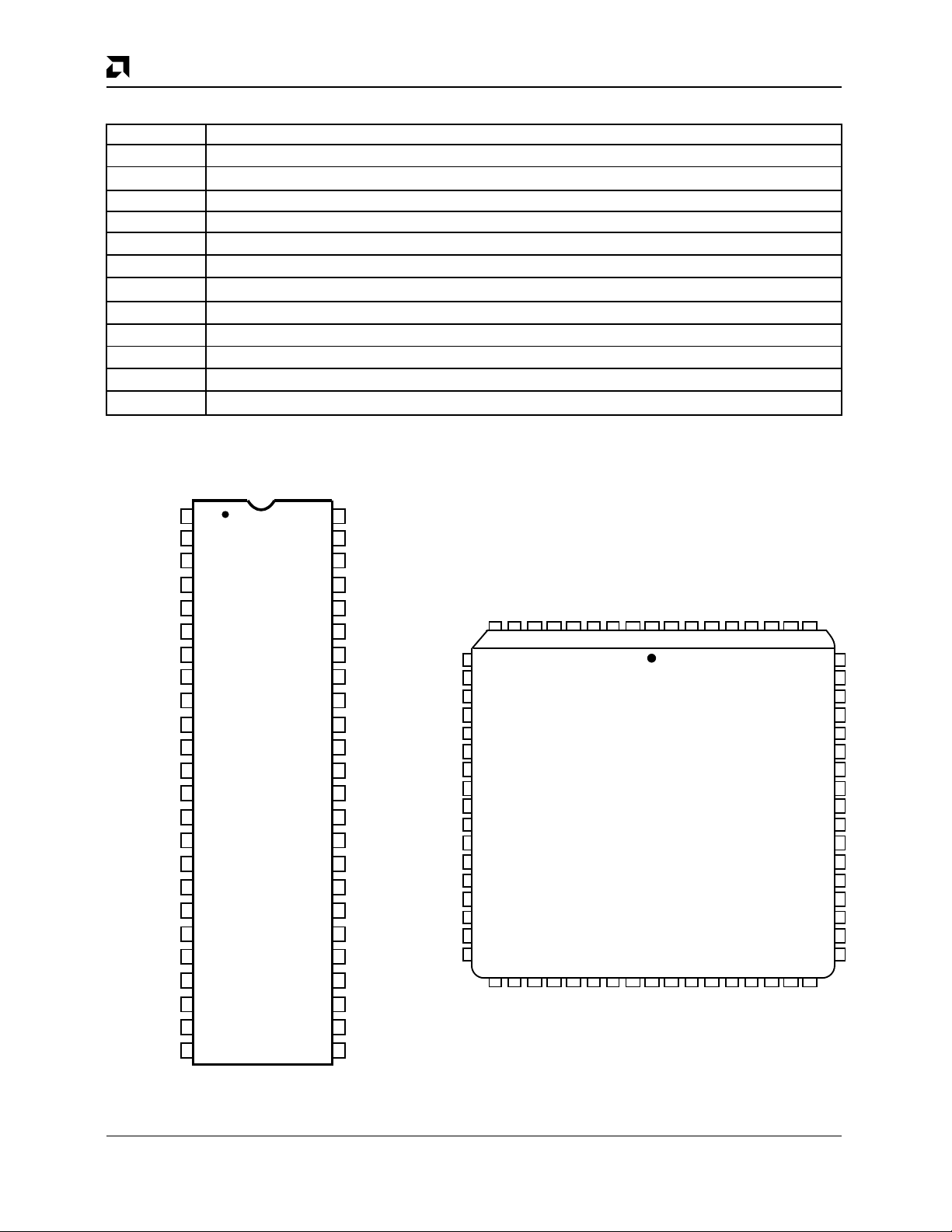

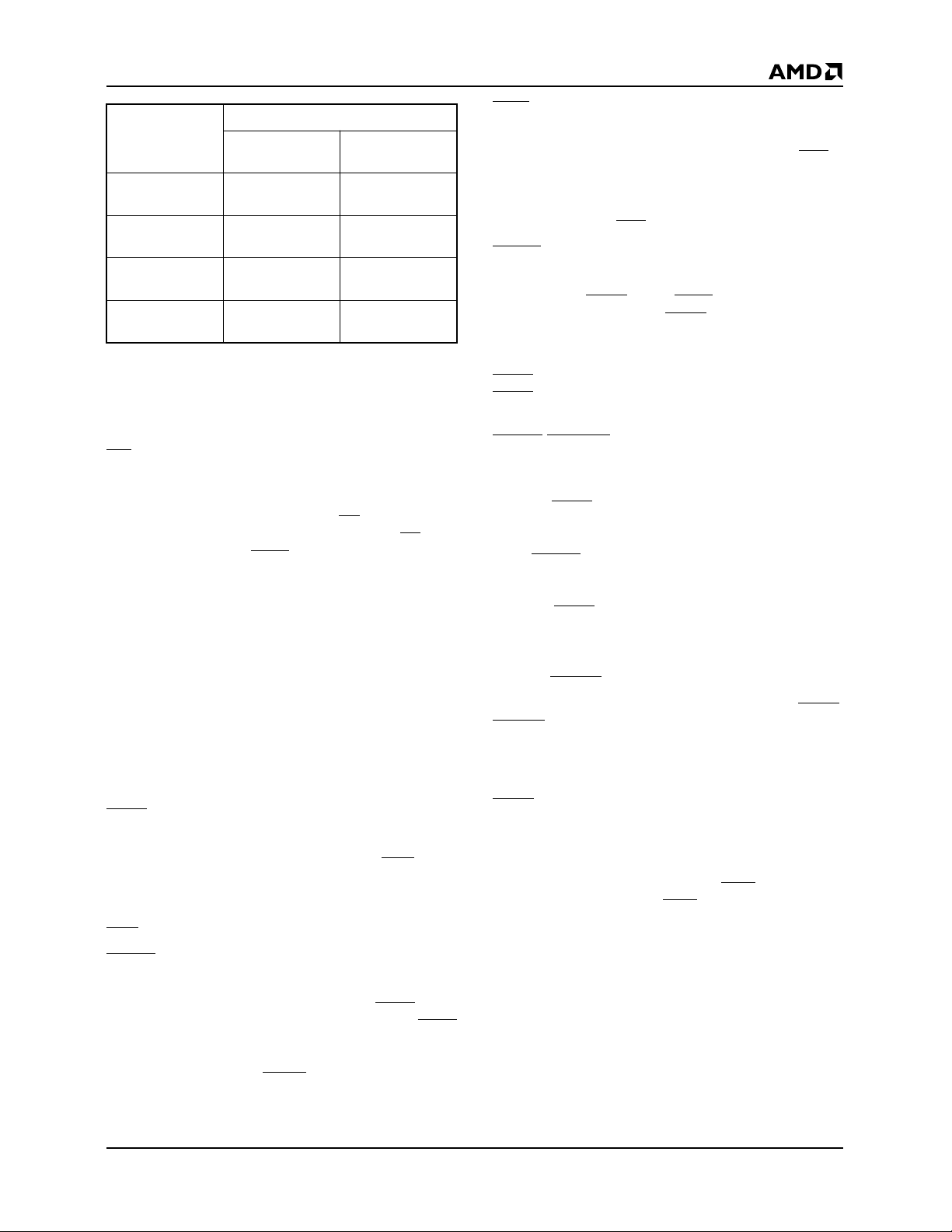

CONNECTION DIAGRAMS

DIP PLCC

1

V

SS

DAL7

DAL6

DAL5

DAL4

DAL3

DAL2

DAL1

DAL0

READ

INTR

DALI

DALO

DAS

BM0/BYTE

BM1/BUSAKO

HOLD/BUSRQ

ALE/AS

HLDA

ADR

READY

RESET

V

CS

SS

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Note:

Pin 1 is marked for orientation.

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

17881B-2

V

DD

DAL8

DAL9

DAL10

DAL11

DAL12

DAL13

DAL14

DAL15

A16

A17

A18

A19

A20

A21

A22

A23

RX

RENA

TX

CLSN

RCLK

TENA

TCLK

NC

NC

DAL2

DAL3

DAL4

DAL5

DAL6

DAL7

VSS

VDD

DAL8

DAL9

DAL10

DAL11

DAL12

NC

NC

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

DAL1

DAL0

NC

NC

READ

7

29

DAL13

INTR

6

30

DAL14

DALI

5

31

DAL15

4

32

DALO

NC

3

33

A16

A17

NC

DAS

NCNCBM1/BUSRQ

BM0/BYTE

1

67

68

36

NC

37

66

38

NC

298

35

342728

A18

A19

65

39

A20

64

40

A21

HOLD/BUSRQ

ALE/AS

63

41

42

A22

A23

HLDA

62

61

43

RX

17881B-3

NC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

RENA

NC

CS

NC

NC

ADR

READY

RESET

NC

NC

VSS

TCLK

TENA

RCLK

CLSN

TX

NC

NC

2

Am79C90

Page 3

PRELIMINARY

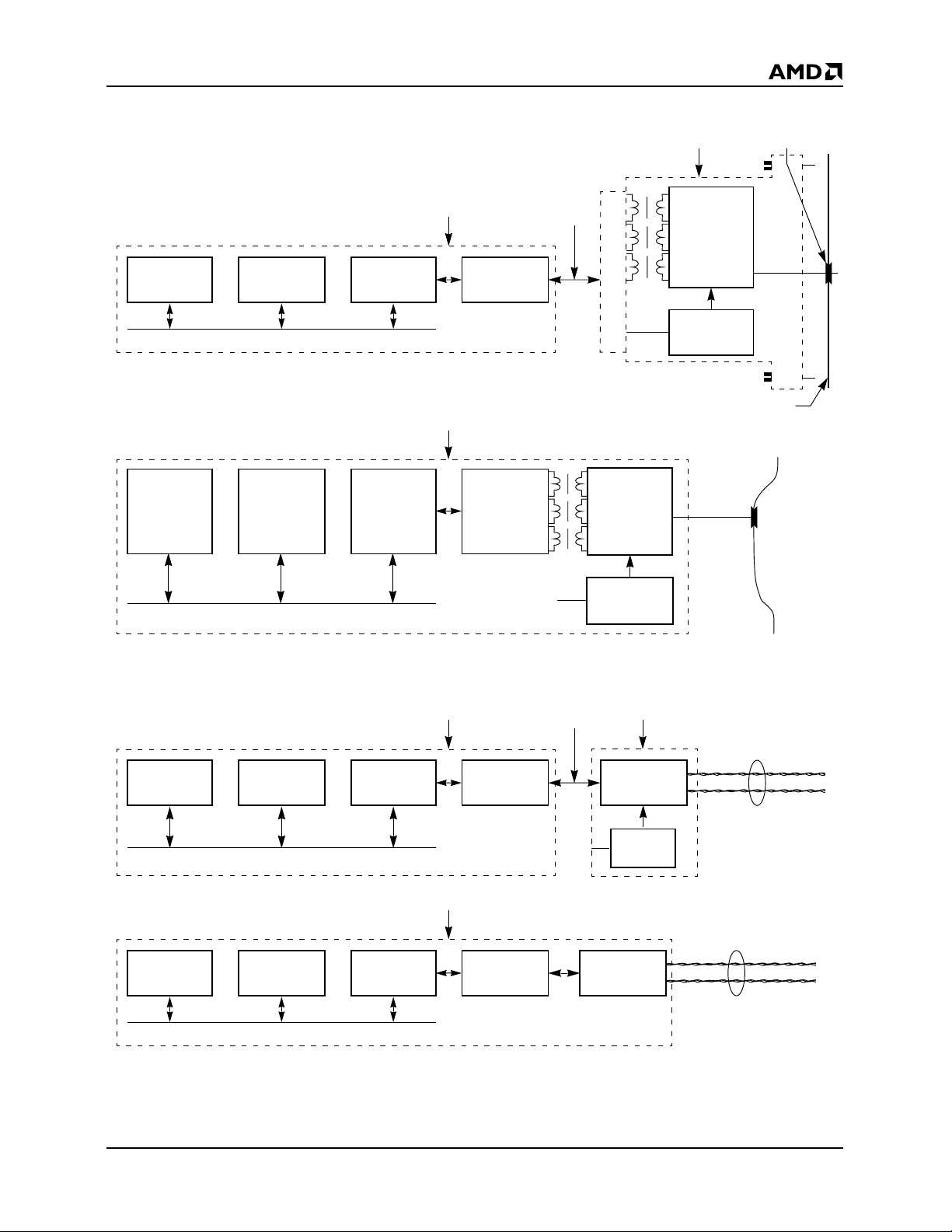

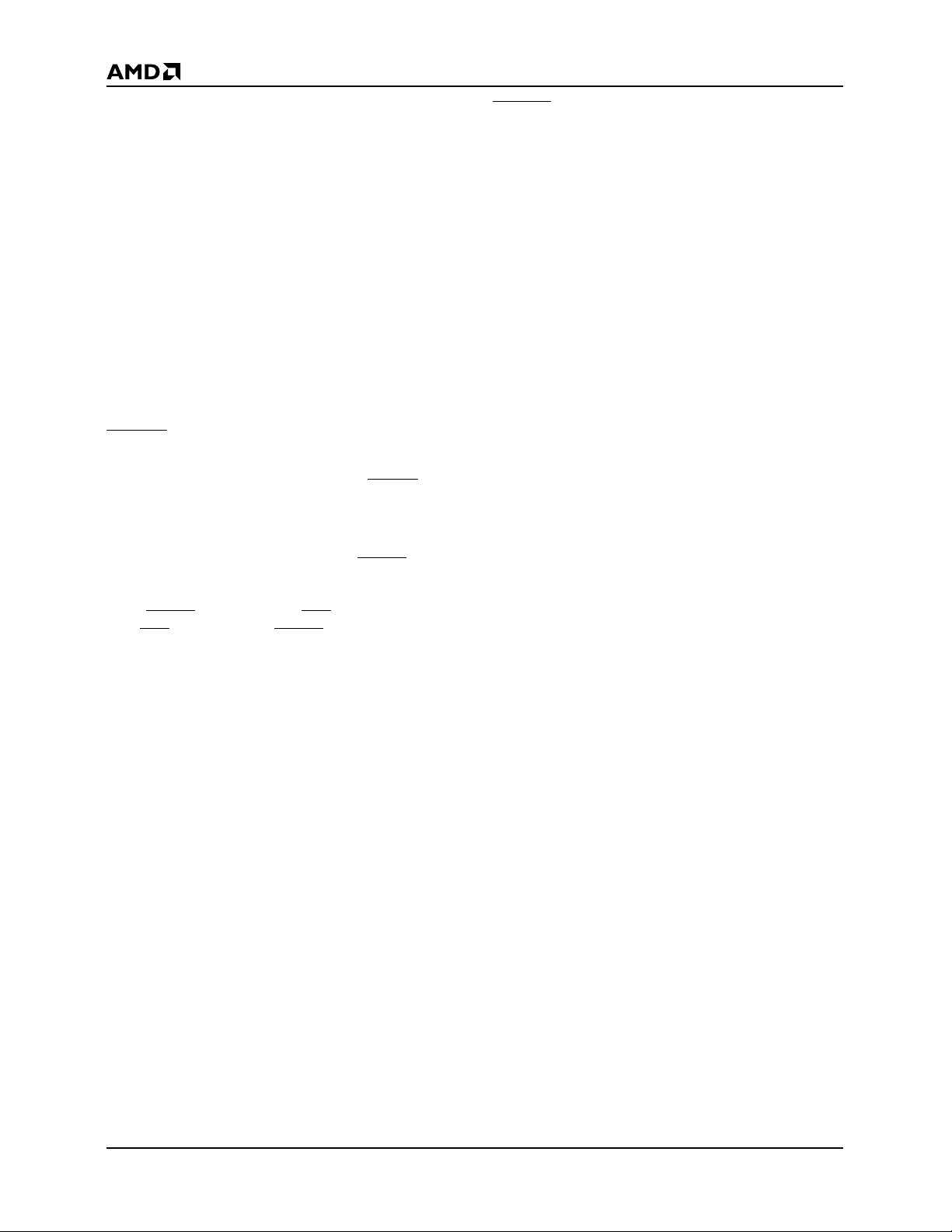

TYPICAL ETHERNET/CHEAPERNET NODE

Ethernet

Local

CPU

Cheapernet

Local

CPU

Local

Memory

Local Bus

Local

Memory

Local Bus

Am79C90

C-LANCE

Am79C90

C-LANCE

DTE

DTE

Am7992B

SIA

Am7992B

SIA

AUI

Cable

Am7996

Transceiver

Power

Supply

MAU

Am7996

Transceiver

Power

Supply

Ethernet Coax

TAP

RG58A/U or

RG58C/U

BNC “T”

Typical Ethernet 10BASE-T Node

Local

CPU

Local

CPU

Local

Memory

Local Bus

Local

Memory

Local Bus

Am79C90

C-LANCE

Am79C90

C-LANCE

DTE

Am7992B

SIA

DTE

Am7992B

SIA

AUI

Cable

MAU

Am79C98

Am79C100

Power

Supply

Am79C98

Am79C100

Twisted-Pair

AUI—Attachment Unit Interface DTE—Data Terminal Equipment MAU—Medium Attachment Unit

Twisted-Pair

17881C-4

Am79C90 3

Page 4

PRELIMINARY

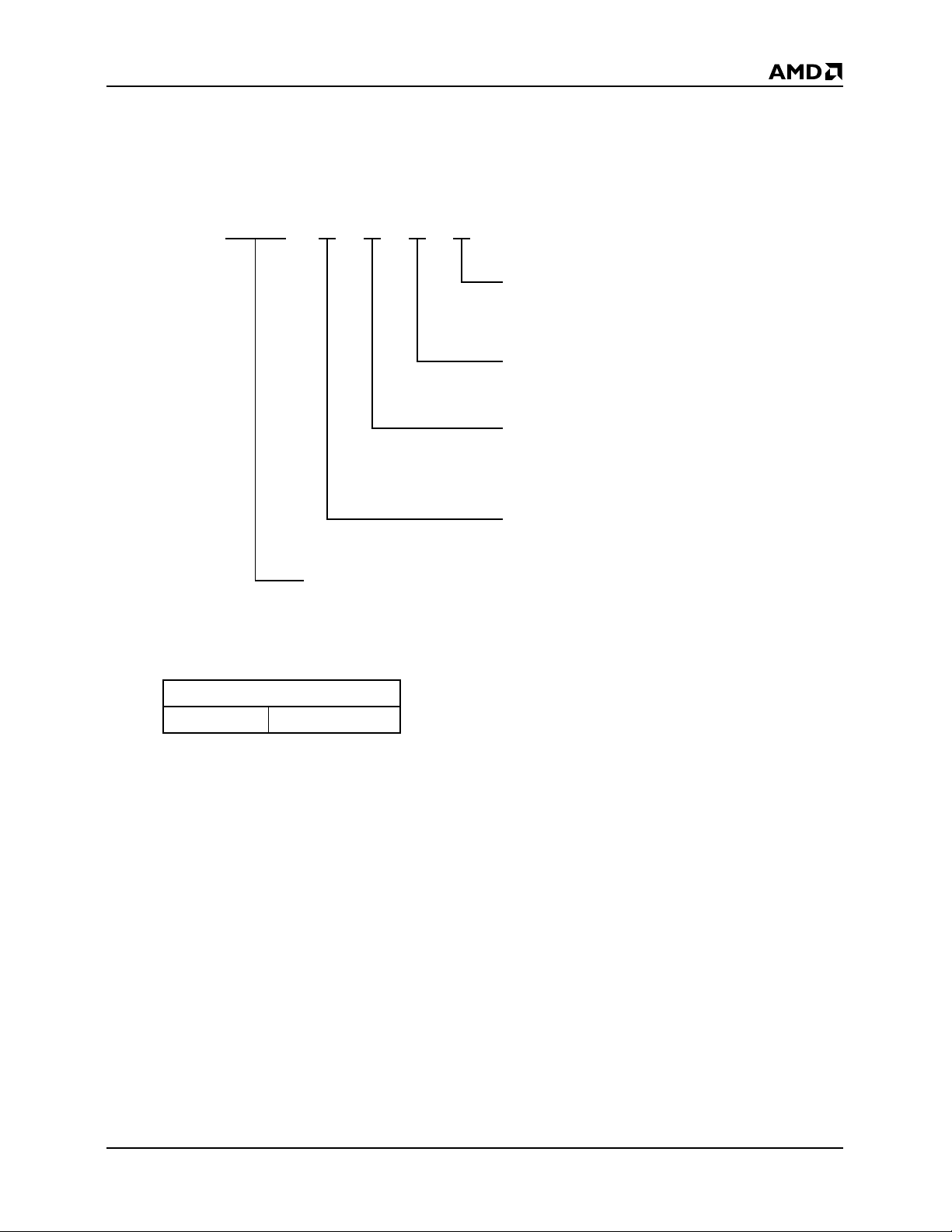

ORDERING INFORMATION

Standard Products

AMD standard products are available in several packages and operating ranges. The order number (valid combination) is formed

by a combination of the elements below.

AM79C90 P C

DEVICE NUMBER/DESCRIPTION

Am79C90

CMOS Local Area Network Controller for Ethernet

B

OPTIONAL PROCESSING

Blank=Standard Processing

TR=Tape and Reel Packaging

OPERATING CONDITIONS

C = Commercial (0°C to +70°C)

PACKAGE TYPE

P=48-Pin Plastic DIP (PD 048)

J=68-Pin Plastic Leaded Chip Carrier (PL 068)

SPEED

Not Applicable

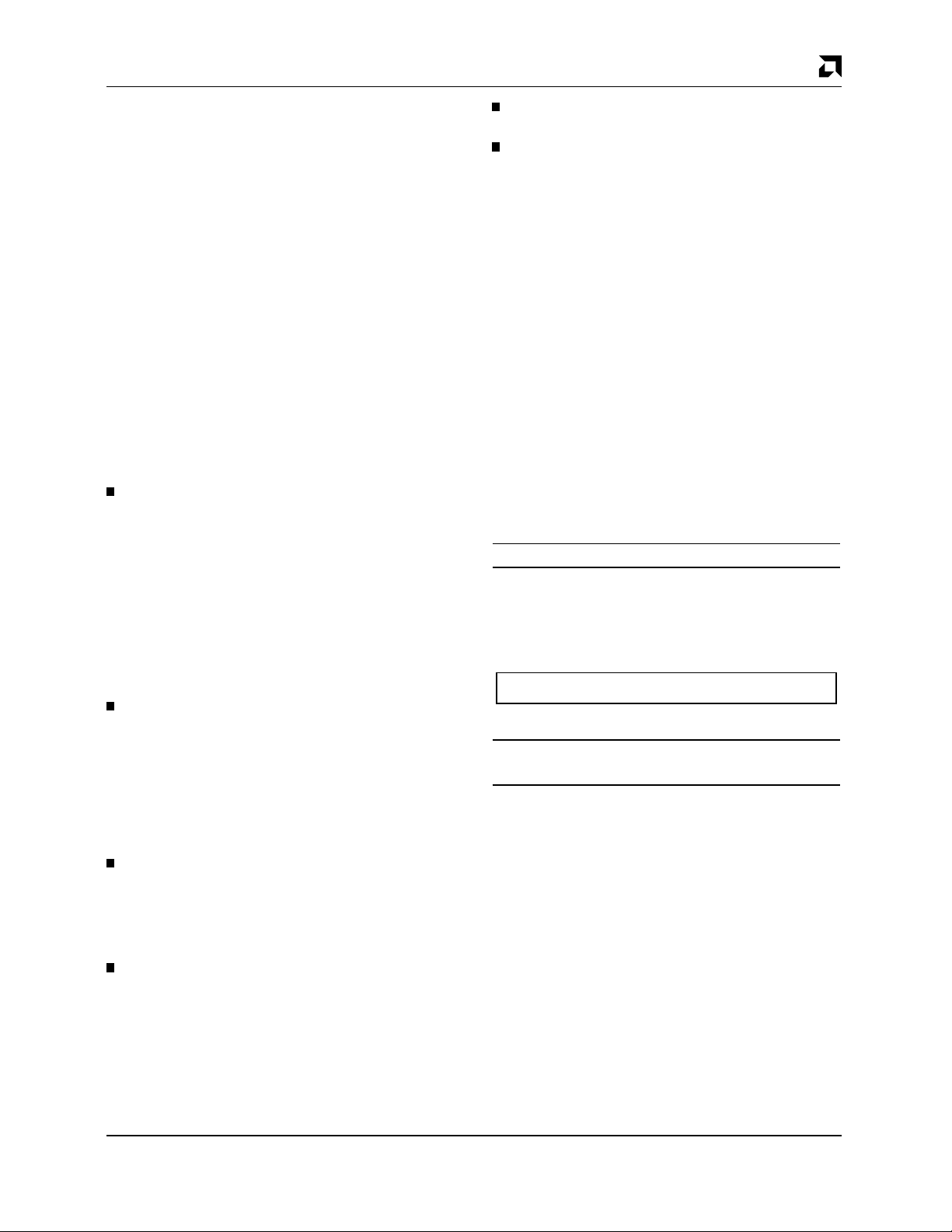

Valid Combinations

AM79C90 PC, JC, JCTR

Valid Combinations

Valid combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales

office to confirm availability of specific valid combinations and

to check on newly released combinations.

4 Am79C90

Page 5

PRELIMINARY

PIN DESCRIPTION

A16–A23

High Order Address Bus (Output, Three-State)

Additional address bits to access a 24-bit address.

These lines are driven as a Bus Master only.

ADR

Register Address Port Select (Input)

When the C-LANCE is a Slave, ADR indicates which of

the two register ports is selected. ADR LOW selects

register data port; ADR HIGH selects register address

port. ADR must be valid throughout the data portion of

the bus cycle and is only used by the C-LANCE when

is LOW.

CS

ALE/AS

Address Latch Enable (Output, Three-State)

Used to demultiplex the DAL lines and define the

address portion of the bus cycle. This l/O pin is programmable through bit (01) of CSR3.

As ALE (CSR3 (01), ACON = 0), the signal transitions

from a HIGH to a LOW during the address portion of

the transfer and remains LOW during the data portion.

ALE can be used by a Slave device to control a latch on

the bus address lines. When ALE is HIGH, the latch is

open, and when ALE goes LOW, the latch is closed.

(CSR3 (01), ACON = 1), the signal pulses LOW

As AS

during the address portion of the bus transaction. The

LOW-to-HlGH transition of AS can be used by a Slave

device to strobe the address into a register.

The C-LANCE drives the ALE/AS line only as a Bus

Master.

BM0/BYTE, BM

(Output, Three-State)

The two pins are programmable through bit (00) of

CSR3.

0, BM1—If CSR3 (00) BCON = 0

BM

PIN 15 = BM0 (Output, Three-State) (48-Pin DlPs)

PIN 16 = BM1 (Output, Three-State) (48-Pin DlPs)

BM0, BM1 (Byte Mask). This indicates that the byte(s)

on the DAL are to be read or written during this bus

transaction. The C-LANCE drives these lines only as a

Bus Master. It ignores the Byte Mask lines when it is a

Bus Slave and assumes word transfers.

1

/BUSAKO

Byte selection using Byte Mask is done as described

by the following table:

BM

1

LOW LOW Whole Word

LOW HIGH Upper Byte

HlGH LOW Lower Byte

HlGH HIGH None

BYTE, B

PIN 15 = BYTE (Output, Three-State) (48-Pin DlPs)

PIN 16 = BUSAKO (Output) (48-Pin DIPs)

Byte selection may also be done using the BYTE line

and DAL00 line, latched during the address portion of

the bus cycle. The C-LANCE drives BYTE only as a

Bus Master and ignores it when a Bus Slave selection

is done (similar to BM0, BM1). Byte selection is done

as outlined in the following table:

B

is not requesting the bus and it receives HLDA,

BUSAKO will be driven LOW. If the C-LANCE is requesting the bus when it receives HLDA, BUSAKO will

remain HIGH.

USAKO—If CSR3 (00) BCON = 1

BYTE DAL

LOW LOW Whole Word

LOW HIGH Illegal Condition

HlGH LOW Lower Byte

HlGH HIGH Upper Byte

USAKO is a bus request daisy chain output. If the chip

BM

0

00

Selection

Selection

Byte Swapping

In order to be compatible with the variety of 16-bit microprocessors available to the designer, the C-LANCE

may be programmed to swap the position of the upperand lower-order bytes on data involved in transfers with

the internal FIFOs.

Byte swapping is done when BSWP = 1. The most

significant byte of the word in this case will appear on

DAL lines 7–0 and the least significant byte on DAL

lines 15–8.

When BYTE = H (indicating a byte transfer) the table indicates on which part of the 16-bit data bus the actual

data will appear.

Whenever byte swap is activated, the only data that is

swapped is data traveling to and from the Transmit/

Receive FIFOs.

Am79C90 5

Page 6

PRELIMINARY

Mode Bits

Signal Line

BYTE = L and

DAL00 = L

BYTE = L and

DAL00 = H

BYTE = H and

DAL00 = H

BYTE = H and

DAL00 = L

BSWP = 0

and BCON = 1

Word Word

Illegal Illegal

Upper Byte Lower Byte

Lower Byte Upper Byte

BSWP = 1

and BCON = 1

CLSN

Collision (Input)

A logical input that indicates that a collision is occurring

on the channel.

CS

Chip Select (Input)

Indicates, when asserted, that the C-LANCE is the

Slave device of the data transfer. CS

throughout the data portion of the bus cycle. CS must

not be asserted when HLDA is LOW.

must be valid

DAL00–DAL15

Data/Address Lines (Input/Output, Three-State)

The time multiplexed Address/Data bus. During the address portion of a memory transfer, DAL00–DAL15

contains the lower 16 bits of the memory address. The

upper 8 bits of address are contained in A16–A23.

During the data portion of a memory transfer, DAL00–

DAL15 contains the read or write data, depending on

the type of transfer.

The C-LANCE drives these lines as a Bus Master and

as a Bus Slave.

D

ALI

Data/Address Line In (Output, Three-State)

An external bus transceiver control line. D

serted when the C-LANCE reads from the DAL lines. It

will be LOW during the data portion of a READ transfer

and remain HIGH for the entire transfer if it is a WRITE.

DALI is driven only when C-LANCE is a Bus Master.

D

ALO

Data/Address Line Out (Output, Three-State)

An external bus transceiver control line. D

serted when the C-LANCE drives the DAL lines. DALO

will be LOW only during the address portion if the transfer is a READ. It will be LOW for the entire transfer if the

transfer is a WRITE. DALO is driven only when

C-LANCE is a Bus Master.

ALI is as-

ALO is as-

DAS

Data Strobe (Input/Output, Three-State)

Defines the data portion of the bus transaction. D

high during the address portion of a bus transaction

and low during the data portion. The LOW-to-HlGH

transition can be used by a Slave device to strobe bus

data into a register. DAS is driven only as a Bus Master.

AS is

HLDA

Bus Hold Acknowledge (Input)

A response to HOLD

to the chip’s assertion of HOLD, the chip is the Bus

Master.

During Bus Master operation, the C-LANCE waits for

A to be deasserted HIGH before reasserting

HLD

HOLD LOW. This insures proper bus handshake under

all situations.

. When HLDA is LOW in response

HOLD/BUSRQ

Bus Hold Request (Output, Open Drain)

Asserted by the C-LANCE when it requires access to

memory. HOLD

transaction. The function of this pin is programmed

through bit (00) of CSR3. Bit (00) of CSR3 is cleared

when RESET is asserted.

When CSR3 (00) BCON = 0

PIN 17 = HOLD

(Output Open Drain and input sense) (48-Pin DIPs)

When CSR3 (00) BCON = 1

PIN 17 = BUSRQ (I/O Sense, Open Drain) (48-Pin DlPs)

If the C-LANCE wants to use the bus, it looks at HOLD/

BUSRQ; if it is HIGH the C-LANCE can pull it LOW and

request the bus. If it is already LOW, the C-LANCE

waits for it to go inactive-HlGH before requesting the

bus.

is held LOW for the entire ensuing bus

INTR

Interrupt (Output, Open Drain)

An attention signal that indicates, when active, that one

or more of the following CSR0 status flags is set: BABL,

MERR, MISS, RINT, TINT or IDON. INTR

bit 06 of CSR0 (INEA = 1). INTR remains asserted until

the source of Interrupt is removed.

is enabled by

RCLK

Receive Clock (Input)

A 10 MHz square wave synchronized to the Receive

data and only active while receiving an Input Bit

Stream.

6 Am79C90

Page 7

PRELIMINARY

READ

(Input/Output, Three-State)

Indicates the type of operation to be performed in the

current bus cycle. This signal is an output when the

C-LANCE is a Bus Master.

High—Data is taken off the DAL lines by the

C-LANCE.

Low—Data is placed on the DAL lines by the

C-LANCE.

The signal is an input when the C-LANCE is a Bus

Slave.

High—Data is placed on the DAL lines by the

C-LANCE.

Low—Data is taken off the DAL lines by the

C-LANCE.

READY

(Input/Output, Open Drain)

When the C-LANCE is a Bus Master, READ

asynchronous acknowledgment from the bus memory

that it will accept data in a WRITE cycle or that it has

put data on the DAL lines in a READ cycle.

As a Bus Slave, the C-LANCE asserts READY when it

has put data on the DAL lines during a READ cycle or

is about to take data off the DAL lines during a write

cycle. READY is a response to DAS and will return High

after DAS has gone High. READY is an input when the

C-LANCE is a Bus Master and an output when the

C-LANCE is a Bus Slave.

Y is an

RENA

Receive Enable (Input)

A logical input that indicates the presence of carrier on

the channel.

RESET

Reset (Input)

Reset causes the C-LANCE to cease operation, clear

its internal logic, force all three-state buffers to the highimpedance state, and enter an idle state with the stop

bit of CSR0 set. It is recommended that a 3.3 k Ω pullup

resistor be connected to this pin.

RX

Receive (Input)

Receive Input Bit Stream.

TCLK

Transmit Clock (Input)

10 MHz clock.

TENA

Transmit Enable (Output)

Transmit Output Bit Stream enable. When asserted, it

enables valid transmit output (TX).

TX

Transmit (Output)

Transmit Output Bit Stream.

V

DD

Power Supply Pin +5 V ± 5%

It is recommended that 0.1 µ F and 10 µ F decoupling

capacitors be used between V

V

SS

Ground

Pin 1 and 24 (48-Pin DlPs) should be connected

together externally, as close to the chip as possible.

DD

and V

SS

.

Am79C90 7

Page 8

AMD

P R E L I M I N A R Y

FUNCTIONAL DESCRIPTION

The parallel interface of the CMOS Local Area Network

Controller for Ethernet (C-LANCE) has been designed

to be “friendly” or easy to interface to a variety of popular

microprocessors. These microprocessors include the

Am29000, 80x86, 680x0, Z8000 and LSI-11. The

C-LANCE has a 24-bit wide linear address space when

it is in the Bus Master Mode. A programmable mode of

operation allows byte addressing in one of two ways:

aByte/Word control signal compatible with the 80x86

and Z8000 or an Upper Data Strobe and Lower Data

Address

Bits

16–23

A16–A23

CPU

DAL0–DAL15

ALE

Data and

Address

Bits 0–15

Buffer

Buffer

Strobe signal compatible with microprocessors such as

the 68000. A programmable polarity on the Address

Strobe signal eliminates the need for external logic. The

C-LANCE interfaces with both multiplexed and demultiplexed data busses and features control signals for

address/data bus transceivers. The C-LANCE is pin-forpin compatible with AMD’s LANCE device (Am7990).

Please refer to Appendix B for a complete comparison

between the C-LANCE and LANCE devices.

Control

A16–A23

DAL0 – DAL15

Buffer

ALE

A16–A23

DAL0–DAL15A16–A23Control

Figure 1. C-LANCE/CPU Interfacing Multiplexed Bus

Latch

Decoder

C-LANCE

ALE

ADR

CS

17881B-5

8

Am79C90

Page 9

Data Bus

P R E L I M I N A R Y

Address

Bus

Data/Address

Bits 0-15

A0–A15

Latch

A16–A23

Buffer

A0–A23

Decode

ALE

Address

Bits 16-23

C-LANCE

CS

Figure 2. C-LANCE/CPU Interfacing Demultiplexed Bus

AMD

17881B-6

During initialization, the CPU loads the starting address

of the initialization block into two internal control registers. The C-LANCE has four internal control and status

registers (CSR0, 1, 2, 3) which are used for various

functions, such as the loading of the initialization block

address, and programming different modes and status

conditions. The host processor communicates with the

C-LANCE during the initialization phase, for demand

transmission, and periodically to read the status bits following interrupts. All other transfers to and from the

memory are automatically handled as DMA.

Interrupts to the microprocessor are generated by the

C-LANCE upon:

completion of its initialization routine

the reception of a packet

the transmission of a packet

transmitter timeout error

a missed packet

memory error

The cause of the interrupt is ascertained by reading

CSR0. Bit (06) of CSR0, (INEA), enables or disables

interrupts to the microprocessor. In systems where polling is used in place of interrupts, bit (07) of CSR0,

(INTR), indicates an interrupt condition.

The basic operation of the C-LANCE consists of two distinct modes: transmit and receive. In the transmit mode,

the C-LANCE chip directly accesses data (in a transmit

buffer) in memory. It prefaces the data with a preamble,

start frame delimiter (SFD), and calculates and appends

a 32-bit CRC. On transmission, the first byte of data

loads into the 48-byte Transmit FIFO; the C-LANCE

then begins to transmit preamble while simultaneously

loading the rest of the packet into Transmit FIFO for

transmission.

In the receive mode, packets are sent via the Am7992B

SlA to the C-LANCE. The packets are loaded into the

64-byte Receive FIFO for preparation of automatic

downloading into buffer memory. A CRC is calculated

and compared with the CRC appended to the data packet. If the calculated CRC does not agree with the packet

CRC, an error bit is set.

Addressing

Packets can be received using three different destination addressing schemes: physical, logical and

promiscuous.

The first type is a full comparison of the 48-bit destination address in the packet with the node address that

was programmed into the C-LANCE during an initialization cycle. There are two types of logical addresses.

One is group type mask where the 48-bit address in the

packet is put through a hash filter to map the 48-bit

physical addresses into 1 of 64 logical groups. If any of

these 64 groups have been preselected as the logical

address, then the 48-bit address is stored in main memory. At this time, a look up is performed by the host computer comparing the 48-bit incoming address with the

pre-stored 48-bit logical address. This mode can be

useful if sending packets to all of a particular type of device simultaneously (i.e., send a packet to all file servers

or all printer servers). Additional details on logical addressing can be found in the INITIALIZATION section

9Am79C90

Page 10

AMD

P R E L I M I N A R Y

under “Logical Address Filter.” The second logical address is a broadcast address where all nodes on the network receive the packet. The last receive mode of

operation is referred to as “promiscuous mode” in which

a node will accept all packets on the medium regardless

of their destination address.

Collision Detection and Implementation

The Ethernet and IEEE 802.3 CSMA/CD network access algorithms are implemented completely within the

C-LANCE. In addition to listening for a clear medium before transmitting, Ethernet handles collisions in a predetermined way. Should two transmitters attempt to seize

the medium at the same time, they will collide and the

data on the medium will be garbled. The transmitting

nodes listen while they transmit, detect the collision,

then continue to transmit for a predetermined length of

time to “jam” the network and ensure that all nodes have

recognized the collision. The transmitting nodes then

delay a random amount of time according to the Ethernet “truncated binary backoff” algorithm in order that the

colliding nodes do not try to repeatedly access the network at the same time. The C-LANCE also offers a selectable Modified Backoff Algorithm for better

performance on busy networks. Up to 16 attempts to access the network are made by the C-LANCE before reporting an error due to excessive collisions.

Error Reporting and Diagnostics

Extensive error reporting is provided by the C-LANCE.

Error conditions reported relate either to the network as

a whole or to individual data packets. Network-related

errors are recorded as flags in the CSRs and are examined by the CPU following interrupt. Packet-related errors are written into descriptor entries corresponding to

the packet.

System errors include:

Babbling Transmitter

—Transmitter attempting to transmit more than

1518 bytes, excluding preamble and start frame

delimiter

Collision

—Collision detection circuitry nonfunctional

Missed Packet

—Insufficient buffer space

Memory timeout

—Memory response failure

Packet-related errors:

CRC

—Invalid data

Framing

—Packet did not end on a byte boundary

Overflow/Underflow

—Indicates abnormal latency in servicing a DMA

request

Buffer

—Insufficient buffer space available

The C-LANCE performs several diagnostic routines

which enhance the reliability and integrity of the system.

These include a CRC check and two loop back modes

(internal/external). Errors may be introduced into the

system to check error detection logic. A Time Domain

Reflectometer is incorporated into the C-LANCE to aid

system designers in locating faults in the Ethernet physical medium. Shorts and opens manifest themselves in

reflections which are sensed by the TDR.

10

Am79C90

Page 11

P R E L I M I N A R Y

Transmit Descriptor for 1st Data Buffer

Transmit Descriptor for 2nd Data Buffer

Transmit Descriptor for 3rd Data Buffer

Transmit Descriptor for Nth Data Buffer

Receive Descriptor for 1st Data Buffer

Receive Descriptor for 2nd Data Buffer

Receive Descriptor for 3rd Data Buffer

Receive Descriptor for Nth Data Buffer

AMD

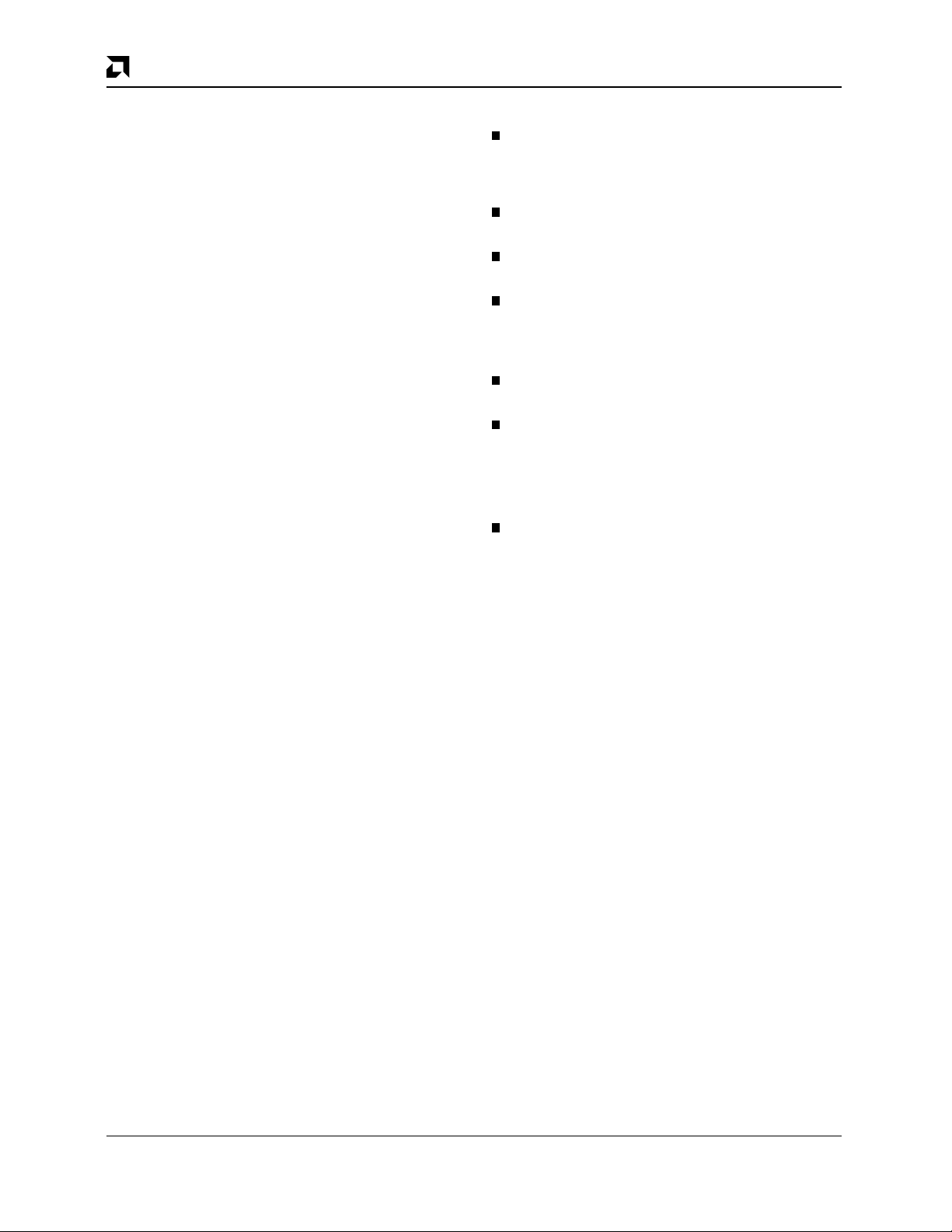

Initialization

Block

Transmit

Descriptor

Ring

(4 words

per entry)

Receive

Descriptor

Ring

(4 words

per entry)

Transmit Data Buffer #1

Transmit Data Buffer #2

Transmit Data Buffer #3

Transmit Data Buffer #N

Receive Data Buffer #1

Receive Data Buffer #2

Receive Data Buffer #3

Receive Data Buffer #N

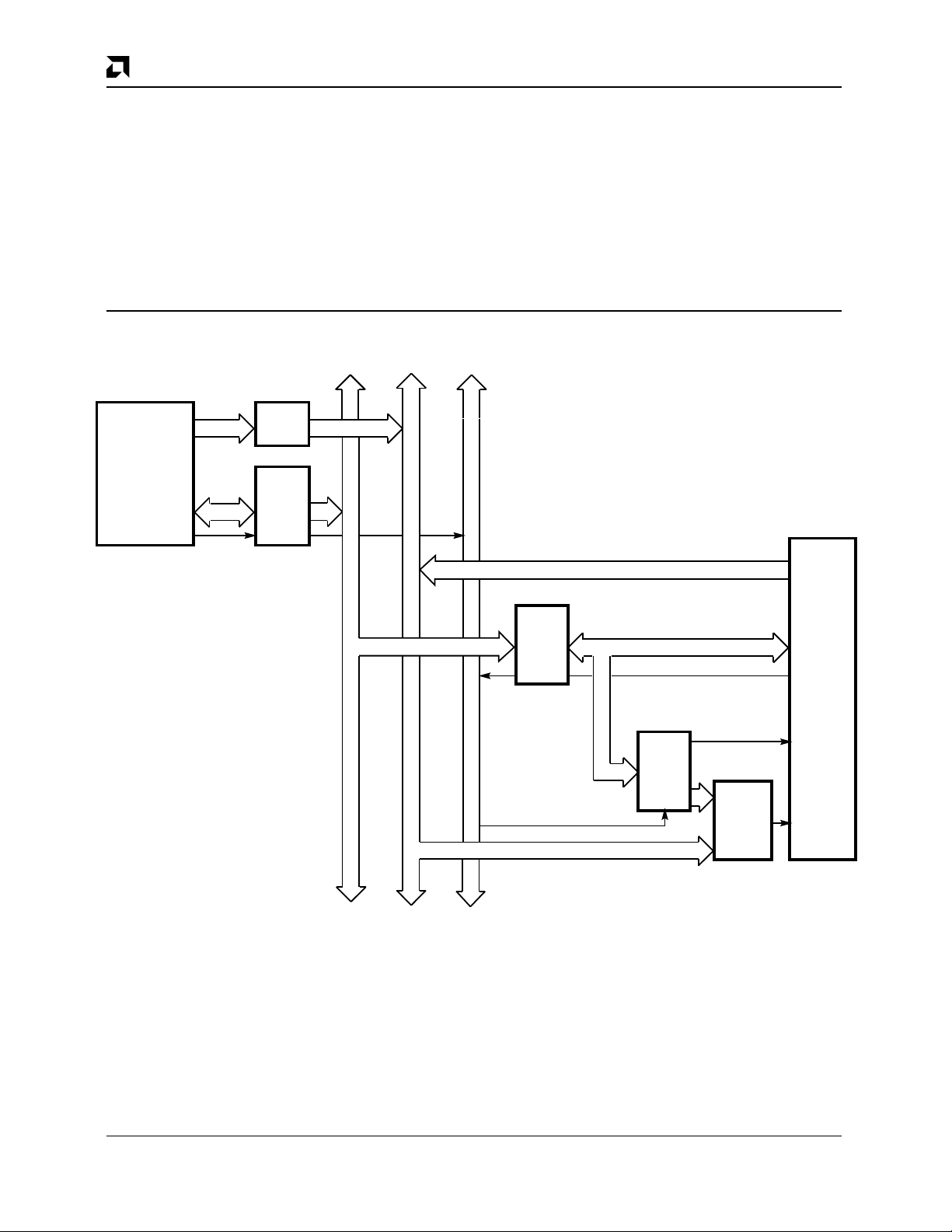

Figure 2-1. C-LANCE/Processor Memory Interface

Transmit

Data

Buffers

Receive

Data

Buffers

17881B-7

11Am79C90

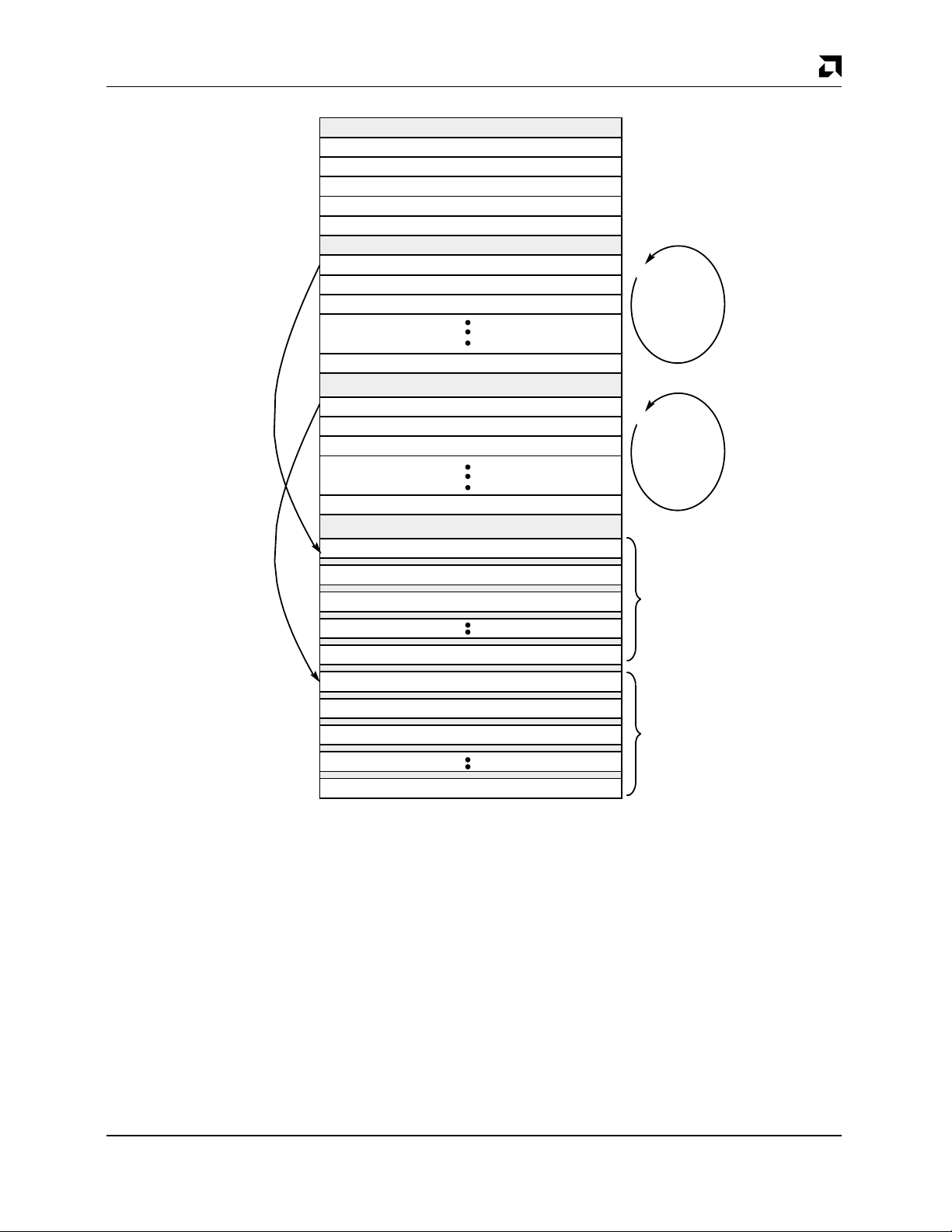

Page 12

AMD

C-LANCE CSR Registers

Pointer to Initialization Block

Initialization

Block

Mode of Operation

Physical Address

Logical Address Filter

Pointer to Receive Ring

Number of Receive Entries (N)

Pointer to Transmit Ring

Number of Transmit Entries (M)

P R E L I M I N A R Y

Receive Descriptor Ring

Address of Receive Buffer 1

Buffer 1 Status

Buffer 1 Byte Count

Buffer 1 Message Count

Transmit Descriptor Ring

Address of Transmit Buffer 1

Buffer 1 Status

Buffer 1 Byte Count

Buffer 1 Error Status

Receive Buffer

Data

Packet

1

Data

2

2

2

2

N

N

N

N

2

2

2

2

Packet

2

Data

Packet

N

Transmit Buffer

Data

Packet

1

Data

Packet

2

Figure 2-2. C-LANCE Memory Management

Buffer Management

A key feature of the C-LANCE and its on-board DMA

channel is the flexibility and speed of communication

between the C-LANCE and the host microprocessor

through common memory locations. The basic organization of the buffer management is a circular queue of

tasks in memory called descriptor rings as shown in

Figures 2-1 and 2-2. There are separate descriptor rings

to describe transmit and receive operations. Up to 128

tasks may be queued up on a descriptor ring awaiting

execution by the C-LANCE. Each entry in a descriptor

ring holds a pointer to a data memory buffer and an entry

for the length of the data buffer. Data buffers can be

chained or cascaded to handle a long packet in multiple

data buffer areas. The C-LANCE searches the descriptor rings in a “lookahead” manner to determine the next

empty buffer in order to chain buffers together or to handle back-to-back packets. As each buffer is filled,

M

M

M

M

Data

Packet

M

17881B-8

the“own” bit is reset, allowing the host processor to

process the data in the buffer.

C-LANCE Interface

CSR bits such as ACON, BCON and BSWP are used for

programming the pin functions used for different interfacing schemes. For example, ACON is used to program the polarity of the Address Strobe signal

(ALE/AS).

BCON is used for programming the pins, for handling

either the BYTE/WORD method for addressing word organized, byte addressable memories where the BYTE

signal is decoded along with the least significant address bit to determine upper or lower byte, or an explicit

scheme in which two signals labeled as BYTE MASK

(BM0 and BM1) indicate which byte is addressed. When

12

Am79C90

Page 13

P R E L I M I N A R Y

the BYTE scheme is chosen, the BM1 pin can be used

for performing the function BUSAKO.

BCON is also used to program pins for different DMA

modes. In a daisy chain DMA scheme, 3 signals are

used (BUSRQ, HLDA, BUSAKO). In systems using a

DMA controller for arbitration, only HOLD and HLDA are

used.

C-LANCE in Bus Slave Mode

The C-LANCE enters the Bus Slave Mode whenever CS

becomes active. This mode must be entered whenever

writing or reading the four status control registers

(CSR0, CSR1, CSR2, and CSR3) and the Register Address Pointer (RAP). RAP and CSR0 may be read or

written to at anytime, but the C-LANCE must be stopped

(by setting the stop bit in CSR0) for CSR1, CSR2, and

CSR3 access.

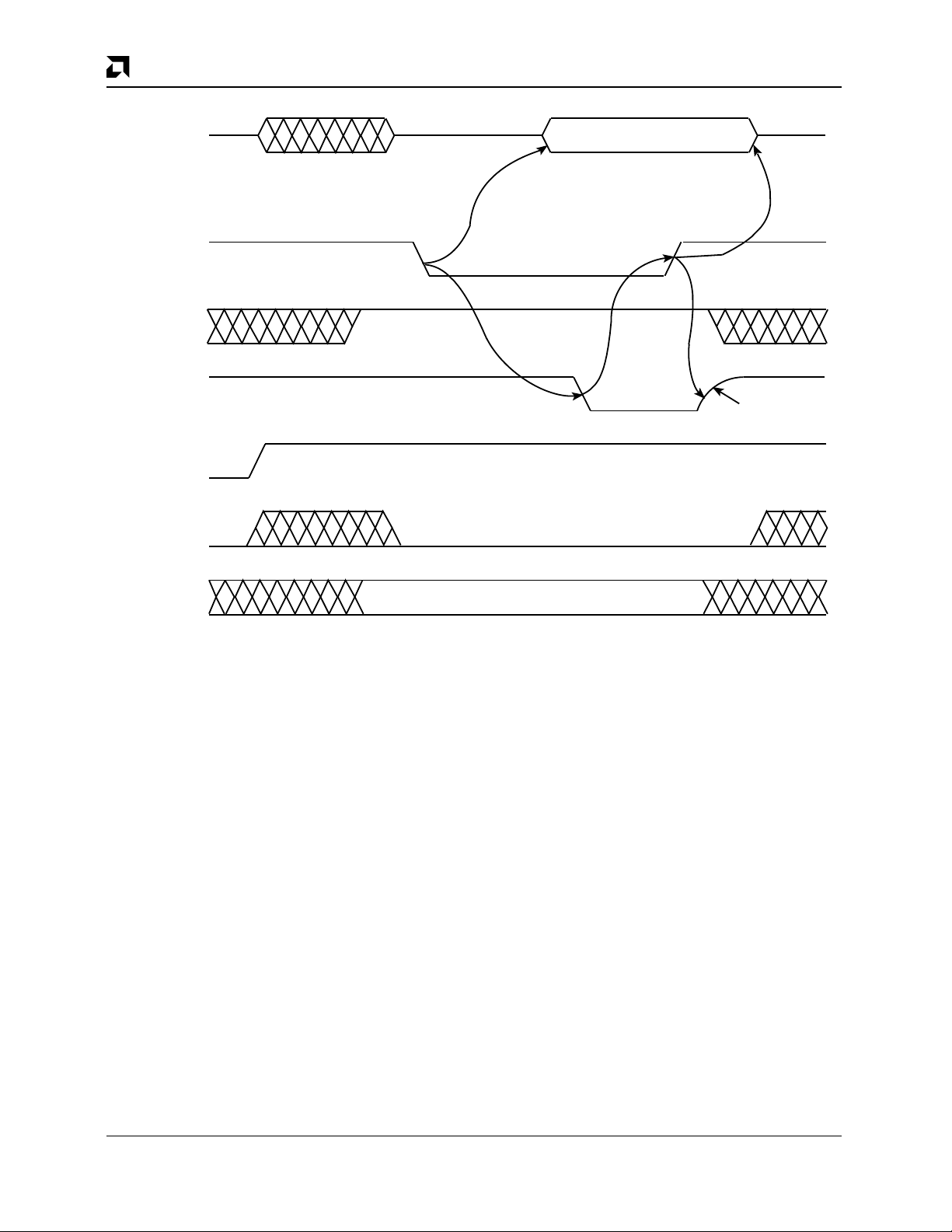

Read Sequence (Slave Mode)

At the beginning of a read cycle, CS, READ, and DAS

are asserted. ADR must be valid at this time. (If ADR is a

“1,” the contents of RAP are placed on the DAL lines.

Otherwise the contents of the CSR register addressed

by RAP are placed on the DAL lines.) After the data on

the DAL lines become valid, the C-LANCE asserts

READY, CS, READ, DAS, and ADR must remain stable

throughout the cycle. Refer to Figure 3.

AMD

Write Sequence (Slave Mode)

This cycle is similar to the read cycle, except that during

this cycle, READ is not asserted (READ is LOW). The

DAL buffers are tristated which configures these lines as

inputs. The assertion of READY by C-LANCE indicates

to the memory device that the data on the DAL lines

have been stored by C-LANCE in its appropriate CSR

register. CS, READ, DAS, ADR and DAL 15:00 must remain stable throughout the write cycle. Refer to

Figure4.

Note: Setting the STOP bit in the C-LANCE will generate a C-LANCE reset, which will cause all bus control

output signals (including

READY

) to float. To guarantee

slave write timing when the STOP bit is being set in

CSR0, the C-LANCE will latch the STOP bit and will wait

for the slave cycle to complete before resetting itself and

floating the output signals.

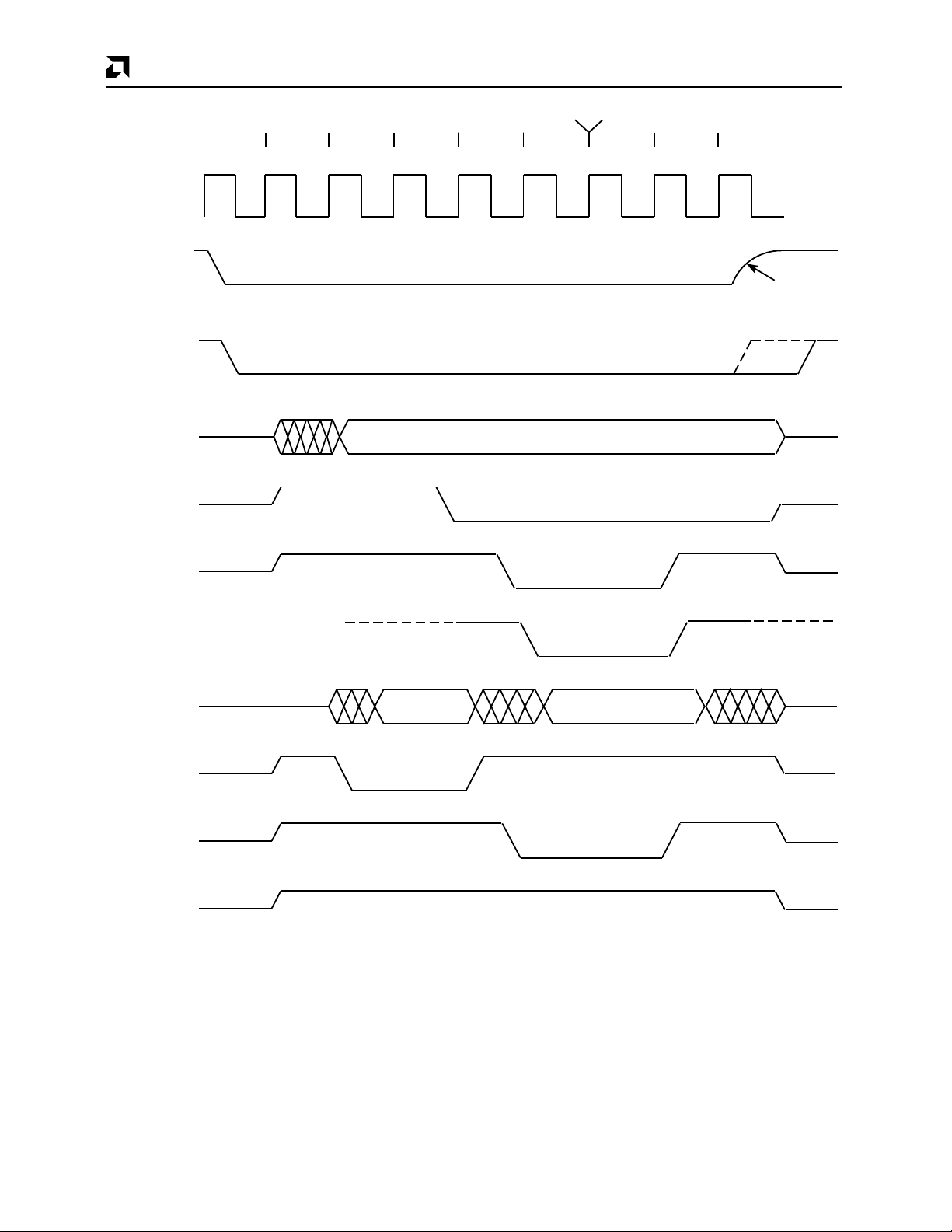

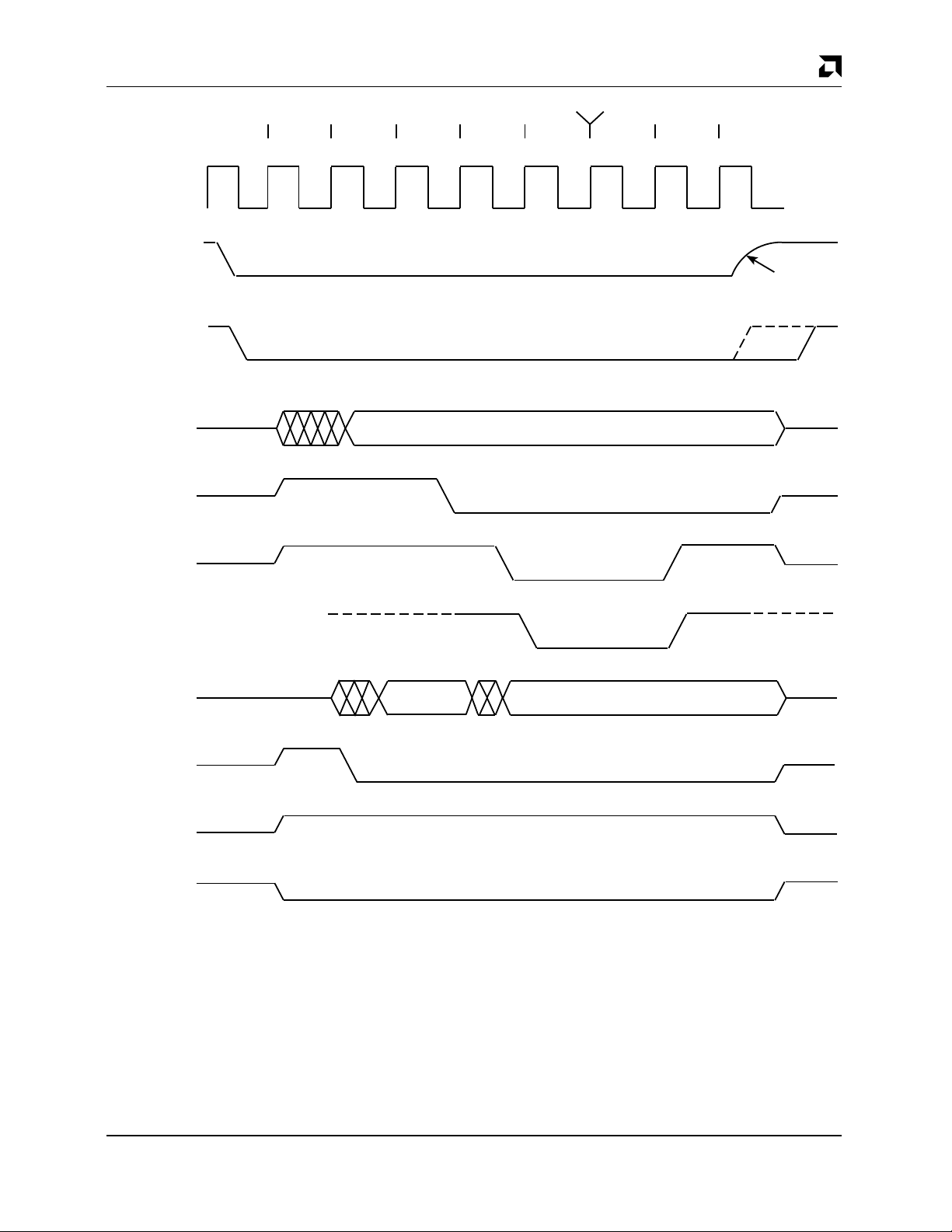

C-LANCE in Bus Master Mode

All data transfers from the C-LANCE in the bus Master

mode are timed by ALE, DAS, and READY. The automatic adjustment of the C-LANCE cycle by the READY

signal allows synchronization with variable cycle time

memory due either to memory refresh or to dual port access. Transfers are a minimum of 600 ns in length except for the first transfer of a bus mastership period in

which the minimum is 700 ns. Transfers can be increased in 100ns increments.

13Am79C90

Page 14

AMD

DAL0–DAL15

DAS

READ

READY

(Output from

C-LANCE)

HOLD

P R E L I M I N A R Y

Read Data

See

Note 1

O.D.

CS

ADR

Note:

1. There are two types of delays which depend on which internal register is accessed.

Type 1 refers to access of CSR0, CSR3 and RAP.

Type 2 refers to access of CSR1 and CSR2 which are longer than Type 1 delay.

Figure 3. Bus Slave Read Timing

17881B-9

14

Am79C90

Page 15

DAL0–DAL15

DAS

READ

READY

(Output from

C-LANCE)

HOLD

CS

P R E L I M I N A R Y

AMD

Write Data

O.D.

ADR

Figure 4. Bus Slave Write Timing

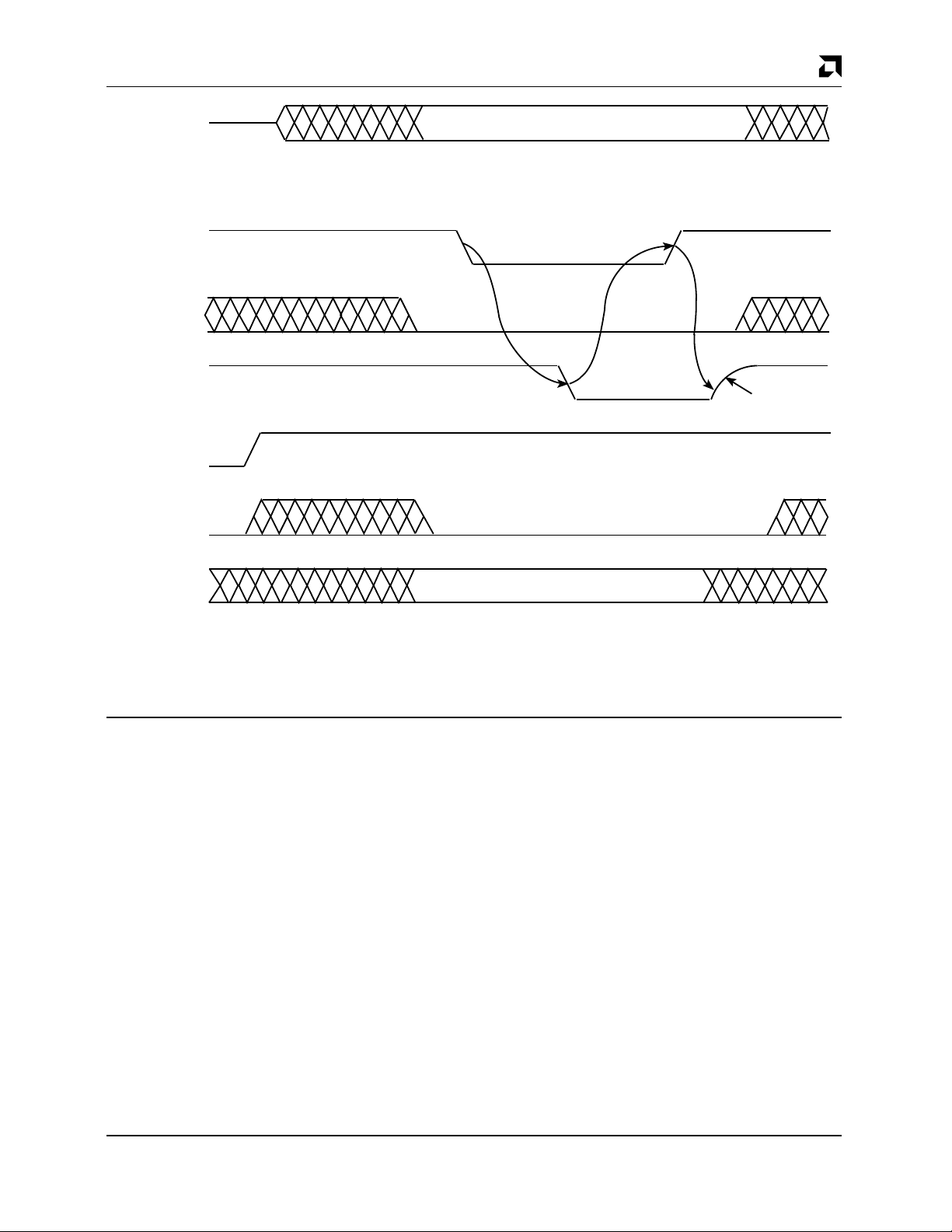

Read Sequence (Master Mode)

A read cycle is begun by placing a valid address on

DAL00 – DAL15 and A16 – A23. The BYTE MASK signals are asserted to indicate a word, upper byte or lower

byte memory reference. READ indicates the type of cycle. ALE or AS is pulsed, and the trailing edge of either

can be used to latch addresses. DAL00 – DAL15 go into

a 3-state mode, and DAS falls LOW to signal the beginning of the memory access. The memory responds by

placing READY LOW to indicate that the DAL lines have

valid data. The C-LANCE then latches memory data on

the rising edge of DAS, which in turn ends the memory

cycle and READY returns HIGH. Refer to Figure 5-1.

17881B-10

The bus transceiver controls, DALI and DALO, are used

to control the bus transceivers. DALI directs data toward

the C-LANCE, and DALO directs data or addresses

away from the C-LANCE. During a read cycle, DALO

goes inactive before DALI becomes active to avoid

“spiking” of the bus transceivers.

Write Sequence (Master Mode)

The write cycle is similar to the read cycle except that the

DAL00 – DAL15 lines change from containing addresses to data after either ALE or AS goes inactive.

After data is valid on the bus, DAS goes active. Data to

memory is held valid after DAS goes inactive. Refer to

Figure 5-2.

15Am79C90

Page 16

AMD

TCLK

HOLD

HLDA

A16–A23

BM0, BM1

ALE

P R E L I M I N A R Y

T

WAIT

T0

0

T1 T2 T3 T4 T5 T6

100 200 300 400 500

Address, BM0, BM1

600

700

O.D.

DAS

READY

DAL0–DAL15

(Read)

DALO

(Read)

DALI

(Read)

READ

(Read)

Address

Data In

Figure 5-1. Bus Master Read Timing (Single DMA Cycle)

17881B-11

16

Am79C90

Page 17

TCLK

HOLD

HLDA

A16–A23

BM0, BM1

ALE

P R E L I M I N A R Y

T

WAIT

T0

0 100 200 300 400 500 600

T1 T2 T3 T4 T5 T6

Address, BM0, BM1

AMD

700

O.D.

DAS

READY

DAL0–DAL15

(Write)

DALO

(Write)

DALI

(Write)

READ

(Write)

Address

Data Out

Figure 5-2. Bus Master Write Timing (Single DMA Cycle)

17881B-12

17Am79C90

Page 18

AMD

P R E L I M I N A R Y

Differences Between Ethernet Versions 1

and 2

a.Version 2 specifies that the collision detect of the

transceiver must be activated during the interpacket gap time.

b.Version 2 specifies some network management

functions, such as reporting the occurrence of collisions, retries and deferrals.

c.Version 2 specifies that when transmission is ter-

minated, the differential transmit lines are driven to

0 volt differentially (half step).

Differences Between IEEE 802.3 and

Ethernet

a.IEEE 802.3 specifies a 2-byte length field rather

than a type field. The length field (802.3) describes

the actual amount of data in the frame.

b.IEEE 802.3 allows the use of a PAD field in the

data section of a frame, while Ethernet specifies

the minimum packet size at 64 bytes. The use of a

PAD allows the user to send and receive packets

which have less than 46 bytes of data.

A list of significant differences between Ethernet and

IEEE 802.3 at the physical layer include the following:

IEEE 802.3 Ethernet

End of Transmission Half Step Full Step (Rev 1)

State or

Half Step (Rev 2)

Common Mode Voltage ±5.5 V 0 – +5 V

Common Mode CurrentLess than 1 mA 1.6 mA ±40%

Receive±, Collision±

Input Threshold ±160 mV ±175 mV

Fault Protection 16 V 0 V

18

Am79C90

Page 19

P R E L I M I N A R Y

PROGRAMMING

This section defines the Control and Status Registers

and the memory data structures required to program the

Am79C90 (C-LANCE).

Programming the Am79C90 (C-LANCE)

The Am79C90 (C-LANCE) is designed to operate in an

environment that includes close coupling with local

memory and microprocessor (HOST). The Am79C90

C-LANCE is programmed by a combination of registers

and data structures resident within the C-LANCE and

memory registers. There are four Control and Status

Registers (CSRs) within the C-LANCE which are programmed by the HOST device. Once enabled, the

C-LANCE has the ability to access memory locations to

acquire additional operating parameters.

The Am79C90 has the ability to do independent buffer

management as well as transfer data packets to and

from the Ethernet. There are three memory structures

accessed by the Chip:

Initialization Block—12 words in contiguous memory starting on a word boundary. It also contains

the operating parameters necessary for device operation. The initialization block is comprised of:

—Mode of Operation

—Physical Address

—Logical Address Mask

—Location to Receive and Transmit Descriptor

Rings

—Number of Entries in Receive and Transmit

Descriptor Rings

Receive and Transmit Descriptor Rings—Two ring

structures, one for incoming and outgoing packets.

Each entry in the rings is 4 words long and each

entry must start on a quadword boundary. The Descriptor Rings are comprised of:

—The address of a data buffer

—The length of that data buffer

—Status information associated with the buffer

Data Buffers—Contiguous portions of memory

reserved for packet buffering. Data buffers may

begin on arbitrary byte boundaries.

In general, the programming sequence of the C-LANCE

may be summarized as:

Program the C-LANCE’s CSRs by a host device to

locate an initialization block in memory. The byte

control, byte address, and address latch enable

modes are also defined here.

AMD

The C-LANCE loads itself with the information contained within the initialization block.

The C-LANCE accesses the descriptor rings for

packet handling.

CONTROL AND STATUS REGISTERS

There are four Control and Status Registers (CSRs) on

the chip. The CSRs are accessed through two bus addressable ports, an address port (RAP) and a data port

(RDP).

Accessing the Control and Status

Registers

The CSRs are read (or written) in a two step operation.

The address of the CSR to be accessed is written into

the RAP during a bus slave transaction. During a subsequent bus slave transaction, the data being read from

(or written into) the RDP is read from (or written into) the

CSR selected in the RAP.

Once written, the address in RAP remains unchanged

until rewritten.

To distinguish the data port from the address port, a discrete input pin is provided.

ADR Input Pin Port

L Register Data Port (RDP)

H Register Address Port (RAP)

Register Data Port (RDP)

CSR DATA

17881B-13

Bit Name Description

15:00 CSR Data Writing data into RDP writes the data

into the CSR selected in RAP. Reading the data from the RDP reads the

data from the CSR selected in RAP.

CSR

1, CSR2 and CSR3 are acces-

sible only when the STOP bit of

CSR

0 is set.

If the STOP bit is not set while attempting to access CSR

CSR

3, the C-LANCE will return

READY, but a READ operation will

return undefined data. WRITE operation is ignored.

1, CSR2 or

015

19Am79C90

Page 20

AMD

P R E L I M I N A R Y

Register Address Port (RAP)

CSR 1:0

RES

17881B-14

Bit Name Description

15:02 RES Reserved. Read as zeroes. Write as

zeroes.

01:00 CSR(1:0) CSR address select. READ/WRITE.

Selects the CSR to be accessed

through the RDP. RAP is cleared by

Bus RESET.

CSR(1 :0) CSR

00 CSR

0

01 CSR1

10 CSR2

11 CSR3

Control and Status Register Definition

Control and Status Register 0 (CSR0)

15 0

ERR

BABL

CERR

MISS

MERR

RINT

TINT

IDON

The C-LANCE updates CSR0 by logical “ORing” the previous and present value of CSR

0.

Bit Name Description

INIT

STRT

STOP

TDMD

TXON

RXON

INEA

INTR

17881B-15

Bit Name Description

14 BABL BABBLE is a transmitter timeout er-

ror. It indicates that the transmitter

has been on the channel longer than

the time required to send the maximum length packet.

BABL is a flag which indicates excessive length in the transmit buffer.

It will be set after 1519 bytes have

been transmitted, excluding preamble and start frame delimiter; the

C-LANCE will continue to transmit

until the whole packet is transmitted

or until there is a failure before the

whole packet is transmitted. When

BABL error occurs, an interrupt will

be generated if INEA = 1.

BABL is READ/CLEAR ONLY and is

set by the C-LANCE, and cleared by

writing a “1” into the bit. Writing a ”0”

has no effect. It is cleared by RESET

or by setting the STOP bit.

13 CERR COLLISION ERROR indicates that

the collision input to the C-LANCE

was not asserted during the transmission, nor within 4.0

µs after the

transmit completed. The collision after transmission is a transceiver test

feature. This function is also known

as heartbeat or SQE (Signal Quality

Error) test.

CERR is READ/CLEAR ONLY and

is set by the C-LANCE and cleared

by writing a “1” into the bit. Writing a

“0” has no effect. It is cleared by RE-

SET or by setting the STOP bit.

CERR error will not cause an interrupt to occur (INTR = 0).

12 MISS MISSED PACKET is set when the

receiver loses a packet because it

does not own any receive buffer, indicating loss of data.

FIFO overflow is not reported because there is no receive ring entry

in which to write status.

When MISS is set, an interrupt will

be generated if INEA = 1.

MISS is READ/CLEAR ONLY, and is

set by the C-LANCE and cleared by

writing a “1” into the bit. Writing a “0”

has no effect. It is cleared by RESET

or by setting the STOP bit.

15 ERR ERROR summary is set by the

“ORing” of BABL, CERR, MISS and

MERR. ERR remains set as long as

any of the error flags are true.

ERR is read only; writing it has no effect. It is cleared by Bus RESET, setting the STOP bit, or clearing the

individual error flags.

20

Am79C90

Page 21

P R E L I M I N A R Y

Bit Name Description

11 MERR MEMORY ERROR is set when the

10 RINT RECEIVER INTERRUPT is set

09 TINT TRANSMITTER INTERRUPT is set

08 IDON INITIALIZATION DONE indicates

C-LANCE is the Bus Master and has

not received READY within 25.6

µs

after asserting the address on the

DAL lines.

When a Memory Error is detected,

the receiver and transmitter are

turned off (CSR

0, TXON = 0, RXON

= 0) and an interrupt is generated if

INEA = 1.

MERR is READ/CLEAR ONLY, and

is set by the C-LANCE and cleared

by writing a “1” into the bit. Writing a

“0” has no effect. It is cleared by

RESET or by setting the STOP bit.

when the C-LANCE updates an entry in the Receive Descriptor Ring for

the last buffer received or reception

is stopped due to a failure.

When RINT is set, an interrupt is

generated if INEA = 1.

RINT is READ/CLEAR ONLY, and is

set by the C-LANCE and cleared by

writing a “1” into the bit. Writing a “0”

has no effect. It is cleared by RESET

or by setting the STOP bit.

when the C-LANCE updates an entry in the transmit descriptor ring for

the last buffer sent or transmission is

stopped due to a failure.

When TINT is set, an interrupt is

generated if INEA = 1.

TINT is READ/CLEAR ONLY and is

set by the C-LANCE and cleared by

writing a “1” into the bit. Writing a “0”

has no effect. It is cleared by RESET

or by setting the STOP bit.

that the C-LANCE has completed

the initialization procedure started

by setting the INIT bit. When IDON is

set, the C-LANCE has read the Initialization Block from memory and

stored the new parameters.

When IDON is set, an interrupt is

generated if INEA = 1.

IDON is READ/CLEAR ONLY, and is

set by the C-LANCE and cleared by

writing a “1” into the bit. Writing a “0”

has no effect. It is cleared by RESET

or by setting the STOP bit.

AMD

Bit Name Description

07 INTR INTERRUPT FLAG is set by the

“ORing” of BABL, MISS, MERR,

RINT, TINT and IDON. If INEA = 1

and INTR = 1, the INTR pin will be

LOW.

INTR is READ ONLY; writing this bit

has no effect. INTR is cleared by

RESET, by setting the STOP bit, or

by clearing the condition causing the

interrupt.

06 INEA INTERRUPT ENABLE allows the

INTR pin to be driven LOW when the

Interrupt Flag is set. If INEA = 1 and

INTR = 1, the INTR pin will be Low. If

INEA = 0, the INTR pin will be HIGH,

regardless of the state of the Interrupt Flag.

INEA is READ/WRITE and cleared

by RESET or by setting the STOP

bit.

INEA can be set at any time, regardless of the state of the STOP bit.

(reference Appendix B).

05 RXON RECEIVER ON indicates that the re-

ceiver is enabled. RXON is set when

STRT is set if DRX = 0 in the MODE

register in the initialization block and

the initialization block has been read

by the C-LANCE by setting the INIT

bit. RXON is cleared when IDON is

set from setting the INIT bit and DRX

= 1 in the MODE register, or a memory error (MERR) has occurred.

RXON is READ ONLY; writing this

bit has no effect. RXON is cleared by

RESET or by setting the STOP bit.

04 TXON TRANSMITTER ON indicates that

the transmitter is enabled. TXON is

set when STRT is set if DTX = 0 in

the MODE register in the initialization block and the INIT bit has been

set. TXON is cleared when IDON is

set and DTX = 1 in the MODE register, or an error, such as MERR,

UFLO or BUFF, has occurred during

transmission.

TXON is READ ONLY; writing this bit

has no effect. TXON is cleared by

RESET or by setting the STOP bit.

21Am79C90

Page 22

AMD

Bit Name Description

03 TDMD TRANSMIT DEMAND, when set,

TDMD is WRITE WITH ONE ONLY

02 STOP STOP disables the C-LANCE from

01 STRT START enables the C-LANCE to

00 INIT INITIALIZE, when set, causes the

causes the C-LANCE to access the

Transmit Descriptor Ring without

waiting for the polltime interval to

elapse. TDMD need not be set to

transmit a packet; it merely hastens

the C-LANCE’s response to a Transmit Descriptor Ring entry insertion by

the host.

and is cleared by the microcode after

it is used. It may read as a “1” for a

short time after it is written because

the microcode may have been busy

when TDMD was set. It is also

cleared by RESET or by setting the

STOP bit. Writing a “0” in this bit has

no effect.

all external activity when set and

clears the internal logic. Setting

STOP is the equivalent of asserting

RESET. The C-LANCE remains inactive and STOP remains set until

the STRT or INIT bit is set. If STRT,

INIT and STOP are all set together,

STOP will override the other bits and

only STOP will be set.

STOP is READ/WRITE WITH ONE

ONLY and set by RESET. Writing a

“0” to this bit has no effect. STOP is

cleared by setting either INIT or

STRT. CSR

when the STOP bit is set.

send and receive packets, perform

direct memory access, and do buffer

management. The STOP bit must be

set prior to setting the STRT bit. Setting STRT clears the STOP bit.

STRT is READ/WRITE and is set

with one only. Writing a “0” into this

bit has no effect. STRT is cleared by

RESET or by setting the STOP bit.

C-LANCE to begin the initialization

procedure and access the Initialization Block. The STOP bit must be set

prior to setting the INIT bit. Setting

INIT clears the STOP bit.

INIT is READ/WRITE WITH “1”

ONLY. Writing a “0” into this bit has

no effect. INIT is cleared by RESET

or by setting the STOP bit.

The C-LANCE latches CSR

a slave read; therefore, the CSR

status bits are guaranteed to be stable for the duration of the CSR

access.

3 must be reloaded

P R E L I M I N A R Y

0 during

Control and Status Register 1 (CSR1)

READ/WRITE: Accessible only when the STOP bit

of CSR

0 is a ONE and RAP = 01.

The C-LANCE preserves the contents of CSR

15 10

Bit Name Description

15:01 IADR The low order 15 bits of the address

of the first word (lowest address) in

the Initialization Block.

00 Must be zero.

1 after STOP.

Control and Status Register 2 (CSR2)

READ/WRITE: Accessible only when the STOP bit

of CSR

0 is a ONE and RAP = 10.

The C-LANCE preserves the contents of CSR

15 0

Bit Name Description

15:08 RES Reserved. Read as zeroes. Write as

07:00 IADR The high order 8 bits of the address

87

zeroes.

of the first word (lowest address) in

the initialization Block.

2 after STOP.

0

0

IADR

‘0’

(15:01)

17881B-16

IADR (23:16)

RES

17881B-17

22

Am79C90

Page 23

P R E L I M I N A R Y

Control and Status Register 3 (CSR3)

CSR3 allows redefinition of the Bus Master interface.

READ/WRITE: Accessible only when the STOP bit

of CSR

0 is ONE and RAP = 11.

3 is cleared by RESET or by

CSR

setting the STOP bit in CSR

15 0213

Bit Name Description

15:03 RES Reserved. Read as zeroes. Write as

02 BSWP BYTE SWAP allows the chip to oper-

01 ACON ALE CONTROL defines the asser-

00 BCON BYTE CONTROL redefines the Byte

zeroes.

ate in systems that consider bits

(15:08) of data to be pointed at an

even address and bits (07:00) to be

pointed at an odd address.

When BSWP = 1, the C-LANCE will

swap the high and low bytes on DMA

data transfers between the Receive

FIFO and bus memory. Only data

from the Receive FIFO transfers is

swapped; the Initialization Block

data and the Descriptor Ring entries

are NOT swapped.

BSWP is READ/WRITE and cleared

by RESET or by setting the STOP bit

in CSR

0.

tive state of ALE when the C-LANCE

is a Bus Master. ACON is READ/

WRITE and cleared by RESET and

by setting the STOP bit in CSR

ACON ALE

0 Asserted HIGH

1 Asserted LOW

Mask and Hold l/O pins. BCON is

READ/WRITE and cleared by

RESET or by setting the STOP bit in

CSR

0.

BCON Pin 16 Pin 15Pin 17

0 BM

1 BUSAKOBYTEBUSRQ

1 BM0 HOLD

0.

BCON

ACON

BSWP

RES

17881B-18

0.

AMD

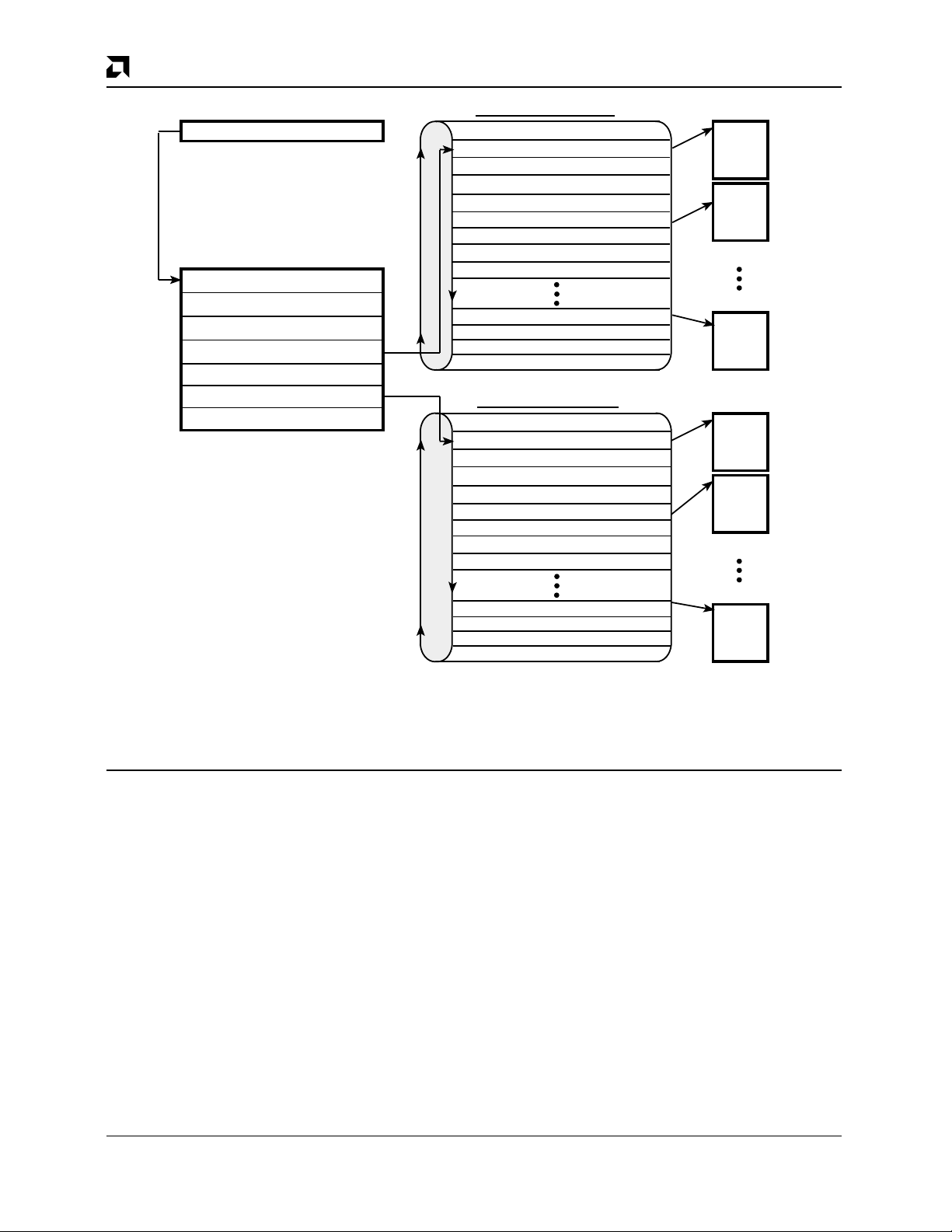

Initialization

Initialization Block

Chip initialization includes the reading of the initialization block in memory to obtain the operating parameters. The following is a definition of the Initialization

Block.

The Initialization Block is read by the C-LANCE when

the INIT bit in CSR0 is set. The INIT bit should be set before or concurrent with the STRT bit to insure proper parameter initialization and chip operation. After the

C-LANCE has read the Initialization Block, IDON is set

in CSR0 and an interrupt is generated if INEA = 1.

Higher Address TLEN–TDR (23:16) IADR +22

TDRA (15:00) IADR +20

RLEN–RDRA (23:16)IADR +18

RDRA (15:00) IADR +16

LADRF (63:48) IADR +14

LADRF (47:32) IADR +12

LADRF (31:16) IADR +10

LADRF (15:00) IADR +08

PADR (47:32) IADR +06

PADR (31:16) IADR +04

PADR (15:00) IADR +02

Base Address of BlockMODE IADR +00

Mode

The Mode Register allows alteration of the C-LANCE’s

operating parameters. Normal operation is with the

Mode Register clear.

15 02134657

14

8

DRX

DTX

LOOP

DTCR

COLL

DRTY

INTL

EMBA

RES

PROM

17881B-19

All data transfers from the C-LANCE in the Bus Master

mode are in words. However, the C-LANCE can handle

odd address boundaries and/or packets with an odd

number of bytes.

23Am79C90

Page 24

AMD

P R E L I M I N A R Y

Bit Name Description

15 PROM PROMISCUOUS mode. When

PROM = 1, all incoming packets are

accepted.

14:08 RES RESERVED. Read as zeroes. Write

as zeroes.

07 EMBA Enable Modified Back-off Algorithm.

When set (EMBA=1), enables the

modified backoff algorithm. EMBA

is cleared by activation of the RESET

pin or setting the STOP bit.

06 INTL INTERNAL LOOPBACK is used with

the LOOP bit to determine where the

loopback is to be done. Internal loopback allows the chip to receive its

own transmitted packet. Since this

represents full duplex operation, the

packet size is limited to 8–32 bytes.

Internal loopback in the C-LANCE is

operational when the packets are

addressed to the node itself.

The C-LANCE will not receive any

packets externally when it is in internal loopback mode.

EXTERNAL LOOPBACK allows the

C-LANCE to transmit a packet

through the SIA transceiver cable

out to the Ethernet medium. It is

used to determine the operability of

all circuitry and connections between the C-LANCE and the physical medium. Multicast addressing in

external loopback is valid only when

DTCR = 1 (user needs to append the

4 bytes CRC).

In external loopback, the C-LANCE

also receives packets from other

nodes. The FIFOs READ/WRITE

pointers may misalign in the

C-LANCE under heavy traffic. The

packet could then be corrupted or

not received. Therefore, the external

loopback execution may need to be

repeated. See specific discussion

under “Loopback” in later section.

INTL is only valid if LOOP = 1; otherwise, it is ignored.

LOOP INTL LOOPBACK

0 X No loopback,

normal

1 0 External

1 1 Internal

05 DRTY DISABLE RETRY. When DRTY = 1,

the C-LANCE will attempt only one

transmission of a packet. If there is a

collision on the first transmission attempt, a Retry Error (RTRY) will be

reported in Transmit Message Descriptor 3 (TMD

3).

Bit Name Description

04 COLL FORCE COLLISION. This bit allows

the collision logic to be tested. The

C-LANCE must be in internal loopback mode for COLL to be valid. If

COLL = 1, a collision will be forced

during the subsequent transmission

attempt. This will result in 16 total

transmission attempts with a retry error reported in TMD

3.

03 DTCR DISABLE TRANSMIT CRC. When

DTCR = 0, the transmitter will generate and append a CRC to the transmitted packet. When DTCR = 1, the

CRC logic is allocated to the receiver

and no CRC is generated and sent

with the transmitted packet. The

ADD_FCS bit (bit 13, TMD

1) can be

used to override a DTCR=1 setting

on a per packet basis.

During loopback, DTCR = 0 will

cause a CRC to be generated on the

transmitted packet, but no CRC

check will be done by the receiver

since the CRC logic is shared and

cannot generate and check CRC at

the same time. The generated CRC

will be written into memory with the

data and can be checked by the host

software.

If DTCR = 1 during loopback, the

host software must append a CRC

value to the transmit data.

The receiver will check the CRC on

the received data and report any

errors.

02 LOOP LOOPBACK allows the C-LANCE to

operate in full duplex mode for test

purposes. The packet size is limited

to 8–32 bytes.The received packet

can be up to 36 bytes (32 + 4 bytes

CRC) when DTCR = 0. During loopback, the runt packet filter is disabled

because the maximum packet is

forced to be smaller than the

minimum size Ethernet packet

(64bytes).

LOOP = 1 allows simultaneous

transmission and reception for a

message constrained to fit within the

Transmit FIFO. The C-LANCE waits

until the entire message is in the

Transmit FIFO before serial transmission begins. The incoming data

stream fills the Receive FIFO. Moving the received message out of the

Receive FIFO to memory does not

begin until reception has ceased.

24

Am79C90

Page 25

P R E L I M I N A R Y

Bit Name Description

In loopback mode, transmit data

chaining is not possible. Receive

data chaining is possible if receive

buffers are 32 bytes long to allow

time for lookahead.

01 DTX DISABLE THE TRANSMITTER

00 DRX DISABLE THE RECEIVER causes

47 10

47:00 PADR PHYSICAL ADDRESS is the unique

causes the C-LANCE to not access

the Transmitter Descriptor Ring, and

therefore, no transmissions are attempted. DTX = 1 will clear the

TXON bit in CSR

is complete.

the C-LANCE to reject all incoming

packets and not access the Receive

Descriptor Ring. DRX = 1 will clear

the RXON bit in the CSR

itialization is complete.

48-bit physical address assigned to

the C-LANCE. PADR (0) must be

zero.

0 when initialization

0 when in-

‘0’

PADR (47:01)

17881B-20

Logical Address Filter

63 0

LADRF

17881B-21

63:00 LADRF The 64-bit mask used by the

C-LANCE to accept logical

addresses.

The purpose of logical (or group or multicast) addresses

is to allow a group of nodes in a network to receive the

same message. Each node can maintain a list of multicast addresses that it will respond to. The logical address filter mechanism in the C-LANCE is a hardware

aide that reduces the average amount of host computer

time required to determine whether or not an incoming

packet with a multicast destination address should be

accepted.

The logical address filter hardware is an implementation

of a hash code searching technique commonly used by

software programmers. If the multicast bit of the destination address of an incoming packet is set, the

AMD

hardware maps this address into one of 64 categories

which correspond to 64 bits in the Logical Address Filter

Register. The hardware then accepts or rejects the

packet depending on the state of the bit in the Logical

Address Filter Register which corresponds to the selected category. For example, if the address maps into

category 24, and bit 24 of the logical address filter register is set, the packet is accepted.

A node can be made a member of several groups by setting the appropriate bits in the logical address filter

register.

The details of the hardware mapping algorithm are as

follows:

If the first bit of an incoming address is a “1” [PADR (0)

=1], the address is deemed logical and is passed

through the logical address filter.

The logical address filter is a 64-bit mask composed of

four sixteen-bit registers, LADRF (63:00) in the initialization block, that is used to accept incoming Logical Addresses. The incoming address is sent through the CRC

circuit. After all 48 bits of the address have gone through

the CRC circuit, the high order 6 bits of the resultant

CRC (32-bit CRC) are strobed into a register. This register is used to select one of the 64-bit positions in the

Logical Address Filter. If the selected filter bit is a “1,” the

address is accepted and the packet will be put in memory. The logical address filter only assures that there is a

possibility that the incoming logical address belongs to

the node. To determine if it belongs to the node, the incoming logical address that is stored in main memory is

compared by software to the list of logical addresses to

be accepted by this node.

The task of mapping a logical address to one of 64-bit

positions requires a simple computer program (see Appendix A) which uses the same CRC algorithm (used in

C-LANCE and defined per Ethernet) to calculate the

HASH (see Figure 7).

Driver software that manages a list of multicast addresses can work as follows. First the multicast address

list and the logical address filter must be initialized.

Some sort of management function such as the driver

initialization routine passes to the driver a list of addresses. For each address in the list the driver uses a

subroutine similar to the one listed in the appendix to set

the appropriate bit in a software copy of the logical address filter register. When the complete list of addresses

has been processed, the register is loaded.

Later, when a packet is received, the driver first looks at

the Individual/Group bit of the destination address of the

packet to find out whether or not this is a multicast address. If it is, the driver must search the multicast address list to see if this address is in the list. If it is not in

the list, the packet is discarded.

25Am79C90

Page 26

AMD

P R E L I M I N A R Y

The Broadcast address, which consists of all ones is a

special multicast address. Packets addressed to the

broadcast address must be received by all nodes. Since

broadcast packets are usually more common than other

multicast packets, the broadcast address should be the

first address in the multicast address list.

The Broadcast address does not go through the Logical

Address Filter and is always enabled. If the Logical Address Filter is loaded with all zeroes, all incoming logical

addresses except broadcast will be rejected. The multicast addressing in external loopback is operational only

when DTCR in the mode register is set to 1.

32-Bit Resultant CRC

CRC

Gen

Enable

31 26 0

64

Logical Address

Filter

63 0

Destination

Address

47 10

“1”

Bit Name Description

31:29 RLEN RECEIVE RING LENGTH is the

number of entries in the receive ring

expressed as a power of two.

RLEN Number of Entries

01

12

24

38

416

532

664

7 128

28:24 RES RESERVED. Read as zeroes. Write

as zeroes.

23:03 RDRA RECEIVE DESCRIPTOR RING AD-

DRESS is the base address (lowest

address) of the Receive Descriptor

Ring.

02:00 MUST BE ZEROES. These bits are

RDRA (02:00) and must be zeroes

because the Receive Ring is aligned

on a quadword boundary.

MUX

6

Select

*Match - 1, the packet is accepted

Match - 0, the packet is rejected

Figure 7. Logical Address Filter Operation

Receive Descriptor Ring Pointer

31 20

29282423 3

RES

RLEN

000 ‘(Quadword

Boundary)’

RDRA (23:03)

Match*

17881B-22

17881B-23

Transmit Descriptor Ring Pointer

31 20

29282423 3

RES

TLEN

31:29 TLEN TRANSMIT RING LENGTH is the

number of entries in the Transmit

Ring expressed as a power of two.

28:24 RES RESERVED. Read as zeroes. Write

as zeroes.

23:03 TDRA TRANSMIT DESCRIPTOR RING

ADDRESS is the base address (lowest address) of the Transmit Descriptor Ring.

02:00 MUST BE ZEROES. These bits are

TDRA (02:00) and must be zeroes

because the Transmit Ring is

aligned on a quadword boundary.

000 ‘(Quadword

Boundary)’

TDRA (23:03)

17881B-24

TLEN Number of Entries

01

12

24

38

416

532

664

7 128

26

Am79C90

Page 27

P R E L I M I N A R Y

Buffer Management

Buffer Management is accomplished through message

descriptors organized in ring structures in memory.

Each message descriptor entry is four words long.

There are two rings allocated for the device: a Receive

ring and a Transmit ring. The device is capable of polling

each ring for buffers to either empty or fill with packets to

or from the channel. The device is also capable of entering status information in the descriptor entry. C-LANCE

polling is limited to looking one ahead of the descriptor

entry the C-LANCE is currently working with.

The location of the descriptor rings and their length are

found in the initialization block, accessed during the initialization procedure by the C-LANCE. Writing a “ONE”

into the STRT bit of CSR0 will cause the C-LANCE to

start accessing the descriptor rings and enable it to send

and receive packets.

The C-LANCE communicates with a HOST device

through the ring structures in memory. Each entry in the

ring is either owned by the C-LANCE or the HOST.

There is an ownership bit (OWN) in the message descriptor entry. Mutual exclusion is accomplished by a

protocol which states that each device can only relinquish ownership of the descriptor entry to the other device; it can never take ownership, and no device can

change the state of any field in any entry after it has relinquished ownership.

Descriptor Ring

Each descriptor in a ring in memory is a 4-word entry.

The following is the format of the receive and the transmit descriptors.

Receive Message Descriptor Entry

Receive Message Descriptor 0 (RMD0)

15 0

LADR

17881B-25

Bit Name Description

15:00 LADR The LOW ORDER 16 address bits of

the buffer pointed to by this descriptor. LADR is written by the host and is

not changed by the C-LANCE.

AMD

Receive Message Descriptor 1 (RMD1)

15 87 0

HADR

ENP

STP

BUFF

CRC

OFLO

FRAM

ERR

OWN

17881B-26

Bit Name Description

15 OWN This bit indicates that the descriptor

entry is owned by the host (OWN = 0)

or by the C-LANCE (OWN = 1). The

C-LANCE clears the OWN bit after

filling the buffer pointed to by the descriptor entry. The host sets the

OWN bit after emptying the buffer.

Once the C-LANCE or host has relinquished ownership of a buffer, it

must not change any field in the four

words that comprise the descriptor

entry.

14 ERR ERROR summary is the OR of

FRAM, OFLO, CRC or BUFF.

13 FRAM FRAMING ERROR indicates that

the incoming packet contained a

non-integer multiple of eight bits and

there was a CRC error. If there was

not a CRC error on the incoming

packet, then FRAM will not be set

even if there was a non-integer multiple of eight bits in the packet. FRAM

is not valid in internal loopback

mode. FRAM is valid only when ENP

is set and OFLO is not.

27Am79C90

Page 28

AMD

P R E L I M I N A R Y

Bit Name Description

12 OFLO OVERFLOW error indicates that the

receiver has lost all or part of the incoming packet due to an inability to

store the packet in a memory buffer

before the internal Receive FIFO

overflowed. OFLO is valid only when

ENP is not set.

11 CRC CRC indicates that the receiver has

detected a CRC error on the incoming packet. CRC is valid only when

ENP is set and OFLO is not.

10 BUFF BUFFER ERROR is set any time the

C-LANCE does not own the next

buffer while data chaining a received

packet. This can occur in either of

two ways: 1) the OWN bit of the next

buffer is zero, or 2) the Receive FIFO

overflow occurred before the

C-LANCE has performed a

lookahead poll of the next receive

descriptor.

If a Buffer Error occurs, an Overflow

Error may also occur internally in the

Receive FIFO, but will not be reported in the descriptor status entry

unless both BUFF and OFLO errors

occur at the same time.

09 STP START OF PACKET indicates that

this is the first buffer used by the

C-LANCE for this packet. It is used

for data chaining buffers.

08 ENP END OF PACKET indicates that this

is the last buffer used by the

C-LANCE for this packet. It is used

for data chaining buffers. If both STP

and ENP are set, the packet fits into

one buffer and there is no data

chaining.

07:00 HADR The HIGH ORDER 8 address bits of

the buffer pointed to by this descriptor. This field is written by the host

and unchanged by the C-LANCE.

Receive Message Descriptor 3 (RMD3)

15 0

15:12 RES RESERVED. Read as zeroes. Write

11:00 MCNT MESSAGE BYTE COUNT is the

1211

MCNT

RES

17881B-28

as zeroes.

length in bytes of the received message. MCNT is valid only when ERR

is clear and ENP is set. MCNT is written by the chip and cleared by the

host.

Transmit Message Descriptor Entry

Transmit Message Descriptor 0 (TMD0)

15 0

LADR

17881B-29

Bit Name Description

15:00 LADR The LOW ORDER 16 address bits of

Transmit Message Descriptor 1 (TMD1)

15 87 0

the buffer pointed to by this descriptor. LADR is written by the host and is

not changed by the C-LANCE.

Receive Message Descriptor 2 (RMD2)

15 0

15:12 MUST BE ONES. This field is written

11:00 BCNT BUFFER BYTE COUNT is the length

28

1211

BCNT

Must be Ones

17881B-27

by the host and is not changed by the

C-LANCE.

of the buffer pointed to by this descriptor, expressed as a two’s complement number. This field is written

by the host and is not changed by the

C-LANCE. Minimum buffer size is 64

bytes for the first buffer of packet.

Am79C90

HADR

ENP

STP

DEF

ONE

MORE

ADD_FCS

ERR

OWN

17881B-30

Page 29

P R E L I M I N A R Y

Bit Name Description

15 OWN This bit indicates that the descriptor

entry is owned by the host (OWN =

O) or by the C-LANCE (OWN = 1).

The host sets the OWN bit after filling

the buffer pointed to by this descriptor. The C-LANCE clears the OWN

bit after transmitting the contents of

the buffer. Neither the host nor the CLANCE may alter a descriptor entry

after it has relinquished ownership.

14 ERR ERROR summary is the “OR” of

LCOL, LCAR, UFLO or RTRY.

13 ADD_FCS Setting ADD_FCS=1, instructs the

controller to append a CRC to this

transmitted frame, regardless of the

setting of the DTCR bit (bit 3 in the

Mode Register). The ADD_FCS bit

allows the controller to be configured

to append CRC on a per packet basis, when DTCR=1. ADD_FCS is

only valid when STP=1.

12 MORE MORE indicates that more than one

retry was needed to transmit a

packet.

11 ONE ONE indicates that exactly one retry

was needed to transmit a packet.

The ONE flag is not valid when

LCOL is set.

10 DEF DEFERRED indicates that the

C-LANCE had to defer while trying to

transmit a packet. This condition occurs if the channel is busy when the

C-LANCE is ready to transmit.

09 STP START OF PACKET indicates that

this is the first buffer to be used by

the C-LANCE for this packet. It is

used for data chaining buffers. STP

is set by the host and is not changed

by the C-LANCE. The STP bit must

be set in the first buffer of the packet,

or the C-LANCE will skip over this

descriptor and poll the next descriptor(s) until the OWN and STP bits

areset.

08 ENP END OF PACKET indicates that this

is the last buffer to be used by the CLANCE for this packet. It is used for

data chaining buffers. If both STP

and ENP are set, the packet fits into

one buffer and there is no data

chaining. ENP is set by the host and

is not changed by the C-LANCE.

07:00 HADR The HIGH ORDER 8 address bits of

the buffer pointed to by this descriptor. This field is written by the host

and is not changed by the C-LANCE.

AMD

Transmit Message Descriptor 2 (TMD2)

15 0

Bit Name Description

15:12 ONES Must be ones. This field is set by the

11:00 BCNT BUFFER BYTE COUNT is the us-

1211

BCNT

ONES

17881B-31

host and is not changed by the

C-LANCE.

able length in bytes of the buffer

pointed to by this descriptor expressed as a negative two’s complement number. This is the number of

bytes from this buffer that will be

transmitted by the C-LANCE. This

field is written by the host and is not

changed by the C-LANCE. The first

buffer of a packet has to be at least

100 bytes minimum when data

chaining and 64 byte (DTCR = 1) or

60 bytes (DCTR = 0) when not data

chaining.

29Am79C90

Page 30

AMD

P R E L I M I N A R Y

Transmit Message Descriptor 3 (TMD3)

15 109 0

TDR

RTRY

LCAR

LCOL

RES

UFLO

BUFF

17881B-32

Bit Name Description

15 BUFF BUFFER ERROR is set by the

14 UFLO UNDERFLOW ERROR indicates

Upon UFLO error, transmitter is

13 RES RESERVED bit. The C-LANCE will

12 LCOL LATE COLLISION indicates that a

11 LCAR LOSS OF CARRIER is set when the

C-LANCE during transmission when

the C-LANCE does not find the ENP

flag in the current buffer and does

not own the next buffer. This can occur in either of two ways: either the

OWN bit of the next buffer is zero, or

Transmit FIFO underflow occurred

before the C-LANCE has performed

a lookahead poll of the next transmit

descriptor. BUFF is set by the

C-LANCE and cleared by the host.

BUFF error will turn off the transmitter (CSR

If a Buffer Error occurs, an Underflow

Error will also occur. BUFF error is

not valid when LCOL or RTRY error

is set during TX data chaining.

that the transmitter has truncated a

message due to data late from memory. UFLO indicates that the Transmit FIFO has emptied before the end

of the packet was reached.

turned off (CSR

write this bit with a “0.”

collision has occurred after the slot

time of the channel has elapsed. The

C-LANCE does not retry on late

collisions.

carrier input (RENA) to the