Datasheet AM79C32AVC, AM79C32AJC, AM79C30AVC, AM79C30AJC Datasheet (AMD Advanced Micro Devices)

Page 1

FINAL

Publication# 09893 Rev: H Amendment/0

Issue Date: December 1998

Am79C30A/32A

Digital Subscriber Controller™ (DSC™) Circuit

DISTINCTIVE CHARACTERISTICS

■

Combines CCITT I.430 S/T- Interface Transceiver,

D-Channel LAPD Processor, Audio

■

Processor (DSC device only), and IOM-2

Interface in a single chip

■

Special operating modes allow realization of

CCITT I.430 power-compliant terminal

equipment

■

S- or T-Interface Transceiver

— Level 1 Physical Layer Controller

— Supports point-to -point, short and extended

passive bus configurations

— Provides multiframe support

■

Certified protocol software support available

■

CMOS technology, TTL compatible

■

D-channel processing capability

— Flag generation/detection

— CRC generation/checking

— Zero insertion/deletion

— Four 2-byte address detectors

— 32-byte receive and 16-byte transmit FIFOs

BLOCK DIAGRAM

AINA

AREF

AINB

EAR1

EAR2

LS1

Audio Interface

LS2

XTAL1

XTAL2

MCLK

CS

WR

RD

CAP1

Main Audio

Processor (MAP)

(Am79C30A

Only)

Oscillator

(OSC)

CAP2

Ba

SBP/IOM-2 Interface

SBIN SCLK BCL/CH2STRB*

SBIOUT SFS

Peripheral Port

(PP)

Bd Be Bf

B-channel Multiplexer

(MUX)

Bb Bc

Microprocessor Interface

(MUX)

B1

B2

HSW

S/T Line

Interface Unit

(LIU)

D

Channel

D-Channel Data

Link Controller

(DLC)

D

Channel

LOUT1

LOUT2

LIN1

LIN2

RESET

S/T Interface

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help y ou e v aluate this produc t. A MD res erves the r ight to c hange or discontin ue w ork on this propos ed

product without notice.

D7 D6 D5 D4 D3 D2 D1 D0 INT

Microprocessor Interface

A2 A1 A0

09893H-1

Page 2

DISTINCTIVE CHARACTERISTICS (continued)

■ Audio processing capability ( DSC ci rcu it on ly)

— Registers for implementation of software-based

speaker phone algorithms

— Dual audio inputs

— Earpiece and loudspeaker drivers

— Codec/filter with A/µ selection

— Programmable gain and equalization filters

GENERAL DESCRIPTION

The Am79C30A Digital Subscriber Controller (DSC)

Circuit and Am79C32A ISDN Data Controller (IDC) Circuit, shown in the Block Diagram, a llow the realiz ation

of highly-integrated Term inal Equipment for the ISDN.

The Am79C30A/32A is fully compatible with the

CCITT-I-series recommendations for the S and T reference points, ensuring that the user of the device may

design TEs which conform to the international standards.

The Am79C30A/32A provides a 192-Kbit/s full d uplex

digital path over four wires between the TE located on

the subscriber's premises and the NT or PABX linecard. All phys ical layer functions and procedur es are

impleme nted in ac cordance with CCIT T Recomm endation I.430, including f raming, sy nchroni za tion, ma intenance, and multiple terminal contention. Both

point-to-point and point-to-multipoint configurations are

supported.

The Am79C30A/32A processes the ISDN basic rate bit

stream, which consists of B1 (64 Kbit/s), B2 (64 Kbit/s),

and D (16 Kbit/s) channels. The B channels are routed

to and from different sections of the Am79C30A/32A

— Programmable sidetone level

— Programmable DTMF, single tone, progress

tone, and ringer tone generation

— Programmable on-chip microphone amplifier

■ P in and software comp atible with the

Am79C32A ISDN Data Controller (IDC™) Cir cuit.

The Am79C32A is used in data-only

applications.

under software control. The D channel is partially processed by the DSC/IDC circuit and is passed to the microprocessor for further processing.

The Main Audio Processor (M AP) uses D igital Signa l

Processing (DSP) to implement a high performance

codec/filter function. The M AP interface supports a

loudspeaker, an earpiece, and t wo separate audio inputs. Progra mmable on-c hip gain is provided t o simplify use of low output level microphones. The user may

alter frequency respons e an d gain of the MAP receive

and transmit paths. T one generators are included to implement ringing, call progress, and DTMF signals.

A Peripheral Po rt (PP) is provided to allow the B channels to be routed off- chip for processing by other peripherals. This port is configurable as either an

industr y-stand ard IOM-2 po rt, or as a serial bus por t

(SBP).

The TE de sign proc ess is si mplified by the availabilit y

of certified protocol software packages, which provide

complete system solutions through OSI Layer 3.

2 Am79C30A/32A Data Sheet

Page 3

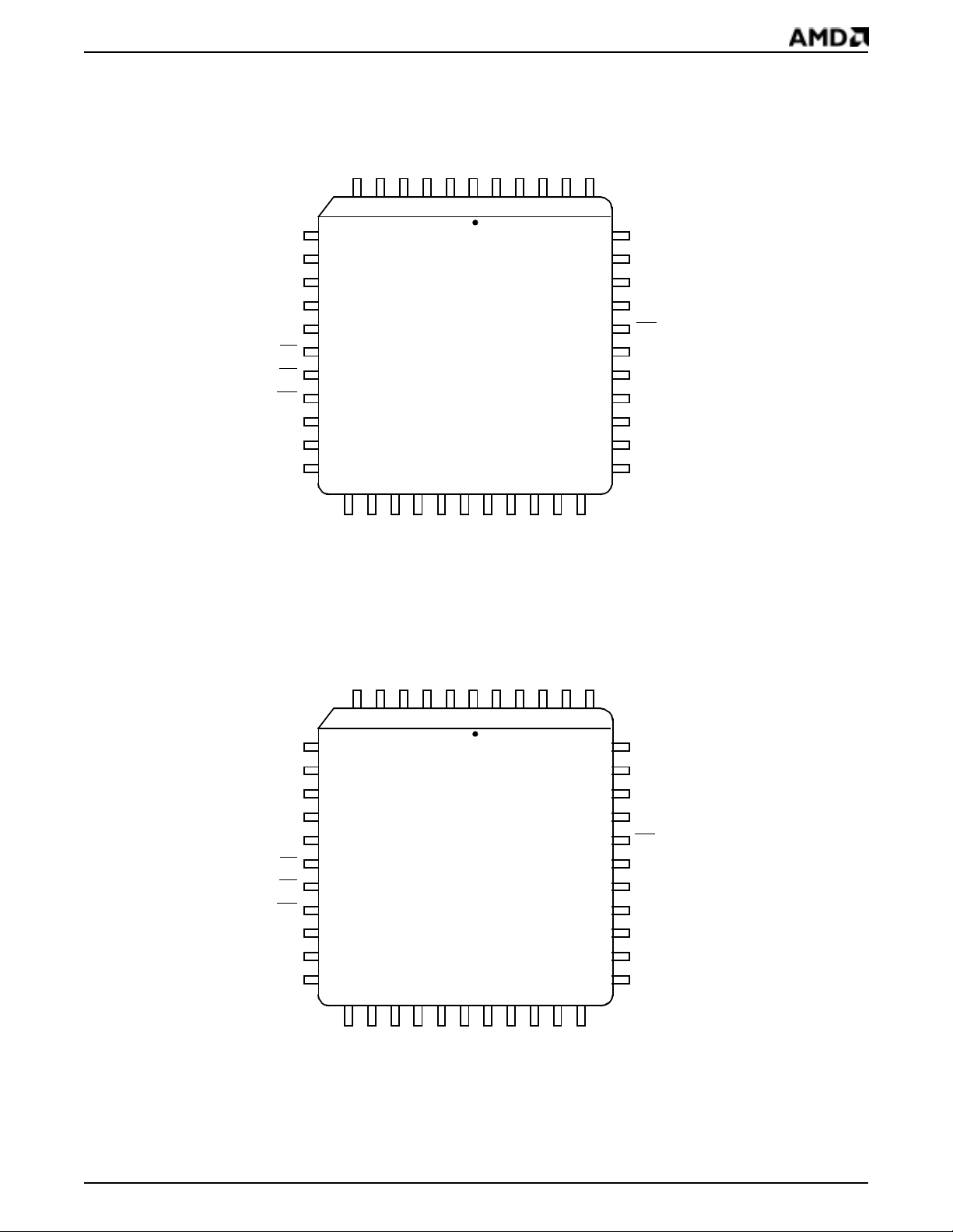

CONNECTION DIAGRAMS

Top View

CAP1

CAP2

AV

CC

DV

CC

RESET

CS

RD

WR

DV

SS

A2

A1

10

11

12

13

14

15

16

17

7

8

9

AVSSAINB

6

18

AINA

5

4

192021

44-Pin PLCC

EAR2

EAR1

LS2

3

2

1

Am79C30A

22

23

24

LS1

44

25

AREF

43

26

LIN1

42

27

LIN2

41

39

38

37

36

35

34

33

32

31

30

29

28

HSW

40

LOUT1

LOUT2

AV

SS

DV

SS

INT

XTAL 1

XTAL 2

MCLK

SFS

SCLK

SBOUT

RSRVD

RSRVD

AV

CC

DV

CC

RESET

CS

RD

WR

DV

SS

A2

A1

7

8

9

10

11

12

13

14

15

16

17

A0

D7D6D5

RSRVD

RSRVD

6

5

181920

44-Pin PLCC

RSRVD

RSRVD

4

3

Am79C32A

21

D4

22

BCL/CH2STRB

RSRVD

2

D3D2D1

LS2

1

23

24

LS1

44

25

AREF

43

26

LIN1

42

D0

27

LIN2

41

SBIN

28

HSW

40

39

38

37

36

35

34

33

32

31

30

29

LOUT1

LOUT2

AV

SS

DV

SS

INT

XTAL 1

XTAL 2

MCLK

SFS

SCLK

SBOUT

A0

D7D6D5

D4

D3D2D1

D0

SBIN

Note:

1. Pin 1 is marked for orientation purposes.

BCL/CH2STRB

2. RSRVD = Reserved pin; should not be connected externally to any signal or supply.

Am79C30A/32A Data Sheet 3

Page 4

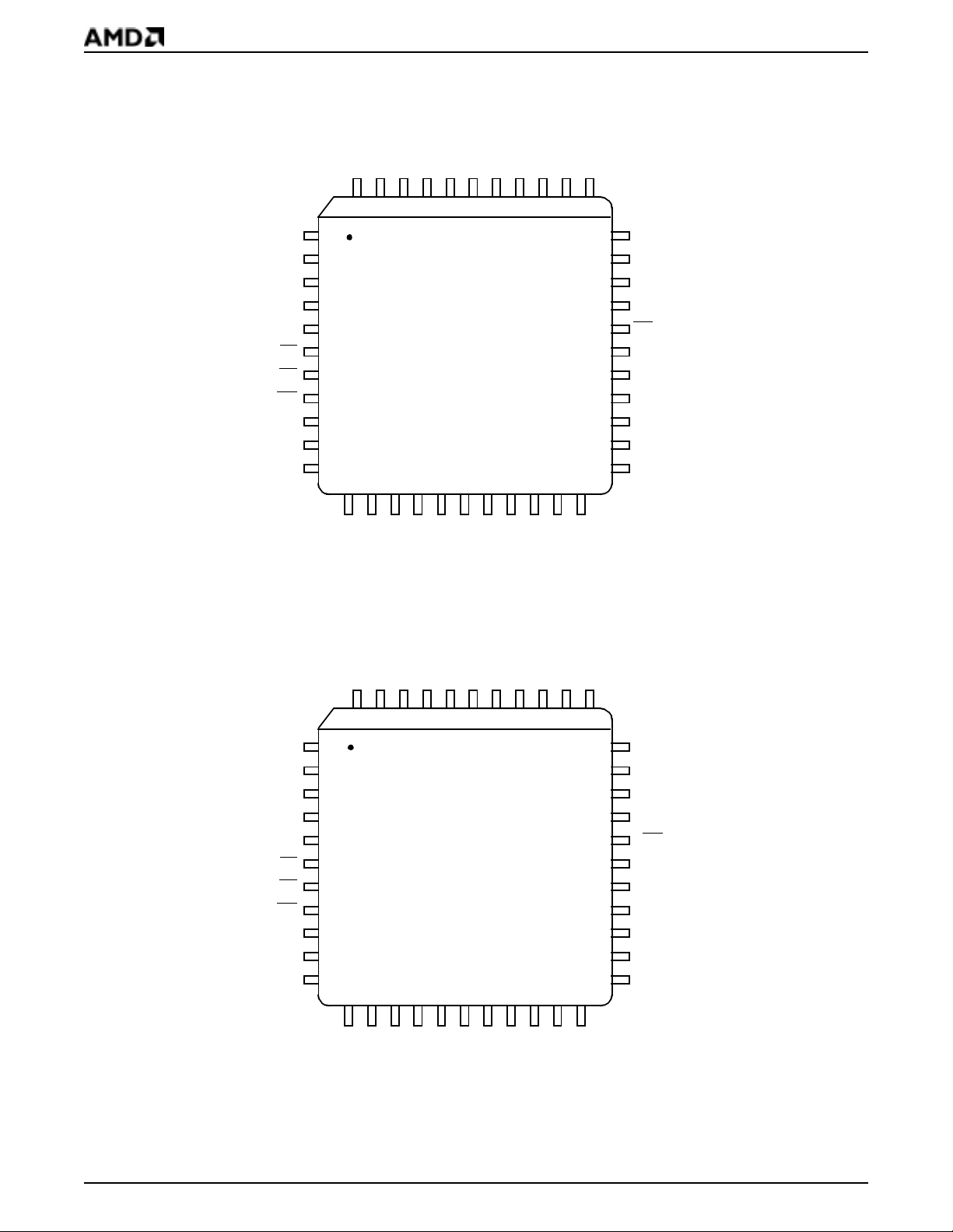

CONNECTION DIAGRAMS (continued)

Top View

AVSSAINB

AINA

44-Pin TQFP

EAR2

EAR1

LS2

LS1

AREF

LIN1

LIN2

HSW

CAP1

CAP2

AV

CC

DV

CC

RESET

CS

RD

WR

DV

SS

A2

A1

1

2

3

4

5

6

7

8

9

10

11

444342

12

131415

A0

D7D6D5

41

40

39

Am79C30A

16

17

D4

BCL/CH2STRB

44-Pin TQFP

38

37

18

19

20

D3D2D1

36

21

D0

35

34

LOUT1

33

LOUT2

32

AV

31

30

29

28

27

26

25

24

23

SS

DV

SS

INT

XTAL1

XTAL2

MCLK

SFS

SCLK

SBOUT

22

SBIN

RSRVD

RSRVD

AV

CC

DV

CC

RESET

CS

RD

WR

DV

SS

A2

10

A1

11

Note:

Pin 1 is marked f or ori entation purposes.

RSRVD

44

1

2

3

4

5

6

7

8

9

121314

A0

RSRVD

RSRVD

43

42

15

D7D6D5

RSRVD

RSRVD

41

40

Am79C32A

16

17

D4

BCL/CH2STRB

LS2

LS1

39

38

18

19

D3D2D1

RSRVD

LIN1

LIN2

HSW

37

36

35

34

20

21

33

32

31

30

29

28

27

26

25

24

23

22

LOUT1

LOUT2

AV

SS

DV

SS

INT

XTAL1

XTAL2

MCLK

SFS

SCLK

SBOUT

D0

SBIN

4 Am79C30A/32A Data Sheet

Page 5

ORDERING INFORMATION

Standard Products

AMD® standard products are available in several packages and operating ranges. The order number (Valid Combination) is

formed by a combination of the elements below.

AM79C30A/32A

JC

OPTIONAL PROCESSING

Blank = Standard Processing

TEMPERATURE RANGE

C = Commercial (0°C to +70°C)

PACKAGE TYPE

J = 44-Pin Plastic Leaded Chip Carrier (PL 044)

V = 44-Pin Thin Plastic Quad Flat Pack (PQT044)

SPEED OPTION

Not Applicable

DEVICE NAME/DESCRIPTION

Am79C30A/32A

Digital Subscriber Controller (DSC) device

ISDN Data Controller (IDC) device

V alid Combinations

AM79C30A JC, VC

AM79C32A JC, VC

Reference Appendix C, Figures 1 & 2, for specific mechanical dimensions of the two packages.

Valid Combina tions li st configu rations p lanned to be supported in volume for this device. Consult the loc al AMD sales

office t o conf irm av ai labi lity of specif ic valid combinations and

to check on newly released combinations.

Valid Combinations

Am79C30A/32A Data Sheet 5

Page 6

PIN DESCRIPTION*

Line Interface Unit (LIU)

HSW

Hook-Switch (Input)

The HSW signal indicates if the hook-switch is on or off

hook. This signal may be generated with a mechanical

switch wired to ground with a pu ll-up resistor to V

Any change in the HSW state causes an interrupt.

LIN1, LIN2

Subscri ber Li ne Input (Differential Inpu t s)

The LIN1 and LIN2 inputs interface to the subscriber (S

reference point) via an isolation transformer. LIN2 is the

positive inpu t; LIN1 is the ne gative input. Th ese pins

are not TTL compatible.

LOUT1, LOUT2

Subscriber Line Output (Differential Outputs)

The LOUT1 and LOUT2 line driver output signals interface to the subscriber line at the S reference point via

an isolation transformer and resistors. LOUT2 is the

positive S-interface driver (sources current during a

High mark), and LOUT 1 is the negative S-interface

driver (sources current during Low mark). For

multi-point applications, all TEs must maintain the

same po larity on t he S Interface. T hese pins are not

TTL compatible.

CC

Main A ud io Processor (MAP)

All MAP pins are analog, and therefore are not TTL

compatible.

AINA, AINB

Analog (Inputs)

These analog inputs allow for two separate analog (audio) inputs to the transmit path of the codec/filter.Input

signals on either of the se pins must be referenced to

AREF.

AREF

Analog Reference (Output)

This is a nominal 2.25-V reference voltage output for biasing the analog inputs. When the MAP is disabled,

this pin is high impedance.

CAP1, CAP2

Capacitor/Resistor (CAP1, Input; CAP2, Output)

An external resistor and capacitor are connected in series between thes e pins. These components are

needed for the integrator in the Analog-to-Digital Converter (ADC).

EAR1, EAR2

Earpiece Interface (Differential Outputs)

EAR1 and EAR2 are the outputs from the receive path

of the codec/filter. These differential outputs can directly drive a minimum load of 130 ohms.

LS1, LS2

Loudspeaker Interface (Differential Outputs)

.

LS1 and LS2 are push-pull outputs which can directly

drive a minimum load of 40 ohms.

Microprocessor Interface (MPI)

A2–A0

Address Line (Inputs)

A2, A1, and A0 signals select source and dest ination

registers for read and write operations on the data bus.

CS

Chip Select (Input)

must be Low to re ad or w rite to the Am 79C30A /

CS

32A. Data transfer occurs over the bidirectional data

lines (D7–D0).

D7–D0

Data Bus ( Bidi rect ional with High -I mpeda nce Stat e)

The eight bidire ctional data bus lines are used to exchange information with the microprocessor. D0 is the

least significant bit (LSB) and D7 is the most significant

bit (MSB). A High on the data bus line corresponds to

a logic 1, and Low corresponds to a logic 0. These lines

act as inputs when both WR and CS are active and as

outputs when both RD

inactive or both RD

pins are in a high-impedance state.

INT

Interrupt (Output)

An active Low output on the INT

nal microprocessor that the Am 79C30A /32A needs interrupt service. INT

INT

pin remains active until the Interrupt Reg ister (IR)

is read or the Am79C30A/32A is reset.

RESET

Reset (Input)

Reset is an active High signal which causes the

Am79C3 0A/32A to im mediate ly termin ate its prese nt

activity and initialize to the reset condition. When reset

returns Low, the Am79C30A/32A enters the Idle mode.

The MCLK output remains active while RESET is hel d

High.

and CS are active. When CS is

and WR are inactive, the D7–D 0

pin informs the exter-

is updated once every 125 µs. The

Note:

* All signal levels are TTL compatible unless otherwise stated.

6 Am79C30A/32A Data Sheet

Page 7

RD

Read (Input)

The active Low read signal is conditioned by CS

and indicates that internal information is to be transferred

onto the data bus. A num ber of interna l registers are

user accessible. The contents of the accessed register

are transferred onto the data bus after the High to Low

transition of the RD

input.

WR

Write (Input)

The active Low write signal is conditioned by CS

and

indicates that external information on the data bus is to

be transferred to an inter nal register. The contents of

the data bus are loaded on the Low t o High transition of

the WR

input.

Oscillator (OSC)

MCLK

Master Clock (Output)

The MCLK output is available for use as the system

clock for the microprocessor. MCLK is derived from the

12.288-MHz crystal via a programmable divider in the

Am79C30A/32A which provides the following MCLK

output frequencies: 12.288, 6.144, 4.096, 3.072, 1.536,

0.768, and 0.384 MHz.

XTAL1, XTAL2

External Crystal (Output, Input)

XT AL1 and XTAL2 are connected to an external parallel

resonant cr ystal for the on-chip oscillator. XTAL2 can

also be connect ed to an external source inste ad of a

crystal, in which case XTAL1 should be left disconnected. The frequency must be 12.288 MHz, ± 80 ppm.

Peripheral Port (PP)

SBIN

Serial Data (I np ut / Output)

When the Peripheral P ort is programmed to SBP mode,

SBIN operates as an input for serial data. When the Peripheral Por t is programm ed to IOM-2 mode, SBI N

functions as the data input except in the special case of

IOM-2 Slave mode, when it becomes an open-drain

output during pa rt or all of the IOM-2 fram e, or when

deactivated.

SBOUT

Serial Data (I np ut / Output)

When the Peripheral P ort is programmed to SBP mode,

SBOUT operates as an output for serial data. When the

Peripheral P ort is programmed to IOM-2 mode, SBOUT

functions as the data output except in the special case

of IOM-2 Slave mode when it becomes an input during

part or all of the IOM-2 frame.

SCLK

Serial Data Clock (Input/Output)

When the PP is prog r ammed to SBP mode, SCLK outputs a 192-k Hz data clock, wh ich may be inverted

under software control. When the PP is programmed to

IOM-2 Mast er m ode, SC LK o utputs a 1.536 -MHz 2X

data clock. In IOM- 2 Slave mode, SCLK functions as

the clock input. The SCLK pin defaults to a high-impedance st ate upon reset, bu t becom es active a fter any

MUX connection is made or if the PP is programmed to

IOM-2 Master mode.

SFS

Serial Fram e Syn c (Inp ut / Ou tp ut)

In SBP mode, SFS outputs an 8-kHz frame synchronization signal. SFS is an output in IOM-2 Master mode,

and an input in IOM -2 S lave mode. As an out put , S FS

is active for 8-bit periods. The SFS pin defaults to a

high-impedance state upon reset, but becomes active

after any MUX connection is made or if the PP is programmed to IOM-2 Master mode. For SBP mod e, the

active signal state is Low during Idle and 8 kH z in Active Data Only and Active Voice and Data modes.

BCL/CH2STRB

Bit Clock/SBP Channel 2 Strobe

(Output, Three-state)

In SBP mode, this pin provides a strobe during the 8-bit

times of the seco nd 64-kbit/s d ata channel. In IOM -2

Master mode, this pin provides a 768-kHz bit clock to

aid in the connection of non-IOM-2 devices to the port.

In IOM-2 Slave mode, this pin is high-impedance.

Power Supply Pins

PLCC/TQFP Packages

AV

CC

AV

SS

DV

SS

DV

CC

Note:

For best performance, decoupling capacitor s should be installed betw een V

Do not use separate supplies for analog and digital power

and ground connections.

+5-V analog power supply, ±5%

Analog ground

Di gital ground

+5-V digital power supply, ±5%

and VSS as close to the chip as pos sible.

CC

Am79C30A/32A Data Sheet 7

Page 8

OPERATIONAL DESCRIPTION

Overview of Power Modes

The minimization of power consumption is a key factor

in the design of Terminal Equipment for the ISDN, and

the DSC/IDC circuit employs two basic app roaches to

power management:

1. The power consumption of the DSC/IDC circuit itself is managed by using four basic power modes

which allow unu sed functional blocks to be disabled. The INIT register may be programmed to select Active V oice and Data, Active Data Only, Idle, or

Power-Down mode, depending upon which DSC/

IDC device resources are required at the time.

2. The power consumption of the controlling micro- processor system may be controlled by driving the processor clock with the DSC/IDC circuit MCLK output.

A wide ra nge of MCLK ope rating f requen cies ma y be

selected, and a special Clock Speed-Up function is

provided which increases the speed of MCLK upon

the occurrence of a key event, without processor intervention. Control of MCLK frequency and Clock

Speed-up i s acc om pl ished by pr ogramming t he I NI T

and INIT2 registers, as descri bed later.

Active Voice and Data Mode

In Active Voice and Data mode al l functional blocks of

the DSC/IDC circuit are available . Device registers may

be accessed through the MPI, the LIU and DLC are

available, t he OSC is ru nning, the Perip heral Por t is

available, MUX connections may be made, the Secondary Tone Ringer may be activated, and the MA P is

operational (DSC circuit only).

Active Data Only Mode

Active Data Only mode is similar to Active Voice and

Data mode, except that the MAP (DSC circuit only) is

disabled to reduce system power co nsumption. This increases the amount of power available f o r t he Secondary Tone Ringer or microprocessor system during the

phases of call setup and teardown, or during a

data-only telephone call.

Idle Mode

Idle mode is the RESET default mode of DSC/IDCcircuit operation, and rep resents an operational sta te in

which power consumption is reduced, yet the microprocessor system is operational to program DSC/IDC circuit registers or perform other required background

tasks. Idle mode may also be ente red by appropriate

programming of the INIT register.

In Idle mode, the MCLK output is available to drive the

microprocessor system, the MPI is available for programming of DSC /IDC registers, and the LIU is available to initiate or respond to S/T interface activity. The

HSW hookswit ch interrupt is als o avai lable in I dle mode.

Idle mode reduces DS C/IDC circ uit power cons umption by disabling the MUX, DLC, and MAP functional

blocks. The P eripheral Port is also disabled, except that

an IOM-2 activation request interr upt is possible, and

the SFS and SCLK outputs may still be activated. The

SFS and SCLK outputs are hig h impedanc e u pon RE SET, but bec ome active after any MUX connect ion is

programmed. The DLC read-only registers are cleared

when the DSC/IDC circuit enters the Idle mode.

Power-Down Mode

Power-Do wn mode consumes the least power of all the

DSC/IDC power options, and differs from Idle mode in

that all clocks, including the XTA L oscillator, are

stopped. Most functiona l blocks are disabled, except

for those required to recognize key external events that

will force the DSC/IDC circuit to return to Idle mode.

The Power-Down mode is not available unless the

Power-Down Enable bit is set in the INIT2 register; see

the INIT2 register description for further details.

Entering the Power-Down Mode

The Power-Down mode is entered by appropriate programming of the INIT and INIT2 registers. Selection of

the Power-Down mode cause s the DSC/IDCcircu it to

begin an internal countdown of at least 250 MCLK cycles after which the MCLK and XT AL1 outputs are both

stopped and held High, and the XTAL2input will be disregarded. The purpose of this countdown cycle is to

allow the microprocessor time for housekeeping operations before its clock is stopped. If an interrupt causes

the DSC INT pin to go Low during the countdown, the

Power-Do wn mode bits in the INIT register will be reset

and the countdown will be canceled.

If the LIU is enabled and in any state ot her than F3 at

the end of the countdown, MCLK is stopped but the oscillator con tinues to r un. T his al lows the LIU to identify

the incoming signal and either (1) generate an interrupt

and force the DSC/IDC circuit to Idle mode when activation is complete, or (2) move to the F3 state and stop

the oscillator once the line goes idle.

Exit i ng the Power-D own Mode

The DSC/IDC circuit will exit the Power-Down mode

and enter the Idle mode if any of the following events

occur:

• The DSC/IDC circuit receives a hardware reset via

the RESET pin.

•The CS

same ti me, as woul d occur du ring a n orma l writ e

operation from the microprocessor to the DSC circuit. No data will be transferred by this operation.

• The HSW hookswitch pin changes state, and the

hookswitch interrupt is enabled.

and WR pins a re both pulled Low at the

8 Am79C30A/32A Data Sheet

Page 9

• The LIU receiver is enabled, detects an incoming

signal on the S/T Interface, and achieves activation

as indicated by a transition to state F7. Both the INT

pin and the F7 t ransition interrupt must b e enabled

for Power-Down mode to be exited. If the LIU is enabled, it may restart the oscillator so that it can identify the activity on the interface. If the activity is

determined to be noise, the LIU will stop the oscillator and continue to monitor the line without an interrupt or returning to Idle mode.

• The IOM-2 Interface is enabled as a clock master

and the SBIN input pin goes Low . This indicates that

a slave device wants to activate the IOM-2 Interface

and communicate with the DSC circuit. Both the INT

pin and the IOM-2 timing request interrupts must be

enabled for Power-Down mode to be exited.

• The IOM-2 Interface is enabled as a clock slav e and

the SCLK input pin goes High. This indicates that

the master device is activating the IOM-2 Interface

and the DSC circuit must wake up in order to monitor the data. Both the INT

pin and the IOM-2 timing

request interrupts must be enabled for Power-Down

mode to be exited.

If the DSC/IDC circuit is awakened by any condition

other than RESET, the MCLK output will be r estored to

its previously programmed frequency, and will not generate any shortened or spurious output cycles. If the

DSC/IDC circu it is revi ved by RESET, MCLK will defau lt

to its normal 6.144-MHz rate. The DSC/IDC circuit provides a minimum of two MCLK cycles prior to activating

the interrupt pin when exiting Power-Down mode.

MCLK Frequency Control

The MCLK frequency selection bits in the INIT register

are unchanged from Revision D. However, additional

MCLK frequencies are available by programming bits in

the INIT2 reg ister. No shor tened or spur ious clock

pulses that might disru pt the external microprocessor

will result when the MCLK frequency is changed.

In order to reduce the probability of errant software disruptin g system op eration, th e INIT2 reg ister require s

two consecutive writes before the value will be entered

into the register. Note that there will be no MCLK countdown as is the c ase for entering Power-Down mode if

INIT2 is programmed to cause MCLK to STOP, and

there will be no shortened or spurious MCLK pulses.

MCLK Clock Speed-up Function

A programmable aut omatic MCL K speed-up option is

provided that will force a hardware reset of INIT2 bit s

3-0, which will cause the MCLK frequency to be restored to the value programmed in the INIT register.

There are two events that will trigger the clock

speed-up function:

1. The DLC receive FIFO threshold has been reached;

or,

2. a second packet begins to be recei ved while data

from a prior pa cket is still in th e rece i ve FIF O.

The second packet case requires provision of an interrupt; see the DLC regi ster section for further information. The clock speed-up function allows the user to

program a ver y slow MCLK frequ ency using INI T2

when D-channel activity is minimal. If a burst of activity

is seen on the D channel and it exceeds the programmed threshold of the receive FIFO or threatens to

overrun the rece ive FIFO s tatus buffers, MCL K will instantly toggle back to the higher frequency programmed in the INIT register. This eliminates the

latency incurred if an interrupt has to be serviced to

change the clock speed, and allows the overall system

power to be reduced during typical voice connec tions.

Note that automatic clock speed-up will not function unless at least one of the associated interrupts are enabled so the processor can be informed that the c lock

speed has been altered.

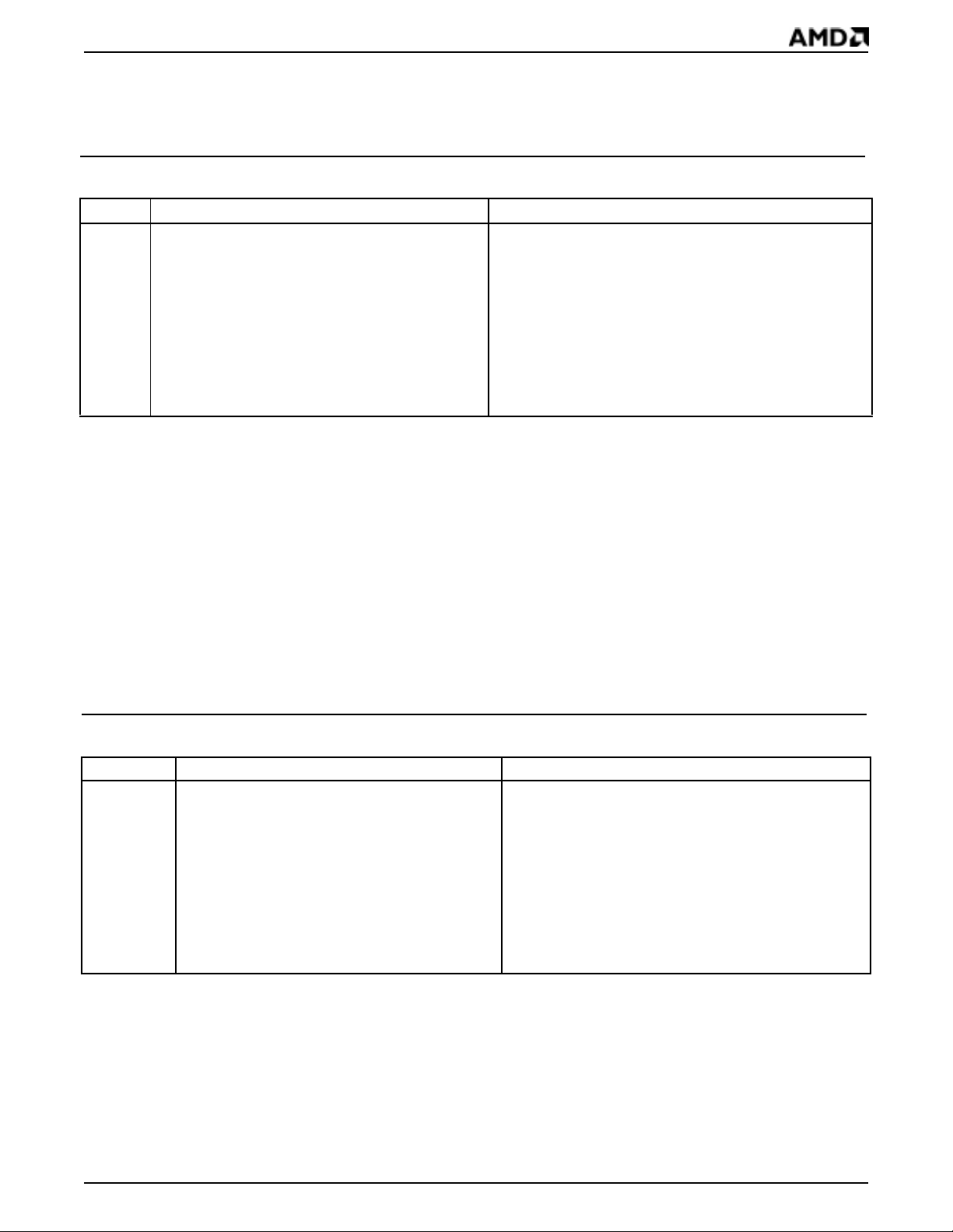

Global Register Functions

INIT Register (INIT) default = 0 0H

Address = Indirect 21 Hex, Read/Write

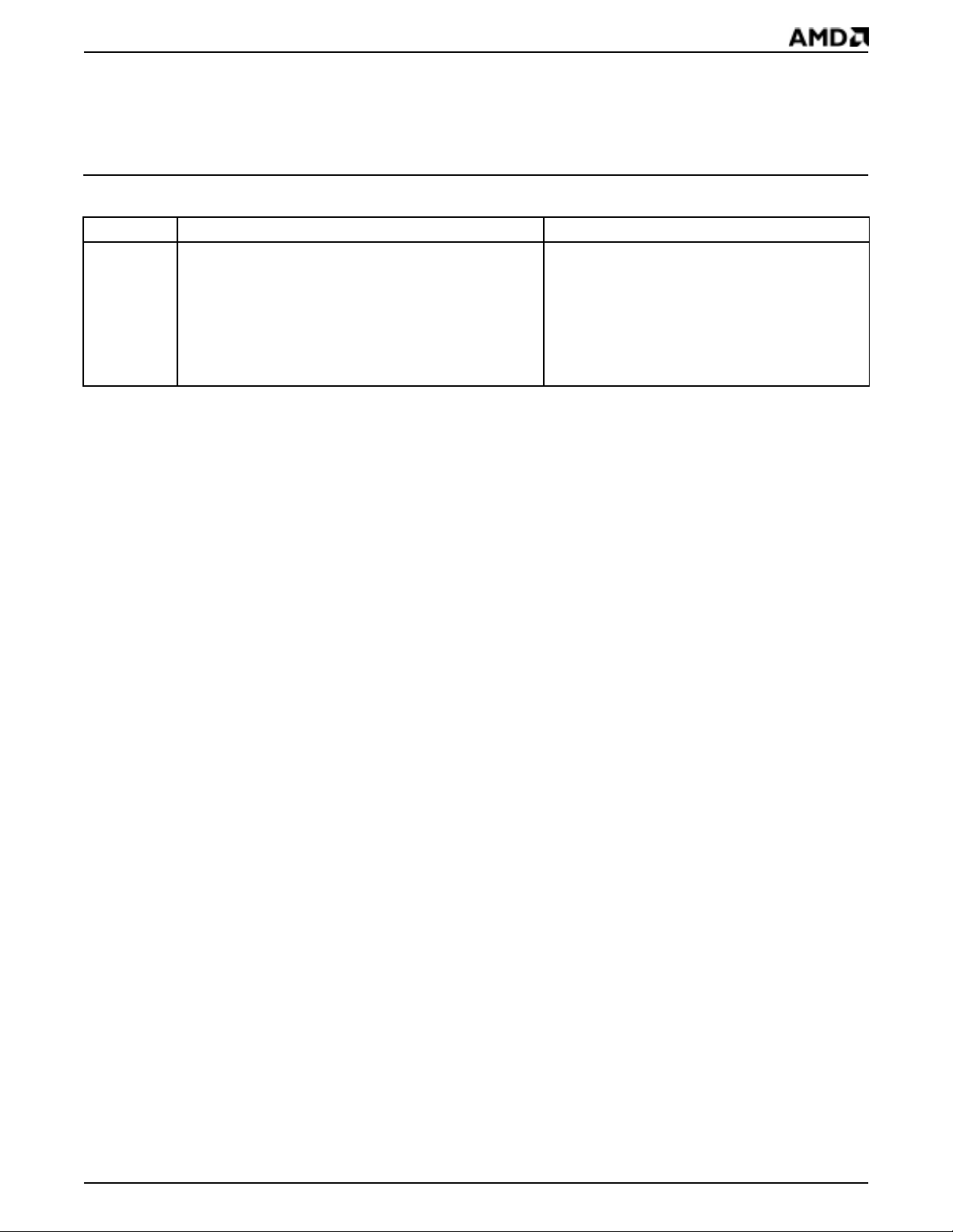

Table 1. INIT Register

Bit

Function76 5 43210

XXXXXX00Idle mode

X X X X X X 0 1 Active Voice and Data mode

X X X X X X 1 0 Active Data Only mode

X X X X X X 1 1 Power-Down m ode

XXXXX0XXINT

XXXXX1XXINT

X X 0 0 0 X X X MCLK frequency = 6.144 MHz

X X 0 0 1 X X X MCLK frequ ency = 12.288 MHz

X X 0 1 0 X X X MCLK frequency = 3,072 MHz

X X 0 1 1 X X X MCLK frequency = 6.144 MHz

X X 1 0 0 X X X MCLK frequency = 4.096 MHz

X X 1 0 1 X X X MCLK frequency = 6.144 MHz

X X 1 1 0 X X X MCLK frequency = 6.144 MHz

X X 1 1 1 X X X MCLK frequency = 6.144 MHz

X 0 X X X X X X DLC receiver abort disabled

X 1 X X X X X X DLC receiver abort enabled

0 X X X X X X X DLC transmitter abort disabled

1 X X X X X X X DLC transmitter abort enabled

output enabled

output disabled

Am79C30A/32A Data Sheet 9

Page 10

INIT2 Register (INIT2) default = 00 H

Address = Indirect 20 Hex, Read/Write

A special write procedure must be followed in order to

modify the contents of the INIT2 Register, since the

INIT2 Register includes control bits which coul d result

in the stopping of the microprocessor clock. This procedure greatly reduces the probability of errant software

disabling the system, and is described as follows:

1. Write the INIT2 address to the Command Register.

2. Write to the Data Register (INIT2 is not yet updated).

3. Write the INIT2 address to the Command Register.

4. Write to the Data Register (INIT2 is updated).

The writes must take place without any intervening indirect accesses to the DSC/IDC circui t.

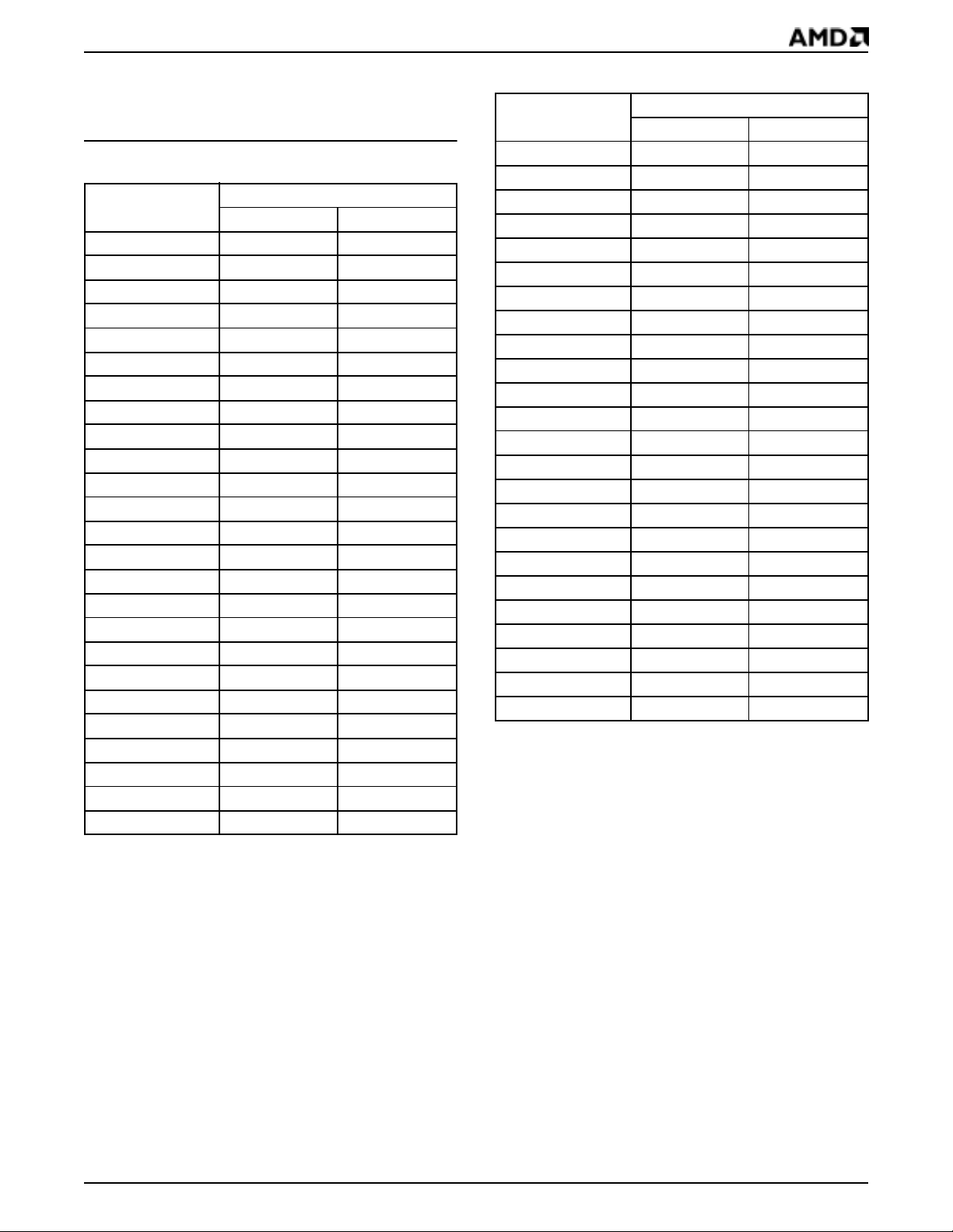

Table 2. I NIT2 Register

Bit

7 6 5 4 3 2 1 0 Function

00XXXXXXReserved, must be written to 0;

READs are undefined

0 0 0 X X X X X Power-Down disabled; writing

11 to the INIT Register will put

the DSC/IDC circuit into Idle

mode

0 0 1 X X X X X Power-Down enabled; writing

11 to the INIT Register will put

the DSC/IDC circuit into

Power-Down mode

0 0 X 0 X X X X Multiframe Interrupt filter

disabled

0 0 X 1 X X X X Multiframe Interrupt filter

enabled (see LIU sect ion for

detailed descripti on)

0 0 X X X 0 X X Clock speed- up option disab led

0 0 X X X 1 X X Clock speed- up option enab led;

if set, this register bit will be

cleared when the DLC FIFO

receive thr eshold or second

packet received interrupt is

triggered

0 0 X X X 0 0 0 MCLK frequenc y determined by

INIT Register

0 0 X X X 0 0 1 MCLK frequency is 1.536 MHz

0 0 X X X 0 1 0 MCLK frequency is 768 kHz

0 0 X X X 0 1 1 MCLK frequency is 384 kHz

0 0 X X X 1 0 0 MCLK stopped in High state

0 0 X X X 1 0 1 Reserved

0 0 X X X 1 1 0 Reserved

0 0 X X X 1 1 1 Reserved

RESET Operation

The Am79C3 0A/32A can be reset by dr iving the

RESET pin High. When power is first supplied to the

DSC/IDC circuit, a reset must be performed. This initializes the DSC /IDC circuit to its default con dition as

defined in Table 3.

Table 3. Reset Pin Conditions

Pin Name State Following RESET

D7–D0 High Impedance

MCLK 6.144 MHz

INT Logical 1

SBOUT High Impedance

SFS High Impedance

SCLK High Impedance

LS1, LS2 High Impedance

EAR1 High Impedance

EAR2 High Impedance

AREF High Impedance

LOUT1 High Impedance

LOUT2 High Impedance

Receive and Transmit Abort Commands

The microprocessor has the option via INIT Register

bits 6 and 7 to abort the receive and transmit D-channel

packets. When the micro processor sets one of these

bits, the Am79C30A /32A a bort s the respective operation. Th e frame ab ort se quence is d efined in gre ater

detail l ater. (See th e Data Lin k Contro ller sec tion on

page 36.)

Interrupt Handling

The Am79 C30A/32A generates either no inte rrupt or

only one interrupt ev ery 125 µs. Once asserted, INT

mains active unt il the microproc essor responds by interrogating the Am 79C30A/32A ’s Interrupt Register (IR)

(see Table 4). Read ing the IR in re sponse to an activated INT

pin deactivates the INT p in and clears the IR.

If an event causing an interrupt occurs while the IR is

being read by the microprocessor, the effect of the

event is held until the microprocessor has completed its

read cycle. A reset clears all conditions causing interrupts.

Bits 0, 1, and 4 of the IR, if set, advise the microprocessor that the respective buffer is ready for reading or

writing. If bit 0 is set due to an empty buffer , the D-channel T r ansmit buffer must be serviced within 375 µs. If bit

1 is set an d the D-ch annel Re ceive buffer is fu ll, the

buffer must be serviced within 425 µs. This is to prevent

erroneous data transfers causing transmitter underrun

and receiver overrun errors. If bit 4 is set then the Bb or

re-

10 Am79C30A/32A Data Sheet

Page 11

Bc buffers must be accessed within 122.4 µs. This is to

prevent erroneous data transfers. Only one interrupt is

used to signal accessibility for both B channels of the S

Interface. Since the data transfer must occur synchronously to the S Interface, any data access to either Bb

or Bc or both must be made within the122.4 µs limit.

Note that even though only a single interrupt is issued,

either or both S-Interface B channels must be serviced.

IR bits 2, 3, 5, 6, and 7, if set, indicate that a bi t has

been set in the associated status or error register. All of

the interrupts generated by the Am79C30A/32A can be

individually disabled. In the case of IR bit 7, the interrupt can also be masked by setting PPIER bit 7 to 0.

DMR1, DMR2, DMR3, LMR2, MCR4, and MF control

the mask conditions that affect the INT

pin. The INT pin

is activated only by interrupts that are not disabled. The

Interrupt Register refle cts the status of enabled interrupt s . Th e I NT

pin can be disabled by setting INIT Reg-

ister bit 2 to a logical 1.

The Am79C30A/32A has facilities that allow the micro-

processor to read the status registers (status update is

inhibited during status read) or the IR at any time during functional operation.

Am79C30A/32A Data Sheet 11

Page 12

Table 4. Format of the Interrupt Register (IR), Read Only

Bit Interrupt Generated/Action Requir ed Interrupt Mask

0 D-channel tr ansm it threshold interrupt/load D-chann el Transmit b uffer DMR1 bit 0

1 D-channel recei ve threshold int errupt/read D-channel Receive buf fer DMR1 bit 1

2 D-channel status interrupt/read DSR1

Source Cause

DSR1 bit 0 Valid Address (VA) or End of Address (EOA) DMR3 bit 0

DSR1 bit 1 When a closing flag is receiv ed or a receive error oc curs DMR1 bit 3

DSR1 bit 6 When a closing flag is transmitted DMR3 bit 1 DMR3 bit 1

3 D-channel error in terrupt/read DER and DSR2 bit 2

Source Cause

DER bit 0 Current received packe t has been aborted DMR2 bit 0

DER bit 1 Non-integer number of bytes received DMR2 bit 1

DER bit 2 Collision abort detected DMR2 bit 2

DER bit 3 FCS error DMR2 bit 3

DER bit 4 Overflo w err or DMR2 bit 4

DER bit 5 Underflow error DMR2 bit 5

DER bit 6 Overrun error DMR2 bit 6

DER bit 7 Underrun error DMR2 bit 7

DSR2 bit 2 Receive packet lost DMR3 bit 6

4 Bb or Bc byte available or buffer empty interrupt/read or write Bb or Bc buffers MCR4 bit 3

5 LIU status interrupt/read LSR

Source Cause

LSR bit 3 Change of state to F3 LMR2 bit 3

LSR bit 4 Change of state fr om /t o F7 LMR2 bit 6

LSR bit 5 Change of state fr om /t o F8 LMR2 bit 4

LSR bit 7 HSW change of state LMR2 bit 5

6 D-channel status interrupt/read DSR2

Source Cause

DSR2 bit 0 Last byte of received pac ket DMR3 bit 2

DSR2 bit 1 Receive byte av ailable DMR3 bit 3

DSR2 bit 3 Last byte transmitted DMR3 bit 4

DSR2 bit 4 T ransmit buffer available DMR3 bit 5

DSR2 bit 7 Start of second packet EFCR bit 1

7 Multiframe or PP interrupt/read MFSB and PPSR

Source Cause

MFSB bit 5 S-data av ailable MF bit 1

MFSB bit 6 Q-bit buffer empty MF bit 2

MFSB bit 7 Multiframe change of state (in/out of sync) MF bit 3

PPSR bit 0 Monitor receive, data available PPIER bit 0

PPSR bit 1 Monitor transmi t, buffer available PPIER bit 1

PPSR bit 2 Monitor EOM receive d PPIER bit 2

PPSR bit 3 Monitor abort received PPI ER bit 3

PPSR bit 4 C/I channel 0, data change PPIER bit 4

PPSR bit 5 C/I channel 1, data change PPIER bit 5

PPSR bit 6 IOM-2 timing request PPIER bit 6

12 Am79C30A/32A Data Sheet

Page 13

FUNCTIONAL DESCRIPTION

Microprocessor Interface (MPI)

The Am79C30A/32A can be connected to any general

purpose 8-bit microproces sor via the MPI. The MCLK

from the Am79C30A/32A can be used as the clock for

the microprocessor. The MPI is an interrupt-driven interface containing all the circuitry necessary for access

to th e inter nal pr ogramm able re gister s, statu s regi sters, coefficient RAM, and transmit/receive buffers .

MPI External Interface

External connections to the MPI are shown in Tab le 5.

Table 5. MPI External Interface

Name Direction Function

D7–D0 Bidirectional Data Bus

A2–A0 Inputs Address Line

RD Input Read Enable

WR Input Write Enable

CS Input Chip Select

RESET Input Initialization

INT Output Interrupt

Direct Registers

Access to the Direct Registers of the Am79C30A/32A

is controlled by the st ate of the CS

, RD, WR, A2, A1,

and A0 input pins, as defined below by Table 6.

Indirect Registers

To read from or write to any of the Indirect Registers, an

indirect address command is first written to the Command Register (CR). One or more data bytes may then

be transferred to or from the selected register through

the Data Register (DR).

Registers within certain groups can be accessed

quickly by using internal circuitry which automatically

increments the indirect value. In Table 7, the bytes

transferred numbers are the number of bytes which are

read or written to the DR after the CR has been loaded.

Whenever the CR is loaded, any previous commands

are automatically terminated.

Table 6. Direct Register Access Guide

CS RD WR A2 A1 A0 Register(s) Accessed Mode

010000Command Register (CR) W

001000Interrupt Register (IR) R

010001Data Register (DR) W

001001Data Register (DR) R

001010D-channel Status Regist er 1 (DSR1) R

001011D-channel Error Register (DER) (2-byte FIFO) R

010100D-channel Transmit buff er (DCTB) (8- or 16-byte FIFO) W

001100D-channel Receive buffer (DCRB) (8- or 32-byte FIFO) R

010101Bb-channel Transmit buff er (BBTB) W

001101Bb-channel Receive buffer (BBRB) R

010110Bc-channel Transmit buffer (BCTB) W

001110Bc-channel Receive buffer (BCRB) R

001111D-channel Status Regist er 2 (DSR2) R

1 X X X X X No access (X = logical 0 or 1) —

Note:

The RD

and WR signals must never both be Low under normal operating conditions.

Am79C30A/32A Data Sheet 13

Page 14

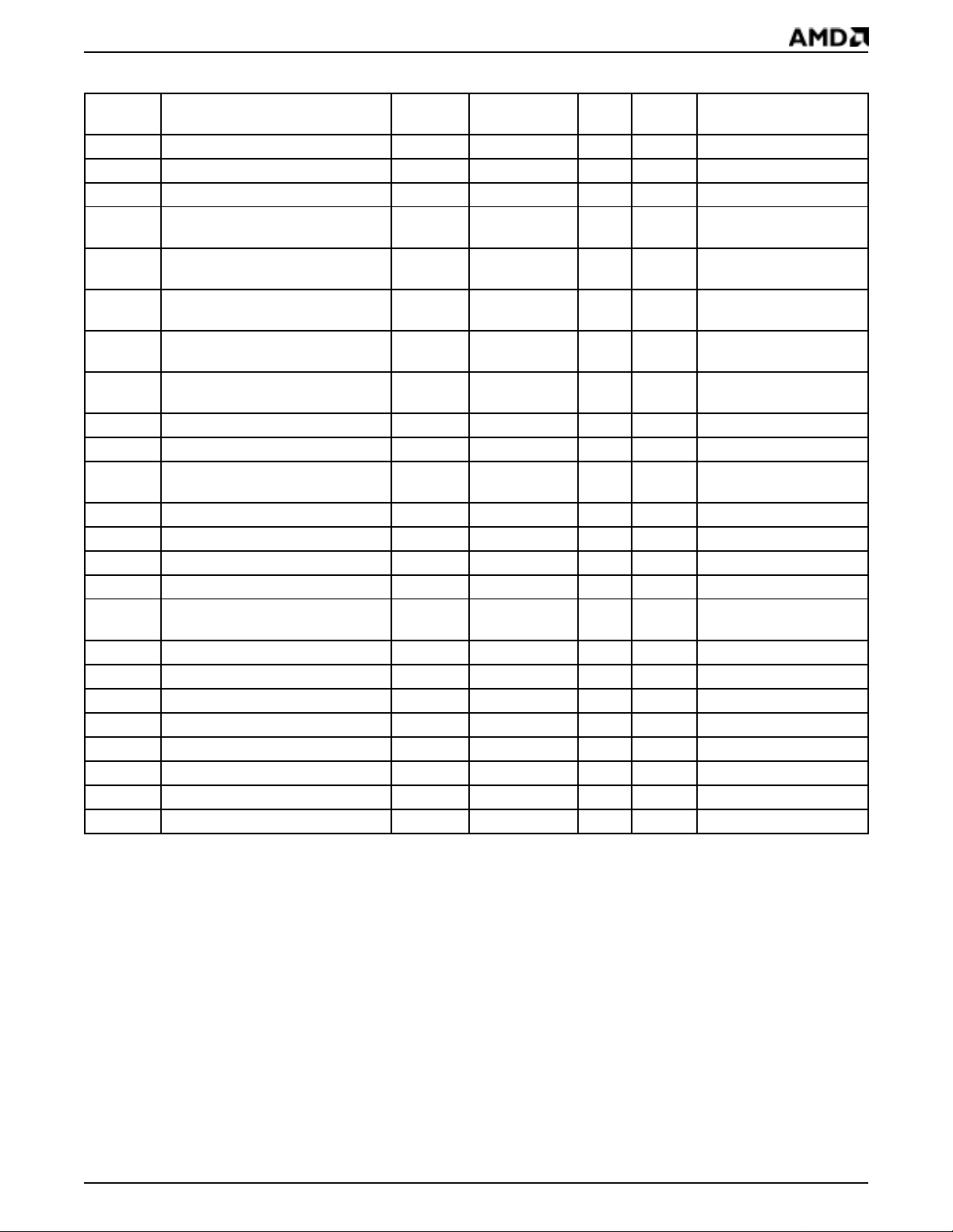

Tabl e 7. Indirect Register Access Guide

Operation

Block Register

INIT Initialization Regist er 1 INIT R/W 21H One byte trans ferred

INIT Initiali zation Register 2 2 INIT2 R/W 20H One byte transferred

LIU LIU Stat us Register 1 LSR R A1H One byte transferred

LIU LIU Priorit y Regi ster 2 LPR R/W A2H One byte tr ansferred

LIU LIU Mode Register 1 3 LMR1 R/W A3H One byte transferred

LIU LIU Mode Register 2 4 LMR2 R/W A4H One byte trans ferred

LIU — 5 Perform 2–4 – A5H

LIU Multiframe Register 6 MF R/W A6H One byte tr ansferred

LIU Multiframe S-bit/Status Register 7 MFSB R A7H One byte transferred

LIU Multiframe Q-bit buffer 8 MFQB W A8H One byte transferred

MUX MUX Control Register 1 1 MCR1 R/W 41H One byte transferr ed

MUX MUX Control Register 2 2 MCR2 R/W 42H One byte transferr ed

MUX MUX Control Register 3 3 MCR3 R/W 43H One byte transferr ed

MUX MUX Control Register 4 4 MCR4 R/W 44H One byte transferr ed

MUX — 5 Pe rform 1–4 — 45H MCR1, 2, 3, 4

MAP X filter Coefficient Register 1 X Coeff. R/W 61H h0 LSB, h0 MSB...h7 MSB

MAP R filter Coefficient Register 2 R Coeff. R/W 62H h0 LSB, h0 MSB...h7 MSB

MAP GX Gain Coefficient Register 3 GX Coeff. R/W 63H LSB, MSB

MAP GR Gain Coefficient Register 4 GR Coeff. R/W 64H LSB, MSB

MAP GER Gain Coefficient Register 5 GER Coeff. R/W 65H LSB, MSB

MAP Sidetone Gain Coefficient Register 6 STG Coeff. R/W 66H LSB, MSB

MAP Frequency T one Generator Regi ster

1, 2

MAP Amplitude Tone Generator Regist er

1, 2

MAP MAP Mode Register 1 9 MMR1 R/W 69H One byte transferred

MAP MAP Mode Register 2 10 MMR2 R/W 6AH One byte transferred

MAP — 11 Perform 1–10 — 6BH 46 bytes loaded 1–10

MAP MAP Mode Register 3 12 MMR3 R/W 6CH One byte transferred

MAP Secondary T one Ringer Amplitude 13 STRA R/W 6DH One byte transferred

MAP Secondary To ne Ringer Frequency 14 STRF R/W 6EH One byte transferred

MAP Tr ansmit Peak Regist er 15 PEAKX R 70H One byte transf erred

MAP Receive Peak Regist er 16 PEAKR R 71H One byte transferred

MAP — 17 Perform 15–16 R 72H One byte transf erred

DLC First Received Byte Address

Registers 1, 2, 3

DLC Second Received Byte Address

Registers 1, 2, 3

DLC Transmit Address Register 3 TAR R/W 83H LSB, MSB

DLC D-channel Receive Byte Limit

Register

DLC D-channel Transmit Byte Count

Register

Register

Number Indirect Name Mode Address Byte Sequence

One byte transferred

7 FTGR1, FTGR2 R/W 67H FTGR1, 2

8 ATGR1,ATGR2 R/W 68H ATGR1, 2

1 FRAR 1, 2, 3 R/W 81H FRAR1, 2

2 SRAR1, 2, 3 R/W 82H SRAR1, 2

4 DRLR R/W 84H LSB, MSB

5 DTCR R/W 85H LSB, MSB

14 Am79C30A/32A Data Sheet

Page 15

Table 7. Indirect Register Access Guide (Continued)

Operation

Block Register

DLC D-channel Mode Register 1 6 DMR1 R/W 86H One byte transferred

DLC D-channel Mode Register 2 7 DMR2 R/W 87H One byte transferred

DLC — 8 Perform 1–7 — 88H 4 bytes loaded 1–7

DLC D-channel Receive Byte Count

Register

DLC Random Number Generator

Register

DLC Random Number Generator

Register

DLC First Received Byte Address

Regi ster 4

DLC Second Received Byte Address

Regi ster 4

DLC D-channel Mode Register 3 14 DMR3 R/W 8EH One byte transferred

DLC D-channel Mode Register 4 15 DMR4 R/W 8FH One byte transferred

DLC — 16 Perform 12–15 — 90H FRAR4, SRAR4, DMR3,

DLC Address Status Register 17 ASR R 91H One byte transferred

DLC Extended FIFO Control Register 18 EFCR R/W 92H One byte transfe rred

PP Peri pheral P ort Control Register 1 1 PPCR1 R/W C0H One byte transferred

PP Peri pheral P ort Status Regi ster 2 PPSR R C1H One byte transferred

PP Peripheral Port Interrupt Enable

Register

PP Monitor Transmit Data Register 4 MTDR W C3H One byte transferred

PP Monitor Receive Data Register 5 MRDR R C3H One byte transferred

PP C/I Transmit Data Register 0 6 CITDR0 W C4H One byte tr ansferred

PP C/I Receive Data Regi st er 0 7 CIRDR0 R C4H One byte transferred

PP C/I Transmit Data Register 1 8 CITDR1 W C5H One byte tr ansferred

PP C/I Receive Data Regi st er 1 9 CIRDR1 R C5H One byte transferred

PP Peri pheral P ort Control Register 2 10 PPCR2 R/W C8H One byte transferr ed

PP Peri pheral P ort Control Register 3 11 PPCR3 R/W C9H One byte transferr ed

Register

Number Indirect Name Mode Address Byte Sequence

9 DRCR R 89H LSB, MSB

10 RNGR1 (LSB) R/W 8AH One byte transferred

11 RNGR2 (MSB) R/W 8BH One byte tr ansferred

12 FRAR4 R/W 8CH One byte transferred

13 SRAR4 R/W 8DH One byte transfe rr ed

DMR4

3 PPIER R/W C2H One byte transferr ed

Line Interface Unit (LIU)

The LIU connects to the four-wire S Interface through a

pair of isolation transformers, one for the transmit and

one for the receive direction, as shown in Figure 1.

The receiver section of the LIU consists of a differential

receiver, circuitry f or bit timing recov ery, circuitry for detecting High and Low marks, and a frame recovery circuit for frame sy nchronizat ion. The re ceiver converts

the received pseudo-ternary coded signals to binary

before delivering them to the other blocks of the

Am79C30A/32A. It also performs collision detection (Eand D-bit comparison) per the CCITT recommenda-

Am79C30A/32A Data Sheet 15

tions so several TEs can be connected to the same S

Inter face .

The transmitter consists of a binar y to pseudo-t ernar y

encoder and a differential line dr iver which meets the

CCITT recommendations for the S Interface.

The Am79C30A/32A can establish multiframe synchronization, receive S bits, and transmit Q bits synchronized to the received frame.

External Interface

The LIU can be connecte d to both point-to- point and

point-to-multipoint configurations at the CCITT S reference point. The point-to-point configuration consists of

one TE connected to the NT or PABX linecard. The

Page 16

point-to-multipoint configuration can have multiple TEs

connected to one NT.

Line Code

Pseudo-ternary coding is used for both transmitting

and receiving over the S Interface. In this type of coding, a binary 1 is represented by a space (zero voltage),

and a binary 0 is represented by a High mark or a Low

mark. T wo consecutive binary 0s are represented by alternate marks to reduce DC of fset on the line. A mark

followed, either im mediately or separated by spaces,

by a mark of the same polarity , is defined as a code violation. Code violations are used to identify the boundaries of the frame.

Note:

The DSC defines “Any Signal” as any frame with at least

three marks above receive threshold.

Frame Structures

In both transmit and receive directions, the bits are

grouped into frames of 48 bits each. The frame structure is identical for both point-to-point and point-to-multipoint configurations. Each frame transmitted at 4 kHz

consists of several groups of bits.

Multifram i ng

If multiframing is enabled, the A m79C30A/32A recognizes and establishes multiframe synchronization

based on the monitoring of the F

(Q-bit control) and M

A

(M-bit control) bits. The Am79C30A/32A also receives

and compiles S bits, and transmits Q bits synchronized

to the received frame.

Establishment of Multi fr am e Sy nc hroni z at io n

When the enable multiframe synchroni zation bit (bit 0

of the Multiframe Register) is set and the LIU is in either

state F6 or F7, the LIU monitors the F

(Q-bit control)

A

and M (M-bit control) bits. When three consecutive multiframes with the M bits and F

bits set as defined in

A

Table 8 are recei ved, the multiframe synchron ized bit

(bit 7 of the Multiframe Register) and multiframe

change of state bit (bit 7 of t he Mul tiframe S bi t/Status

buffer) are set. Note that S-bit data is received, compiled, an d transferre d to the use r after att aining s ynchronization at the start of the next multiframe.

S-Bit Reception

The default operation of the DSC/IDC circuit is that the

LIU will receive and pass multiframe data to the user in

5-bit increments four times per multiframe, regardless

of the value of the data. After multiframe synchronization has been requested and established the microprocessor can read the Multiframe S bit/Status buffer

(MFSB) once the S-bit available bit (MFSB bit 5) is set.

The S-data available bit is set to a logical 1 when the

Am79C30A/32A has received five S bits (one S bit per

S-interface frame) synchronized to the setting of the

F

-bit to a logical 1 and transferred them into the

A

MFSB. Once the S-bit available bit is set, the MFSB

must be accessed within 1.25 ms or succeeding S data

will be lost.

Subsequent to the original definition of the DSC/IDC

circuit, the CCITT has defined a structure for the 20

multiframe bits, which specifies five 4-bit channels. Furthermore, the idle code for these channels has been

defined as 0000. An enh anc ed m ode o f mult iframe reception has been included, which may be enabled by

setting INIT2 bit 4 to a 1. This enhanced mode reduces

processor overhead by generating an interrupt only

upon the reception of a non-zero S-channel word.

INIT2 bit 4 wil l be automatic ally cleared by ha rdware

when the five received data bits in the MFSB are not all

0s, as long as MF bit 1 (interrupt enable) is set. This allows subsequent valid all-zero words to be received.

Furthermore, when the first five S bits of the multiframe

are loaded into the MFSB, bit 4 o f the MF regist er will

be set, which allows identification of th e position of received words wit h in t h e mu lt iframe.

Binary

to

Pseudo-ternar y

To

MUX

Frame

Recovery

Coder

and

DLC

Decoder Slicer

Timing

Recovery

Figure 1. LIU Block Diagram

16 Am79C30A/32A Data Sheet

Line Drivers

S

Balanced

Receiver

09893H-2

Page 17

Table 8. Multiframin g Structu res

Frame Number NT-to-TE Q Control Bit FA NT-to-TE M Bit (M) NT-to-TE S Bit (S) TE-to-NT FA Bit (Q Bit)

1 1 1 SC11 Q1

2 0 0 SC21 0

3 0 0 SC31 0

4 0 0 SC41 0

5 0 0 SC51 0

6 1 0 SC12 Q2

7 0 0 SC22 0

8 0 0 SC32 0

9 0 0 SC42 0

10 0 0 SC52 0

11 1 0 SC13 Q3

12 0 0 SC23 0

13 0 0 SC33 0

14 0 0 SC43 0

15 0 0 SC53 0

16 1 0 SC14 Q4

17 0 0 SC24 0

18 0 0 SC34 0

19 0 0 SC44 0

20 0 0 SC54 0

1 1 1 SC11 Q1

2 0 0 SC21 0

etc.

Transmission of Q bits

The microprocessor can load the Multiframe Q-bit

buffer (MFQB) once the Q-bit buffer empty bit (bit 6 of

the Multiframe S bit/Status buffer) is set. The Q-bit

buffer empty bit is set to a logical 1 at reset or when

data that has been written to the Multiframe Q-bit buffer

is transferred to the L IU. The Q-bit buffer empty bit is

cleared to a logical 0 when the Mul tiframe S-bi t/Status

buffer is read. After multiframing has be en requested

and established, the Am79C30A/32A transfers the data

written into the Q-bit Register to the LIU, synchronized

to the multiframe, irrespective of the receipt of valid

Q-control bits. If the microprocess or does not reload

the Q-bit Register for retransmissions , the Q-bit pattern

is repeated in the next multiframe.

If multiframing is enabled but multiframe synchronization is not established, the LIU transmits the value

loaded in MFQB bit 4 in all Q bits. The default value of

MFQB bit 4 is a logical 0 which satisfies the CCITT recommendations. When synchronization is achieved, the

contents of MFQB bits 3 to 0 are transmitted according

to Table 8.

Loss of Multi fr a m e Synchronizatio n

The Am79C30A/32A continuously monitors the FA

(Q-bit control) and the M bits to ensure multiframe synchronization. Onc e multiframe synchronization is established, multiframe synchronization is lost if three

consecutive invalid multiframes are received, or the LIU

is no longer in state F6 or F7, or multiframing is disabled. When loss of multiframe synchronization occurs,

bit 7 of the Multiframe Register is set to a logical 0, and

bit 7 of th e Multifra me S bit/S tatus buffer is set to a

logical 1. The A m79C30A/ 32A also t erm inates the reception of S bits and transmission of Q bits until multiframing synchronization is re-established.

HSW

The hookswitch c ircuitry on the DSC circui t provides the

attached mic roprocessor with a way of converting an

external mechanical hookswitch into a software status

condition capabl e of generating an interrupt . De bounce

and glitch rejection are pr ov ided internal to the D SC circuit. The logic rej ects glitches less than 16 2 ns and provides deboun ce of 16 m s. HSW status repor ting is

disabled afte r RESET. It is enabled by any of the fo llo wing: taking the devic e out of Idl e mode , a write to a MUX

Control Register (MCR3–MCR1), or unmasking the

HSW interrupt.

Am79C30A/32A Data Sheet 17

Page 18

LIU Registers

The LIU contains the registers shown in Tab l e 9.

as 1, F4 as 2, and so on, where bit 0 is the LSB. The

LIU interrupts the microprocessor via bit 4 of the LSR

when activation has been achieved (that is, when the

LIU moves to state F7 upon receipt of INFO 4). During

T able 9. LIU Registers

Registers No./Registers Mnemonic

LIU Status Register 1 LSR

LIU Priority Register 1 LPR

LIU Mode Registers 2 LMR1, LMR2

Multiframe Register 1 MF

Multiframe S-bit/Status

Register

Multiframe Q-bit buffer 1 MFQB

1 MFSB

reset the LSR is 0.

Even though the LIU Status Register (LSR) is

read-only, no default value upon power-up is given due

to the uncer tain s tate of bit 6 (Hookswitch State). Following RESET, the LIU State is F2 and the HSW bit reflects the HSW pin, producing a power-up value of

either 00H or 40H.

LIU D-Channel Priority Register (LPR), Read/Write

The LPR cont ains the prio rity level for D-channel access. Its default value after reset is 0.

LIU Status Register (LSR), Read Only

Address = Indirect A1H

The LSR format is shown in Table 10.

Table 10. LIU Status Register

Generates

Bit Logical 1

0-2 Binary values 000 through 110

represent the LIU activation

circuitry’s current state (F2

through F8, respe ctively) bi t 2 is

MSB

3 Change of st ate to F3 If LMR2 bit 3 = 1

4 Change of st ate from/to F7 If LMR2 bit 6 = 1

5 Change of st ate from/to F8 If LMR2 bit 4 = 1

6 HSW state No

7 HSW change of state If LMR2 bit 5 = 1

Interrupt

No

When the microprocessor reads the LSR, bits 3, 4, 5,

and 7 are cleared. The other bits retain the current status of the LIU. bi ts 0 to 2 are defined such that state F2

(see CCITT I.430 state matrix tables) is coded as 0, F3

The D-channel access procedure of the Am79C30A/

32A uses the priority level programmed in the LPR. The

priority mechanism defined by the CC ITT I-series recommendations i s fully implem ented if the LPR is programmed via the m icroprocessor to con form to the

priority class of the Layer-2 frame to be transmitted.The

LPR has 16 possible programmable priority levels. The

priority levels are numbered 0–15. Priority Level 0 corresponds to counting eight 1s in the echo channel, priority Level 1 corresponds to counting ten 1s in the echo

channel, priority Level 2 corresponds to counting

twelve 1s, etc. The DSC circuit automatically handles

transitions between the programmed priority level n

and the associated odd value n + 1. Th e priority is

incremented following a succ essfully transmitted

packet, and decrem ented when the highe r count has

been satisfied.

The LPR format is shown in Table 11.

Table 11. LIU Priority Register

Bits Description

3, 2, 1, 0 D-channel access priority level bit 0 is LSB

7, 6, 5, 4 Reserved, reads logical 0

18 Am79C30A/32A Data Sheet

Page 19

LIU Mode Re gi st er ( LM R 1 ), Read/Write

Address = Indirect A3H

LMR1 is defined in Table 12.

Table 12. LIU Mode Register 1

Bit Logical 1 Logical 0 (default value)

0 Enable B1 tr ansmit Disable B1 transmit

1 Enable B2 tr ansmit Disable B2 transmit

2 Disable F tra nsm it Enable F transmit

3 Disable F

4 Activation request No activation request

5 Go from F8 to F3 No transition

6 Enable receiver/transmitter Disable receiver/transmitter

7 Reserved; must be set to logical 0 Reserved; must be set to logical 0

Notes:

The F a nd F

bits in LMR1 (bits 2 and 3) shou ld be enab led duri ng the acti va tion pr ocedu re so the Am79C30 A/32 A can respond

A

with INFO 3.

LMR1 bit 4 is used to tran sf er t he signal s PH-AR and Exp iry of Timer from t he micropr ocessor to the LIU (s ee CCITT I.4 30 state

diagram—activati on request). PH-AR i s defined as bit 4 being a logical 1 and Expiry of Timer is defined as the transition of bit 4

from a logical 1 to a logi cal 0. This bit must not be set until the LIU, as ref lected in the LSR, is in stat e F3, F6, or F7 and the

receiver has been enabled for a minimum of 250 µs.

LMR1 bit 6 is primarily used to disab le the r eceiv er when the terminal does not requi re access t o the S Inter f ace si gnals . This bi t

is cleared by reset and must be written to lo gical 1 in order to receive activati on from the S Interf ace, or to request acti vation.

transmit Enable FA transmi t

A

LIU Mode Register 2 (LMR2), Read/Write

Address = Indirect A4H

LMR2 is used to select the operations found in Table 13.

Table 13. LIU Mode Register 2

Bit Logical 1 Logical 0 (Default Value)

0 D-channel loopback at Am79C30A/32A enable D-channel loopback at Am79C30A/32A disable

1 D-channel loopback at LIU enable D-channel loopback at LIU disable

2 D-channel back-off disable D-channel back- off enable

3 F3 change of state i nterrupt enable F3 change of state interrupt disable

4 F8 change of state i nterrupt enable F8 change of state interrupt disable

5 HSW interrupt enable HSW interrupt disable

6 F7 change of state i nterrupt enable F7 change of state interrupt disable

7 Reserved; must be set to logical 0 Reserved; must be set to logical 0

Am79C30A/32A Data Sheet 19

Page 20

The three D-channel loopback controls defined in

Am79C30A NT/PABX

D

D

MPI

S

Am79C30A NT/PABX

DD

E

E

S

LMR2 bits 0, 1, and 2 are explained below:

Bit 0, D-channel loopback at Am79C30A/32A enable:

Bit 1, D-channel loopback at LIU enable:

Am79C30A NT/PABX

DD

S

DD

E

This remote loopback is provided for maintenance purposes from the NT’s perspective. The NT transmits

D-channel bits to the A m79C30A/32A wh ere they are

internally looped (with the Data Link Controller) and

transmitted back to the NT. The incoming D-channe l

data can be accessed by the microprocessor; however ,

the microprocessor cannot send data on the outgoin g

D channel.

Any difference between the transmitted D-channel bits

and the received E-channel bits to/from the

Am79C30A/32A (normal ly detected as an error which

halts the transmission) is ignored, thereby allowing the

transmission to continue.

This local loopback is provided fo r local testing. Data on

the incoming D channel is ignored. The data from the

microproc essor is pr ocessed by th e DLC a nd then

looped back to the microprocessor.

Bit 2, D-channel back-off disable:

This loopback is provided for maintenance purposes

from the TE’s perspective. The Am79C30A/32A transmits D-chan nel bits to the NT whe re they are loope d

and transmi tted back to the Am79 C30A/32A i n the E

channel. The operation is normal except dif ferences

between the D an d E channels do no t halt the transmission.

Multiframe Register (MF), Read/Write

Address = Indirect A6H

Bit Logical 1 Logical 0 (Default Value)

0 Enable M u lti fra m e syn c Disable Mu ltiframe sy n c

1 Enable S-data available interrupt Disable interrupt

2 Enable Q-bit buffer empty interrupt Disable interrupt

3 Enable Multiframe change of state interrupt Disable int errupt

4 First subframe Not first subfra me

5, 6 Not used, reads logical 0 Not used, reads logical 0

7 Multiframe synchronized (read only) Multiframe not synchronized (read only)

Table 14. Multifram e Register

20 Am79C30A/32A Data Sheet

Page 21

Multiframe S-bit/Status Buffer (MFSB), Read Only

Address = Indirect A7H

Table 15. Multiframe S-Bit/Status Buffer

Bit Description Generates Interrupt

0S1 No

1 S2 No

2 S3 No

3 S4 No

4 S5 No

5 S-data available If MF bit 1 = 1

6 Q-bit buffer empty If MF bit 2 = 1

7 Multiframe change of state If MF bit 3 = 1

The logical channels available at the MUX are shown in

Figure 2, They are:

1. From/to the LIU channels B1 and B2

2. From/to the MAP channel Ba

3. From/to the MPI channels Bb and Bc

4. From/to the PP channels Bd, Be, and Bf

For any specific application, the MUX can be pro-

grammed by the microprocessor to route any three

B-channel ports to any other three B-channel

ports.Programmable bidirectional bit reversal is provided for both of the MPI data channels Bb and Bc.

MUX Control Registers 1, 2, and 3

(MCR1, MCR2, and MCR3), Read/Write

Addresses = Indirect 41H, 42H, 43H

The MFSB reset default value is 40H.

Multi frame Q - bit Buffer (M F QB), W r ite Only

Address = Indirect A8H

Table 16. Multiframe Q-Bit Buffer

Bit Description

0 Q1 (default = 1)

1 Q2 (default = 1)

2 Q3 (default = 1)

3 Q4 (default = 1)

4

5, 6, 7 Not used

Q-bit val ue when m ultiframing enabled but

synchronization not achieved (default = 0)

Multiplexer (MUX)

The MUX contains the registers found in Table 17.

Table 17. MUX Registers

Register No./Registers Mnemonic

MUX Control

Registers

4

The Multiplexer is used to selectively route 64-Kbit/s

full-duplex B channels between the LIU (Line Interface

Unit), MAP (Main Audio Processor), MPI (Microprocessor Interface), and the PP (Per iphe ral Port).

MCR1, MCR2, MCR3,

MCR4

The MUX can support three bidirectional paths. The

contents of the MUX Control Registers MCR1, MCR2,

and MCR3 direct the flow of data between the eight

MUX logical B channels (see Figure 2). These three

MCRs are programmed to connect any two B-channel

ports together by writing the appropriate channel code

into an MCR. The se MCR s have the same forma t,

where bits 7–4 indicat e port 1 and bits 3–0 i ndicate port

2. In ea ch of th ese three MCR register s, the chann el

codes f ound in Table 18 ar e used f or bo th po rts 1 and 2.

Table 18. MCR Register Channel Codes

Code Channel

0000 No connection (default value)

0001 B1 (LIU)

0010 B2 (LIU)

0011 Ba (MAP)

0100 Bb (MPI)

0101 Bc (MPI)

0110 Bd (PP channel 1)

0111 Be (PP channel 2)

1000 Bf (PP channel 3)

For example, to connect B1(LIU) with Bb (MPI) and B2 (LIU)

with Ba (MAP), the contents of the MCRs would be:

Port 1 Port 2

Register 7 6 5 4 3 2 1 0 Channel Connection

MCR1 0 0 0 1 0 1 0 0 B1 (LIU) Bb (MPI)

MCR2 0 0 1 0 0 0 1 1 B2 (LIU) Ba (MAP)

MCR3 0 0 0 0 0 0 0 0 No connect No connect

Am79C30A/32A Data Sheet 21

Page 22

Peripheral P ort

Bd Be Bf

Bb

MPI

B-channel

Bc

Ba MAP

Figure 2. MUX Logical Channels

Therefore, in this example, MCR1 provides a data link

from the S Interface and MCR2 sets up a voice connection across the S Interface.

To loopback a channel, the same channel code is used

for port 1 and port 2. For example, to loopback B1, B2,

and Ba, the MCRs would be:

Port 1 Port 2

Register 7 6 5 4 3 2 1 0 Channel Connection

MCR1 0 0 0 1 0 0 0 1 B1 (LIU) Loopback

MCR2 0 0 1 0 0 0 1 0 B2 (LIU) Loopback

MCR3 0 0 1 1 0 0 1 1 Ba (MAP) Loopback

MCR3 has higher priority than MCR2. MCR2 has

higher priority than MCR1.

If multiple connections are made t o the s am e port, the

data from t he connecti ng port s in the highest priority

B1

LIU

MUX

B2

09893H-3

MCR will overwrite the data from the connecting port in

the lower priority MCR, for example:

Port 1 Port 2

Register 7 6 5 4 3 2 1 0 Channel Connection

MCR1 0 0 0 0 0 0 0 0 No connect

MCR2 00010100B1 (LIU) Bb (MPI)

MCR3 0 1 0 0 0 0 1 1 Bb (MPI) Ba (MAP)

The final data transfers are:

B1 (LIU) receives Bb (MPI),

Ba (MAP) receives Bb (MPI),

Bb (MPI) receives Ba (MAP).

Therefore, the data transfer from B1 (LIU) to Bb (MPI)

is lost in the arrangement proposed in MCR2.

22 Am79C30A/32A Data Sheet

Page 23

MUX Control Register 4 (MCR4), Read/Write

Address = Indirect 44H

The MUX Control Register 4 (MCR4) can prevent interrupt generation by masking the output of IR bit 4. MCR4 has

the format shown in Table 19.

Table 19. MUX Control Register 4

Bit Logical 1 Logical 0 (Default Value)

0–2 Reserved, must be set to logical 0 Reserved, must be set to l ogical 0

3 Enab le Bb- or Bc-channe l byte a vaila ble interru pt (IR Bit 4) Disable interrupt

4 Reverse bit order of Bb (LSB transmitted/received first) No Bb bit rever sal (MSB transmitted/received first)

5 Reverse bit or der of Bc (LSB transmitted/received fi rst) No Bc bit reversal (MSB tr ansmitted/received first )

6 Reserved, must be set to logical 0 Reserved, must be set to logical 0

7 Reserved, must be set to logical 0 Reserved, must be set to logical 0

Am79C30A/32A Data Sheet 23

Page 24

Main A ud io Processor (MAP)

(Am79C30A only)

Overview

The MAP, as illustrated in Figur e 3, implements audio-band analog-to-digital (ADC) and digital-to-analog

(DAC) conversions together with a wide variety of audio

support functions. Analog interfaces are provided for a

handset ea rpiece, a handse t mouthpiece, a microphone, and a loudspeaker. A programmable analog

pream plifier is inc luded in f ront of the A /D conver ter.

The codec and filter function s are implemen ted using

digital signal processi ng (DSP) techniques to provide

operational stability and programmable features. There

is one programmable digital gain stage i n the transmit

path and two in the receive path to allow precise signal

level control. Sidetone attenuation is programmable,

and programmable equalization filters are present in

both the receive and transmit paths in order to m odify

the frequen cy response of either or both paths. Tone

generation capability is inc lude d to allow generat ion of

ringing signals, DTMF tones, and call progress signals.

MAP operation is described in detail in the following

sections.

Audio Inputs

The audio input port consists of two inputs (AINA a nd

AINB) which are selectable, one at a time, by register

programming. Signals applied to these inputs must be

AC-coupled.

Earpiece and Loudspeake r Drivers

The earpiece and loudspeaker drivers each con sist of

amplifiers with differential, low-impedance outputs. The

MAP receive path signal may be routed to either of

these outputs, or to both outputs simultaneously . Alternatively, the MAP receive path may be routed to the

EAR outputs while the S econdary Tone Ringe r (STR)

is routed to the LS outputs. The EA R drivers can drive

loads Š130 ohms between the EAR1 and E AR2 pins,

while the LS drivers can drive loads Š40 ohms between

the LS1 and L S2 pins. The m aximum capa citive-loading between EAR1 and EAR2 or between LS1 and LS2

is 100 pF. The EAR outputs are high-impedanc e wh en

the MAP is disa bled. The LS outputs are high impedance when both the MAP and the Seco ndary Tone

Ringer are disabled.

CAP1

CAP2

PEAKX

AINA

AINB

AREF

EAR1

GA*

Analog

Sidetone

Gain*

ADC Decimators, BPF

Digital

Loopback 1

DTMF

(A)

GEN.

Digital

X* GX* COMP*

Sidetone

Gain*

Loopback 2

EAR2

DAC

Interpolators, LPF

R* GER* GR* EXP*

+

LS1

LS2

Notes:

Minimum Default Maximum Step

GX 0 dB** 0 dB 12 dB 0.5 dB

GER –10 dB** 0 dB 18 dB 0.5 dB

GR –12 dB** 0 dB 0 dB 0.5 dB

STG –18 dB** –18 dB 0 dB 0.5 dB

GA 0 dB 0 dB 24 dB 6.0 dB

ASTG –27 dB** 8 –6 dB 1.5 dB

*Program m able

**These registers can also be progr am med for infinite attenuation t o break the signal path if desired.

STR*

Tone*

Ringer

Tone*

Gen.

(B)(C)

Figure 3. Mai n Audio Processor Block Diagram

Ba channel

to

MUX

Transmitter

Receiver

Ba channel

from

MUX

PEAKR

09893H-4

24 Am79C30A/32A Data Sheet

Page 25

Programmabl e A na l og Preamplifie r

A programmable analog preamplifier GA is inc luded in

front of the A/D convert er and is adjustable in 6-dB increments from 0 dB to +24 dB. The existing GX gain

stage in the transmit path may be used for finer adjustment of transmit gain. This pream plifier eliminates the

need for an exter nal operation al amplifier when interfacing electret-type handsets to the DSC circuit.

Analog Sidetone

Analog sidetone takes the analog input to the transmitter ADC and sums it into the single-ended input of the

EAR output buffer. The summing point is a fter the out put selection switch. The analog sidetone path has programmable attenuation between –6 and –27 dB, plus

infinity (off). Default is infinity. Programm ing is via four

bits in the Extended FIFO Control Register, EFCR.6–3.

The programming values are given in Table 20.

Table 20. Analog Sidetone

0000 =∞ 0100 = –22.5 dB

0001 = –27.0 dB 0101 = –21.0 dB

0010 = –25.5 dB 0110 = –19.5 dB

0011 = –24.0 dB 0111 = –18.0 dB

1000 = –16.5 dB 1100 = –10.5 dB

1001 = –15.0 dB 1101 = –9.0 dB

1010 = –13.5 dB 1110 = –7.5 dB

1011 = –12.0 dB 1111 = –6.0 dB

Signal Processing

Transmitter

The transmitter performs a series of operations as described below.

1. An ADC converts the incoming analog signal at a

sampling rate of 512 kHz.

2. The Band Pass filter and a series of decimators reject DC and 50- to 60-Hz line frequencies while reducing the sampling rate to 8 kHz.

3. The X filter is an 8-tap user-programmable filter for

tuning the microphone. The default is flat with unity

gain.

4. The GX filter is a programmable gain filter that allows the user to program a gain of 0 to +12 dB in

0.5-dB steps. The default value is 0 dB.

5. The µ-law or A-law digital compression algorithm

conver ts the linear output of the GX filter to µ- or

A-law code. The default algorithm is µ-law code.

The MSB (sign bit) is transferred first to (or from) the

MUX.

Receiver

The receiver perf orms a series of operations described

as follows:

1. An expander converts the input A- or µ-law data to

digital linear data. The most significant bit is transferred from the MUX first. The def ault value is µ-law .

2. The GR filter is a programmable gain filter that allows the user to program a gain of –12 to 0 dB in

0.5-dB steps. The default value of GR is 0 dB.

3. The GER and Sidetone Gain (STG) are programmable constant multipliers whi ch allow the user to

program a gain of –10 t o +18 dB i n 0.5-d B steps

(default value 0 dB) and –18 to 0 dB in 0.5-dB steps

(default value –18 dB) respectively. The GER provides volume control (for the hearing impaired) and

should b e programmed to 0 dB for nor mal operation. The sidetone gain path provides feedback from

the trans mi tte r.

4. The R filter is provided to correct fo r spea ker attenuation distor tion and is a user-programmable filter

similar to the X filter in the transmitter.

5. A series of interpolators increases the sampling

frequency.

6. A DAC converts the digital signal to the analog

audio output signal.

PEAK Hold Registers

Logic in the form of two microprocessor accessible

peak hold registers will be provided to allow for support

of a software based speaker phone solution. These

registers, one in the transmit path (PEAKX) and one in

the receive path (PEAKR), will provide the compressed

maximum (peak) absolute value of the data in the path

since the register was last read. With appropriate s oftware, this can be used to implement a hands-free function. Refer to the MAP block diagr am for the location of

these registers in the processing path.

The following assumptions are made:

1. The GX and GR blocks are used as gai n/attenuators, without modification to their range or resolution.

2. The data is presented in compressed A-law format,

without the alternate bit inversion. The sign bit is not

presented.

3. The data extraction point for the transmit path is

after the X filter.

4. The data extraction point for the receive path is immediately following the expander.

5. The compressed data from the transmit and receive

paths is presented using the same compression

algorithm.

Am79C30A/32A Data Sheet 25

Page 26

6. The peak registers are double-buffered and can be

read asynchronously to the operation of the DSP

register. They are cleared on read.

7. The peak registers default to “don't care” values

when the part is reset. An initial read operation is required to clear the register before using it for the first

time.

The PEAKX register is at indirect address 70H, while

the PEAKR register is at indirect address 71H. Both

may be accessed v ia back-to-back read data regist er

operations by loading the command register with 72H.

T o ne Generators

The MAP contains three tone generators which can be

enabled via MAP Mode Register 2, bits 2, 3, and 4.

Only one of the three tone generator bits i n t he regi ster

can be set at a time. If more than one bit is set, all three

bits are considered set to zero and tone generation is

disabled. The tone generators are:

DTMF Generato r

This generator provides tone injection at a sampling

rate of 32 kHz into the transmit and sidetone paths (Figure 3, Block A). The DT MF f requenc i es generated are

guaranteed to ±1.2% deviation.

The DTMF generator may be used to gen erate single

frequency outputs. To obtain a single frequency out of

the DTMF generator, load a zero code into one of the

two frequency registers.

Tone Generation

This generator provides call progress tones to the receive path, where it is added to the incoming spee ch

(Figure 3, Block B).

Tone Ringer

This generator provides tone alert signals output

through the receive path to the loudspeaker or earpiece (Figure 3, Block C).

To program the DTMF tone generators, two frequency

values and two amplitude values must be written to the

two 8-bit Frequency Tone Generator Registers

(FTGR1, FTGR2) and the two 8-bit Amplitude Tone

Generator Registers (ATGR1, ATGR2), respectively.

The Tone Ge nerator and the Tone Ringer use the frequency pro grammed in FTGR1. Th e Tone Ge nerator

uses th e amplitude programm ed in ATGR1 while the

Tone Ringer uses th e amplitude progr ammed in ATGR2.

Common freq uency valu es are l isted in Table 22.

The FTGR codes to obtain DTMF dialing output frequencies are listed in Table 21.

Table 21. DTMF Codes

FTGR 2 or 1

HEX REG VALUE

FTGR 1 or 2 FREQ 1209 1336 1477 1633

5AH 697 1 2 3 A

63H 770 4 5 6 B

6EH 852 7 8 9 C

79H 941 * 0 # D

9BH ABH BFH D3H

26 Am79C30A/32A Data Sheet

Page 27

The output frequency of the DTMF tone generator approximately equals:

64000

DTMF Frequency in Hz

where

i

is the decimal equivalent of value programmed

----------------------------------------------------=

integer 8192

⁄()

1+

i

into the FTGR reg ister. This allows the DTM F generator to supply common dua l tone call progress signals

such as Busy or Dial tones.

Table 22. Tone Ringer and Tone Generator

Frequency Coefficients

Frequency (Hz) Hex Code

2666 AB

2000 81

1600 67

1333 56

1142 4A

1000 41

889 39

800 34

727 2F

667 2B

615 28

571 25

533 23

500 21

471 1F

444 1D

421 1B

400 1A

381 19

364 18

348 17

333 16

320 15

The ATGR registers allow the user to program a gain of

–18 dB to 0 dB in 2-dB steps. Example ATGR codes to