Page 1

PS3210B-1299

The Data Coding Leader

Advanced Hardware

Architectures

TM

Advanced Hardware

Architectures, Inc.

2365 NE Hopkins Court

Pullman, WA 99163-5601

509.334.1000

Fax: 509.334.9000

e-mail: sales@aha.com

http://www.aha.com

Product Specification

AHA3210B

10 MBytes/sec DCLZ

Data Compression Coprocessor IC

Page 2

Advanced Hardware Architectures, Inc.

PS3210B-1299 i

Table of Contents

1.0 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1.2 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1.3 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

2.0 Modes of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2.1 Port A and B Port Data Bus Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2.1.1 Dual Data Bus Mode: In-Line Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2.1.2 Single Data Bus Mode: Look-Aside Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2.1.3 Port A Peripheral Chip Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2.2 Data Processing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2.2.1 Compression Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2.2.2 Compression Flush Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

2.2.3 Decompression Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

2.2.4 Decompression Output Disabled Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

2.2.5 Pass Through A to B Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

2.2.6 Pass Through B to A Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

3.0 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

3.1 DCLZ Control: Address 00 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

3.2 DCLZ Status: Address 01 Hex - Read Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3.3 Comp Ratio Optimization: Address 02 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

3.4 DMA Configuration: Address 03 Hex - Read/Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

3.5 Port A Control 0: Address 04 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.6 Port A Control 1: Address 05 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

3.7 Port A Status: Address 06 Hex - Read Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3.8 Port A Byte Count: Address 07,08,09 Hex - Read/Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.9 Port B Control 0: Address 0A Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.10 Port B ControL 1: Address 0B Hex - Read/Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

3.11 Port B Status: Address 0C Hex - Read Only. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.12 Port B Byte Count: Address 0D,0E,0F Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.13 Port B Byte Comparator: Address 10,11,12 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.14 Record Length: Address 13,14,15 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 1

3.15 Record Count: Address 16,17,18 Hex - Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.16 Interrupt Status: Address 19 Hex - Read Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.17 Interrupt Clear: Address 19 Hex - Write Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.18 Interrupt Disable: Address 1A Hex - Read/Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.19 Identification: Address 1F Hex - Read Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

4.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.1 Processor Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.2 Port A Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

4.3 Port B Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

5.0 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

6.0 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

6.1 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

6.2 Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

6.2.1 DC Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

6.2.2 AC Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

6.2.3 Pin Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

7.0 Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Page 3

Advanced Hardware Architectures, Inc.

ii PS3210B-1299

8.0 Packaging. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

9.0 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

9.1 Available Parts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

9.2 Part Numbering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

10.0 AHA Related Technical Publications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Page 4

Advanced Hardware Architectures, Inc.

PS3210B-1299 iii

Figures

Figure 1: Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Figure 2: Dual Data Bus Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Figure 3: Single Data Bus Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Figure 4: Port A Peripheral Chip Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Figure 5: Compression Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Figure 6: Compression Flush Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Figure 7: Decompression Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Figure 8: Decompression Output Disabled Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Figure 9: Pass Through A to B Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Figure 10: Pass Through B to A Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Figure 11: Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Figure 12: Dynamic Current - Idd vs. Compression Ratio. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Figure 13: Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Figure 14: Reset Timing - Power Up. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Figure 15: Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Figure 16: Processor Read Cycle - DSN, RWN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Figure 17: Processor Write Cycle - DSN, RWN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Figure 18: Processor Read Cycle - IORDN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Figure 19: Processor Write Cycle - IOWRN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Figure 20: Processor Read Cycle from Port A Peripheral - DSN, RWN Controlled . . . . . . . . . . . . . . . . . . . . . . . . . .36

Figure 21: Processor Write Cycle to Port A Peripheral - DSN, RWN Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Figure 22: Processor Read Cycle from Port A Peripheral - IORDN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Figure 23: Processor Write Cycle to Port A Peripheral - IOWRN Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Figure 24: DMA Slave Transfer Timing for Data Into Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Figure 25: DMA Slave Transfer Timing for Data Out of Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Figure 26: DMA Master Transfer Timing for Data Into Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Figure 27: DMA Master Transfer Timing for Data Out of Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Figure 28: AHA3210B Package Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Page 5

Advanced Hardware Architectures, Inc.

iv PS3210B-1299

Tables

Table 1: Data Bus Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Table 2: Register Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Table 3: DCLZ Mode Bit Decode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Table 4: Supported Modes for DCLZ Control Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Table 5: DATA BUS MODE Bit Decode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 6: Port A DMA Bus Master/Slave Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 7: Port B DMA Bus Master/Slave Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 8: Clock Timing Specification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Table 9: Reset Timing Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Table 10: Processor Read Cycle Timings - DSN, RWN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Table 11: Processor Write Cycle Timings - DSN, RWN Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Table 12: Processor Read Cycle Timings - IORDN Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Table 13: Processor Write Cycle Timings - IOWRN Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Table 14: Processor Read Cycle Timings from Port A Peripheral - DSN, RWN Controlled . . . . . . . . . . . . . . . . . . .36

Table 15: Processor Write Cycle to Port A Peripheral Timings - DSN, RWN Controlled. . . . . . . . . . . . . . . . . . . . . .37

Table 16: Processor Read Cycle from Port A Peripheral Timings - IORDN Controlled . . . . . . . . . . . . . . . . . . . . . . .38

Table 17: Processor Write Cycle to Port A Peripheral Timings - IOWRN Controlled. . . . . . . . . . . . . . . . . . . . . . . . .39

Table 18: DMA Slave Transfer Timing for Data Into Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Table 19: DMA Slave Transfer Timing for Data Out of Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Table 20: DMA Master Transfer Timing for Data Into Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Table 21: DMA Master Transfer Timing for Data Out of Port A,B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Page 6

PS3210B-1299 Page 1 of 45

Advanced Hardware Architectures, Inc.

1.0 INTRODUCTION

The AHA3210B is a single-chip CMOS

lossless compression and decompression int egrated

circuit under development implementing the

industry standard Data Compression Lempel Ziv

(DCLZ) adaptive compression algorithm. The

device processes data in compression,

decompression or pass-through modes. The

AHA3210B is based on the earlier 10 MBytes/sec

introduction, AHA3210. It maintains the same

pinout, performance, flexibility and I/O interface as

AHA3210.

Content Addressable Memor y within the DCLZ

engine eliminates external SRAMs typically

required for dictionary storage in a compression

system. Other supporting system features include

two 24-bit counters, automatic multiple-record

transfer, compression ratio optimization and DCLZ

error detection logic.

The DCLZ algorithm is approved by several

standards organi zations including QIC, DA T , ANSI,

ISO and ECMA. DCLZ has been accepted by

Hewlett-Packard and other system companies

worldwide as their standard of choice in their tape

storage peripherals. The algorithm exhibits an

average compression ratio of 2 to 1 over typical

computer data.

This specification contains a functional

overview, operation modes, register descriptions,

DC and AC Electrical characteristics, ordering

information and Related Technical Publications. It

is intended for hardware and software engineers

designing a compress ion system u sing AHA3210B.

AHA designs and develops lossless

compression, forward error correction and data

storage formatter/controller ICs. Technical

publications are available upon request from us or

our sales representatives/agents worldwide.

1.1 FEATURES

PERFORMANCE:

• 10 MBytes/sec data compressi on, decompr ession

or pass-through rate with a 20 MHz clock

• 2 to 1 average compression ratio

• High compression of small records

• Automatic multiple-record transfers without

microprocessor intervention

• Dynamic compression ratio monitoring

• Error checking in decompression mode

reportable via an interrupt

FLEXIBILITY:

• In-Line and Look-Aside architectures supported

• Polled or interrupt driven I/O

• Two independent DMA ports programmable for

8 or 16-bit t ransfers; mast er or slave mode

SYSTEM INTERFACE:

• Single chip data compression solution

• No SRAM required

• Programmable interrupts

• Interfaces directly with AHA’s tape format

controller, AHA5140, and industry standard

SCSI controllers

OTHERS:

• Open standard DCLZ adaptive lossless

compression algorithm

• Standards include: QIC DDS/DAT, ANSI, ISO

and ECMA

• Low power stand-by operation

• EIAJ-standard 100 pin plastic quad flat package

• Software emulation of the algorithm available

1.2 APPLICATIONS

• DDS-DAT, QIC, 8mm or DLT tape drives

• High performance laser printers

1.3 FUNCTIONAL OVERVIEW

The AHA3210B Data Compression

Coprocessor IC is a high performance, single chip

data compression solution, for use in tape drives,

disk drives and embedded controller applications.

The processor interface is us ed to t ran sf er da ta

to the registers inside the chip. The PROCMODE

strapping pin selects between a Motorola and an

Intel style processor interface.

The DCLZ Engine implements the DCLZ

lossless data compression algorithm. It contains a

compressor, which inputs uncompres sed data from

the Port A interface, compresses it, and sends the

compressed codes to the Port B interface. The

DCLZ Engine also contains a de compressor , whic h

inputs compressed co des f rom the Port B interfa ce,

decompresses it, and sends the uncompressed data

to the Port A interfac e. The Recor d Lengt h regis ter

and Record Count register al low uncompressed data

to be partitioned into fixed sized blocks, and then

compressed and decompressed automatically.

Page 7

Page 2 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

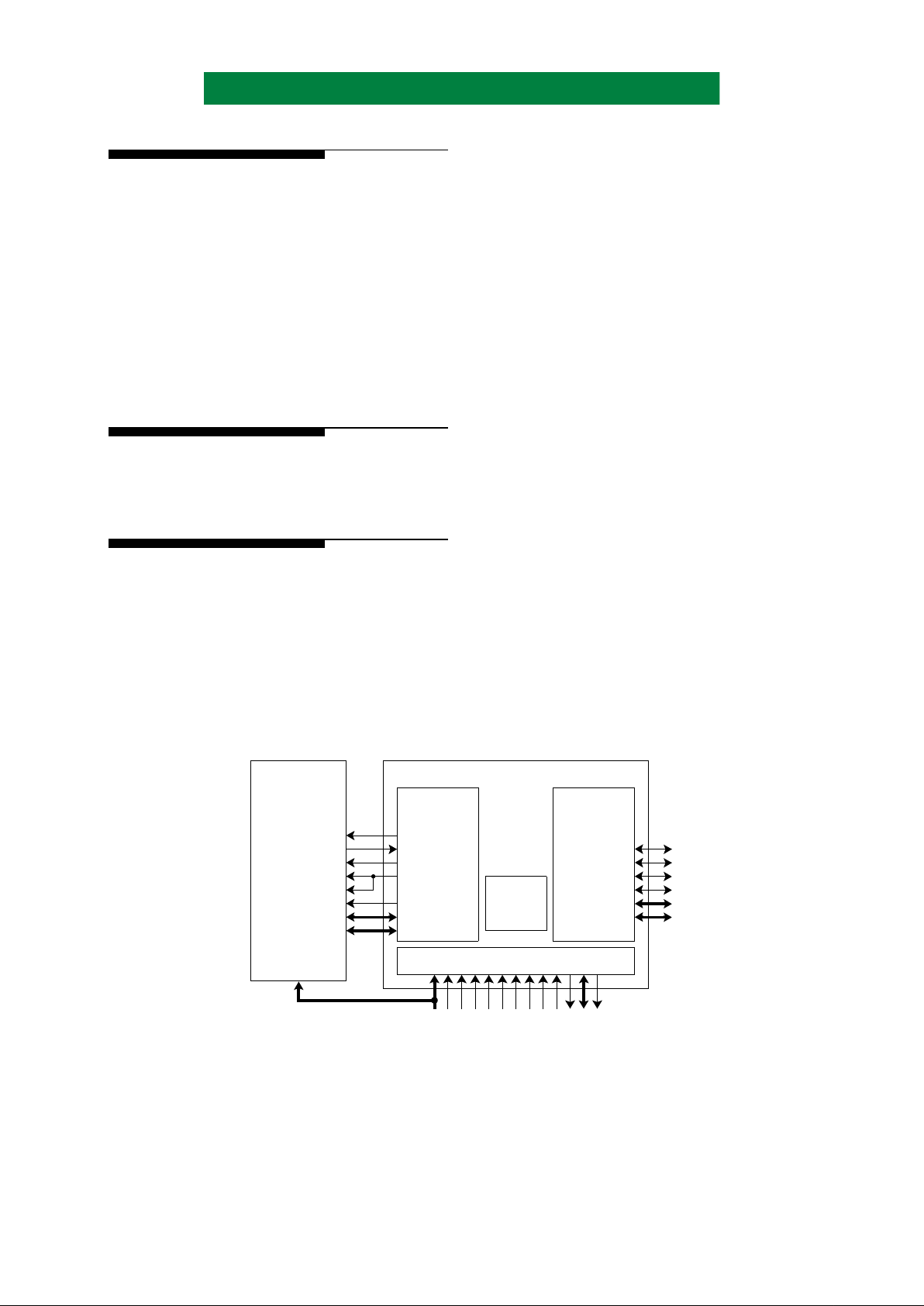

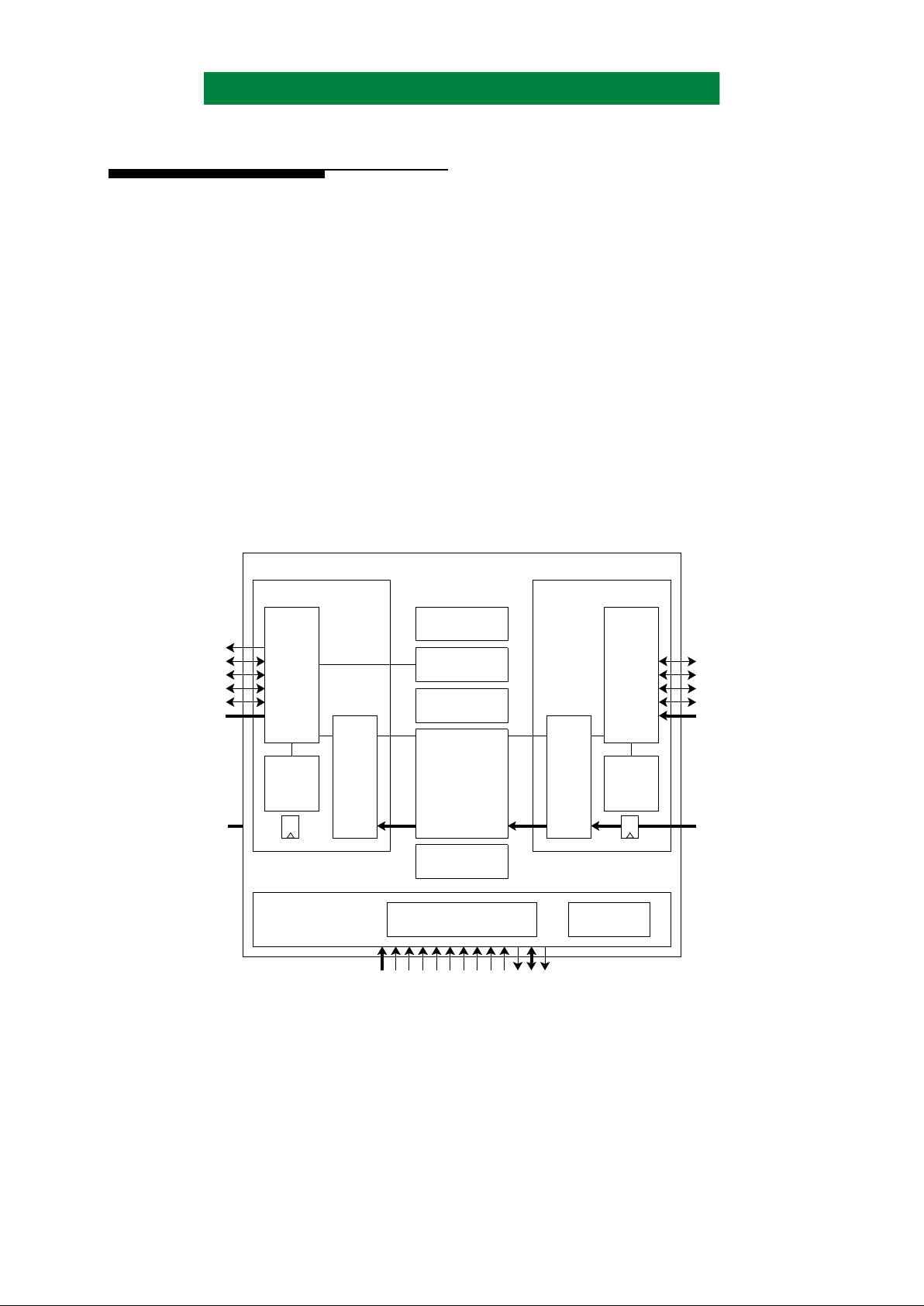

Figure 1: Functional Block Diagram

The Pass Through Controller bloc k allows data

to be transferred bet ween Port A and Port B without

being compressed or decompressed.

Port A and Port B are two independent DMA

interfaces. For compression and decompre ssi on

operations, Port A transf ers uncompressed data and

Port B transfers compre ssed cod es. Each p ort has a

byte counter , which counts the number of bytes that

are transferred through the port. The configuration

of the DMA interface on each po rt is programmable.

These functions incl ude DMA master or slave, eight

or sixteen bit t ransfers, and contr ol pin enabling and

polarity . The Port B Byte Count register has a Port B

Byte Comparator register, allowing the chip to

interrupt after a programmed amount of data has

been transferred on the Port B data bus, DB[15:0].

Register accesses to a peripheral chip connected to

Port A are also supported.

2.0 MODES OF OPERATION

There are two classes of the modes of operatio n

for this chip. The first class is determined by the

Port A and Port B DMA data bus configurations.

Port A and Port B can be dual independent data

buses, or Port A and Port B can be connected to

create a single data bus. The second class is

determined by the method data is processed through

the chip in compression, decompression or pass

through modes.

2.1 PORT A AND B PORT DATA BUS

CONFIGURATION

Port A and Port B data bus configuration is

controlled by the DATA BUS MODE[2:0] bits in

the DMA Configuration regi ster . These bits contro l

the single and dual data bus modes, as well as Port

A and Port B being the DMA bus master or slave

(see Table 1).

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTACSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 8

PS3210B-1299 Page 3 of 45

Advanced Hardware Architectures, Inc.

Table 1: Data Bus Modes

2.1.1 DUAL DATA BUS MODE: IN-LINE

APPLICATION

In dual data bus mode, Port A and Port B

transfer data on unique, independent data buses.

This is used for in-line applications, whe n data is

transferred from th e host interface, t hrough the data

compression coprocessor, and into the system

buffer (see Figure 2).

In dual data bus mode, the data rate during

compression is sustained at 10 MB/sec, except

when the compression ratio is less than 1 (which

occurs briefly when a compression dictionary is

first being built, or when data is actually

expanding). The data rate during decompression,

pass through A to B, a nd pass through B to A modes

is sustained at 10 MBytes/sec (see Figure 3).

2.1.2 SINGLE DATA BUS MODE: LOOK-ASIDE

APPLICATION

In single data bus mode, Port A and Port B

transfer data on a common data bus. This

connection is made external to the chip, on the PC

board. This is used in a look aside application, when

the data compression coproc essor transfers data into

and out of the system buffer.

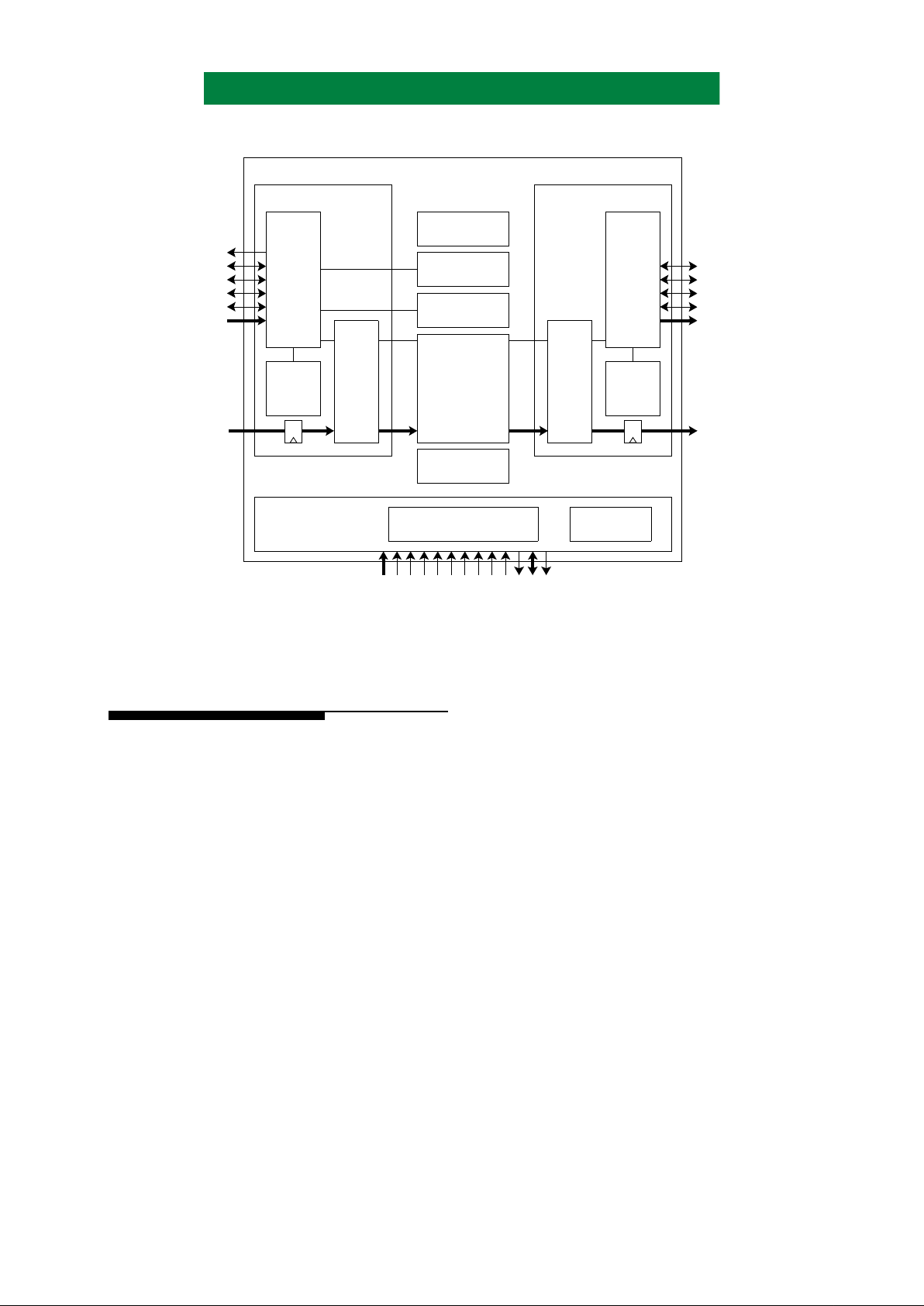

Figure 2: Dual Data Bus Mode

Figure 3: Single Data Bus Mode

DATA BUS

MODE[2]

DA TA BUS

MODE[1]

DATA BUS

MODE[0]

FUNCTION

0 0 0 Dual data bus: Port B slave, Port A slave

0 0 1 Dual data bus: Port B slave, Port A master

0 1 0 Dual data bus: Port B master, Port A slave

0 1 1 Dual data bus: Port B master, Port A master

1 0 0 Dual data bus: Port B slave, Port A slave with peripheral access

101Reserved

1 1 0 Dual data bus: Port B master, Port A slave with peripheral access

1 1 1 Single data bus: Port B master, Port A master

HOST

INTERFACE

BUS

INTERFACE

PROCESSOR INTERFACE

SYSTEM

TAPE

DRIVE

BUS CONTROLLER

BUFFER

INTERFACE

PORT A

INTERFACE

SINGLE DATA

BUS ARBITER

DCLZ

ENGINE

PORT B

INTERFACE

HOST

INTERFACE

BUS

INTERFACE

PROCESSOR INTERFACE

SYSTEM

TAPE

DRIVE

BUS CONTROLLER

BUFFER

INTERFACE

PORT A

INTERFACE

SINGLE DATA

BUS ARBITER

DCLZ

ENGINE

PORT B

INTERFACE

Page 9

Page 4 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

2.1.3 PORT A PERIPHERAL CHIP INTERFACE

A peripheral chip can be connected to Port A,

and have its registers accessed through the

processor interface of the data compression chip

(see Figure 4). This is used in in-line applications,

for peripheral chips with a common DMA and

processor data bus (such as the NCR 53C90A/B and

the NCR 53C94/5/6 SCSI controllers).

It is the firm ware’s responsib ility to ensure

accesses to the peripheral chip’s registers do not

occur while DMA transfers ar e occurring on Port A.

This mode is only s upported when Port A is a DMA

slave, in dual data bus mode.

2.2 DATA PROCESSING MODES

The data processing modes a re controlled by the

DCLZ MODE[2:0] bits in the DCLZ Control

register.

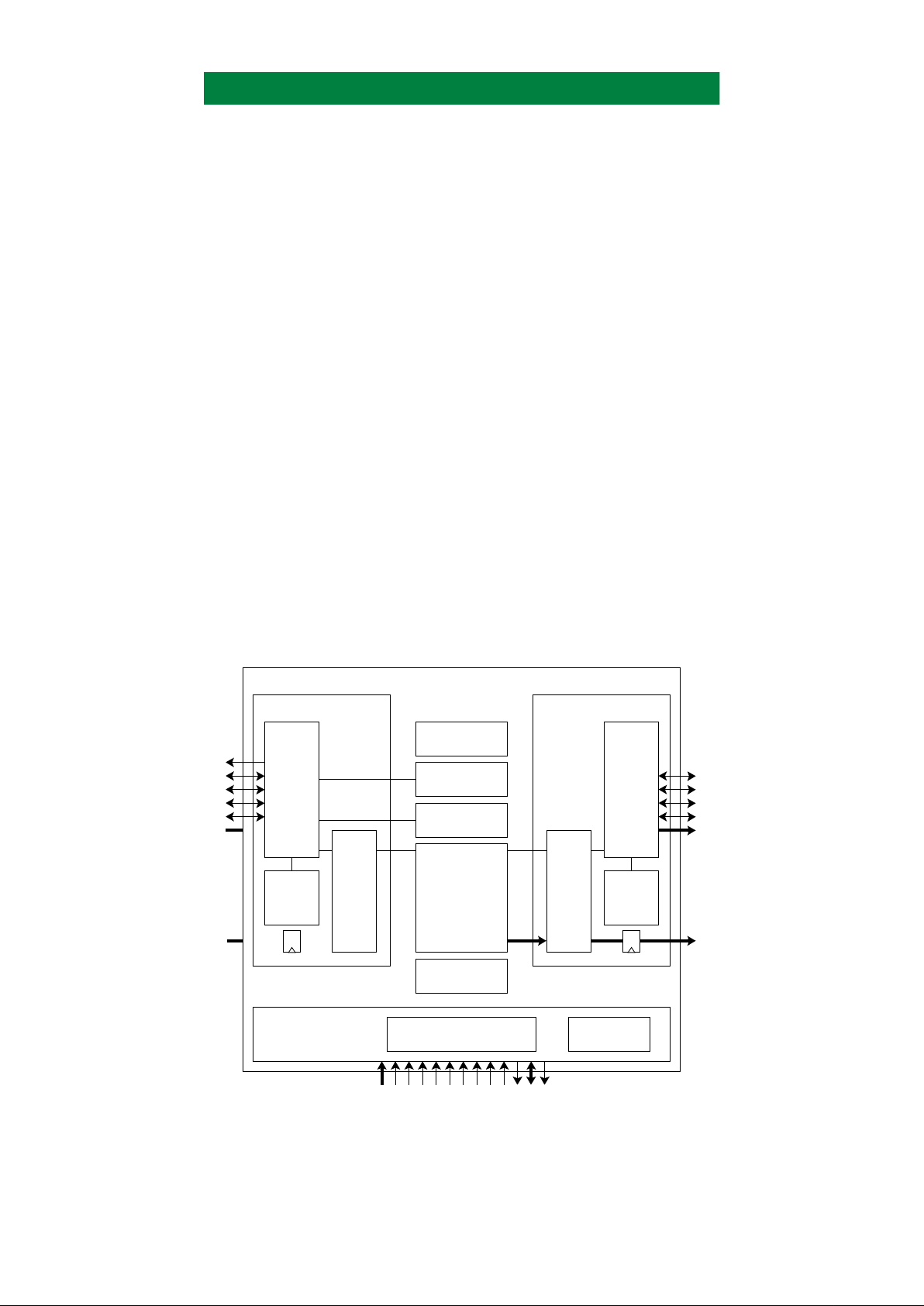

2.2.1 COMPRESSION MODE

During compression mode, uncompres sed data

flows into Port A. It is then comp ressed by the

DCLZ engine. The resulting compressed data is

then transferred out of Port B (see Figure 5).

The uncompressed data i s partitioned into fixed

sized recor ds. The size is stored in the Record

Length register inside the chip. After a record has

been compressed, an end of record codeword is

inserted into the compres sed data. The end of record

codewords are then used during decompression, to

control data flow.

Multiple records can be compressed without

processor intervention. The Record Count register

inside the chip stores the number of records to

compress. A compression sequence has been

completed after the last byte of the last record has

been compressed and transfer red out of Port B. This

event sets the Port B End of Transfer interrupt.

Compression ratio is defined as the number of

uncompressed bytes divided by the number of

compressed bytes. The Port A Byte Counter co unts

the number of uncompressed bytes. The Por t B Byte

Counter counts the number of compressed bytes.

The compression ratio can also be automatically

controlled, by programming the Comp Ratio

Optimization register.

The following sequence is used to p rog ram the

chip to compress multiple, fixed size records:

- Program Record Length register

- Program Record Count register

- Program Interrupt Disable register

- Enable PORT B END OF TRANSFER Interrupt

- Program Comp Ratio Optimization register

- Program DCLZ Control register

DCLZ MODE[2:0] Compression

COMP RATIO OPT ENABLE 1

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT B END OF TRANSFER interrupt signals

compression completed

Figure 4: Port A Peripheral Chip Interface

PROCESSOR INTERFACE

DCLZ

ENGINE

PORT B

CS/

DREQ

DACK/

DBWR/

RD/

DBP[1:0]

DB[15:0]

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

WR/

A[3:0]

PORT A

INTERFACE

PERIPHERAL

A[4:0]

PORTACSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESETN

CLK

DTACKN/READY

D[7:0]

INTN/INT

CHIP

AHA3210B Compression Chip

Page 10

PS3210B-1299 Page 5 of 45

Advanced Hardware Architectures, Inc.

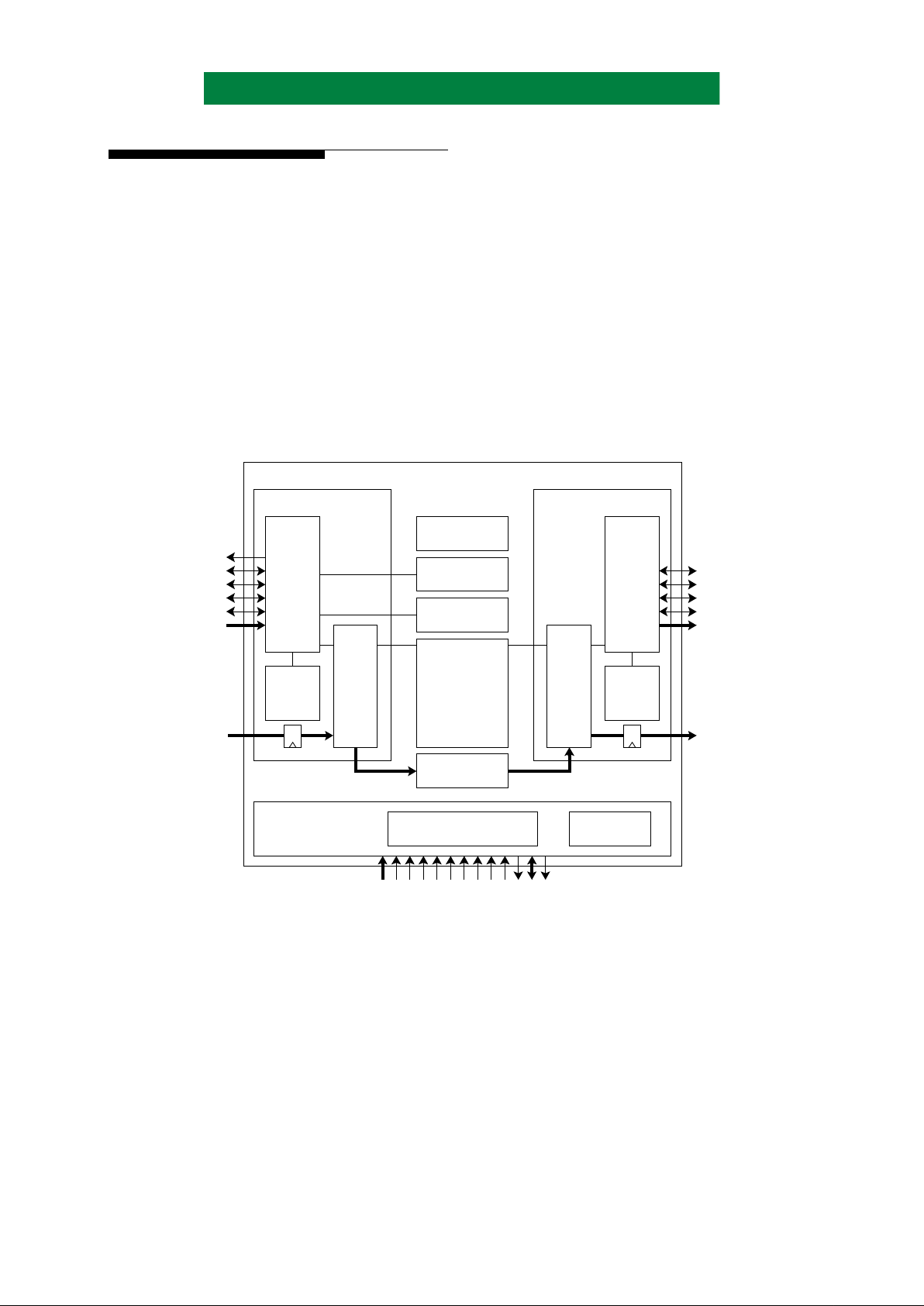

Figure 5: Compression Mode

2.2.2 COMPRESSION FLUSH MODE

Normal compression operat ions complete when

the Record Length register and the Record Count

register both decrement to zero. All data in the chip

is then compressed, and transferred out of Port B.

There is no data in the chip, and the chip is said to be

flushed (see Figure 6).

Consider the scenario when a compression

operation is require d to comple te premat urel y (i.e.,

before the Record Length register and the Record

Count register have both decremented to zero). In

this scenario, Port A DMA i s inactive, because there

is no more uncompressed data to transfer into the

chip. Due to the DCLZ data compression algor ithm,

there may be partially compr essed data in the DCLZ

engine at this ti me.

Compression flush mode is used to complete

the compression operation , transfer all compr essed

data out of Port B, and get the chi p into t he flus hed

state. Note that the compression flush operation

inserts an end of recor d code word at the appropriate

location, near the end of the compressed data

stream.

The chip should only be programmed into

compression flus h m od e wh en the Port A Inter fa ce

is empty (i.e., when the Port Inte rface Byte Count in

the Port A Status register is zero) and the DCLZ

engine contains data (i.e., when the DCLZ Engine

Flushed bit in the DCLZ S tatus r egister is zero) and

the DCLZ Engine is not already in the process of

flushing (i.e., The DCLZ EOR COUNT bit in the

DCLZ Status register is zero).

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTACSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 11

Page 6 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

The following sequence is use d to prog ram the

chip for Compression Flush mode for the scenario

described above:

- Program DCLZ Control register

DCLZ MODE[2:0] Compression

COMP RATIO OPT ENABLE 1

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 1

- Wait until the PAUSED bit in the DCLZ Status register is set

- Program Record Count register to 000000 hex

- Program Interrupt Disable register

- Enable PORT B END OF TRANSFER Interrupt

- If the DCLZ Engine Flushed bit is zero and the DCLZ EOR

COUNT bit is zero, then there is data in the DCLZ Engine to

transfer out via compression flush mode.

BEGIN

- Program DCLZ Control register

DCLZ MODE[2:0] Compression flush

COMP RATIO OPT ENABLE 1

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT B END OF TRANSFER interrupt signals

compression completed

END

- If the DCLZ Engine Flushed bit is zero and the DCLZ EOR

COUNT bit is one, then the DCLZ Engine is already in the

process of flushing.

BEGIN

- Program DCLZ Control register

DCLZ MODE[2:0] Compression

COMP RATIO OPT ENABLE 1

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT B END OF TRANSFER interrupt signals

compression completed

END

- If the DCLZ Engine Flushed bit is one and the Port B Interface

Byte Count is not zero, then there is data in the Port B Interface

to transfer out.

BEGIN

- Program DCLZ Control register

DCLZ MODE[2:0] Compression

COMP RATIO OPT ENABLE 1

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT B END OF TRANSFER interrupt signals

compression completed

END

- If the DCLZ Engine Flushed bit is one and the Port B Interface

Byte Count is zero, then the DCLZ Engine and the Port B

Interface are already flushed.

Figure 6: Compression Flush Mode

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTACSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 12

PS3210B-1299 Page 7 of 45

Advanced Hardware Architectures, Inc.

2.2.3 DECOMPRESSION MODE

During decompression mode, compressed data

flows into Port B. It is then uncompressed by the

DCLZ engine. The resulting uncompressed data is

then transferred out of Port A.

The compressed data is partitioned into records,

with End of Record codewords embedded in the

compressed data. Multiple records can be

automatically decompressed, by programming the

number of records into the Record Coun t register . A

decompression sequence has been completed after

the last byte of the last record has been

uncompressed and then transferred out of Port A.

This event sets the Port A End of T r ansfer int errupt.

The following sequence is used to p rogram the

chip to decompress multiple records:

- Program Record Count register

- Program Interrupt Disable register

- Enable PORT A END OF TRANSFER Interrupt

- Program DCLZ Control register

DCLZ MODE[2:0] Decompression

COMP RATIO OPT ENABLE 0

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT A END OF TRANSFER Interrupt signals

decompression completed

Figure 7: Decompression Mode

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTA CSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 13

Page 8 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

2.2.4 DECOMPRESSION OUTPUT DISABLED

MODE

The DCLZ algorithm allows the compression

dictionary to be shared between multiple records.

To decompress records in the middle of a multiple

record sequence, the pr eceding records must first be

decompressed, in order to properly build the

compression dictionary.

Decompression output disabled mode allows

the preceding records to be decompressed, while

discarding the unwanted un compr essed data. Once

this is completed, the chip can be programmed to

decompression mode, to decompr ess and output the

desired records.

In decompression output disabled mode, the

data is discarded between the Port A Interface and

the Port A pins. Port A DMA remains inactive . The

Port B Byte Counter, the Port A Byte Counter, the

Port B Interface Byte Count, the Port A Interface

Byte Count, the Record Count regis ter , and the Port

A End of Transfer Interrupt operate as in

decompression mode. It is recommended that the

Port A Interface be empty and th e chip paused

before switching between decompression output

disabled and decompression modes.

The following sequence is used to p rog ram the

chip to decompress multiple records in output

disabled mode:

- Program Record Count register

- Program Interrupt Disable register

- Enable PORT A END OF TRANSFER Interrupt

- Program DCLZ Control register

DCLZ MODE[2:0] Decomp; Output

Disabled Mode

COMP RATIO OPT ENABLE 0

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT A END OF TRANSFER Interrupt signals

decompression output disabled completed

Figure 8: Decompression Output Disabled Mode

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTA CSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 14

PS3210B-1299 Page 9 of 45

Advanced Hardware Architectures, Inc.

2.2.5 PASS THROUGH A TO B MODE

During pass through A to B mode, data enters

Port A, is transferred through the Port A Interface

and the Port B Interface, and then transferred out of

Port B. The data is not altered as it passes through

the chip.

The Record Le ngth register determines the

number of bytes in a record. The Record Count

register determines the number of records. Multiply

the values of these two registers to determine the

total number of bytes that will be transferred

through the chip. The pass through sequence has

been completed after the last byte of the last record

has been transferred out of Port B. This event sets

the Port B End of Transfer interrupt.

The following sequence is used to p rogram the

chip to pass through data from Port A to Port B:

- Program Record Length register

- Program Record Count register

- Program Interrupt Disable register

- Enable PORT B END OF TRANSFER Interrupt

- Program DCLZ Control register

DCLZ MODE[2:0] Pass through A to B

COMP RATIO OPT ENABLE 0

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT B END OF TRANSFER interrupt signals pass

through A to B completed

Figure 9: Pass Through A to B Mode

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTACSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 15

Page 10 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

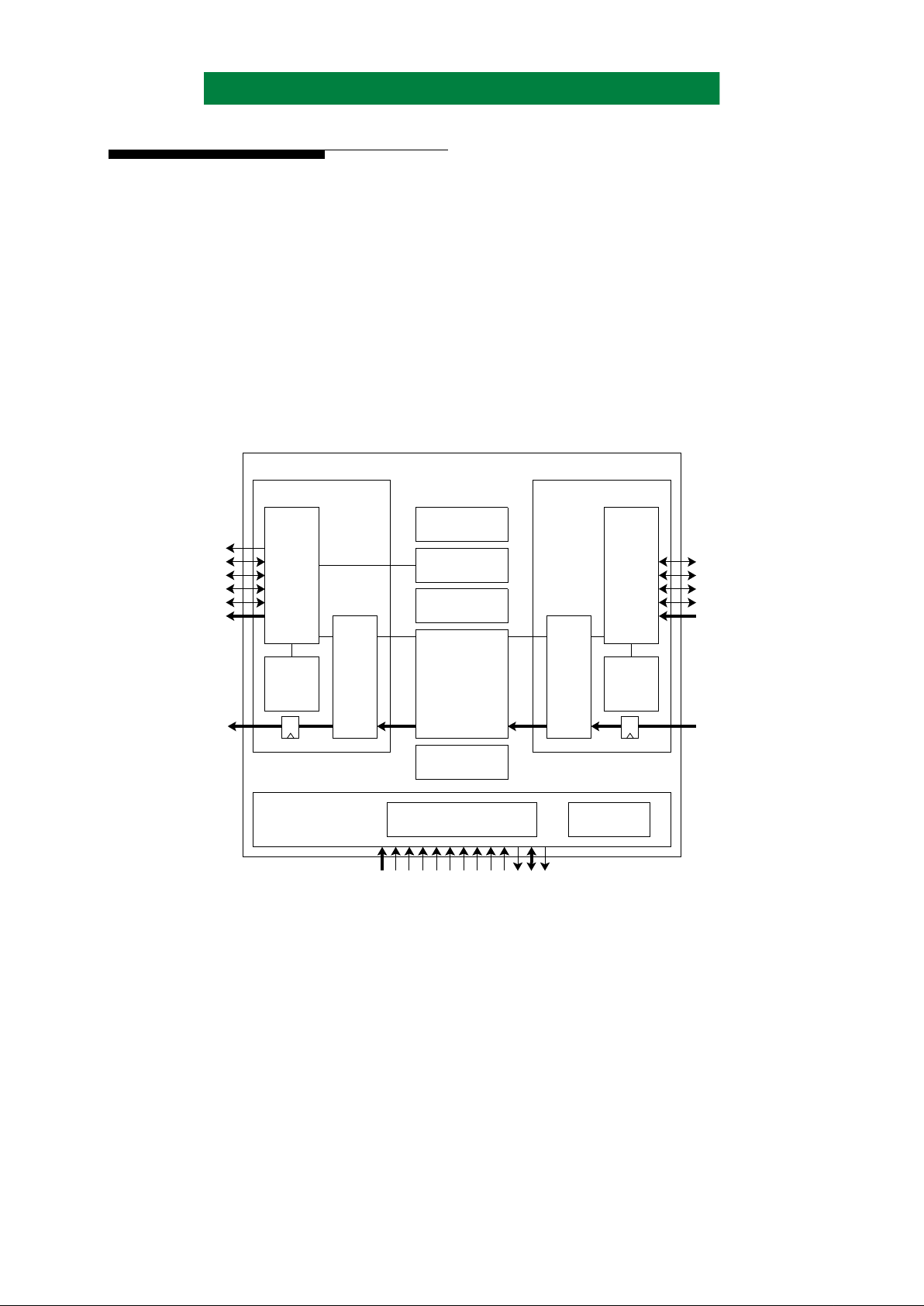

2.2.6 PASS THROUGH B TO A MODE

During pass through B to A mode, data enters

Port B, is transferred through the Port B Interface

and Port A In terface, and is then transferred out of

Port A. The data is not altered as it passes through

the chip.

The Record Le ngth register determines the

number of bytes in a record. The Record Count

register determines the number of records. Multiply

the values of these two registers to determine the

total number of bytes that will be transferred

through the chip. The pass through sequence has

been completed after the last byte of the last record

has been transferred out of Port A. This event sets

the Port A End of Transfer interrupt.

The following sequence is used to p rogram the

chip to pass through data from Port B to Port A:

- Program Record Length register

- Program Record Count register

- Program Interrupt Disable register

- Enable PORT A END OF TRANSFER Interrupt

- Program DCLZ Control register

DCLZ MODE[2:0] Pass through B to A

COMP RATIO OPT ENABLE 0

RESET DICT AFTER EOR 0

RESET DICT 0

PAUSE AFTER EOR 0

PAUSE 0

- The PORT A END OF TRANSFER interrupt signals pass

through B to A completed

Figure 10: Pass Through B to A Mode

PORT A

BYTE

COUNTER

PORT B

BYTE

COUNTER

PORT A

DMA

STATE

MACHINE

PORT A

FIFO

PORT B

DMA

STATE

MACHINE

PORT B

FIFO

SINGLE DATA

BUS ARBITER

RECORD COUNT

REGISTER

RECORD LENGTH

REGISTER

PROCESSOR INTERFACE

STATE MACHINE

PASS THROUGH

CONTROLLER

INTERRUPT

LOGIC

PROCESSOR

INTERFACE

DCLZ

ENGINE

PORT A INTERFACE PORT B INTERFACE

ACSN

DREQA

DACKA

AOE

AWE

DAPTY[1:0]

DA[15:0]

A[4:0]

PORTACSN

CSN

RWN/IOWRN

DSN/IORDN

PROCMODE

TRISTATEN

TEST

RESTN

CLK

DTACKN/READY

D[7:0]

INTN/INT

DREQB

DACKB

BOE

BWE

DBPTY[1:0]

DB[15:0]

(8 Bytes) (8 Bytes)

AHA3210B Compression Chip

Page 16

PS3210B-1299 Page 11 of 45

Advanced Hardware Architectures, Inc.

3.0 REGISTER DESCRIPTION

Table 2: Register Address Map

Notations:

* These registers have one or more reserved bits set to ‘0’. These registers read back ‘0’ from these reserved bits.

** A soft reset is generated by writing a reset command to DCLZ MODE[2:0].

U - These bits remain unchanged after a soft reset.

x - Indicates undefined bit.

ADDRESS READ WRITE

HARD

RESET

SOFT**

RESET

0x00 DCLZ Control DCLZ Control 1110,0000 111U,UUUU

0x01 DCLZ Status Reserved 0000,0011 0000,0011

0x02 Comp Ratio Optimization Comp Ratio Optimization 0000,0000 Unchanged

0x03 *DMA Configuration DMA Configuration 0000,0101 Unchanged

0x04 Port A Control 0 Port A Control 0 0000,0000 Unchanged

0x05 *Port A Control 1 Port A Control 1 x000,00xx Unchanged

0x06 Port A Status Reserved 0000,0000 0U00,0000

0x07 Port A Byte Count [7:0] Port A Byte Count [7:0] 0000,0000 Unchanged

0x08 Port A Byte Count [15:8] Port A Byte Count [15:8] 0000,0000 Unchanged

0x09 Port A Byte Count [23:16] Port A Byte Count [23:16] 0000,0000 Unchanged

0x0A Port B Control 0 Port B Control 0 0000,0000 Unchanged

0x0B *Port B Control 1 Port B Control 1 x000,00xx Unchanged

0x0C Port B Status Reserved 0000,0000 0U00,0000

0x0D Port B Byte Count [7:0] Port B Byte Count [7:0] 0000,0000 Unchanged

0x0E Port B Byte Count [15:8] Port B Byte Count [15:8] 0000,0000 Unchanged

0x0F Port B Byte Count [23:16] Port B Byte Count [23:16] 0000,0000 Unchanged

0x10 Port B Byte Comparator [7:0] Port B Byte Comparator [7:0] Undefined Unchanged

0x11 Port B Byte Comparator [15:8] Port B Byte Comparator [15:8] Undefined Unchanged

0x12 Port B Byte Comparator [23:16] Port B Byte Comparator [23:16] Undefined Unchanged

0x13 Record Length [7:0] Record Length [7:0] Undefined Unchanged

0x14 Record Length [15:8] Record Length [15:8] Undefined Unchanged

0x15 Record Length [23:16] Record Length [23:16] Undefined Unchanged

0x16 Record Count [7:0] Record Count [7:0] Undefined Unchanged

0x17 Record Count [15:8] Record Count [15:8] Undefined Unchanged

0x18 Record Count [23:16] Record Count [23:16] Undefined Unchanged

0x19 Interrupt Stat us Interr upt Clear 0000,0000 Unchanged

0x1A *Interrupt Disable Interrupt Disable 0011,1111 Unchanged

0x1F Identification Reserved 0100,0001 0100,0001

Page 17

Page 12 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

3.1 DCLZ CONTROL: ADDRESS 00 HEX - READ/WRITE

DCLZ MODE[2 :0] = DCLZ Control r egister [7:5]:

The DCLZ MODE bits determine how the chip will process data as follows.

– Pass through modes transfer data through the chip without any compression or decompression

operation. Pass through A to B transfers data into Port A and out of Port B. Pass through B to A

transfers data into Port B and out of Port A.

– Compression mode transfers uncompressed data into Port A, compresses it, and transfers

compressed data out of Port B.

– Compression flush mode causes all data in the DCLZ Engine to be compr essed inc luding an end of

record codeword, and then flushed out of the chip through Port B.

– Decompression mode transfers compressed data into Port B, decompresses it, and transfers

uncompressed data out of Port A.

– Decompression output disabled mode transfers compressed data into Port B, decompresses it and

builds the decompression dictionary, but does not transfer any uncompressed data out of Port A.

– Reset mode resets all state machines and data in Port A, Port B, single data bus arbiter, and the

DCLZ engine. It also resets the dictionary. It resets the registers as shown in Table 2.

The DCLZ Control bits should always be programmed to the reset mode, when switching between all

modes, except between compression and compression flush modes and between decompression and

decompression output disabled modes. It is recommended that the Port A Interface be empty and the

chip paused before switching between decompression output disabled and decompression modes. The

DCLZ MODE bits are set to on e when the chip is rese t from the RESETN pin. The DCLZ MODE bits

are decoded as shown below:

Table 3: DCLZ Mode Bit Decode

COMP RATIO OPT ENABLE:

The COMPRESSION RATIO OPTIMIZATION ENABLE bit enables the automatic compression ratio

optimizer during compression. This bit enables the THRESH[5:0] and PERIOD[1:0] bits in the Comp

Ratio Optimization register. A one enables optimization, and a zero disables optimization. This bit is

cleared to zero when the chip is reset from the RESETN pin.

RESET DICT AFTER EOR:

During compression, the RESET DICTIONARY AFTER END OF RECORD bit causes the DCLZ

engine to reset the compr ession dicti onary after each end of record, and before the fi rst subsequent byt e

which is not designated as an end of record. A one resets the dictionary after end of record, and a zero

has no effect on the di ction ary. This bit is cleared to zero when the chip is rese t from the RESETN pin.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x00 D C L Z M O DE[2:0]

COMP

RATIO OPT

ENABLE

RESET DICT

AFTER EOR

RESET

DICT

PAUSE

AFTER EOR

PAUSE

DCLZ

MODE[2]

DCLZ

MODE[1]

DCLZ

MODE[0]

FUNCTION

0 0 0 Pass through A to B

0 0 1 Pass through B to A

010Compression

0 1 1 Compression flush

1 0 0 Decompression

1 0 1 Decompression output disable

110Reserved

111Reset

Page 18

PS3210B-1299 Page 13 of 45

Advanced Hardware Architectures, Inc.

RESET DICT

The RESET DICTIONARY bit causes the compression dictionary to be reset after completing the

current byte, and before the next byte which is not designated as an end of record. A one causes the

dictionary to be reset, and a zero has no effect on the dictionary. The RESET DICT bit will be

automatically cleared, once a dictionary rese t has occurred. This bit is c le are d to zer o when t h e ch ip i s

reset from the RESETN pin.

PAUSE AFTER EOR:

Writing a one to the PAUSE AFTER END OF RECORD bit causes the Port A interface, the DCLZ

Engine and the Port B interface to pause after each end of record has been processed. The PA USED

status bit in the DCLZ Status register is then set. To allow the chip to continue, a zero must be written

to the PAUSE bit. This bit is cleared to zero when the chip is reset from the RESETN pin.

PAUSE:

Writi ng a one to the PAUSE bit causes the Port A interface, the DCLZ Engine, and the Port B interface

to pause. The PAUSED status bit in the DCLZ Status regist er i s then set. Writ ing a zero to the PAUSE

bit allows the chip to resume operation after it has been paused or paused after end of record. PAUSE

bit operation is suppor ted during processor write cyc les which program the DCLZ Control bit s out of the

Reset state. This bit is cleared to zero when the chip is reset from the RESETN pin.

Table 4: Supported Modes for DCLZ Control Register Bits

3.2 DCLZ STATUS: ADDRESS 01 HEX - READ ONLY

res - Reserved. Bits read back zeros.

DCLZ EOR COUNT:

The DCLZ EOR COUNT bit shows the number of end of records contai ned in the DCLZ Engi ne. This

bit operates in compression, compression flush, decompression, and decompression output disabled

mode. This bit is cleared to zero when the reset or pass through A to B or pass through B to A code is

programmed to the DCLZ MODE bits in the DCLZ Control register, or when the chip is reset by the

RESETN pin. The DCLZ EOR COUNT bit can transition frequently when the DCLZ Engine is actively

processing data (i.e., when it is not paused). Therefore, the DCLZ EOR COUNT bit should only be

considered valid when the PAUSED bit is one.

DCLZ ENGINE FLUSHED:

This bit operates in compression, compression flush, decompression, and decompression output

disabled modes only. When the DCLZ ENGINE FLUSHED bit is a one, there is no data in the DCLZ

Engine. This occurs a fter an end of record has bee n processed thr ough the DCLZ Engine , and before the

first byte of t he n ext r ecord has entered t he DCLZ Engine. Once the first byte of the next re cor d e n te rs

the DCLZ Engine, the DCLZ ENGINE FLUSHED bit is cleared to zero. The DCLZ ENGINE

FLUSHED bit is set to one when the DCLZ MODE bits are programmed to pass through A to B, pass

through B to A, or reset mode. Also, the DCLZ ENGINE FLUSHED bit is set to one when the chip is

reset by the RESETN pin. The DCLZ ENGINE FLUSHED bit can transi tion frequently when the DCLZ

Engine is actively processing data (i.e., when it is not paused). Therefore, the DCLZ ENGINE

FLUSHED bit should only be considered valid when the PAUSED bit is one.

MODE

COMP RATIO

OPT ENABLE

RESET DICT

AFTER EOR

RESET

DICT

PAUSE

AFTER EOR

PAUSE

Compression YES YES YES YES YES

Compression flush YES YES YES YES YES

Decompression NO NO NO YES YES

Decompression output disabled NO NO NO YES YES

Pass through A to B NO NO NO YES YES

Pass through B to A NO NO NO YES YES

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x01 res

DCLZ EOR

COUNT

DCLZ ENGINE

FLUSHED

P AUSED

Page 19

Page 14 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

PAUSED:

When the PAUSED bit is one, the Port A interface, the DCLZ Engine, and the Port B interface ar e

paused. The Port A By te Cou nt regi sters, t he Port B Byte Co unt regist ers, th e Port A S tatus r egister, the

Port B Statu s register , the Record Lengt h registers, and the Record Count reg isters are stable at this time.

This bit is set to one when the chip is reset from the RESETN pin, or when the DCLZ Control bits are

programmed to the Reset state.

3.3 COMP RATIO OPTIMIZATION: ADDRESS 02 HEX - READ/WRITE

This register is used to control the compression ratio during compression mode, by automatically

resetting the compression dictionary if the compression ratio is below the programmed threshold. If the

compression dictionary is less than half full the optimization circuit will check the compression ratio and

compare it to the compression ratio programmed in the THRESHOLD parameter every 1024 input bytes

and reset the dictionary if the compression ratio does not meet or exceed this value. After the dictionary is

greater than half full, the optim izer will check the compression ratio against a threshold every n bytes ,

where n is determined by the value of the PERIOD bits. The threshold is set by the value of the THRESH

bits. Optimization is enabled by setting COMP RATIO OPT ENABLE bit in the DCLZ Control register.

The compression ratio is specified by the thresh old bits according to the following formula:

For example, if THRESH is set at 32 the com pression ratio is 2. This compression ratio i s a target. After

every N number of bytes as specified by the PERIOD field has been input, the actual compression ratio is

checked against the target. If the actual is less than the target, the dictionary is automatically reset. The

THRESH[5:0] and PERIOD[1:0] bits are zero when the chip is reset by the RESETN pin.

3.4 DMA CONFIGURATION: ADDRESS 03 HEX - READ/WRITE

res - Reserved. Bits must always be written with zeros. They read back zeros.

DATA BUS MODE [2:0]:

The DA TA BUS MODE bits determine the data configuration for the Port A and Port B DMA buses. In

dual data bus mode, Port A and Por t B are indepe nde nt, isolat ed data buses. Dat a tra nsfer s on each b us

may occur simultane ously . In this mode, Port A and Port B can b e any combination of DMA bus masters

or slaves. This mode is intend ed for in lin e applicatio ns. In sing le bus mode, the Por t A and Port B data

buses are connected together on the PC board.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x02

THRESH[5:0] PERIOD[1:0]

PERIOD

bit 1 bit 0 Size

0 0 512 bytes

0 1 1024 bytes

1 0 2048 bytes

1 1 4096 bytes

COMPRESSION RANGES

Compression Ratio Threshold Value

1 → 20 → 32

2 → 333 → 42

3 → 443 → 48

4 → 849 → 56

8 → 64 57 → 63

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x03 res

DATA BUS MODE[2:0]

compression ratio

64

64 THRESH–

-----------------------------------=

Page 20

PS3210B-1299 Page 15 of 45

Advanced Hardware Architectures, Inc.

Both Port A and Port B are DMA bus masters. The Single Data Bus Arbiter circuit inside the chip

resolves all bus con tention on thi s si ngle d ata bu s. Port A and Port B will never simul taneous ly r equest

the data bus in this mode. This mode i s intended for l ook aside app lications. No te that in s ingle data bus

mode, the DMA port which is transfer ring data out of t he chip has pri ority over the DMA port which is

transferring data into the chip.

The Port A interface suppo rts re gister a ccesse s to a per ipher al chi p on the Por t A data b us. regi ster and

DMA accesses between the Po rt A interface and the per ipheral chip occur on a si ngle data bus, DA[7:0].

This mode is only supported when Port A is a DMA slave in dual data bus mode.

Data bus mode bits are set to 101 after the chip is reset by RESETN.

Table 5: DATA BUS MODE Bit Decode

The Port A and Port B DMA control pins change direction, based on the master or slave mode. The

following table shows the DMA control pin direction for DMA bus master and slave modes: Port A

DMA Bus Master/Slave Pin Configuration

Table 6: Port A DMA Bus Master/Slave Pin Configuration

Table 7: Port B DMA Bus Master/Slave Pin Configuration

3.5 PORT A CONTROL 0: ADDRESS 04 HEX - READ/WRITE

ENABLE DA PULLUP:

A one enables the pullups on the DA[15 :0] pins . A zero tri states the pull ups on th e DA[15:0] pins. This

bit is cleared to zero when the chip is reset by the RESETN pin.

DATA BUS

MODE[2]

DA TA BUS

MODE[1]

DATA BUS

MODE[0]

FUNCTION

0 0 0 Dual data bus: Port B slave, Port A slave

0 0 1 Dual data bus: Port B slave, Port A master

0 1 0 Dual data bus: Port B master, Port A slave

0 1 1 Dual data bus: Port B master, Port A master

1 0 0 Dual data bus: Port B slave, Port A slave with peripheral access

101Reserved

1 1 0 Dual data bus: Port B master, Port A slave with peripheral access

1 1 1 Single data bus: Port B master, Port A master

PIN NAME

PORT A DMA

BUS MASTER

PORT A DMA

BUS SLAVE

DREQA Output Input

DACKA Input Output

AOE Input Output

AW E Input Output

PIN NAME

PORT B DMA

BUS MASTER

PORT B DMA

BUS SLAVE

DREQB Output Input

DACKB Input Output

BOE Input Output

BWE Input Output

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x04

ENABLE

DA

PULLUP

ENABLE

DAPTY

PULLUP

AWE

ENABLE

AOE

ENABLE

AWE

POLARITY

AOE

POLARITY

DREQA

POLARITY

DACKA

POLARITY

Page 21

Page 16 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

ENABLE DAPTY PULLUP:

A one enables the pullups on th e DAPTY[1 :0] pins. A zero tristates the pullups on the DAP TY[1:0] pins.

This bit is cleared to zero when the chip is reset by the RESETN pin.

AWE ENABLE:

A one enables the A WE input when Port A is a DMA bus master , and enables the A WE output when Port

A is a DMA bus sl ave. A zero disables t he AWE input when Port A is a DMA bus master, and tristates

the AWE output when Port A is a DMA bus slave. This bit is cleared to zero when the chip is reset by

the RESETN pin.

AOE ENABLE:

A one enables the AOE input when Port A is a DMA bus master , and enables t he AOE output when Port

A is a DMA bus slave. A zero disable s t he AOE i nput when Port A is a DMA bus master, and tristates

the AOE output when Port A is a DMA bus slave. This bit is cleared to zero when the chip is reset by

the RESETN pin.

AWE POLARITY:

A one makes AWE high active. A zero makes A WE low active. This bit is cleared to zero when the chip

is reset by the RESETN pin.

AOE POLARITY:

A one makes AOE high active. A zer o makes AOE low act ive. This bit is cl eared to z ero when the chip

is reset by the RESETN pin.

DREQA POLARITY:

A one makes DREQA high active. A zero makes DREQA low active. This bit is cleared to zero when

the chip is reset by the RESETN pin.

DACKA POLARITY:

A one makes DACKA high active. A z ero makes DACKA low active. This bit is cl ear ed to zero when

the chip is reset by the RESETN pin.

3.6 PORT A CONTROL 1: ADDRESS 05 HEX - READ/WRITE

DATA BUS WIDTH:

A one makes the Port A data bus 16 bi ts wide, with data transf erred on the DA[15:0] p ins. A zero makes

the Port A data bus 8 bits wide, with data transferred on the DA[7:0] pins. This bit should only be

changed afte r the reset code ha s been programmed to the DCLZ Control bits in the DCLZ Control

register. This bit is undefined when the chip is reset from the RESETN pin.

DATA15TO8:

The DATA 15TO8 bi t causes on e byte to be t ransferred on DA[15:8] on t he next DMA cycle i nto or out

of Port A, when Port A is in 16 bit mode. The intended use of this bit is to transfer a single byte on

DA[15:8] only during t he first DMA cycl e of a contiguo us data transfer sequence. The DATA15T O8 bit

only functions when Port A is in 16 bit mode, and is ignored when Port A is in 8 bit mode. The

DATA15TO8 bit should only be changed after the reset code has been programmed into the DCLZ

Control bits in the DCLZ Control register, or after the chip has paused after end of record, or after the

chip has paused be cause the Port A or Por t B end of transf er inter rupt has occurred . DATA15TO8 ta kes

effect only on the next DMA cycle, which is defin ed as the next occurrence when DACKA pulses active,

and is supported when Port A is a DMA bus master or a DMA bus slave. After the DMA cycle occurs,

the DA TA15TO8 bit is automa tically cleared. DATA15TO8 i s cleared to zero when the chi p is reset from

the RESETN pin.

res - Reserved. Bit must always be written with a zero. It reads back a zero.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x05

DAT A

BUS

WIDTH

DATA15TO8

res

PORT A

DISABLE

CLEAR

INTERF ACE

CLEAR

BYTE

COUNTER

ENABLE

PARITY

ODD

PARITY

Page 22

PS3210B-1299 Page 17 of 45

Advanced Hardware Architectures, Inc.

PORT A DISABLE:

A one disables the Port A control and data buses. The Port A output control signals are made hi-

impedance. The Port A inp ut con trol signa ls ar e ig nored. The DA[15 :0] a nd DAPTY[1:0] data pins are

put into a hi-impeda nce sta te and any tr ansit ions on them are i gnored . A zero in t his bi t posi tion pl aces

Port A into normal operatio nal mode. This bit should only be cha nged while the chip is paus ed at an End

of Transfe r condition. The co ntents of the DCLZ Cont rol register , t he DMA Configuration r egister , and

the Port A Control 0 register, should not be changed while this bit is a one. This bit is cleared to zero

when the chip is reset from the RESETN pin.

CLEAR INTERFACE:

Writi ng a one crea tes a pul se, which clears the Port A Interf ace. W r iting a zero has no ef fect on the Port

A Interface. This bit is always a zero when it is read. The CLEAR INTERF ACE bit is int ended to be used

only when the chip has paused after end of record, or paused becaus e the Port A or Port B end of transf er

interrupt has occurred.

CLEAR BYTE COUNTER:

Writi ng a one crea tes a puls e, which cle ars the Port A Byte Count regi ster. Writing a zero has no ef fect

on the Port A Byte Count register. This bit is always a zero when it is read.

ENABLE PARITY:

A one enables parity on DAPTY[1:0] when Port A is in 16 bit mode, and on DAPTY[0] when Port A is

in 8 bit mode. W riting a zero disables parity on Port A. This bit is undefined when the chi p is reset fro m

the RESETN pin.

ODD PARITY:

A one selects odd parit y on Port A. A ze ro select s even par ity on Port A. This bit i s undefined whe n the

chip is reset from the RESETN pin.

3.7 PORT A STATUS: ADDRESS 06 HEX - READ ONLY

res - Reserved. Bit reads back zero.

DATA7TO0:

When Port A is in 16 bit mode, the DATA7T O0 bit shows whet her the l ast DMA cycle o f a data transf er

sequence out of Port A contains one or two valid bytes. This occurs for the last byte of the last record,

as determined by the Record Count register. If the last byte of the last record is the first byte in the

sequence to output a word, that byte is output on DA[7:0], the data on DA[15:8] is undefined, and the

DATA7TO0 bit is set. If the last byte of the last record is the second byte in the sequence to output a

word, the second to last byte is output on DA[7:0], the last byte is output on DA[15:8], and the

DATA7 TO0 bi t is clear ed. The DATA7T O0 bit is cleared during al l DMA cycles into Port A, during a ll

DMA cycles when Port A is in 8 bit mode, and when the chip is reset from the RESETN pin.

EOR COUNT[1:0]:

The EOR COUNT[1:0] bits show the number of bytes wit h act iv e end of record flags contained in the

Port A Interface. These bits operate in compression, compressi on flush, decompres sion, decompression

output disabled, pass through A to B, and pass throu gh B to A modes. These bits are c leared to zero when

a one is written to the CLEAR INTERFACE bit in Port A Control 1 register, or when the reset code is

programmed to the DCLZ MODE bits in the DCLZ Control register, or when the chip is reset by the

RESETN pin. During data transfers, the se bits should onl y be read when the PAUSED bit in the DCLZ

Status register is a one.

INTERFACE BYTE COUNT[3:0]:

The INTERFACE BYTE COUNT[3:0] bits show the number of bytes that are held in the Port A

Interface. These bits ar e cleared to zero when a one i s written to the CLEAR INTERFACE bit in Port A

Control 1 register , or when th e reset code is progra mmed to the DCLZ MODE bi ts in the DCLZ Control

register , or when the chi p is re se t by th e RE SETN pin. Dur ing data tran sf er s, th ese bit s shou ld onl y be

read when the PAUSED bit in the DCLZ Status register is a one.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x06 res

DATA7TO0 EOR COUNT[1:0] INTERFACE BYTE COUNT[3:0]

Page 23

Page 18 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

3.8 PORT A BYTE COUNT: ADDRESS 07,08,09 HEX - READ/WRITE

Least Significant Byte (address 07 hex):

Middle Byte (address 08 hex)

Most Significant Byte (address 09 hex):

The Port A Byte Count re gister counts the number of byt es that are tran sferred by the Port A DMA State

Machine. This register counts in compression, compression flush, decompression, decompression output

disabled, pass through A to B, and pass through B to A modes. The regi ster is clear ed to zero when a one is

written to the CLEAR BYTE COUNTER bit in Port A Control 1 register, or when the chip is reset by the

RESETN pin. During data transfers, this registe r should only be written or read when the PAUSED bit in the

DCLZ Status register is a one. The counter rolls over from FFFFFF hex to 000000 hex.

3.9 PORT B CONTROL 0: ADDRESS 0A HEX - READ/WRITE

ENABLE DB PULLUP:

A one enables the pullups on t he DB[15:0] pi ns. A zero tri states the pullups on th e DB[15:0] pin s. This

bit is cleared to zero when the chip is reset by the RESETN pin.

ENABLE DBPTY PULLUP:

A one enables the pu llups on the DBP TY[1:0] pi ns. A zero tristates the pullups on the DBP TY[1:0] pins.

This bit is cleared to zero when the chip is reset by the RESETN pin.

BWE ENABLE:

A one enables the BWE i nput when Port B is a DMA bus mas ter, a nd enables the BWE output when Port

B is a DMA bus slave. A zero di sables the BWE input when Port B is a DMA bus master, and tristates

the BWE output when Port B is a DMA bus slave. This bit is cleared to zero when the chip is reset by

the RESETN pin.

BOE ENABLE:

A one enables the BOE input when Port B is a DMA bus master , and enables the BOE output when Port

B is a DMA bus slave. A zero disables the BOE input when Port B is a DMA bus master, and tristates

the BOE output when Port B is a DMA bus slave. This bit is cleared to zero when the chip is reset by

the RESETN pin.

BWE POLARITY:

A one makes BWE high acti ve. A zero makes BWE low active. Thi s bit is cleared to zero when the chip

is reset by the RESETN pin.

BOE POLARITY:

A one makes BOE high active. A zero makes BOE low active. This bit is cleared t o zero when the chip

is reset by the RESETN pin.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x07

[7:0]

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x08

[15:8]

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x09

[23:16]

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x0A

ENABLE

DB

PULLUP

ENABLE

DBPTY

PULLUP

BWE

ENABLE

BOE

ENABLE

BWE

POLARITY

BOE

POLARITY

DREQB

POLARITY

DACKB

POLARITY

Page 24

PS3210B-1299 Page 19 of 45

Advanced Hardware Architectures, Inc.

DREQB POLARITY:

A one makes DREQB high active. A zero makes DREQB low active. This bit is cleared to zero when

the chip is reset by the RESETN pin.

DACKB POLARITY:

A one makes DACKB high active. A zero makes DACKB low active. This bit is cl ear ed to zer o when

the chip is reset by the RESETN pin.

3.10 PORT B CONTROL 1: ADDRESS 0B HEX - READ/WRITE

DATA BUS WIDTH:

A one makes the Port B data bus 16 bits wide, with data tra nsferred on t he DB[15:0] pins . A zero makes

the Port B data bus 8 bits wide, with data transferred on the DB[7:0] pins. This bit should only be

changed afte r the reset code ha s been programmed to the DCLZ Control bits in the DCLZ Control

register. This bit is undefined when the chip is reset from the RESETN pin.

DATA15TO8:

The DATA 15TO8 bit causes one byt e to be transferr ed on DB[15:8] on th e next DMA cycle in to or out

of Port B, when Port B is in 16 bit mode. The intended use of this bit is to transfer a single byte on

DB[15:8] only during the first DMA cycle of a c ontiguous data trans fer sequence. The DATA15T O8 bit

only functions when Port B is in 16 bit mode, and is ignored when Port B is in 8 bit mode. The

DATA15TO8 bit should only be changed after the reset code has been programmed into the DCLZ

Control bits in the DCLZ Control register, or after the chip has paused after end of record, or after the

chip has paused be cause the Port A or Por t B end of transf er inter rupt has occurred . DATA15TO8 ta kes

effect only on the ne xt DMA cycle, which is defined as the next occurrence when DACKB pulses active,

and is supported when Port B is a DMA bus mast er or a DMA bus slave. After th e DMA c ycl e occurs,

the DA TA15TO8 bit is automa tically cleared. DATA15TO8 i s cleared to zero when the chi p is reset from

the RESETN pin.

res - Reserved. Bit must always be written with a zero. It reads back a zero.

ENABLE PORT B COMPARATOR:

A one enables the comparison of the Port B Byte Count register with the Port B Byte Comparator

register, allowing the Port B Comparator Interrupt to be set and the chip to pause. A zero disables the Port

B Byte Comparator register and prohibits the Port B Comparator Interrupt.

CLEAR INTERFACE:

Writi ng a one creat es a pulse , which clea rs the Por t B Interfac e. W rit ing a zer o has no ef fect on the Port

B Interface. This bit is always zero when it is read. This bit is intended to be used in Port B slave input

or output and master o utput mo des. The CL EAR INTERFACE bit is intended to be used onl y when the

chip has paused after end of rec ord, or paused becaus e the Port A or Port B end of transfe r has occurred.

CLEAR BYTE COUNTER:

Writi ng a on e c rea tes a pulse, which clear s the Port B Byte Count register. Wr it ing a zero has no ef fe ct

on the Port B Byte Count register. This bit is always zero when it is read.

ENABLE PARITY:

A one enables parity on DBPTY[1:0] when Port B is in 16 bit mode, and on DBPTY[0] when Port B is

in 8 bit mode. Writing a zero disables parity on Port B. This bit is undefined when the chip is reset from

the RESETN pin.

ODD PARITY:

A one selects odd parity on Port B. A zero selec ts even pari ty on Port B. This bit is unde fined when the

chip is reset from the RESETN pin.

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

0x0B

DATA

BUS

WIDTH

DATA15T O8

res

ENABLE

PORT B

COMP ARATOR

CLEAR

INTERF ACE

CLEAR

BYTE

COUNTER

ENABLE

PARITY

ODD

PARITY

Page 25

Page 20 of 45 PS3210B-1299

Advanced Hardware Architectures, Inc.

3.11 PORT B STATUS: ADDRESS 0C HEX - READ ONLY

res -Reserved. Bit must always be written with a zero. It reads back a zero.

DATA7TO0:

When Port B is in 16 bit mode, the DATA7TO0 bit shows whether the last DMA cycle of a data transfer

sequence out of Port B contains one or two valid bytes. This occurs for the last byte of the last record,

as determined by the Record Count register. If the last byte of the last record is the first byte in the

sequence to output a word, that byte is output on DB[7:0], the data on DB[15:8] is undefined, and the

DATA7TO0 bit is set. If the last byte of the last record is the second byte in the sequence to output a

word, the second to last byte is output on DB[7:0], the last byte is output on DB[15:8], and the

DATA7 TO0 bit is clear ed. The DATA7TO0 bit is clear ed during al l DMA cycles into P ort B, during all

DMA cycles when Port B is in 8 bit mode, and when the chip is reset from the RESETN pin.

EOR COUNT[1:0]:

The EOR COUNT[1:0] bits show the number of bytes wit h act iv e end of reco rd fl ags contained in the

Port B Interface. These bits operate in compression, compression flush, pass through A to B modes.

These bits are cleared to zero when a one is written to the CLEAR INTERFACE bit in Port B Control

1 register , or when the re set or decompres sion or decompressi on output disa bled or pass thr ough B to A

code is programmed to the DCLZ MODE bits in the DCLZ Control register, or when the chip is reset

by the RESETN pin. During data tra nsfer s, these bits s hould onl y be rea d when the PAUSED bit in the

DCLZ Status register is a one.

INTERFACE BYTE COUNT[3:0]:

The INTERFACE BYTE COUNT[3:0] bits show the number of bytes that are held in the Port B

Interface. These bi ts are cleared to zero when a one is writt en to t he CLEAR INTERFACE bit in Port B

Control 1 register , or when th e reset code is progra mmed to the DCLZ MODE bits in the DCLZ Control

register , or when the chip is reset by the RESETN pin. During data tra nsf er s, these bits should only be

read when the PAUSED bit in the DCLZ Status register is a one.

3.12 PORT B BYTE COUNT: ADDRESS 0D,0E,0F HEX - READ/WRITE

Least Significant Byte (address 0D hex):

Middle Byte (address 0E hex):

Most Significant Byte (address 0F hex):

The Port B Byte Count register counts the number of bytes t hat are transferre d by the Port B DMA State

Machine. This register counts in compression, compression flush, decompression, decompression output

disabled, pass through A to B, and pass through B to A modes. The regi ster is clear ed to zero when a one is

written to the CLEAR BYTE COUNTER bit in Port B Control 1 register, or when the chip is reset by the

RESETN pin. During data transfers, this registe r should only be written or read when the PAUSED bit in the