Page 1

High Performance,

V

Data Sheet

FEATURES

Complete rate gyroscope on a single chip

±300°/sec angular rate sensing

Ultrahigh vibration rejection: 0.01°/sec/g

Excellent 16°/hour null bias stability

Internal temperature compensation

2000 g powered shock survivability

SPI digital output with 16-bit data-word

Low noise and low power

3.3 V to 5 V operation

−40°C to +105°C operation

Ultrasmall, light, and RoHS compliant

Two package options

Low cost SOIC_CAV package for yaw rate (z-axis) response

Innovative ceramic vertical mount package (LCC_V) for

pitch and roll response

APPLICATIONS

Rotation sensing in high vibration environments

Rotation sensing for industrial and instrumentation

applications

High performance platform stabilization

Digital Output Gyroscope

ADXRS453

GENERAL DESCRIPTION

The ADXRS453 is an angular rate sensor (gyroscope) intended

for industrial, instrumentation, and stabilization applications in

high vibration environments. An advanced, differential, quad

sensor design rejects the influence of linear acceleration, enabling

the ADXRS453 to offer high accuracy rate sensing in harsh

environments where shock and vibration are present.

The ADXRS453 uses an internal, continuous self-test architecture. The integrity of the electromechanical system is checked by

applying a high frequency electrostatic force to the sense structure

to generate a rate signal that can be differentiated from the baseband rate data and internally analyzed.

The ADXRS453 is capable of sensing an angular rate of up to

±300°/sec. Angular rate data is presented as a 16-bit word that

is part of a 32-bit SPI message.

The ADXRS453 is available in a 16-lead plastic cavity SOIC

(SOIC_CAV) and an SMT-compatible vertical mount package

(LCC_V), and is capable of operating across a wide voltage

range (3.3 V to 5 V).

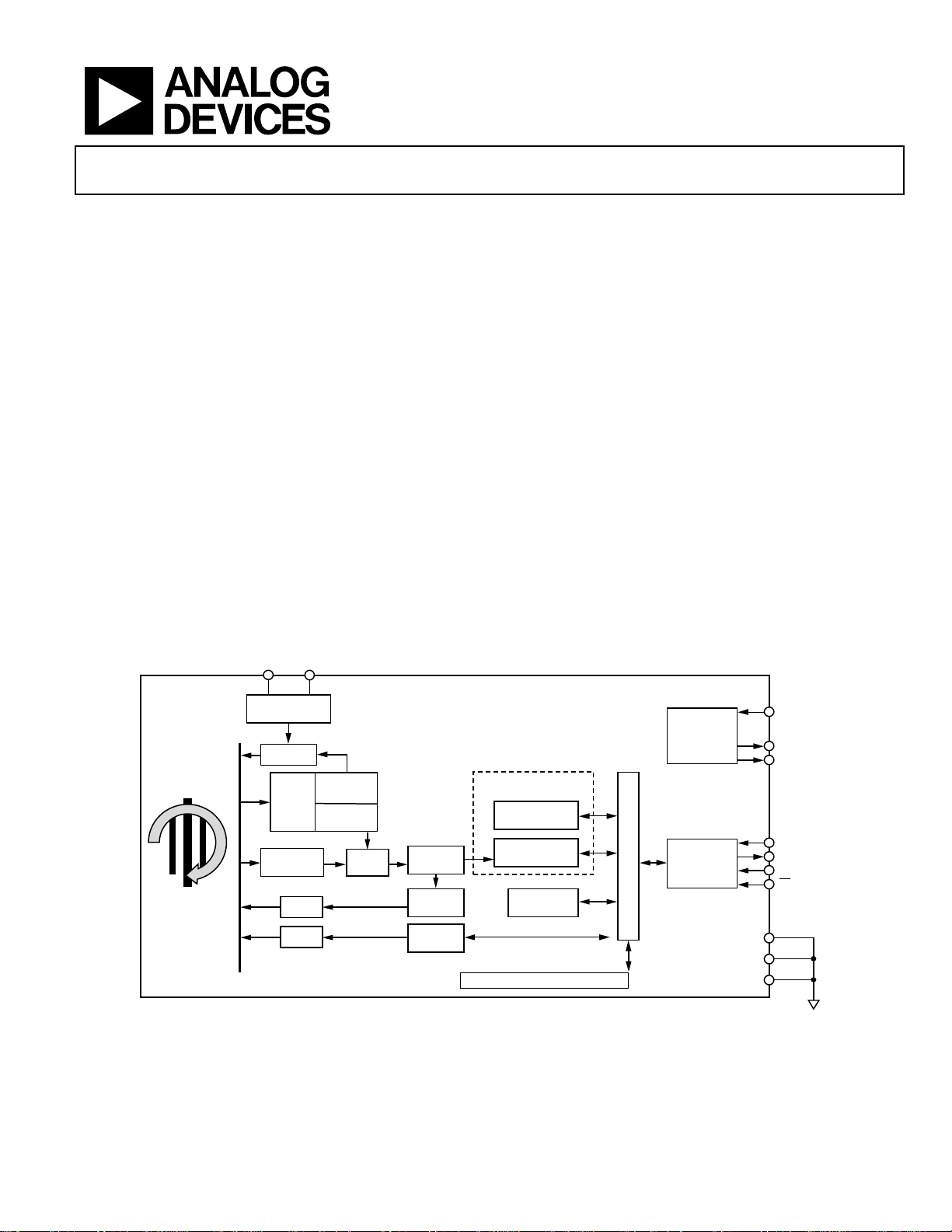

FUNCTIONAL BLOCK DIAGRAM

CP5

HIGH VO LTAG E

GENERATION

Z-AXIS ANGULAR

RATE SENSOR

HV DRIVE

PHASE-

LOCKED

LOOP

BAND-PASS

FILTER

Q DAQ

P DAQ

X

CLOCK

DIVIDER

AMPLITUDE

DETECT

12-BIT

ADC

DEMOD

Q FILTER

SELF-TEST

CONTROL

ADXRS453

ARITHMETIC

LOGIC UNIT

DECIMATION

TEMPERATURE

CALIBRATIO N

Figure 1.

FILTER

FAULT

DETECT ION

EEPROM

REGISTERS/MEMORY

LDO

REGULATOR

SPI

INTERFACE

P

DD

DV

DD

AV

DD

MOSI

MISO

SCLK

CS

DV

SS

P

SS

AV

SS

09155-001

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

Page 2

ADXRS453 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 4

Thermal Resistance ...................................................................... 4

Rate Sensitive Axis ....................................................................... 4

ESD Caution .................................................................................. 4

Pin Configurations and Function Descriptions ........................... 5

Typical Performance Characteristics ............................................. 7

Theory of Operation ........................................................................ 9

Continuous Self-Test .................................................................... 9

Mechanical Performance ............................................................... 10

Noise Performance ......................................................................... 11

Applications Information .............................................................. 12

Calibrated Performance ............................................................. 12

Mechanical Considerations for Mounting .............................. 12

Application Circuits ................................................................... 12

ADXRS453 Signal Chain Timing ............................................. 13

SPI Communication Protocol ....................................................... 14

Command/Response ................................................................. 14

Device Data Latching ................................................................. 15

SPI Timing Characteristics ....................................................... 16

Command/Response Bit Definitions ....................................... 17

Fault Register Bit Definitions ................................................... 18

Recommended Start-Up Sequence with CHK Bit

Assertion ...................................................................................... 20

Rate Data Format ............................................................................ 21

Memory Map and Registers .......................................................... 22

Memory Map .............................................................................. 22

Memory Register Definitions ................................................... 23

Package Orientation and Layout Information ............................ 25

Solder Profile............................................................................... 26

Package Marking Codes ............................................................ 27

Outline Dimensions ....................................................................... 28

Ordering Guide .......................................................................... 29

REVISION HISTORY

12/11—Rev. A to Rev. B

Changes to Features Section............................................................ 1

Changes to Rate Sensitive Axis Section ......................................... 4

Deleted Endnote 1, Table 3 .............................................................. 4

Deleted Figure 5; Renumbered Sequentially ................................. 6

Changes to Figure 4 .......................................................................... 6

Changes to Figure 32 ...................................................................... 25

Deleted Figure 36 ............................................................................ 26

6/11—Rev. 0 to Rev. A

Changes to Bit 30 and Bit 31 in Table 9 ....................................... 14

Updated Outline Dimensions ....................................................... 29

Changes to Ordering Guide .......................................................... 30

1/11—Revision 0: Initial Version

Rev. B | Page 2 of 32

Page 3

Data Sheet ADXRS453

SPECIFICATIONS

TA = T

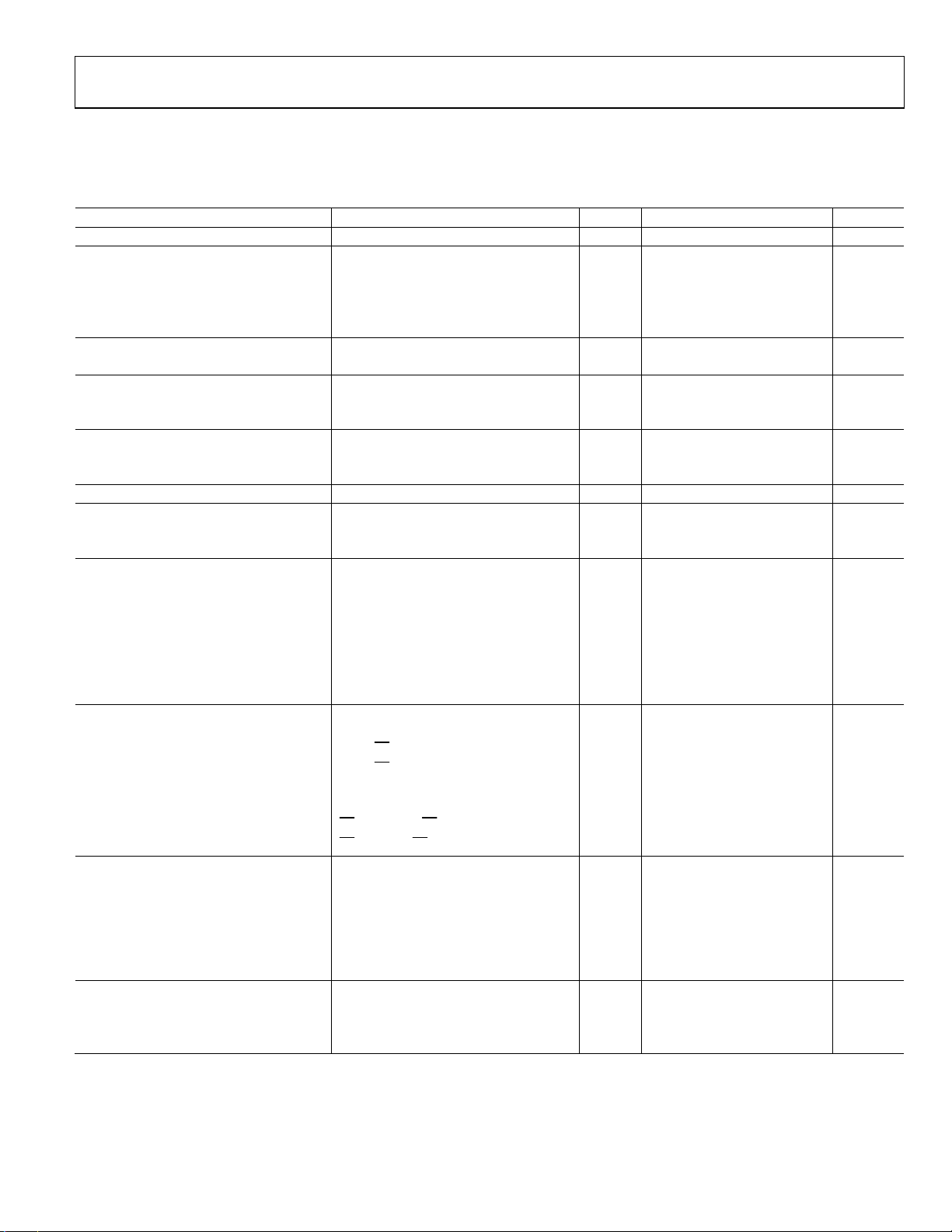

Table 1.

Parameter Test Conditions/Comments Symbol Min Typ Max Unit

MEASUREMENT RANGE Full-scale range FSR ±300 ±400 °/sec

SENSITIVITY

NULL ACCURACY TA = 25°C ±0.4 °/sec

NOISE PERFORMANCE

T

LOW-PASS FILTER

SENSOR RESONANT FREQUENCY f0 13 15.5 19 kHz

SHOCK AND VIBRATION IMMUNITY

SELF-TEST

SPI COMMUNICATIONS

MEMORY REGISTERS

POWER SUPPLY

1

Maximum limit is guaranteed by Analog Devices, Inc., characterization.

2

Cross-axis sensitivity specification does not include effects due to device mounting on a printed circuit board (PCB).

3

Minimum and maximum limits are guaranteed by design.

MIN

to T

, PDD = 5 V, angular rate = 0°/sec, bandwidth = f0/200 (~77.5 Hz), ±1 g, continuous self-test on.

MAX

See

Figure 2

Nominal Sensitivity 80 LSB/°/sec

Sensitivity Tolerance TA = −40°C to +105°C −3 +3 %

Nonlinearity1 Best fit straight line 0.05 % FSR rms

Cross-Axis Sensitivity2 −3 +3 %

T

= −40°C to +105°C ±0.5 °/sec

A

Rate Noise Density TA = 25°C 0.015 °/sec/√Hz

= 105°C 0.023 °/sec/√Hz

A

Cutoff (−3 dB) Frequency f0/200 fLP 77.5 Hz

Group Delay3 f = 0 Hz tLP 3.25 4 4.75 ms

Sensitivity to Linear Acceleration DC to 5 kHz 0.01 °/sec/g

Vibration Rectification 0.0002 °/sec/g2

See the

Continuous Self-Test section

Magnitude 2559 LSB

Fault Register Threshold Compared to LOCSTx register data 2239 2879 LSB

Sensor Data Status Threshold Compared to LOCSTx register data 1279 3839 LSB

Frequency f0/32 fST 485 Hz

ST Low-Pass Filter

Cutoff (−3 dB) Frequency f0/8000 1.95 Hz

Group Delay3 52 64 76 ms

Clock Frequency 8.08 MHz

Voltage Input High

Voltage Input Low

MOSI,

MOSI,

CS

CS

, SCLK

, SCLK

0.85 × P

−0.3 P

PDD + 0.3 V

DD

× 0.15 V

DD

Voltage Output Low MISO, current = 3 mA 0.5 V

Voltage Output High MISO, current = −2 mA PDD − 0.5 V

Pull-Up Current

CS

, PDD = 3.3 V, CS = PDD × 0.15

CS

, PDD = 5 V, CS = PDD × 0.15

See the

Memory Register Definitions

60 200 μA

80 300 μA

section

Temperature Register

Value at 45°C 0 LSB

Scale Factor 5 LSB/°C

Quadrature, Self-Test, and Rate Registers

Scale Factor 80 LSB/°/sec

Supply Voltage PDD 3.15 5.25 V

Quiescent Supply Current IDD 6.0 8.0 mA

Turn-On Time Power-on to 0.5°/sec of final value 100 ms

Rev. B | Page 3 of 32

Page 4

ADXRS453 Data Sheet

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Acceleration (Any Axis, 0.5 ms)

Unpowered 2000 g

Powered 2000 g

Supply Voltage (PDD) −0.3 V to +6.0 V

Output Short-Circuit Duration

Indefinite

(Any Pin to Ground)

Operating Temperature Range

LCC_V Package −55°C to +125°C

SOIC_CAV Package −40°C to +125°C

Storage Temperature Range

LCC_V Package −65°C to +150°C

SOIC_CAV Package −40°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, for a device

soldered in a printed circuit board (PCB) for surface-mount

packages.

Table 3. Thermal Resistance

Package Type θJA θJC Unit

16-Lead SOIC_CAV (RG-16-1) 191.5 25 °C/W

14-Lead Ceramic LCC_V (EY-14-1) 185.5 23 °C/W

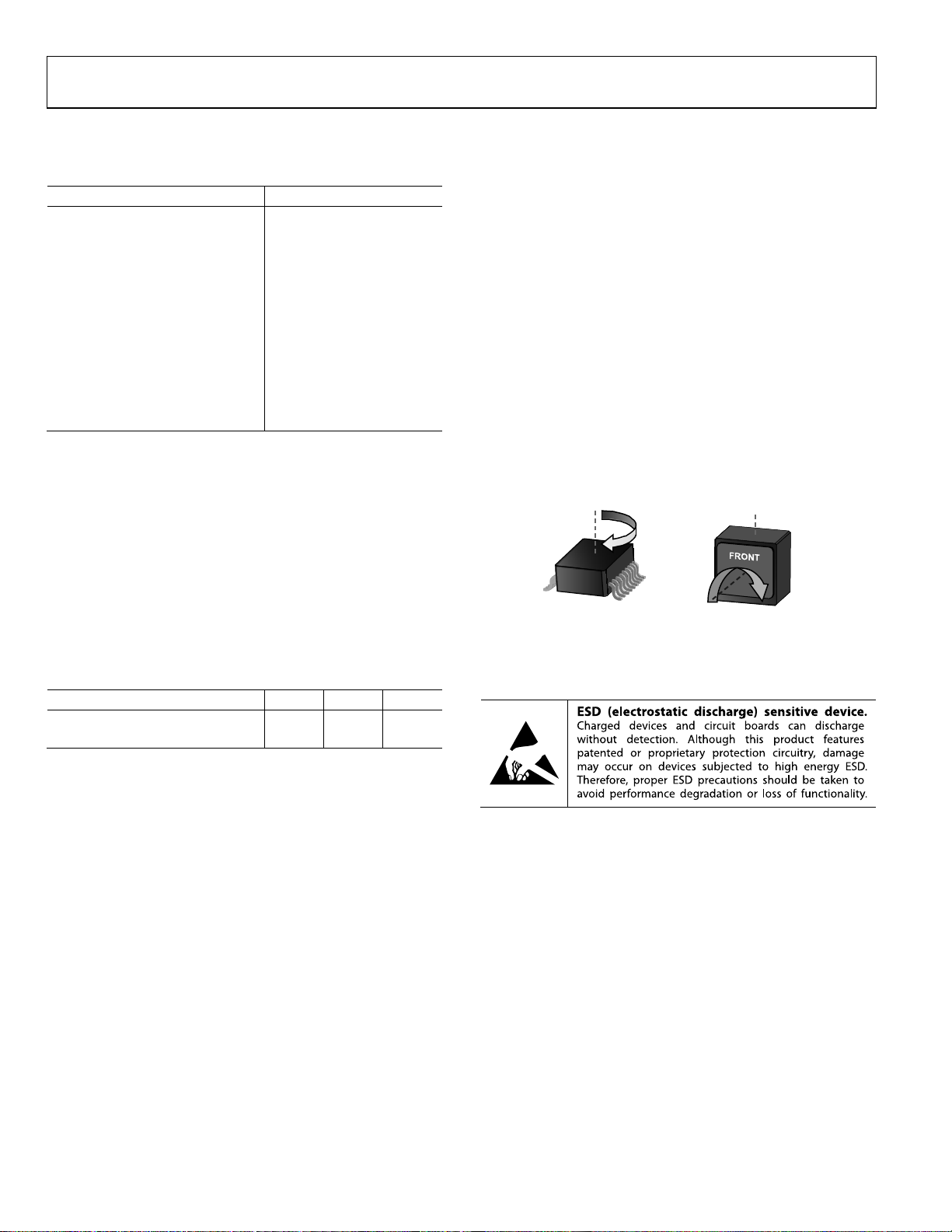

RATE SENSITIVE AXIS

The ADXRS453 is available in two package options.

The SOIC_CAV package is for applications that require

z-axis (yaw) rate sensing.

The LCC_V (vertical mount) package is for applications

that require x-axis or y-axis (pitch or roll) rate sensing.

The package has terminals on two faces. However, the terminals on the back are for internal evaluation only and should

not be used in the end application. The terminals on the

bottom of the package incorporate metallization bumps

that ensure a minimum solder thickness for improved solder

joint reliability. These bumps are not present on the back

terminals and, therefore, poor solder joint reliability can be

encountered if the back terminals are used in the end

application. For the outline dimensions of this package, see

Figure 38.

RATE

AXIS

+

16

RATE

SOIC PACKAGE

9

Figure 2. Rate Signal Increases with Clockwise Rotation

AXIS

Z-AXIS

+

LCC_V PACKAGE

09155-002

ESD CAUTION

Rev. B | Page 4 of 32

Page 5

Data Sheet ADXRS453

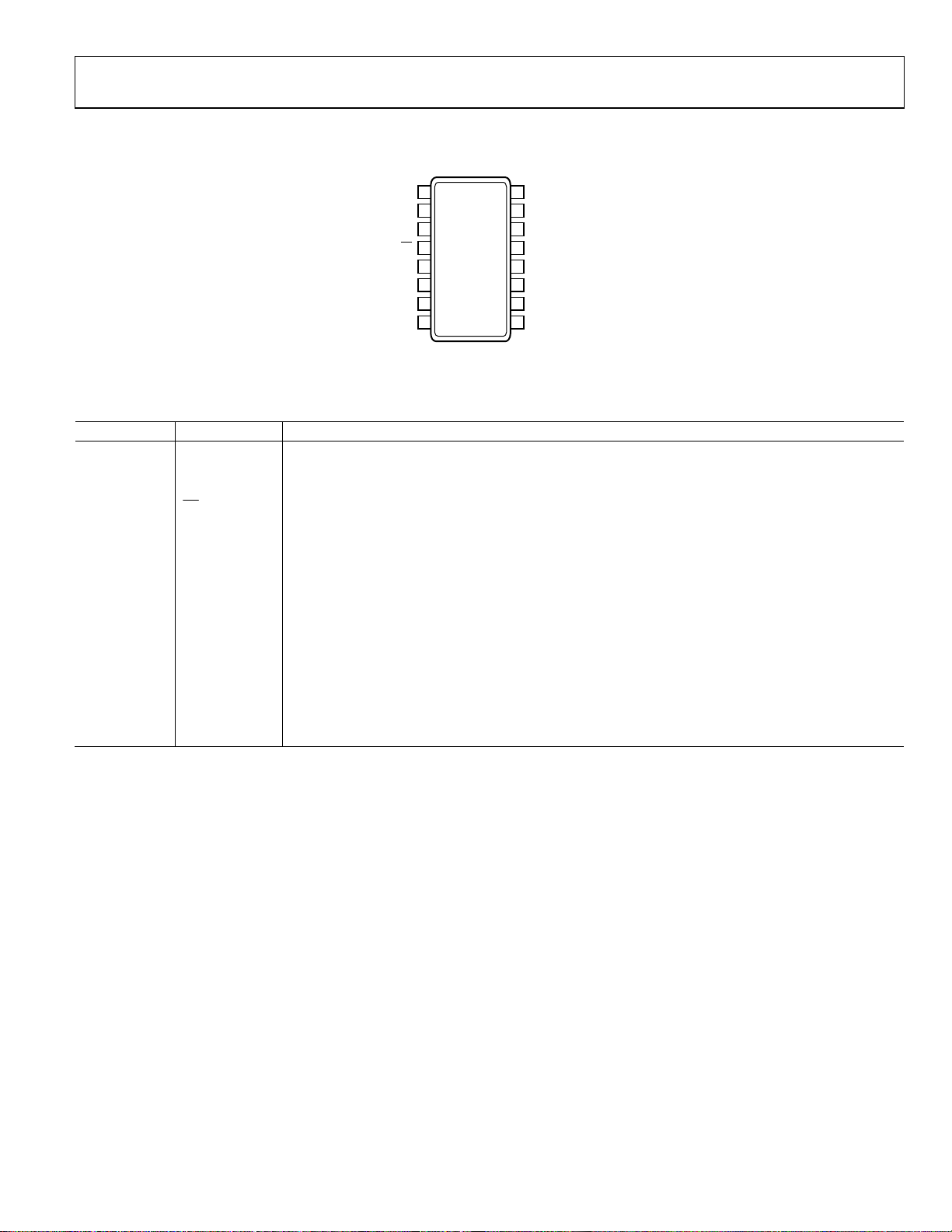

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

DV

RSVD

RSVD

CS

MISO

P

P

DD

DD

SS

V

X

1

2

3

ADXRS453

4

TOP VIEW

(Not to Scale)

5

6

7

8

16

SCLK

15

MOSI

14

AV

DD

13

DV

SS

12

RSVD

11

AV

SS

10

RSVD

9

CP5

09155-003

Figure 3. Pin Configuration, 16-Lead SOIC_CAV

Table 4. Pin Function Descriptions, 16-Lead SOIC_CAV

Pin No. Mnemonic Description

1 DVDD Digital Regulated Voltage. See Figure 25 for the application circuit diagram.

2 RSVD Reserved. This pin must be connected to DVSS.

3 RSVD Reserved. This pin must be connected to DVSS.

4

CS

Chip Select.

5 MISO Master In/Slave Out.

6 PDD Supply Voltage.

7 PSS Switching Regulator Ground.

8 VX High Voltage Switching Node. See Figure 25 for the application circuit diagram.

9 CP5 High Voltage Supply. See Figure 25 for the application circuit diagram.

10 RSVD Reserved. This pin must be connected to DVSS.

11 AVSS Analog Ground.

12 RSVD Reserved. This pin must be connected to DVSS.

13 DVSS Digital Signal Ground.

14 AVDD Analog Regulated Voltage. See Figure 25 for the application circuit diagram.

15 MOSI Master Out/Slave In.

16 SCLK SPI Clock.

Rev. B | Page 5 of 32

Page 6

ADXRS453 Data Sheet

PDDPSSMOSI

14 13 12 11 10 9 8

1234567

SS

AV

NOTES

1. THE PACKAGE HAS T ERMINALS ON TWO FACES. HO WEVER, THE TERM INALS ON

THE BACK ARE FO R INTERNAL EVALUATI ON ONLY AND SHOULD NO T BE USED IN

THE END APPL ICATIO N. THE T ERMINALS ON THE BOT TOM O F THE PACKAG E

INCORPORAT E METAL LIZAT ION BUMPS THAT ENSURE A MINIMUM SOLDER

THICKNESS FOR IMPROVED SOLDER JOINT RELIABILITY. THESE BUMPS ARE

NOT PRESENT ON THE BACK TERMINAL S AND, THEREFORE, P OOR SOL DER

JOINT REL IABILI TY CAN BE ENCOUNT ERED IF TH E BACK TERMINALS ARE USED

IN THE END APPLICATI ON. FO R THE OUT LINE DI MENSIONS OF THI S PACKAGE,

SEE FIGURE 38.

DVSSCS

DD

DD

AV

MISO

DV

TOP VIEW

(Not to Scale)

SCLK

VXRSVD

CP5

RSVD

09155-004

Figure 4. Pin Configuration, 14-Terminal LCC_V

Table 5. Pin Function Descriptions, 14-Terminal LCC_V

Pin No. Mnemonic Description

1 AVSS Analog Ground.

2 AVDD Analog Regulated Voltage. See Figure 26 for the application circuit diagram.

3 MISO Master In/Slave Out.

4 DVDD Digital Regulated Voltage. See Figure 26 for the application circuit diagram.

5 SCLK SPI Clock.

6 CP5 High Voltage Supply. See Figure 26 for the application circuit diagram.

7 RSVD Reserved. This pin must be connected to DVSS.

8 RSVD Reserved. This pin must be connected to DVSS.

9 VX High Voltage Switching Node. See Figure 26 for the application circuit diagram.

10

CS

Chip Select.

11 DVSS Digital Signal Ground.

12 MOSI Master Out/Slave In.

13 PSS Switching Regulator Ground.

14 PDD Supply Voltage.

Rev. B | Page 6 of 32

Page 7

Data Sheet ADXRS453

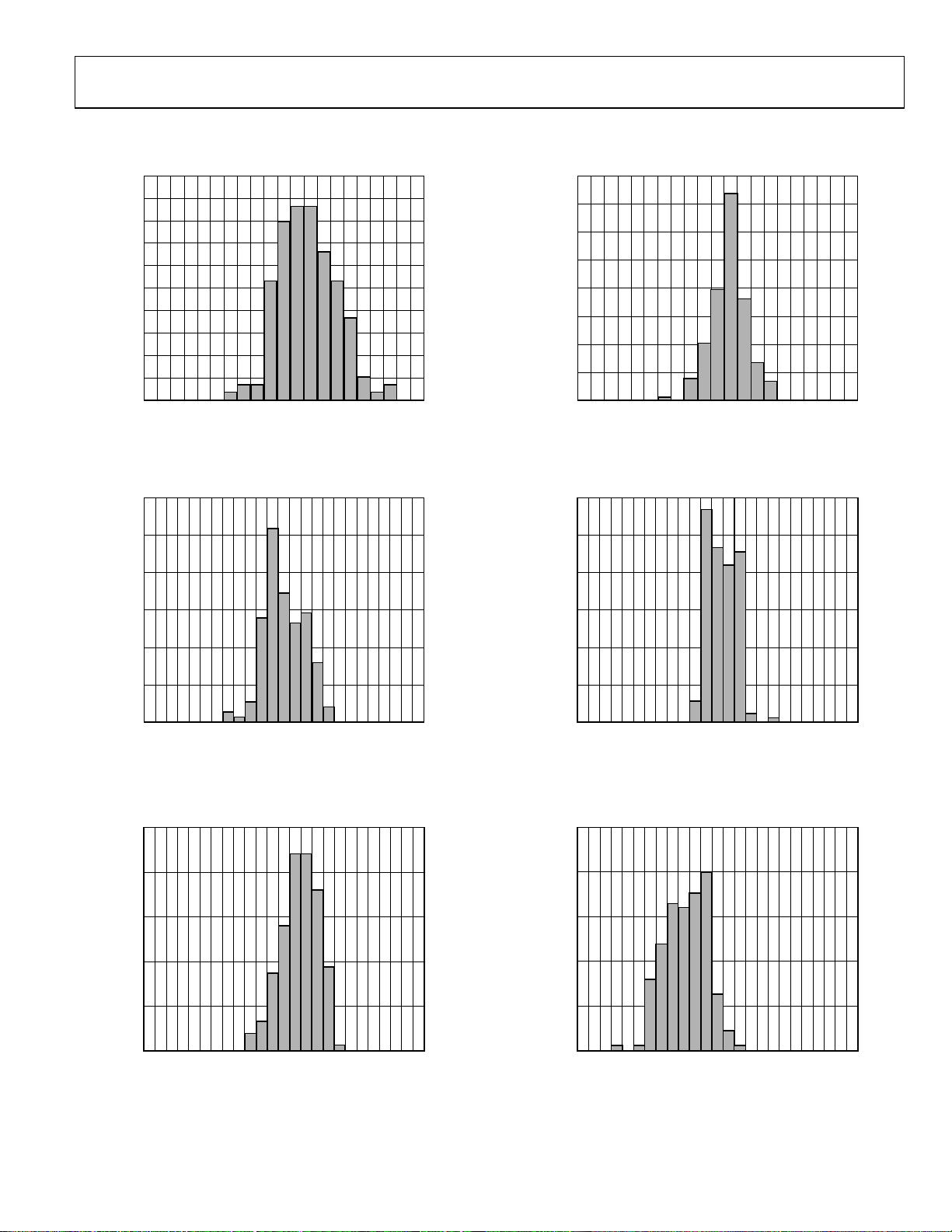

TYPICAL PERFORMANCE CHARACTERISTICS

20

18

16

14

12

10

8

6

4

PERCENT OF POPULATION (%)

2

0

–2.0 –1.6 –1.2 –0.8 –0.4 0 2.01.61.20.80.4

ERROR (°/sec)

Figure 5. SOIC_CAV Null Accuracy at 25°C

09155-006

40

35

30

25

20

15

10

PERCENT OF POPULATION (%)

5

0

–2.0 –1.6 –1.2 –0.8 –0.4 0 2.01.61.20.80.4

ERROR (°/sec)

Figure 8. LCC_V Null Accuracy at 25°C

09155-009

30

25

20

15

10

PERCENT OF POPUL ATION (%)

5

0

–2.5

–2.0

–3.0

–1.5

–1.0

–0.5

ERROR (°/sec)

0

Figure 6. SOIC_CAV Null Drift over Temperature

25

20

15

30

25

20

15

10

PERCENT OF POPUL ATION (%)

5

0

0.5

1.0

1.5

2.0

2.5

3.0

09155-007

–2.5

–2.0

–3.0

–1.5

–0.5

–1.0

ERROR (°/ sec)

0

1.5

1.0

0.5

3.0

2.5

2.0

09155-010

Figure 9. LCC_V Null Drift over Temperature

25

20

15

PERCENT OF POPULATION (%)

10

5

0

–0.030

–0.025

–0.020

–0.015

–0.010

–0.005

CHANGE IN SENSI TIVITY (%)

Figure 10. LCC_V Sensitivity Error at 25°C

0

0.030

0.025

0.020

0.015

0.010

0.005

09155-011

10

5

PERCENT OF POPULATIO N (%)

0

–3.0

–2.5

–2.0

–1.5

CHANGE IN SENSI TIVITY (%)

0

0.5

1.0

1.5

2.0

2.5

–1.0

–0.5

3.0

09155-008

Figure 7. SOIC_CAV Sensitivity Error at 25°C

Rev. B | Page 7 of 32

Page 8

ADXRS453 Data Sheet

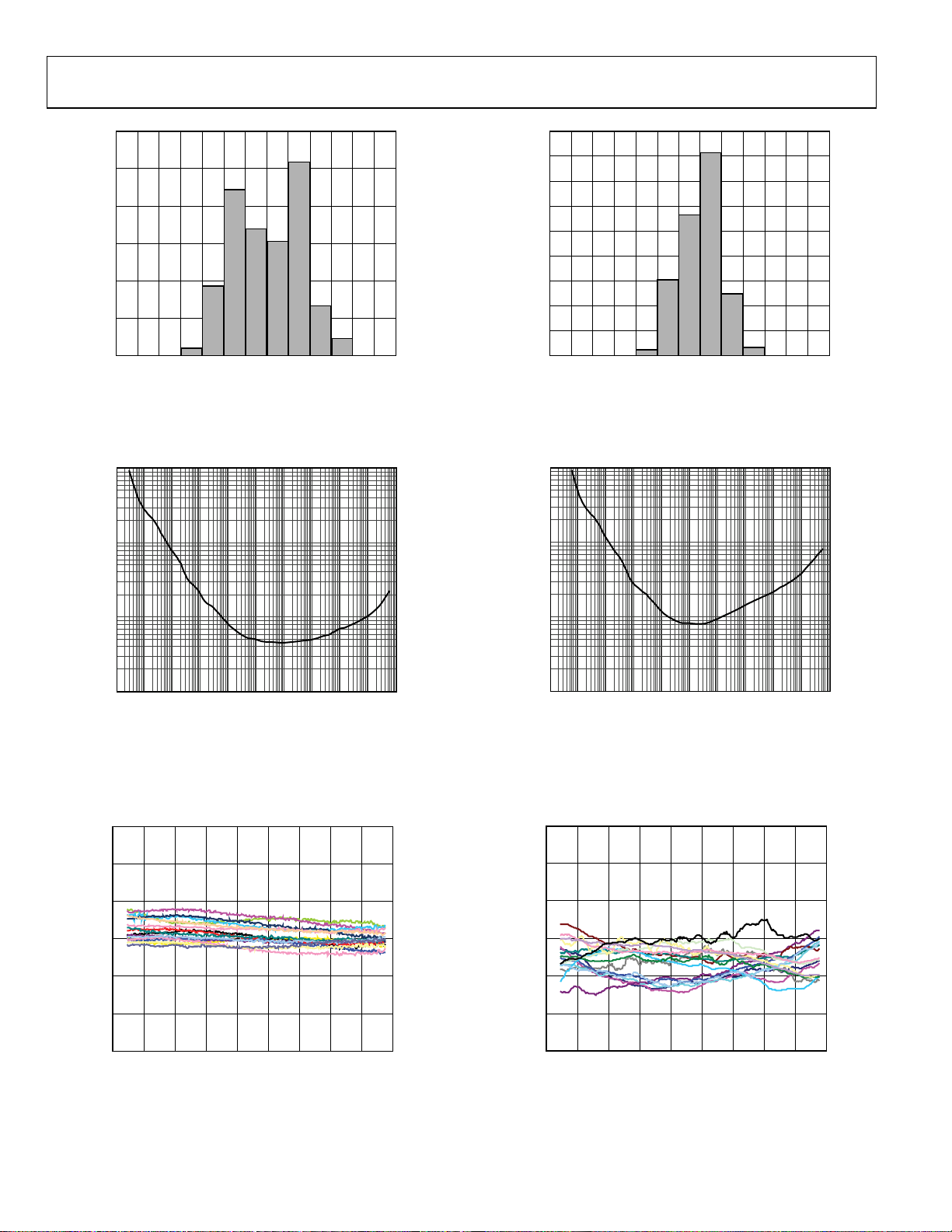

30

25

20

15

10

PERCENT OF POPULATION (%)

5

0

–3 –2 –1

0

ERROR (%)

Figure 11. SOIC_CAV Sensitivity Drift over Temperature

321

09155-012

45

40

35

30

25

20

15

10

PERCENT OF POPULAT ION (%)

5

0

–3 –2 –1

0

ERROR (%)

Figure 14. LCC_V Sensitivity Drift over Temperature

321

09155-015

ROOT ALL AN VARIANCE (°/ sec)

0.001

1

0.1

0.01

0.01

0.001

0.0001

0.00001

0.0000001

0.000001

AVERAGING TIME (Hours)

Figure 12. Typical Root Allan Variance at 40°C

3

2

1

1

0.1

0.01

ROOT ALL AN VARIANCE (°/ sec)

1

0.1

10

100

1000

09155-013

0.001

0.0000001

0.01

0.001

0.0001

0.00001

0.000001

AVERAGING TIME (Hours)

1

0.1

10

100

1000

09155-016

Figure 15. Typical Root Allan Variance at 105°C

3

2

1

0

–1

NULL OUTPUT (°/sec)

–2

–3

–50 –30 –10 10 30 50 70 90 110 130

TEMPERATURE (°C)

Figure 13. Null Output over Temperature, 16 Devices Soldered on PCB

09155-014

Rev. B | Page 8 of 32

0

ERROR (%)

–1

–2

–3

–50 –30 –10 10 30 50 70 90 110 130

TEMPERATURE (°C)

Figure 16. Sensitivity over Temperature, 16 Devices Soldered on PCB

09155-017

Page 9

Data Sheet ADXRS453

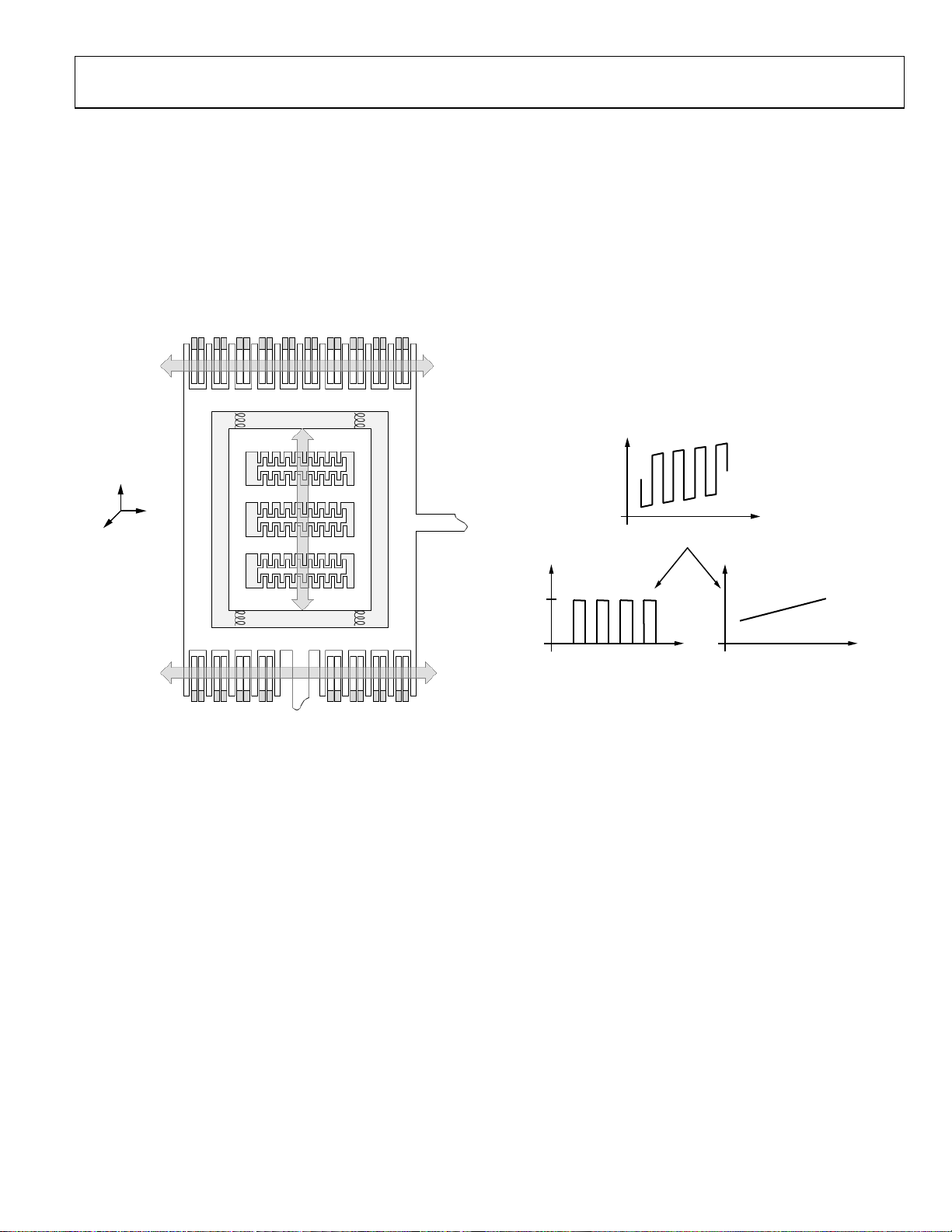

THEORY OF OPERATION

The ADXRS453 operates on the principle of a resonator gyroscope.

Figure 17 shows a simplified version of one of four polysilicon

sensing structures. Each sensing structure contains a dither frame

that is electrostatically driven to resonance. This produces the

necessary velocity element to produce a Coriolis force when the

device experiences angular rate. In the SOIC_CAV package, the

ADXRS453 is designed to sense a z-axis (yaw) angular rate; the

LCC_V vertical mount package orients the device such that it

can sense pitch or roll angular rate on the same PCB.

X

Y

Z

CONTINUOUS SELF-TEST

The ADXRS453 gyroscope implements a complete electromechanical self-test. An electrostatic force is applied to the

gyroscope frame, resulting in a deflection of the capacitive sense

fingers. This deflection is exactly equivalent to deflection that

occurs as a result of external rate input. The output from the

beam structure is processed by the same signal chain as a true

rate output signal, providing complete coverage of both the

electrical and mechanical components.

The electromechanical self-test is performed continuously

during operation at a rate higher than the output bandwidth of

the device. The self-test routine generates equivalent positive

and negative rate deflections. This information can then be

filtered with no overall effect on the demodulated rate output.

RATE SIGNAL WITH

CONTINUOUS SELF-T EST SIGNAL.

Figure 17. Simplified Gyroscope Sensing Structure

When the sensing structure is exposed to angular rate, the

resulting Coriolis force couples into an outer sense frame,

which contains movable fingers that are placed between fixed

pickoff fingers. This forms a capacitive pickoff structure that

senses Coriolis motion. The resulting signal is fed to a series of

gain and demodulation stages that produce the electrical rate

signal output. The quad sensor design rejects linear and angular

acceleration, including external g-forces and vibration. This is

achieved by mechanically coupling the four sensing structures

such that external g-forces appear as common-mode signals

that can be removed by the fully differential architecture

implemented in the ADXRS453.

The resonator requires 22.5 V (typical) for operation. Because

only 5 V is typically available in most applications, a switching

regulator is included on chip.

SELF-TEST AMPLITUDE.

INTERNALL Y COMPARED

TO THE SPECIFICATION

09155-018

TABLE LI MITS.

Figure 18. Continuous Self-Test Demodulation

LOW FREQUENCY RATE

INFORMAT ION.

The difference amplitude between the positive and negative

self-test deflections is filtered to f

/8000 (~1.95 Hz) and is

0

continuously monitored and compared to hard-coded self-test

limits. If the measured amplitude exceeds these limits (listed in

Table 1), one of two error conditions is asserted, depending on

the magnitude of the self-test error.

For less severe self-test error magnitudes, the CST bit of the

fault register is asserted. However, the status bits (ST[1:0])

in the sensor data response remain set to 01 for valid

sensor data.

For more severe self-test errors, the CST bit of the fault

register is asserted and the status bits (ST[1:0]) in the

sensor data response are set to 00 for invalid sensor data.

Table 1 lists the thresholds for both of these failure conditions.

If desired, the user can access the self-test information by issuing

a read command to the self-test memory register (Address 0x04).

See the SPI Communication Protocol section for more information about error reporting.

09155-019

Rev. B | Page 9 of 32

Page 10

ADXRS453 Data Sheet

(

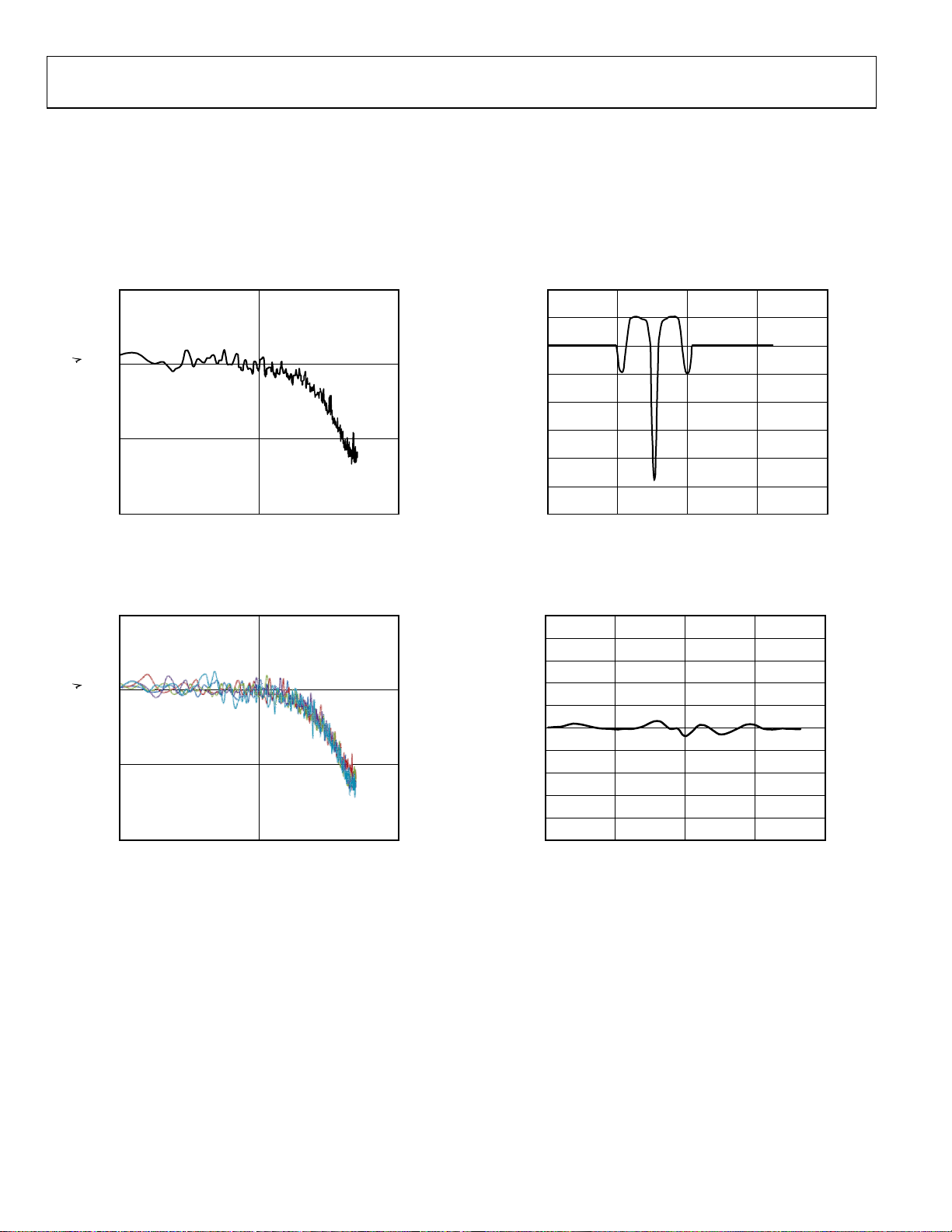

MECHANICAL PERFORMANCE

The ADXRS453 has excellent shock and vibration rejection.

Figure 19 shows the output noise response of the ADXRS453 in

a vibration free environment. Figure 20 shows the response of

the same device to 15 g rms random vibration (50 Hz to 5 kHz).

As shown in Figure 20, no frequencies are particularly sensitive

to vibration. Response to vibration in all axes is similar.

0.1

0.01

Shock response is also excellent, as shown in Figure 21 and

Figure 22. Figure 21 shows a 99 g input stimulus applied to

each axis, and Figure 22 shows the typical response to this

shock in each axis. Shock response of 0.01°/sec/g is apparent.

40

20

0

g)

–20

–40

0.001

GYRO OUTPUT (°/sec/ Hz)

0.0001

5 50 500

FREQUENCY (Hz)

Figure 19. ADXRS453 Output Noise Response with No Vibration Applied

0.1

0.01

0.001

GYRO OUTPUT (°/sec/ Hz)

0.0001

5 50 500

FREQUENCY (Hz)

Figure 20. ADXRS453 Output Noise Response with 15 g RMS Random

Vibration (50 Hz to 5 kHz) Applied

–60

INPUT STIMULUS

–80

–100

–120

00.100.05 0.15 0.20

09155-020

TIME (Seconds)

09155-022

Figure 21. 99 g Shock Input

10

8

6

4

2

0

–2

–4

GYRO OUTPUT (°/sec)

–6

–8

–10

00.100.05 0.15 0.20

09155-021

TIME (Seconds)

09155-023

Figure 22. Typical Output Response Due to 99 g Shock (see Figure 21)

Rev. B | Page 10 of 32

Page 11

Data Sheet ADXRS453

NOISE PERFORMANCE

The ADXRS453 noise performance is very consistent from

device to device and varies very predictably with temperature.

Table 6 contains statistical noise data at three temperature

points for a large population of ADXRS453 devices (more than

3000 parts from several manufacturing lots).

Table 6. Statistical Noise Data

Noise (°/sec/√Hz)

Te mp e ra tu r e

Mean Standard Deviation

−40°C 0.0109 0.0012

+25°C 0.0149 0.0015

+105°C 0.0222 0.0019

Noise increases fairly linearly with temperature, as shown in

Figure 23.

0.050

0.045

0.040

0.035

0.030

0.025

0.020

0.015

NOISE DENSITY (°/sec/ Hz)

0.010

0.005

0

–50 500 100 150

Figure 23. Noise Density vs. Temperature, 16 Devices

TEMPERATURE (° C)

09155-024

Rev. B | Page 11 of 32

Page 12

ADXRS453 Data Sheet

V

G

APPLICATIONS INFORMATION

CALIBRATED PERFORMANCE

The ADXRS453 gyroscope uses internal EEPROM memory to

store its temperature calibration information. The calibration

information is encoded into the device during factory test. The

calibration data is used to perform offset, gain, and self-test corrections over temperature. By storing this information internally,

the ADXRS453 eliminates the need for the customer to perform

system level temperature calibration.

MECHANICAL CONSIDERATIONS FOR MOUNTING

Mount the ADXRS453 in a location close to a hard mounting

point of the PCB. Mounting the ADXRS453 at an unsupported

PCB location (that is, at the end of a lever or in the middle of a

trampoline, as shown in Figure 24) can result in apparent measurement errors because the gyroscope is subject to the resonant

vibration of the PCB. Locating the gyroscope near a hard mounting

point helps to ensure that any PCB resonances at the gyroscope

are above the frequency at which harmful aliasing with the

internal electronics can occur. To ensure that aliased signals do

not couple into the baseband measurement range, design the

module so that the first system level resonance occurs at a

frequency higher than 800 Hz.

GYROSCOPE

PCB

MOUNTING POINTS

Figure 24. Incorrectly Placed Gyroscope

9155-025

1

DV

1µF

GND

3.3V TO 5V

1µF

470µH

GND

DD

RSVD

RSVD

CS

MISO

P

DD

P

SS

V

8

X

>24V BREAKDOWN

Figure 25. Recommended Application Circuit, SOIC_CAV Package

TOP VIEW

114

AV

1µF

1µF

100nF

ND

SS

AV

DD

MISO

DV

DD

SCLK

CP5

RSVD RSVD

DIODE

MOSI

DV

P

P

CS

V

SCLK

MOSI

AV

DV

RSVD

AV

RSVD

CP5

DD

SS

SS

X

16

1µF

DD

SS

SS

100nF

9

GND

09155-026

TO 5V

3.3

1µF

GND

470µH

APPLICATION CIRCUITS

Figure 25 and Figure 26 show the recommended application

circuits for the ADXRS453 gyroscope. These application circuits

provide a connection reference for the available package types.

Note that DV

ground through 1 F capacitors; do not connect these supplies

together. In addition, an external diode and inductor must be

connected for proper operation of the internal shunt regulator

(see Table 7). These components allow the internal resonator

drive voltage to reach its required level.

Table 7. Components for ADXRS453 Application Circuits

Component Qty Description

Inductor 1 470 H

Diode 1 >24 V breakdown voltage

Capacitor 3 1 F

Capacitor 1 100 nF

, AVDD, and PDD are all individually connected to

DD

Rev. B | Page 12 of 32

GND

DIODE

>24V BREAKDOWN

Figure 26. Recommended Application Circuit, LCC_V Package

09155-027

Page 13

Data Sheet ADXRS453

ADXRS453 SIGNAL CHAIN TIMING

The ADXRS453 primary signal chain is shown in Figure 27. The

signal chain is the series of necessary functional circuit blocks

through which the rate data is generated and processed. This

sequence of electromechanical elements determines how quickly

the device can translate an external rate input stimulus to an SPI

word that is sent to the master device.

The group delay, which is a function of the filter characteristic,

is the time required for the output of the low-pass filter to be

within 10% of the external rate input. In Figure 27, the group

delay is shown to be ~4 ms. Additional delay can be observed

due to the timing of SPI transactions and the population of the

rate data into the internal device registers. Figure 27 illustrates

this delay through each element of the signal chain.

PRIMARY SIGNAL CHAIN

The transfer function for the rate data LPF is given as

2

64

1

Z

1

1

Z

where:

11

T

(f

is the resonant frequency of the ADXRS453.)

0

f

0

(typ)kHz16

The transfer function for the continuous self-test LPF is given as

1

6364

Z

1

where:

T

f

0

is the resonant frequency of the ADXRS453.)

(f

0

GROUP DELAY

(typ)ms116

4ms

SPI

<2.2ms

DELAY

MISO

MOSI

09155-028

Z-AXIS ANG ULAR

RATE SENSOR

<5µs

DELAY

BAND-PASS

FILTER

ARITHMETI C

<5µs

DELAY

12-BIT ADC

Figure 27. Primary Signal Chain and Associated Delays

<5µs

DELAY

DEMOD

LOGIC UNI T

RATE DATA

LPF

CONTINUOUS

SELF-TEST

LPF

<64ms

GROUP DELAY

TRANSACTION

REGISTERS/MEMORY

Rev. B | Page 13 of 32

Page 14

ADXRS453 Data Sheet

SPI COMMUNICATION PROTOCOL

COMMAND/RESPONSE

Input/output is handled through a 32-bit command/response

SPI interface. With the command/response SPI interface, the

response to a command is issued during the next sequential

SPI exchange (see Figure 28).

The format for the interface is defined as follows:

Clock Phase = Clock Polarity = 0

Table 9 shows the commands that can be sent from the master

device to the gyroscope. Table 10 shows the responses to these

commands from the gyroscope. For descriptions of the bits in

the commands and responses, see the Command/Response Bit

Definitions section and the Fault Register Bit Definitions

section.

CS

The device response to the initial command is 0x00000001.

This response prevents the transmission of random data to the

master device upon the initial command/response exchange.

The SPI interface uses the ADXRS453 pins described in Table 8.

Table 8. SPI Signals

Signal Pin Description

Serial Clock SCLK

Chip Select

Master Out/

CS

MOSI

Slave In

Master In/

MISO

Slave Out

Exactly 32 clock cycles during CS

Active low chip select pin

Input for data sent to the gyroscope

(slave) from the main controller (master)

Output for data sent to the main controller

(master) from the gyroscope (slave)

active

SCLK

MOSI

MISO

32 CLOCK

CYCLES

COMMAND N

RESPONSE N – 1

Figure 28. SPI Protocol

32 CLOCK

CYCLES

COMMAND N + 1

RESPONSE N

09155-029

Table 9. SPI Commands

Bit

Command

Sensor

Data

Read 1 0 0 SM2 SM1 SM0 A8 A7 A6 A5 A4 A3 A2 A1 A0 P

Write 0 1 0 SM2 SM1 SM0 A8 A7 A6 A5 A4 A3 A2 A1 A0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 P

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SQ1 SQ0 1 SQ2 CHK P

Table 10. SPI Responses

Bit

Command

Sensor

Data

Read 0 1 0 P0 1 1 1 0 SM2 SM1 SM0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 P1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SQ2 SQ1 SQ0 P0 ST1 ST0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 PLL Q NVM POR PWR CST CHK P1

Write 0 0 1 P0 1 1 1 0 SM2 SM1 SM0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 P1

R/W Error 0 0 0 P0 1 1 1 0 SM2 SM1 SM0 0 0 SPI RE DU PLL Q NVM POR PWR CST CHK P1

Rev. B | Page 14 of 32

Page 15

Data Sheet ADXRS453

DEVICE DATA LATCHING

To allow for rapid acquisition of data from the ADXRS453,

device data latching is implemented, as shown in Figure 29.

When the chip select pin is asserted (

in the device is latched into memory. When the full MOSI

command is received and the chip select pin is deasserted

CS

(

goes high), the data is shifted into the SPI port registers

in preparation for the next sequential command/response

exchange. Device data latching allows for an extremely fast

sequential transfer delay of 0.1 µs (see Table 11).

DEVICE DATA IS LATCHED AFT ER THE

ASSERTION OF CS. LATCHED DATA IS

TRANSMITT ED DURING THE NEXT

SEQUENTIAL COMMAND/RESP ONSE

EXCHANGE.

CS

CS

goes low), the data

Note that the transmitted data is only as recent as the sequential

transmission delay implemented by the system. Conditions that

result in a sequential transfer delay of several seconds cause the

next sequential device response to contain data that is several

seconds old.

SCLK

MOSI

MISO

32 CLOCK

CYCLES

COMMAND N

0x…

RESPONSE N – 1

0x00000001

32 CLOCK

CYCLES

COMMAND N + 1

0x…

RESPONSE N

0x…

32 CLOCK

CYCLES

COMMAND N + 2

0x…

RESPONSE N + 1

0x…

9155-031

Figure 29. Device Data Latching

Rev. B | Page 15 of 32

Page 16

ADXRS453 Data Sheet

S

SPI TIMING CHARACTERISTICS

The following conditions apply to the SPI command/response

timing characteristics in Table 11:

All timing parameter are guaranteed through

characterization.

All timing is shown with respect to 10% DV

DD

and

Parameters are valid for 3.0 V ≤ DV

Capacitive load for all signals is assumed to be ≤80 pF.

Ambient temperature is −40°C ≤ T

The MISO pull-up is 47 kΩ or 110 µA.

90% of the actual delivered voltage waveform.

Table 11. SPI Command/Response Timing Characteristics

Symbol Min Max Unit Description

fOP 8.08 MHz SPI operating frequency

t

1/2 × t

SCLKH

t

1/2 × t

SCLKL

t

123.7 ns SCLK period

SCLK

− 13 ns SCLK high time

SCLK

− 13 ns SCLK low time

SCLK

tF 5.5 13 ns SCLK fall time

tR 5.5 13 ns SCLK rise time

tSU 37 ns Data input (MOSI) setup time

t

49 ns Data input (MOSI) hold time

HIGH

tA 20 ns Data output (MISO) access time

tV 40 ns Data output (MISO) valid after SCLK

t

0 ns Data output (MISO) lag time

LAG_MISO

t

40 ns Data output (MISO) disable time

DIS

t

1/2 × t

LEAD

t

LAG_

CS

1/2 × t

ns

SCLK

ns

SCLK

Enable (CS

Enable (CS

) lead time

) lag time

tTD 0.1 µs Sequential transfer delay

≤ 5.5 V.

DD

≤ +105°C.

A

CS

t

TD

t

LAG_CS

t

DIS

09155-030

CLK

MISO

MOSI

t

LEAD

t

t

SCLK

t

SCLKHtSCLKL

A

MSB LSB

t

HIGH

t

SU

MSB LSB

t

V

t

t

R

F

t

LAG_MISO

Figure 30. SPI Timings

Rev. B | Page 16 of 32

Page 17

Data Sheet ADXRS453

COMMAND/RESPONSE BIT DEFINITIONS

Table 12. SPI Interface Bit Definitions

Bits Description

SQ2 to SQ0 Sequence bits (from master)

SM2 to SM0 Sensor module bits (from master)

A8 to A0 Register address

D15 to D0 Data

P Command odd parity

SPI SPI command/response

RE Request error

DU Data unavailable

ST1, ST0 Status bits

P0 Response, odd parity, Bits[31:16]

P1 Response, odd parity, Bits[31:0]

SQ2 to SQ0 Bits

The SQ2 to SQ0 bits provide the system with a means of synchronizing the data samples that are received from multiple sensors.

To facilitate correct synchronization, the ADXRS453 gyroscope

includes the SQ[2:0] bits in the response sequence as they were

received in the request.

SM2 to SM0 Bits

The SM2 to SM0 bits are the sensor module bits from the master

device. These bits are not implemented in the ADXRS453 and

are hard-coded to 000 for all occurrences.

A8 to A0 Bits

The A8 to A0 bits represent the memory address for data read or

data write. These bits should be supplied by the master when the

memory registers are being accessed; these bits are ignored for all

sensor data requests. For a complete description of the available

memory registers, see the Memory Register Definitions section.

D15 to D0 Bits

The D15 to D0 bits are the 16-bit device data, which can

contain any of the following:

Data from the master to be written to a memory register, as

specified by the A8 to A0 bits.

Sensor rate output data from the slave.

Device data from the slave read from the memory register

specified by the A8 to A0 bits, as well as the data from the

next sequential register.

Following a write command, the 16-bit data that is written

to the specified memory register in the ADXRS453 and is

reflected back to the master device for correlation.

P Bit

A parity bit (P) is required for all master-to-slave data transmissions. The communication protocol requires one parity bit to

achieve odd parity for the entire 32-bit command. “Don’t care”

bits are also factored into the parity calculation.

SPI Bit

The SPI bit is set when either of the following occurs:

Too many or not enough bits were transmitted.

A message from the control module contains a parity error.

A SPI error causes the device to issue a R/W error response

regardless of the SPI command type issued by the master

device (see Table 10). In addition, any error during a sensor

data request results in the device issuing a read/write error.

RE Bit

The request error (RE) bit is the communication error bit transmitted from the ADXRS453 device to the control module. Request

errors can occur when

An invalid command is sent from the control module.

A read/write command specifies an invalid memory

register.

A write command attempted to write to a nonwritable

memory register.

DU Bit

After the chip select pin is deasserted (CS goes high), the user

must wait 0.1 µs before reasserting the

command/response frame with the device. Failure to adhere to

this timing specification may result in a data unavailable (DU)

error.

pin to initiate another

CS

ST1 and ST0 Bits

The status bits (ST1 and ST0) are used to signal to the master

device the type of data contained in the response message (see

Table 13).

Table 13. Status Bit Code Definitions

ST[1:0] Contents of Bits[D15:D0]

00 Invalid data for sensor data response

01 Valid sensor data

10 Sensor self-test data

11 Read/write response

Either of the following conditions can result in the ST[1:0] bits

being set to 00 during a sensor data response:

The self-test response is sufficiently different from its

nominal value (see the Specifications section for the

appropriate limits).

The PLL fault bit is active (see the PLL Bit section).

P0 Bit

P0 is the parity bit that establishes odd parity for Bits[31:16]

of the device response.

P1 Bit

P1 is the parity bit that establishes odd parity for the entire

32-bit device response.

Rev. B | Page 17 of 32

Page 18

ADXRS453 Data Sheet

FAULT REGISTER BIT DEFINITIONS

Table 14 describes the bits available for signaling faults to

the user. The individual bits of the fault registers are updated

asynchronously, depending on their respective detection criteria;

however, it is recommended that the fault registers be read at a

rate of at least 250 Hz. When asserted, an individual status bit

is not deasserted until it is read by the master device. If the error

persists after a fault register read, the status bit is immediately

reasserted and remains asserted until the next sequential

command/response exchange. The bits in the FAULT0 register are

appended to every sensor data response (see Table 10). Both

fault registers can be accessed by issuing a read command to

Address 0x0A.

Table 14. Fault Register Bit Definitions

Register Bit Name Description

FAULT1 Fail Failure that sets the ST[1:0] bits to 00

AMP Amplitude detection failure

OV Regulator overvoltage

UV Regulator undervoltage

FAULT0 PLL Phase-locked loop failure

Q Quadrature error

NVM Nonvolatile memory fault

POR Power-on or reset failed to initialize

PWR

CST

CHK Check: generate faults

Fail Bit

The fail flag is asserted when the ST[1:0] bits are set to 00 (see

the ST1 and ST0 Bits section). Assertion of the fail bit indicates

that the device has experienced a gross failure and that the sensor

data could be invalid.

AMP Bit

The AMP fault bit is asserted when the measured amplitude

of the silicon resonator has been significantly reduced. This

condition can occur if the voltage supplied to CP5 falls below

the requirements of the internal voltage regulator. This fault bit

is OR’ed with the CST fault bit; therefore, during a sensor data

request, the CST bit position represents either an AMP failure

or a CST failure. The full fault register can be read from memory

to determine the specific failure.

OV Bit

The OV fault bit is asserted if the internally regulated voltage

(nominally 3 V) is observed to exceed 3.3 V. This measurement

is low-pass filtered to prevent artifacts such as noise spikes from

asserting a fault condition. When an OV fault occurs, the PWR

fault bit is asserted simultaneously. Because the OV fault bit is not

transmitted as part of a sensor data response, it is recommended

that the user read back the FAULT1 and FAULT0 memory

registers upon the assertion of a PWR error to determine the

specific error condition.

Power regulation failed due to overvoltage or undervoltage condition

Continuous self-test failure or amplitude

detection failed

Rev. B | Page 18 of 32

UV Bit

The UV fault bit is asserted if the internally regulated voltage

(nominally 3 V) is observed to be less than 2.77 V. This measurement is low-pass filtered to prevent artifacts such as noise

spikes from asserting a fault condition. When a UV fault occurs,

the PWR fault bit is asserted simultaneously. Because the UV

fault bit is not transmitted as part of a sensor data response, it is

recommended that the user read back the FAULT1 and FAULT0

memory registers upon the assertion of a PWR error to determine

the specific error condition.

PLL Bit

The PLL bit indicates that the device has experienced a failure

in the phase-locked loop functional circuit block. This occurs

when the PLL fails to achieve synchronization with the resonator

structure. If the PLL status flag is active, the ST[1:0] bits of the

sensor data response are set to 00, indicating that the response

contains potentially invalid rate data.

Q Bit

A Q fault is asserted based on two independent quadrature

calculations.

The quad memory register (Address 0x08) contains a value

corresponding to the total instantaneous quadrature present

in the device. If this value exceeds 4096 LSB, a Q fault is

issued.

An internal quadrature accumulator records the amount

of quadrature correction performed by the ADXRS453. A

Q fault is issued when the quadrature error present in the

device has contributed to an equivalent of 4°/sec (typical)

of rate offset.

NVM Bit

An NVM error is transmitted to the control module when the

internal nonvolatile memory data fails a checksum calculation.

This check is performed once every 50 µs and does not include

the PIDx memory registers.

POR Bit

An internal check is performed on device startup to ensure that

the volatile memory of the device is functional. This is accomplished by programming a known value from the device ROM

into a volatile memory register. This value is then continuously

compared to the known value in ROM every 1 µs for the duration

of the device operation. If the value stored in the volatile memory

changes or does not match the value stored in ROM, the POR

error flag is asserted. The value stored in ROM is rewritten to

the volatile memory upon a device power cycle.

Page 19

Data Sheet ADXRS453

PWR Bit

The device performs a continuous check of the internal 3 V

regulated voltage level. If either an overvoltage (OV) or undervoltage (UV) fault is asserted, the PWR bit is also asserted. This

condition occurs if the regulated voltage is observed to be either

above 3.3 V or below 2.77 V. An internal low-pass filter removes

high frequency glitching effects to prevent the PWR bit from

being asserted unnecessarily. To determine whether the fault is

a result of an overvoltage or undervoltage condition, the OV

and UV fault bits must be read.

CST Bit

The ADXRS453 is designed with continuous self-test functionality. The measured self-test amplitudes are compared to the

limits presented in Table 1. Deviations from these values result

in reported self-test errors. The two thresholds for a self-test

failure are as follows:

Self-test value > ±512 LSB from nominal results in the

assertion of the self-test flag in the fault register.

Self-test value > ±1856 LSB from nominal results in the

assertion of the self-test flag in the fault register and the

setting of the ST[1:0] bits to 00, indicating that the rate

data contained in the sensor data response is potentially

invalid.

CHK Bit

The CHK bit is transmitted by the control module to the

ADXRS453 as a method of generating faults. By asserting the

CHK bit, the device creates conditions that result in the generation of all faults represented in the fault registers. For example,

the self-test amplitude is deliberately altered to exceed the fault

detection threshold, resulting in a self-test error. In this way, the

device is capable of checking both its ability to detect a fault

condition and its ability to report that fault condition to the

control module.

The fault conditions are initiated nearly simultaneously; however, the timing for receiving fault codes when the CHK bit is

asserted depends on the time required to generate each unique

fault. It takes no more than 50 ms for all internal faults to be

generated and the fault register to be updated to reflect the

condition of the device. Until the CHK bit is cleared, the status

bits (ST[1:0]) are set to 10, indicating that the data should be

interpreted by the control module as self-test data. After the

CHK bit is deasserted, an additional 50 ms are required for the

fault conditions to decay and for the device to return to normal

operation. See the Recommended Start-Up Sequence with CHK

Bit Assertion section for the proper methodology for asserting

the CHK bit.

Rev. B | Page 19 of 32

Page 20

ADXRS453 Data Sheet

RECOMMENDED START-UP SEQUENCE WITH CHK BIT ASSERTION

Figure 31 illustrates a recommended start-up sequence that can

be implemented by the user. Alternate start-up sequences can

be used, but the response from the ADXRS453 must be handled

correctly. If the start-up sequence is implemented immediately

after power is applied to the device, the total time to implement

the following fault detection routine is approximately 200 ms.

As described in the Device Data Latching section, the data

present in the device upon the assertion of the

MOSI: SENSOR DATA REQUEST

CHK BIT ASSERTED

MISO: ST ANDARD INITIAL

RESPONSE

CS

DATA LATCH POINT

CS

signal is used

MOSI: SENSOR DATA

REQUEST (T HIS CLEARS

THE CHK BIT)

MISO: SENSOR DATA

RESPONSE

XX X

in the next sequential command/response exchange. This results

in an apparent one-transaction delay before the data resulting

from the assertion of the CHK bit is reported by the device. For

all other read/write interactions with the device, no such delay

exists, and the MOSI command is serviced during the next

sequential command/response exchange.

Note that if the CHK bit is deasserted and the user tries to obtain

data from the device before the CST fault flag clears, the device

reports the data as error data.

MOSI: SENSOR DATA

REQUEST

MISO: CHK RESPONSE

ST[1:0] = 10

MOSI: SENSOR DATA

REQUEST

MISO: CHK RESPONSE

ST[1:0] = 10

SCLK

MOSI

MISO

POWER IS

APPLIED TO

THE DEVICE.

WAIT 100ms T O

ALLOW FOR

THE INTERNAL

CIRCUITRY TO

BE INITIALIZED.

32 CLOCK

CYCLES

t = 100ms t = 150ms t = 200ms t = 200ms +

WHEN THE 100ms S TART-UP

TIME HAS EL APSED, THE

MASTER DEVICE IS FREE TO

ASSERT THE CHK BIT AND

START THE PROCESS OF

INTERNAL ERRO R

CHECKING. DURING THE

FIRST COMMAND/

RESPONSE EXCHANG E

AFTER POWER-ON, THE

ADXRS453 IS DESIG NED

TO ISSUE A PREDEFINED

RESPONSE.

32 CLOCK

CYCLES

0x…0x00000001

A 50ms DELAY IS REQUIRED

SO THAT THE GENERATION

OF FAULTS WITHIN THE

DEVICE IS AL LOWED T O

COMPLETE. HOWEVER,

BECAUSE THE DEVICE DATA

IS LATCHED BEFORE THE

CHK BIT IS ASSERTED, THE

DEVICE RESPO NSE DURING

THIS COMMAND/RESPONSE

EXCHANGE DOES NO T

CONTAIN FAUL T

INFORMATION. THIS

RESPONSE CAN BE

DISCARDED.

32 CLOCK

CYCLES

0x200000000x200000000x20000003 0x20000000

0x…FF OR 0x…FE

(PARITY DEPE NDENT)

ANOTHER 50ms DELAY MUST

BE OBSERVED TO ALLOW

THE FAULT CO NDITIO NS TO

CLEAR. IF THE DEVICE I S

FUNCTIONI NG PROPERL Y,

THE MISO RESPONSE

CONTAINS ALL ACTIVE

FAULTS, AS WELL AS HAVING

SET THE MESSAGE FORMAT

TO SELF-TEST DATA. THIS IS

INDICATED THRO UGH THE ST

BITS BEING SET TO 10.

THE FAULT BITS OF THE

ADXRS453 REMAIN ACTI VE

UNTIL CLEARED. DUE TO

THE REQUIRED DECAY

PERIOD FO R EACH FAULT

CONDITIO N, FAULT

CONDITIO NS REMAIN

PRESENT UPON THE

IMMEDIATE DEASSERTION

OF THE CHK BIT. THIS

RESULTS IN A SECOND

SEQUENTIAL RESPONSE IN

WHICH THE FAUL T BITS ARE

ASSERTED. AG AIN, THE

RESPONSE IS FORMATT ED

AS SELF-TEST DATA

INDICATING THAT THE FAUL T

BITS HAVE BEEN S ET

INTENTIONALLY.

Figure 31. Recommended Start-Up Sequence

32 CLOCK

CYCLES

0x…FF OR 0x…FE

(PARITY DEPENDENT)

t

TD

t = 200ms + 2

ALL FAULT

CONDITIO NS ARE

CLEARED, AND ALL

SUBSEQUENT DATA

EXCHANGES NEED

ONLY OBSERVE

THE SEQUENTIAL

TRANSFER DELAY

TIMING

PARAMETER.

t

TD

09155-032

Rev. B | Page 20 of 32

Page 21

Data Sheet ADXRS453

RATE DATA FORMAT

The ADXRS453 gyroscope transmits rate data in a 16-bit format

as part of a 32-bit SPI data frame. See Table 10 for the full 32-bit

format of the sensor data response. The rate data is transmitted

MSB first, from D15 to D0.

Table 15. Rate Data

16-Bit Rate Data

Decimal (LSBs) Hex (D15:D0)

+32,767 0x7FFF Maximum possible positive data value (not guaranteed)

… … …

+24,000 0x5DC0 +300°/sec rotation (positive FSR)

… … …

+160 0x00A0 +2°/sec rotation

… … …

+80 0x0050 +1°/sec rotation

… … …

+40 0x0028 +0.5°/sec rotation

… … …

+20 0x0014 +0.025°/sec rotation

… … …

0 0x0000 Zero rotation value

… … …

−20 0xFFEC −0.025°/sec rotation

… … …

−40 0xFFD8 −0.5°/sec rotation

… … …

−80 0xFFB0 −1°/sec rotation

… … …

−160 0xFF60 −2°/sec rotation

… … …

−24,000 0xA240 −300°/sec rotation (negative FSR)

… … …

−32,768 0x8000 Maximum possible negative data value (not guaranteed)

Description

The data is formatted as a twos complement number with a scale

factor of 80 LSB/°/sec. Therefore, the highest obtainable value

for positive (clockwise) rotation is 0x7FFF (decimal +32,767),

and the highest obtainable value for negative (counterclockwise)

rotation is 0x8000 (decimal −32,768). Performance of the device

is not guaranteed above ±24,000 LSB (±300°/sec).

Rev. B | Page 21 of 32

Page 22

ADXRS453 Data Sheet

MEMORY MAP AND REGISTERS

MEMORY MAP

Table 16 provides a list of the memory registers that can be

read from or written to by the user. See the SPI Communication

Protocol section for the proper input sequence to read from or

write to a specific memory register. Each memory register has

eight bits of data; however, when a read request is performed,

the data always returns as a 16-bit message. This is accomplished

by appending the data from the next sequential register to the

memory address that was specified.

Table 16. Memory Register Map

Address Register Name D7 (MSB) D6 D5 D4 D3 D2 D1 D0 (LSB)

0x00 RATE1 RTE15 RTE14 RTE13 RTE12 RTE11 RTE10 RTE9 RTE8

0x01 RATE0 RTE7 RTE6 RTE5 RTE4 RTE3 RTE2 RTE1 RTE0

0x02 TEM1 TEM9 TEM8 TEM7 TEM6 TEM5 TEM4 TEM3 TEM2

0x03 TEM0 TEM1 TEM0 Unused Unused Unused Unused Unused Unused

0x04 LOCST1 LCST15 LCST14 LCST13 LCST12 LCST11 LCST10 LCST9 LCST8

0x05 LOCST0 LCST7 LCST6 LCST5 LCST4 LCST3 LCST2 LCST1 LCST0

0x06 HICST1 HCST15 HCST14 HCST13 HCST12 HCST11 HCST10 HCST9 HCST8

0x07 HICST0 HCST7 HCST6 HCST5 HCST4 HCST3 HCST2 HCST1 HCST0

0x08 QUAD1 QAD15 QAD14 QAD13 QAD12 QAD11 QAD10 QAD9 QAD8

0x09 QUAD0 QAD7 QAD6 QAD5 QAD4 QAD3 QAD2 QAD1 QAD0

0x0A FAULT1 Unused Unused Unused Unused Fail AMP OV UV

0x0B FAULT0 PLL Q NVM POR PWR CST CHK 0

0x0C PID1 PIDB15 PIDB14 PIDB13 PIDB12 PIDB11 PIDB10 PIDB9 PIDB8

0x0D PID0 PIDB7 PIDB6 PIDB5 PIDB4 PIDB3 PIDB2 PIDB1 PIDB0

0x0E SN3 SNB31 SNB30 SNB29 SNB28 SNB27 SNB26 SNB25 SNB24

0x0F SN2 SNB23 SNB22 SNB21 SNB20 SNB19 SNB18 SNB17 SNB16

0x10 SN1 SNB15 SNB14 SNB13 SNB12 SNB11 SNB10 SNB9 SNB8

0x11 SN0 SNB7 SNB6 SNB5 SNB4 SNB3 SNB2 SNB1 SNB0

Data is transmitted MSB first. For proper acquisition of data from

the memory register, make the read request to the even-numbered

register address only; for example, to read the LOCSTx registers,

Address Register 0x04, but not Register 0x05. For a description of

each memory register listed in Table 16, see the Memory Register

Definitions section.

Rev. B | Page 22 of 32

Page 23

Data Sheet ADXRS453

MEMORY REGISTER DEFINITIONS

The SPI-accessible memory registers are described in this section.

As noted in the Memory Map section, when requesting data

from a memory register, only the first sequential memory address

should be addressed. The data returned by the device contains 16

bits of memory register information. Bits[15:8] contain the MSB

of the requested information, and Bits[7:0] contain the LSB.

Rate (RATEx) Registers

Addresses: 0x00 (RATE1)

0x01 (RATE0)

Register update rate: f

Scale factor: 80 LSB/°/sec

The RATEx registers contain the temperature compensated rate

output of the device, filtered to f

also be accessed by issuing a sensor data read request to the device.

The data is presented as a 16-bit, twos complement number.

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

RTE15 RTE14 RTE13 RTE12 RTE11 RTE10 RTE9 RTE8

D7 D6 D5 D4 D3 D2 D1 D0

RTE7 RTE6 RTE5 RTE4 RTE3 RTE2 RTE1 RTE0

Temperature (TEMx) Registers

Addresses: 0x02 (TEM1)

0x03 (TEM0)

Register update rate: f

Scale factor: 5 LSB/°C

The TEMx registers contain a value corresponding to the

temperature of the device. The data is presented as a 10-bit,

twos complement number. 0 LSB corresponds to a temperature

of approximately 45°C (see Table 17).

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

TEM9 TEM8 TEM7 TEM6 TEM5 TEM4 TEM3 TEM2

D7 D6 D5 D4 D3 D2 D1 D0

TEM1 TEM0 Unused

Table 17. Sample Temperatures and TEMx Register Contents

Temperature Value of TEM1 and TEM0 Registers1

45°C 0000 0000 00XX XXXX

85°C 0011 0010 00XX XXXX

0°C 1100 0111 11XX XXXX

1

X = don’t care.

/32 (~485 Hz)

0

/200 (~77.5 Hz). This data can

0

/32 (~485 Hz)

0

Low CST (LOCSTx) Registers

Addresses: 0x04 (LOCST1)

0x05 (LOCST0)

Register update rate: f

/16 (~970 Hz)

0

Scale factor: 80 LSB/°/sec

The LOCSTx registers contain the value of the temperature

compensated and low-pass filtered continuous self-test delta.

This value is a measure of the difference between the positive

and negative self-test deflections and corresponds to the values

presented in Table 1. The device issues a CST error if the value

of the self-test exceeds the established self-test limits. The self-test

data is filtered to f

/8000 (~1.95 Hz) to prevent false triggering

0

of the CST fault bit. The data is presented as a 16-bit, twos complement number, with a scale factor of 80 LSB/°/sec.

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

LCST15 LCST14 LCST13 LCST12 LCST11 LCST10 LCST9 LCST8

D7 D6 D5 D4 D3 D2 D1 D0

LCST7 LCST6 LCST5 LCST4 LCST3 LCST2 LCST1 LCST0

High CST (HICSTx) Registers

Addresses: 0x06 (HICST1)

0x07 (HICST0)

Register update rate: f

/16 (~970 Hz)

0

Scale factor: 80 LSB/°/sec

The HICSTx registers contain the unfiltered self-test information.

The HICSTx data can be used to supplement fault diagnosis in

safety critical applications because sudden shifts in the self-test

response can be detected. However, the CST bit of the fault

register is not set when the HICSTx data is observed to exceed

the self-test limits. Only the LOCSTx memory registers, which

are designed to filter noise and the effects of sudden temporary

self-test spiking due to external disturbances, control the assertion of the CST fault bit. The data is presented as a 16-bit, twos

complement number.

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

HCST15 HCST14 HCST13 HCST12 HCST11 HCST10 HCST9 HCST8

D7 D6 D5 D4 D3 D2 D1 D0

HCST7 HCST6 HCST5 HCST4 HCST3 HCST2 HCST1 HCST0

Rev. B | Page 23 of 32

Page 24

ADXRS453 Data Sheet

Quad Memory (QUADx) Registers

Addresses: 0x08 (QUAD1)

0x09 (QUAD0)

Register update rate: f

/64 (~240 Hz)

0

Scale factor: 80 LSB/°/sec equivalent

The QUADx registers contain a value corresponding to the amount

of quadrature error present in the device at a given time. Quadrature can be likened to a measurement of the error of the motion

of the resonator structure and can be caused by stresses and aging

effects. The quadrature data is filtered to f

/200 (~77.5 Hz) and can

0

be read frequently to detect sudden shifts in the level of quadrature.

The data is presented as a 16-bit, twos complement number.

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

QAD15 QAD14 QAD13 QAD12 QAD11 QAD10 QAD9 QAD8

D7 D6 D5 D4 D3 D2 D1 D0

QAD7

QAD6 QAD5 QAD4 QAD3 QAD2 QAD1 QAD0

Fault (FAULTx) Registers

Addresses: 0x0A (FAULT1)

0x0B (FAULT0)

Register update rate: Not applicable

Scale factor: Not applicable

The FAULTx registers contain the state of the error flags in the

device. The FAULT0 register is appended to the end of every

device data transmission (see Table 10); however, this register

can also be accessed independently through its memory location.

The individual fault bits are updated asynchronously, requiring

<5 µs to activate, as soon as the fault condition exists on chip. When

toggled, each fault bit remains active until the fault register is read

or a sensor data command is received. If the fault is still active

after the bit is read, the fault bit is immediately reasserted.

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

Unused Fail AMP OV UV

D7 D6 D5 D4 D3 D2 D1 D0

PLL Q NVM POR PWR CST CHK 0

Part ID (PIDx) Registers

Addresses: 0x0C (PID1)

0x0D (PID0)

Register update rate: Not applicable

Scale factor: Not applicable

The (PIDx) registers contain a 16-bit number that identifies the

version of the ADXRS453. Combined with the serial number, this

information allows for a higher degree of device individualization

and tracking. The initial product ID is R01 (0x5201), with subsequent versions of silicon incrementing this value to R02, R03,

and so on.

MSB LSB

D15 D14 D13 D12 D11 D10 D9 D8

PIDB15 PIDB14 PIDB13 PIDB12 PIDB11 PIDB10 PIDB9 PIDB8

D7 D6 D5 D4 D3 D2 D1 D0

PIDB7 PIDB6 PIDB5 PIDB4 PIDB3 PIDB2 PIDB1 PIDB0

Serial Number (SNx) Registers

Addresses: 0x0E (SN3)

0x0F (SN2)

0x10 (SN1)

0x11 (SN0)

Register update rate: Not applicable

Scale factor: Not applicable

The SNx registers contain a 32-bit identification number that

uniquely identifies the device. To read the entire serial number,

two memory read requests must be initiated. The first read

request to Address 0x0E returns the upper 16 bits of the serial

number, and the following read request to Address 0x10 returns

the lower 16 bits of the serial number.

MSB LSB

D31 D30 D29 D28 D27 D26 D25 D24

SNB31 SNB30 SNB29 SNB28 SNB27 SNB26 SNB25 SNB24

D23 D22 D21 D20 D19 D18 D17 D16

SNB23 SNB22 SNB21 SNB20 SNB19 SNB18 SNB17 SNB16

D15 D14 D13 D12 D11 D10 D9 D8

SNB15 SNB14 SNB13 SNB12 SNB11 SNB10 SNB9 SNB8

D7 D6 D5 D4 D3 D2 D1 D0

SNB7 SNB6 SNB5 SNB4 SNB3 SNB2 SNB1 SNB0

Rev. B | Page 24 of 32

Page 25

Data Sheet ADXRS453

9

PACKAGE ORIENTATION AND LAYOUT INFORMATION

ADXRS453

(PACKAGE FRONT)

14

8

1

7

NOTES

1. THE PACKAGE HAS T ERMINALS ON TWO FACES. HOWEVER, THE TERMINALS ON THE

BACK ARE FOR INT ERNAL EVAL UATION O NLY AND SHO ULD NOT BE US ED IN THE E ND

APPLICATI ON. THE TERMINAL S ON THE BOTTO M OF THE PACKAGE INCO RPORATE

METALLIZATION BUMPS THAT ENSURE A MINIMUM SOLDER THICKNESS FOR IMPROVED

SOLDER JOINT RELIABILITY. THESE BUMPS ARE NOT PRESENT ON THE BACK TERMINALS

AND, THEREF ORE, PO OR SOL DER JOINT RELIABIL ITY CAN BE ENCOUNTERED I F THE BACK

TERMINALS ARE USED IN T HE END APPLI CATION. FOR THE OUTLINE DIMENSIONS OF THIS

PACKAGE, SEE FIGURE 38.

9155-033

Figure 32. 14-Lead Ceramic LCC_V, Vertical Mount

0.55

.462

11.232

1.27

0.572

5.55

2.55

2.55

1.55

0.55

0.95

0.55

0.95

1.55

1.691

Figure 33. Sample SOIC_CAV Solder Pad Layout (Land Pattern),

Dimensions Shown in Millimeters, Not to Scale

09155-034

1.5

1 1

0.80.8

1.5

09155-035

Figure 34. Sample LCC_V Solder Pad Layout (Land Pattern), Dimensions

Shown in Millimeters, Not to Scale

Rev. B | Page 25 of 32

Page 26

ADXRS453 Data Sheet

SOLDER PROFILE

SUPPLIER TP ≥ T

SUPPLIER

T

P

MAXIMUM RAMP-UP RATE = 3°C/sec

MAXIMUM RAMP-DOWN RATE = 6°C/sec

T

L

T

SMAX

T

SMIN

TEMPERATURE

25

PREHEAT AREA

C

t

P

t

S

TIME 25°C TO PEAK

T

T

– 5°C

C

C

TIME

USER TP ≤ T

USER

t

P

t

L

C

t

P

TC – 5°C

09155-037

Figure 35. Recommended Soldering Profile

Table 18. Recommended Soldering Profile Limits

Profile Feature Sn63/Pb37 Pb-Free

Average Ramp Rate (TL to TP) 3°C/sec max 3°C/sec max

Preheat

Minimum Temperature (T

Maximum Temperature (T

Time (T

Ramp-Up Rate (T

SMIN

to T

), tS 60 sec to 120 sec 60 sec to 120 sec

SMAX

to TL) 3°C/sec max 3°C/sec max

SMAX

) 100°C 150°C

SMIN

) 150°C 200°C

SMAX

Time Maintained Above Liquidous (tL) 60 sec to 150 sec 60 sec to 150 sec

Liquidous Temperature (TL) 183°C 217°C

Classification Temperature (TC)

1

220°C 250°C

Peak Temperature (TP) TC + 0°C/−5°C TC + 0°C/−5°C

Time Within 5°C of Actual Peak Temperature (tP) 10 sec to 30 sec 20 sec to 40 sec

Ramp-Down Rate (TP to TL) 6°C/sec max 6°C/sec max

Time 25°C to Peak Temperature 6 minutes max 8 minutes max

1

Based on IPC/JEDEC J-STD-020D.01 for SnPb and Pb-free processes. Package volume < 350 mm3, package thickness > 2.5 mm.

Rev. B | Page 26 of 32

Page 27

Data Sheet ADXRS453

PACKAGE MARKING CODES

XRS453

BEYZ n

#YYWW

LLLLLLLLL

Figure 36. LCC_V and SOIC_CAV Package Marking Codes

Table 19. Package Code Designations

Marking Meaning

XRS Angular rate sensor

453 Series number

B Temperature grade (−40°C to +105°C)

RG Package designator (SOIC_CAV package)

EY Package designator (LCC_V package)

Z RoHS compliant

n Revision number

# Pb-free designation

YYWW Assembly date code

LLLLLLLLL Assembly lot code (up to nine characters)

XRS453

BRGZ n

#YYWW

LLLLLLLLL

09155-038

Rev. B | Page 27 of 32

Page 28

ADXRS453 Data Sheet

C

V

OUTLINE DIMENSIONS

10.30 BSC

PIN 1

INDICATOR

3.73

3.58

3.43

0.28

0.18

0.08

OPLANARITY

0.10

0.50

0.45

0.40

16

1

9.59 BSC

1.27 BSC

0.75

0.70

0.65

9

8

7.80

BSC

0.58

0.48

0.38

1.50

1.35

1.20

10.42

BSC

0.25 GAGE

PLANE

8°

4°

0°

DETAIL A

DETAIL A

0.87

0.77

0.67

072409-B

Figure 37. 16-Lead Small Outline, Plastic Cavity Package [SOIC_CAV]

(RG-16-1)

Dimensions shown in millimeters

FRONT

IEW

0.275

REF

9.20

9.00 SQ

8.80

8.08

8.00

7.92

0.350

0.305

0.260

4.40

4.00

3.60

BACK VI EW

1.60

8

0.80

(PINS 2, 6,

9, 13)

7.18

7.10

7.02

0.50

TYP

0.675 NOM

0.500 MIN

0.30

REF

0.35

REF

0.35

REF

0.80 REF

(METALLIZATION BUMP

BUMP HEIGHT 0.03 NOM)

SIDE VI EW

R0.20

REF

1.50

(PINS 2, 6)

(PINS 9-10,

89

1.00

12-13)

13 14

10

11 12

TERMINALS ON BACK SIDE

OF PACKAGE ARE FOR

EVALUATION TESTING ONLY.

0.80

(PINS 10,

11, 12 )

04-08-2010-A

1.175

REF

C0.30

REF

1.70

REF

(ALL PINS)

1.70

REF

(ALL PINS)

7.70

7.55

7.40

1 2 345 6 7

1.00

(PINS 2, 6)

1 2 345 6 7

14

13 12 11 10

1.40

(PINS 1,

7, 8, 14)

(PINS 3-5, 10-12)

BOTTOM VIEW ( PADS SIDE)

0.60

(PINS 3-5)

0.30

REF

0.40

(PINS 1, 7)

9

Figure 38. 14-Terminal Ceramic Leadless Chip Carrier, Vertical Form [LCC_V]

(EY-14-1)

Dimensions shown in millimeters

Rev. B | Page 28 of 32

Page 29

Data Sheet ADXRS453

ORDERING GUIDE

Temperature

Range Package Description

Model

1

ADXRS453BEYZ −40°C to +105°C 14-Terminal Ceramic Leadless Chip Carrier, Vertical Form [LCC_V] EY-14-1

ADXRS453BEYZ-RL −40°C to +105°C 14-Terminal Ceramic Leadless Chip Carrier, Vertical Form [LCC_V] EY-14-1

ADXRS453BRGZ −40°C to +105°C 16-Lead Small Outline, Plastic Cavity Package [SOIC_CAV] RG-16-1

ADXRS453BRGZ-RL −40°C to +105°C 16-Lead Small Outline, Plastic Cavity Package [SOIC_CAV] RG-16-1

EVAL-ADXRS453Z Evaluation Board, SOIC_CAV

EVAL-ADXRS453Z-V Evaluation Board, LCC_V

EVAL-ADXRS453Z-M Analog Devices Inertial Sensor Evaluation System (Includes ADXRS453 Satellite)

EVAL-ADXRS453Z-S ADXRS453 Satellite, Standalone, to be used with Inertial Sensor Evaluation System

1

Z = RoHS Compliant Part.

Package

Option

Rev. B | Page 29 of 32

Page 30

ADXRS453 Data Sheet

NOTES

Rev. B | Page 30 of 32

Page 31

Data Sheet ADXRS453

NOTES

Rev. B | Page 31 of 32

Page 32

ADXRS453 Data Sheet

NOTES

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09155-0-12/11(B)

Rev. B | Page 32 of 32

Loading...

Loading...