Page 1

Precision Analog Microcontroller, 12-Bit Analog I/O, Large

Data Sheet

FEATURES

Analog input/output

Multichannel, 12-bit, 1 MSPS ADC

Up to 16 ADC channels

Fully differential and single-ended modes

0 V to V

12-bit voltage output DACs

4 DAC outputs available

On-chip voltage reference

On-chip temperature sensor (±3°C)

Voltage comparator

Microcontroller

ARM7TDMI core, 16-bit/32-bit RISC architecture

JTAG port supports code download and debug

Clocking options

Trimmed on-chip oscillator (±3%)

External watch crystal

External clock source up to 41.78 MHz

41.78 MHz PLL with programmable divider

Memory

126 kB Flash/EE memory, 32 kB SRAM

In-circuit download, JTAG-based debug

Software-triggered in-circuit reprogrammability

Vectored interrupt controller for FIQ and IRQ

8 priority levels for each interrupt type

Interrupt on edge or level external pin inputs

analog input range

REF

Memory, ARM7TDMI MCU with Enhanced IRQ Handler

ADuC7124/ADuC7126

On-chip peripherals

2× fully I

SPI (20 MBPS in master mode, 10 MBPS in slave mode)

2× UART channels

Up to 40 GPIO port

4× general-purpose timers

Programmable logic array (PLA)

16-bit, 6-channel PWM

Power supply monitor

Power

Specified for 3 V operation

Active mode: 11.6 mA at 5 MHz, 33.3 mA at 41.78 MHz

Packages and temperature range

Fully specified for −40°C to +125°C operation

64-lead LFCSP and 80-lead LQFP

Tools

Low cost QuickStart development system

Full third-party support

APPLICATIONS

Industrial control and automation systems

Smart sensors, precision instrumentation

Base station systems, optical networking

Patient monitoring

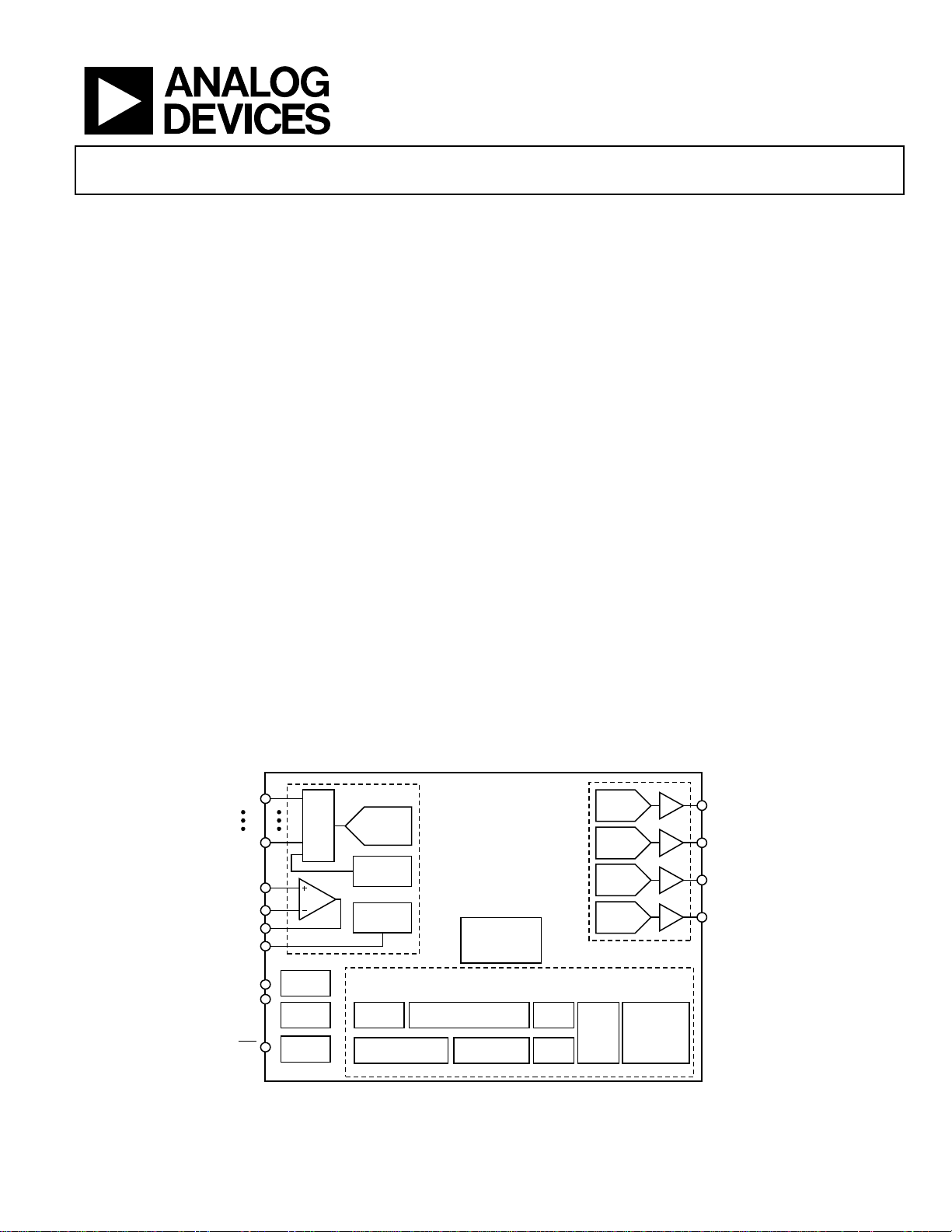

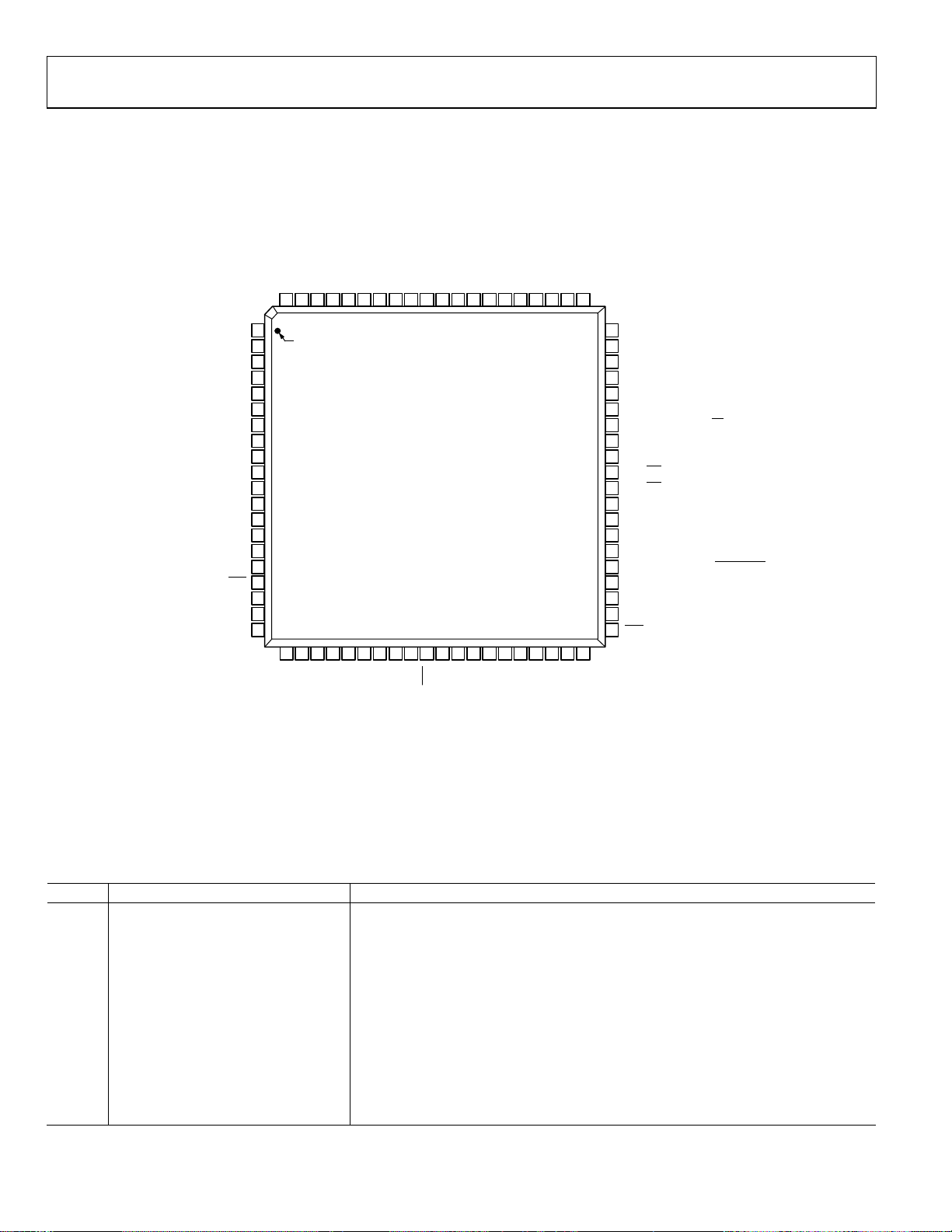

FUNCTIONAL BLOCK DIAGRAM

2

C-compatible channels

With 4-byte FIFO on input and output stages

With 16-byte FIFO on input and output stages

All GPIOs are 5 V tolerant

Watchdog timer (WDT) and wake-up timer

16 PLA elements

ADC0

MUX

ADC15

CMP0

CMP1

CMP

OUT

V

REF

XCLKI

XCLKO

RST

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of p atents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

OSC

AND PLL

PSM

POR

1MSPS

12-BIT ADC

TEMP

SENSOR

BAND GAP

REF

PLA

63k × 16 FLASH/EEPROM

4 GENERAL-

PURPOSE TIMERS

ADuC7124/ADuC7126

ARM7TDMI-BAS ED MCU WITH

ADDITIO NAL PERIPHERALS

8k × 32 SRAM

VECTORED

INTERRUPT

CONTROL LER

SPI, 2 × I2C,

2 × UART

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010–2012 Analog Devices, Inc. All rights reserved.

GPIO

JTAG

PWM

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

EXTERNAL

MEMORY

INTERFACE

DAC0

DAC1

DAC2

DAC3

09123-001

Page 2

ADuC7124/ADuC7126 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 3

General Description ......................................................................... 4

Specifications..................................................................................... 5

Timing Specifications .................................................................. 8

Absolute Maximum Ratings.......................................................... 13

ESD Caution................................................................................ 13

Pin Configurations and Function Descriptions ......................... 14

Typical Performance Characteristics ........................................... 23

Terminology .................................................................................... 26

ADC Specifications ....................................................................26

DAC Specifications..................................................................... 26

Overview of the ARM7TDMI Core ............................................. 27

Thumb Mode (T)........................................................................ 27

Long Multiply (M)...................................................................... 27

EmbeddedICE (I) ....................................................................... 27

Exceptions ................................................................................... 27

ARM Registers ............................................................................ 27

Interrupt Latency........................................................................ 28

Memory Organization ...................................................................29

Memory Access........................................................................... 29

Flash/EE Memory....................................................................... 29

SRAM........................................................................................... 29

Memory Mapped Registers....................................................... 29

ADC Circuit Overview .................................................................. 37

Transfer Function....................................................................... 37

Typical Operation....................................................................... 38

MMRs Interface.......................................................................... 38

Converter Operation.................................................................. 40

Driving the Analog Inputs ........................................................ 41

Calibration................................................................................... 42

Temperature Sensor ................................................................... 42

Band Gap Reference................................................................... 43

Nonvolatile Flash/EE Memory ..................................................... 44

Programming.............................................................................. 44

Flash/EE Memory Security ....................................................... 45

Flash/EE Control Interface ....................................................... 45

Execution Time from SRAM and Flash/EE............................ 48

Reset and Remap ........................................................................ 48

Other Analog Peripherals.............................................................. 51

DAC.............................................................................................. 51

Power Supply Monitor............................................................... 53

Comparator................................................................................. 53

Oscillator and PLL—Power Control........................................ 54

Digital Peripheral ........................................................................... 58

General-Purpose Input/Output ............................................... 58

Serial Port Mux........................................................................... 60

UART Serial Interface................................................................ 60

Serial Peripheral Interface......................................................... 66

I2C................................................................................................. 70

PWM General Overview........................................................... 78

Programmable Logic Array (PLA) .......................................... 81

Processor Reference Peripherals................................................... 84

Interrupt System......................................................................... 84

IRQ............................................................................................... 84

Fast Interrupt Request (FIQ) .................................................... 85

Vectored Interrupt Controller (VIC)....................................... 86

Timers.......................................................................................... 91

External Memory Interfacing................................................... 97

Hardware Design Considerations .............................................. 101

Power Supplies.......................................................................... 101

Grounding and Board Layout Recommendations............... 102

Clock Oscillator........................................................................ 102

Power-On Reset Operation..................................................... 103

Outline Dimensions..................................................................... 104

Ordering Guide ........................................................................ 105

Rev. C | Page 2 of 108

Page 3

Data Sheet ADuC7124/ADuC7126

REVISION HISTORY

5/12—Rev. B to Rev. C

Changed bit to byte in General Description Section....................4

Changes to Table 2 and Table 3 .......................................................8

Changes to Tabl e 4 and to Figure 2 and Figure 3..........................9

Changes to Tabl e 5 and Figure 4....................................................10

Changes to Tabl e 6 and Figure 5....................................................11

Changes Tabl e 7 and Figure 6 ........................................................12

Changes to Pin 50 and Pin 51 in Tabl e 9 ......................................14

Changes to Serial Downloading (In-Circuit Programming)

Section...............................................................................................44

Changes to Tabl e 77 ........................................................................57

Changes to Table 78 ........................................................................58

Changes to Table 90 ........................................................................60

Changes to Normal 450 UART Baud Rate Generation

Section...............................................................................................61

Changes to Serial Peripheral Interface Section ...........................66

Added equation to Timers Section and added Hr: Min: Sec

1/128 Format Section......................................................................91

Changes to Figure 69 ................................................................... 103

Updated Outline Dimensions..................................................... 104

Changes to Ordering Guide........................................................ 105

1/11—Rev A to Rev B

Changes to Table 1 ............................................................................5

10/10—Rev. 0 to Rev. A

Added ADuC7126..............................................................Universal

Changes to Features Section ............................................................1

Moved Figure 1..................................................................................1

Changes to Figure 1...........................................................................1

Changes to General Description Section .......................................4

Changes to Voltage Output at 25°C, Voltage TC, IOV

in Active Mode, and IOV

Current in Pause Mode Parameters,

DD

Current

DD

Table 1 .................................................................................................5

Change to Table 8 ............................................................................13

Changed REFGND to GND

......................................................13

REF

Changes to Figure 7 and Table 9....................................................14

Added Figure 8 and Table 10; Renumbered Sequentially..........18

Change to Figure 17 Caption.........................................................25

Change to Memory Mapped Registers Section...........................29

Change to Figure 26........................................................................30

Changes to Table 18 ........................................................................32

Changes to Table 21 ........................................................................33

Changes to Table 22 ........................................................................34

Moved Table 25................................................................................35

Change to Table 25 ..........................................................................35

Added Table 26 ................................................................................35

Change to Table 27 ..........................................................................36

Changes to Temperature Sensor Section......................................42

Deleted Table 59; Renumbered Sequentially ...............................43

Added Downloading (In-Circuit Programming) via I

C Section ..........................................................................................44

Change to JTAG Access Section and Table 37.............................45

Changes to Table 45 ........................................................................46

Changes to RSTCFG Register Section..........................................49

Deleted Table 72 and Table 75.......................................................49

Deleted Table 78 ..............................................................................50

Changes to DAC Section, Table 62, and Table 64 .......................51

Changes to References to ADC and the DACs Setion, Table 66,

Configuring DAC Buffers in Op Amp Mode Section,

DACBCFG Register Section, and Table 67 ..................................52

Added DACBKEY1 Register Section and DACBKEY2 Register

Section ..............................................................................................53

Changes to Table 69 and Figure 45 ...............................................54

Changes to and External Crystal Selection and External Clock

Selection ...........................................................................................55

Changes to PLLCON Register and POWCON0 Register

Section ..............................................................................................56

Changes to Table 78 ........................................................................58

Changes to Table 81 ........................................................................59

Changes to Table 84 and Table 90.................................................60

Changes to Table 93, COM0FCR Register Section, COM1FCR

Register Section, and Table 94.......................................................63

Changes to Serial Peripheral Interface Section ...........................66

Change to SPI Registers Section....................................................67

Changes to SPIDIV Register Section and Table 101 ..................68

Change to I

2

C Master Transmit Register Section .......................73

Change to Table 109........................................................................74

Change to I

2

C Slave Status Registers Section ..............................75

Change to Table 113........................................................................79

Changes to Table 114 Title and Figure 50....................................80

Change to IRQCLRE Register Register .......................................90

Change to Figure 54........................................................................92

Changes to Table 141, T1CLRI Register Section, and T1CAP

Register Section ...............................................................................93

Changes to Table 143 ......................................................................94

Added External Memory Interfacting Section, Table 145,

Table 146, and Figure 57.................................................................96

Added XMCFG Register Section, Table 147, Table 148,

Table 149, and Table 150 ................................................................97

Added Figure 58 and Figure 59 .....................................................98

Added Figure 60 and Figure 61 .....................................................99

Changes to Figure 62 to Figure 65 ..............................................100

Changes to Figure 67 and Figure 68 ...........................................101

Change to Power-On Reset Operation Section and

Figure 69.........................................................................................102

Added Figure 71............................................................................103

Changes to Ordering Guide.........................................................104

9/10—Revision 0: Initial Version

2

Rev. C | Page 3 of 108

Page 4

ADuC7124/ADuC7126 Data Sheet

GENERAL DESCRIPTION

The ADuC7124/ADuC7126 are fully integrated, 1 MSPS,

12-bit data acquisition system incorporating high performance

multichannel ADCs, 16-bit/32-bit MCUs, and Flash/EE memory

on a single chip.

The ADC consists of up to 12 single-ended inputs. An additional

four inputs are available but are multiplexed with the four DAC

output pins. The ADC can operate in single-ended or differential input mode. The ADC input voltage range is 0 V to VREF.

A low drift band gap reference, temperature sensor, and voltage

comparator complete the ADC peripheral set.

The DAC output range is programmable to one of three voltage

ranges. The DAC outputs have an enhanced feature of being

able to retain their output voltage during a watchdog or software reset sequence.

The devices operate from an on-chip oscillator and a PLL

generating an internal high frequency clock of 41.78 MHz.

This clock is routed through a programmable clock divider

from which the MCU core clock operating frequency is

generated. The microcontroller core is an ARM7TDMI®,

16-bit/32-bit RISC machine, which offers up to 41 MIPS of

peak performance. Thirty-two kilobytes of SRAM and 126 kB

of nonvolatile Flash/EE memory are provided on-chip. The

ARM7TDMI core views all memory and registers as a single

linear array.

The ADuC7124/ADuC7126 contain an advanced interrupt

controller. The vectored interrupt controller (VIC) allows every

interrupt to be assigned a priority level. It also supports nested

interrupts to a maximum level of eight per IRQ and FIQ. When

IRQ and FIQ interrupt sources are combined, a total of 16

nested interrupt levels are supported.

On-chip factory firmware supports in-circuit download via the

UART serial interface port or the I

emulation is also supported via the JTAG interface. These features are incorporated into a low cost QuickStart™ development

system supporting this MicroConverter® family.

The parts contain a 16-bit PWM with six output signals.

For communication purposes, the parts contain 2× I

that can be individually configured for master or slave mode.

An SPI interface supporting both master and slave modes is

also provided. Thirdly, 2× UART channels are provided. Each

UART contains a configurable 16-byte FIFO with receive and

transmit buffers.

The parts operate from 2.7 V to 3.6 V and is specified over an

industrial temperature range of −40°C to +125°C. When operating at 41.78 MHz, the power dissipation is typically 120 mW.

The ADuC7124 is available in a 64-lead LFCSP package. The

ADuC7126 is available in a 80-lead LQFP package.

2

C port, while nonintrusive

2

C channels

Rev. C | Page 4 of 108

Page 5

Data Sheet ADuC7124/ADuC7126

SPECIFICATIONS

AVDD = IOVDD = 2.7 V to 3.6 V, V

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

ADC CHANNEL SPECIFICATIONS Eight acquisition clocks and f

ADC Power-Up Time 5 s

DC Accuracy

1, 2

Resolution 12 Bits

Integral Nonlinearity ±0.6 ±1.5 LSB 2.5 V internal reference

±1.0 LSB 1.0 V external reference

Differential Nonlinearity

3, 4

+0.7/−0.6 LSB 1.0 V external reference

DC Code Distribution 1 LSB ADC input is a dc voltage

5

ENDPOINT ERRORS

Offset Error ±1 ±2 LSB

Offset Error Match ±1 LSB

Gain Error ±2 ±5 LSB

Gain Error Match ±1 LSB

DYNAMIC PERFORMANCE fIN = 10 kHz sine wave, f

Signal-to-Noise Ratio (SNR) 69 dB Includes distortion and noise components

Total Harmonic Distortion (THD) −78 dB

Peak Harmonic or Spurious Noise −75 dB

Channel-to-Channel Crosstalk −90 dB

ANALOG INPUT

Input Voltage Ranges

4

Differential Mode V

Single-Ended Mode 0 to V

Leakage Current ±1 ±6 µA

Input Capacitance 24 pF During ADC acquisition

ON-CHIP VOLTAGE REFERENCE 0.47 µF from V

Output Voltage 2.5 V

Accuracy ±5 mV TA = 25°C

Reference Temperature Coefficient ± 15 p pm/°C

Power Supply Rejection Ratio 80 dB

Output Impedance 45 Ω TA = 25°C

Internal V

Power-On Time 1 ms

REF

EXTERNAL REFERENCE INPUT

Input Voltage Range 0.625

DAC CHANNEL SPECIFICATIONS RL = 5 kΩ, CL = 100 pF

DC Accuracy

7

Resolution 12 Bits

Relative Accuracy ±2 LSB

Differential Nonlinearity ±1 LSB Guaranteed monotonic

Offset Error 10 mV 2.5 V internal reference

Gain Error

8

Gain Error Mismatch 0.1 % % of full scale on DAC0

= 2.5 V internal reference, f

REF

= 41.78 MHz, TA = −40°C to +125°C, unless otherwise noted.

CORE

±0.5 +1/−0.9 LSB 2.5 V internal reference

Measured on adjacent channels; input channels

not being sampled have a 25 kHz sine wave

connected to them

6

± V

CM

AVDD V

/2 V

REF

V

REF

to AGND

REF

1.0 %

SAMPLE

/2

ADC

= 1 MSPS

Rev. C | Page 5 of 108

Page 6

ADuC7124/ADuC7126 Data Sheet

Parameter Min Typ Max Unit Test Conditions/Comments

ANALOG OUTPUTS

Output Voltage Range 0 0 to DAC

Output Voltage Range 1 0 to 2.5 V

Output Voltage Range 2 0 to DACVDD V

Output Impedance 0.5 Ω

DAC IN OP AMP MODE

DAC Output Buffer in Op Amp Mode

Input Offset Voltage ±0.4 mV

Input Offset Voltage Drift 4 µV/°C

Input Offset Current 2 nA

Input Bias Current 2.5 nA

Gain 70 dB 5 kΩ load

Unity Gain Frequency 4.5 MHz RL = 5 kΩ, CL = 100 pF

CMRR 78 dB

Settling Time 12 µs RL = 5 kΩ, CL = 100 pF

Output Slew Rate 3.2 V/µs RL = 5 kΩ, CL = 100 pF

PSRR 75 dB

DAC AC CHARACTERISTICS

Voltage Output Settling Time 10 µs

Digital-to-Analog Glitch Energy ±10 nV-sec

COMPARATOR

Input Offset Voltage ±15 mV

Input Bias Current 1 µA

Input Voltage Range AGND AVDD – 1.2 V

Input Capacitance 8.5 pF

Hysteresis

4, 6

2 15 mV

Response Time 4 µs

TEMPERATURE SENSOR

Voltage Output at 25°C 1.415 V ADuC7124

1.392 V ADuC7126

Voltage Temperature Coefficient 3.914 mV/°C ADuC7124

4.52 mV/°C ADuC7126

Accuracy ±3 °C A single point calibration is required

θJA Thermal Impedance

64-Lead LFCSP

24

POWER SUPPLY MONITOR (PSM)

IOVDD Trip Point Selection 2.79 V Two selectable trip points

3.07 V

Power Supply Trip Point Accuracy ±2.5 % Of the selected nominal trip point voltage

POWER-ON RESET 2.41 V

WATCHD OG T IME R ( WDT )

Timeout Period

0 512 sec

FLASH/EE MEMORY

Endurance

Data Retention

9

10

10,000 Cycles

20 Years TJ = 85°C

DIGITAL INPUTS All digital inputs excluding XCLKI and XCLKO

Logic 1 Input Current ±0.2 ±1 µA VIH = VDD or VIH = 5 V

Logic 0 Input Current −40 −60 µA VIL = 0 V; except TDI, TDO, and RTCK

−80 −120 µA VIL = 0 V; TDI, TDO, and RTCK

Input Capacitance 5 pF

V DAC

REF

°C/W

Rev. C | Page 6 of 108

range: DACGND to DACVDD

REF

1 LSB change at major carry (where maximum

number of bits simultaneously change in the

DACxDAT register)

Hysteresis can be turned on or off via the

CMPHYST bit in the CMPCON register

100 mV overdrive and configured with

CMPRES = 11

Page 7

Data Sheet ADuC7124/ADuC7126

Parameter Min Typ Max Unit Test Conditions/Comments

LOGIC INPUTS

V

, Input Low Voltage 0.8 V

INL

V

, Input High Voltage 2.0 V

INH

LOGIC OUTPUTS All digital outputs excluding XCLKO

VOH, Output High Voltage 2.4 V I

VOL, Output Low Voltage

CRYSTAL INPUTS XCLKI and XCLKO

Logic Inputs, XCLKI Only

V

V

XCLKI Input Capacitance 20 pF

XCLKO Output Capacitance 20 pF

INTERNAL OSCILLATOR 32.768 kHz

±3 %

MCU CLOCK RATE

From 32 kHz Internal Oscillator 326 kHz CD = 7

From 32 kHz External Crystal 41.78 MHz CD = 0

Using an External Clock 0.05 44 MHz TA = 85°C

0.05 41.78 MHz TA = 125°C

START-UP TIME Core clock = 41.78 MHz

At Power-On 66 ms

From Pause/Nap Mode 2.6 µs CD = 0

247 µs CD = 7

From Sleep Mode 1.58 ms

From Stop Mode 1.7 ms

PROGRAMMABLE LOGIC ARRAY (PLA)

Pin Propagation Delay 12 ns From input pin to output pin

Element Propagation Delay 2.5 ns

POWER REQUIREMENTS

Power Supply Voltage Range

AVDD to AGND and IOVDD to IOGND 2.7 3.6 V

Analog Power Supply Currents

AVDD Current 165 µA ADC in idle mode

DACVDD Current

Digital Power Supply Current

IOVDD Current in Active Mode Code executing from Flash/EE

8.1 12.5 mA CD = 7

11.6 17 mA CD = 3

33.3 50 mA CD = 0 (41.78 MHz clock)

IOVDD Current in Pause Mode 20.6 30 mA CD = 0 (41.78 MHz clock)

IOVDD Current in Sleep Mode 110 µA TA = 85°C

600 680 µA TA = 125°C

Additional Power Supply Currents

ADC 1.26 mA At 1 MSPS

0.7 mA At 62.5 kSPS

DAC 315 µA Per DAC

3

All logic inputs excluding XCLKI

11

, Input Low Voltage 0.8 V

INL

, Input High Voltage 1.6 V

INH

4

12, 13

14

0.4 V I

0.02 µA

Rev. C | Page 7 of 108

= 1.6 mA

SOURCE

= 1.6 mA

SINK

Page 8

ADuC7124/ADuC7126 Data Sheet

Parameter Min Typ Max Unit Test Conditions/Comments

ESD TESTS 2.5 V reference, TA = 25°C

HBM Passed Up To 3 kV

FICDM Passed Up To 1.5 kV

1

All ADC channel specifications are guaranteed during normal core operation.

2

Apply to all ADC input channels.

3

Measured using the factory-set default values in the ADC offset register (ADCOF) and gain coefficient register (ADCGN).

4

Not production tested but supported by design and/or characterization data on production release.

5

Measured using the factory-set default values in ADCOF and ADCGN with an external AD845 op amp as an input buffer stage as shown in Figure 37. Based on external ADC

system components, the user may need to execute a system calibration to remove external endpoint errors and achieve these specifications (see the Calibration section).

6

The input signal can be centered on any dc common-mode voltage (VCM) as long as this value is within the ADC voltage input range specified.

7

DAC linearity is calculated using a reduced code range of 100 to 3995.

8

DAC gain error is calculated using a reduced code range of 100 to internal 2.5 V V

9

Endurance is qualified as per JEDEC Standard 22 Method A117 and measured at −40°C, +25°C, +85°C, and +125°C.

10

Retention lifetime equivalent at junction temperature (TJ) = 85°C as per JEDEC Standard 22 Method A117. Retention lifetime derates with junction temperature.

11

Test carried out with a maximum of eight I/Os set to a low output level.

12

Power supply current consumption is measured in normal, pause, and sleep modes under the following conditions: normal mode with 3.6 V supply, pause mode with

3.6 V supply, and sleep mode with 3.6 V supply.

13

IOVDD power supply current increases typically by 2 mA during a Flash/EE erase cycle.

14

This current must be added to the AVDD current.

TIMING SPECIFICATIONS

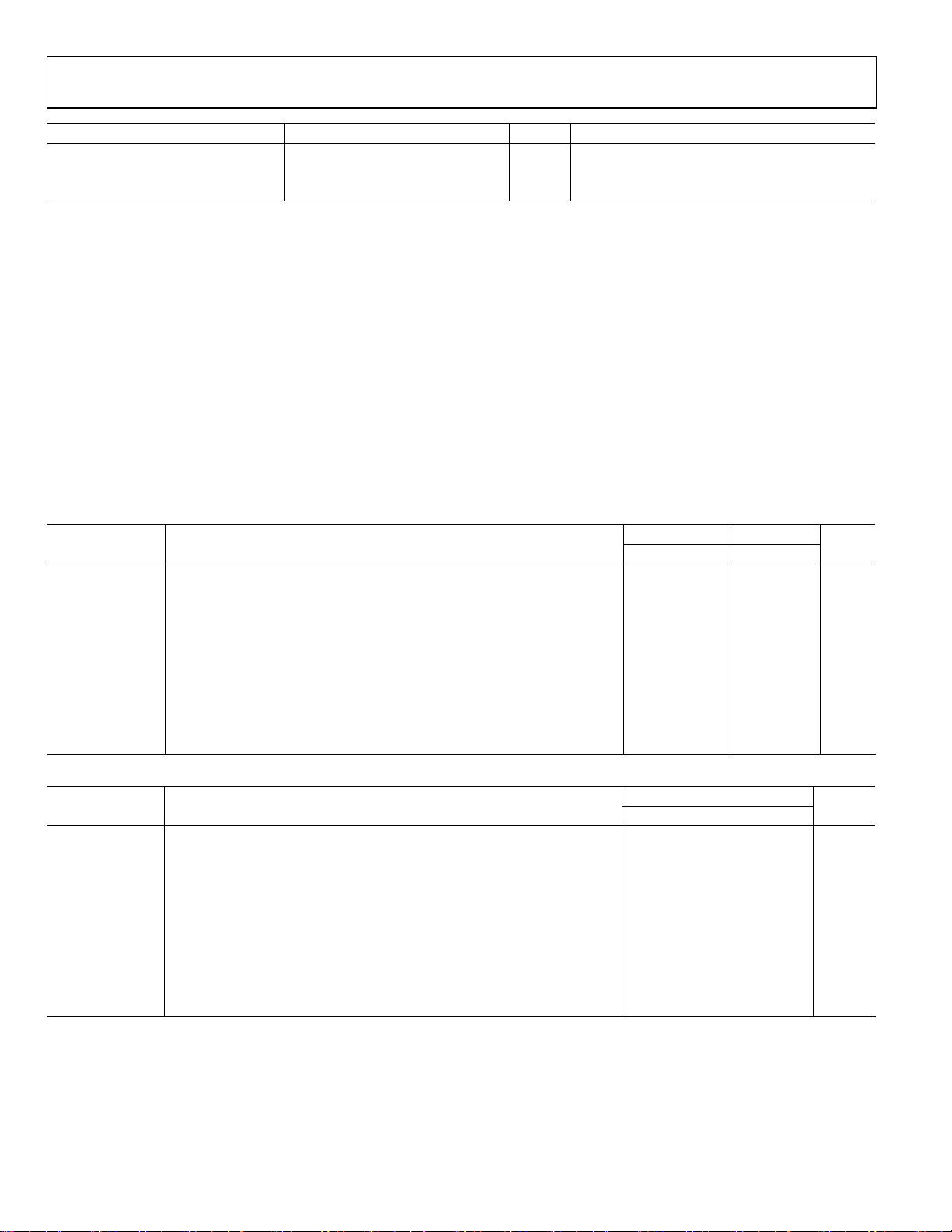

I2C Timing

Table 2. I2C Timing in Fast Mode (400 kHz)

Slave Master

Parameter Description Min Max Typ Unit

tL SCL low pulse width 200 1360 ns

tH SCL high pulse width 100 1140 ns

t

Start condition hold time 300 ns

SHD

t

Data setup time 100 740 ns

DSU

t

Data hold time 0 400 ns

DHD

t

Setup time for repeated start 100 ns

RSU

t

Stop condition setup time 100 800 ns

PSU

t

Bus-free time between a stop condition and a start condition 1.3 µs

BUF

tR Rise time for both SCL and SDA 300 200 ns

tF Fall time for both SCL and SDA 300 ns

.

REF

Table 3. I2C Timing in Standard Mode (100 kHz)

Slave

Parameter Description Min Max Unit

tL SCL low pulse width 4.7 µs

tH SCL high pulse width 4.0 ns

t

Start condition hold time 4.0 µs

SHD

t

Data setup time 250 ns

DSU

t

Data hold time 0 3.45 µs

DHD

t

Setup time for repeated start 4.7 µs

RSU

t

Stop condition setup time 4.0 µs

PSU

t

Bus-free time between a stop condition and a start condition 4.7 µs

BUF

tR Rise time for both SCL and SDA 1 µs

tF Fall time for both SCL and SDA 300 ns

Rev. C | Page 8 of 108

Page 9

Data Sheet ADuC7124/ADuC7126

t

SDA (I/O )

SCL (I)

t

PSU

BUF

PS

STOP

CONDITION

CONDITI ON

START

MSB LSB ACK MSB

t

DSU

t

DHD

t

SHD

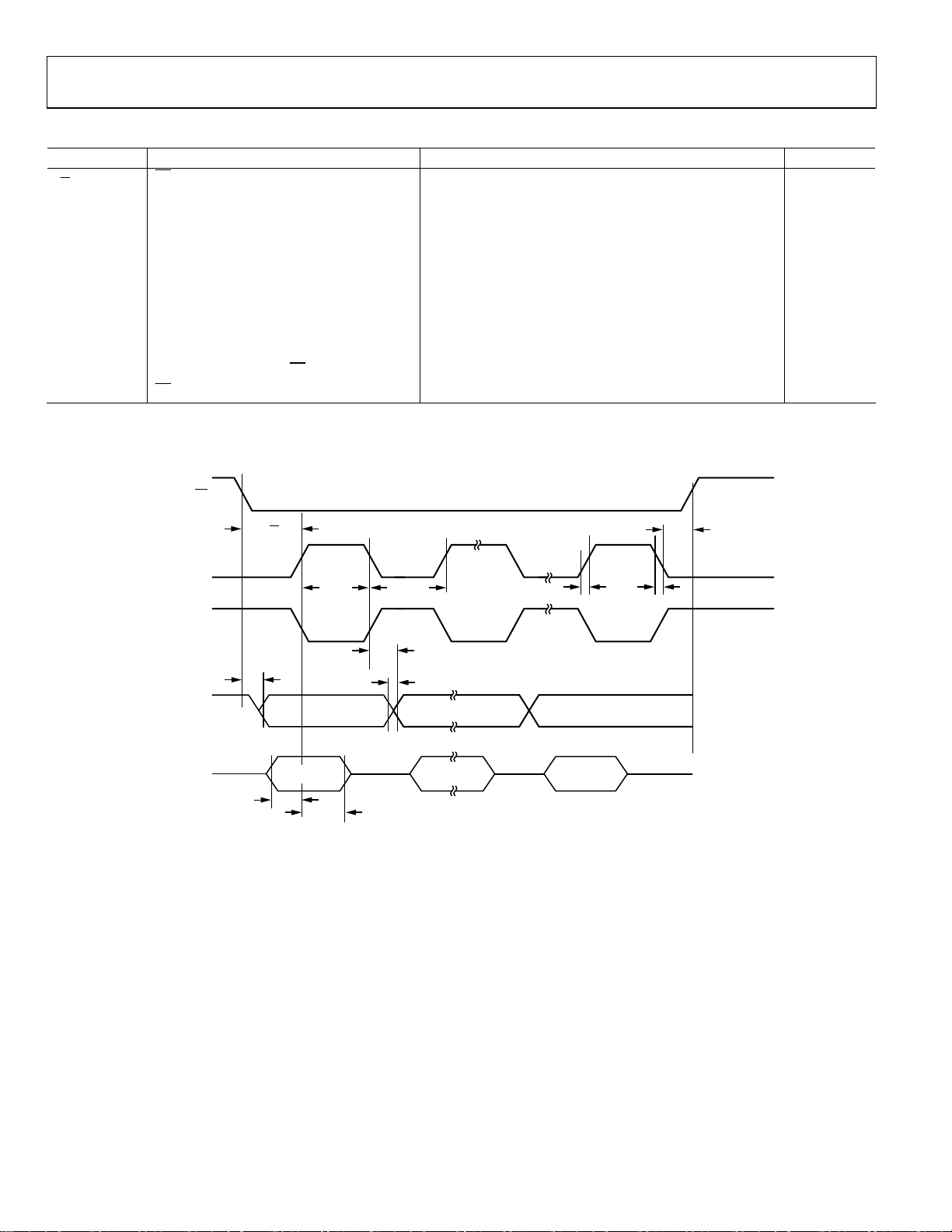

Figure 2. I

t

H

t

L

2

C-Compatible Interface Timing

t

DSU

t

RSU

t

DHD

REPEATED

S(R)

START

t

R

t

F

t

R

1982–71

t

F

9123-029

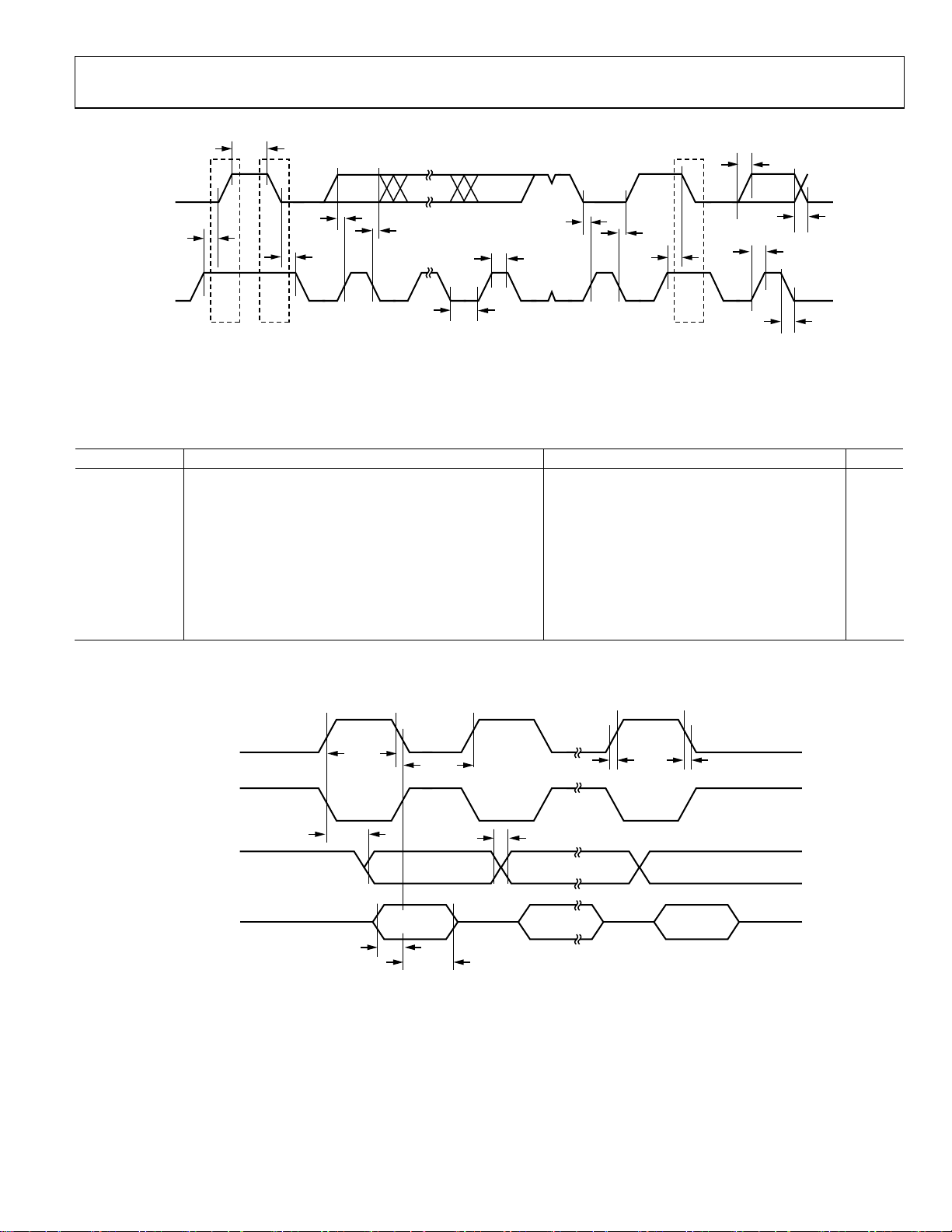

SPI Timing

Table 4. SPI Master Mode Timing (Phase Mode = 1)

Parameter Description Min Typ Max Unit

tSL SCLK low pulse width

tSH SCLK high pulse width

t

Data output valid after SCLK edge 25 ns

DAV

t

Data input setup time before SCLK edge

DSU

t

Data input hold time after SCLK edge

DHD

1

1

(SPIDIV + 1) × t

1

1 × t

1

2 × t

(SPIDIV + 1) × t

ns

UCLK

ns

UCLK

ns

UCLK

ns

UCLK

tDF Data output fall time 5 12.5 ns

tDR Data output rise time 5 12.5 ns

tSR SCLK rise time 5 12.5 ns

tSF SCLK fall time 5 12.5 ns

1

t

= 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

UCLK

SCLK

(POLARI TY = 0)

SCLK

(POLARI TY = 1)

MOSI MSB BIT 6 TO BIT 1 LSB

MISO MSB IN BIT 6 TO BIT 1 LSB IN

t

SH

t

DAV

t

DSU

t

DHD

t

SL

t

DF

t

DR

t

SR

t

SF

9123-030

Figure 3. SPI Master Mode Timing (Phase Mode = 1)

Rev. C | Page 9 of 108

Page 10

ADuC7124/ADuC7126 Data Sheet

Table 5. SPI Master Mode Timing (Phase Mode = 0)

Parameter Description Min Typ Max Unit

tSL SCLK low pulse width

tSH SCLK high pulse width

t

Data output valid after SCLK edge 25 ns

DAV

t

Data output setup before SCLK edge 75 ns

DOSU

t

Data input setup time before SCLK edge

DSU

t

Data input hold time after SCLK edge

DHD

tDF Data output fall time 5 12.5 ns

tDR Data output rise time 5 12.5 ns

tSR SCLK rise time 5 12.5 ns

tSF SCLK fall time 5 12.5 ns

1

t

= 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

UCLK

SCLK

(POLARI TY = 0)

SCLK

(POLARI TY = 1)

MOSI MSB BIT 6 TO BIT 1 LSB

t

DOSU

1

1

1

1

t

SH

t

SL

t

DAV

t

DF

t

DR

(SPIDIV + 1) × t

(SPIDIV + 1) × t

1 × t

ns

UCLK

2 × t

ns

UCLK

t

SR

ns

UCLK

ns

UCLK

t

SF

MISO MSB IN BIT 6 TO BIT 1 LS B IN

t

DSU

t

DHD

Figure 4. SPI Master Mode Timing (Phase Mode = 0)

09123-031

Rev. C | Page 10 of 108

Page 11

Data Sheet ADuC7124/ADuC7126

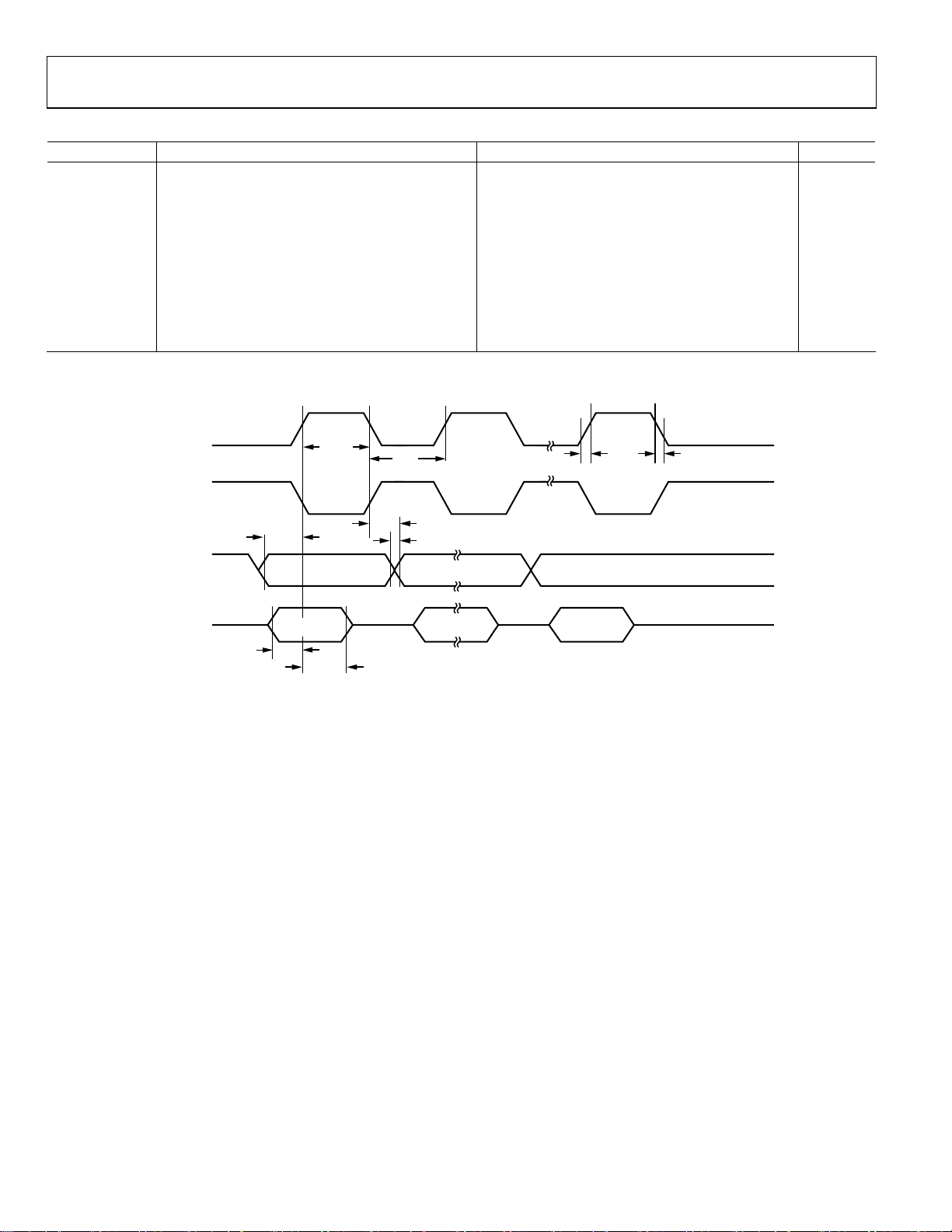

Table 6. SPI Slave Mode Timing (Phase Mode = 1)

Parameter Description Min Typ Max Unit

t

CS

CS to SCLK edge

tSL SCLK low pulse width (SPIDIV + 1) × t

tSH SCLK high pulse width (SPIDIV + 1) × t

t

Data output valid after SCLK edge 25 ns

DAV

t

Data input setup time before SCLK edge

DSU

t

Data input hold time after SCLK edge

DHD

1

1

2 × t

tDF Data output fall time 5 12.5 ns

tDR Data output rise time 5 12.5 ns

tSR SCLK rise time 5 12.5 ns

tSF SCLK fall time 5 12.5 ns

t

SFS

1

t

= 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

UCLK

high after SCLK edge

CS

CS

t

SCLK

(POLARI TY = 0)

SCLK

(POLARI TY = 1)

MISO MSB BIT 6 TO BIT 1 LSB

CS

t

SH

t

DAV

t

SL

t

DF

200 ns

ns

HCLK

ns

HCLK

1 × t

ns

UCLK

ns

UCLK

0 ns

t

SFS

t

SR

t

DR

t

SF

MOSI MSB IN BIT 6 TO BIT 1 L SB IN

t

DSU

t

DHD

09123-132

Figure 5. SPI Slave Mode Timing (Phase Mode = 1)

Rev. C | Page 11 of 108

Page 12

ADuC7124/ADuC7126 Data Sheet

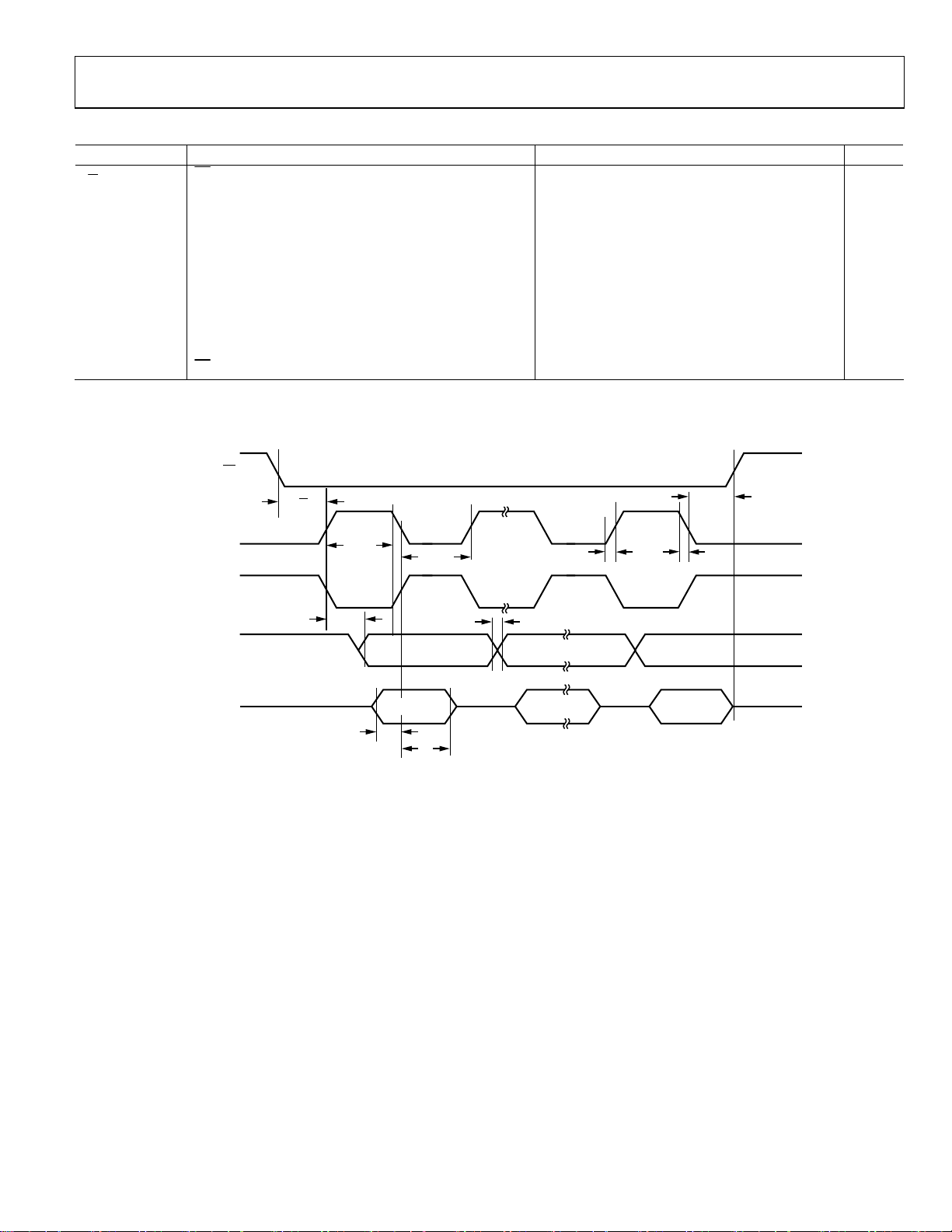

Table 7. SPI Slave Mode Timing (Phase Mode = 0)

Parameter Description Min Typ Max Unit

t

CS

CS to SCLK edge

tSL SCLK low pulse width (SPIDIV + 1) × t

tSH SCLK high pulse width (SPIDIV + 1) × t

t

Data output valid after SCLK edge 25 ns

DAV

t

Data input setup time before SCLK edge1 1 × t

DSU

t

Data input hold time after SCLK edge

DHD

1

2 × t

tDF Data output fall time 5 12.5 ns

tDR Data output rise time 5 12.5 ns

tSR SCLK rise time 5 12.5 ns

tSF SCLK fall time 5 12.5 ns

t

DOCS

t

SFS

1

t

= 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

UCLK

Data output valid after CS

high after SCLK edge

CS

edge

CS

t

CS

SCLK

(POLARI TY = 0)

t

SH

SCLK

(POLARI TY = 1)

t

DAV

t

DF

MISO

t

DOCS

MSB BIT 6 TO BIT 1 LSB

200 ns

ns

HCLK

ns

HCLK

ns

UCLK

ns

UCLK

25 ns

0 ns

t

SFS

t

SL

t

DR

t

SR

t

SF

MOSI

MSB IN BIT 6 TO BI T 1 LSB IN

t

DSU

t

DHD

09123-033

Figure 6. SPI Slave Mode Timing (Phase Mode = 0)

Rev. C | Page 12 of 108

Page 13

Data Sheet ADuC7124/ADuC7126

ABSOLUTE MAXIMUM RATINGS

AGND = GND

otherwise noted.

Table 8.

Parameter Rating

AVDD to IOVDD −0.3 V to +0.3 V

AGND to DGND −0.3 V to +0.3 V

IOVDD to IOGND, AVDD to AGND −0.3 V to +6 V

Digital Input Voltage to IOGND −0.3 V to +5.3 V

Digital Output Voltage to IOGND −0.3 V to IOVDD + 0.3 V

V

to AGND −0.3 V to AVDD + 0.3 V

REF

Analog Inputs to AGND −0.3 V to AV

Analog Outputs to AGND −0.3 V to AVDD + 0.3 V

Operating Temperature Range, Industrial –40°C to +125°C

Storage Temperature Range −65°C to +150°C

Junction Temperature 150°C

θJA Thermal Impedance

64-Lead LFCSP 24°C/W

80-Lead LQFP 38°C/W

Peak Solder Reflow Temperature

SnPb Assemblies (10 sec to 30 sec) 240°C

RoHS Compliant Assemblies

(20 sec to 40 sec)

= DACGND = GND

REF

, TA = 25°C, unless

REF

260°C

+ 0.3 V

DD

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Only one absolute maximum rating can be applied at any one time.

ESD CAUTION

Rev. C | Page 13 of 108

Page 14

ADuC7124/ADuC7126 Data Sheet

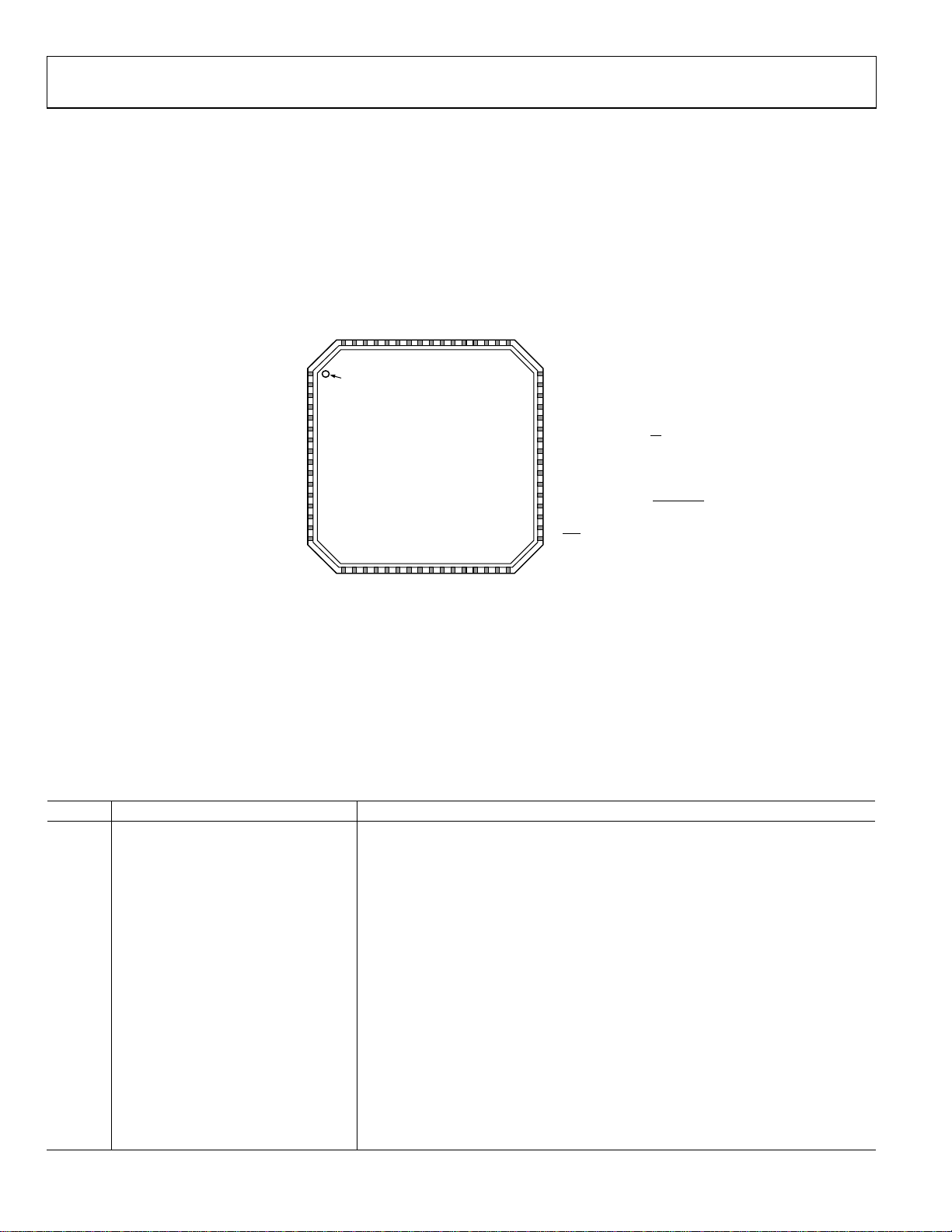

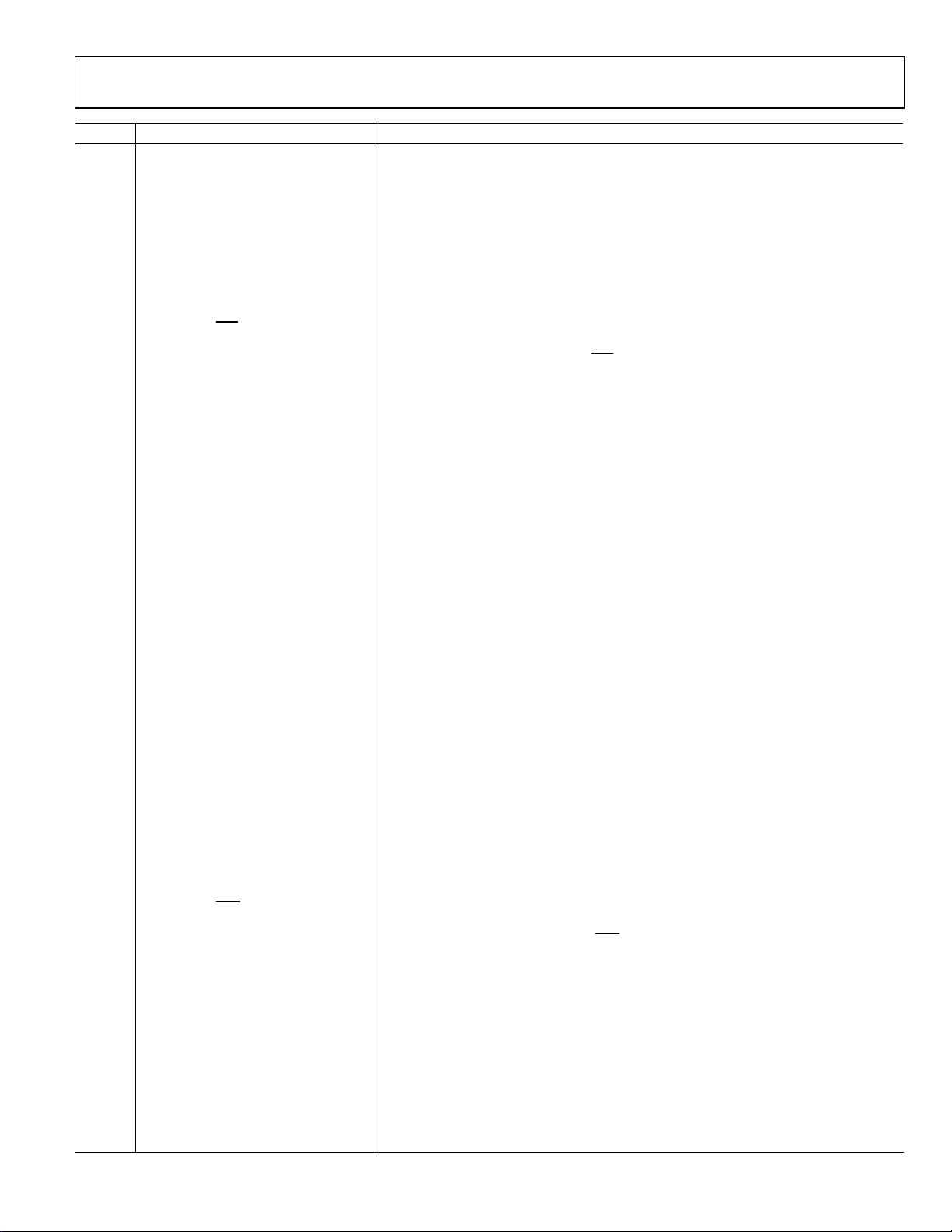

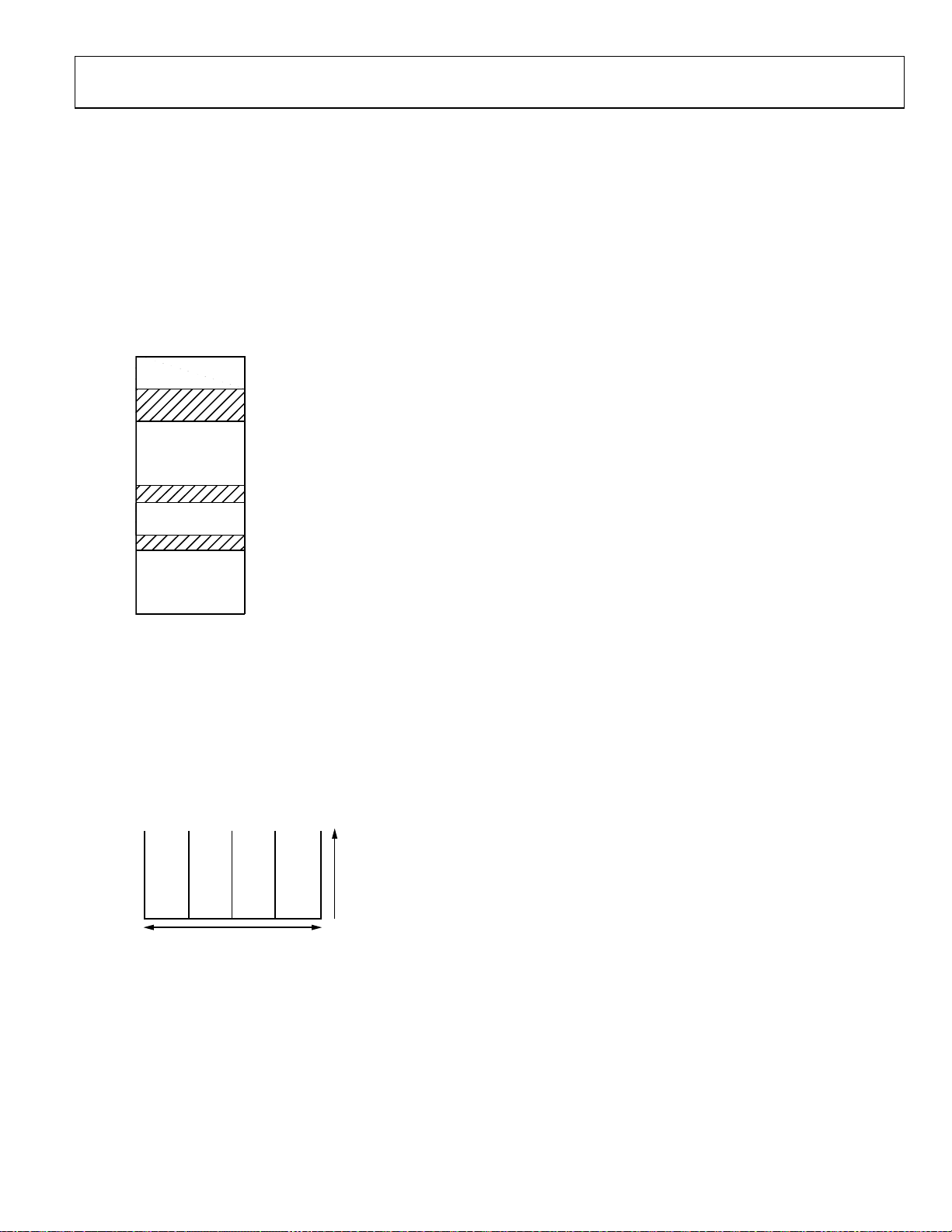

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

REF

REF

GND

AGND

AVDDDAC

V

ADuC7124

TOP VIEW

(Not to Scale)

REF

RTCK

P4.4/PLAO[12]

P4.3/PLAO[11]

P4.2/PLAO[10]

P1.0/T1/SPM0/SIN0/I2C0SCL/PLAI[0]

P1.1/SPM1/SOUT0/ I2C0SDA/PL AI[1]

P1.2/SPM2/RTS/I2C1SCL/ PLAI[2]

49

48

P1.3/SPM3/CTS/I2C1SDA/PLAI[3]

47

P1.4/SPM4/RI/SPICLK/PLAI[4]/IRQ2

46

P1.5/SPM 5/DCD/SPI MISO/ PLAI[5] /IRQ3

45

P4.1/PLAO[9]/SOUT1

44

P4.0/PLAO[8]/SIN1

43

P1.6/SPM6/PLAI[6]

42

P1.7/SPM7/DTR/ SPICS/PLAO[0]

41

P3.7/PWM

P3.6/PWM

40

IOV

39

DD

IOGND

38

P0.7/ECLK/XCLK/SPM8/PLAO[4]/SIN0

37

P2.0/SPM9/PLAO[5]/CONV

36

IRQ1/P0.5/ADC

35

IRQ0/P0.4/PWM

34

RST

33

SYNC

TRIP

/PLAI[15]

/PLAI[14]

/PLAO[2]

BUSY

/PLAO[1]

TRIP

START

/SOUT0

BM/P0.0/ CMP

ADC4

ADC5

ADC6

ADC7

ADC8

ADC9

ADCNEG

DACGND

DACV

DAC0/ADC12

DAC1/ADC13

TMS

TDI

XCLKO

XCLKI

/PLAI[7]

OUT

ADC3/CMP1

ADC2/CMP0

ADC1

ADC0

646362616059585756555453525150

PIN 1

1

INDICATOR

2

3

4

5

6

7

8

9

DD

10

11

12

13

14

15

16

NC = NO CONNECT

NOTES

1. THE EXP OSED PADDLE MUST BE SO LDERED TO THE PCB TO ENSURE PRO PER

HEAT DISSIPATIO N, NOISE , AND MECHANICAL STRENGT H BENEFIT S.

171819202122232425262728293031

DD

DGND

DD

LV

IOV

TCK

IOGND

TDO

P4.6/PLAO[14]

P4.7/PLAO[15]

P3.0/PWM0/PLAI[8]

P0.6/T1/MRST/PLAO[3]

BUSY

P3.1/PWM1/PLAI[9]

P3.3/PWM3/PLAI[11]

P3.2/PW M2/PLAI[10]

P0.3/TRST/ADC

P3.4/PW M4/PLAI[12]

32

P3.5/PW M5/PLAI[13]

09123-107

Figure 7. ADuC7124 Pin Configuration

Table 9. Pin Function Descriptions (ADuC7124 64-Lead LFCSP)

Pin No. Mnemonic Description

0 Exposed Paddle Exposed Paddle. The LFCSP_VQ has an exposed paddle that must be left unconnected.

1 ADC4 Single-Ended or Differential Analog Input 4.

2 ADC5 Single-Ended or Differential Analog Input 5.

3 ADC6 Single-Ended or Differential Analog Input 6.

4 ADC7 Single-Ended or Differential Analog Input 7.

5 ADC8 Single-Ended or Differential Analog Input 8.

6 ADC9 Single-Ended or Differential Analog Input 9.

7 ADCNEG

Bias Point or Negative Analog Input of the ADC in Pseudo Differential Mode. Must be

connected to the ground of the signal to convert. This bias point must be between 0 V

and 1 V.

8 DACGND Ground for the DAC. Typically connected to AGND.

9 DACVDD 3.3 V Power Supply for the DACs. Must be connected to AVDD.

10 DAC0/ADC12

DAC0 Voltage Output (DAC0).

Single-Ended or Differential Analog Input 12 (ADC12).

11 DAC1/ADC13

DAC1 Voltage Output (DAC1).

Single-Ended or Differential Analog Input 13 (ADC13).

12 TMS JTAG Test Port Input, Test Mode Select. Debug and download access.

13 TDI JTAG Test Port Input, Test Data In.

Rev. C | Page 14 of 108

Page 15

Data Sheet ADuC7124/ADuC7126

Pin No. Mnemonic Description

14 XCLKO Output from the Crystal Oscillator Inverter.

15 XCLKI

16 BM/P0.0/CMP

/PLAI[7]

OUT

17 DGND Ground for Core Logic.

18 LVDD

19 IOVDD 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.

20 IOGND Ground for GPIO. Typically connected to DGND.

21 P4.6/PLAO[14]

22 P4.7/PLAO[15]

23 P0.6/T1/MRST/PLAO[3]

24 TCK JTAG Test Port Input, Test Clock. Debug and download access.

25 TDO JTAG Test Port Output, Test Data Out.

26 P3.0/PWM0/PLAI[8]

27 P3.1/PWM1/PLAI[9]

28 P3.2/PWM2/PLAI[10]

29 P3.3/PWM3/PLAI[11]

30 P0.3/TRST/ADC

BUSY

31 P3.4/PWM4/PLAI[12]

32 P3.5/PWM5/PLAI[13]

33

34 IRQ0/P0.4/PWM

RST

/PLAO[1]

TRIP

Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator

Circuits.

Multifunction I/O Pin.

Boot mode (BM). The ADuC7124 enters download mode if BM is low at reset and

executes code if BM is pulled high at reset through a 1 kΩ resistor.

General-Purpose Input and Output Port 0.0 (P0.0).

Voltage Comparator Output (CMP

OUT

)

Programmable Logic Array Input Element 7 (PLAI[7]).

2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a

0.47 µF capacitor to DGND only.

General-Purpose Input and Output Port 4.6 (P4.6).

Programmable Logic Array Output Element 14 (PLAO[14]).

General-Purpose Input and Output Port 4.7 (P4.7).

Programmable Logic Array Output Element 15 (PLAO[15]).

Multifunction Pin, Driven Low After Reset.

General-Purpose Output Port 0.6 (P0.6).

Timer1 Input (T1).

Power-On Reset Output (MRST).

Programmable Logic Array Output Element 3 (PLAO[3]).

General-Purpose Input and Output Port 3.0 (P3.0).

PWM Phase 0 (PWM0).

Programmable Logic Array Input Element 8 (PLAI[8]).

General-Purpose Input and Output Port 3.1 (P3.1).

PWM Phase 1 (PWM1).

Programmable Logic Array Input Element 9 (PLAI[9]).

General-Purpose Input and Output Port 3.2 (P3.2).

PWM Phase 2 (PWM2).

Programmable Logic Array Input Element 10 (PLAI[10]).

General-Purpose Input and Output Port 3.3 (P3.3).

PWM Phase 3 (PWM3).

Programmable Logic Array Input Element 11 (PLAI[11]).

General-Purpose Input and Output Port 0.3 (P0.3).

JTAG Test Port Input, Test Reset (TRST). JTAG reset input. Debug and download access. If

this pin is held low, JTAG access is not possible because the JTAG interface is held in reset

and P0.1/P0.2/P0.3 are configured as GPIO pins.

Signal Output (ADC

ADC

BUSY

BUSY

).

General-Purpose Input and Output Port 3.4 (P3.4).

PWM Phase 4 (PWM4).

Programmable Logic Array Input 12 (PLAI[12]).

General-Purpose Input and Output Port 3.5 (P3.5).

PWM Phase 5 (PWM5).

Programmable Logic Array Input Element 13 (PLAI[13]).

Reset Input, Active Low.

Multifunction I/O Pin.

External Interrupt Request 0, Active High (IRQ0).

General-Purpose Input and Output Port 0.4 (P0.4).

PWM Trip External Input (PWM

TRIP

).

Programmable Logic Array Output Element 1 (PLAO[1]).

Rev. C | Page 15 of 108

Page 16

ADuC7124/ADuC7126 Data Sheet

Pin No. Mnemonic Description

35 IRQ1/P0.5/ADC

36

P2.0/SPM9/PLAO[5]/CONV

37 P0.7/ECLK/XCLK/SPM8/PLAO[4]/SIN0

38 IOGND Ground for GPIO. Typically connected to DGND.

39 IOVDD 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.

40 P3.6/PWM

41 P3.7/PWM

42

P1.7/SPM7/DTR/SPICS

TRIP

SYNC

43 P1.6/SPM6/PLAI[6]

44 P4.0/PLAO[8]/SIN1

45 P4.1/PLAO[9]/SOUT1

46 P1.5/SPM5/DCD/SPIMISO/PLAI[5]/IRQ3

47 P1.4/SPM4/RI/SPICLK/PLAI[4]/IRQ2

48 P1.3/SPM3/CTS/I2C1SDA/PLAI[3]

49 P1.2/SPM2/RTS/I2C1SCL/PLAI[2]

/PLAO[2]

BUSY

/PLAI[14]

/PLAI[15]

Multifunction I/O Pin.

External Interrupt Request 1, Active High (IRQ1).

General-Purpose Input and Output Port 0.5 (P0.5).

Signal Output (ADC

ADC

BUSY

BUSY

).

Programmable Logic Array Output Element 2 (PLAO[2]).

/SOUT0 General-Purpose Input and Output Port 2.0 (P2.0).

START

Serial Port Multiplexed (SPM9).

Programmable Logic Array Output Element 5 (PLAO[5]).

Start Conversion Input Signal for ADC (CONV

START

UART0 Output (SOUT0).

General-Purpose Input and Output Port 0.7 (P0.7).

Output for External Clock Signal (ECLK).

Input to the Internal Clock Generator Circuits (XCLK).

Serial Port Multiplexed (SPM8).

Programmable Logic Array Output Element 4 (PLAO[4]).

UART0 Input (SIN0).

General-Purpose Input and Output Port 3.6 (P3.6).

PWM Safety Cutoff (PWM

TRIP

).

Programmable Logic Array Input Element 14 (PLAI[14]).

General-Purpose Input and Output Port 3.7 (P3.7).

PWM Synchronization Input/Output (PWM

SYNC

).

Programmable Logic Array Input Element 15 (PLAI[15]).

/PLAO[0] General-Purpose Input and Output Port 1.7 (P1.7).

Serial Port Multiplexed. UART, SPI (SPM7).

Data Terminal Ready (DTR).

Chip Select (SPICS).

Programmable Logic Array Output Element 0 (PLAO[0]).

General-Purpose Input and Output Port 1.6 (P1.6).

Serial Port Multiplexed (SPM6).

Programmable Logic Array Input Element 6 (PLAI[6]).

General-Purpose Input and Output Port 4.0 (P4.0).

Programmable Logic Array Output Element 8 (PLAO[8]).

UART1 Input (SIN1).

General-Purpose Input and Output Port 4.1 (P4.1).

Programmable Logic Array Output Element 9 (PLAO[9]).

UART1 Output (SOUT1).

General-Purpose Input and Output Port 1.5 (P1.5).

Serial Port Multiplexed. UART, SPI (SPM5).

Data Carrier Detect (DCD).

Master Input, Slave Output (SPI MISO).

Programmable Logic Array Input Element 5 (PLAI[5]).

External Interrupt Request 3, Active High (IRQ3).

General-Purpose Input and Output Port 1.4 (P1.4).

Serial Port Multiplexed. UART, SPI (SPM4).

Ring Indicator (RI).

Serial Clock Input/Output (SPI SCLK).

Programmable Logic Array Input Element 4 (PLAI[4]).

External Interrupt Request 2, Active High (IRQ2).

General-Purpose Input and Output Port 1.3 (P1.3).

Serial Port Multiplexed. UART, I2C1 (SPM3).

Clear to Send (CTS).

I2C1 (I2C1SDA).

Programmable Logic Array Input Element 3 (PLAI[3]).

General-Purpose Input and Output Port 1.2 (P1.2).

Serial Port Multiplexed (SPM2).

Ready to Send (RTS).

I2C1 (I2C1SCL).

Programmable Logic Array Input Element 2 (PLAI[2]).

).

Rev. C | Page 16 of 108

Page 17

Data Sheet ADuC7124/ADuC7126

Pin No. Mnemonic Description

50 P1.1/SPM1/SOUT0/I2C0SDA/PLAI[1]

51 P1.0/T1/SPM0/SIN0/I2C0SCL/PLAI[0]

52 P4.2/PLAO[10]

53 P4.3/PLAO[11]

54 P4.4/PLAO[12]

55 RTCK JTAG Test Port Output, JTAG Return Test Clock.

56 V

57 DAC

REF

External Voltage Reference for the DACs. Range: DACGND to DACVDD.

REF

58 AVDD 3.3 V Analog Power.

59 AGND Analog Ground. Ground reference point for the analog circuitry.

60 GND

REF

61 ADC0 Single-Ended or Differential Analog Input 0.

62 ADC1 Single-Ended or Differential Analog Input 1.

63 ADC2/CMP0

64 ADC3/CMP1

General-Purpose Input and Output Port 1.1 (P1.1).

Serial Port Multiplexed (SPM1).

UART download pin, UART0 Output (SOUT0).

I2C0 (I2C0SDA).

Programmable Logic Array Input Element 1 (PLAI[1]).

General-Purpose Input and Output Port 1.0 (P1.0).

Timer1 Input (T1).

Serial Port Multiplexed (SPM0).

UART download pin, UART0 Input (SIN0).

I2C0 (I2C0SCL).

Programmable Logic Array Input Element 0 (PLAI[0]).

General-Purpose Input and Output Port 4.2 (P4.2).

Programmable Logic Array Output Element 10 (PLAO[10]).

General-Purpose Input and Output Port 4.3 (P4.3).

Programmable Logic Array Output Element 11 (PLAO[11]).

General-Purpose Input and Output Port 4.4 (P4.4).

Programmable Logic Array Output Element 12 (PLAO[12]).

2.5 V Internal Voltage Reference. Must be connected to a 0.47 µF capacitor when using

the internal reference.

Ground Voltage Reference for the ADC. For optimal performance, the analog power

supply should be separated from IOGND and DGND.

Single-Ended or Differential Analog Input 2 (ADC2).

Comparator Positive Input (CMP0).

Single-Ended or Differential Analog Input 3 (ADC3).

Comparator Negative Input (CMP1).

Rev. C | Page 17 of 108

Page 18

ADuC7124/ADuC7126 Data Sheet

BM/P0.0/CMP

ADC4

ADC5

ADC6

ADC7

ADC8

ADC9

ADC10

ADCNEG

DACGND

DACV

DAC0/ADC12

DAC1/ADC13

DAC2/ADC14

DAC3/ADC15

TMS

P0.1/PWM4/BLE

XCLKO

XCLKI

/PLAI[7]/MS0

OUT

TDI

REF

ADC3/CMP179ADC2/CMP078ADC177ADC076ADC1175GND

80

1

PIN 1

2

3

4

5

6

7

8

9

10

DD

11

12

13

14

15

16

17

18

19

20

21

22

23

24

DD

DD

LV

IOV

DGND

AGND73AGND72AV

74

25

27

IOGND

DD

71

ADuC7126

TOP VIEW

30

28

29

TCK

TDO

REF

DAC

DD

REF

V

IOGND68IOV

70

31

P4.5/AD13/PL AO[13]/RT CK66P4.4/AD12/PL AO[12]65P4.3/AD11/PLAO[11]64P4.2/AD10/PL AO[10]63P1.0/T1/SPM0/SIN0/I2C0SCL/PLAI[0]62P1.1/SPM1/SOUT0/I2C0SDA/PLAI[1]61P1.2/SPM2/RTS/I2C1SCL/PLAI[2]

69

67

33

34

60

P1.3/SPM3/CTS/I 2C1SDA/PLAI[3]

59

P1.4/SPM4/RI/SPICLK/PLAI[4]/IRQ2

58

P1.5/SPM5/ DCD/SPIMI SO/PL AI[5]/IRQ3

57

P4.1/SPM11/SOUT1/AD9/PLAO[9]

56

P4.0/SPM10/SIN1/AD8/PLAO[8]

55

P1.6/SPM6/PLAI[6]

54

P1.7/SPM7/DTR/SPI CS/PLAO[0]

53

P3.7/AD7/PWM

52

P3.6/AD6/PWM

51

P2.2/RS/PWM1/PLAO[7]

50

P2.1/WS/PWM0/PLAO[6]

49

P2.3/SPM12/AE/SIN1

48

IOV

DD

47

IOGND

46

P0.7/SPM8/ECLK/XCLK/PLAO[4]/SIN0

45

P2.0/SPM9/PLAO[5]/CONV

44

P2.7/PWM3/MS3

43

IRQ1/P0.5/ADC

42

IRQ0/P0.4/PWM

41

RST

35

36

37

39

BUSY

/PLAI[15]

SYNC

/PLAI[14]

TRIP

/PLAO[2]/MS2

BUSY

/PLAO[1]/MS1

TRIP

START

/SOUT0

P0.2/PWM5/BHE

P2.5/PWM1/MS138P2.6/PWM2/MS2

P4.6/AD14/PLAO[14]26P4.7/AD15/PLAO[15]

P3.0/AD0/PWM0/PLAI[8]32P3.1/AD1/PWM1/PLAI[9]

P0.6/T1/MRST/PLAO[3]/MS3

P3.2/AD2/PWM2/PLAI[10]

P0.3/TRST/A16/ADC

P3.3/AD3/P WM3/PL AI[11]

P3.4/AD4/PWM4/PLAI[12]40P3.5/AD5/PWM5/PLAI[13]

P2.4/SPM13/PWM0/MS0/SOUT1

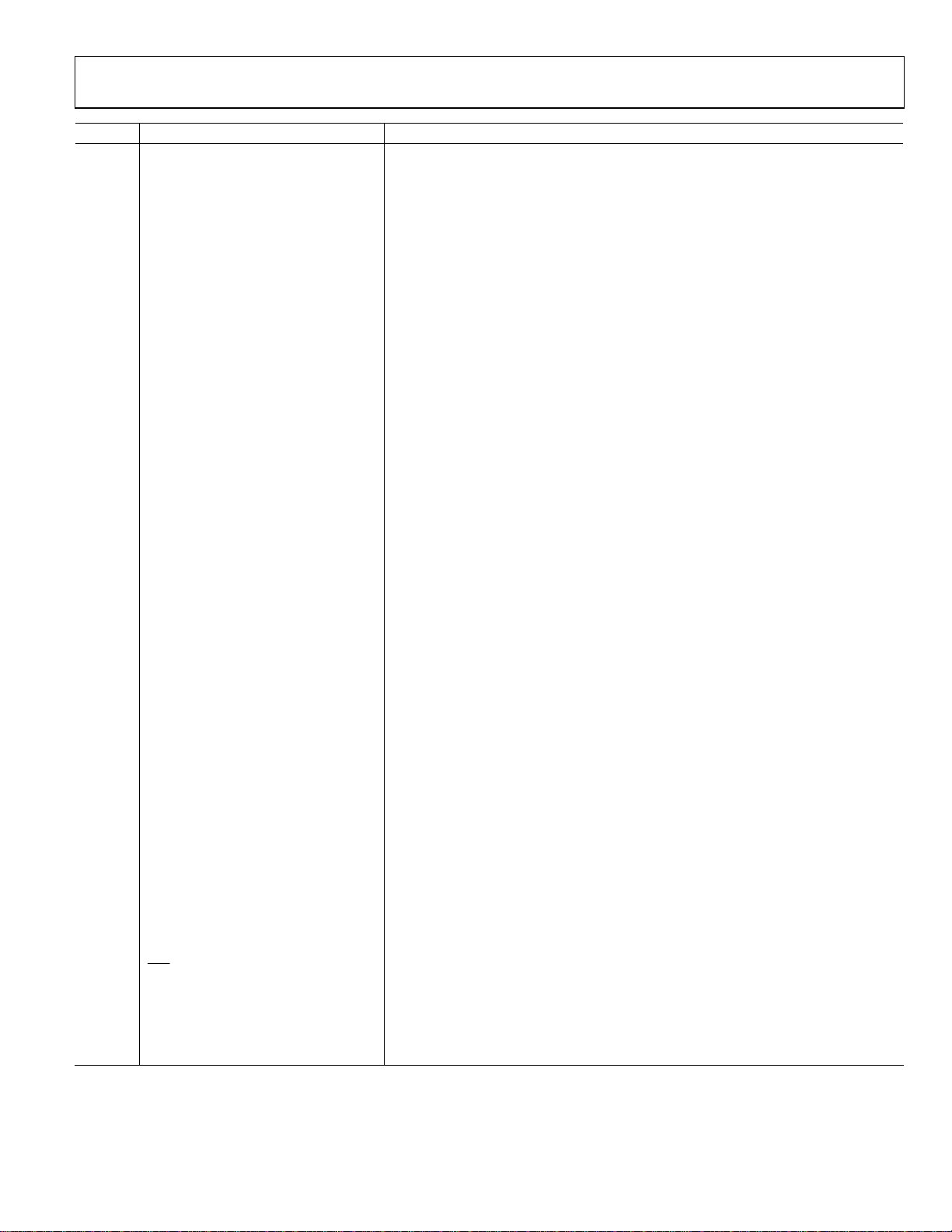

Figure 8. ADuC7126 Pin Configuration

Table 10. Pin Function Descriptions (ADuC7126 80-Lead LQFP)

Pin No. Mnemonic Description

1 ADC4 Single-Ended or Differential Analog Input 4.

2 ADC5 Single-Ended or Differential Analog Input 5.

3 ADC6 Single-Ended or Differential Analog Input 6.

4 ADC7 Single-Ended or Differential Analog Input 7.

5 ADC8 Single-Ended or Differential Analog Input 8.

6 ADC9 Single-Ended or Differential Analog Input 9.

7 ADC10 Single-Ended or Differential Analog Input 10.

8 ADCNEG

Bias Point or Negative Analog Input of the ADC in Pseudo Differential Mode. Must be

connected to the ground of the signal to convert. This bias point must be between 0 V

and 1 V.

9 DACGND Ground for the DAC. Typically connected to AGND.

10 DACVDD 3.3 V Power Supply for the DACs. Must be connected to AVDD.

Rev. C | Page 18 of 108

09123-108

Page 19

Data Sheet ADuC7124/ADuC7126

Pin No. Mnemonic Description

11 DAC0/ADC12

12 DAC1/ADC13

13 DAC2/ADC14

14 DAC3/ADC15

15 TMS JTAG Test Port Input, Test Mode Select. Debug and download access.

16 TDI JTAG Test Port Input, Test Data In. Debug and download access.

17

P0.1/PWM4/BLE

General-Purpose Input and Output Port 0.1 (P0.1).

18 XCLKO Output from the Crystal Oscillator Inverter.

19 XCLKI

20 BM/P0.0/CMP

/PLAI[7]/MS0

OUT

21 DGND Ground for Core Logic.

22 LVDD

23 IOVDD 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.

24 IOGND Ground for GPIO. Typically connected to DGND.

25 P4.6/AD14/PLAO[14]

26 P4.7/AD15/PLAO[15]

27 P0.6/T1/MRST/PLAO[3]/MS3

28 TCK JTAG Test Port Input, Test Clock. Debug and download access.

29 TDO JTAG Test Port Output, Test Data Out. Debug and download access.

30

P0.2/PWM5/BHE

31 P3.0/AD0/PWM0/PLAI[8]

32 P3.1/AD1/PWM1/PLAI[9]

33 P3.2/AD2/PWM2/PLAI[10]

DAC0 Voltage Output (DAC0).

Single-Ended or Differential Analog Input 12 (ADC12).

DAC1 Voltage Output (DAC1).

Single-Ended or Differential Analog Input 13 (ADC13).

DAC2 Voltage Output (DAC2).

Single-Ended or Differential Analog Input 14 (ADC14).

DAC3 Voltage Output (DAC3).

Single-Ended or Differential Analog Input 15 (ADC15).

PWM Phase 4 (PWM4).

External Memory Byte Low Enable (BLE).

Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator

Circuits.

Multifunction I/O Pin.

Boot Mode Entry Pin (BM). The ADuC7126 enters UART download mode if BM is low at

reset and executes code if BM is pulled high at reset through a 1 kΩ resistor.. The

ADuC7126 enters I2C download mode in I2C version parts if BM is low at reset with a

flash address of 0x800014 = 0xFFFFFFFFF. The ADuC7126 executes code if BM is pulled

high at reset or if BM is low at reset with a flash address 0x800014 ≠ 0xFFFFFFFFF.

General-Purpose Input and Output Port 0.0 (P0.0).

Voltage Comparator Output/Programmable Logic Array Input Element 7 (CMP

OUT

).

External Memory Select 0 (MS0). By default, this pin is configured as GPIO.

2.6 V Output of the On-Chip Voltage Regulator. This output must be connected to a 0.47

µF capacitor to DGND only.

General-Purpose Input and Output Port 4.6 (P4.6).

External Memory Interface (AD14).

Programmable Logic Array Output Element 14 (PLAO[14]).

General-Purpose Input and Output Port 4.7 (P4.7).

External Memory Interface (AD15).

Programmable Logic Array Output Element 15 (PLAO[15]).

Multifunction Pin, Driven Low After Reset.

General-Purpose Output Port 0.6 (P0.6).

Timer1 Input (T1).

Power-On Reset Output (MRST).

Programmable Logic Array Output Element 3 (PLAO[3]).

External Memory Select 3 (MS3).

General-Purpose Input and Output Port 0.2 (P0.2).

PWM Phase 5 (PWM5).

External Memory Byte High Enable (BHE).

General-Purpose Input and Output Port 3.0 (P3.0).

External Memory Interface (AD0).

PWM Phase 0 (PWM0).

Programmable Logic Array Input Element 8 (PLAI[8]).

General-Purpose Input and Output Port 3.1 (P3.1).

External Memory Interface (AD1).

PWM Phase 1 (PWM1).

Programmable Logic Array Input Element 9 (PLAI[9]).

General-Purpose Input and Output Port 3.2 (P3.2).

External Memory Interface (AD2).

PWM Phase 2 (PWM2).

Programmable Logic Array Input Element 10 (PLAI[10]).

Rev. C | Page 19 of 108

Page 20

ADuC7124/ADuC7126 Data Sheet

Pin No. Mnemonic Description

34 P3.3/AD3/PWM3/PLAI[11]

35 P2.4/SPM13/PWM0/MS0/SOUT1

36 P0.3/TRST/A16/ADC

BUSY

37 P2.5/PWM1/MS1

38 P2.6/PWM2/MS2

39 P3.4/AD4/PWM4/PLAI[12]

40 P3.5/AD5/PWM5/PLAI[13]

41

42 IRQ0/P0.4/PWM

43 IRQ1/P0.5/ADC

RST

/PLAO[1]/MS1

TRIP

/PLAO[2]/MS2

BUSY

44 P2.7/PWM3/MS3

45

P2.0/SPM9/PLAO[5]/

CONV

START

/SOUT0

46 P0.7/SPM8/ECLK/XCLK/PLAO[4]/SIN0

47 IOGND Ground for GPIO. Typically connected to DGND.

48 IOVDD 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.

General-Purpose Input and Output Port 3.3 (P3.3).

External Memory Interface (AD3).

PWM Phase 3 (PWM3).

Programmable Logic Array Input Element 11 (PLAI[11]).

General-Purpose Input and Output Port 2.4 (P2.4).

Serial Port Multiplexed (SPM13)

PWM Phase 0 (PWM0).

External Memory Select 0 (MS0).

UART1 Output (SOUT1).

General-Purpose Input and Output Port 0.3 (P0.3).

JTAG Test Port Input, Test Reset (TRST).JTAG Reset Input. Debug and download access. If

this pin is held low, JTAG access is not possible because the JTAG interface is held in

reset and P0.1/P0.2/P0.3 are configured as GPIO pins.

Address Line (A16).

ADC

Signal Output (ADC

BUSY

BUSY

).

General-Purpose Input and Output Port 2.5 (P2.5).

PWM Phase 1 (PWM1).

External Memory Select 1 (MS1).

General-Purpose Input and Output Port 2.6 (P2.6).

PWM Phase 2 (PWM2).

External Memory Select 2 (MS2).

General-Purpose Input and Output Port 3.4 (P3.4).

External Memory Interface (AD4).

PWM Phase 4 (PWM4).

Programmable Logic Array Input 12 (PLAI[12]).

General-Purpose Input and Output Port 3.5 (P3.5).

External Memory Interface (AD5).

PWM Phase 5 (PWM5).

Programmable Logic Array Input Element 13 (PLAI[13]).

Reset Input, Active Low.

Multifunction I/O Pin.

External Interrupt Request 0, Active High (IRQ0).

General-Purpose Input and Output Port 0.4 (P0.4).

PWM Trip External Input (PWM

TRIP

).

Programmable Logic Array Output Element 1 (PLAO[1]).

External Memory Select 1 (MS1)..

Multifunction I/O Pin.

External Interrupt Request 1, Active High (IRQ1).

General-Purpose Input and Output Port 0.5 (P0.5).

ADC

Signal Output (ADC

BUSY

BUSY

).

Programmable Logic Array Output Element 2 (PLAO[2]).

External Memory Select 2 (MS2).

General-Purpose Input and Output Port 2.7 (P2.7).

PWM Phase 3 (PWM3).

External Memory Select 3 (MS3).

General-Purpose Input and Output Port 2.0 (P2.0).

Serial Port Multiplexed (SPM9).

Programmable Logic Array Output Element 5 (PLAO[5]).

CONV

START

Start Conversion Input Signal for ADC (

).

UART0 Output (SOUT0).

General-Purpose Input and Output Port 0.7 (P0.7).

Serial Port Multiplexed (SPM8).

Output for External Clock Signal (ECLK).

Input to the Internal Clock Generator Circuits (XCLK).

Programmable Logic Array Output Element 4 (PLAO[4]).

UART0 Input (SIN0).

Rev. C | Page 20 of 108

Page 21

Data Sheet ADuC7124/ADuC7126

Pin No. Mnemonic Description

49 P2.3/SPM12/AE/SIN1

50

51

P2.1/WS

P2.2/RS

52 P3.6/AD6/PWM

53 P3.7/AD7/PWM

54

P1.7/SPM7/DTR/SPICS

/PWM0/PLAO[6] General-Purpose Input and Output Port 2.1 (P2.1).

/PWM1/PLAO[7] General-Purpose Input and Output Port 2.2 (P2.2).

/PLAI[14]

TRIP

/PLAI[15]

SYNC

/PLAO[0] General-Purpose Input and Output Port 1.7 (P1.7).

55 P1.6/SPM6/PLAI[6]

56 P4.0/SPM10/SIN1/AD8/PLAO[8]

57 P4.1/SPM11/SOUT1/AD9/PLAO[9]

58 P1.5/SPM5/DCD/SPIMISO/PLAI[5]/IRQ3

59 P1.4/SPM4/RI/SPICLK/PLAI[4]/IRQ2

60 P1.3/SPM3/CTS/I2C1SDA/PLAI[3]

61 P1.2/SPM2/RTS/I2C1SCL/PLAI[2]

General-Purpose Input and Output Port 2.3 (P2.3).

Serial Port Multiplexed (SPM12).

External Memory Access Enable (AE).

UART1 Input (SIN1).

External Memory Write Strobe (WS

).

PWM Phase 0 (PWM0).

Programmable Logic Array Output Element 6 (PLAO[6]).

External Memory Read Strobe (RS

).

PWM Phase 1 (PWM1).

Programmable Logic Array Output Element 7 (PLAO[7]).

General-Purpose Input and Output Port 3.6 (P3.6).

External Memory Interface (AD6).

PWM Safety Cutouff (PWM

TRIP

).

Programmable Logic Array Input Element 14 (PLAI[14]).

General-Purpose Input and Output Port 3.7 (P3.7).

External Memory Interface (AD7).

PWM Synchronization (PWM

SYNC

).

Programmable Logic Array Input Element 15 (PLAI[15]).

Serial Port Multiplexed (SPM7).

Data Terminal Ready (DTR).

Chip Select (SPICS

).

Programmable Logic Array Output Element 0 (PLAO[0]).

General-Purpose Input and Output Port 1.6 (P1.6).

Serial Port Multiplexed (SPM6).

Programmable Logic Array Input Element 6 (PLAI[6]).

General-Purpose Input and Output Port 4.0 (P4.0).

Serial Port Multiplexed (SPM10).

UART1 Input (SIN1).

External Memory Interface (AD8).

Programmable Logic Array Output Element 8 (PLAO[8]).

General-Purpose Input and Output Port 4.1 (P4.1).

Serial Port Multiplexed (SPM11).

UART1 Output (SOUT1).

External Memory Interface (AD9).

Programmable Logic Array Output Element 9 (PLAO[9]).

General-Purpose Input and Output Port 1.5 (P1.5).

Serial Port Multiplexed (SPM5).

Data Carrier Detect (DCD).

Master Input, Slave Output (SPI MISO).

Programmable Logic Array Input Element 5 (PLAI[5]).

External Interrupt Request 3, Active High (IRQ3).

General-Purpose Input and Output Port 1.4 (P1.4).

Serial Port Multiplexed (SPM4).

Ring Indicator (RI).

Serial Clock Input/Output (SPI SCLK).

Programmable Logic Array Input Element 4 (PLAI[4]).

External Interrupt Request 2, Active High (IRQ2).

General-Purpose Input and Output Port 1.3 (P1.3).

Serial Port Multiplexed (SPM3).

Clear to Send (CTS).

I2C1 (I2C1SDA).

Programmable Logic Array Input Element 3 (PLAI[3]).

General-Purpose Input and Output Port 1.2 (P1.2).

Serial Port Multiplexed (SPM2).

Ready to Send (RTS).

I2C1 (I2C1SCL).

Programmable Logic Array Input Element 2 (PLAI[2]).

Rev. C | Page 21 of 108

Page 22

ADuC7124/ADuC7126 Data Sheet

Pin No. Mnemonic Description

62 P1.1/SPM1/SOUT0/I2C0SDA/PLAI[1]

63 P1.0/T1/SPM0/SIN0/I2C0SCL/PLAI[0]

64 P4.2/AD10/PLAO[10]

65 P4.3/AD11/PLAO[11]

66 P4.4/AD12/PLAO[12]

67 P4.5/AD13/PLAO[13]/RTCK

68 IOVDD 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.

69 IOGND Ground for GPIO. Typically connected to DGND.

70 V

71 DAC

REF

External Voltage Reference for the DACs. Range: DACGND to DACVDD.

REF

72 AVDD 3.3 V Analog Power.

73, 74 AGND Analog Ground. Ground reference point for the analog circuitry.

75 GND

REF

76 ADC11 Single-Ended or Differential Analog Input 11.

77 ADC0 Single-Ended or Differential Analog Input 0.

78 ADC1 Single-Ended or Differential Analog Input 1.

79 ADC2/CMP0

80 ADC3/CMP1

General-Purpose Input and Output Port 1.1 (P1.1).

Serial Port Multiplexed (SPM1).

UART0 Output (SOUT0).

I2C0 (I2C0SDA).

Programmable Logic Array Input Element 1 (PLAI[1]).

General-Purpose Input and Output Port 1.0 (P1.0).

Timer1 Input (T1).

Serial Port Multiplexed (SPM0).

UART0 Input (SIN0).

I2C0 (I2C0SCL).

Programmable Logic Array Input Element 0 (PLAI[0]).

General-Purpose Input and Output Port 4.2 (P4.2).

External Memory Interface (AD10).

Programmable Logic Array Output Element 10 (PLAO[10]).

General-Purpose Input and Output Port 4.3 (P4.3).

External Memory Interface (AD11).

Programmable Logic Array Output Element 11 (PLAO[11]).

General-Purpose Input and Output Port 4.4 (P4.4).

External Memory Interface (AD12).

Programmable Logic Array Output Element 12 (PLAO[12]).

General-Purpose Input and Output Port 4.5 (P4.5).

External Memory Interface (AD13).

Programmable Logic Array Output Element 13 (PLAO[13]).

JTAG Return Test Clock (RTCK).

2.5 V Internal Voltage Reference. Must be connected to a 0.47 µF capacitor when using

the internal reference.

Ground Voltage Reference for the ADC. For optimal performance, the analog power

supply should be separated from IOGND and DGND.

Single-Ended or Differential Analog Input 2 (ADC2).

Comparator Positive Input (CMP0).

Single-Ended or Differential Analog Input 3 (ADC3).

Comparator Negative Input (CMP1).

Rev. C | Page 22 of 108

Page 23

Data Sheet ADuC7124/ADuC7126

TYPICAL PERFORMANCE CHARACTERISTICS

0.4

0.3

0.3

0.2

0.1

DNL (LSB)

0

–0.1

–0.2

0

500

1000

1500

2000

ADC CODES

3000

2500

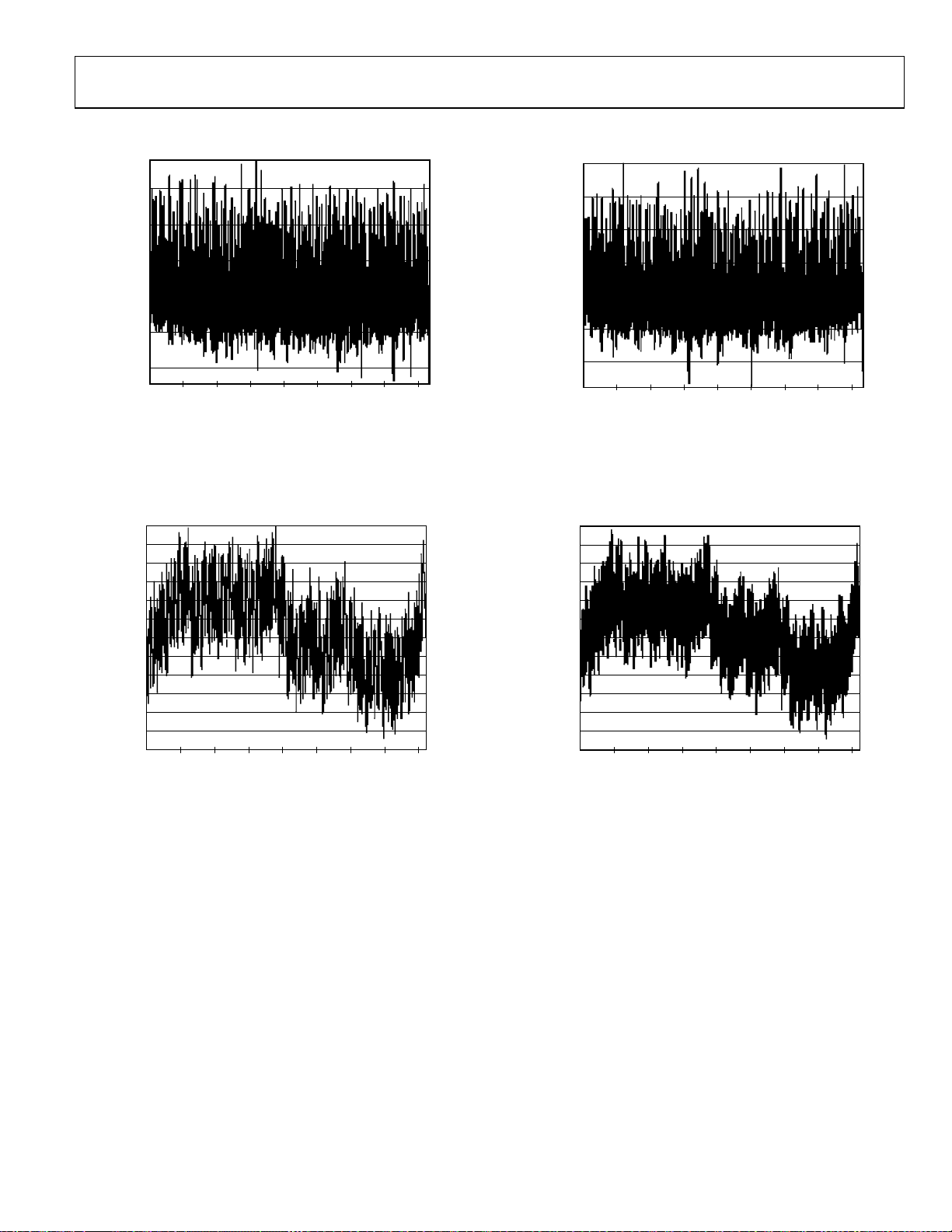

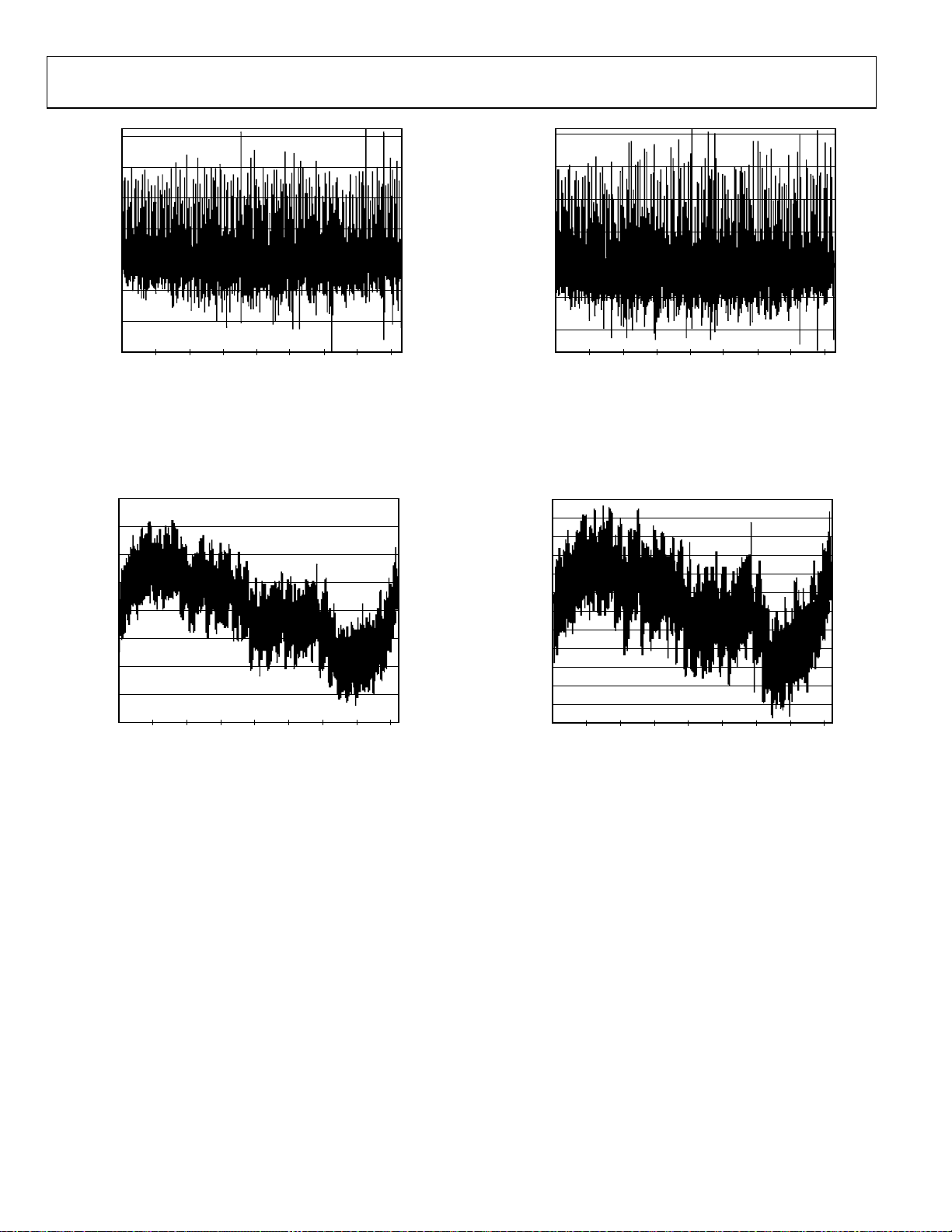

Figure 9. Typical DNL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = ADC0, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst Case Positive = 0.38 LSB, Code 1567

Worst Case Negative= −0.24 LSB, Code 4094

0.6

0.5

0.4

0.3

0.2

0.1

0

INL (LSB)

–0.1

–0.2

–0.3

–0.4

–0.5

–0.6

0

500

1000

1500

2000

ADC CODES

2500

3000

Figure 10. Typical INL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = ADC0, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst Case Positive = 0.60 LSB, Code 1890

Worst Case Negative= −0.54 LSB, Code 3485

3500

3500

4000

4000

4095

09123-209

4095

0.2

0.1

DNL (LS B)

0

–0.1

–0.2

09123-208

0

500

1000

1500

2000

ADC CODES

3000

2500

3500

09123-210

4000

4095

Figure 11. Typical DNL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = DAC1/ADC13, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst Case Positive = 0.40 LSB, Code 607

Worst Case Negative= −0.27 LSB, Code 2486

0.6

0.5

0.4

0.3

0.2

0.1

0

INL (LSB)

–0.1

–0.2

–0.3

–0.4

–0.5

–0.6

0

500

1000

1500

2000

ADC CODES

2500

3000

3500

4000

09123-211

4095

Figure 12. Typical INL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = DAC1/ADC13, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst Case Positive = 0.58 LSB, Code 480

Worst Case Negative= −0.54 LSB, Code 3614

Rev. C | Page 23 of 108

Page 24

ADuC7124/ADuC7126 Data Sheet

0.4

0.4

0.3

0.2

0.1

0

DNL (LSB)

–0.1

–0.2

–0.3

0

500

1000

1500

ADC CODES

2000

3000

2500

Figure 13. Typical DNL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = ADC8, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst-Case Positive = 0.42 LSB, Code 3583

Worst-Case Negative = −0.32 LSB, Code 3073

0.8

0.6

0.4

0.2

0

INL (LSB)

–0.2

–0.4

–0.6

–0.8

0

500

1000

1500

2000

ADC CODES

2500

3000

Figure 14. Typical INL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = ADC8, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst-Case Positive = 0.64 LSB, Code 802

Worst-Case Negative = −0.69 LSB, Code 3485

3500

3500

4000

4000

4095

09123-213

4095

0.3

0.2

0.1

DNL (LSB)

0

–0.1

–0.2

09123-212

0

500

1000

1500

ADC CODES

2000

3000

2500

3500

09123-214

4000

4095

Figure 15. Typical DNL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = DAC3/ADC15, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst-Case Positive = 0.41 LSB, Code 2016

Worst-Case Negative = −0.26 LSB, Code 3841

0.6

0.5

0.4

0.3

0.2

0.1

0

INL (LSB)

–0.1

–0.2

–0.3

–0.4

–0.5

–0.6

–0.6

0

500

1000

1500

2000

ADC CODES

2500

3000

3500

4000

09123-215

4095

Figure 16. Typical INL Error,

Temperature 25°C, V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = DAC3/ADC15, ADCCN = ADC0, Sampling Rate = 345 kHz

Worst-Case Positive = 0.55 LSB, Code 738

Worst-Case Negative = −0.68 LSB, Code 3230

Rev. C | Page 24 of 108

Page 25

Data Sheet ADuC7124/ADuC7126

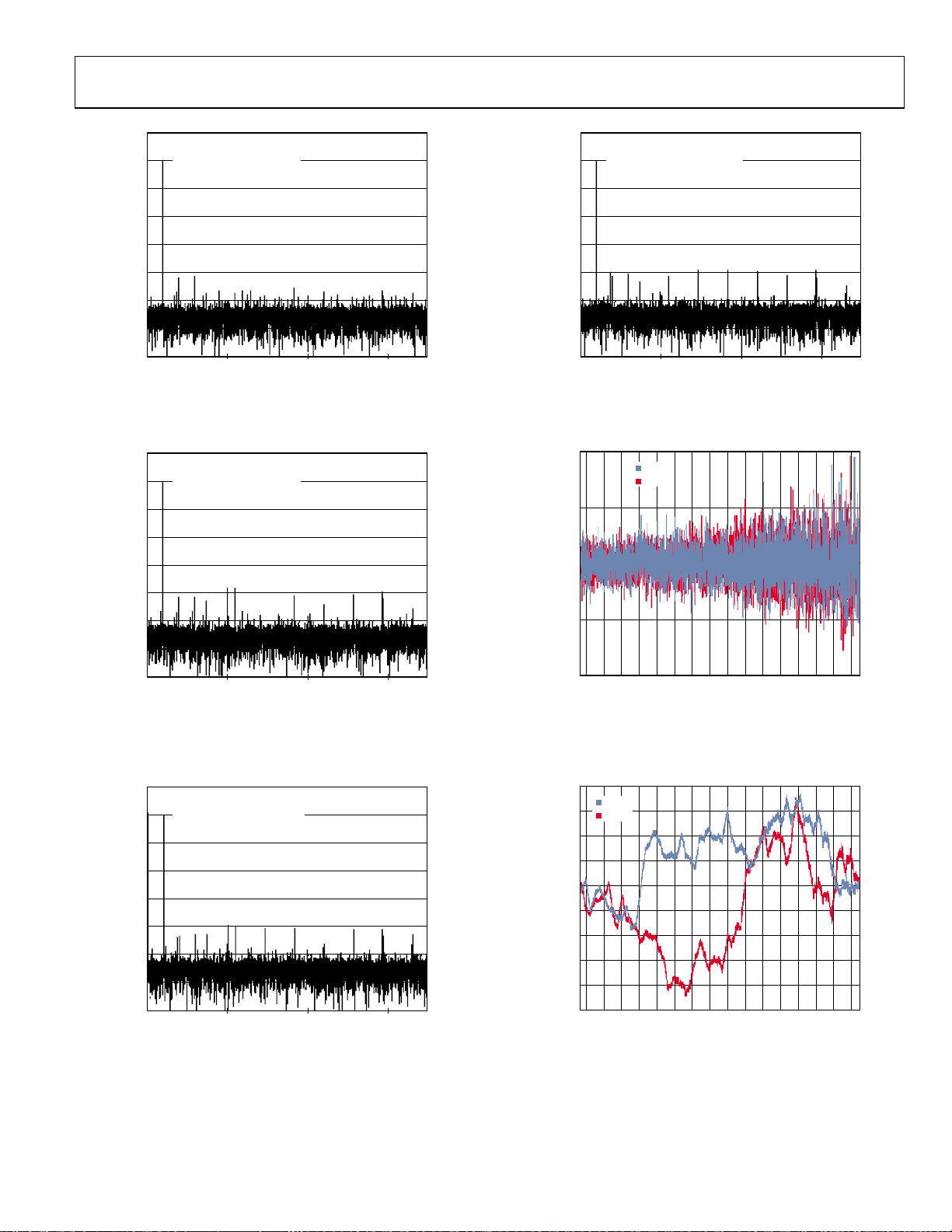

–20

20

SNR: 69.85dB

THD: –79.91dB

0

PHSN: –82.93dB, 29.771kHz

20

SNR: 65.97dB

THD: –78.63dB

0

PHSN: –77.83dB, 146.6038kHz

–20

–40

–60

–80

–100

SINAD, THD, AND PHSN OF ADC (dB)

–120

–140

0 50 100 150 174.1

FREQUENCY (kHz)

Figure 17. SINAD, THD, and PHSN of ADC,

= Internal 2.5 V, Single-Ended Mode

V

REF

ADCCP = ADC0

20

SNR: 67.10dB

THD: –79.79dB

0

PHSN: –76.14dB, 54.9738kHz

–20

–40

–60

–80

–100

SINAD, THD, AND PHSN OF ADC (dB)

–120

–140

0 50 100 150 174.1

FREQUENCY (kHz)

Figure 18. SINAD, THD, and PHSN of ADC,

= Internal 2.5 V, Single-Ended Mode

V

REF

ADCCP = DAC1/ADC13, ADCCN = ADC0

20

SNR: 67.44dB

THD: –82.33dB

0

PHSN: –79.31dB, 54.9738kHz

–20

–40

–60

–80

–100

SINAD, THD, AND PHSN OF ADC (dB)

–120

–140

0 50 100 150 174.1

FREQUENCY (kHz)

Figure 19. SINAD, THD, and PHSN of ADC,

= Internal 2.5 V, Single-Ended Mode

V

REF

ADCCP = ADC8, ADCCN = ADC0

09123-216

09123-217

09123-218

–40

–60

–80

–100

SINAD, THD, AND PHSN OF ADC (dB)

–120

–140

0 50 100 150 174.1

FREQUENCY (kHz)

09123-219

Figure 20. SINAD, THD, and PHSN of ADC,

V

= Internal 2.5 V, Single-Ended Mode

REF

ADCCP = ADC15/DAC3, ADCCN = ADC0

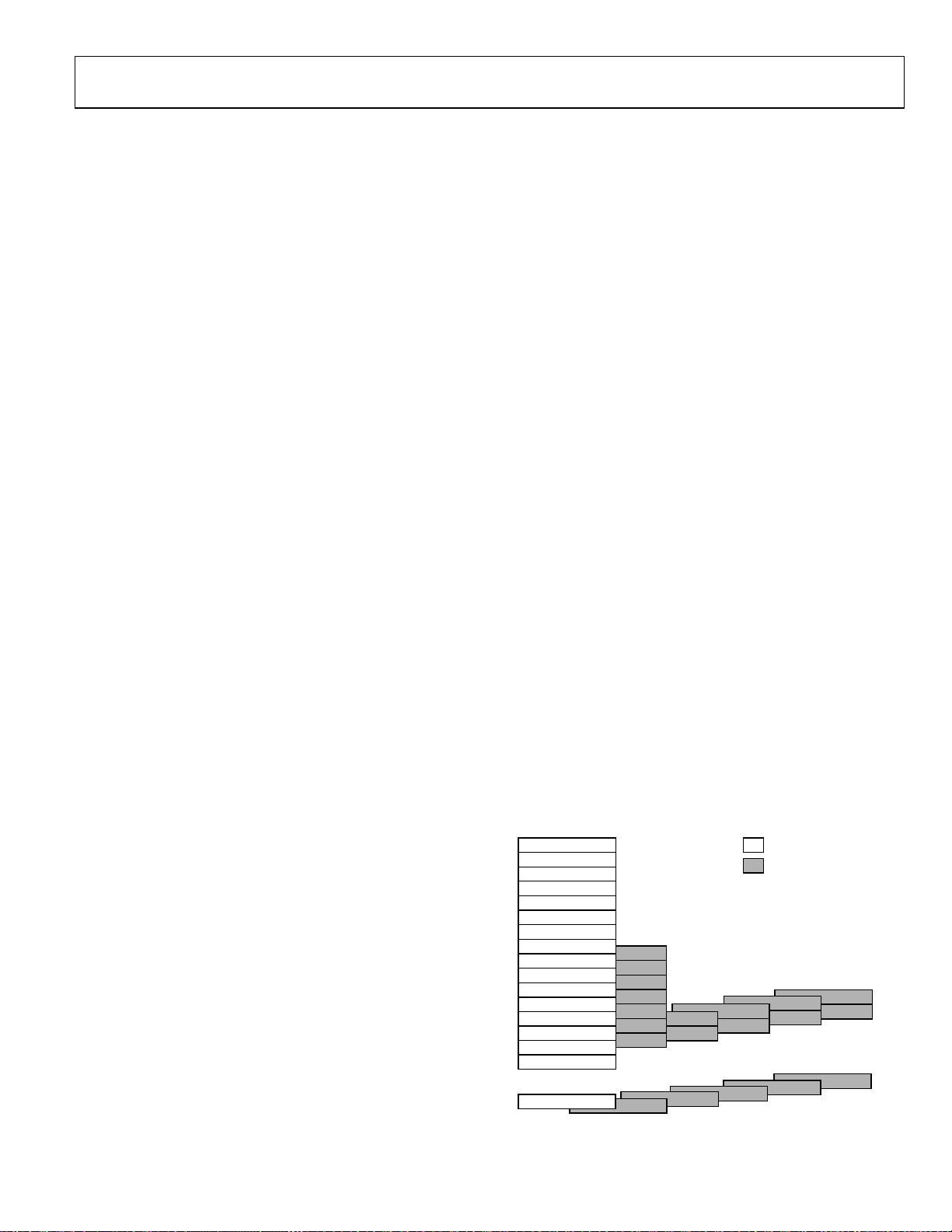

0.2

0.1

0

DNL (LS B)

–0.1

–0.2

250

500

750

DAC0

DAC1

1000

1250

1500

1750

ADC CODES

2000

2250

2500

2750

3000

3250

3500

3750

4000

09123-220

4095

Figure 21. DAC DNL Error,

DAC0 Max Positive DNL: 0.188951, DAC1 Max Positive DNL: 0.190343

DAC0 Max Negative DNL: −0.120081, DAC1 Max Negative DNL: −0.15697

2.0

DAC0

1.5

DAC1

1.0

0.5

0

–0.5

INL (LSB)

–1.0

–1.5

–2.0

3750

4000

09123-221

4095

–2.5

250

500

750

1000

1250

1500

1750

ADC CODES

2000

2250

2500

2750

3000

3250

3500

Figure 22. DAC INL Error,

DAC0 Max Positive INL: 1.84106, DAC1 Max Positive INL: 1.75312

DAC0 Max Negative INL: −0.887319, DAC1 Max Negative INL: −2.23708

Rev. C | Page 25 of 108

Page 26

ADuC7124/ADuC7126 Data Sheet

TERMINOLOGY

ADC SPECIFICATIONS

Integral Nonlinearity (INL)

The maximum deviation of any code from a straight line

passing through the endpoints of the ADC transfer function.

The endpoints of the transfer function are zero scale, a point

½ LSB below the first code transition, and full scale, a point

½ LSB above the last code transition.

Differential Nonlinearity (DNL)

The difference between the measured and the ideal 1 LSB

change between any two adjacent codes in the ADC.

Offset Error

The deviation of the first code transition (0000…000) to

(0000…001) from the ideal, that is, ½ LSB.

Gain Error

The deviation of the last code transition from the ideal AIN

voltage (full scale − 1.5 LSB) after the offset error has been

adjusted out.

Signal to (Noise + Distortion) Ratio

The measured ratio of signal to (noise + distortion) at the

output of the ADC. The signal is the rms amplitude of the

fundamental. Noise is the rms sum of all nonfundamental

signals up to half the sampling frequency (f

/2), excluding dc.

S

The ratio is dependent upon the number of quantization levels

in the digitization process; the more levels there are, the smaller

the quantization noise becomes.

The theoretical signal to (noise + distortion) ratio for an ideal

N-bit converter with a sine wave input is given by

Signal to (Noise + Distortion) = (6.02 N + 1.76) dB

Thus, for a 12-bit converter, this is 74 dB.

Total Harmonic Distortion

The ratio of the rms sum of the harmonics to the fundamental.

DAC SPECIFICATIONS

Relative Accuracy

Otherwise known as endpoint linearity, relative accuracy is a

measure of the maximum deviation from a straight line passing

through the endpoints of the DAC transfer function. It is

measured after adjusting for zero error and full-scale error.

Voltage Output Settling Time

The amount of time it takes the output to settle to within a

1 LSB level for a full-scale input change.

Rev. C | Page 26 of 108

Page 27

Data Sheet ADuC7124/ADuC7126

OVERVIEW OF THE ARM7TDMI CORE

The ARM7® core is a 32-bit reduced instruction set computer

(RISC). It uses a single 32-bit bus for instruction and data. The

length of the data can be eight bits, 16 bits, or 32 bits. The

length of the instruction word is 32 bits.

The ARM7TDMI is an ARM7 core with four additional

features.

• T support for the Thumb® (16-bit) instruction set.

• D support for debug.

• M support for long multiplications.

• I includes the EmbeddedICE module to support embedded

system debugging.

THUMB MODE (T)

An ARM instruction is 32 bits long. The ARM7TDMI

processor supports a second instruction set that has been

compressed into 16 bits, called the Thumb instruction set.

Faster execution from 16-bit memory and greater code density