Page 1

SPI-/I2C-Compatible, Temperature Sensor,

4-Channel ADC and Quad Voltage Output

FEATURES

ADT7516: four 12-bit DACs

ADT7517: four 10-bit DACs

ADT7519: four 8-bit DACs

Buffered voltage output

Guaranteed monotonic by design over all codes

10-bit temperature-to-digital converter

10-bit 4-channel ADC

DC input bandwidth

Input range: 0 V to 2.28 V

Temperature range: −40°C to +120°C

Temperature sensor accuracy: ±0.5°C typ

Supply range: 2.7 V to 5.5 V

DAC output range: 0 V to 2 V

Power-down current: <10 μA

Internal 2.28 V

option

REF

Double-buffered input logic

Buffered reference input

Power-on reset to 0 V DAC output

Simultaneous update of outputs (LDAC function)

On-chip, rail-to-rail output buffer amplifier

®

SPI

, I2C®, QSPI™, MICROWIRE™, and DSP compatible

4-wire serial interface

SMBus packet error checking (PEC) compatible

16-lead QSOP package

APPLICATIONS

Portable battery-powered instruments

Personal computers

Smart battery chargers

Telecommunications systems

Electronic text equipment

Domestic appliances

Process control

1

Protected by U.S. Patent Numbers: 6,169,442; 5,867,012; and 5,764,174.

REF

ADT7516/ADT7517/ADT7519

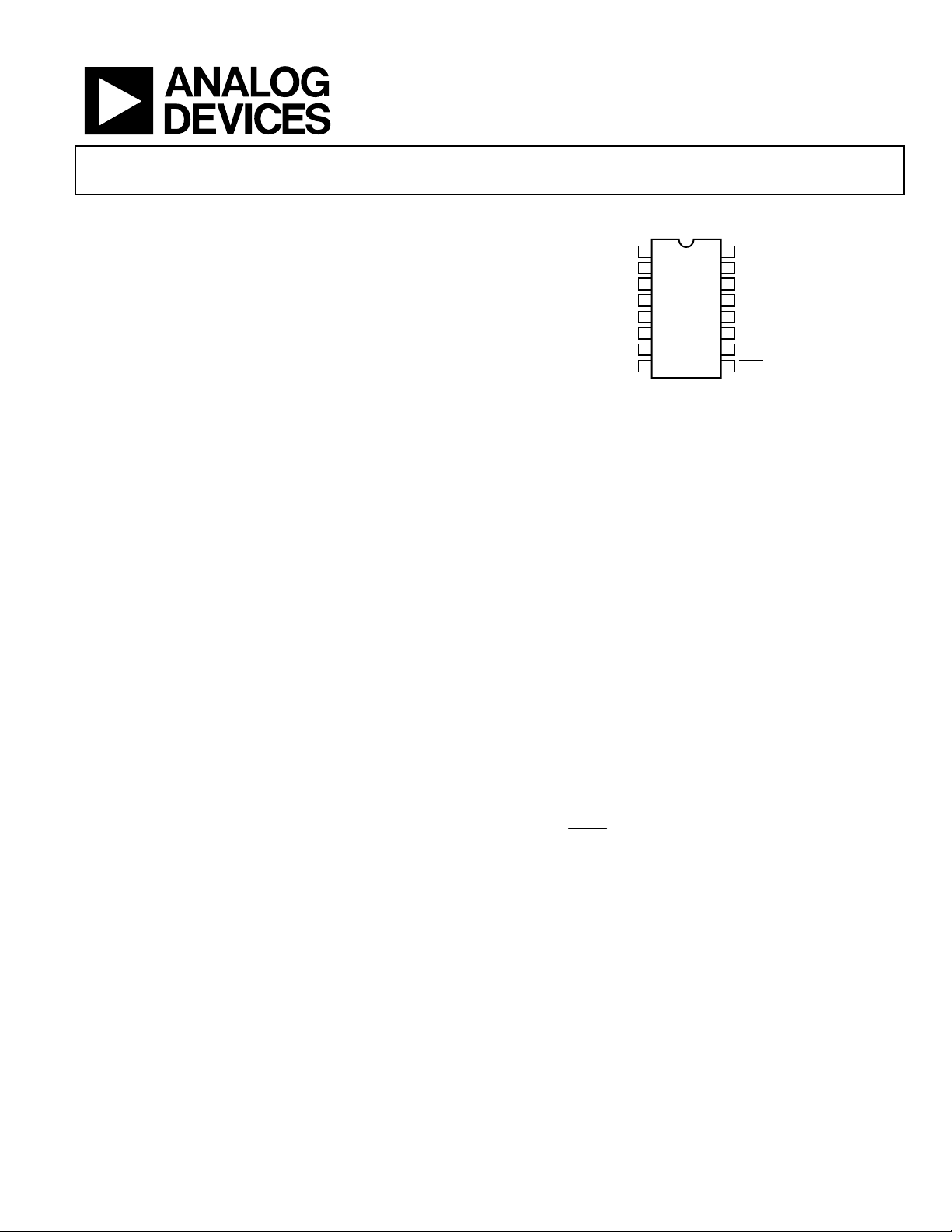

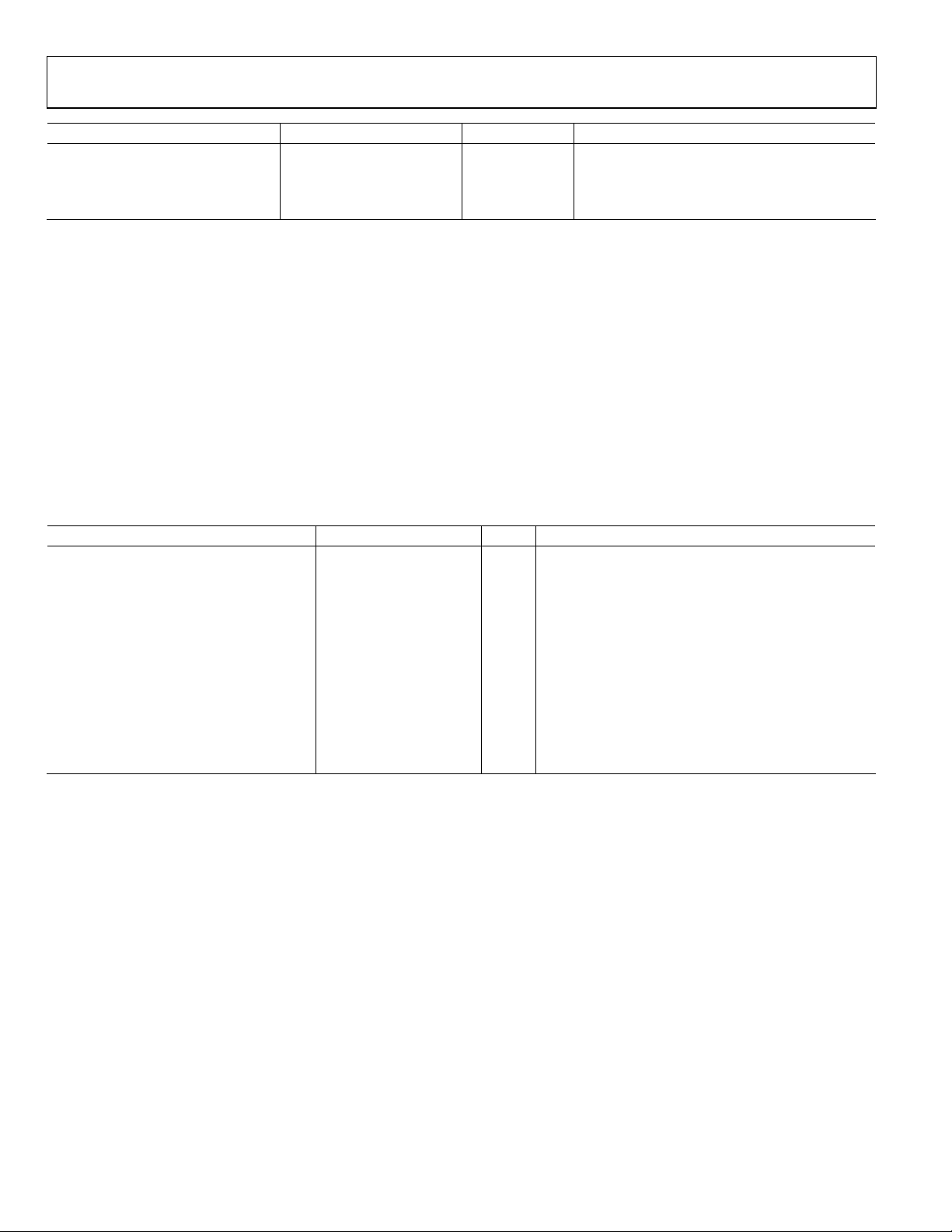

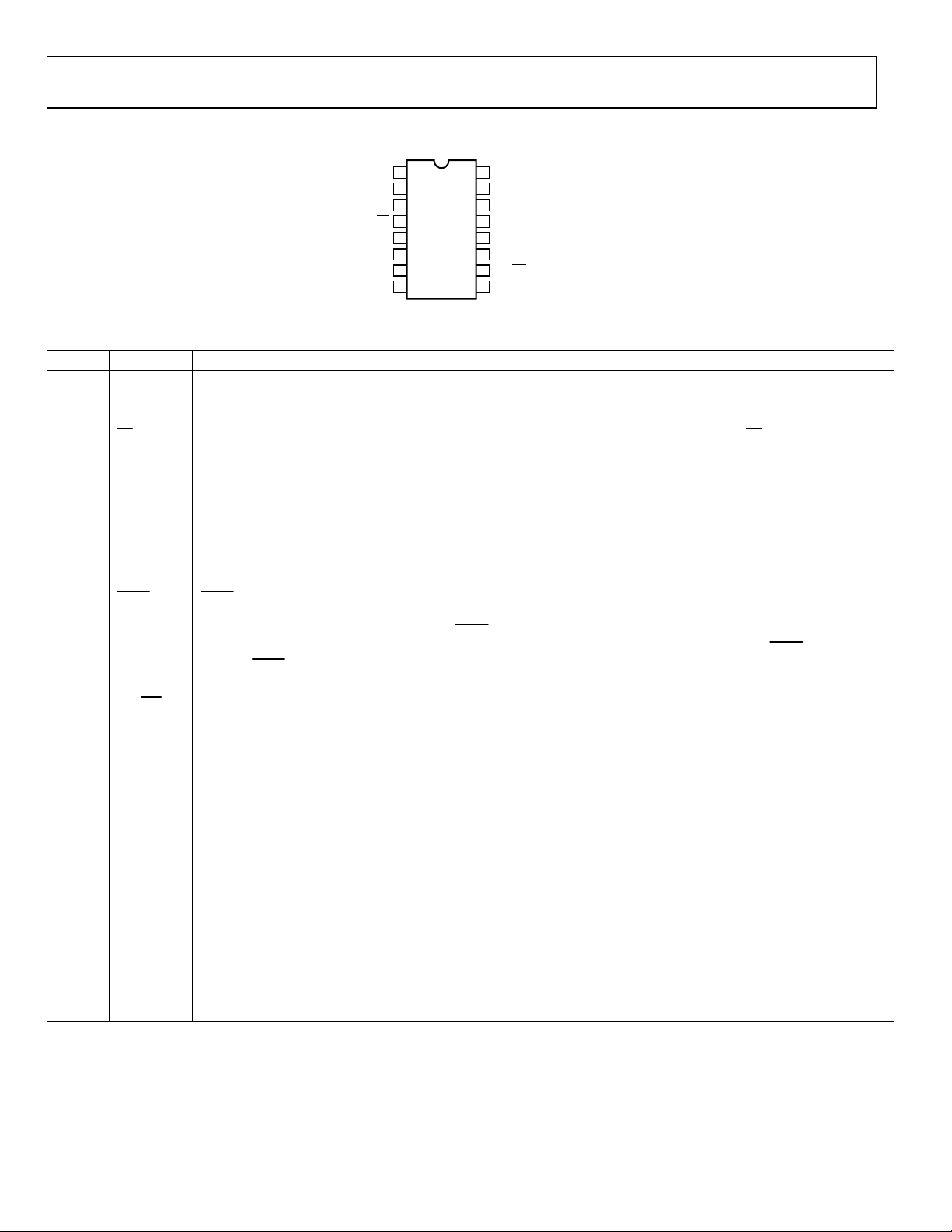

PIN CONFIGURATION

1

V

-B

OUT

V

-A

2

OUT

V

REF

D+/AIN1

D–/AIN2

-IN

CS

GND

V

DD

ADT7516/

3

ADT7517/

ADT7519

4

TOP VIEW

5

(Not to Scale)

6

7

8

GENERAL DESCRIPTION

The ADT7516/ADT7517/ADT75191 combine a 10-bit temperature-to-digital converter, a 10-bit 4-channel ADC, and a quad

12-/10-/8-bit DAC, respectively, in a 16-lead QSOP package.

The parts also include a band gap temperature sensor and a

10-bit ADC to monitor and digitize the temperature reading to

a resolution of 0.25°C.

The ADT7516/ADT7517/ADT7519 operate from a single 2.7 V

5.5 V supply. The input voltage range on the ADC channels is

to

0 V to 2.28 V, and the input bandwidth is dc. The reference for

the ADC channels is derived internally. The output voltage of

the DAC ranges from 0 V to V

time of 7 s typical.

The ADT7516/ADT7517/ADT7519 provide two serial interface

op

tions: a 4-wire serial interface that is compatible with SPI,

QSPI, MICROWIRE, and DSP interface standards, and a 2-wire

SMBus/I

controlled through the serial interface.

The reference for the four DACs is derived either internally or

fr

simultaneously using the software LDAC function or the

external

incorporate a power-on reset circuit, ensuring that the DAC

output powers up to 0 V and remains there until a valid write

takes place.

The wide supply voltage range, low supply current, and SPI-/

I

make them ideal for a variety of applications, including

personal computers, office equipment, and domestic appliances.

2

C interface. They feature a standby mode that is

om a reference pin. The outputs of all DACs can be updated

LDAC

pin. The ADT7516/ADT7517/ADT7519

2

C-compatible interface of the ADT7516/ADT7517/ADT7519

16

V

-C

OUT

V

-D

15

OUT

AIN4

14

SCL/SCLK

13

SDA/DIN

12

11

DOUT/ADD

INT/INT

10

LDAC/AIN3

9

Figure 1.

, with an output voltage settling

DD

02883-006

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

Page 2

ADT7516/ADT7517/ADT7519

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Pin Configuration............................................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

DAC AC Characteristics.............................................................. 6

Timing Diagrams.......................................................................... 7

Functional Block Diagram .............................................................. 8

Absolute Maximum Ratings............................................................ 9

ESD Caution.................................................................................. 9

Pin Configuration and Functional Descriptions........................ 10

Typical Performance Characteristics ........................................... 11

REVISION HISTORY

10/06—Rev. A to Rev. B

Updated Format..................................................................Universal

hanges to Features..........................................................................1

C

Changes to General Description.....................................................1

Changes to Specifications.................................................................3

Changes to Absolute Maximum Ratings........................................9

Changes to Table 10........................................................................28

Changes to ADT7516/ADT7517/ADT7519 Registers Section......28

Changes to Serial Interface Section...............................................37

Changes to Ordering Guide...........................................................44

Terminology.................................................................................... 17

Theory of Operation ...................................................................... 19

Power-Up Calibration................................................................ 19

Conversion Speed....................................................................... 19

Function Description—Voltage Output.................................. 20

Functional Description—Analog Inputs................................. 23

ADC Transfer Function............................................................. 23

Functional Description—Measurement.................................. 25

ADT7516/ADT7517/ADT7519 Registers............................... 28

Serial Interface............................................................................ 37

SMBus Alert Response .............................................................. 42

Outline Dimensions....................................................................... 43

Ordering Guide .......................................................................... 43

8/04—Rev. 0 to Rev. A

Updated Format...................................................................... Universal

leted ADT7518

De

Added ADT7519..................................................................... Universal

Change to Internal V

Change to Equation.............................................................................26

7/03—Initial Version: Rev. 0

Value .............................................................5

REF

Rev. B | Page 2 of 44

Page 3

ADT7516/ADT7517/ADT7519

SPECIFICATIONS

Temperature range is as follows: A version: −40°C to +120°C, VDD = 2.7 V to 5.5 V, GND = 0 V, REFIN = 2.25 V, unless otherwise noted.

Table 1.

Parameter

DAC DC PERFORMANCE

1

2, 3

Min Typ Max Unit Conditions/Comments

ADT7519

Resolution 8 Bits

Relative Accuracy ±0.15 ±1 LSB

Differential Nonlinearity ±0.02 ±0.25 LSB Guaranteed monotonic over all codes

ADT7517

Resolution 10 Bits

Relative Accuracy ±0.5 ±4 LSB

Differential Nonlinearity ±0.05 ±0.5 LSB Guaranteed monotonic over all codes

ADT7516

Resolution 12 Bits

Relative Accuracy ±2 ±16 LSB

Differential Nonlinearity ±0.02 ±0.9 LSB Guaranteed monotonic over all codes

Offset Error ±0.4 ±2 % of FSR

Gain Error ±0.3 ±2 % of FSR

Lower Deadband 20 65 mV

Upper Deadband 60 100 mV

Lower deadband exists only if offset error is

tive, see Figure 40

nega

Upper deadband exists if V

= VDD and off-set

REF

plus gain error is positive, see Figure 41

Offset Error Drift

Gain Error Drift

4

4

–12 ppm of FSR/°C

–5 ppm of FSR/°C

DC Power Supply Rejection Ratio4 –60 dB ∆VDD = ±10%

DC Crosstalk

4

200 μV See Figure 5

ADC DC ACCURACY Maximum VDD = 5 V

Resolution 10 Bits

Total Unadjusted Error (TUE) 2 3 % of FSR VDD = 2.7 V to 5.5 V

Total Unadjusted Error (TUE) 2 % of FSR VDD = 3.3 V ±10%

Offset Error ±0.5 % of FSR

Gain Error ±2 % of FSR

ADC BANDWIDTH DC Hz

ANALOG INPUTS

Input Voltage Range 0 2.28 V AIN1 to AIN4, C4 = 0 in Control Configuration 3

0 VDD V AIN1 to AIN4, C4 = 0 in Control Configuration 3

DC Leakage Current ±1 μA

Input Capacitance 5 20 pF

Input Resistance 10 MΩ

THERMAL CHARACTERISTICS

Internal Temperature Sensor Internal reference used, averaging on

Accuracy @ VDD = 3.3 V ±10% ±1.5 °C TA = 85°C

±0.5 ±3 °C TA = 0°C to +85°C

±2 ±5 °C TA = –40°C to +120°C

Accuracy @ VDD = 5 V ±5% ±2 ±3 °C TA = 0°C to +85°C

±3 ±5 °C TA = –40°C to +120°C

Resolution 10 Bits Equivalent to 0.25°C

Long-Term Drift 0.25 °C Drift over 10 years if part is operated at 55°C

Rev. B | Page 3 of 44

Page 4

ADT7516/ADT7517/ADT7519

Parameter

1

Min Typ Max Unit Conditions/Comments

External Temperature Sensor External transistor = 2N3906

Accuracy @ VDD = 3.3 V ±10% ±1.5 °C TA = 85°C

±3 °C T

±5 °C T

= 0°C to +85°C

A

= −40°C to +120°C

A

Accuracy @ VDD = 5 V ±5% ±2 ±3 °C TA = 0°C to +85°C

±3 ±5 °C TA = −40°C to +120°C

Resolution 10 Bits Equivalent to 0.25°C

Output Source Current 180 μA High level

11 μA Low level

Thermal Voltage Output

8-Bit DAC Output

Resolution 1 °C

Scale Factor 8.97 mV/°C 0 V to V

17.58 mV/°C 0 V to 2 V

output, TA = −40°C to +120°C

REF

output, TA = −40°C to +120°C

REF

10-Bit DAC Output

Resolution 0.25 °C

Scale Factor 2.2 mV/°C 0 V to V

4.39 mV/°C 0 V to 2 V

output, TA = −40°C to +120°C

REF

output, TA = −40°C to +120°C

REF

CONVERSION TIMES Single channel mode

Slow ADC

VDD/AIN 11.4 ms Averaging (16 samples) on

712 μs Averaging off

Internal Temperature 11.4 ms Averaging (16 samples) on

712 μs Averaging off

External Temperature 24.22 ms Averaging (16 samples) on

1.51 ms Averaging off

Fast ADC

VDD/AIN 712 μs Averaging (16 samples) on

44.5 μs Averaging off

Internal Temperature 2.14 ms Averaging (16 samples) on

134 μs Averaging off

External Temperature 14.25 ms Averaging (16 samples) on

890 μs Averaging off

ROUND ROBIN UPDATE RATE

5

Time to complete one measurement cycle

through all channels

Slow ADC @ 25°C

Averaging On 79.8 ms AIN1 and AIN2 are selected on Pin 7 and Pin 8

Averaging Off 4.99 ms AIN1 and AIN2 are selected on Pin 7 and Pin 8

Averaging On 94.76 ms D+ and D– are selected on Pin 7 and Pin 8

Averaging Off 9.26 ms D+ and D– are selected on Pin 7 and Pin 8

Fast ADC @ 25°C

Averaging On 6.41 ms AIN1 and AIN2 are selected on Pin 7 and Pin 8

Averaging Off 400.84 μs AIN1 and AIN2 are selected on Pin 7 and Pin 8

Averaging On 21.77 ms D+ and D– are selected on Pin 7 and Pin 8

Averaging Off 3.07 ms D+ and D– are selected on Pin 7 and Pin 8

DAC EXTERNAL REFERENCE INPUT

V

Input Range 1 VDD V Buffered reference

REF

V

Input Impedance >10 MΩ Buffered reference and power-down mode

REF

4

Reference Feedthrough –90 dB Frequency = 10 kHz

Channel-to-Channel Isolation –75 dB Frequency = 10 kHz

Rev. B | Page 4 of 44

Page 5

ADT7516/ADT7517/ADT7519

Parameter

1

Min Typ Max Unit Conditions/Comments

ON-CHIP REFERENCE

Reference Voltage

Temperature Coefficient

OUTPUT CHARACTERISTICS

Output Voltage

4

4

4

6

2.2662 2.28 2.2938 V

80 ppm/°C

0.001 VDD − 0.1 V

This is a measure of the minimum and maximum

ive capability of the output amplifier

dr

DC Output Impedance 0.5 Ω

Short Circuit Current 25 mA VDD = 5 V

16 mA VDD = 3 V

Power-Up Time 2.5 μs Coming out of power-down mode, VDD = 5 V

5 μs Coming out of power-down mode, VDD = 3.3 V

DIGITAL INPUTS

4

Input Current ±1 μA VIN = 0 V to VDD

VIL, Input Low Voltage 0.8 V

VIH, Input High Voltage 1.89 V

Pin Capacitance 3 10 pF All digital inputs

SCL, SDA Glitch Rejection 50 ns

Input filtering suppresses n

oise spikes of less

than 50 ns

LDAC Pulse Width

20 ns Edge triggered input

DIGITAL OUTPUT

Digital High Voltage, VOH 2.4 V I

SOURCE

= I

= 200 μA

SINK

Output Low Voltage, VOL 0.4 V IOL = 3 mA

Output High Current, IOH 1 mA V

Output Capacitance, C

INT/INT Output Saturation Voltage

I2C TIMING CHARACTERISTICS7,

50 pF

OUT

0.8 V I

8

= 5 V

OH

= 4 mA

OUT

Serial Clock Period, t1 2.5 μs Fast mode I2C, see Figure 2

Data In Setup Time to SCL High, t2 50 ns

Data Out Stable after SCL Low, t3 0 ns See Figure 2

SDA Low Setup Time to SCL

Low (Start Condition), t

4

SDA High Hold Time after SCL

High (Stop Condition), t

5

50 ns See Figure 2

50 ns See Figure 2

SDA and SCL Fall Time, t6 300 ns See Figure 2

SDA and SCL Rise Time, t7 300

SPI TIMING CHARACTERISTICS

CS to SCLK Setup Time, t1

4, 10

0 ns See Figure 3

9

ns See Figure 2

SCLK High Pulse Width, t2 50 ns See Figure 3

SCLK Low Pulse Width, t3 50 ns See Figure 3

Data Access Time after SCLK

Falling Edge, t

11

4

Data Setup Time Prior to SCLK

Rising Edge, t

5

Data Hold Time after SCLK

Rising Edge, t

6

CS to SCLK Hold Time, t7

CS to DOUT High Impedance, t8

35 ns

20 ns See Figure 3

0 ns See Figure 3

0 μs See Figure 3

40 ns See Figure 3

POWER REQUIREMENTS

VDD 2.7 5.5 V

VDD Settling Time 50 ms VDD settles to within 10% of its final voltage level

IDD (Normal Mode)

12

3 mA V

= 3.3 V, VIH = VDD, and VIL = GND

DD

2.2 3 mA VDD = 5 V, VIH = VDD, and VIL = GND

Rev. B | Page 5 of 44

Page 6

ADT7516/ADT7517/ADT7519

Parameter

1

Min Typ Max Unit Conditions/Comments

IDD (Power-Down Mode) 10 μA VDD = 3.3 V, VIH = VDD, and VIL = GND

10 μA VDD = 5 V, VIH = VDD, and VIL = GND

Power Dissipation 10 mW VDD = 3.3 V, normal mode

33 μW VDD = 3.3 V, shutdown mode

1

See the Terminology section.

2

DC specifications are tested with the outputs unloaded.

3

Linearity is tested using a reduced code range: ADT7516 (Code 115 to 4095); ADT7517 (Code 28 to 1023); ADT7519 (Code 8 to 255).

4

Guaranteed by design and characterization, not production tested.

5

Round robin is the continuous sequential measurement of the following channels: VDD, internal temperature, external temperature (AIN1, AIN2), AIN3, and AIN4.

6

For the amplifier output to reach its minimum voltage, the offset error must be negative. For the amplifier output to reach its maximum voltage (V

plus gain error must be positive.

7

The SDA and SCL timing is measured with the input filters turned on to meet the fast mode I2C specification. Switching off the input filters improves the transfer rate

but has a negative effect on the EMC behavior of the part.

8

Guaranteed by design, not production tested. All I2C timing specifications are for fast mode operation but the interface is still capable of handling the slower standard

rate specifications.

9

The interface is also capable of handling the I2C standard mode rise time specification of 1000 ns.

10

All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD), and timed from a voltage level of 1.6 V.

11

Measured with the load circuit shown in Figure 4.

12

The IDD specification is valid for all DAC codes and full-scale analog input voltages. Interface inactive. All DACs and ADCs active. Load currents excluded.

= VDD), the offset

REF

DAC AC CHARACTERISTICS

VDD = 2.7 V to 5.5 V, RL = 4.7 kΩ to GND, CL = 200 pF to GND, 4.7 kΩ to VDD, all specifications T

Table 2.

Parameter

1, 2

Min Typ

Output Voltage Settling Time V

3

Max Unit Conditions/Comments

= VDD = 5 V

REF

ADT7519 6 8 μs 1/4 scale to 3/4 scale change (0x40 to 0xC0)

ADT7517 7 9 μs 1/4 scale to 3/4 scale change (0x100 to 0x300)

ADT7516 8 10 μs 1/4 scale to 3/4 scale change (0x400 to 0xC00)

Slew Rate 0.7 V/μs

Major-Code Change Glitch Energy 12 nV-s 1 LSB change around major carry

Digital Feedthrough 0.5 nV-s

Digital Crosstalk 1 nV-s

Analog Crosstalk 0.5 nV-s

DAC-to-DAC Crosstalk 3 nV-s

Multiplying Bandwidth 200 kHz V

Total Harmonic Distortion –70 dB V

1

See the Terminology section.

2

Guaranteed by design and characterization, not production tested.

3

At 25°C.

= 2 V ±0.1 V p-p

REF

= 2.5 V ±0.1 V p-p; frequency = 10 kHz

REF

MIN

to T

, unless otherwise noted.

MAX

Rev. B | Page 6 of 44

Page 7

ADT7516/ADT7517/ADT7519

V

O

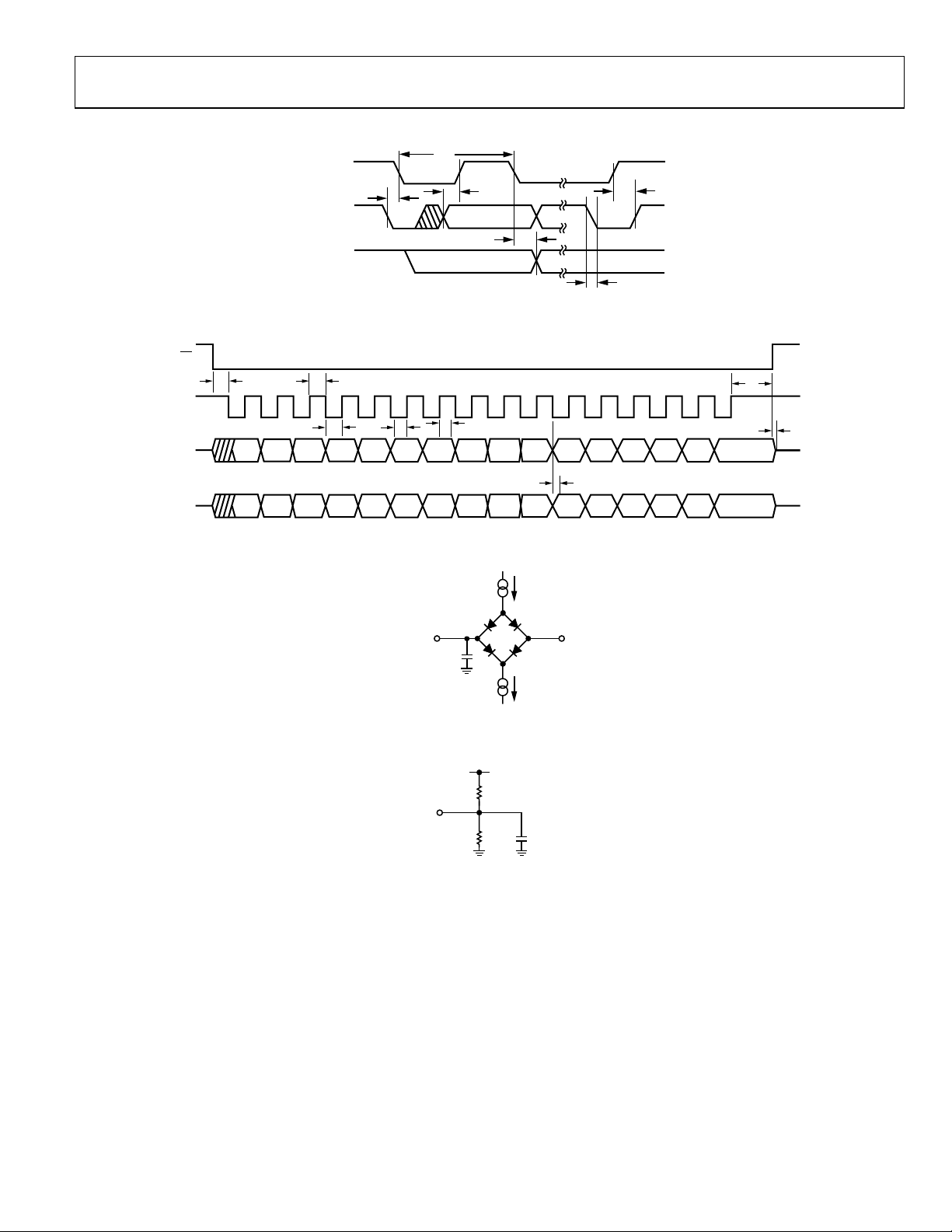

TIMING DIAGRAMS

t

1

SCL

t

Figure 2. I

2

t

3

2

C Bus Timing Diagram

SDA

DATA IN

SDA

DATA OUT

t

4

CS

SCLK

DIN

DOUT

t

1

D7

XXXXXXXXD7D6D5D4D3D2D1 D0

t

2

t

t

3

D6D5D4D3D2D1D0X X XXXXX X

t

6

5

t

4

Figure 3. SPI Bus Timing Diagram

t

5

t

6

02883-002

t

7

t

8

02883-003

TO OUTPUT

PIN

50pF

C

200µA I

L

200µA I

OL

1.6V

OH

2883-004

Figure 4. Load Circuit for Access Time and Bus Relinquish Time

DD

TO DAC

UTPUT

4.7kΩ

4.7kΩ

200pF

02883-005

Figure 5. Load Circuit for DAC Outputs

Rev. B | Page 7 of 44

Page 8

ADT7516/ADT7517/ADT7519

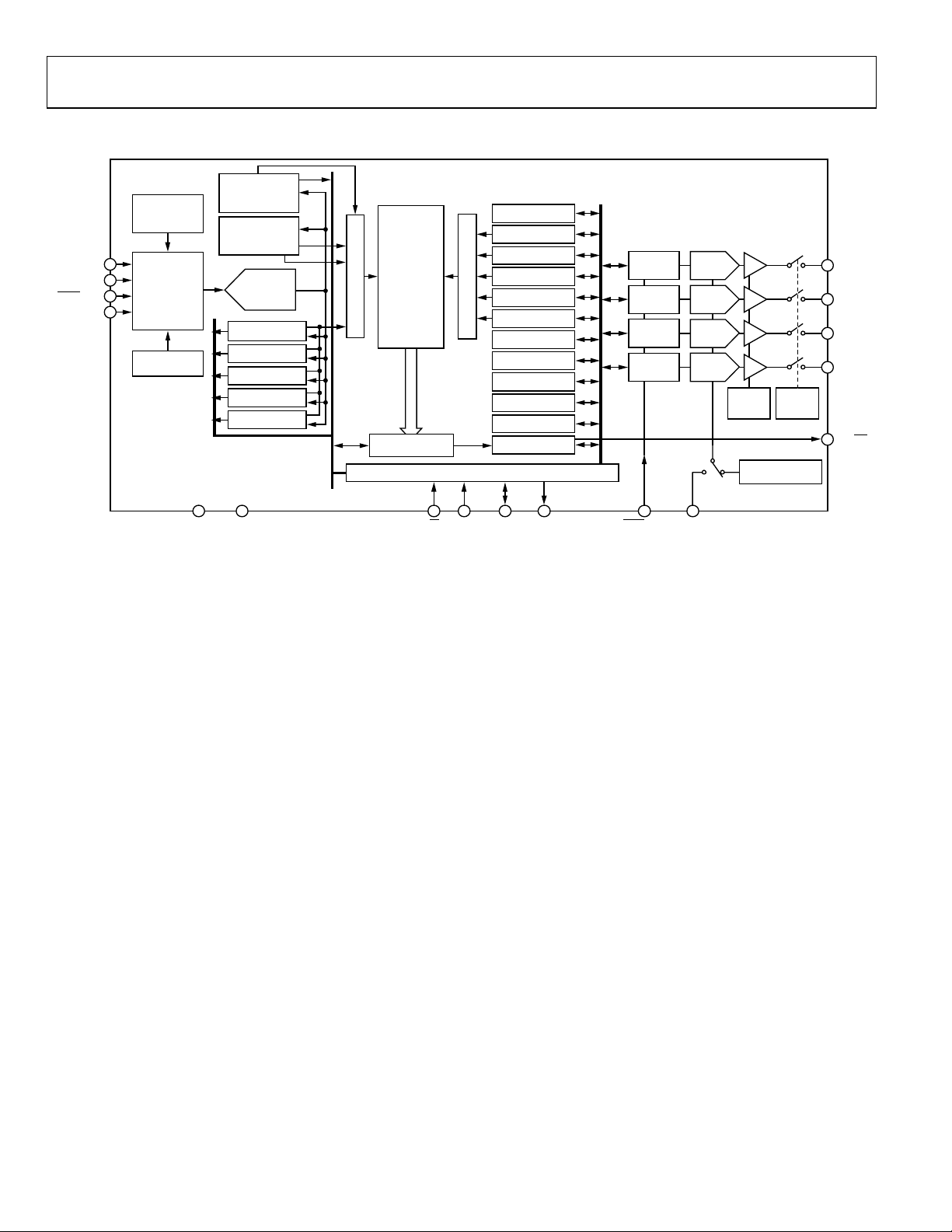

FUNCTIONAL BLOCK DIAGRAM

INTERNAL

D+/AIN1

D–/AIN2

LDAC/AIN3

AIN4

7

8

9

14

ON-CHIP

TEMPERATURE

SENSOR

ANALOG

MUX

V

DD

SENSOR

TEMPERATURE

VALUE REGISTER

EXTERNAL

TEMPERATURE

VALUE REGISTER

A-TO-D

CONVERTER

V

DD

VALUE REGISTER

AIN1

VALUE REGISTER

AIN2

VALUE REGISTER

AIN3

VALUE REGISTER

AIN4

VALUE REGISTER

DIGITAL MUX

LIMIT

COMPARATOR

STATUS

REGISTERS

ADDRESS POI NTER

REGIST ER

T

HIGH

REGISTERS

T

LOW

REGISTERS

VCCLIMIT

REGISTERS

AIN

DIGITAL MUX

SPI/SMBus INTERFACE

HIGH

REGISTERS

AIN

LOW

REGISTERS

CONTROL CO NFIG. 1

REGIST ER

CONTROL CO NFIG. 2

REGIST ER

CONTROL CO NFIG. 3

REGIST ER

DAC CONFIGU RATION

REGISTERS

LDAC CONFIG URATION

REGISTERS

INTERRUPT MASK

REGISTERS

LIMIT

LIMIT

LIMIT

LIMIT

ADT7516/ADT7517/ADT7519

DAC A

REGISTERS

DAC B

REGISTERS

DAC C

REGISTERS

DAC D

REGISTERS

STRING

DAC A

STRING

DAC B

STRING

DAC C

STRING

DAC D

GAIN

SELECT

LOGIC

INTERNAL

REFERENCE

POWER-

DOWN

LOGIC

2

1

16

15

10

V

OUT

V

OUT

V

OUT

V

OUT

INT/INT

-A

-B

-C

-D

12

5

6

GND

V

DD

Figure 6. Functional Block Diagram

13

4

SCL

CS

SDA

11

ADD

for the ADT7516/ADT7517/ADT7519

9

LDAC/AIN33V

REF

-IN

02883-001

Rev. B | Page 8 of 44

Page 9

ADT7516/ADT7517/ADT7519

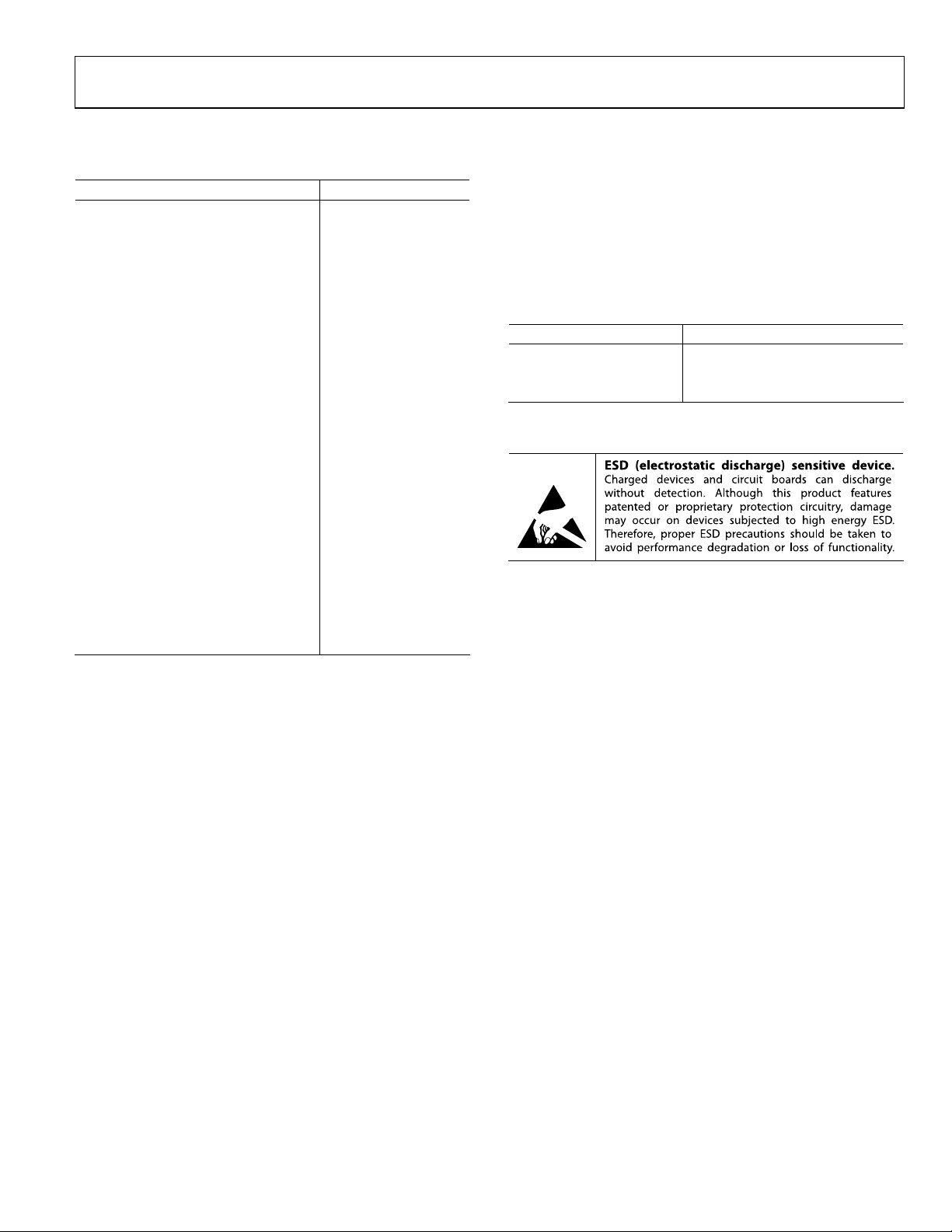

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

VDD to GND –0.3 V to +7 V

Analog Input Voltage to GND –0.3 V to VDD + 0.3 V

Digital Input Voltage to GND –0.3 V to VDD + 0.3 V

Digital Output Voltage to GND –0.3 V to VDD + 0.3 V

Reference Input Voltage to GND –0.3 V to VDD + 0.3 V

Operating Temperature Range –40°C to +120°C

Storage Temperature Range –65°C to +150°C

Junction Temperature 150°C

Power Dissipation1 (TJ max – TA)/θJA

Thermal Impedance2

θ

Junction-to-Ambient 105.44°C/W

JA

θ

Junction-to-Case 38.8°C/W

JC

IR Reflow Soldering

Peak Temperature 220°C (0°C/5°C)

Time at Peak Temperature 10 sec to 20 sec

Ramp-Up Rate 3°C/sec maximum

Ramp-Down Rate –6°C/sec maximum

Time 25°C to Peak Temperature 6 min maximum

IR Reflow Soldering (Pb-Free Package)

Peak Temperature 260°C (+0°C)

Time at Peak Temperature 20 sec to 40 sec

Ramp-Up Rate 3°C/sec maximum

Ramp-Down Rate –6°C/sec maximum

Time 25°C to Peak Temperature 8 min maximum

1

Values relate to the package being used on a 4-layer board.

2

Junction-to-case resistance is applicable to components featuring a

preferential flow direction, for example, components mounted on a heat

sink. Junction-to-ambient resistance is more useful for air cooled PCBmounted components.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

2

Table 4. I

C Address Selection

ADD Pin I2C Address

Low 1001 000

Float 1001 010

High 1001 011

ESD CAUTION

Rev. B | Page 9 of 44

Page 10

ADT7516/ADT7517/ADT7519

PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

V

OUT

V

OUT

V

-IN

REF

CS

GND

V

D+/AIN1

D–/AIN2

-B

-A

DD

1

2

ADT7516/

3

ADT7517/

ADT7519

4

TOP VIEW

5

(Not to Scale)

6

7

8

16

V

15

V

14

AIN4

13

SCL/SCLK

SDA/DIN

12

DOUT/ADD

11

INT/INT

10

LDAC/AIN3

9

OUT

OUT

-C

-D

02883-006

Figure 7. Pin Configuration (QSOP Package)

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

1 V

2 V

3 V

4

-B Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

OUT

-A Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

OUT

-IN Reference Input Pin for All Four DACs. This input is buffered and has an input range from 1 V to VDD.

REF

SPI Active Low Control Input. This is the frame synchronization signal for the input data. When CS goes low, it enables

CS

the input register, and data is transferred in on the rising edges and out on the falling edges of the subsequent serial

clocks. It is recommended that this pin be tied high to V

when operating the serial interface in I2C mode.

DD

5 GND Ground Reference Point. Ground reference point for all circuitry on the part. Analog and digital ground.

6 VDD Positive Supply Voltage, 2.7 V to 5.5 V. The supply should be decoupled to ground.

7 D+/AIN1 D+: Positive Connection to External Temperature Sensor.

AIN1: Analog Input. Single-ended analog input channel. Input range is 0 V to 2.28 V or 0 V to V

.

DD

8 D–/AIN2 D–: Negative Connection to External Temperature Sensor.

.

DD

9

AIN2: Analog Input. Single-ended analog input channel. Input range is 0 V to 2.28 V or 0 V to V

/AIN3 LDAC: Active Low Control Input. Transfers the contents of the input registers to their respective DAC registers. A

LDAC

falling edge on this pin forces any or all DAC registers to be updated if the input registers have new data. A minimum

pulse width of 20 ns must be applied to the LDAC pin to ensure proper loading of a DAC register. This allows

simultaneous update of all DAC outputs. Bit C3 of the Control Configuration 3 register enables the LDAC pin. Default is

10

Over Limit Interrupt. The output polarity of this pin can be set to give an active low or active high interrupt when

INT/INT

11 DOUT/ADD

with the LDAC

AIN3: Analog Input. Single-ended analog input channel. Input range is 0 V to 2.28 V or 0 V to V

temperature, V

DOUT: SPI Serial Data Output. Log

pin controlling the loading of the DAC registers.

.

DD

, or AIN limits are exceeded. The default is active low. Open-drain output, needs a pull-up resistor.

DD

ic output. Data is clocked out of any register at this pin. Data is clocked out on the

falling edge of SCLK. Open-drain output, needs a pull-up resistor.

2

ADD: I

C Serial Bus Address Selection Pin. Logic input. A low on this pin gives the Address 1001 000; leaving it floating

gives the Address 1001 010; and setting it high gives the address 1001 011. The I

2

C address set up by the ADD pin is

not latched by the device until after this address has been sent twice. On the eighth SCL cycle of the second valid

communication, the serial bus address is latched in. Any subsequent change on this pin has no effect on the I2C serial

bus address.

12 SDA/DIN

2

C Serial Data Input/Output. I2C serial data to be loaded into the registers of the part and read from these

SDA: I

registers is provided on this pin. Open-drain configuration, needs a pull-up resistor.

DIN: SPI Serial Data Input. S

erial data to be loaded into the part’s registers is provided on this pin. Data is clocked into

a register on the rising edge of SCLK. Open-drain configuration, needs a pull-up resistor.

13 SCL/SCLK

Serial Clock Input. This is the clock input for the serial port. The serial clock is used t

o clock data out of any register of

the ADT7516/ADT7517/ADT7519, and also to clock data into any register that can be written to. Open-drain

configuration, needs a pull-up resistor.

14 AIN4 Analog Input. Single-ended analog input channel. Input range is 0 V to 2.28 V or 0 V to VDD.

15 V

16 V

-D Buffered Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

OUT

-C Buffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

OUT

Rev. B | Page 10 of 44

Page 11

ADT7516/ADT7517/ADT7519

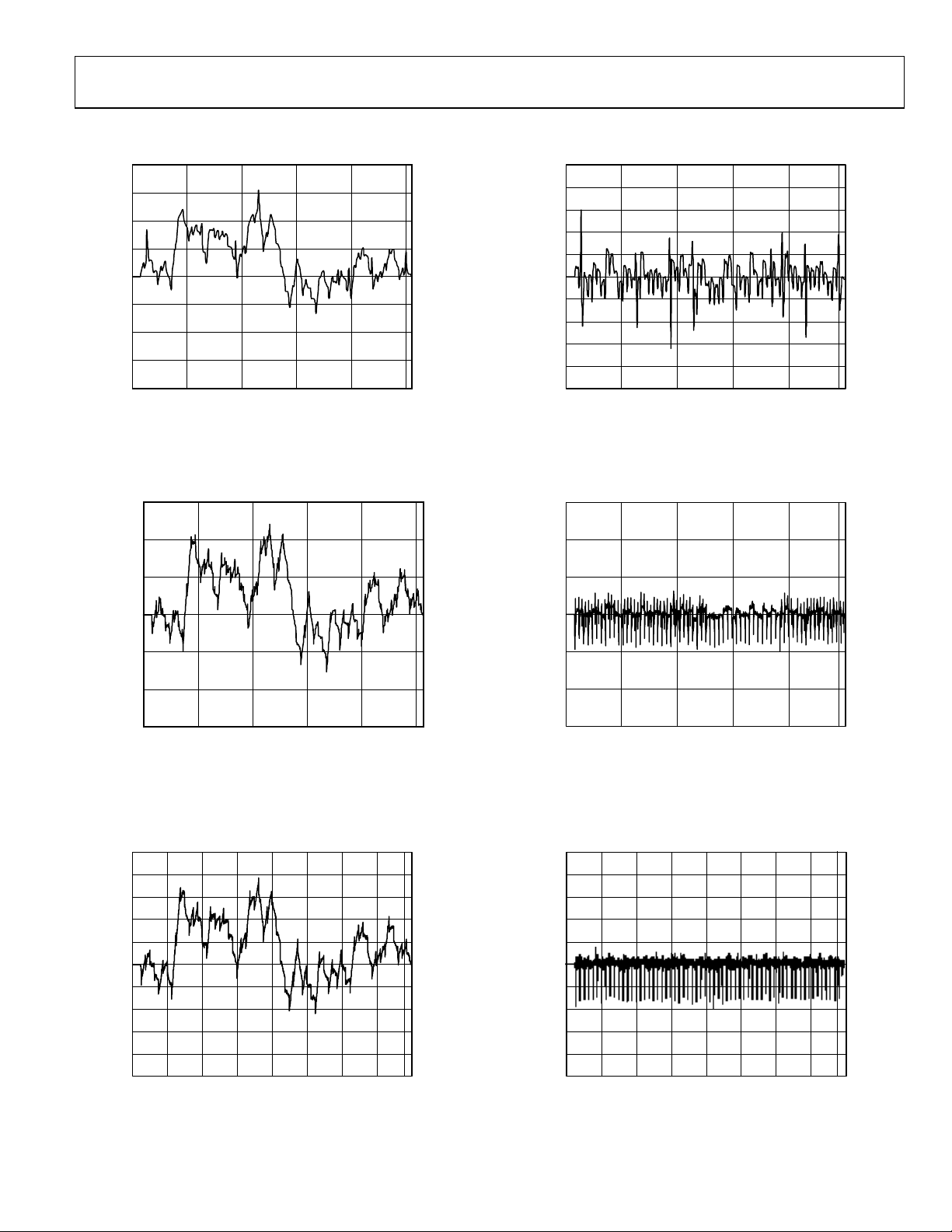

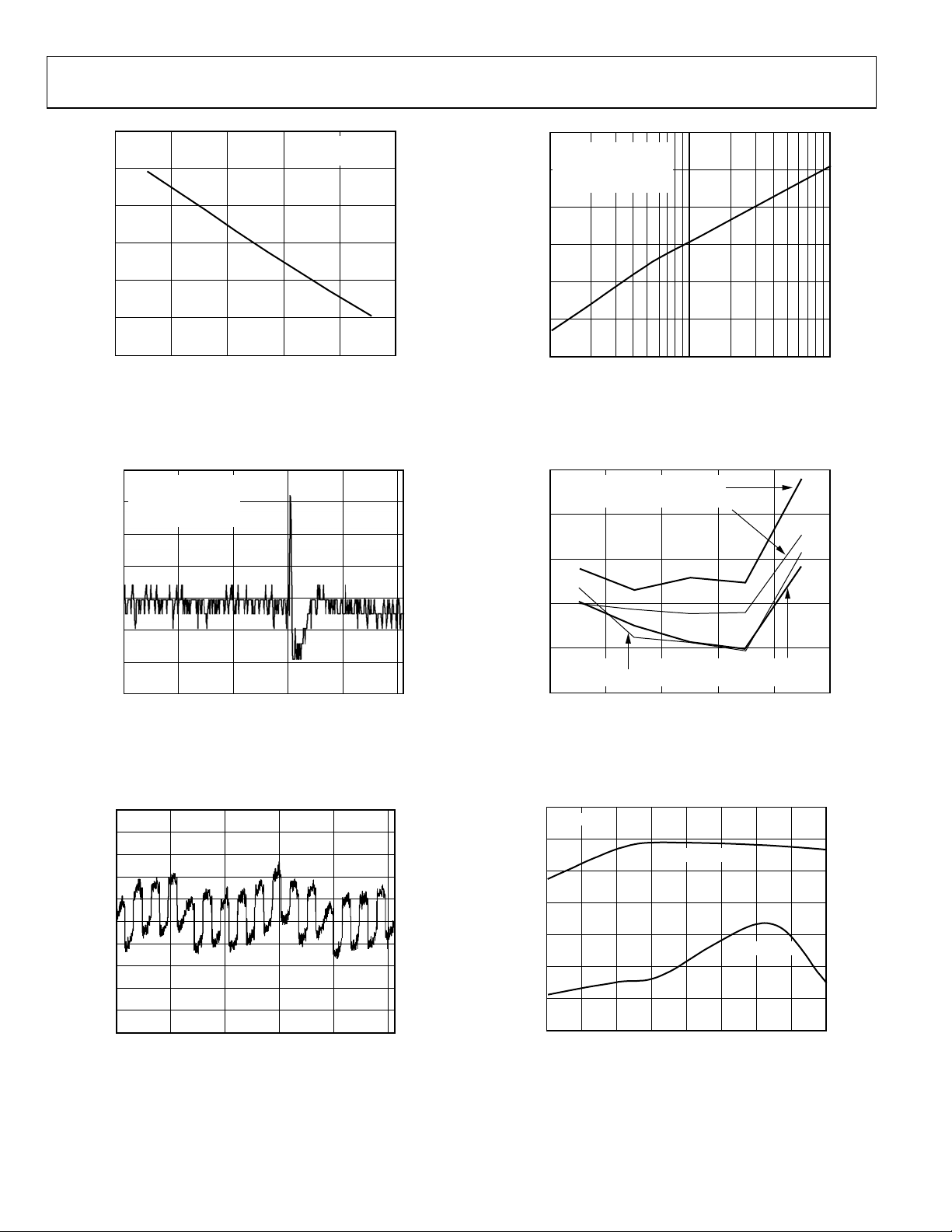

TYPICAL PERFORMANCE CHARACTERISTICS

0.20

0.15

0.10

0.05

0

–0.05

INL ERROR (LSB)

–0.10

–0.15

–0.20

0 50 100 150 200 250

DAC CODE

Figure 8. ADT7519 Typical DAC INL Plot

02883-009

0.10

0.08

0.06

0.04

0.02

0

–0.02

DNL ERROR (LSB)

–0.04

–0.06

–0.08

–0.10

0 50 100 150 200 250

DAC CODE

Figure 11. ADT7519 Typical

DAC DNL Plot

02883-012

0.6

0.4

0.2

0

INL ERROR (LSB)

–0.2

–0.4

–0.6

0 200 400 600

Figure 9. ADT7517 Typical DAC INL Plot

2.5

2.0

1.5

1.0

0.5

0

–0.5

INL ERROR (LSB)

–1.0

–1.5

–2.0

–2.5

Figure 10. ADT7516 Typical DAC INL Plot

DAC CODE

800 1000

20001500500 10000 2500 3000 3500 4000

DAC CODE

0.3

0.2

0.1

0

–0.1

DNL ERROR (LSB)

–0.2

02883-010

02883-011

–0.3

0 200 400 600 800 1000

DAC CODE

Figure 12. ADT7517 Typical

1.0

0.8

0.6

0.4

0.2

0

–0.2

DNL ERROR (LSB)

–0.4

–0.6

–0.8

–1.0

DAC CODE

Figure 13. ADT7516 Typical

DAC DNL Plot

20001500500 10000 2500 3000 3500 4000

DAC DNL Plot

02883-013

02883-014

Rev. B | Page 11 of 44

Page 12

ADT7516/ADT7517/ADT7519

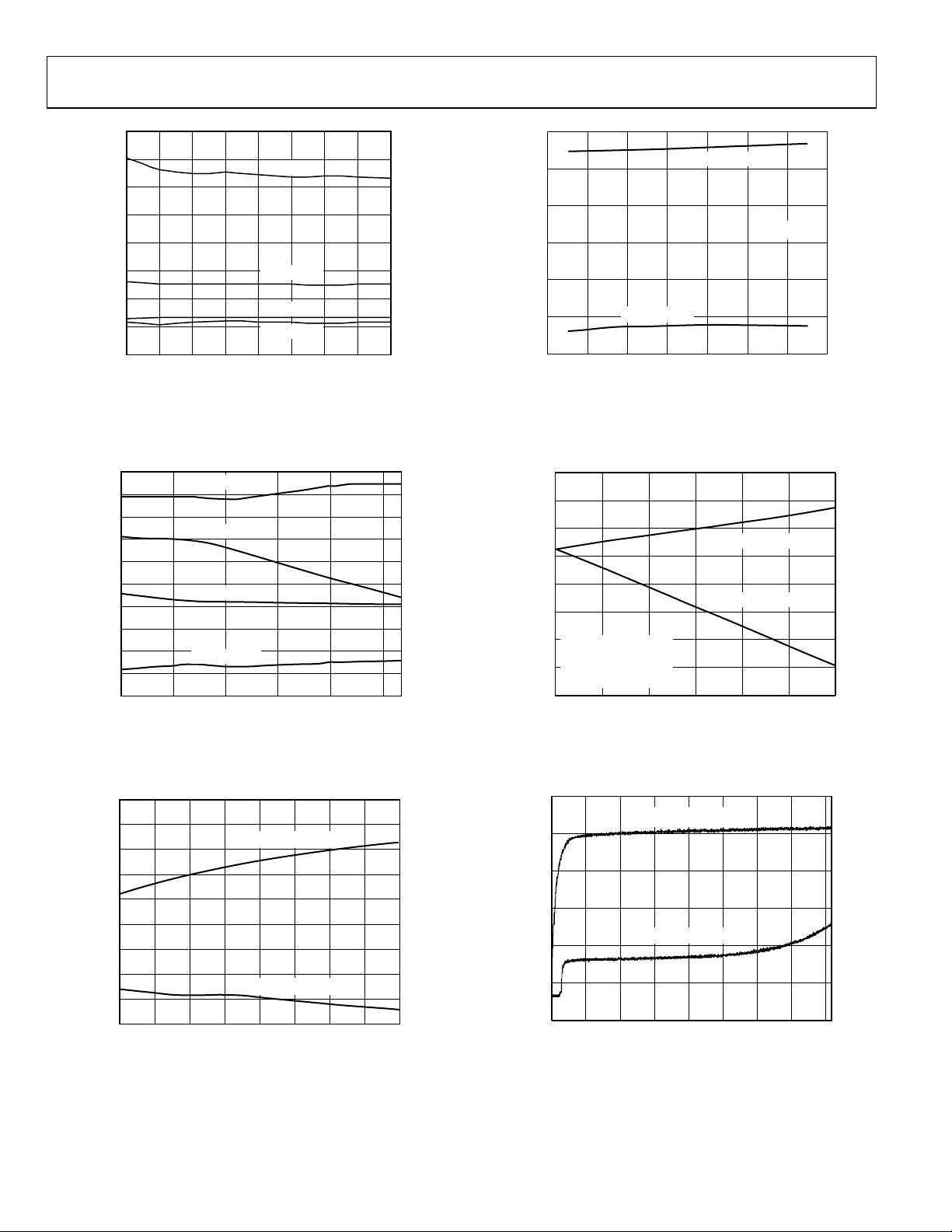

0.30

10

0.25

0.20

0.15

0.10

0.05

ERROR (LSB)

0

–0.05

–0.10

1.01.52.02.53.03.54.04.5 5.0

Figure 14. ADT7519 DAC INL and DNL Error vs. V

0.14

0.12

0.10

0.08

0.06

0.04

0.02

ERROR (LSB)

0

–0.02

–0.04

–0.06

–40 110805020–10

INL WCP

INL WCN

DNL WCP

DNL WCN

TEMPERATURE ( °C)

INL WCP

DNL WCP

DNL WCN

INL WCN

(V)

V

REF

REF

Figure 15. ADT7519 DAC INL Error and DNL Error vs. Temperature

5

0

–5

ERROR (LSB)

–10

–15

02883-015

–20

2.7 3.3 3.6 4. 0

GAIN ERROR

Figure 17. DAC Offset Error and Gain Error vs. V

2.505

2.500

2.495

2.490

2.485

2.480

DAC OUTPUT (V)

2.475

VDD = 5V

V

= 5V

REF

DAC OUTPUT

2.470

02883-016

LOADED TO MI DSCALE

2.465

0123

Figure 18. DAC V

Source and Sink Current Capability

OUT

OFFSET ERROR

(V)

V

DD

SOURCE CURRENT

CURRENT (mA)

V

= 2.25V

REF

4.5 5.0

SINK CURRENT

45

02883-018

5.5

DD

02883-019

6

0

–0.2

–0.4

–0.6

–0.8

–1.0

ERROR (LSB)

–1.2

–1.4

–1.6

–1.8

–40 120100806040200–20

OFFSET ERROR

GAIN ERROR

TEMPERATURE ( °C)

Figure 16. DAC Offset Error and Gain Error vs. Temperature

02883-017

Rev. B | Page 12 of 44

(mA)

CC

I

1.98

1.96

1.94

1.92

1.90

1.88

1.86

DAC OUTPUT UNLOADED

DAC OUTPUT LOADED

04350030002500200015001000500

DAC CODE

Figure 19. Supply Current vs. DAC Code

02883-020

000

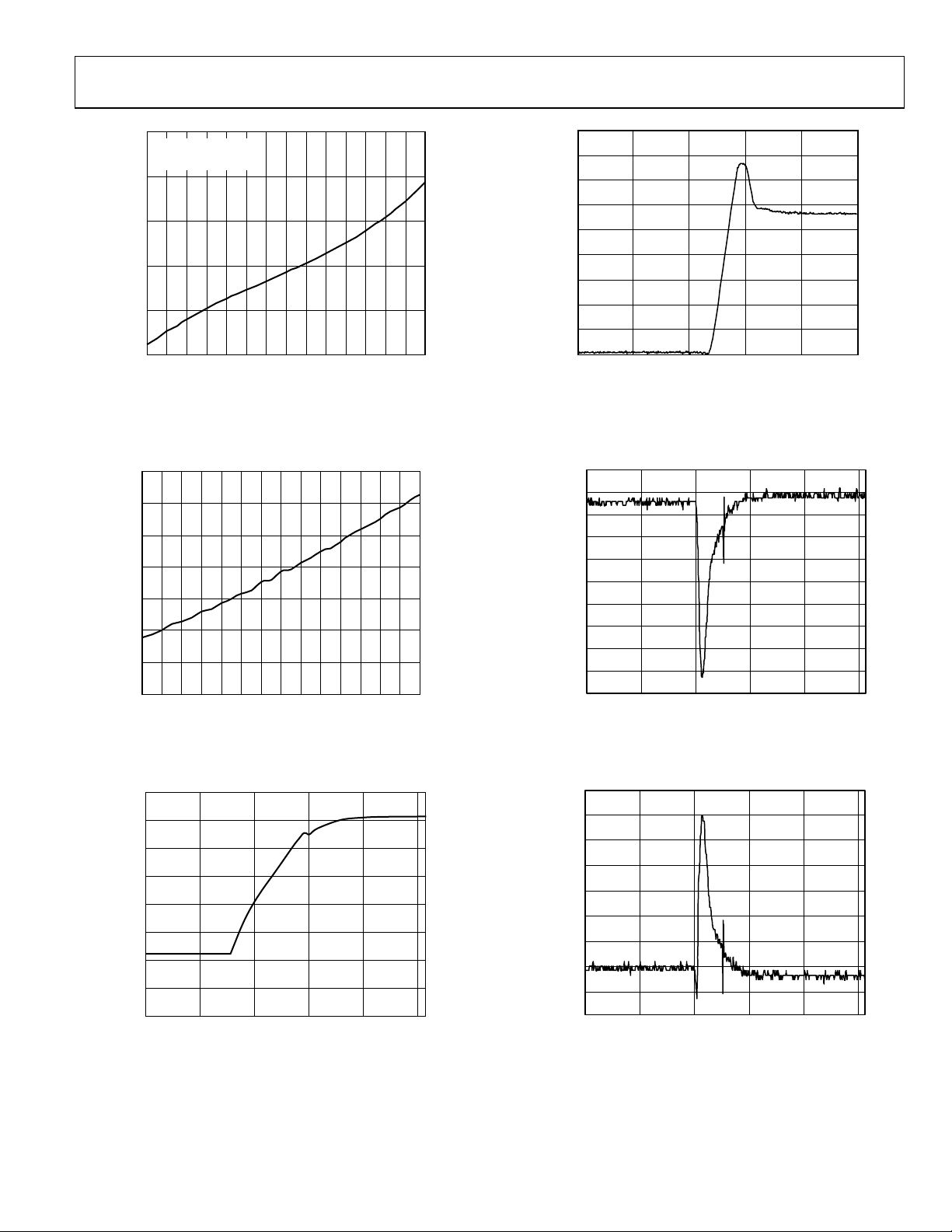

Page 13

ADT7516/ADT7517/ADT7519

2.00

ADC OFF

DAC OUTPUTS AT 0V

1.95

1.90

(mA)

CC

I

1.85

1.80

1.75

2.7 3.1 3.5 3.9 4.3 4.7 5.12.9 3.3 3.7 4.1 4.5 4.9 5.3 5.5

V

(V)

CC

Figure 20. Supply Current vs. Supply Voltage @ 25°C

7

6

5

4

(mA)

CC

I

3

2

1

0

2.7 2.9 3.1 3.3 3.5 3.7 3.9 4.1 4.3 4. 5 4.7 4. 9 5.1 5. 3 5.5

(V)

V

CC

Figure 21. Power-Down Current vs. Supply Voltage @ 25°C

02883-021

02883-022

1.8

1.6

1.4

1.2

1.0

0.8

DAC OUTPUT (V)

0.6

0.4

0.2

0

024

Figure 23. Exiting Powe

0.4700

0.4695

0.4690

0.4685

0.4680

0.4675

0.4670

DAC OUTPUT (V )

0.4665

0.4660

0.4655

0.4650

02 4681

68

TIME (µs)

r-Down to Midscale

TIME (µs)

Figure 24. ADT7516 DAC Major Code Transition Glitch Energy;

01

1…11 to 100...00

02883-024

10

02883-025

0

4.0

3.5

3.0

2.5

2.0

1.5

DAC OUTPUT (V)

1.0

0.5

0

02 4681

Figure 22. DAC Half-Scale Settling (

TIME (µs)

1/4 to 3/4 Scale Code Change)

02883-023

0

Rev. B | Page 13 of 44

0.4730

0.4725

0.4720

0.4715

0.4710

0.4705

DAC OUTPUT (V)

0.4700

0.4695

0.4690

0.4685

02 4681

TIME (µs)

Figure 25. ADT7516 DAC Major Code Transition Glitch Energy;

0…00 to 011…11

10

02883-026

0

Page 14

ADT7516/ADT7517/ADT7519

0

–2

–4

VDD= 5V

T

= 25°C

A

0

±100mV RIPPLE ON V

V

= 2.25V

REF

–10

= 3.3V

V

DD

TEMPERATURE = 25°C

–20

CC

–6

–8

FULL-SCAL E ERROR (mV)

–10

–12

2.329

2.328

2.327

2.326

2.325

DAC OUTPUT (V)

2.324

2.323

2.322

12 3

V

(V)

REF

Figure 26. DAC Full-Scale Error vs. V

VDD= 5V

= 5V

V

REF

DAC OUTPUT LO ADED

TO MIDSCALE

012 345

TIME (µs)

45

REF

–30

AC PSRR (dB)

–40

–50

02883-027

–60

110

FREQUENCY (kHz)

02883-030

100

Figure 29. PSRR vs. Supply Ripple Frequency

1.5

EXTERNAL T EMPERATURE @ 5V

1.0

0.5

0

TEMPERATURE ERRO R (°C)

–0.5

02883-028

–1.0

INTERNAL T EMPERATURE @ 3.3V

INTERNAL T EMPERATURE @ 5V

–30 0 40 85 120

EXTERNAL T EMPERATURE @ 3.3V

TEMPERATURE ( °C)

02883-031

Figure 27. DAC-to-

1.0

0.8

0.6

0.4

0.2

0

–0.2

INL ERROR (LSB)

–0.4

–0.6

–0.8

–1.0

0 200 400 600 800 1000

Figure 28. ADC INL with V

DAC Crosstalk

ADC CODE

= VDD (3.3 V)

REF

02883-029

Rev. B | Page 14 of 44

Figure 30. Internal Temperature Error @ 3.3 V and 5 V

3

V

= 3.3V

DD

2

1

0

–1

ERROR (LSB)

–2

–3

–4

–40 –20 0

OFFSET ERROR

GAIN ERROR

20 40 60 80 100 120

TEMPERATURE (°C)

Figure 31. ADC Offset Error and Gain Error vs. Temperature

02883-032

Page 15

ADT7516/ADT7517/ADT7519

A

3

2

1

0

ERROR (LSB)

–1

–2

–3

2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

OFFSET ERROR

GAIN ERROR

VDD (V)

02883-033

10

VDD = 3.3V

COMMON-MODE

8

VOLTAGE = 100mV

6

4

2

0

–2

TEMPERATURE ERROR (°C)

–4

–6

1 100 200 300 400 500 600

NOISE FREQ UENCY (Hz)

02883-036

Figure 32. ADC Offset Error and Gain Error vs. V

15

10

5

D+ TO GND

0

–5

D+ TO V

CC

–10

–15

TEMPERATURE E RROR (°C)

–20

–25

01020

30 40 50 60 70 80 90 100

PCB LEAKAGE RESI STANCE (MΩ)

VDD = 3.3V

TEMPERATURE = 25°C

DD

Figure 33. External Temperature Error vs. PCB Leakage Resistance

0

–10

VDD = 3.3V

Figure 35. External Temperature Error vs. Common-Mode Noise Frequency

70

60

50

40

30

TURE ERROR (°C)

20

10

TEMPER

0

02883-034

–10

1100200

NOISE FREQUENCY (MHz)

VDD = 3.3V

DIFFE RENTI AL-MO DE

VOLTAGE = 100mV

300 400 500 600

02883-037

Figure 36. External Temperature Error vs. Differential-

Mode No

ise Frequency

0.6

VDD = 3.3V

0.4

–20

–30

–40

TEMPERATURE ERROR (°C)

–50

–60

0 5 10 15 20 25

CAPACITANCE (nF)

30 35 40 45 50

02883-035

Figure 34. External Temperature Error vs. Capacitance Between D+ and D–

0.2

0

–0.2

TEMPERATURE ERRO R (°C)

–0.4

–0.6

1 100 200 300 400 500 600

±250mV

NOISE FRE QUENCY (Hz)

02883-038

Figure 37. Internal Temperature Error vs. Power Supply Noise Frequency

Rev. B | Page 15 of 44

Page 16

ADT7516/ADT7517/ADT7519

A

A

140

EXTERNAL T EMPERATURE

120

100

80

60

TEMPERATURE (°C)

40

20

0

0

10 20

INTERNAL TEMPERATURE

O

R

T

E

M

P

E

E

N

V

I

R

O

H

A

N

G

C

F

A

T

U

R

E

M

E

N

T

N

H

E

R

E

E

D

30 40 50

TIME (s)

02883-039

60

0

–5

–10

TION (dB)

–15

TTENU

–20

–25

10 100 1k 10k 100k 1M 10M

1

Figure 38. Temperature Sensor Response to Thermal Shock Figure 39. DAC Multiplying Bandwidth (Sma

FREQUENCY ( Hz)

ll Signal Frequency Response)

02883-040

Rev. B | Page 16 of 44

Page 17

ADT7516/ADT7517/ADT7519

TERMINOLOGY

Relative Accuracy

Relative accuracy or integral nonlinearity (INL) is a measure of

e maximum deviation, in LSBs, from a straight line passing

th

through the endpoints of the transfer function. Typical INL vs.

code plots are shown in

Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured

cha

nge and the ideal 1 LSB change between any two adjacent

codes. A specified differential nonlinearity of ±0.9 LSB maximum

ensures monotonicity. Typical DAC DNL vs. code plots can be

seen in

Figure 11, Figure 12, and Figure 13.

Tot a l U n ad ju s te d E rr o r ( TU E)

Total unadjusted error is a comprehensive specification that

in

cludes the sum of the relative accuracy error, gain error, and

offset error under a specified set of conditions.

Offset Error

Offset error is a measure of the offset error of the DAC and the

o

utput amplifier (see Figure 40 and Figure 41). It can be

gative or positive, and it is expressed in mV.

ne

Offset Error Match

Offset error match is the difference in offset error between any

tw

o channels.

Gain Error

Gain error is a measure of the span error of the DAC. It is the

de

viation in slope of the actual DAC transfer characteristic from

the ideal expressed as a percentage of the full-scale range.

Gain Error Match

Gain error match is the difference in gain error between any

tw

o channels.

Offset Error Drift

Offset error drift is a measure of the change in offset error

wi

th changes in temperature. It is expressed in ppm of

full-scale range/°C.

Gain Error Drift

Gain error drift is a measure of the change in gain error

wi

th changes in temperature. It is expressed in ppm of

full-scale range/°C.

Long-Term Temperature Drift

Long-term temperature drift is a measure of the change in

t

emperature error with the passage of time. It is expressed in °C.

The concept of long-term stability has been used for many years

to describe the amount an IC parameter shifts during its

lifetime. This is a concept that has typically been applied to both

voltage references and monolithic temperature sensors.

Figure 8, Figure 9, and Figure 10.

Unfortunately, integrated circuits cannot be evaluated at room

temperature (25°C) for 10 years or so to determine this shift.

Manufacturers perform accelerated lifetime testing of integrated

circuits by operating ICs at elevated temperatures (between

125°C and 150°C) over a shorter period (typically between

500 hours and 1000 hours). As a result, the lifetime of an

integrated circuit is significantly accelerated due to the increase

in rates of reaction within the semiconductor material.

DC Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by

cha

nges in the supply voltage. PSRR is the ratio of the change in

to a change in VDD for full-scale output of the DAC. It is

V

OUT

measured in dB. V

DC Crosstalk

DC crosstalk is the dc change in the output level of one DAC in

sponse to a change in the output of another DAC. It is

re

measured with a full-scale output change on one DAC while

monitoring another DAC. It is expressed in µV.

Reference Feedthrough

Reference feedthrough is the ratio of the amplitude of the signal

a

t the DAC output to the reference input when the DAC output

is not being updated (that is, LDAC is high). It is expressed in dB.

Channel-to-Channel Isolation

Channel-to-channel isolation is the ratio of the amplitude of the

s

ignal at the output of one DAC to a sine wave on the reference

input of another DAC. It is measured in dB.

Major Code Transition Glitch Energy

Major code transition glitch energy is the energy of the impulse

in

jected into the analog output when the code in the DAC

register changes state. It is normally specified as the area of the

glitch in nV-s and is measured when the digital code is changed

by 1 LSB at the major carry transition (011 . . . 11 to 100 . . . 00

or 100 . . . 00 to 011 . . . 11).

Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into

t

he analog output of a DAC from the digital input pins of the

device. However, it is measured when the DAC is not being

written to. It is specified in nV-s and is measured with a fullscale change on the digital input pins, that is, from all 0s to all

1s or vice versa.

Digital Crosstalk

Digital crosstalk is the glitch impulse transferred to the output

one DAC at midscale in response to a full-scale code change

of

(all 0s to all 1s and vice versa) in the input register of another

DAC. It is measured in standalone mode and is expressed in nV-s.

is held at 2 V and VDD is varied ±10%.

REF

Rev. B | Page 17 of 44

Page 18

ADT7516/ADT7517/ADT7519

Analog Crosstalk

Analog crosstalk is the glitch impulse transferred to the output

of

one DAC due to a change in the output of another DAC. It is

measured by loading one of the input registers with a full-scale

code change (all 0s to all 1s and vice versa) while keeping

LDAC

high. Then pulse

LDAC

low and monitor the output of

the DAC whose digital code was not changed. The area of the

glitch is expressed in nV-s.

DAC-to-DAC C rosst a l k

DAC-to-DAC crosstalk is the glitch impulse transferred to the

of one DAC due to a digital code change and subsequent

output

output change of another DAC. This includes both digital and

analog crosstalk. It is measured by loading one of the DACs

with a full-scale code change (all 0s to all 1s and vice versa) with

LDAC

low and monitoring the output of another DAC. The

energy of the glitch is expressed in nV-s.

Multiplying Bandwidth

The multiplying bandwidth is a measure of the finite bandwidth

o

f the amplifiers within the DAC. A sine wave on the reference

(with full-scale code loaded to the DAC) appears on the output.

The multiplying bandwidth is the frequency at which the output

amplitude falls to 3 dB below the input.

Total Harmonic Distortion (THD)

THD is the difference between an ideal sine wave and its

ttenuated version using the DAC. The sine wave is used as

a

the reference for the DAC, and the THD is a measure of the

harmonics present on the DAC output, expressed in dB.

Round Robin

The term round robin is used to describe the ADT7516/ADT7517/

ADT7519

cycling through the available measurement channels

in sequence, taking a measurement on each channel.

DAC Output S ettling Tim e

DAC output settling time is the time required, following a

rescribed data change, for the output of a DAC to reach and

p

remain within ±0.5 LSB of the final value. A typical prescribed

change is from 1/4 scale to 3/4 scale.

OUTPUT

VOLTAG E

NEGATIVE

OFFSET

ERROR

AMPLI FIER

FOOTROOM

NEGATIVE

OFFSET

ERROR

Figure 40. DAC Transfer Function with Negative Offset

LOWER

DEADBAND

CODES

DAC CODE

OUTPUT

VOLTAGE

POSITIVE

OFFSET

ERROR

Figure 41. DAC Transfer Function with Positive Offset (V

DAC CODE FUL L-SCALE

GAIN ERROR

OFFSET ERROR

ACTUAL

IDEAL

GAIN ERROR

OFFSET ERROR

UPPER

DEADBAND

CODES

ACTUAL

IDEAL

+

02883-007

+

02883-008

= VDD)

REF

Rev. B | Page 18 of 44

Page 19

ADT7516/ADT7517/ADT7519

THEORY OF OPERATION

Directly after the power-up calibration routine, the ADT7516/

ADT7517/ADT7519 go into idle mode. In this mode, the

devices are not performing any measurements and are fully

powered up. All four DAC outputs are at 0 V.

To begin monitoring, write to the Control Configuration 1

r

egister (Address 0x18) and set Bit C0 = 1. The ADT7516/

ADT7517/ADT7519 go into the power-up default measurement

mode (round robin). The devices proceed to take measurements

on the V

channel, internal temperature sensor channel,

DD

external temperature sensor channel (AIN1 and AIN2), AIN3,

and finally AIN4. After they finish taking measurements on the

AIN4 channel, the devices immediately loop back to start

taking measurements on the V

channel and repeat the same

DD

cycle as before. This loop continues until the monitoring is

stopped by resetting Bit C0 of the Control Configuration 1

register to 0.

It is also possible to continue monitoring as well as switching to

sin

gle-channel mode by writing to the Control Configuration 2

register (Address 0x19) and setting Bit C4 = 1. Further explanation of the single-channel and round robin measurement modes

is given in later sections. All measurement channels have

averaging enabled on them at power-up. Averaging forces the

devices to take an average of 16 readings before giving a final

measured result. To disable averaging and consequently

decrease the conversion time by a factor of 16, set Bit C5 = 1 in

the Control Configuration 2 register.

There are four single-ended analog input channels on the

ADT7516/AD

T7517/ADT7519, AIN1 to AIN4. AIN1 and

AIN2 are multiplexed with the external temperature sensor

terminals (D+ and D−). Bit C1 and Bit C2 of the Control

Configuration 1 register (Address 0x18) are used to select

between AIN1/AIN2 and the external temperature sensor.

The input range on the analog input channels is dependent on

whether the ADC reference used is the internal V

or VDD. To

REF

meet linearity specifications, it is recommended that the maximum

V

value is 5 V. Bit C4 of the Control Configuration 3 register

DD

be used to select between the internal reference and V

as the

DD

ADC reference of the analog inputs.

Controlling the DAC outputs can be done by writing to the MSB

a

nd LSB registers of the DAC (Address 0x10 to Address 0x17).

The power-up default setting is to have a low going pulse on the

LDAC

pin (Pin 9) controlling the updating of the DAC outputs

from the DAC registers. Alternatively, one can configure the

updating of the DAC outputs to be controlled by means other

than the

LDAC

pin by setting Bit C3 = 1 of the Control

Configuration 3 register (Address 0x1A). The DAC configuration register (Address 0x1B) and the LDAC configuration

register (Address 0x1C) can now be used to control the DAC

updating. These two registers also control the output range of

the DACs and select between the internal or external reference.

DAC A and DAC B outputs can be configured to give a voltage

output proportional to the temperature of the internal and

external temperature sensors, respectively.

2

The dual serial interface defaults to the I

C protocol on powerup. To select and lock in the SPI protocol, follow the selection

process as described in the

2

C protocol cannot be locked in, though the SPI protocol

The I

Serial Interface Selection section.

is automatically locked in on selection. The interface can be

switched back to be I

off and on. When using I

or GND.

V

DD

2

C on selection when the device is powered

2

C, the CS pin should be tied to either

There are a number of different operating modes on the

ADT7516/AD

T7517/ADT7519 devices and all of them can be

controlled by the configuration registers. These features consist

of enabling and disabling interrupts, polarity of the INT/

INT

pin, enabling and disabling the averaging on the measurement

cha

nnels SMBus timeout, and software reset.

POWER-UP CALIBRATION

It is recommended that no communication to the part be

initiated until approximately 5 ms after V

has settled to

DD

within 10% of its final value. It is generally accepted that most

systems take a maximum of 50 ms to power up. Power-up time

is directly related to the amount of decoupling on the voltage

supply line.

During the 5 ms after V

has settled, the part is performing a

DD

calibration routine. Any communication to the device during

calibration interrupts this routine, and can cause erroneous

temperature measurements. If it is not possible to have V

DD

at its

nominal value by the time 50 ms has elapsed or if communication

to the device has started prior to V

that a measurement be taken on the V

temperature measurement is taken. The V

settling, it is recommended

DD

channel before a

DD

measurement is

DD

used to calibrate out any temperature measurement error due to

different supply voltage values.

CONVERSION SPEED

The internal oscillator circuit used by the ADC has the capability

to output two different clock frequencies. This means that the

ADC is capable of running at two different speeds when doing a

conversion on a measurement channel. Thus, the time taken to

perform a conversion on a channel can be reduced by setting

Bit C0 of the Control Configuration 3 register (Address 0x1A).

This increases the ADC clock speed from 1.4 kHz to 22 kHz. At

the higher clock speed, the analog filters on the D+ and D–

input pins (external temperature sensors) are switched off. This

is why the power-up default setting is to have the ADC working

at the slow speed. The typical times for fast and slow ADC

speeds are given in the

Specifications section.

Rev. B | Page 19 of 44

Page 20

ADT7516/ADT7517/ADT7519

V

V

The ADT7516/ADT7517/ADT7519 power up with averaging

on. This means every channel is measured 16 times and internally averaged to reduce noise. The conversion time can also be

sped up by turning off the averaging. This is done by setting

Bit C5 of the Control Configuration 2 register (Address 0x19) to 1.

FUNCTION DESCRIPTION—VOLTAGE OUTPUT

Digital-to-Analog Converters

The ADT7516/ADT7517/ADT7519 have four resistor string

DACs fabricated on a CMOS process with resolutions of 12, 10,

and 8 bits, respectively. They contain four output buffer amplifiers

and are written to via I

See the Serial Interface section for more information.

The ADT7516/ADT7517/ADT7519 operate from a single

supply of 2.7 V to 5.5 V, and the output buffer amplifiers

provide rail-to-rail output swing with a slew rate of 0.7 V/μs. All

four DACs share a common reference input, V

reference input is buffered to draw virtually no current from the

reference source because it offers the source a high impedance

input. The devices have a power-down mode to completely turn

off all DACs with a high impedance output.

Each DAC output is not updated until it receives the LDAC

command. Therefore, though the DAC registers would have

been written to with a new value, this value is not represented

by a voltage output until the DACs receive the LDAC command.

Reading back from any DAC register prior to issuing an LDAC

command results in the digital value that corresponds to the

DAC output voltage. Thus, the digital value written to the DAC

register cannot be read back until after the LDAC command has

been initiated. This LDAC command can be given by either

pulling the

LDAC

Bit D4 and Bit D5 of the DAC configuration register

(Address 0x1B), or using the LDAC register (Address 0x1C).

When using the

the low going pulse width should be 20 ns minimum. The

LDAC

pin has to go high and low again before the DAC

registers can be reloaded.

Digital-to-Analog Section

The architecture of one DAC channel consists of a resistor string

DAC followed by an output buffer amplifier. The voltage at the

V

-IN pin or the on-chip reference of 2.28 V provides the

REF

reference voltage for the corresponding DAC. Figure 42 shows a

block diagram of the DAC architecture. Because the input

coding to the DAC is straight binary, the ideal output voltage is

given by

V

=

OUT

where:

D = decimal equivalent of the binary code that is loaded to the

DAC register

2

C serial interface or SPI serial interface.

-IN. The

REF

pin low (falling edge loads DACs), setting up

LDAC

pin to control the DAC register loading,

DV

×

REF

N

2

0 to 255 for ADT7519 (8 bits)

0 to 1023 for ADT7517 (10 bits)

0 to 4095 for ADT7516 (12 bits)

N = DAC resolution.

Resistor String

The resistor string section is shown in Figure 43. It is simply a

string of resistors, each of approximately 603 Ω. The digital

code loaded to the DAC register determines at which node on

the string the voltage is tapped off to be fed into the output

amplifier. The voltage is tapped off by closing one of the

switches connecting the string to the amplifier. Because it is a

string of resistors, it is guaranteed monotonic.

-IN

REF

REFERENCE

BUFFER

INT V

INPUT

REGISTER

REF

DAC

REGISTER

Figure 42. Single DAC Channel Architecture

RESISTOR

STRING

GAIN MODE

(GAIN = 1 OR 2)

OUTPUT BUF F E R

AMPLIFIER

V

-A

OUT

02883-041

R

R

R

R

R

Figure 43. Resistor String

2.28V

INTERNAL V

Figure 44. DAC Reference Buffer Circuit

REF

TO OUTPUT

AMPLIFIER

REF

STRING

DAC A

STRING

DAC B

STRING

DAC C

STRING

DAC D

-IN

02883-042

02883-043

Rev. B | Page 20 of 44

Page 21

ADT7516/ADT7517/ADT7519

V

DAC Reference Inputs

There is an input reference pin for the DACs. This reference

input is buffered (see Figure 44).

The advantage of the buffered input is the high impedance it

p

resents to the voltage source driving it. The user can have an

external reference voltage as low as 1 V and as high as V

DD

. The

restriction of 1 V is due to the footroom of the reference buffer.

LDAC

The

configuration register controls the option to select

between internal and external voltage references. The default

selection is external reference.

Output Amplifier

The output buffer amplifier can generate output voltages to

within 1 mV of either rail. Its actual range depends on the value

of V

, gain, and offset error.

REF

If a gain of 1 is selected (Bit 0 to Bit 3 of the DAC configuration

r

egister = 0), the output range is 0.001 V to V

REF

.

If a gain of 2 is selected (Bit 0 to Bit 3 of the DAC configuration

r

egister = 1), the output range is 0.001 V to 2 V

. Because

REF

of clamping, however, the maximum output is limited to

V

− 0.001 V.

DD

The output amplifier can drive a load of 4.7 kΩ to GND or V

in parallel with 200 pF to GND or V

(see Figure 5). The

DD

DD

source and sink capabilities of the output amplifier can be seen

in the plot of

Figure 18.

The slew rate is 0.7 V/µs with a half-scale settling time to

B (at 8 bits) of 6 µs.

±0.5 LS

Thermal Voltage Output

The ADT7516/ADT7517/ADT7519 can output voltages that are

proportional to temperature. DAC A output can be configured

to represent the temperature of the internal sensor and the DAC B

output can be configured to represent the external temperature

sensor. Bit C5 and Bit C6 of the Control Configuration 3 register

select the temperature proportional output voltage. Each time a

temperature measurement is taken, the DAC output is updated.

The output resolution for the ADT7519 is 8 bits with 1°C change

corresponding to 1 LSB change. The output resolution for the

ADT7516 and ADT7517 is capable of 10 bits with 0.25°C change

OPTIONAL CAPACITOR, UP TO

3nF MAX. CAN BE ADDED TO

IMPROVE HIGH FREQ UENCY

NOISE REJECT ION IN NOISY

ENVIRONMENTS

REMOTE

SENSING

TRANSISTOR

(2N3906)

Figure 45. Signal Conditioning for External Diode Temperature Sensor

D+

C1

D–

LOW-PASS

FILTER

f

= 65kHz

C

,

I N × I I

corresponding to 1 LSB change. The default output resolution

for the ADT7516 and ADT7517 is 8 bits. To increase this to

10 bits, set C1 = 1 in the Control Configuration 3 register. The

default output range is 0 V to V

0 V to 2 V

. Increasing the output voltage span to 2 V

REF

and this can be increased to

REF

be done by setting D0 = 1 for DAC A (internal temperature

sensor) and D1 = 1 for DAC B (external temperature sensor) in

the DAC configuration register (Address 0x1B).

The output voltage is capable of tracking a maximum temperat

ure range of −128°C to +127°C, but the default setting is

−40°C to +127°C. If the output voltage range is 0 V to V

-IN = 2.25 V), then this corresponds to 0 V representing

(V

REF

−40°C, and 1.48 V representing +127°C. This, of course, gives

an upper deadband between 1.48 V and V

REF

.

The internal and external analog temperature offset registers

n be used to vary this upper deadband and, consequently, the

ca

temperature that 0 V corresponds to.

mples of how this is done using a DAC output voltage span

exa

of V

and 2 V

REF

, respectively. Simply write in the temperature

REF

Tabl e 6 and Ta b le 7 give

value, in twos complement format, at which 0 V is to start. For

example, if using the DAC A output and 0 V to start at −40°C,

program 0xD8 into the internal analog temperature offset

register (Address 0x21). This is an 8-bit register and has a

temperature offset resolution of only 1°C for all device models.

Use Equation 1 to Equation 4 to determine the value to

program into the offset registers.

Table 6. Thermal Voltage Output (0 V to V

REF

)

O/P Voltage (V) Default °C Max °C Sample °C

0 −40 −128 0

0.5 +17 −71 +56

1 +73 −15

1.12 +87 −1

1.47 +127 +39

1.5 UDB1 +42 UDB

2 UDB

2.25 UDB

1

Upper deadband has been reached. DAC output is not capable of increasing.

See Figure 41.

DD

BIAS

BIAS

DIODE

1

1

V

OUT+

TO ADC

V

OUT–

+99 UDB

+127 UDB

02883-044

REF

REF

+113

+127

UDB

can

-IN

1

1

1

1

Rev. B | Page 21 of 44

Page 22

ADT7516/ADT7517/ADT7519

T

V

I N × I I

INTERNAL

SENSE

RANSISTOR

BIAS

DIODE

Figure 46. Top Level Structure of Int

Table 7. Thermal Voltage Output (0 V to 2 V

REF

)

O/P Voltage (V) Default °C Max °C Sample °C

0 –40 –128 0

0.25 –26 –114 +14

0.5 +12 –100 +28

0.75 +3 –85 +43

1 +17 –71 +57

1.12 +23 –65 +63

1.47 +43 –45 +83

1.5 +45 –43 +85

2 +73 –15 +113

2.25 +88 0 +127

2.5 +102 +14 UDB1

2.75 +116 +28 UDB1

3 UDB1 +42 UDB1

3.25 UDB1 +56 UDB1

3.5 UDB1 +70 UDB1

3.75 UDB1 +85 UDB1

4 UDB1 +99 UDB1

4.25 UDB1 +113 UDB1

4.5 UDB1 +127 UDB1

1

Upper deadband has been reached. DAC output is not capable of increasing.

See Figure 41.

For negative temperatures,

Offset Register Code (d) = (0 V

Temp) + 128 (1)

where D7 of Offset Register Code is set to 1 for negative

emperatures.

t

For example,

Offset Register Code (d) = −40 + 128 = 88d = 0x58

Since a negative temperature has been inserted into the

e

quation, DB7 (MSB) of the offset register code is set to 1.

Therefore, 0x58 becomes 0xD8.

0x58 + DB7(1) = 0xD8

For positive temperatures,

Offset Register Code (d) = 0 V

Temp (2)

BIAS

DD

V

OUT+

TO ADC

V

OUT–

2883-045

ernal Temperature Sensor

For example,

Offset Register Code (d) = 10d

= 0x0A

The following equation is used to work out the various

t

emperatures for the corresponding 8-bit DAC output:

8-Bit Temp = (DAC O/P)/1 LS

For example, if the output is 1.5 V, V

has an LSB size = 2.25 V/256 = 8.79 × 10

B + (0 V Temp) (3)

-IN = 2.25 V, 8-bit DAC

REF

–3

, and 0 V temp is at

−128°C, then the resultant temperature is

−3

1.5/(8.79 × 10

) + (−128) = +43°C

The following equation is used to work out the various

emperatures for the corresponding 10-bit DAC output:

t

10-Bit Temp = [(DAC O/

For example, if the output is 0.4991 V, V

DAC has an LSB size = 2.25 V/1024 = 2.197 × 10

P)/1 LSB] × 0.25 + (0 V Temp) (4)

-IN = 2.25 V, 10-bit

REF

–3

, and 0 V

temperature is at −40°C, then the resulting temperature is

–3

[0.4991/(2.197 × 10

)] × 0.25 + (–40) = +16.75°C

Figure 47 shows a graph of the DAC output vs. temperature for

a V

-IN = 2.25 V.

REF

2.25

2.10

1.95

1.80

1.65

1.50

1.35

1.20

1.05

0.90

DAC OUTPUT (V)

0.75

0.60

0.45

0.30

0.15

0

–128 –110 –90 –70 –50 –30 –10 10 30 50 70 90 110 127

TEMPERATURE (°C)

Figure 47. DAC Output vs. Temperature V

0V = –128°C

0V = –40°C

REF

0V = 0°C

-IN = 2.25 V

02883-046

Rev. B | Page 22 of 44

Page 23

ADT7516/ADT7517/ADT7519

A

A

th

FUNCTIONAL DESCRIPTION—ANALOG INPUTS

Single-Ended Inputs

The ADT7516/ADT7517/ADT7519 offer four single-ended

analog input channels. The analog input range is from 0 V to

2.28 V, or 0 V to V

is recommended that the maximum V

Selection between the two input ranges is done by Bit C4 of the

Control Configuration 3 register (Address 0x1A). Setting this

bit to 0 sets up the analog input ADC reference to be sourced

from the internal voltage reference of 2.28 V. Setting the bit to 1

sets up the ADC reference to be sourced from V

The ADC resolution is 10 bits and is mostly suitable for dc

put signals. Bits[C1:C2] of the Control Configuration 1

in

register (Address 0x18) are used to set up Pin 7 and Pin 8 as

AIN1 and AIN2.

-channel analog input path.

4

AIN1

AIN2

AIN3

AIN4

Converter Operation

The analog input channels use a successive approximation ADC

based on a capacitor DAC. Figure 49 and Figure 50 show simplif

ied schematics of the ADC. Figure 49 shows the ADC during

uisition phase. SW2 is closed and SW1 is in Position A.

acq

The comparator is held in a balanced condition and the

sampling capacitor acquires the signal on AIN.

IN

REF/2

IN

REF/2

When the ADC eventually goes into conversion phase (see

Figure 50), SW2 opens and SW1 moves to Position B, causing

. To maintain the linearity specification, it

DD

value be set at 5 V.

DD

Figure 48 shows the overall view of the

M

U

L

T

I

P

L

E

X

E

R

10-BIT

ADC

Figure 48. Quad Analog Input Path

INT V

SAMPLING

CAPACITOR

A

SW1

B

SW2

ACQUISITI ON

PHASE

COMPARATOR

Figure 49. ADC Acquisition Phase

INT V

SAMPLING

CAPACITOR

A

SW1

B

SW2

CONVERSION

PHASE

COMPARATOR

Figure 50. ADC Conversion Phase

REF

REF

TO ADC

VAL UE

REGISTER

CAP DAC

CONTROL

LOGIC

CAP DAC

CONTROL

LOGIC

REF

REF

DD

.

02883-047

V

DD

02883-048

V

DD

02883-049

e comparator to become unbalanced. The control logic and

the DAC are used to add and subtract fixed amounts of charge

from the sampling capacitor to bring the comparator back into

a balanced condition. When the comparator is rebalanced, the

conversion is complete. The control logic generates the ADC

output code.

alog inputs.

an

Figure 51 shows the ADC transfer function for the

ADC TRANSFER FUNCTION

The output coding of the ADT7516/ADT7517/ADT7519 analog

inputs is straight binary. The designed code transitions occur

midway between successive integer LSB values (that is, 1/2 LSB,

3/2 LSB). The LSB is V

V

= 2.28 V. The ideal transfer characteristic is shown in

REF

Figure 51.

111. ..111

111.. .110

111. ..00 0

011. ..111

ADC CODE

000...010

000...001

000...000

Figure 51. Single-Ended Transfer Function

To work out the voltage on any analog input channel, the

following method can be used:

1 LSB = reference (V)/1024

Convert value read back from AIN value register into decimal.

AIN voltage =

where d =

decimal.

For example, if internal reference is used, V

AIN value = 512d

1 LSB size = 2.2

AIN voltage = 512 × 2.226 × 10

Analog Input ESD Protection

Figure 52 shows the input structure on any of the analog input

pins that provide ESD protection. The diode provides the main

ESD protection for the analog inputs. Care must be taken that

the analog input signal never drops below the GND rail by

more than 200 mV. If this happens, the diode becomes forwardbiased and starts conducting current into the substrate. The

4 pF capacitor is the typical pin capacitance and the resistor is a

lumped component made up of the on resistance of the

multiplexer switch.

/1024 or internal V

DD

1LSB = INT V

1LSB = V

ANALOG INPUT

REF

/1024

DD

+V

– 1LSB0V 1/2LSB

REF

AIN value (d) × LSB size

8 V/1024 = 2.226 × 10

−3

= 1.14 V

/1024, internal

REF

/1024

= 2.28 V.

REF

−3

02883-050

Rev. B | Page 23 of 44

Page 24

ADT7516/ADT7517/ADT7519

A

Ω

IN

4pF

100

02883-051

Figure 52. Equivalent Analog Input ESD Circuit

AIN Interrupts

The measured results from the AIN inputs are compared with

the AIN V

(greater than comparison) and V

HIGH

(less than or

LOW

equal to comparison) limits. An interrupt occurs if the AIN

inputs exceed or equal the limit registers. These voltage limits

are stored in on-chip registers. Note that the limit registers are

8 bits long and the AIN conversion result is 10 bits long. If the

S/W RESET

INTERRUPT

STATUS

REGISTER

(TEMP AND

AIN1 TO AIN4)

STATUS BITSSTATUS BIT

WATCHDOG

LIMIT

COMPARISONS

INTERRUPT

STATUS

REGIS TER 2

(V

)

DD

INTERRUPT

REGISTERS

MASK

voltage limits are not masked out, then any out-of-limit comparisons generate flags that are stored in the Interrupt Status 1

register (Address = 0x00) and one or more out-of-limit results

cause the INT/

INT

output to pull either high or low depending

on the output polarity setting. It is good design practice to mask

out interrupts for channels that are of no concern to the

application. Figure 53 shows the interrupt structure for the

ADT7516/ ADT7517/ADT751

9. It gives a block diagram

representation of how the various measurement channels affect

the INT/

INTERNAL

TEMP

EXTERNAL

TEMP

V

DD

DIODE

FAULT

AIN1 TO AIN4

INT

pin.

INT/INT

(LATCHED OUTPUT)

INT/INT

READ RESET

CONTROL

CONFIGURATION

REGISTER 1

ENABLE BIT

02883-052

Figure 53. ADT7516/ADT7517/ADT7519 Interrupt Structure

Rev. B | Page 24 of 44

Page 25

ADT7516/ADT7517/ADT7519

FUNCTIONAL DESCRIPTION—MEASUREMENT

Temperature Sensor

The ADT7516/ADT7517/ADT7519 contain an ADC with

special input signal conditioning to enable operation with

external and on-chip diode temperature sensors. When the

ADT7516/ADT7517/ADT7519 operate in single-channel mode,

the ADC continually processes the measurement taken on one

channel only. This channel is preselected by Bits[C0:C2] in the

Control Configuration 2 register (Address 0x19). When in

round robin mode, the analog input multiplexer sequentially

selects the V

to measure its internal temperature, either the external temperature sensor or AIN1 and AIN2, AIN3, and then AIN4. These

signals are digitized by the ADC and the results are stored in

the various value registers.

The measured results from the temperature sensors are com-

ared with the internal and external T

p

These temperature limits are stored in on-chip registers. If the

temperature limits are not masked, any out-of-limit comparisons

generate flags that are stored in the Interrupt Status 1 register.

One or more out-of-limit results cause the INT/

pull either high or low depending on the output polarity setting.

Theoretically, the temperature measuring circuit can measure

t

emperatures from −128°C to +127°C with a resolution of

0.25°C. However, temperatures outside T

guaranteed operating temperature range of the device.

Temperature measurement from −128°C to +127°C is possible

using an external sensor.

Temperature measurement is initiated by three methods. The

irst method is applicable when the part is in single-channel

f

measurement mode. The temperature is measured 16 times and

internally averaged to reduce noise. In single-channel mode, the

part is continuously monitoring the selected channel, that is, as

soon as one measurement is taken another one is started on the

same channel. The total time to measure a temperature channel

with the ADC operating at slow speed is typically 11.4 ms

(712 µs × 16) for the internal temperature sensor and 24.22 ms

(1.51 ms × 16) for the external temperature sensor. The new

temperature value is stored in two 8-bit registers and is ready

for reading by the I

of disabling the averaging by setting Bit 5 in the Control

Configuration 2 register (Address 0x19). The ADT7516/

ADT7517/ADT7519 default on power-up is with averaging

enabled.

The second method is applicable when the part is in round

ro

bin measurement mode. The part measures both the internal

and external temperature sensors as it cycles through all

possible measurement channels. The two temperature channels

are measured each time the part runs a round robin sequence.

In round robin mode, the part is continuously measuring all

channels.

input channel, the on-chip temperature sensor

DD

and T

HIGH

are outside the

A

2

C or SPI interface. The user has the option

LOW

INT

limits.

output to

Temperature measurement is also initiated after every read or

wr

ite to the part when the part is in either single-channel

measurement mode or round robin measurement mode.

Once serial communication has started, any conversion in

p

rogress stops and the ADC resets. Conversion restarts

immediately after the serial communication has finished. The

temperature measurement proceeds normally as described above.

V

Monitoring

DD

The ADT7516/ADT7517/ADT7519 also have the ability to

monitor their own power supply. The part measures the voltage

on its V

pin to a resolution of 10 bits. The resulting value is

DD

stored in two 8-bit registers; the two LSBs are stored in register

Address 0x03 and the eight MSBs are stored in register

Address 0x06. This allows the option of doing just a 1-byte read

if 10-bit resolution is not important. The measured result is

compared with the V

HIGH

and V

limits. If the VDD interrupt is

LOW

not masked, any out-of-limit comparison generates a flag in the

Interrupt Status 2 register and one or more out-of-limit results

cause the INT/

INT

output to pull either high or low, depending

on the output polarity setting.

Measuring the voltage on the V

pin is regarded as monitoring

DD

a channel along with the internal, external, and AIN channels.

The user can select the V

channel for single-channel

DD

measurement by setting Bit C4 = 1 and setting Bits[C0:C2] to all

0s in the Control Configuration 2 register.

When measuring the V

value, the reference for the ADC is

DD

sourced from the internal reference. Tab l e 8 shows the data

fo

rmat. As the maximum measurable V