Page 1

a

R

DSP

ADSP-2141L

APPLICATIONS

Security Coprocessor for High Speed Networking Prod-

ucts (Routers, Switches, Hubs)

Cryptographic Core for Firewalls, Hardware Encryptors,

and More

Crypto Peripheral for Implementing Secure NIC Adapt-

ers (10/100 Ethernet, Token Ring, ISDN)

Secure Modem-on-a-Chip (V.34, ADSL)

FEATURES

DES CRYPTO BLOCK

640 Mbps Sustained Performance—Single DES

214 Mbps Sustained Performance—Triple DES

Supports All Modes: ECB; CBC; 64-Bit OFB; and 1-, 8-,

64-Bit CFB. Includes Automatic Padding

Implements IPsec ESP Transforms Autonomously at

OC-3 (155 Mbps) Rates (3-DES, SHA-1)

HASH BLOCK

Hardware-Based SHA-1 and MD-5 Hashing

253 Mbps Sustained Performance—SHA-1

315 Mbps Sustained Performance—MD-5

Implements IPsec AH and HMAC Transforms

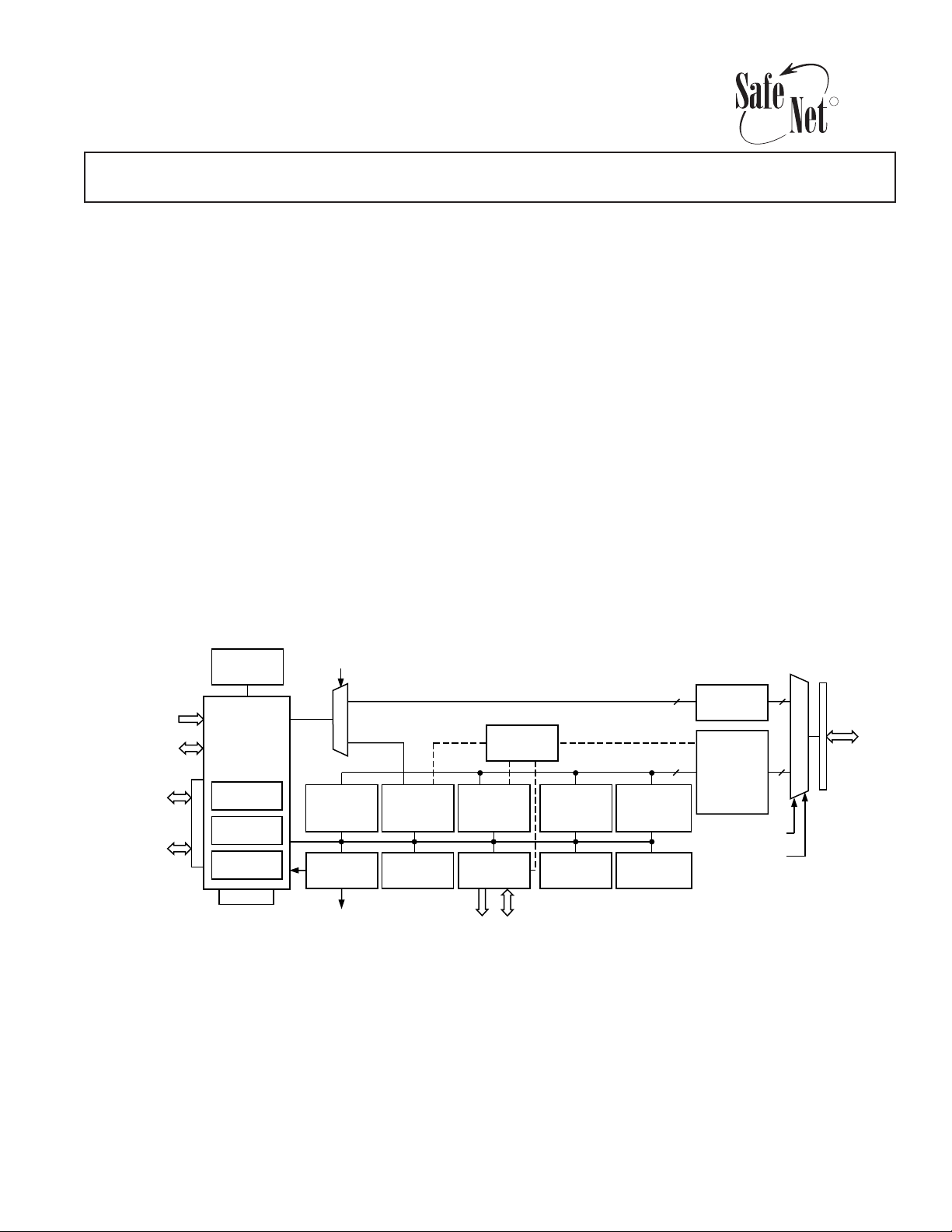

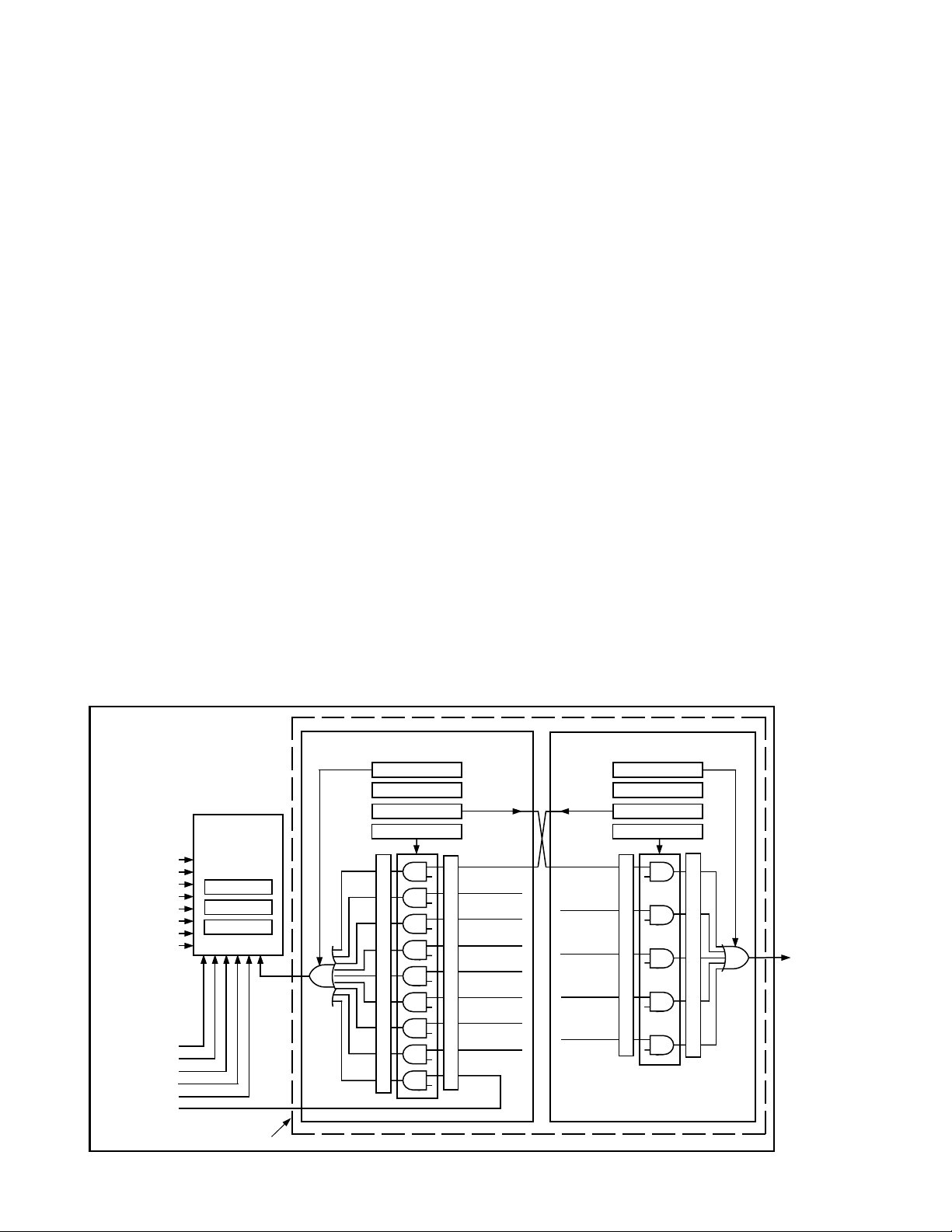

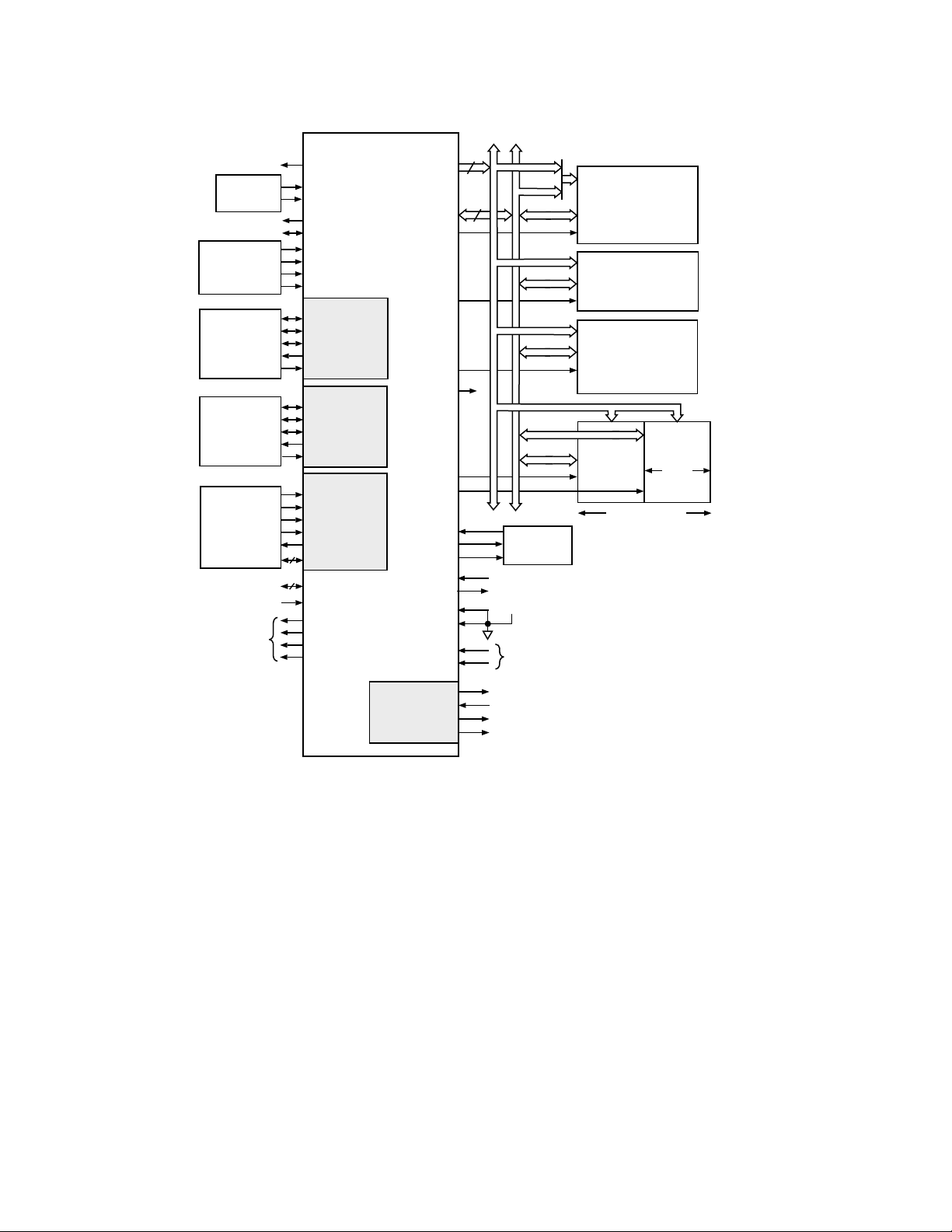

FUNCTIONAL BLOCK DIAGRAM

INTERRUPTS

FLAGS

SPORT 0

SERIAL

PORTS

SPORT 1

KERNEL

MODE

CONTROL

ADSP-218x

DSP CORE

KERNEL ROM

32K 3 24

PROG ROM

16K 3 24

DATA ROM

16K 3 16

TIMER

BUS_MODE

IDMA

BUS

PROTECTED

KERNEL

RAM

(4K 3 16)

INTERRUPT

CONTROLLER

PF7/INT_H

IDMA MODE

PCI MODE

ENCRYPT

(DES, 3-DES)

APPLICATION

REGISTERS

BLOCK

(MD-5, SHA-1)

26-BITS

ADDR

HASH

BLOCK

EXTERNAL

MEMORY

INTERFACE

RAM/ROM

SECURE KERNEL CONTROL

Tamper-Resistant Isolation of Cryptographic Functions

Enforces Security Perimeter Around Crypto Functions

and Crypto Storage Locations

Anticloning Protection

Secure Algorithm Download

SafeNet CGX LIBRARY

On-Chip SafeNet CGX Crypto Library with Flexible CGX

API

Includes

Chained

and

Parallel Execution

Commands

Such as Hash-and-Encrypt

Embodied as 32K Words (32K ⴛ 24) Kernel Program

Mask-Programmed into On-Chip ROM

On-Chip Protected 4K ⴛ 16 Security Scratchpad RAM

RANDOM NUMBER GENERATOR

Hardware-Based Nondeterministic Random Number

Generator

Generates Internal Session Keys That Are Never

Exposed Outside of the SafeNet DSP

Redundant Fail-Safe Design

Up to 1.3 Mbits of Random Data Available per Second

DMA-32

CONTROLLER

32-BITS

DATA

RNG

BLOCK

LASER

VARIABLE

STORE

16

32

PUBLIC KEY

ACCELERATOR

EMI BUS

SERIAL

EEPROM

INTERFACE

IDMA

INTERFACE

PCI OR

CARDBUS

INTERFACE

BUS_MODE

BUS_SEL

16

32

16OR

32-BIT

BUS

SafeNet is a registered trademark of Information Resource Engineering (IRE).

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

Page 2

ADSP-2141L

PUBLIC KEY ACCELERATOR

Accelerator for Math-Intensive Public Key Operations

Diffie-Hellman Negotiate: <29 ms (1024-Bit Modulus,

180-Bit Exponent)

RSA 1024-Bit Sign: <29 ms; RSA 1024-Bit Verify: 6 ms

DSA Sign: <39 ms; DSA Verify: <66 ms

KEY MANAGEMENT BLOCK

Laser-Programmed Unique Triple-DES Cryptovariable

Protects Off-Chip Storage

Support for Secure Storage of Both Secret Keys and

Public/Private Key Pairs

Trust-Model Rules Enforcement

Only Encrypted Keys May Be Exported Off the Chip

Internal Key Cache for 15 Keys—Can Be Expanded to

700 Keys On-Chip

Keys May Also Be Securely Stored Off-Chip, Allowing

Unlimited Storage

DSP CORE

40 MIPS Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

Zero-Overhead Looping

Low Power Dissipation

16K Words (16K ⴛ 24) On-Chip Program RAM

16K Words (16K ⴛ 16) On-Chip Data RAM

64M Words Off-Chip Program and Data Memory

Programmable 16-Bit Interval Timer with Prescale

PCI BUS/CARDBUS INTERFACE

32-Bit 3.3 V Bus Interface

MHz or 40 MHz* Bus Speed

33

Bus Master and Target Modes

Can Directly DMA Between Crypto Functions and Other

PCI Bus Agents

*66 MHz speed pending chip characterization.

GENERAL DESCRIPTION

The ADSP-2141L SafeNet DSP is a highly integrated embedded

security processor that incorporates a sophisticated, general

purpose DSP, along with a number of high performance Cryptographic function blocks, as well as PCI, DMA and Serial

EEPROM interfaces. It is fabricated in 0.35 µ CMOS triple-

layer metal technology and uses a 3.3 V power supply. It is

available in a 208-lead MQFP package with a commercial (0°C

to 70°C) temperature range.

DSP Core

The DSP is a standard Analog Devices ADSP-218x core with

full ADSP-2100 family compatibility. The ADSP-218x Core

combines the base DSP components from the ADSP-2100

family with the addition of two serial ports, a 16-bit internal

DMA port, a byte DMA port, a programmable timer, Flag I/O,

extensive interrupt capabilities, and on-chip program and data

memory. The external memory interface of the 218x core has

been extended to support up to 64M-words addressing for both

program and data memory. Some core enhancements have been

added in the ADSP-2141L, including on-chip security ROM

and interrupt functions. Refer to the Analog Devices ADSP-2183

data sheet for further information.

SafeNet CGX Library–Secure Kernel

The SafeNet CGX Library is a crypto library embodied as firmware (a secure kernel) that is mask-programmed into ROM within

the DSP. This solution protects the library from tampering. The

CGX Library provides the Application Programming Interface

(API) to applications that require security services from the

ADSP-2141L. Those applications may be software executing in

user mode on the DSP, or they may be external host software

accessing the ADSP-2141L via a PCI bus. Approximately 40

Crypto commands—called CGX (CryptoGraphic eXtensions)—

are provided at the API and a simple control block structure is

used to pass arguments into the secure kernel and return status.

The CGX library includes integrated drivers for the various

hardware crypto blocks on the chip. This allows the programmer to ignore those details and concentrate on other product

design issues.

The CGX library firmware runs under a protected mode state

of the DSP as described in the Kernel Mode Control section

following. This guarantees the security integrity of the system

during the execution of CGX processes and, for example, prevents

disclosure of cryptographic key data or tampering with a

security operation.

Kernel Mode Control

The Kernel Mode Control subsystem is responsible for enforcing

the security perimeter around the cryptographic functions of

the ADSP-2141L. The device may operate in either user mode

(kernel space is not accessible) or kernel mode (kernel space is

accessible) at a given time. When in kernel mode, the kernel RAM

and certain protected crypto registers and functions (kernel

space) are accessible only to the CGX library firmware. The

CGX Library executes host-requested macro-level functions

and then returns control to the calling application. The kernel

mode control subsystem resets the DSP should any security

violation occur, such as attempting to access a protected

memory location while in user mode.

–2–

REV. 0

Page 3

ADSP-2141L

Protected Kernel RAM

The 4K × 16 kernel RAM provides a secure storage area on the

ADSP-2141L for sensitive data such as keys or intermediate

calculations during public key operations. The Kernel Mode

Control subsystem (above) enforces the protection by allowing

only internal secure kernel mode access to this RAM. A public

keyset and a cache of up to 15 secret keys may be stored in kernel

RAM. Secure key storage may be expanded to 700 secret keys

by assigning segments of the DSP’s internal data RAM to be

protected. Furthermore, a virtually unlimited number of data

encryption keys may be stored in an encrypted form in off-chip

memory.

Encrypt Block

The encrypt block performs high speed DES and Triple-DES

encrypt/decrypt operations. All four standard modes of DES are

supported: Electronic Code Book (ECB), Cipher Block Chaining

(CBC), 64-bit Output Feedback (OFB) and 1-bit, 8-bit and 64bit Cipher Feedback (CFB). The DES encrypt/decrypt operations

are highly pipelined and execute full 16-round DES in only four

clock cycles. Hardware support for padding insertion, verification

and removal further accelerates the encryption operation. Context switching is provided to minimize the overhead of changing

crypto keys and Initialization Vectors (IVs) to nearly zero.

Hash Block

The secure hash block is tightly coupled with the encrypt block

and provides hardware accelerated one-way hash functions.

Both the MD-5 and SHA-1 algorithms are supported. Combined

operations that chain both hashing and encrypt/decrypt functions

are provided in order to significantly reduce the processing time

for data that needs both operations applied. For hash-then-encrypt

and hash-then-decrypt operations, the ADSP-2141L can perform

parallel execution of both functions from the same source and

destination buffers. For encrypt-then-hash and decrypt-then-hash

operations, the processing must be sequential, but minimum

latency is still provided through the pipeline chaining design. An

offset may be specified between the start of hashing and the

start of encryption to support certain protocols such as IPsec. A

‘mutable bit handler’ is also provided on the hash engine to

facilitate IPsec AH processing.

Random Number Generator (RNG) Block

The hardware random number generator provides a true, nondeterministic noise source for the purpose of generating keys,

Initialization Vectors (IVs), and other random number requirements. Random numbers are provided as 16-bit words to the

kernel. The CGX kernel requests random numbers as needed to

perform requested CGX commands such as CGX_Gen_Key,

and can also directly supply from 1 to 65,535 random bytes to a

host application via the CGX_Random command.

Public Key Accelerator

The public key accelerator module works in concert with the

CGX kernel firmware to provide full public key services to the

host application. The kernel provides macro-level functions to

perform Diffie-Hellman key agreement, RSA encrypt or decrypt,

DSA compute and verify digital signatures. The hardware accelerator block speeds computation-intensive operations such as

large vector multiply, add, subtract, square.

PCI/Cardbus Interface

A full 40 MHz/33 MHz PCI bus interface has been added to the

core DSP functions. The 32-bit PCI interface supports both bus

master and target modes. The ADSP-2141L is capable of using

DMA to directly access data on other PCI entities and pass that

data through its encryption/hash engines.

32-Bit DMA Controller

The ADSP-2141L incorporates a high performance 32-bit DMA

controller which can be set up to move data efficiently between

Host PCI memory, the hash/encrypt blocks, and/or external

memory. The DMA controller can be used with the PCI bus in

master mode, thus autonomously moving 32-bit data with minimal DSP intervention. Up to 255 long words (1020 bytes) can

be moved in a burst at up to 160 Mbytes per second.

Application Registers

The application registers are a set of memory-mapped registers

that facilitate communications between the ADSP-2141L and a

host processor via the PCI bus. One of the registers is a mailbox

that is 44 bytes long and set up to hold the CGX command

structure passed between the host and DSP processors. The

application registers also provide the mechanism that allows the

DSP and the external host to negotiate ownership of the hash/

encrypt block.

Serial EEPROM Interface

The serial EEPROM interface allows an external nonvolatile

memory to be connected to the ADSP-2141L for storing PCI

configuration information (Plug and Play), as well as generalpurpose nonvolatile storage. For example, encrypted (black)

keys could be stored into EEPROM for fast recovery after a

power outage.

Interrupt Controller

The DSP core provides support for 14 interrupt sources, including six external and eight internal. All interrupts are prioritized

into 12 levels and interrupt nesting may be enabled or disabled

under software control. The security block interrupt controller

provides enhancements to the DSP interrupt functions.

Primarily, the interrupt controller provides a new interrupt

generation capability to the DSP or to an external host processor.

Under programmable configuration control, a crypto interrupt

may be generated due to completion of certain operations such

as encrypt complete, hash complete. The interrupt may either

be directed at the DSP core (on IRQ2), or provided on an output line (PF7/INT_H) to a host subsystem.

Laser Variable Storage

The laser variable storage consists of 256 bits of tamper-proof

factory-programmed data that is only accessible to the internal

function blocks and the security kernel. Included in these laser

variable bits are:

• Local Storage Variable (master key-encryption key)

• Randomizer Seed (to supplement the true entropy fed into

the RNG)

• Program Control Data (enables/disables various features and

configures the ADSP-2141L)

• CRC of the Laser Data (to verify laser data integrity).

REV. 0

–3–

Page 4

ADSP-2141L

The Program Control Data Bits (PCDBs) include configuration

for permitted key lengths, algorithm enables, Red KEK loading.

Most of the PCDB settings may be overridden with a digitally

signed token which may be loaded into the ADSP-2141L when

it boots. These tokens are created by IRE and each is targeted to

a specific ADSP-2141L using a hash of its unique identity.

Downloadable Secure Code

The ADSP-2141L allows additional security functions to be added

to the device through a secure download feature. Up to 16K

words of code may be downloaded into internal memory within

the DSP and this code can be given the security privileges of the

CGX kernel firmware. All downloaded firmware is authenticated

with a digital signature and verified with an on-chip public key.

Additional functions could include new encryption, hash or

public key algorithms such as IDEA, RC-4,

RIPEMD, elliptic

curve, or any other application that needs direct control over the

protected cryptographic hardware.

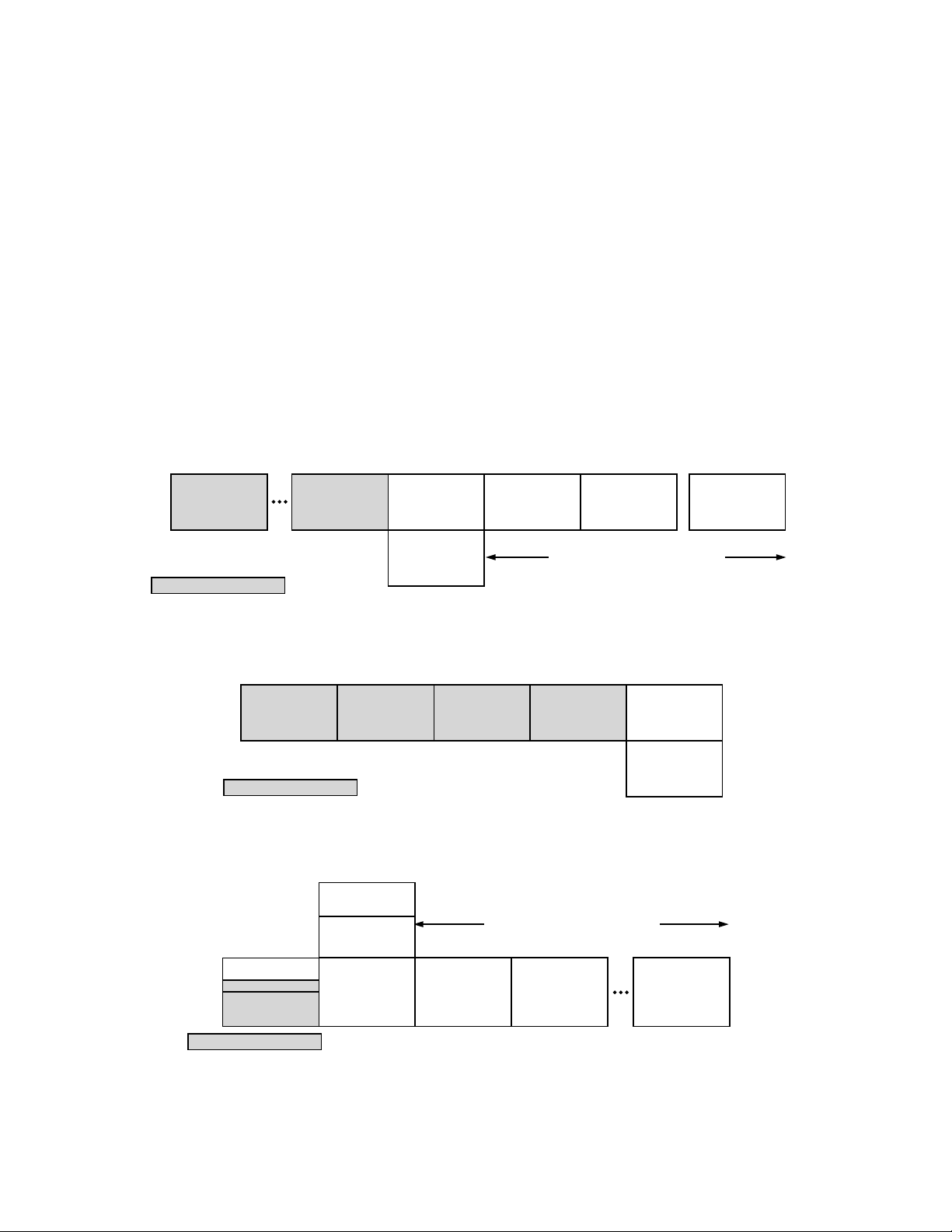

0x3FFF

0x2000

PMOVLAYL = LS NIBBLE OF PMOVLAY

PMOVLAYH = MS 3 NIBBLES OF PMOVLAY

8K KERNEL TOP

KERNEL MODE

(PMOVLAYL = C)

(PMOVLAYH = 000)

SHADED = KERNEL SPACE

8K KERNEL BASE

KERNEL MODE

(PMOVLAYL = F)

(PMOVLAYH = 000)

0x1FFF

0x0000

8K INTERNAL

PAGE

(PMOVLAYL = 0)

(PMOVLAYH = 000)

8K INTERNAL

(COMMON BANK)

ARCHITECTURE OVERVIEW

This section provides an architecture-level description of the

unique function blocks within the ADSP-2141L.

Memory Map

The ADSP-2141L memory map is very similar to that of the

ADSP-2183 DSP, except that it includes significantly more offchip memory addressing, and has additional crypto registers

which are accessible to the user.

DSP Core

The DSP core is architecturally identical to the ADSP-218x

with a few exceptions.

• The memory map includes additional external memory

addressing through the PMOVLAY and DMOVLAY mechanisms. For more information, see the Memory Map section.

• Additional memory-mapped crypto registers are available in

the kernel data RAM space.

• The PF7/INT_H flag pin may be reassigned to be the host

interrupt output.

8K EXTERNAL

PAGE = 0

(PMOVLAYL = 1)

(PMOVLAYH = 000)

8K EXTERNAL

PAGE 1

(PMOVLAYL = 2)

(PMOVLAYH = 000)

UP TO 64 MEGAWORDS

EXTERNAL PROGRAM MEMORY

(PMOVLAYL ALTERNATES 2, 1, 2, 1...)

8K KERNEL

(PMOVLAYL = 2)

(PMOVLAYH = FFF)

PAGE 8191

Figure 1. Program Memory (MMAP = 0)

0x3FFF

0x2000

PMOVLAYL = LS NIBBLE OF PMOVLAY

PMOVLAYH = MS 3 NIBBLES OF PMOVLAY

8K KERNEL TOP

KERNEL MODE

(PMOVLAYL = C)

(PMOVLAYH = 000)

SHADED = KERNEL SPACE

(PMOVLAYH = 000)

Figure 2. Program Memory (MMAP = 1)

0x3FFF

MEMORY-MAPPED

0x3FE0

0x3FDF

0x1FFF

MEMORY-MAPPED

0x1800

0x17FF

0x1000

0x0FFF

0x0000

4K KERNEL RAM

(DMOVLAY = 000F)

SHADED = KERNEL SPACE

0x2000

REGISTERS

PROTECTED

KERNEL MODE

REGISTERS

8160 WORDS

INTERNAL

8K INTERNAL

(DMOVLAYL = 0)

(DMOVLAYH = 000)

8K KERNEL

KERNEL MODE

(PMOVLAYL = D)

32

8K KERNEL

KERNEL MODE

(PMOVLAYL = E)

(PMOVLAYH = 000)

(DMOVLAYL ALTERNATES 2, 1, 2, 1...)

8K EXTERNAL

PAGE = 0

(DMOVLAYL = 1)

(DMOVLAYH = 000)

8K KERNEL

KERNEL MODE

(PMOVLAYL = F)

(PMOVLAYH = 000)

0x1FFF

0x0000

UP TO 64 MEGAWORDS

EXTERNAL DATA MEMORY

8K EXTERNAL

PAGE 1

(DMOVLAYL = 2)

(DMOVLAYH = 000)

8K INTERNAL

(PMOVLAYL = 0)

(PMOVLAYH = 000)

8K EXTERNAL

8K KERNEL

PAGE 8191

(DMOVLAYL = 2)

(DMOVLAYH = FFF)

Figure 3. Data Memory

–4–

REV. 0

Page 5

ADSP-2141L

• IRQ2 now can include interrupt sources from the crypto

subsystem, depending on interrupt mask registers.

• A new read register has been added to indicate the state of

interrupt enable and interrupt masks.

• The kernel mode control subsystem has been added to supervise the protected mode of operation of the DSP core.

• Internal RAM protection logic has been added to allow the

kernel to seize increments of 1K word of internal PRAM and

DRAM.

• Bus mode configuration (218x vs. PCI) pins have been added.

• 32K words of kernel program ROM have been added to the

DSP memory space. (See the Memory Map section.)

Kernel Mode Control

The kernel mode control subsystem provides the following

functions which serve to enforce the security integrity of the

ADSP-2141L:

• Provide a means to securely enter the kernel mode.

• Provide a means to properly exit the kernel mode.

• Prevent user mode access to protected memory and register

locations.

• Manage interrupts during kernel mode executions.

• Manage the reset function to ensure that sensitive variables

in DSP registers are erased.

Most of the kernel mode control functions are implemented in

the hardware of the ADSP-2141L and are not directly visible to

nonkernel applications (user mode). Any attempt by a user

mode application program running on the DSP to access a

kernel space addresses (PRAM 0x2001 – 0x3FFF, PMOVLAY

000C – 000F; or DRAM 0x0000 – 0x17FF, DMOVLAY 000F)

results in an immediate chip reset and all sensitive registers and

memory locations are erased. Kernel mode may only be entered

via a call, jump or increment to address 0x2000 with PMOVLAY

set to 0x000F. Once in kernel mode, any branch to nonkernel

space program memory causes the DSP to return to user mode.

(Note: For security reasons when in kernel mode, the DSP does

not respond to Emulator bus requests.)

The kernel mode can be interrupted during execution; however,

during certain periods where sensitive data is being moved, all

interrupts are disabled. Within the interrupt service routine,

another call to the kernel (CGX call) may be made if desired,

although there are limitations on which CGX commands may

preempt another. (For information, see the ADSP-2141L CGX

Interface Programmer’s Guide http://www.ire-ma.com/proddoc.htm.)

Only one level of kernel mode nesting is permitted. An interrupt

to a user mode vector location while in nested kernel mode will

also trigger the violation reset logic.

Once the interrupt service routine is finished, the return-frominterrupt must return control back to the kernel at the address/

overlay that was originally interrupted, otherwise the protection

logic will issue a chip reset.

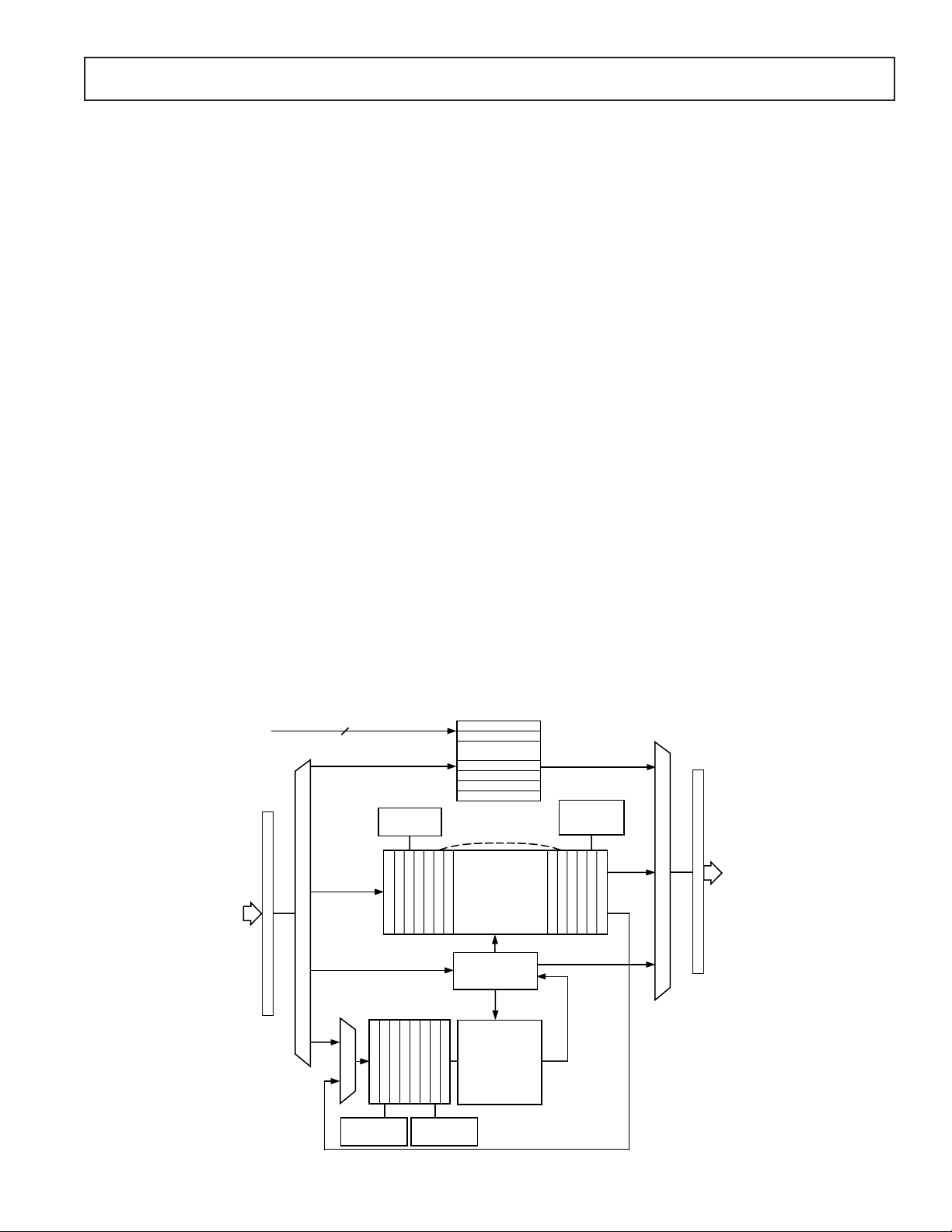

Hash and Encrypt Block Overview

The encrypt block is tightly coupled to the hash block in the

ADSP-2141L and therefore the two are discussed together.

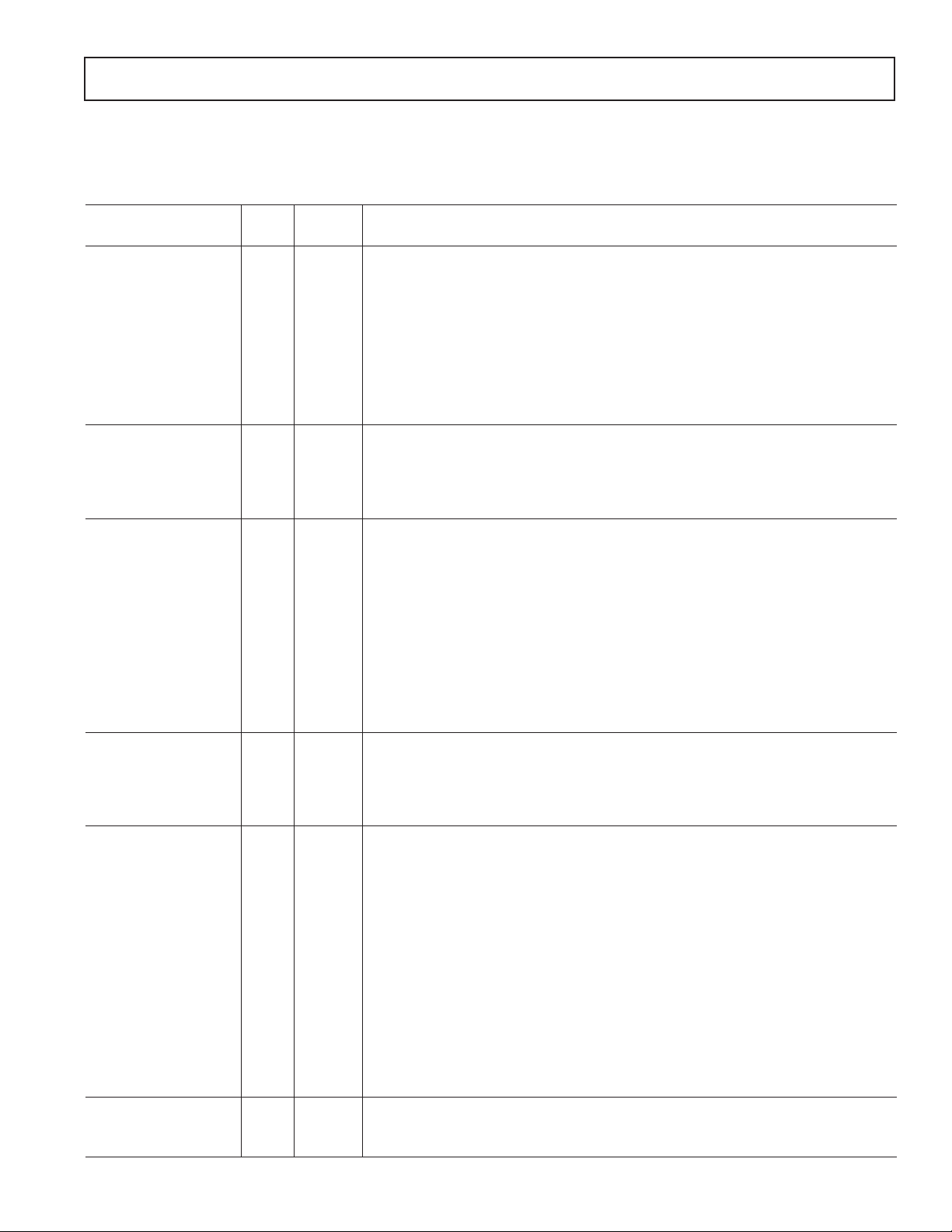

Refer to Figure 4, Hash/Encrypt Functional Block Diagram, for

the following description.

The algorithms implemented in the combined hash and encryption block are: DES, Triple DES, MD-5 and SHA-1. Data can

be transferred to and from the module once to perform both

hashing and encryption on the same data stream. The DES

encrypt/decrypt operations are highly paralleled and pipelined,

and execute full 16-round DES in only four clock cycles. The

internal data flow and buffering allows parallel execution of

hashing and encryption where possible, and allows processing of

data concurrently with I/O of previous and subsequent blocks.

REV. 0

REGISTER

ADDRESS

DSP

OR

PCI

16-/32-BIT

INPUT

BUS

7

WR

INSERTION

WRITE

CONTEXT

512-BIT

MUTABLE BIT

PROCESSING

PAD

FIFO

PAD

INSERTION

512-BIT

FIFO

ENCRYPT/

DECRYPT

BLOCK

CONTEXT

STORAGE (0/1)

HASH

BLOCK

(ENCRYPT-THEN-HASH)

(DECRYPT-THEN-HASH)

RD

PAD

CONSUME

AND VERIFY

READ

CONTEXT

HASH

DIGEST

Figure 4. Hash/Encrypt Functional Block Diagram

–5–

16-/32-BIT

OUTPUT

BUS

DSP

OR

PCI

Page 6

ADSP-2141L

Context switching is optimized to minimize the overhead of

changing cryptographic keys to near zero.

The software interface to the module consists of a set of

memory-mapped registers, all of which are visible to the DSP and

most of which can be enabled for host access via the PCI bus. A

set of five, 16-bit registers define the operation to be performed,

the length of the data buffer to be processed, in bytes, the offset

between the start of hashing and encryption (or vice versa), and

the padding operation. If the data length is unknown at the time

the encrypt/decrypt operation is started, the data length register

may be set to zero, which specifies special handling. In this case,

data may be passed to the hash/encrypt block indefinitely until

the end of data is encountered. At that time, the operation is

terminated by writing a new control word to the hash/encrypt

control register (either to process the next packet or to invoke

the idle state if there is no further work to do). This will close

out the processing for the packet, including the addition of the

selected crypto padding.

A set of seven status registers provides information on when a

new operation can be started, when there is space available to

accept new data, when there is data available to be read out, and

the results from the padding operation.

Crypto Contexts

There are two sets of crypto-context registers. Each context

contains a DES or triple DES key, initialization vector, and

precomputed hashes (inner and outer) of the authentication key

for HMAC operations. The contexts also contain registers to

reload the byte count from a previous operation (which is part

of the hashing context), as well as an IV (also called salt) for

decrypting a black key, if necessary.

Once a crypto-context has been loaded and the operation

defined, data is processed by writing it to a data input FIFO. At

the I/O interface, data is always written to, or read from, the

same address. Internally, the hash and encryption functions

have separate 512-bit FIFOs, each with their own FIFO management pointers. Incoming data is automatically routed to one

or both of these FIFOs, depending on the operation in progress.

Output from the encryption block is read from the data output

FIFO. In encrypt-hash or decrypt-hash operations, the data is

also automatically passed to the hashing data input FIFO. Output

from the hash function is always read from the digest register of

the appropriate crypto-context.

The initialization vector to be used for a crypto operation can be

loaded as part of a crypto-context. When an operation is complete,

the same context will contain the resulting IV produced at the

end, which can be saved away and restored later to continue the

operation with more data.

In certain packet-based applications such as IPsec, a feature is

available that avoids the need for the control software to generate

and load random IVs for outgoing (encrypted) packets. Effectively, the IV register can be configured to be automatically

updated with new random numbers for each encrypted packet,

with almost no software intervention.

Padding

When the input data is not a multiple of eight bytes (a 64-bit

DES block), the encrypt module can be configured to automatically append pad bytes. There are several options for how the

padding is constructed, which are specified using the pad control

word of the operation description. Options include zero padding,

pad-length character padding (PKCS#7), incrementing count,

–6–

with trailing pad length and next header byte (for IPsec), or

fixed character padding. Note that for the IPsec and PKCS#7

pad protocols, there are cases where the padding not only fills

out the last 8-byte block, but also causes an additional 8-byte

block of padding to be added.

For the hash operations, padding is automatically added as

specified in the MD-5 and SHA-1 standards. When the hash

final command is issued indicating the last of the input data, the

algorithm-specified padding and data count bits are added to the

end of the hash input buffer prior to computing the hash.

Data Offsets

Certain security protocols, including IPsec, require portions of a

data packet to be hashed while the remainder of the data is both

hashed and encrypted. The ADSP-2141L supports this requirement through the OFFSET register, which allows specifying the

number of 32-bit dwords of offset between the hash and encrypt/

decrypt operations.

Black Key Loads

The cryptographic keys loaded as part of a crypto-context can

be stored off-chip in a black, or encrypted, form. If the appropriate control bit is set (HECNTL Bit 15), the DES or 3-DES key

will be decrypted immediately after it is written into the context

register. The hardware handles this decryption automatically.

The Key Encryption Key (KEK) that covers the black keys

is loaded in a dedicated write-only KEK register within the

ADSP-2141L. The IV for decrypting the black secret key is

called ‘salt’ and must be stored along with the black key (as part

of the context). Note that 3-DES CBC mode is used for protecting 3-DES black keys and single DES CBC is used for

single DES black keys.

When black keys are used, the key-decrypt operation adds a

6-cycle overhead (0.15 µs @ 40 MHz) for DES keys or 36-cycle

overhead (0.9 µs @ 40 MHz) for triple DES keys each time a

new crypto-context is loaded. (Note that if the same context is

used for more than one packet operation, the key decryption does

not need to be performed again.) Depending on the sequencing

of operations, this key decryption may in fact be hidden (from a

performance impact perspective) if other operations are underway.

This is because the black key decryption process only requires

that the DES hardware be available. For example, if the DSP is

reading the previous hash result from the output FIFO, the

black key decryption can be going on in parallel. Also note that

the data driver firmware does NOT have to wait for the key to

be decrypted before writing data to the input FIFO. The hardware automatically waits for the key to be decrypted before

beginning to process data for a given packet. So, with efficient

pipeline programming, it is possible to make the impact of black

key essentially zero.

The KEK for key decryption is loaded via the secure kernel

firmware using one of the CGX key manipulation commands.

(For more information, see the Command Summary section.)

This KEK is typically the same for all black keys, since it is usually

protecting local storage only. It is designated the DKEK in the

CGX API.

One of the laser-programmed configuration bits specifies whether

red (plaintext) keys are allowed to be loaded into the ADSP2141L from a host. If the AllowRedKeyLoad laser bit is not set,

keys may only be loaded in their black form. This is useful in

systems where export restrictions limit the key length that may

be used or where the external storage environment is untrusted.

REV. 0

Page 7

ADSP-2141L

If the AllowRedKeyLoad bit is set, keys may be loaded either in

their black form, or in the red or unencrypted form. Note that

the laser configuration bit may be overridden with a signed

enabler token. (For more information, see the Laser Variable

Storage section.)

Depending on the definition of the security module boundary in

a given application, FIPS 140-1 may require the use of black

keys to protect key material. In other words, if the security

boundary does not enclose the database where keys are stored,

those keys must be protected from compromise. Black key is a

satisfactory way to meet this FIPS requirement.

Random Number Generator (RNG) Block

The random number generator is designed to provide highly

random, nondeterministic binary numbers at a high delivery rate

with little software intervention. The random numbers are accessible to the kernel firmware in a 16-bit register that may be read

by the DSP in kernel mode. Once the register is read, the RNG

immediately generates a new 16-bit value that is available within

12 microseconds.

All application-level access to random numbers should occur

through the Kernels CGX_RANDOM command (see the

Command Summary section).

The random number generator is designed using a “shot noise”

true entropy source which is sampled by the master 40 MHz

clock of the ADSP-2141L. The entropy source then feeds a

complex nonlinear combinatorial circuit that produces the final

RNG output based on the interaction of the entropy source and

the 40 MHz system clock. Over 200 stages of Linear Feedback

Shift Register (LFSR) are incorporated into the RNG design.

In order to facilitate FIPS 140-1 compliance, an option may be

selected during CGX kernel initialization to enable an ANSI

X9.17 Annex C post-randomizer to be applied to the output of

the RNG. This randomizer applies the DES ECB algorithm

multiple times to further disperse and whiten the random source.

Although this is not necessary to ensure the quality of the random

numbers, it meets the criteria for a NIST-approved random number generation algorithm.

Public Key Accelerator (PKAC)

The public key arithmetic coprocessor (otherwise known as a

BigNum processor) is designed to support long vector calculations of the kind needed to perform RSA, Diffie-Hellman and

Elliptic Curve operations.

The PKAC can perform multiplication, squaring, addition and

subtraction on arbitrary length bit vectors. The CGX software is

responsible for setting the address register for the operands and

result, as well as specifying the length and operation type. Once

the operation type field is written, the processor polls the operation complete status while the calculation is carried out.

The PKAC utilizes the protected kernel RAM for input, output

and intermediate variable storage. It may only be accessed from

the secure kernel mode. Since public key computations typically

take many milliseconds to complete, they may be preempted

using a DSP interrupt.

Most application interaction with the public key accelerator will

occur via the CGX software interface (see the Command Interface section). Both high level public key operations such as RSA

Sign or Create Diffie-Hellman Key, as well as primitive operations

such as Multiply Vector, Add Long Vector, etc., are presented

via the CGX interface.

PCI/Cardbus Interface

The ADSP-2141L appears as a target on the PCI Bus as a single

contiguous memory space of 128k bytes. In this memory space,

the host can access the following:

• The unprotected internal crypto registers of the ADSP-2141L

• IDMA access to the DSP’s internal program memory (PM)

and data memory (DM)

• Paged access to external memory connected to the

ADSP-2141L

• The Kernel RAM (KRAM) if it has been unprotected by an

extended mode program

As a PCI Master, the ADSP-2141L can transfer data between:

• The unprotected internal crypto registers and FIFOs of the

ADSP-2141L and PCI Host memory

• External memory and PCI Host memory

A 32-bit DMA engine within the ADSP-2141L facilitates these

transfers and permits full PCI bandwidth use.

Serial EEPROM Interface

The serial EEPROM interface allows the ADSP-2141L to automatically read the PCI configuration parameters at chip power-up.

IRE can provide the data content for the EEPROM to properly

set the chip device vendor ID, type and properties for full compliance with the PCI Plug and Play standards.

In addition to being used for storage of host bus parameters, any

extra space in the EEPROM may be accessed by the DSP, either

in user mode or kernel mode. Support for this function is not

included in the standard CGX command set. Refer to the

ADSP-2141 User’s Manual for the information on the data

contents of the EEPROM. Refer to http://www.analog.com/

industry/dsp/ire.html.

REV. 0

Table I. Interrupt Sources

Internal Interrupt Sources External Interrupt Sources

Interrupt Notes Interrupt Notes

Reset or Power-Up (PUCR = 1) IRQ2 Edge- or Level-Sensitive

Power-Down IRQL1 Level-Sensitive

SPORT0 Transmit IRQL0 Level-Sensitive

SPORT0 Receive IRQE Edge-Sensitive

BDMA Interrupt IRQ1 Edge- or Level-Sensitive

SPORT1 Transmit Mixed with IRQ1 IRQ0 Edge- or Level-Sensitive

SPORT1 Receive Mixed with IRQ0

Timer

–7–

Page 8

ADSP-2141L

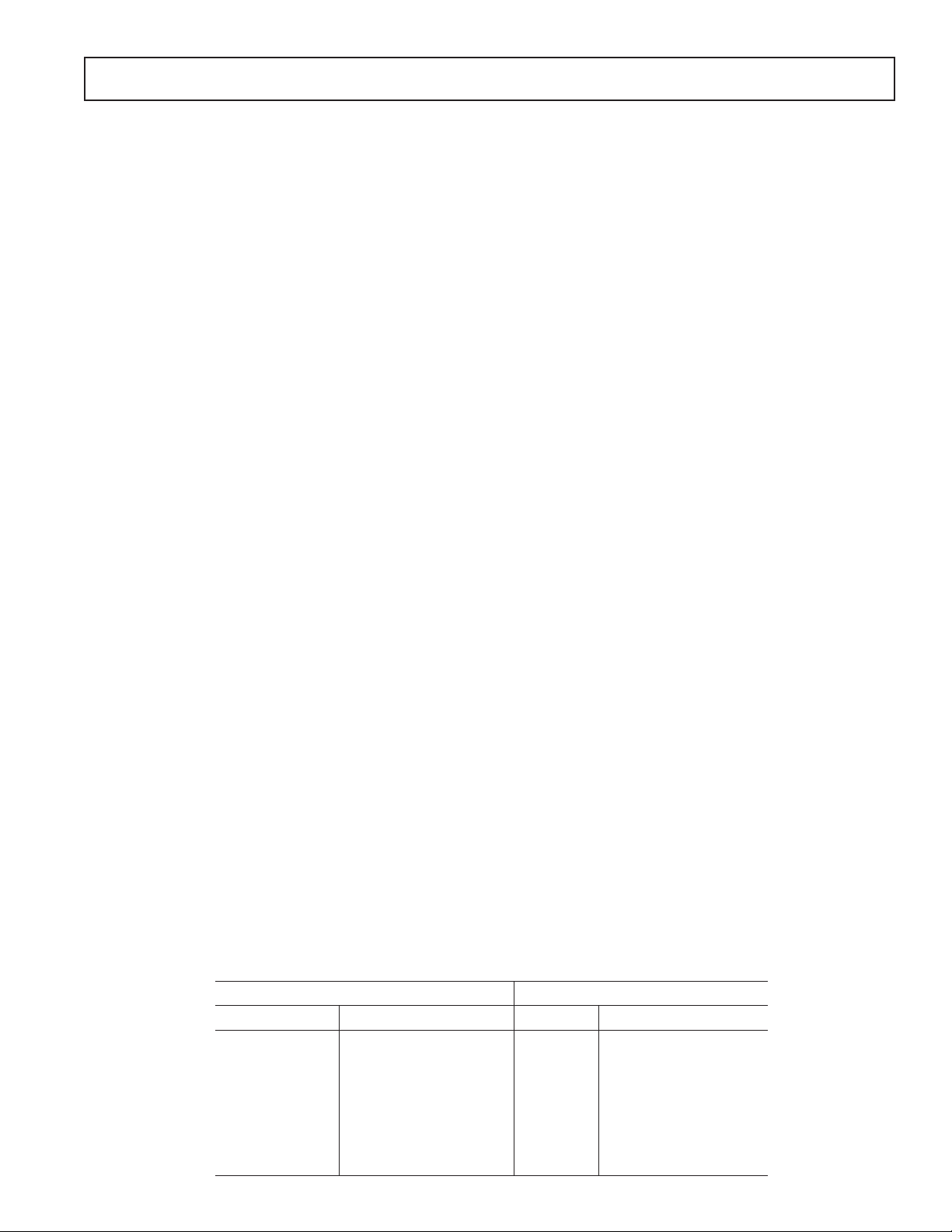

Interrupt Controller

The DSP core of the ADSP-2141L provides a powerful set of

interrupt sources. A total of 14 interrupt sources are available,

although two pairs are multiplexed, yielding 12 simultaneous

sources. Refer to Table I.

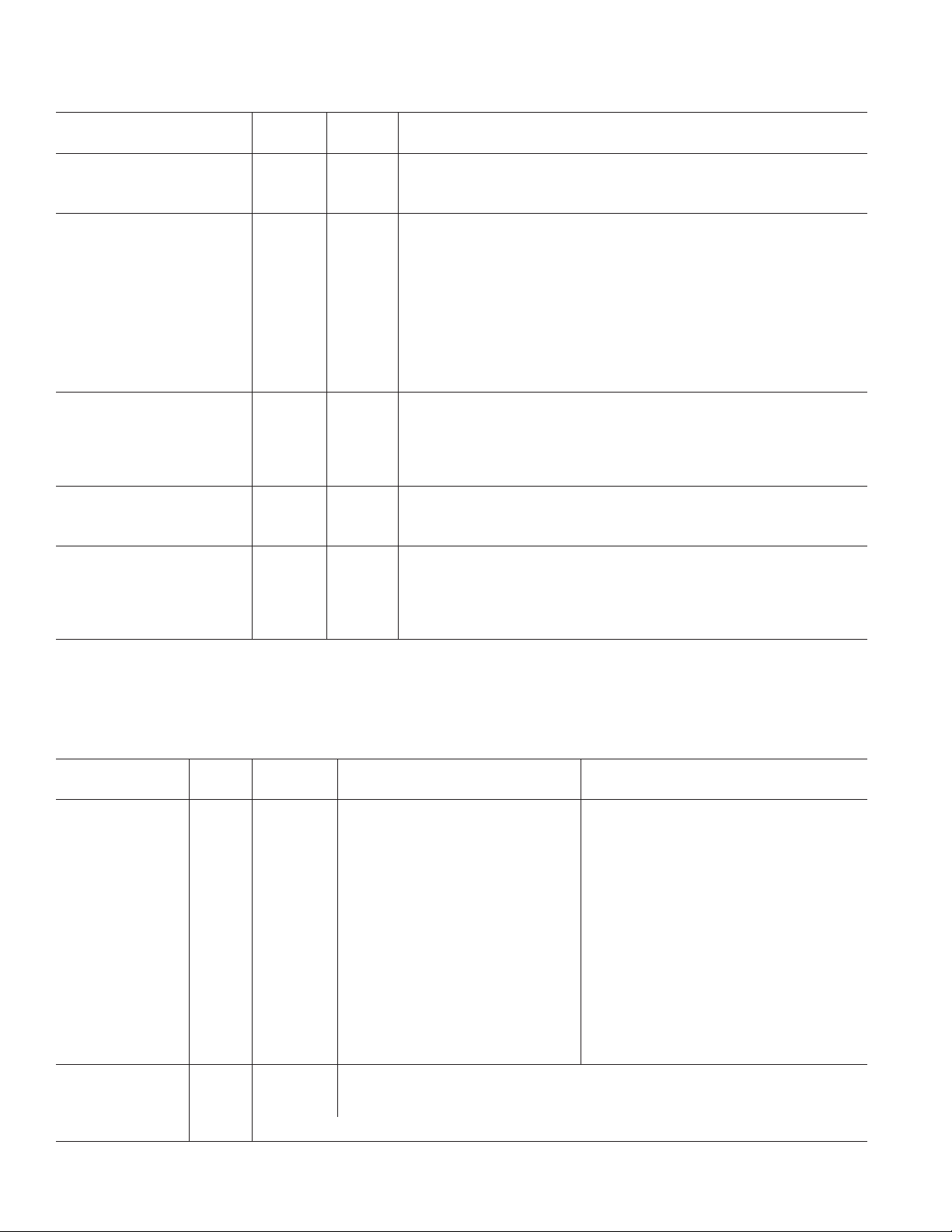

The ADSP-2141L enhances the existing interrupt controller

within the ADSP-218x DSP Core with some additional functions related to the crypto functional blocks and the external

host bus interfaces. Two additional interrupt controller subsystems have been added to the basic interrupt controller as

shown in Figure 5.

The DSP interrupt controller allows programming between one

and nine sources for the IRQ2 interrupt to the DSP. The

DIMASK register provides the mask to select which interrupt

source is enabled. A pair of status registers, DUMSTAT and

DMSTAT, allow the DSP firmware to read the status of any

interrupt source either before or after the mask is applied.

The host interrupt controller allows programming between one

and five sources for the PF7/INT_H interrupt output signal

(which may be connected to the interrupt input of the host

system). The HMASK register provides the mask to select which

interrupt source is enabled. A pair of status registers, HUMSTAT

and HMSTAT, allow the host firmware to read the status of any

interrupt source either before or after the mask is applied.

Laser Variable Storage

The laser variables are configured through 256 Fuses in the

ADSP-2141L, which are programmed during IC manufacture.

Each ADSP-2141L produced is programmed with a unique set

of Laser Variables.

• Local Storage Variable (LSV—the Master Key-Encryption-Key)

• Internal Seed Variable

• 48-Bit Program Control Data (enables/disables various features and configures the ADSP-2141L)

• CRC of the Laser Data (to verify integrity of the laser bits)

The LSV is a unique triple DES master key-encrypting key that

allows the ADSP-2141L to securely store data (primarily other keys)

off-chip for later reloading. This is necessary if more storage space

is needed than is available with on-chip RAM, or if keys need to

be saved and restored after a power outage. Each ADSP-2141L

produced is programmed with a unique, randomly generated

local storage variable.

The internal seed variable is used to randomly initialize the

RNG circuits before the entropy is mixed in. Each ADSP-2141L

produced is programmed with a unique, randomly generated

internal seed variable which is loaded into the RNG at chip boot

time and cannot ever be read by software.

The 48 Program Control Data Bits (PCDBs) include configuration for permitted key lengths, algorithm enables, red KEK

loading, internal IC pulse timing characteristics. The PCDBs

provide configuration data that falls into three categories:

• Internal IC pulse-timing characteristics

• ADSP-2141L hardware version number field

• ADSP-2141L feature enables

The first two categories consist of data that cannot be altered

once the ADSP-2141L has been fabricated.

The feature enables can be overridden using a factory token

enabler which may be passed to the CGX kernel as part of the

CGX_INIT command. This token is digitally signed with an

IRE private key and verified internal to the ADSP-2141L with

its public key. The CGX_INIT command is documented in the

ADSP-2141 CGX Interface Programmer’s Guide (available from

http://www.ire-ma.com/proddoc.htm).

DSP

INTERNAL

INTERRUPTS

RESET

POWER DOWN

SPORT0 Tx

SPORT0 Rx

BDMA INT

TIMER INT

SPORT1 Tx

SPORT1 Rx

EXTERNAL

INTERRUPTS

IRQE

IRQL0

IRQL1

IRQ0

IRQ1

IRQ2

SUBSYSTEM BOUNDRY

ADSP-2183

INTERRUPT

CONTROLLER

ICNTL

IMASK

IFC

CRYPTO INTERRUPT

IRQ2

DSP INTERRUPT CONTROLLER

DICFG

DICLR

DIFRC

DIMASK

HOST

INTERRUPT

H/E CONTEXT1

DONE

H/E CONTEXT0

DONE

HOST

WROTE CMD

DMA xFER

DONE

DMA xFER

QUEUED

EXT MEM

CONFLICT

DSP MASKED STATUS REGISTER

HASH/ENC

ERROR

DSP UNMASKED STATUS REGISTER

IRQ2

HOST INTERRUPT CONTROLLER

DSP

INTERRUPT

H/E CONTEXT1

DONE

H/E CONTEXT0

DONE

DSP

WROTE

CMD

HASH/ENC

ERROR

Figure 5. Interrupt Controller Block Diagram

–8–

HICFG

HICLR

HIFRC

HIMASK

HOST UNMASKED STATUS REGISTER

HOST MASKED STATUS REGISTER

INTH

TO HOST

REV. 0

Page 9

ADSP-2141L

PIN FUNCTIONS

I/O Descriptions

This section describes the physical I/O hardware on the ADSP-2141L.

PIN FUNCTION DESCRIPTIONS–I/O Hardware

# of Input/

Pin Name Pins Output Function

External Memory Bus

Address [25:0] 26 O Address Output Pins for Program, Data, Byte and I/O Spaces (13 Bits 2183, 13 Bits

from Overlay Register) Note: A0 not used for 32-bit memory.

Data [31:0] 32 I/O Data I/O Pins for Program and Data Memory Spaces

D31:0 are used for wide-bus data memory.

D23:0 are used for DSP Program RAM.

D23:8 are used for I/O Space.

D23:8 are used for DSP Data RAM.

D15:8 are used for byte memory.

D23:16 are also used as Byte Space Addresses

Interrupts

IRQ2 1 I Edge- or Level-Sensitive Interrupt Request

IRQL0 1 I Level-Sensitive Interrupt Requests

IRQL1 1 I Level-Sensitive Interrupt Requests

IRQE 1 I Edge-Sensitive Interrupt Request

Bus Signals

BR 1 I Bus Request Input

BG 1 O Bus Grant Output

BGH 1 O Bus Grant Hung Output

PMS 1 O Program Memory Select Output

DMSL 1 O Data Memory Select Output (Lower 16 Bits for 32-Bit DM)

DMSH 1 O Upper Memory Select Output (Upper 16 Bits for 32-Bit DM, Not Used for 16-Bit DM)

BMS 1 O Byte Memory Select Output

IOMS 1 O I/O Space Memory Select Output

CMS 1 O Combined Memory Select Output (PMS, DMS*, IOMS, BMS)

RD 1 O Memory Read Enable Output

WR 1 O Memory Write Enable Output

Miscellaneous

MMAP 1 I Memory Map Select Input (1 = Overlay External at 0x0000)

BMODE 1 I Boot Option Control Input (0 = BDMA, 1 = IDMA)

CLKIN, XTAL 2 I Clock or Quartz Crystal Input (1/2 of the ADSP-2141 Clock)

CLKOUT 1 O Processor Clock Output

Serial Ports

SPORT0

SCLK0 1 I/O Serial Port 0 Clock

DR0 1 I Serial Port 0 Receive Data Input

RFS0 1 I/O Serial Port 0 Receive Frame Sync

DT0 1 O Serial Port 0 Transmit Data Output

TFS0 1 I/O Serial Port 0 Transmit Frame Sync

SPORT1

Port Configuration

(System Control Reg) –> 1 = Serial Port 0 = Other

SCLK1 1 I/O Serial Port 1 Clock

DR1 1 I Serial Port 1 Receive Data Input Flag In

RFS1 1 I/O Serial Port 1 Receive Frame Sync IRQ0

DT1 1 O Serial Port 1 Transmit Data Output Flag Out

TFS1 1 I/O Serial Port 1 Transmit Frame Sync IRQ1

Power-Down

PWD 1 I Power-Down Initiate Control

PWDACK 1 O Power-Down Acknowledge

REV. 0

–9–

Page 10

ADSP-2141L

# of Input/

Pin Name Pins Output Function

Flags

PF6:0 7 I/O Programmable I/O Pins

PF7/INT_H 1 I/O Programmable I/O Pin–or–Interrupt Output (Host Mode)

Emulator

EE 1 (Emulator Only)

EBR 1 (Emulator Only)

EBG 1 (Emulator Only)

ERESET 1 (Emulator Only)

EMS 1 (Emulator Only)

EINT 1 (Emulator Only)

ECLK 1 (Emulator Only)

ELIN 1 (Emulator Only)

ELOUT 1 (Emulator Only)

Serial EEPROM Interface

EE_DI 1 O Serial EEPROM Data In

EE_DO 1 I Serial EEPROM Data Out

EE_CS 1 O Serial EEPROM Chip Select

EE_SK 1 O Serial EEPROM Clock

Bus Select

BUS_MODE 1 I Processor Bus Select

BUS_SEL 1 I Bus Select

PCI Bus (Dedicated Pins)

PCI_CLK 1 I PCI Clock

PCI_PAR 1 I/O PCI Parity Bit

PCI_IRDY 1 I/O PCI Initiator Ready

PCI_STOP 1 I/O PCI Abort Transfer

*When DMS is enabled for generation of CMS, the CMS is activated for DSP access to external memory only, NOT for DMA controller accesses.

Bus Mode Descriptions

The Pin Function Descriptions, Bus Mode table, shows the multiplexed pins in 2183 and PCI mode. For more information on the

PCI pins MPLX1–MPLX12, see the Pin Functions Description–PCI Mode Multiplex Bus table on the following page.

PIN FUNCTION DESCRIPTIONS—Bus Mode

# of Input/ 2183 Mode PCI Mode

Bus Mode Pins Output (bus_mode = 0, bus_sel = 0) (bus_mode = 1, bus_sel = 0)

MPLX_RESET 1 I RESET_1 Pci_rst

MPLX1 1 I/O Pci_cbe3

MPLX2 1 I/O Pci_cbe2

MPLX3 1 I/O Pci_cbe1

MPLX4 1 I/O Pci_cbe0

MPLX5 1 I IRD Pci_idsel

MPLX6 1 I IWR Pci_gnt

MPLX7 1 I/O IS Pci_frame

MPLX8 1 I/O IAL Pci_devsel

MPLX9 1 I/O IACK Pci_trdy

MPLX10 1 I/O FL0 Pci_perr

MPLX11 1 I/O FL1 Pci_serr

MPLX12 1 O FL2 Pci_req

MPLX_BUS[31:0] 32 I/O IAD15:0 Pci_ad15:0

N/C 31:16 Pci_ad31:16

Power

GND 24 – Ground Pins

VDD 22 – Power Supply Pins (3.3 V)

Total: 208 Includes the pins from this table and the I/O Hardware Pin Function Description table.

–10–

REV. 0

Page 11

ADSP-2141L

IDMA Mode Multiplex Bus Pin Definition

IDMA Port (218x Mode)

PIN FUNCTION DESCRIPTIONS—IDMA Mode Multiplex Bus

Pin Name IDMA Name Pins I/O Description

MPLX5 IRD 1 I IDMA Port Read Input

MPLX6 IWR 1 I IDMA Port Write Input

MPLX7 IS 1 I IDMA Port Select

MPLX8 IAL 1 I IDMA Port Address Latch

MPLX9 IACK 1 O IDMA Port Access Ready Acknowledge

MPLX10 FL0 1 O Output Flags

MPLX11 FL1 1 O Output Flags

MPLX12 FL2 1 O Output Flags

MPLX_BUS IAD 16 I/O IDMA Data I/O

PCI Port

PIN FUNCTION DESCRIPTIONS—PCI Mode Multiplex Bus

Pin Name PCI Name Pins I/O Description

MPLX1 Pci_cbe3 1 I/O Bus Command / Byte Enable 3

MPLX2 Pci_cbe2 1 I/O Bus Command / Byte Enable 2

MPLX3 Pci_cbe1 1 I/O Bus Command / Byte Enable 1

MPLX4 Pci_cbe0 1 I/O Bus Command / Byte Enable 0

MPLX5 Pci_idsel 1 I Initialization Device Select

MPLX6 Pci_gnt 1 I Bus Grant

MPLX7 Pci_frame 1 I/O Cycle Frame

MPLX8 Pci_devsel 1 I/O Device Select

MPLX9 Pci_trdy 1 I/O Target Ready

MPLX10 Pci_perr 1 I/O Parity Error

MPLX11 Pci_serr 1 I/O System Error

MPLX12 Pci_req 1 O PCI Bus Request

MPLX_BUS Pci_ad15:0

Pci_ad31:16 32 I/O PCI Address/Data Bus

PF7/INT_H Pci_intA 1 O PCI Interrupt A Request

SYSTEM INTERFACE

The ADSP-2141L may be integrated into a wide variety of systems, including those that already have a microprocessor and

those that will use the ADSP-2141L as the main processor. The

device can be configured into one of two Host Bus modes:

IDMA or PCI.

IDMA Bus Mode

The IDMA bus mode operates the same as in a native ADSP218x device, as described in this section.

The IDMA port provides an efficient means of communication

between a host system and the ADSP-2141L. The port is used

to access the on-chip program memory and data memory of the

DSP with only one DSP cycle per word overhead. The IDMA

port cannot, however, be used to write to the DSP’s memorymapped control registers.

The IDMA port has a 16-bit multiplexed address and data bus,

and supports reading or writing 16-bit data (DM) or 24-bit

program memory (PM). The IDMA port is completely asynchronous and can be written to while the ADSP-2141L is operating at full speed.

The DSP memory address is latched and then automatically

incremented after each IDMA transaction. An external device can

therefore access a block of sequentially addressed memory by

REV. 0

–11–

specifying only the starting address of the block. This increases

throughput as the address does not have to be sent for each

memory access.

The IDMA port access occurs in two phases. The first is the

IDMA address latch cycle. When the acknowledge is asserted, a

14-bit address and 1-bit destination type can be driven onto the

bus by an external device. The address specifies an on-chip

memory location; the destination type specifies whether it is a

DM or PM access. The falling edge of the address latch signal

latches this value to the IDMAA register.

Once the address is stored, data can either be read from or

written to the ADSP-2141L’s on-chip memory. Asserting the

select line (IS) and the appropriate read or write line (IRD and

IWR respectively) signals the ADSP-2141L that a particular

transaction is required. In either case, there is a one-processorcycle delay for synchronization. The memory access consumes

an additional processor cycle.

Once an access has occurred, the latched address is automatically incremented and another access can occur.

Through the IDMAA register, the ADSP-2141L can also

specify the starting address and data format for DMA operation.

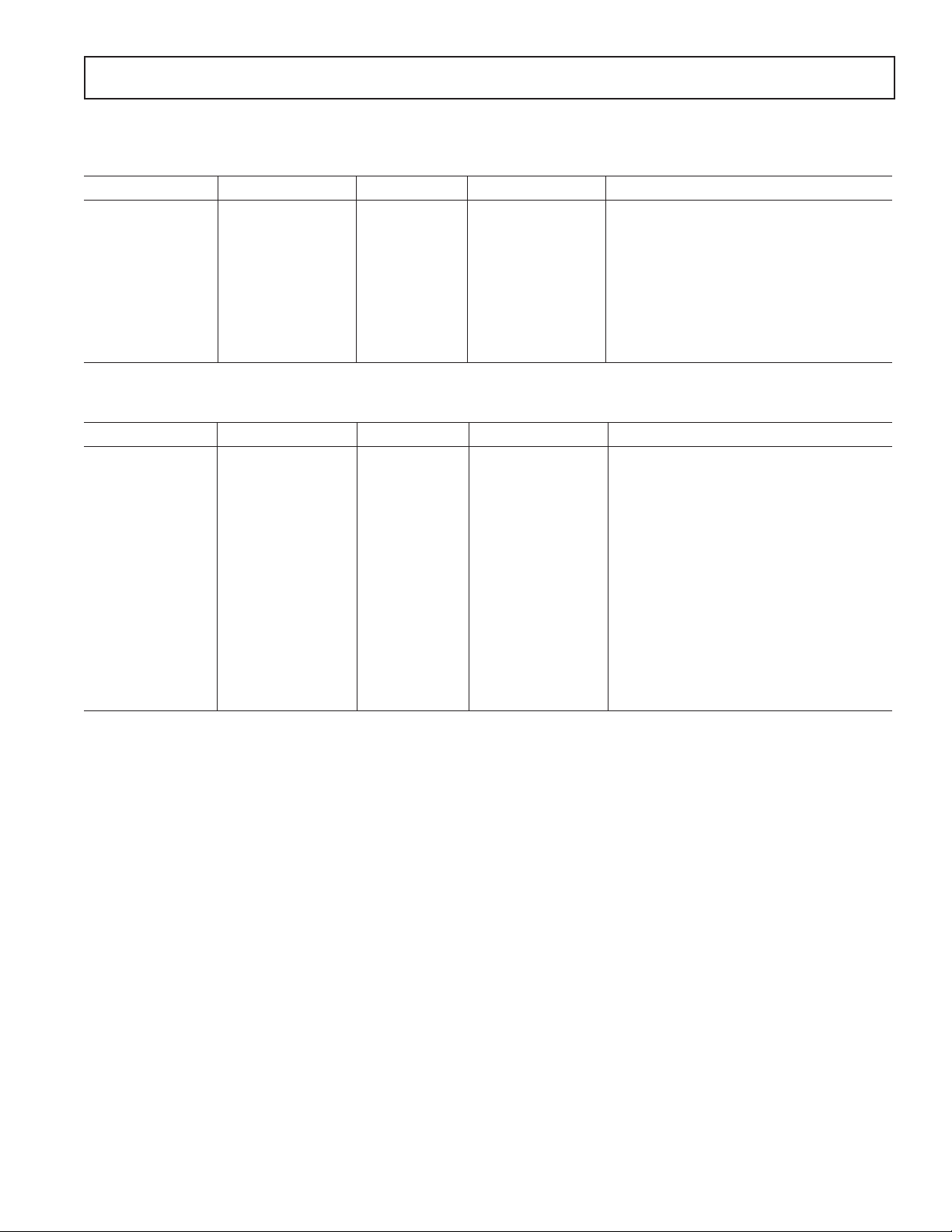

Figure 6 illustrates a typical system configuration for the

IDMA mode.

Page 12

ADSP-2141L

1/2X CLOCK

OR

CRYSTAL

INTERRUPT

SOURCES

SERIAL

DEVICE

SERIAL

DEVICE

SYSTEM

INTERFACE

OR

mCONTROLLER

NC

NC

CLKOUT

CLKIN

XTAL

FL0–2

PF0–7

IRQ2

IRQE

IRQL0

IRQL1

SCLK1

RFS1 OR IRQ0

TFS1 OR IRQ1

DT1 OR FO

DR1 OR FI

SCLK0

RFS0

TFS0

DT0

DR0

IDMA PORT

IRD

IWR

IS

IAL

IACK

16

IAD15–0

16

MPLX31–16

RESET

PCI_CLK

PCI_PAR

PCI_IRDY

PCI_STOP

ADSP-2141

SPORT1

SPORT0

ADDR25–0

DATA 31–0

BMS

IOMS

PMS

CMS

(OPTIONAL)

DMSH

DMSL

BR

BG

BGH

PWD

PWDACK

BUS_MODE

BUS_SEL

MMAP

BMODE

EXTERNAL

MEMORY BUS

26

32

VDD

VDD OR GND

A13–0

D23–16

D15–8

A10–0

D23–8

A25–0

D23–0

A25–0*

D15–0

D31–16

BUS

ARBITER

A0-A21

DATA

CS

ADDR

DATA

CS

ADDR

DATA

8K 3 24

PM SEGMENTS

UP TO 32M 3 32

BYTE

MEMORY

(BOOT

LOADER)

16-BIT

I/O SPACE

2048

LOCATIONS

PROGRAM

OVERLAY

MEMORY

8192

DATA

OVERLAY

MEMORY

8192

8K 3 16

SEGMENTS

EEPROM

EE_DI

EE_DO

EE_CS

EE_SK

*ADDR0 FROM THE ADSP-2141

IS NO CONNECT FOR 32-BIT MEMORY.

NC

ADSP-2141 ADDR1 IS WIRED TO RAM A0.

Figure 6. ADSP-2141L IDMA System Configuration

–12–

REV. 0

Page 13

PCI Bus Mode

Figure 7 illustrates a typical system configuration for the

PCI mode.

ADSP-2141

1/2X CLOCK

OR

CRYSTAL

INTERRUPT

SOURCES

SERIAL

DEVICE

SERIAL

DEVICE

PCI

BUS

INTA

CLKOUT

CLKIN

XTAL

PF0–6

IRQ2

IRQE

IRQL0

IRQL1

SCLK1

RFS1 OR IRQ0

TFS1 OR IRQ1

DT1 OR FO

DR1 OR FI

SCLK0

RFS0

TFS0

DT0

DR0

PCI PORT

4

PCI_CBE3-0

PCI_IDSEL

PCI_REQ

PCI_GNT

PCI_FRAME

PCI_DEVSEL

PCI_TRDY

PCI_PERR

PCI_SERR

32

PCI_AD31–0

PCI_RST

PCI_CLK

PCI_PAR

PCI_IRDY

PCI_STOP

PF7/INT_H

SPORT1

SPORT0

ADDR25-0

DATA 31-0

IOMS

(OPTIONAL)

DMSH

DMSL

BGH

PWD

PWDACK

BUS_MODE

BUS_SEL

MMAP

BMODE

BMS

PMS

CMS

BR

BG

EXTERNAL

MEMORY BUS

26

32

VDD

VDD OR GND

A13–0

D23–8

D23–0

D15–0

D31–16

A0-A21

DATA

CS

ADDR

DATA

CS

ADDR

DATA

8K 3 24

PM SEGMENTS

BYTE

MEMORY

(BOOT

LOADER)

16-BIT

I/O SPACE

2048

LOCATIONS

PROGRAM

OVERLAY

MEMORY

8192

OVERLAY

MEMORY

D23–16

D15–8

A10–0

A25–0

A25–0*

SEGMENTS

UP TO 32M 3 32

BUS

ARBITER

*ADDR0 FROM THE ADSP-2141

IS NO CONNECT FOR 32-BIT MEMORY.

ADSP-2141 ADDR1 IS WIRED TO RAM A0.

DATA

8192

8K 3 16

ADSP-2141L

REV. 0

EEPROM

EE_DI

EE_DO

EE_CS

EE_SK

SERIAL

EEPROM

Figure 7. ADSP-2141L PCI System Configuration

–13–

Page 14

ADSP-2141L

DEVICE OPERATION

OPERATIONAL MODES

Security Modes

The ADSP-2141L operates in one of two security modes: kernel

mode or user mode. The mode switching is performed on the fly

as program execution proceeds. Kernel mode is entered via a

jump or call to address 0x2000 with PMOVLAY set to 0x000F.

Kernel mode will exit on its own once it has completed a requested

operation (or terminates due to an error).

Special interrupt handling is performed if the DSP is executing

in kernel mode. While executing a CGX command in kernel

mode, it is possible to interrupt to a nonprotected vector location and then invoke the kernel again during the interrupt handler. The [IF CONDITION] RTI instruction must be used to

return to the kernel from the interrupt handler. The return

address and PMOVLAY page must match the interrupted address and PMOVLAY page. If not, the violation reset logic will

be triggered. Only one level of kernel mode nesting is permitted.

An interrupt to a nonprotected vector location while in nested

kernel mode will also trigger the violation reset logic.

While in kernel mode, it is possible to interrupt to a protected

vector location. In this case, the processor remains in kernel

mode. The [IF CONDITION] RTI instruction must be used to

return the processor from the interrupt handler. There is no

imposed limit on the number of nested interrupts to a protected

vector location.

Bus Modes

The ADSP-2141L Host Bus may be configured for one of two

personalities: IDMA Mode or PCI Bus Mode. The selection of

mode is made with two hardware control inputs BUS_MODE

and BUS_SEL at boot time.

Table II. Bus Mode Selection

Bus Mode Pins BUS_MODE BUS_SEL

IDMA Mode 0 0

PCI Bus Mode 1 0

This selection may not be changed after the ADSP-2141L

comes out of power-up reset. It is typically expected that the bus

mode signals are tied to ground or VDD on the PC Board.

Boot Modes

The ADSP-2141L may be bootstrap-loaded from one of three

sources: byte-wide memory, host processor bus, or external

program memory. The selection of mode is made with two

hardware control inputs BMODE and MMAP. When the host

processor boot mode is selected, any one of the two bus modes

may be used.

Table III. Boot Mode Selection

Boot Mode Pins BMODE MMAP

Byte-Wide (BDMA) Boot Mode 0 0

Host Bus (IDMA) Boot Mode 1 0

External Program Boot Mode 0 1

The hardware pin states are not relevant after the ADSP-2141L

comes out of power-up reset. Refer to the ADSP-2141L User’s

Manual (available from IRE) for information on BDMA, IDMA

and external program boot modes.

COMMAND INTERFACE

This section provides a general overview of the software command interface to the crypto functions in the ADSP-2141L.

Refer to the ADSP-2141 CGX Interface Programmer’s Guide

(available from http://www.ire-ma.com/proddoc.htm) for more

details.

Overview

The ADSP-2141L provides an embedded crypto library that

provides a command interface API (Application Programming

Interface) to outside applications. These commands are referred

to as CGX (CryptoGraphic eXtensions).

The CGX API simultaneously enforces certain security policies

within the ADSP-2141L and insulates applications from the

details of many complex cryptographic operations. The security

policy built into the ADSP-2141L has some of the following

rules:

• Unencrypted (red) keys may never be retrieved from the

ADSP-2141L.

• Keys within the ADSP-2141L are marked with an attributes

field that specifies key type and trust level.

• A key’s type field must match the use in a requested operation (i.e., cannot use a KEK to encrypt traffic).

• Keys generated internal to the ADSP-2141L (i.e., from RNG)

are marked as trusted.

• Keys that are negotiated or imported from outside systems are

marked untrusted (although they may still be quite secure).

• Separate trusted and untrusted key hierarchies may be maintained and customer applications may choose which trust

level is required for a given command.

For most key management operations, the CGX interface must

be used. However, for certain high performance encryption/

hashing applications, the CGX interface may be bypassed and

either the DSP or a host processor may exercise direct control

over the hash/encrypt block.

–14–

REV. 0

Page 15

ADSP-2141L

COMMAND SUMMARY

Approximately 40 CGX Commands are supported in the API to the ADSP-2141L.

General Utilities

INIT Initializes Secure Kernel and Allow Reconfiguration of the ADSP-2141L

DEFAULT Restores Factory Default Settings

RANDOM Generates Random Numbers (between 1K and 64K bytes)

GET CHIPINFO Returns ADSP-2141L System Information

SELF TEST Runs a suite of self-tests on the hardware and CGX

Symmetrical Key Management

UNCOVER KEY Loads and Decrypts a Secret Key

GEN KEY Generates a Secret Key

GEN KEK Generates an Internal Key Encryption Key

GEN RKEK Generates a Key Recovery Key Encryption Key

SAVE KEY Saves a key protected by the Recovery Key (RKEK)

LOAD KEY Imports a Red (plaintext) User Secret Key

DERIVE KEY Derives a Secret Key from a Pass Phrase

TRANSFORM KEY Transforms a Secret Key using IPsec

DESTROY KEY Removes Secret Key from the KCR

EXPORT KEY Exports an IRE-format Secret Key

IMPORT KEY Imports an IRE-format Secret Key

Symmetrical Encryption

ENCRYPT Encrypts Data

DECRYPT Decrypts Data

LOAD KG Loads Secret Key into HW/SW Key Generator

Hash

HASH INIT Initializes the Hash Operator

HASH DATA Hash Customer Data

HASH ENCRYPT Hash and Encrypt Customer Data

HASH DECRYPT Hash and Decrypt Customer Data

PRF Functions

MERGE KEY Combines two secret keys into one key

MERGE LONG KEY Combines two secret keys into a data string (long key)

EXTRACT LONG KEY Creates a secret key from a data string (long key)

PRF DATA Hash multiple data items using HMAC

PRF KEY Completes the above HMAC and create secret key

Asymmetrical Key Management

GEN PUBKEY Generates a Public Keyset (Public and Private Parts)

GEN NEWPUBKEY Generates a part of a Public Keyset

GEN NEGKEY Generates a Diffie-Hellman Derived Secret Key

EXPORT PUBKEY Exports an IRE-format Public Key

IMPORT PUBKEY Imports an IRE-format Public Key

Asymmetrical Encryption

PUBKEY ENCRYPT Encrypts Data using RSA Public Key

PUBKEY DECRYPT Decrypts Data using RSA Public Key

Digital Signatures

SIGN Digitally Signs a Message

VERIFY Verifies a Digital Signature

Math Utilities

ADD VECTOR Performs a Vector Add Operation

SUB VECTOR Performs a Vector Subtract Operation

MULT VECTOR Performs a Vector Multiply Operation

EXP VECTOR Performs a Vector Exponentiate Operation

SHIFT VECTOR Performs a Vector Right or Left Shift Operation

Extended Mode

LOAD EXTENDED Loads/Enables Extended (Downloaded) Algorithm Block

EXECUTE EXTENDED Executes Extended (Downloaded) Algorithm Block

REV. 0

–15–

Page 16

ADSP-2141L

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +4.6 V

Input Voltage . . . . . . . . . . . . . . . . . . . . –0.5 V to V

Output Voltage Swing . . . . . . . . . . . . . –0.5 V to V

+ 0.5 V

DD

+ 0.5 V

DD

Operating Temperature Range (Ambient) . . . . . 0°C to 70°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (5 sec) MQFP . . . . . . . . . . . . . . . . . 280°C

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the ADSP-2141L features proprietary ESD protection circuitry, permanent damage

may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

Frequency Dependency For Timing Specifications

t

is defined as 0.5t

CK

. The ADSP-2141L uses an input clock

CKI

with a frequency equal to half the instruction rate: a 20.0 MHz

input clock (which is equivalent to 50 ns) yields a 25 ns processor

cycle (equivalent to 40 MHz). t

period should be substituted for all relevant timing parameters to

obtain the specification value.

Example: t

= 0.5tCK – 7 ns = 0.5 (25 ns) – 7 ns = 8 ns

CKH

values within the range of 0.5t

CK

CKI

–16–

REV. 0

Page 17

SPECIFICATIONS

ADSP-2141L

RECOMMENDED OPERATING CONDITIONS

K Grade

Parameter Min Max Unit

V

T

DD

AMB

Supply Voltage 3.0 3.6 V

Ambient Operating Temperature 0 70 °C

ELECTRICAL CHARACTERISTICS

DC SPECIFICATIONS

K Grade

Parameter Test Conditions Min Typ Max Unit

V

IH

V

IH

V

IL

V

OH

V

OL

I

IH

I

IL

I

OZH

I

OZL

I

DD

I

DD

C

I

C

O

NOTES

1

Bidirectional pins: D0–D31, RFS0, RFS1, SCLK0, SCLK1, TFS0, TFS1, IAD0–15, PF0–PF7.

2

Input only pins: IRQ2, BR, MMAP, BMODE, BUS MODE, BUS SEL, DR0, DR1, PWD, IRQL0, IRQL1, IRQE, IS, IRD, IWR, IAL.

3

Input only pins: CLKIN, RESET, IRQ2, BR, MMAP, BMODE, BUS MODE, BUS SEL, DR0, DR1, PWD, IRQL0, IRQL1, IRQE, IS, IRD, IWR, IAL.

4

Output pins: BG, BGH, PMS, DMSL, DMSH, BMS, IOMS, CMS, RD, WR, IACK, PWDACK, A0–A25, DT0, DT1, CLKOUT, FL2–0.

5

Although specified for TTL outputs, all ADSP-2141L outputs are CMOS-compatible and will drive to VDD and GND, assuming no dc loads.

6

Guaranteed but not tested.

7

Output pins: BG, BGH, PMS, DMSL, BMS, IOMS, DMSH, CMS, RD, WR, IACK, PWDACK, A0–A25, DT0, DT1, CLKOUT, FL2–0, EE_DI, EE_CS, EE_SK.

8

0 V on BR. CLKIN active (to force three-state condition).

9

Three-statable pins: A0–A25, D0–D31, PMS, DMSL, DMSH, BMS, IOMS, CMS, RD, WR, DT0, DT1, SCKL0, SCLK1, TFS0, TFS1, RFS0, RFS1, IAD0–

IAD15, PF0–PF7.

10

Idle refers to ADSP-2141L state of operation during execution of IDLE Instruction. Deasserted pins are driven to either VDD or GND.

11

Current reflects device operating with no output loads.

12

VIN = 0.4 V and 2.4 V. For typical supply currents, refer to Power Dissipation section.

13

IDD measurement taken with 93% of instructions executing from internal memory and 7% from external memory. H/E operations are executing from internal

memory concurrently with PCI transactions. Initialization operations are executed from external memory.

14

Applies to MQFP package type.

15

Output pin capacitance is the capacitive load for any three-stated output pin.

Specifications subject to change without notice.

Hi-Level Input Voltage

Hi-Level CLKIN/Reset Voltage @ VDD = max 2.4 V

Lo-Level Input Voltage

Hi-Level Output Voltage

Lo-Level Output Voltage

Hi-Level Input Current

Lo-Level Input Current

Three-State Leakage Current

Three-State Leakage Current

Supply Current (Idle)

Supply Current (Dynamic)

Input Pin Capacitance

Output Pin Capacitance

1, 2

1, 3

1, 4, 5

1, 4, 5

3

3

10, 11

3, 6, 14

6, 7, 14, 15

7

9

11, 13

@ VDD = max 2.0 V

@ VDD = min 0.4 V

@ VDD = min

I

= –0.5 mA 2.4 V

OH

@ V

= min

DD

= –100 µA

I

OH

6

VDD – 0.3 V

@ VDD = min

I

= 2 mA 0.4 V

OL

@ VDD = max

V

= V

IN

max 10 µA

DD

3 @ VDD = max

= 0 V 10 µA

V

IN

@ VDD = max

V

= VDD max

IN

@ VDD = max

V

= 0 V

IN

8

9

10 µA

8 µA

@ VDD = 3.3

= 25°C

T

AMB

t

= 25 ns

CK

t

= 30 ns

CK

12

12

16 mA

15 mA

@ VDD = 3.3

T

= 25°C

AMB

t

= 25 ns

CK

= 30 ns

t

CK

12

12

195 mA

165 mA

@ VIN = 2.5 V

f

= 1.0 MHz

IN

= 25°C8pF

T

AMB

@ VIN = 2.5 V

f

= 1.0 MHz

IN

T

= 25°C8pF

AMB

REV. 0

–17–

Page 18

ADSP-2141L

DC SPECIFICATIONS– PCI Bus Pins

K Grade

Parameter Test Conditions Min Max Unit

V

IH

V

IL

V

OH

V

OL

I

IH

I

IL

I

OZH

I

OZL

C

I

C

CLK

C

IDSEL

L

PIN

NOTES

1

Bidirectional pins: MPLX_BUS [31:0}, MPLX1–4, MPLX7–10, MPLX12

2

Input only pins: MPLX_RESET, MPLX5, MPLX6, PCI_CLK, PCI_PAR, PCI_IRDY, PCI_STOP

3

Output only pins: MPLX11

4

Leakage currents include High-Z output leakage for bidirectional buffers with three-state outputs.

5

Lower capacitance of IDSEL (MPLX_5) input-only pin allows for nonresistive connection to Address/Data bus.

Hi-Level Input Voltage

Lo-Level Input Voltage

Hi-Level Output Voltage

Lo-Level Output Voltage

Hi-Level Input Current

Lo-Level Input Current

Three-State Leakage Current

Three-State Leakage Current

Input Pin Capacitance T

PCI CLK Pin Capacitance T

PCI IDSEL Pin Capacitance

Pin Inductance 20 nH

1, 2

1, 2

2

0.5 V

DD

1, 3

1, 3

2

4

1

5

I

= –500 µA 0.9 V

OUT

I

= 1500 µA 0.1 V

OUT

0 < VIN < V

0 < VIN < V

0 < VIN < V

0 < VIN < V

AMB

AMB

T

AMB

DD

DD

DD

DD

= 25°C10pF

= 25°C5 12pF

= 25°C8pF

–0.5 0.3 V

DD

VDD + 0.5 V

DD

V

V

DD

V

10 µA

10 µA

10 µA

10 µA

TIMING PARAMETERS

PCI Clock

The ADSP-2141L is targeted for use in PCI add-on I/O slave card designs. It provides a glueless interface to the PCI bus. All bus

drivers are compliant with PCI interface electrical switching and drive capability specifications.

The ADSP-2141L does not implement the following signals: LOCK, INTB, INTC, INTD, SBO, SDONE, CLKRUN, AD[64:32],

C/BE[7:4], REQ64, ACK64, PAR64.

Parameter Min Max Unit

Timing Requirements:

t

CYC

t

HIGH

t

LOW

NOTES

1

Rise and fall times are specified in terms of the edge rate measured in V/ns. This slew rate must be met across the minimum peak-to-peak portion of the waveform as

shown in Figure 8.

2

The minimum RST slew rate applies only to the rising (deassertion) edge of the reset signal, and ensures that system noise cannot render an otherwise monotonic

signal to appear to bounce in the switching range.

(Guaranteed Over Operating Temperature and Digital Supply Range)

CLK Cycle Time 25 100 ns

CLK High Time 11 ns

CLK Low Time 11 ns

CLK Slew Rate

RST Slew Rate

0.6V

0.5V

0.4V

0.3V

0.2V

1

2

t

CYC

t

CC

CC

CC

CC

CC

HIGH

t

LOW

1 4 V/ns

50 mV/ns

2V p-p

(

MINIMUM

)

Figure 8. Clock Waveform

–18–

REV. 0

Page 19

ADSP-2141L

Parameter Min Max Unit

PCI Bus Interface

Timing Requirements:

t

VAL

t

ON

t

OFF

t

SU

t

H

t

RST-OFF

CLK to Signal Valid 2 11 ns

CLK to Low-Z Delay 2 ns

CLK to High-Z Delay 28 ns

Input Setup to CLK 7 ns

Input Hold After CLK 1 ns

RST Active to Outputs High-Z 40 ns

CLK

OUTPUT

DELAY

THREE-STATE

OUTPUT

CLK

INPUT

V

TEST

t

VAL

V

(3.3V SIGNALING)

STEP

OUTPUT CURRENT # LEAKAGE CURRENT

t

ON

V

TH

V

TL

t

OFF

t

SU

V

TEST

INPUTS

VALID

t

H

V

TEST

Figure 9. Output (Top) and Input Timing Measurement Conditions

V

TH

V

TL

V

MAX

REV. 0

–19–

Page 20

ADSP-2141L

Parameter Min Max Unit

Clock Signals and Reset

Timing Requirements:

t

CKI

t

CKIL

t

CKIH

Switching Characteristics:

t

CKL

t

CKH

t

CKOH

Control Signals

Timing Requirement:

t

RSP

NOTE

1

Applies after power-up sequence is complete. Internal phase lock loop requires no more than 2000 CLKIN cycles assuming stable CLKIN (not including crystal

oscillator start-up time).

CLKIN Period 50 100 ns

CLKIN Width Low 15 ns

CLKIN Width High 15 ns

CLKOUT Width Low 0.5tCK – 7 ns

CLKOUT Width High 0.5tCK – 7 ns

CLKIN High to CLKOUT High 0 20 ns

RESET Width Low

CLKIN

1

t

CKI

t

CKIH

5t

CK

ns

CLKOUT

t

CKIL

t

CKL

t

CKOH

t

CKH

Figure 10. Clock Signals and Reset

–20–

REV. 0

Page 21

ADSP-2141L

Parameter Min Max Unit

Interrupts and Flags

Timing Requirements:

t

t

IFS

IFH

IRQx, FI, or PFx Setup Before CLKOUT Low

IRQx, FI, or PFx Hold After CLKOUT High

Switching Characteristics:

t

FOH

t

FOD

NOTES

1

If IRQx and FI inputs meet t

the following cycle. (Refer to the Interrupt Controller Operation section in the Program Control chapter of the ADSP-2100 Family User’s Manual for further information on interrupt servicing.)

2

Edge-sensitive interrupts require pulsewidths greater than 10 ns; level-sensitive interrupts must be held low until serviced.

3

IRQx = IRQ0, IRQ1, IRQ2, IRQL0, IRQL1, IRQE.

4

PFx = PF0, PF1, PF2, PF3, PF4, PF5, PF6, PF7.

5

Flag Outputs = PFx, FL0, FL1, FL2, Flag_out.

Flag Output Hold After CLKOUT Low

Flag Output Delay from CLKOUT Low

and t

IFS

setup/hold requirements, they will be recognized during the current clock cycle; otherwise the signals will be recognized on

IFH

CLKOUT

1, 2, 3, 4

1, 2, 3, 4

5

5

t

FOD

t

FOH

0.25tCK + 15 ns

0.25t

CK

ns

0.5tCK – 7 ns

0.5t

+ 5 ns

CK

FLAG

OUTPUTS

IRQx

PFx

t

IFH

FI

t

IFS

Figure 11. Interrupts and Flags

REV. 0

–21–

Page 22

ADSP-2141L

Parameter Min Max Unit

Bus Request/Bus Grant

Timing Requirements:

t

BH

t

BS

BR Hold After CLKOUT High

BR Setup Before CLKOUT Low

Switching Characteristics:

t

SD

t

SDB

t

SE

t

SEC

t

SDBH

t

SEH

NOTES

xMS = PMS, DMSL, DMSH, CMS, IOMS, BMS.

1

BR is an asynchronous signal. If BR meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise, the signal will be recognized

on the following cycle. Refer to the ADSP-2100 Family User’s Manual for BR/BG cycle relationships.

2

BGH is asserted when the bus is granted and the processor requires control of the bus to continue.

CLKOUT High to xMS, RD, WR Disable 0.25tCK + 10 ns

xMS, RD, WR Disable to BG Low 0 ns

BG High to xMS, RD, WR Enable 0 ns

xMS, RD, WR Enable to CLKOUT High 0.25tCK – 6 ns

xMS, RD, WR Disable to BGH Low

BGH High to xMS, RD, WR Enable

CLKOUT

1

1

2

2

t

BH

0.25tCK + 2 ns

0.25tCK + 17 ns

0ns

0ns

BR

CLKOUT

PMS, DMSL,

BMS, RD, WR

BG

BGH

t

BS

t

SD

t

SDB

t

SDBH

Figure 12. Bus Request/Bus Grant

t

SEC

t

SE

t

SEH

–22–

REV. 0

Page 23

ADSP-2141L

Parameter Min Max Unit

External Memory Write: ADSP-2141L DMA Initiated

Switching Characteristics:

t

A

t

DW

t

DH

t

WP

t

WDE

t

ASW

t

DDR

t

CWR

t

AW

t

AH

t

WRA

t

WWR

1. If wait-state(s) added, then referenced to last wait-state clock interval.

2. w = DMA wait states × t

Clock to Address and DMSx 59ns

Data Setup Before Write Deasserted 0.5tCK – 2 + w ns

Data Hold After Write Deasserted 0.5tCK – 8 ns

Write Pulsewidth 0.5tCK – 5 + w ns

Write Low to Data Enabled –5 ns

Address, DMSx Setup Before Write Low 1 ns

Data Disable Before Write/Read Low 0 ns

Clock High to Write Low 6 12 ns

Address, DMSx Setup Before Write High 0.5tCK – 2 + w ns

Address and DMSx Hold After Clock 2 ns

Address, DMSx Hold After Write High 0.5tCK – 7 ns

Write High to Read/Write Low 0.5tCK – 3 ns

.

CK

25ns (REF @ 40MHz)

DSP CLOCK

OUT

EXT. ADDR

(A25–0)

t

ASW

t

AH

EXT. DMSH

EXT. DMSL

EXT. WR

EXT. DATA

(D31–0)

t

t

A

CWR

t

WDE

t

AW

t

WP

t

DW

t

WRA

t

DH

Figure 13. External Memory Write: ADSP-2141L DMA Initiated

t

WWR

t

DDR

REV. 0

–23–

Page 24

ADSP-2141L

Parameter Min Max Unit

External Memory Read—ADSP-2141L DMA Initiated

Timing Requirements:

t

RDD

t

AA

t

SUR

t

RDH

Switching Characteristics:

t

A

t

ASR

t

AH

t

RDA

t

CRD

t

RP

t

RWR

1. If wait-state(s) added, then referenced to last wait-state clock interval.

2. w = DMA wait states × t

Read Low to Data Valid 0.5tCK – 8 + w ns

Address, DMSx Valid to Data Valid 0.5t

– 3 + w ns

CK

Data Valid Before Read Deasserted 4 ns

Data Hold After Read Deasserted 1 ns

Clock to Address and DMSx Active 5 9 ns

Address, DMSx Setup Before Read Low 2 ns

Address and DMSx Hold After Clock 2 ns

Address, DMSx Hold After Read High 0.5tCK – 7 ns

Clock High to RD Low 8 12 ns

Read Pulsewidth 0.5tCK – 5 + w ns

RD High to Read or Write Low 0.5tCK – 3 ns

.

CK

25ns (REF @ 40MHz)

DSP CLOCK

OUT

EXT. ADDR

(A25–0)

EXT. DMSH

EXT. DMSL

t

A

t

AA

t

ASR

t

CRD

t

RP

t

RDA

t

RWR

t

AH

EXT. RD

EXT. DATA

(D31–0)

t

RDD

t

SUR

t

RDH

Figure 14. External Memory Read – ADSP-2141L DMA Initiated

–24–

REV. 0

Page 25

ADSP-2141L

Parameter Min Max Unit