Page 1

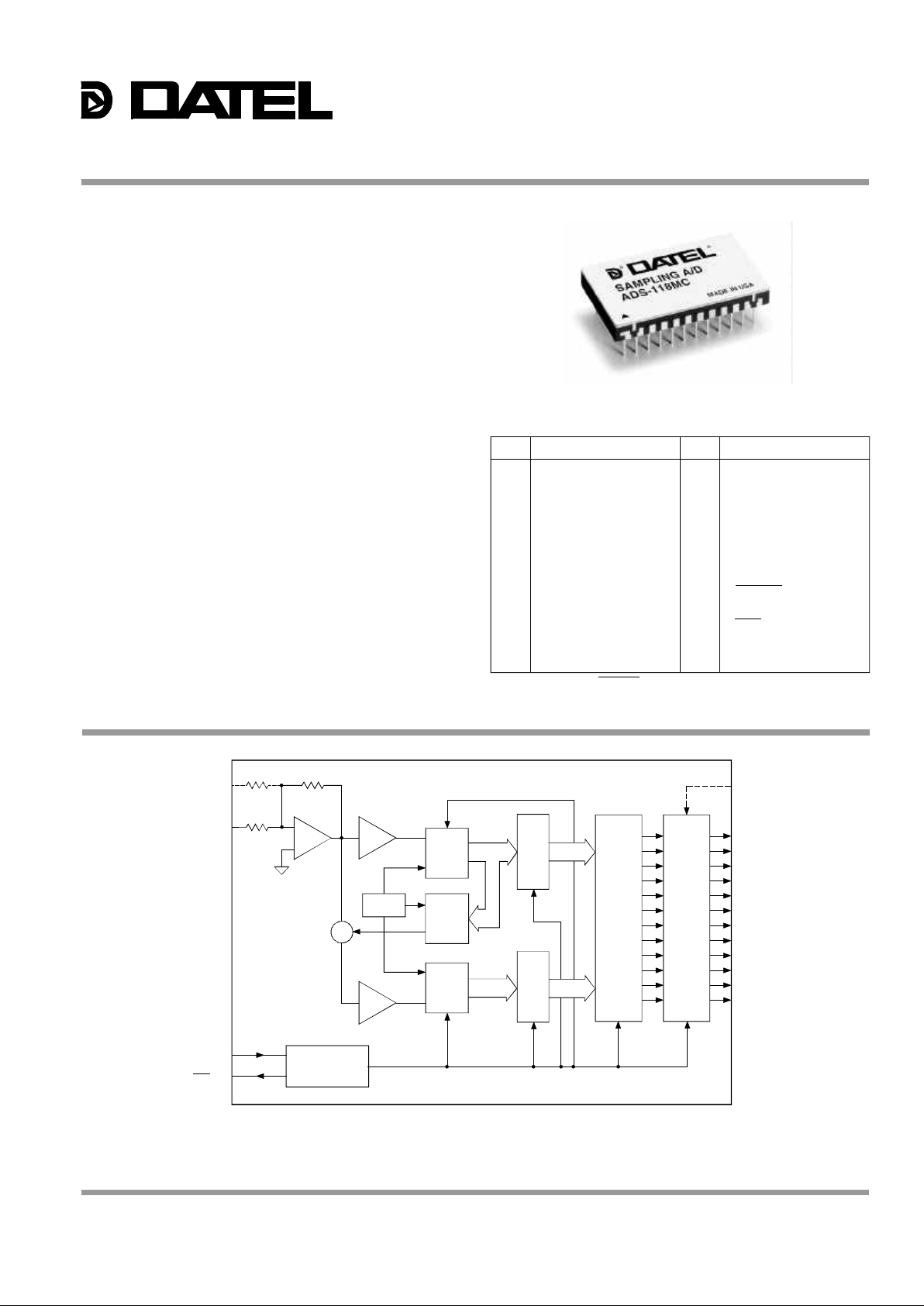

Figure 1. ADS-118/118A Functional Block Diagram

FEATURES

• 12-bit resolution

• 5MHz minimum sampling rate

• Functionally complete

• Small 24-pin DDIP

• Requires only ±5V supplies

• Low-power, 1.3 Watts

• Outstanding dynamic performance

• No missing codes over full military temperature range

• Edge-triggered, no pipeline delay

• Ideal for both time and frequency-domain applications

GENERAL DESCRIPTION

DATEL's ADS-118 and ADS-118A are 12-bit, 5MHz, sampling

A/D converters packaged in space-saving 24-pin DDIP’s. The

ADS-118 offers an input range of ±1V and has three-state

outputs. The ADS-118A has an input range of ±1.25V and

features direct adjustment of offset error.

These functionally complete low-power devices (1.3 Watts)

contain an internal fast-settling sample/hold amplifier, a 12-bit

subranging A/D converter, a precise voltage reference, timing/

control logic, and error-correction circuitry. All timing and

control logic operates from the rising edge of a single start

convert pulse. Digital input and output levels are TTL. Models

are available for use in either commercial (0 to +70°C) or

military (–55 to +125°C) operating temperature ranges.

Applications include radar, transient signal analysis, process

control, medical/graphic imaging, and FFT spectrum analysis.

®

®

INNOV A TION and EX CELLENCE

ADS-118, ADS-118A

12-Bit, 5MHz, Low-Power

Sampling A/D Converters

DATEL, Inc., 11 Cabot Boulevard, Mansfield, MA 02048-1151 (U.S.A.) • Tel: (508) 339-3000 Fax: (508) 339-6356 • For immediate assistance: (800) 233-2765

INPUT/OUTPUT CONNECTIONS

PIN FUNCTION PIN FUNCTION

1 BIT 12 (LSB) 24 NO CONNECTION

2 BIT 11 23 ANALOG GROUND

3 BIT 10 22 NO CONNECTION

4 BIT 9 21 +5V ANALOG SUPPLY

5 BIT 8 20 –5V SUPPLY

6 BIT 7 19 ANALOG INPUT

7 BIT 6 18 ANALOG GROUND

8 BIT 5 17 ENABLE/OFFSET ADJ.

9 BIT 4 16 START CONVERT

10 BIT 3 15 EOC

11 BIT 2 14 DIGITAL GROUND

12 BIT 1 (MSB) 13 +5V DIGITAL SUPPLY

*

* ADS-118, Pin 17 is ENABLE

ADS-118A, Pin 17 is OFFSET ADJUST

REF

DAC

REGISTER

REGISTER

3-STATE OUTPUT REGISTER

12 BIT 1 (MSB)

11 BIT 2

10 BIT 3

9 BIT 4

8 BIT 5

7 BIT 6

6 BIT 7

5 BIT 9

4 BIT 9

3 BIT 10

2 BIT 11

1 BIT 12 (LSB)

TIMING AND

CONTROL LOGIC

OFFSET ADJUST 17

ANALOG INPUT 19

START CONVERT 16

EOC 15

–

+

S/H

BUFFER

DIGITAL CORRECTION LOGIC

FLASH

ADC

1

FLASH

ADC

2

Σ

AMP

21

+5V ANALOG

SUPPLY

20

–5V SUPPLY

18, 23

ANALOG

GROUND

13

+5V DIGITAL

SUPPLY

14

DIGITAL

GROUND

22, 24

NO CONNECT

(ADS-118A only)

17 ENABLE

(ADS-118A only)

Page 2

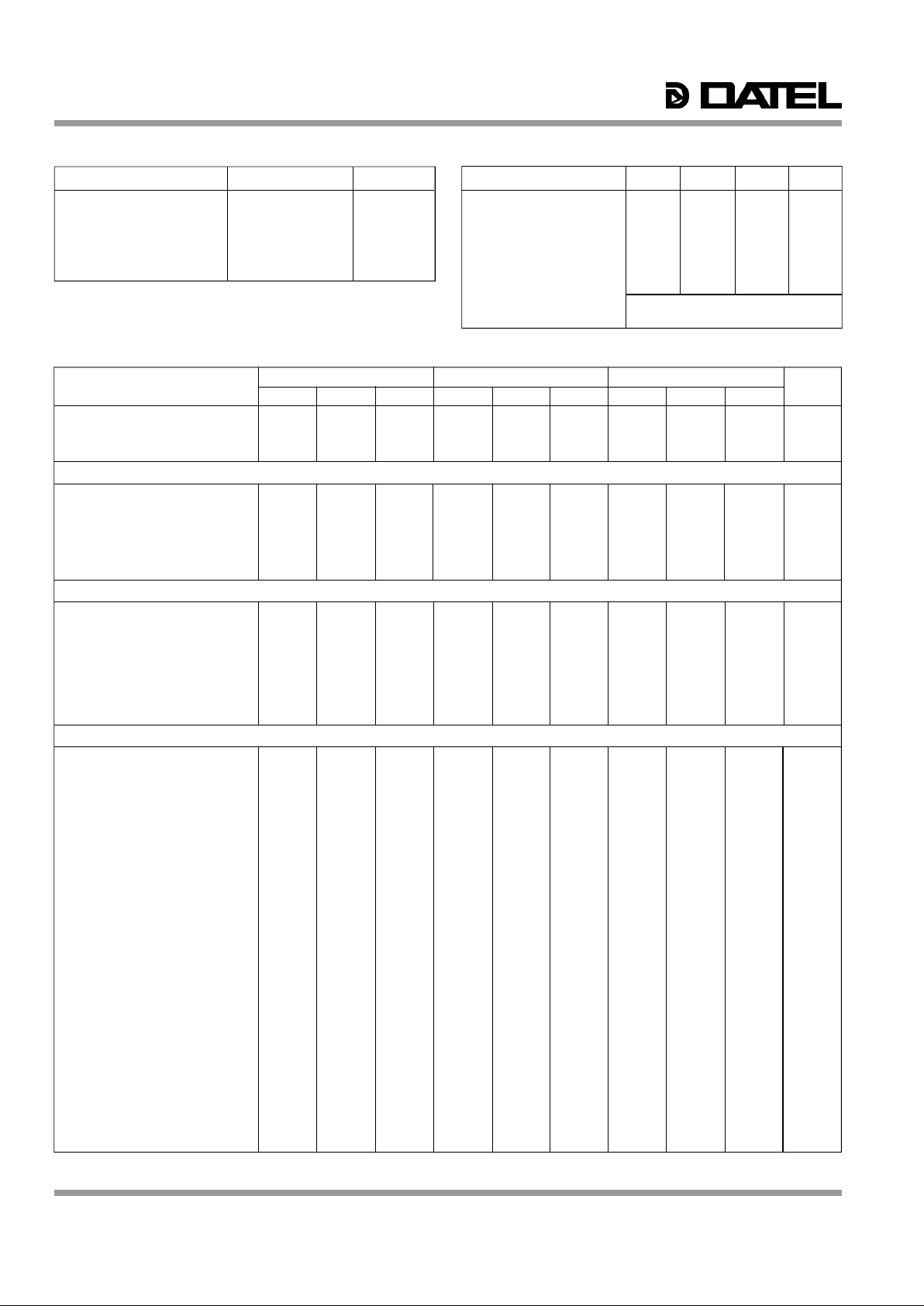

ADS-118/118A

® ®

2

PARAMETERS MIN. TYP. MAX. UNITS

Operating Temp. Range, Case

ADS-118/118AMC 0 — +70 °C

ADS-118/118AMM, GM, 883 –55 — +125 °C

Thermal Impedance

θjc — 2 — °C/Watt

θca — 23 — °C/Watt

Storage Temperature Range –65 — +150 °C

Package Type 24-pin, metal-sealed, ceramic DDIP or SMT

Weight 0.42 ounces (12 grams)

ABSOLUTE MAXIMUM RATINGS

PARAMETERS LIMITS UNITS

+5V Supply (Pins 13, 21) 0 to +6 Volts

–5V Supply (Pin 20) 0 to –6 Volts

Digital Input (Pin 16, 17) –0.3 to +V

DD +0.3 Volts

Analog Input (Pin 19) ±5 Volts

Lead Temperature (10 seconds) +300 °C

PHYSICAL/ENVIRONMENTAL

+25°C 0 to +70°C –55 to +125°C

ANALOG INPUT MIN. TYP. MAX. MIN. TYP. MAX. MIN. TYP. MAX. UNITS

Input Voltage Range, ADS-118 ➁ — ±1 — — ±1 — — ±1 — Volts

Input Resistance 475 500 — 475 500 — 475 500 — Ω

Input Capacitance — 6 15 — 6 15 — 6 15 pF

DIGITAL INPUT

Logic Levels

Logic "1" +2.0 — — +2.0 — — +2.0 — — Volts

Logic "0" — — +0.8 — — +0.8 — — +0.8 Volts

Logic Loading "1" — — +20 — — +20 — — +20 µA

Logic Loading "0" — — –20 — — –20 — — –20 µA

Start Convert Positive Pulse Width ➂ 50 100 — 50 100 — 50 100 — ns

STATIC PERFORMANCE

Resolution — 12 — — 12 — — 12 — Bits

Integral Nonlinearity (f

in = 10kHz) — ±0.75 — — ±1.0 — — ±1.5 — LSB

Differential Nonlinearity (f

in = 10kHz) — ±0.5 +0.75 — ±0.5 ±0.95 — ±0.75 +0.95 LSB

Full Scale Absolute Accuracy — ±0.1 ±0.5 — ±0.5 ±0.75 — ±0.75 ±1.5 %FSR

Bipolar Zero Error (Tech Note 2) — ±0.1 ±0.5 — ±0.5 ±0.85 — ±0.85 ±2.0 %FSR

Bipolar Offset Error (Tech Note 2) — ±0.1 ±0.5 — ±0.5 ±1.5 — ±1.5 ±2.5 %FSR

Gain Error (Tech Note 2) — ±0.1 ±0.5 — ±0.5 ±1.0 — ±1.0 ±2.5 %

No Missing Codes (f

in = 10kHz) 12 — — 12 — — 12 — — Bits

DYNAMIC PERFORMANCE

Peak Harmonics (–0.5dB)

dc to 500kHz — –76 –71 — –74 –70 — –72 –66 dB

500kHz to 1MHz — –75 –71 — –74 –70 — –70 –65 dB

1MHz to 2.5MHz — –69 –69 — –73 –67 — –66 –60 dB

Total Harmonic Distortion (–0.5dB)

dc to 500kHz — –72 –68 — –71 –67 — –70 –65 dB

500kHz to 1MHz — –71 –67 — –70 –66 — –67 –63 dB

1MHz to 2.5MHz — –70 –66 — –69 –65 — –66 –60 dB

Signal-to-Noise Ratio

(w/o distortion, –0.5dB)

dc to 500kHz 67 69 — 66 69 — 64 67 — dB

500kHz to 1MHz 66 69 — 65 68 — 63 66 — dB

1MHz to 2.5MHz 66 69 — 65 68 — 63 66 — dB

Signal-to-Noise Ratio ➃

(& distortion, –0.5dB)

dc to 500kHz 65 68 — 64 67 — 62 66 — dB

500kHz to 1MHz 65 68 — 64 67 — 61 65 — dB

1MHz to 2.5MHz 64 67 — 63 66 — 60 64 — dB

Noise — 195 — — 195 — — 195 — µVrms

Two-tone Intermodulation

Distortion (f

in = 1MHz,

975kHz, f

s = 5MHz, –0.5dB) — –74 — — –74 — — –74 — dB

Input Bandwidth (–3dB)

Small Signal (–20dB input) — 20 — — 20 — — 20 — MHz

Large Signal (–0.5dB input) — 10 — — 10 — — 10 — MHz

Feedthrough Rejection (f

in = 2.5MHz) — 80 — — 80 — — 80 — dB

Slew Rate — ±400 — — ±400 — — ±400 — V/µs

Aperture Delay Time — +10 — — +10 — — +10 — ns

Aperture Uncertainty — 3 — — 3 — — 3 — ps rms

FUNCTIONAL SPECIFICATIONS

(TA = +25°C, ±VDD = ±5V, 5MHz sampling rate, and a minimum 3 minute warmup ➀ unless otherwise specified.)

Page 3

ADS-118/118A

® ®

3

the adjustment circuitry shown in Figures 2a and 2b. When

using this circuitry, or any similar offset and gain-calibration

hardware, make adjustments following warmup. To avoid

interaction, always adjust offset before gain.

3. To enable the three-state outputs, connect ENABLE

(pin 17) to a logic "0" (low). To disable, connect pin 17 to

logic "1" (high). The three-state outputs are permanently

enabled in the ADS-118A.

4. Applying a start convert pulse while a conversion is in

progress (EOC = logic "1") will initiate a new and inaccurate

conversion cycle.

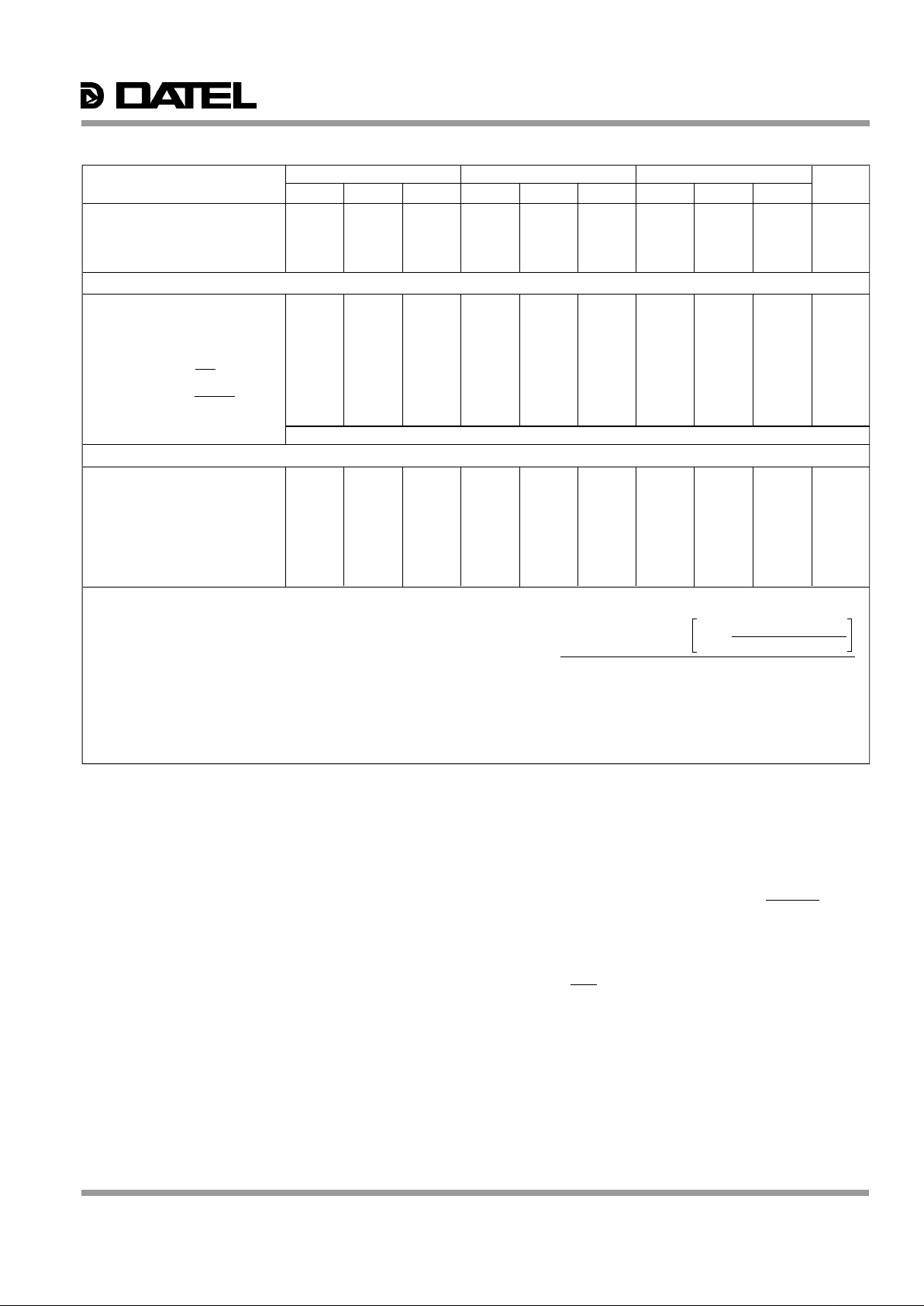

+25°C 0 to +70°C –55 to +125°C

DYNAMIC PERFORMANCE (Cont.) MIN. TYP. MAX. MIN. TYP. MAX. MIN. TYP. MAX. UNITS

S/H Acquisition Time

( to ±0.001%FSR, 10V step) — 85 90 — 85 90 — 85 90 ns

Overvoltage Recovery Time ➄ — 200 — — 200 — — 200 — ns

A/D Conversion Rate 5 — — 5 — — 5 — — MHz

DIGITAL OUTPUTS

Logic Levels

Logic "1" +2.4 — — +2.4 — — +2.4 — — Volts

Logic "0" — — +0.4 — — +0.4 — — +0.4 Volts

Logic Loading "1" — — –4 — — –4 — — –4 mA

Logic Loading "0" — — +4 — — +4 — — +4 mA

Delay, Falling Edge of EOC to

Output Data Valid — — 20 — — 20 — — 20 MHz

Delay, Falling Edge of ENABLE to

Output Data Valid — — 10 — — 10 — — 10 MHz

Output Coding

Offset Binary

POWER REQUIREMENTS

Power Supply Ranges ➅

+5V Supply +4.75 +5.0 +5.25 +4.75 +5.0 +5.25 +4.9 +5.0 +5.25 Volts

–5V Supply –4.75 –5.0 –5.25 –4.75 –5.0 –5.25 –4.9 –5.0 –5.25 Volts

Power Supply Currents

+5V Supply — +205 +220 — +205 +220 — +205 +220 mA

–5V Supply — –80 –90 — –80 –90 — –80 –90 mA

Power Dissipation — 1.3 1.5 — 1.3 1.5 — 1.3 1.5 Watts

Power Supply Rejection — — ±0.1 — — ±0.1 — — ±0.1 %FSR/%V

Footnotes:

➄ This is the time required before the A/D output data is valid once the analog input

is back within the specified range.

➅ The minimum supply voltages of +4.9V and –4.9V for ±V

DD are required for

–55°C operation only. The minimum limits are +4.75V and –4.75V when

operating at +125°C

6.02

(SNR + Distortion) – 1.76 + 20 log

Full Scale Amplitude

Actual Input Amplitude

➀ All power supplies should be on before applying a start convert pulse. All

supplies and the clock (start convert pulses) must be present during warmup

periods. The device must be continuously converting during this time.

➁ Input voltage ranges for ADS-118A is ±1.25V

➂ A 100ns wide start convert pulse is used for all production testing. For

applications requiring less than an 5MHz sampling rate, wider start convert

pulses can be used.

NOTE: The device only requires the rising edge of a start convert pulse to

operate.

➃ Effective bits is equal to:

TECHNICAL NOTES

1. Obtaining fully specified performance from the ADS-118

requires careful attention to pc-card layout and power supply

decoupling. The device’s analog and digital ground systems

are connected to each other internally. For optimal performance, tie all ground pins (14, 18, and 23) directly to a large

analog ground plane beneath the package.

Bypass all power supplies to ground with 4.7µF tantalum

capacitors in parallel with 0.1µF ceramic capacitors. Locate

the bypass capacitors as close to the unit as possible.

2. The ADS-118 achieves its specified accuracies without the

need for external calibration. If required, the device’s small

initial offset and gain errors can be reduced to zero using

Page 4

ADS-118/118A

® ®

4

SIGNAL

INPUT

GAIN

ADJUST

50

Ω

To Pin19

of ADS-118A

Potentiometer is at 25Ω during the device's factory trim procedure.

20k

Ω

–15V (or –5V)

+15V (or +5V)

To Pin17

of ADS-118A

ZERO/

OFFSET

ADJUST

To Pin19

of ADS-118

–15V

SIGNAL

INPUT

GAIN

ADJUST

1.98k

Ω

50Ω

+15V

2k

Ω

1.2M

Ω

20k

Ω

–15V

+15V

ZERO/

OFFSET

ADJUST

CALIBRATION PROCEDURE

Any offset and/or gain calibration procedures should not be

implemented until devices are fully warmed up. To avoid

interaction, offset must be adjusted before gain. The ranges of

adjustment for the circuits in Figures 2a and 2b are guaranteed

to compensate for the ADS-118's initial accuracy errors and

may not be able to compensate for additional system errors.

A/D converters are calibrated by positioning their digital

outputs exactly on the transition point between two adjacent

digital output codes. This can be accomplished by connecting

LED’s to the digital outputs and adjusting until certain LED's

"flicker" equally between on and off. Other approaches employ

digital comparators or microcontrollers to detect when the

outputs change from one code to the next.

For the ADS-118, offset adjusting is normally accomplished at

the point where the MSB is a 1 and all other output bits are 0’s

and the LSB just changes from a 0 to a 1. This digital output

transition ideally occurs when the applied analog input is

+½LSB (+244µV for ADS-118; +305µV for ADS-118A).

Gain adjusting is accomplished when all bits are 1’s and the

LSB just changes from a 1 to a 0. This transition ideally occurs

when the analog input is at +full scale minus 1½ LSB's

(+0.99927V for ADS-118; +1.249085V for ADS-118A).

Zero/Offset Adjust Procedure

1. Apply a train of pulses to the START CONVERT input

(pin 16) so the converter is continuously converting.

2. Apply +244µV (ADS-118) or +305µV (ADS-118A) to the

ANALOG INPUT (pin 19).

Table 1. Output Coding for Bipolar Operation

+FS –1 LSB +0.99951V 1111 1111 1111 +1.2494V

+3/4 FS +0.75000V 1110 0000 0000 +0.9375V

+1/2 FS +0.50000V 1100 0000 0000 +0.6250V

0 0.00000V 1000 0000 0000 0.0000V

–1/2 FS –0.50000V 0100 0000 0000 –0.6250V

–3/4 FS –0.75000V 0010 0000 0000 –0.9375V

–FS +1 LSB –0.99951V 0000 0000 0001 –1.2494V

–FS –1.00000V 0000 0000 0000 –1.2500V

ADS-118 OUTPUT CODING ADS-118A

INPUT INPUT

BIPOLAR RANGE OFFSET BINARY RANGE

SCALE (±1V ) MSB LSB (±1.25V )

3. Adjust the offset potentiometer until the output bits are

1000 0000 00000 and the LSB flickers between 0 and 1.

Gain Adjust Procedure

1. Apply +0.99927V (ADS-118) or +1.249085V (ADS-118A) to

the ANALOG INPUT (pin 19).

2. Adjust the gain potentiometer until all output bits are 1's

and the LSB flickers between 1 and 0.

3. To confirm proper operation of the device, vary the input

signal to obtain the output coding listed in Table 1.

Figure 2a. Optional ADS-118 External

Gain and Offset Adjust Circuits

Figure 2b. Optional ADS-118A

Gain and Offset Adjust Circuits

Page 5

ADS-118/118A

® ®

5

Note: Scale is approximately 10ns per division.

OUTPUT

DATA

DATA N-1 VALID DATA N VALID

20ns typ.

INVALID DATA

130ns min.

150ns typ.

START

CONVERT

INTERNAL S/H

N N+1

100ns typ.

35ns min., 40ns typ., 50ns max.

Acquisition Time

85ns typ.

90ns max.

10ns typ.

EOC

30ns, ±5ns

Conversion Time

140ns typ., 150ns max.

Hold

INVALID DATA

50ns typ.

70ns max.

ADS-118

ADS-118A

19

16

12

11

10

9

8

7

6

5

4

3

2

1

15

17

BIT 1 (MSB)

BIT 2

BIT 3

BIT 4

BIT 5

BIT 6

BIT 7

BIT 8

BIT 9

BIT 10

BIT 11

BIT 12 (LSB)

EOC

ENABLE (1-12)

or OFFSET ADJUST

ANALOG

INPUT

START

CONVERT

A single +5V supply should be used for both the +5V analog and +5V digital.

If separate supplies are used, the difference between the two cannot exceed 100mV.

➀

0.1µF

0.1µF

4.7µF

4.7µF

13, 21

20

18, 23

–5V

+5V

14

➀

+ +

Figure 3. Typical Connection Diagram

Figure 4. ADS-118/118A Timing Diagram

Page 6

ADS-118/118A

® ®

6

Electrically-insulating, thermally-conductive "pads" may be

installed underneath the package. Devices should be soldered

to boards rather than socketed, and of course, minimal air flow

over the surface can greatly help reduce the package

temperature.

In more severe ambient conditions, the package/junction

temperature of a given device can be reduced dramatically

(typically 35%) by using one of DATEL's HS Series heat sinks.

See Ordering Information for the assigned part number. See

page 1-183 of the DATEL Data Acquisition Components

Catalog for more information on the HS Series. Request DATEL

Application Note AN8, "Heat Sinks for DIP Data Converters",

or contact DATEL directly, for additional information.

THERMAL REQUIREMENTS

All DATEL sampling A/D converters are fully characterized

and specified over operating temperature (case) ranges of

0 to +70°C and –55 to +125°C. All room temperature

(T

A = +25°C) production testing is performed without the use

of heat sinks or forced air cooling. Thermal impedance

figures for each device are listed in their respective

specification tables.

These devices do not normally require heat sinks, however,

standard precautionary design and layout procedures should

be used to ensure devices do not overheat. The ground and

power planes beneath the package, as well as all pcb signal

runs to and from the device, should be as heavy as possible

to help conduct heat away from the package.

Figure 5. FFT Analysis of ADS-118

Figure 6. ADS-118 Histogram and Differential Nonlinearity

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

0 250 500 750 1 1.25 1.5 1.75 2 2.25 2.5

Amplitude Relative to Full Scale (dB)

kHz kHz kHz MHz MHz MHz MHz MHz MHz MHz

(fs = 5MHz, fin = 2.45MHz, Vin = –0.5dB, 4,096-point FFT)

Frequency

Digital Output Code

+0.67

–0.47

0

4096

Number of Occurences

0

4096

Digital Output Code

DNL (LSB's)

0

Page 7

ADS-118/118A

®

®

7

Figure 7. ADS-118/118A Evaluation Boar d Schematic (ADS-B118)

2.2MF

.01MF

20MHY

2.2MF

20MHY

2.2MF

20MHY

2.2MF

0.01MF

20MHY

74HCT573

20MHY

2.2MF

20MHY

2.2MF

0.01MF

20MHY

2.2MF

20K

1.98K

1.2M

74HCT86

OPTIONAL

OPTION

0.1MF

OPTION

.1MF

0.1MF

GAIN

500

74HCT86

74HCT86

2K

0.1MF

2.2MF

2.2MF

OFFSET

119

20K

74HCT573

50

4.7MF

ANALOG

INPUT

+5VA

+5VA

-5VA

-5VA

+15V

+15V

-15V

-15V

B12

B11

B10

B9

B8

B7

B6

START

B5

B4

B3

B2

B1

(LSB)

(MSB)

CONVERT

OELE

8Q

7Q

6Q

5Q

4Q

3Q

2Q

1Q

8D

7D

6D

5D

4D

3D

2D

1D

OELE

8Q

7Q

6Q

5Q

4Q

3Q

2Q

1Q

8D

7D

6D

5D

4D

3D

2D

1D

+5VD

TRIG

+5VA

ENABLE

AGND

EOC

-5V

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B1

DGND

ANAIN

AGND

34

32

30

28

26

24

22

20

33

6

8

10

12

14

16

18

31

27

29

23

25

19

21

3

5

7

9

11

13

15

17

12

4

3

4

7

813

14

17

18

11

10

20

2

5

6

912

15

16

19

1

4

5

10

6

11

1

2

3

12

56

43

87

10 9

12 11

14 13

16 15

18 17

20 19

22 21

24 23

26 25

9

10

8

14

8

7

1

2

3

12

13

11

4

5

6

1

2

3

7

14

+

+

1

2

3

1

2

3

4

7

813

14

17

18

11

10

20

2

5

6

9

12

15

16

19

1

1

2

3

4

5

6

7

8

9

10

11

1213

14

15

16

17

18

19

20

21

22

23

24

+

P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1P1

P1P1P1P1P1P1P1P1P1

SG3

SG2

SG1

+5VA

C7

C14

L7,

JPR2

+15V

C6

C13

L6

-15V

C5

C12

L5

-5VA

C4

C11

L4

U3

+5V

L3

C3

C10

+5VF

L1

C1

C8

-5V

L2

C2

C9

U4

SG9

R2

R5

R6

P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2P2

SG4

U5

C20

X1

C19

SG8

SG7

C18

SG6

C21

R1

U5

U5

+5VF

U5

R4

JPR3

C15

+5VF

JPR4

C16

C17

R3

119A

+5V

P3

P4

SG5

-5V

+5V

+5V

+5VF

+5VF

+5VF

U2

+5VF

JPR5

R7

JPR6

JPR1

ADS-118/119

U1

C22

FOR ADS-119 10MHZ

FOR ADS-118/118A 5MHZ

118A

118A

119A

119

1

3

4

3

2

2

1

3

2

1

118

118A

BETWEEN THESE TWO POINTS.

2. AS AN OPTION, COXIAL CABLE

SEE NOTE 2

SEE NOTE 2

3

2

1

SPARE GATES

ALL RESISTORS ARE IN OHMS

C1-C6 ARE 20V

ALL CAPACITORS ARE 50V

1. UNLESS OTHERWISE SPECIFIED

NOTES:

119

118

0.01MF

0.01MF

0.01MF

0.01MF

Page 8

ADS-118/118A

® ®

® ®

INNOV A TION and EX CELLENCE

DATEL makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein

do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice. The DATEL logo is a registered DATEL, Inc. trademark.

MECHANICAL DIMENSIONS INCHES (mm)

24-Pin DDIP

Versions

0.200 MAX.

(5.080)

0.235 MAX.

(5.969)

0.600 ±0.010

(15.240)

0.80 MAX.

(20.32)

0.100 TYP.

(2.540)

0.100

(2.540)

0.018 ±0.002

(0.457)

0.100

(2.540)

0.040

(1.016)

1.31 MAX.

(33.27)

1 12

13

24

1.100

(27.940)

0.190 MAX.

(4.826)

0.010

(0.254)

+0.002

–0.001

SEATING

PLANE

0.025

(0.635)

Dimension Tolerances

(unless otherwise indicated):

2 place decimal (.XX) ±0.010 (±0.254)

3 place decimal (.XXX) ±0.005 (±0.127)

Lead Material: Kovar alloy

Lead Finish:

50 microinches (minimum) gold plating

over 100 microinches (nominal) nickel plating

PIN 1 INDEX

ORDERING INFORMATION

OPERATING 24-PIN

MODEL NUMBER TEMP. RANGE PACKAGE

ADS-118MC 0 to +70°C DDIP

ADS-118MM –55 to +125°C DDIP

ADS-118AMC 0 to +70°C SMT

ADS-118AMM –55 to +125°C SMT

ACCESSORIES

ADS-B118 Evaluation Board (without ADS-118)

HS-24 Heat Sink for all ADS-118 DDIP models

Receptacles for PC board mounting can be ordered through AMP, Inc., Part # 3-331272-8 (Component Lead

Socket), 24 required. For MIL-STD-883 product, or surface mount packaging, contact DATEL.

24-Pin

Surface Mount

Versions

ADS-118MC

ADS-118MM

ADS-118AMC

ADS-118AMM

DS-0231D 10/96

ISO 9001

ISO 9001

REGISTERED

0.80 MAX.

(20.32)

0.015

(0.381)

MAX. radius

for any pin

1.31 MAX.

(33.02)

0.100 TYP.

(2.540)

0.100

(2.540)

0.190 MAX.

(4.826)

0.040

(1.016)

0.020 TYP.

(0.508)

0.020

(0.508)

24

13

121

PIN 1

INDEX

0.130 TYP.

(3.302)

Dimension Tolerances

(unless otherwise indicated):

2 place decimal (.XX) ±0.010 (±0.254)

3 place decimal (.XXX) ±0.005 (±0.127)

Lead Material: Kovar alloy

Lead Finish: 50 microinches (minimum) gold plating

over 100 microinches (nominal) nickel plating

0.060 TYP.

(1.524)

0.010 TYP.

(0.254)

Loading...

Loading...