Page 1

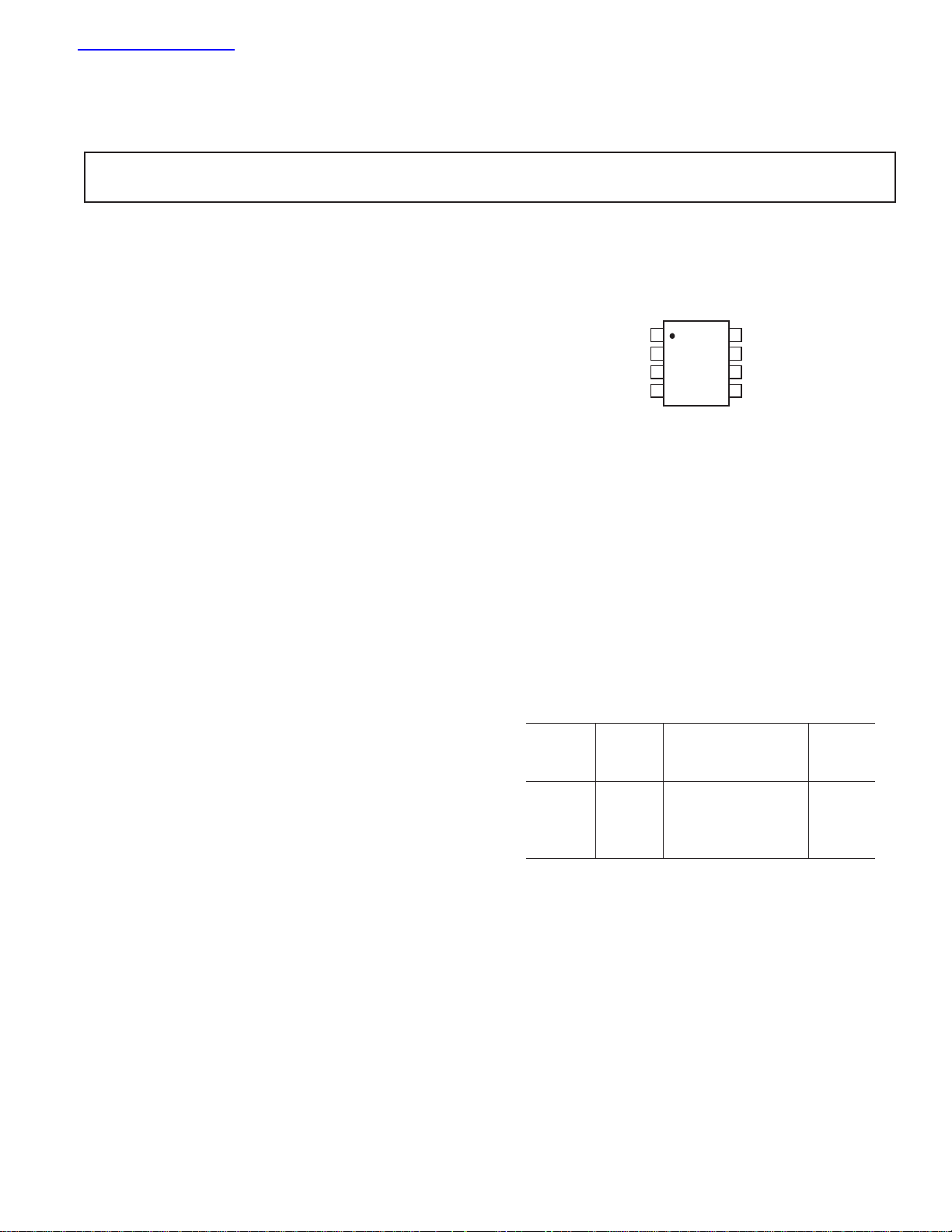

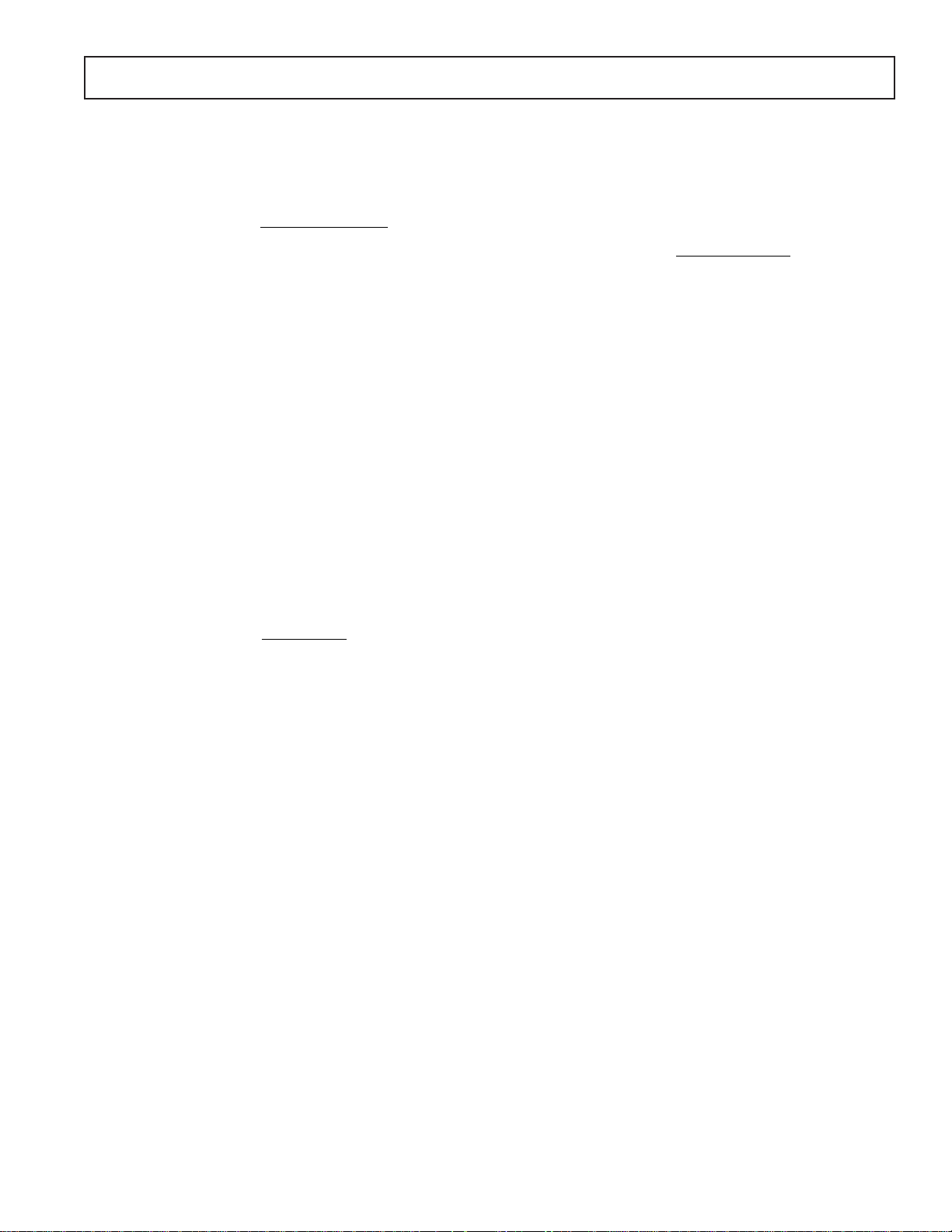

TOP VIEW

(Not to Scale)

8

7

6

5

1

2

3

4

NIC = NO INTERNAL CONNECTION

TP = TEST PIN (DO NOT CONNECT)

TP

V

IN

NIC

GND

TP

NIC

V

OUT

TRIM

ADR42x

查询ADR420供应商

Ultraprecision Low Noise, 2.048 V/2.500 V/

a

FEATURES

Low Noise (0.1 Hz to 10 Hz)

ADR420: 1.75 V p-p

ADR421: 1.75 V p-p

ADR423: 2.0 V p-p

ADR425: 3.4 V p-p

Low Temperature Coefficient: 3 ppm/C

Long-Term Stability: 50 ppm/1000 Hours

Load Regulation: 70 ppm/mA

Line Regulation: 35 ppm/V

Low Hysteresis: 40 ppm Typical

Wide Operating Range

ADR420: 4 V to 18 V

ADR421: 4.5 V to 18 V

ADR423: 5 V to 18 V

ADR425: 7 V to 18 V

Quiescent Current: 0.5 mA Maximum

High Output Current: 10 mA

Wide Temperature Range: –40C to +125C

APPLICATIONS

Precision Data Acquisition Systems

High-Resolution Converters

Battery-Powered Instrumentation

Portable Medical Instruments

Industrial Process Control Systems

Precision Instruments

Optical Network Control Circuits

3.00 V/5.00 V XFET

ADR420/ADR421/ADR423/ADR425

PIN CONFIGURATION

Surface-Mount Packages

®

Voltage References

8-Lead SOIC

8-Lead Mini_SOIC

GENERAL DESCRIPTION

The ADR42x series are ultraprecision second-generation XFET

voltage references featuring low noise, high accuracy, and excellent

long-term stability in a SOIC and Mini_SOIC footprints. Patented

temperature drift curvature correction technique and XFET (eXtra

implanted junction FET) technology minimize nonlinearity of the

voltage change with temperature. The XFET architecture offers

superior accuracy and thermal hysteresis to the bandgap

references. It also operates at lower power and lower supply

headroom than the Buried Zener references.

The superb noise, stable, and accurate characteristics of ADR42x

make them ideal for precision conversion applications such as

optical network and medical equipment. The ADR42x trim

terminal can also be used to adjust the output voltage over a

±0.5% range without compromising any other performance. The

ADR42x series voltage references offer two electrical grades and

are specified over the extended industrial temperature range

of –40°C to +125°C. Devices are available in 8-lead SOIC-8 or

30% smaller 8-lead Mini_SOIC-8 packages.

XFET is a registered trademark of Analog Devices, Inc.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

Table I. ADR42x Products

Output Initial

ADR420 Voltage Accuracy Tempco

Products V

O

mV % ppm/°C

ADR420 2.048 1, 3 0.05, 0.15 3, 10

ADR421 2.50 1, 3 0.04, 0.12 3, 10

ADR423 3.00 1.5, 4 0.04, 0.12 3, 10

ADR425 5.00 2, 6 0.04, 0.12 3, 10

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

Page 2

ADR42x–SPECIFICATIONS

ADR420 ELECTRICAL SPECIFICATIONS

(@ VIN = 5.0 V to 15.0 V, TA = 25C, unless otherwise noted.)

Parameter Symbol Conditions Min Typ Max Unit

Output Voltage A Grade V

Initial Accuracy V

O

OERR

2.045 2.048 2.051 V

–3 +3 mV

–0.15 +0.15 %

Output Voltage B Grade V

Initial Accuracy V

O

OERR

2.047 2.048 2.049 V

–1 +1 mV

–0.05 +0.05 %

Temperature Coefficient A Grade TCV

O

–40°C < TA < +125°C 2 10 ppm/°C

B Grade 1 3 ppm/°C

Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Voltage Noise Density e

Turn-On Settling Time t

Long-Term Stability ∆V

Output Voltage Hysteresis V

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Specifications subject to change without notice.

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

p-p 0.1 Hz to 10 Hz 1.75 µV p-p

N

N

R

O

O_HYS

SC

VIN = 5 V to 18 V 10 35 ppm/V

–40°C < T

I

LOAD

–40°C < T

< +125°C

A

= 0 mA to 10 mA 70 ppm/mA

< +125°C

A

No Load 390 500 µA

–40°C < T

< +125°C 600 µA

A

1 kHz 60 nV/√Hz

1,000 Hours 50 ppm

= 10 kHz 75 dB

IN

2V

10 µs

40 ppm

27 mA

ADR421 ELECTRICAL SPECIFICATIONS

(@ VIN = 5.0 V to 15.0 V, TA = 25C, unless otherwise noted.)

Parameter Symbol Conditions Min Typ Max Unit

Output Voltage A Grade V

Initial Accuracy V

O

OERR

2.497 2.500 2.503 V

–3 +3 mV

–0.12 +0.12 %

Output Voltage B Grade V

Initial Accuracy V

O

OERR

2.499 2.500 2.501 V

–1 +1 mV

–0.04 +0.04 %

Temperature Coefficient A Grade TCV

O

–40°C < TA < +125°C 2 10 ppm/°C

B Grade 1 3 ppm/°C

Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Voltage Noise Density e

Turn-On Settling Time t

Long-Term Stability ∆V

Output Voltage Hysteresis V

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

p-p 0.1 Hz to 10 Hz 1.75 µV p-p

N

N

R

O

O_HYS

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Specifications subject to change without notice.

SC

VIN = 5 V to 18 V 10 35 ppm/V

–40°C < T

I

LOAD

–40°C < T

< +125°C

A

= 0 mA to 10 mA 70 ppm/mA

< +125°C

A

No Load 390 500 µA

–40°C < T

< +125°C 600 µA

A

1 kHz 80 nV/√Hz

1,000 Hours 50 ppm

= 10 kHz 75 dB

IN

2V

10 µs

40 ppm

27 mA

–2–

REV. B

Page 3

ADR420/ADR421/ADR423/ADR425

ADR423 ELECTRICAL SPECIFICATIONS

(@ VIN = 5.0 V to 15.0 V, TA = 25C, unless otherwise noted.)

Parameter Symbol Conditions Min Typ Max Unit

Output Voltage A Grade V

Initial Accuracy V

O

OERR

2.996 3.000 3.004 V

–4 +4 mV

–0.13 +0.13 %

Output Voltage B Grade V

Initial Accuracy V

O

OERR

2.9985 3.000 3.0015 V

–1.5 +1.5 mV

–0.04 +0.04 %

Temperature Coefficient A Grade TCV

O

–40°C < TA < +125°C 2 10 ppm/°C

B Grade 1 3 ppm/°C

Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Voltage Noise Density e

Turn-On Settling Time t

Long-Term Stability ∆V

Output Voltage Hysteresis V

− V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

p-p 0.1 Hz to 10 Hz 2 µV p-p

N

N

R

O

O_HYS

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Specifications subject to change without notice.

SC

VIN = 5 V to 18 V 10 35 ppm/V

–40°C < T

I

LOAD

–40°C < T

< +125°C

A

= 0 mA to 10 mA 70 ppm/mA

< +125°C

A

No Load 390 500 µA

–40°C < T

< +125°C 600 µA

A

1 kHz 90 nV/√Hz

1,000 Hours 50 ppm

= 10 kHz 75 dB

IN

2V

10 µs

40 ppm

27 mA

ADR425 ELECTRICAL SPECIFICATIONS

(@ VIN = 7.0 V to 15.0 V, TA = 25C, unless otherwise noted.)

Parameter Symbol Conditions Min Typ Max Unit

Output Voltage A Grade V

Initial Accuracy V

O

OERR

4.994 5.000 5.006 V

–6 +6 mV

–0.12 +0.12 %

Output Voltage B Grade V

Initial Accuracy V

O

OERR

4.998 5.000 5.002 V

–2 +2 mV

–0.04 +0.04 %

Temperature Coefficient A Grade TCV

O

–40°C < TA < +125°C 2 10 ppm/°C

B Grade 1 3 ppm/°C

Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Voltage Noise Density e

Turn-On Settling Time t

Long-Term Stability ∆V

Output Voltage Hysteresis V

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

p-p 0.1 Hz to 10 Hz 3.4 µV p-p

N

N

R

O

O_HYS

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Specifications subject to change without notice.

SC

VIN = 7 V to 18 V 10 35 ppm/V

–40°C < T

I

LOAD

–40°C < T

< +125°C

A

= 0 mA to 10 mA 70 ppm/mA

< +125°C

A

No Load 390 500 µA

–40°C < T

< +125°C 600 µA

A

1 kHz 110 nV/√Hz

1,000 Hours 50 ppm

= 10 kHz 75 dB

IN

2V

10 µs

40 ppm

27 mA

REV. B

–3–

Page 4

A

WARNING!

ESD SENSITIVE DEVICE

DR420/ADR421/ADR423/ADR425

ABSOLUTE MAXIMUM RATINGS

*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V

Output Short-Circuit Duration to GND . . . . . . . . . Indefinite

Storage Temperature Range

R, RM Packages . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

ADR42x . . . . . . . . . . . . . . . . . . . . . . . . . . –40°C to +125°C

Junction Temperature Range

R, RM Packages . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . 300°C

*Absolute maximum ratings apply at 25°C, unless otherwise noted.

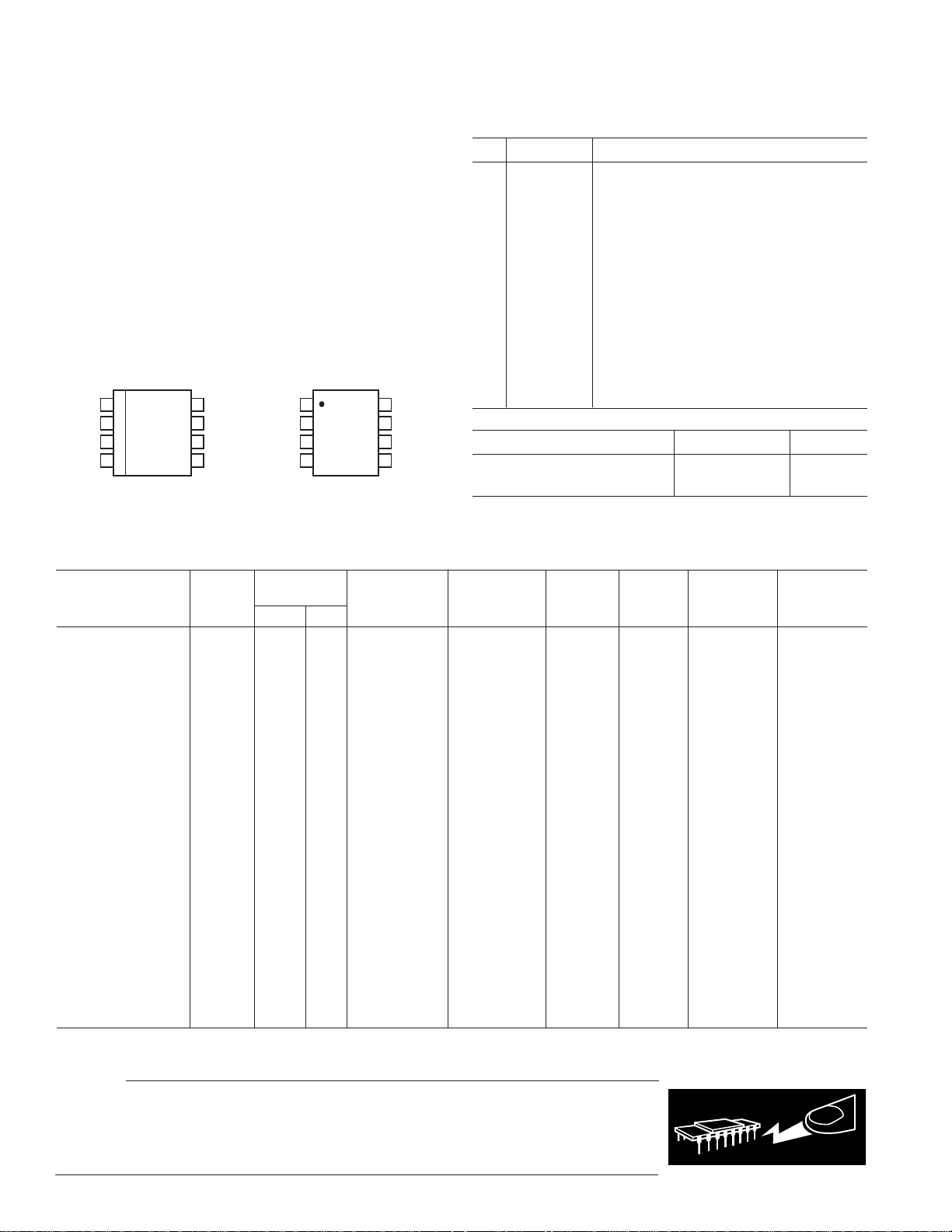

PIN CONFIGURATIONS

SOIC-8

1

TP

ADR42x

2

V

IN

NIC

3

4

GND

NIC = NO INTERNAL CONNECTION

TP = TEST PIN (DO NOT CONNECT)

8

TP

7

NIC

6

V

OUT

TRIM

5

Mini_SOIC-8

1

TP

ADR42x

2

V

IN

3

NIC

4

GND

NIC = NO INTERNAL CONNECTION

TP = TEST PIN (DO NOT CONNECT)

8

TP

7

NIC

6

V

OUT

TRIM

5

ORDERING GUIDE

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Description

1, 8 TP Test Pin. There are actual connections in TP

pins but they are reserved for factory testing

purposes. Users should not connect anything to TP pins, otherwise the device may

not function properly.

2V

IN

Input Voltage

3, 7 NIC No Internal Connect. NICs have no internal

connections.

4 GND Ground Pin = 0 V

5 TRIM Trim Terminal. It can be used to adjust the

output voltage over a ±0.5% range without

affecting the temperature coefficient.

6V

OUT

Package Type θ

Output Voltage

*

JA

Unit

8-Lead Mini_SOIC (RM) 190 °C/W

8-Lead SOIC (R) 130 °C/W

*θJA is specified for the worst-case conditions, i.e., θJA is specified for device soldered

in circuit board for surface-mount packages.

Output Initial Temperature Number of

Temperature

Voltage Accuracy Coefficient Package Package Top Parts per Range

Model V

O

mV % ppm/°C Description Option Mark Reel °C

ADR420AR 2.048 3 0.15 10 SOIC SO-8 ADR420 98 –40 to +125

ADR420AR-Reel7 2.048 3 0.15 10 SOIC SO-8 ADR420 3,000 –40 to +125

ADR420BR 2.048 1 0.05 3 SOIC SO-8 ADR420 98 –40 to +125

ADR420BR-Reel7 2.048 1 0.05 3 SOIC SO-8 ADR420 3,000 –40 to +125

ADR420ARM-Reel7 2.048 3 0.15 10 Mini_SOIC RM-8 R4A 1,000 –40 to +125

ADR421AR 2.50 3 0.12 10 SOIC SO-8 ADR421 98 –40 to +125

ADR421AR-Reel7 2.50 3 0.12 10 SOIC SO-8 ADR421 3,000 –40 to +125

ADR421BR 2.50 1 0.04 3 SOIC SO-8 ADR421 98 –40 to +125

ADR421BR-Reel7 2.50 1 0.04 3 SOIC SO-8 ADR421 3,000 –40 to +125

ADR421ARM-Reel7 2.50 3 0.12 10 Mini_SOIC RM-8 R5A 1,000 –40 to +125

ADR423AR 3.00 4 0.13 10 SOIC SO-8 ADR423 98 –40 to +125

ADR423AR-Reel7 3.00 4 0.13 10 SOIC SO-8 ADR423 3,000 –40 to +125

ADR423BR 3.00 1.5 0.04 3 SOIC SO-8 ADR423 98 –40 to +125

ADR423BR-Reel7 3.00 1.5 0.04 3 SOIC SO-8 ADR423 3,000 –40 to +125

ADR423ARM-Reel7 3.00 4 0.13 10 Mini_SOIC RM-8 1,000 –40 to +125

ADR425AR 5.00 6 0.12 10 SOIC SO-8 ADR425 98 –40 to +125

ADR425AR-Reel7 5.00 6 0.12 10 SOIC SO-8 ADR425 3,000 –40 to +125

ADR425BR 5.00 2 0.04 3 SOIC SO-8 ADR425 98 –40 to +125

ADR425BR-Reel7 5.00 2 0.04 3 SOIC SO-8 ADR425 3,000 –40 to +125

ADR425ARM-Reel7 5.00 6 0.12 10 Mini_SOIC RM-8 R7A 1,000 –40 to +125

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD42x features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

REV. B

Page 5

ADR420/ADR421/ADR423/ADR425

PARAMETER DEFINITIONS

Temperature Coefficient

The change of output voltage over the operating temperature

range and normalized by the output voltage at 25°C, expressed

in ppm/°C. The equation follows:

TCV ppm C

O

/

=

°

()

VCTT

()– ()

21

OO

°×

25

()(– )

O

21

6

×

10

VT VT

where

V

(25°C) = VO at 25°C

O

V

(T1) = VO at Temperature 1

O

V

(T2) = VO at Temperature 2.

O

Line Regulation

The change in output voltage due to a specified change in input

voltage. It includes the effects of self-heating. Line regulation is

expressed in either percent per volt, parts-per-million per volt,

or microvolts per volt change in input voltage

Load Regulation

The change in output voltage due to a specified change in load

current. It includes the effects of self-heating. Load regulation is

expressed in either microvolts per milliampere, parts-per-million

per milliampere, or ohms of dc output resistance.

Long-Term Stability

Typical shift of output voltage at 25°C on a sample of parts

subjected to operation life test of 1000 hours at 125°C:

∆∆VVt Vt

=

()– ()

OO O

V ppm

()

O

01

Vt Vt

()– ()

OO

01

=×

Vt

()

O

0

10

6

where

V

(t0) = VO at 25°C at Time 0

O

V

(t1) = VO at 25°C after 1,000 hours operation at 125°C.

O

Thermal Hysteresis

Thermal hysteresis is defined as the change of output voltage

after the device is cycled through temperature from +25°C to

–40°C to +125°C and back to +25°C. This is a typical value

from a sample of parts put through such a cycle.

VVCV

__

O HYS O O TC

V ppm

_

O HYS

()

()–

=°

25

VCV

()–

°

25

OOTC

=

VC

()

O

25

_

°

×

10

6

where

V

(25°C) = VO at 25°C

O

V

= VO at 25°C after temperature cycle at +25°C to –40°C

O_TC

to +125°C and back to +25°C.

Input Capacitor

Input capacitors are not required on the ADR42x. There is no

limit for the value of the capacitor used on the input, but a 1 µF to

10 µF capacitor on the input will improve transient response in

applications where the supply suddenly changes. An additional

0.1 µF in parallel will also help to reduce noise from the supply.

Output Capacitor

The ADR42x does not need output capacitors for stability

under any load condition. An output capacitor, typically 0.1 µF,

will filter out any low-level noise voltage and will not affect

the operation of the part. On the other hand, the load transient

response can be improved with an additional 1 µF to 10 µF

output capacitor in parallel. A capacitor here will act as a source

of stored energy for sudden increase in load current. The only

parameter that will degrade, by adding an output capacitor, is

turn-on time and it depends on the size of the capacitor chosen.

REV. B

–5–

Page 6

A

DR420/ADR421/ADR423/ADR425

A

DR42x Series

2.0495

2.0493

2.0491

2.0489

2.0487

– V

2.0485

OUT

V

2.0483

2.0481

2.0479

2.0477

2.0475

–40 –10 20 50 80 110 125

–Typical Performance Characteristics

TEMPERATURE – C

5.0025

5.0023

5.0021

5.0019

5.0017

– V

5.0015

OUT

V

5.0013

5.0011

5.0009

5.0007

5.0005

–40

–10 20 40 80 110 125

TEMPERATURE – C

TPC 1. ADR420 Typical Output Voltage vs. Temperature

2.5015

2.5013

2.5011

2.5009

2.5007

– V

2.5005

OUT

V

2.5003

2.5001

2.4999

2.4997

2.4995

–40 –10 20 50 80 110 125

TEMPERATURE – C

TPC 2. ADR421 Typical Output Voltage vs. Temperature

3.0010

3.0008

3.0006

3.0004

3.0002

– V

3.0000

OUT

V

2.9998

2.9996

2.9994

2.9992

2.9990

–40

–10 20 40 80 110 125

TEMPERATURE – C

TPC 4. ADR425 Typical Output Voltage vs. Temperature

0.55

SUPPLY CURRENT – mA

0.50

0.45

0.40

0.35

0.30

0.25

4

+125C

+25C

–40C

6 8 10 12 14 15

INPUT VOLTAGE – V

TPC 5. ADR420 Supply Current vs. Input Voltage

0.55

0.50

SUPPLY CURRENT – mA

0.45

0.40

0.35

0.30

0.25

4

+125C

+25C

–40C

6 8 10 12 14 15

INPUT VOLTAGE – V

TPC 3. ADR423 Typical Output Voltage vs. Temperature

–6–

TPC 6. ADR421 Supply Current vs. Input Voltage

REV. B

Page 7

ADR420/ADR421/ADR423/ADR425

0.55

0.50

+125C

+25C

–40C

14

SUPPLY CURRENT – mA

0.45

0.40

0.35

0.30

0.25

4

6 8 10 12 15

INPUT VOLTAGE – V

TPC 7. ADR423 Supply Current vs. Input Voltage

0.55

0.50

0.45

0.40

0.35

SUPPLY CURRENT – mA

0.30

+125C

+25C

–40C

70

IL = 0mA TO 5mA

60

50

VIN = 5V

40

30

20

LOAD REGULATION – ppm/mA

10

0

–40

VIN = 6.5V

–10 20 50 80 110 125

TEMPERATURE – C

TPC 10. ADR421 Load Regulation vs. Temperature

70

60

50

40

30

20

LOAD REGULATION – ppm/mA

10

V

V

= 7V

IN

= 15V

IN

IL = 0mA TO 10mA

0.25

6

81012 15

INPUT VOLTAGE – V

14

TPC 8. ADR425 Supply Current vs. Input Voltage

70

IL = 0mA TO 5mA

60

VIN = 4.5V

50

40

VIN = 6V

30

20

LOAD REGULATION – ppm/mA

10

0

–40

–10 20 50 80 110 125

TEMPERATURE – C

TPC 9. ADR420 Load Regulation vs. Temperature

0

–40

–10 20 40 80 110 125

TEMPERATURE – C

TPC 11. ADR423 Load Regulation vs. Temperature

35

30

25

20

15

10

LOAD REGULATION – ppm/mA

5

0

–40

–10 20 40 80 110 125

TEMPERATURE – C

VIN = 15V

I

= 0mA TO 10mA

L

TPC 12. ADR425 Load Regulation vs. Temperature

REV. B

–7–

Page 8

A

DR420/ADR421/ADR423/ADR425

6

VIN = 4.5V TO 15V

5

4

3

2

LINE REGULATION – ppm/V

1

0

–40 –10 20 50 80 110

TEMPERATURE – C

125

TPC 13. ADR420 Line Regulation vs. Temperature

6

VIN = 5V TO 15V

5

4

3

2

LINE REGULATION – ppm/V

1

14

12

10

8

6

4

LINE REGULATION – ppm/V

2

0

–40

–10 20 50 80 110

TEMPERATURE – C

VIN = 7.5V TO 15V

125

TPC 16. ADR425 Line Regulation vs. Temperature

2.5

2.0

–40C

+25C

1.5

+85C

1.0

DIFFERENTIAL VOLTAGE – V

0.5

0

–40 –10 20 50 80 110

TEMPERATURE – C

125

TPC 14. ADR421 Line Regulation vs. Temperature

9

8

7

6

5

4

3

LINE REGULATION – ppm/V

2

1

0

–40

–10 20 50 80 110

TEMPERATURE – C

VIN = 5V TO 15V

TPC 15. ADR423 Line Regulation vs. Temperature

0

0

12345

LOAD CURRENT – mA

TPC 17. ADR420 Minimum Input-Output Voltage

Differential vs. Load Current

2.5

2.0

–40C

+25C

1.5

+125C

1.0

DIFFERENTIAL VOLTAGE – V

0.5

0

0

12345

LOAD CURRENT – mA

TPC 18. ADR421 Minimum Input-Output Voltage

Differential vs. Load Current

–8–

REV. B

Page 9

ADR420/ADR421/ADR423/ADR425

2.5

2.0

–40C

1.5

1.0

DIFFERENTIAL VOLTAGE – V

0.5

0

0

12345

+25C

+125C

LOAD CURRENT – mA

1V/DIV

TIME – 1s/DIV

TPC 19. ADR423 Minimum Input-Output Voltage

Differential vs. Load Current

2.5

2.0

–40C

1.5

1.0

DIFFERENTIAL VOLTAGE – V

0.5

0

0

12345

+25C

+125C

LOAD CURRENT – mA

TPC 20. ADR425 Minimum Input-Output Voltage

Differential vs. Load Current

30

TEMPERATURE

+25C –40C

+125C +25C

25

SAMPLE SIZE – 160

TPC 22. ADR421 Typical Noise Voltage

0.1 Hz to 10 Hz

50V/DIV

TIME – 1s/DIV

TPC 23. Typical Noise Voltage 10 Hz to 10 kHz

1k

REV. B

20

15

FREQUENCY

10

5

0

0

–100

–90

–80

–70

–60

–50

–40

–30

102030405060708090

–20

–10

DEVIATION – ppm

TPC 21. ADR421 Typical Hysteresis

100

110

120

ADR425

100

VOLTAGE NOISE DENSITY

10

130

MORE

10

100 1k 10k

FREQUENCY – Hz

ADR420

ADR423

ADR421

TPC 24. Voltage Noise Density vs. Frequency

–9–

Page 10

A

DR420/ADR421/ADR423/ADR425

C

= 0F

BYPASS

V

IN

V

OUT

TIME – 100s/DIV

LINE INTERRUPTION

500mV/DIV

500mV/DIV

TPC 25. ADR421 Line Transient Response

C

= 0.1F

BYPASS

V

IN

LINE INTERRUPTION

500mV/DIV

CL = 100nF

V

OUT

LOAD ON

LOAD OFF

TIME – 100s/DIV

1mA LOAD

1V/DIV

2V/DIV

TPC 28. ADR421 Load Transient Response

CIN = 0.01F

NO LOAD

V

2V/DIV

OUT

V

OUT

TIME – 100s/DIV

500mV/DIV

TPC 26. ADR421 Line Transient Response

CL = 0F

V

OUT

LOAD ON

LOAD OFF

TIME – 100s/DIV

1mA LOAD

1V/DIV

2V/DIV

TPC 27. ADR421 Load Transient Response

V

2V/DIV

IN

TIME – 4s/DIV

TPC 29. ADR421 Turn-Off Response

CIN = 0.01F

NO LOAD

2V/DIV

V

OUT

V

2V/DIV

IN

TIME – 4s/DIV

TPC 30. ADR421 Turn-On Response

–10–

REV. B

Page 11

ADR420/ADR421/ADR423/ADR425

C

= 0.01F

LOAD

NO INPUT CAP

2V/DIV

V

OUT

V

2V/DIV

IN

TIME – 4s/DIV

TPC 31. ADR421 Turn-Off Response

C

= 0.01F

LOAD

NO INPUT CAP

2V/DIV

V

OUT

V

2V/DIV

IN

50

45

40

35

30

25

20

15

OUTPUT IMPEDANCE –

10

5

10

100

1k 10k

FREQUENCY – Hz

ADR425

ADR423

ADR421

TPC 34. Output Impedance vs. Frequency

–10

–20

–30

–40

–50

–60

–70

RIPPLE REJECTION – dB

–80

–90

ADR420

100k

TIME – 4s/DIV

TPC 32. ADR421 Turn-On Response

C

= 0.1F

BYPASS

RL = 500

CL = 0

V

OUT

V

IN

TIME – 100s/DIV

5V/DIV

2V/DIV

TPC 33. ADR421 Turn-On/Turn-Off Response

10 1M100

1k 10k 100k

FREQUENCY – Hz

TPC 35. Ripple Rejection vs. Frequency

REV. B

–11–

Page 12

A

DR420/ADR421/ADR423/ADR425

THEORY OF OPERATION

The ADR42x series of references uses a new reference generation

technique known as XFET (eXtra implanted junction FET).

This technique yields a reference with low supply current, good

thermal hysteresis, and exceptionally low noise. The core of the

XFET reference consists of two junction field-effect transistors

(JFET), one of which has an extra channel implant to raise its

pinch-off voltage. By running the two JFETs at the same drain

current, the difference in pinch-off voltage can be amplified and

used to form a highly stable voltage reference.

The intrinsic reference voltage is around 0.5 V with a negative

temperature coefficient of about –120 ppm/°C. This slope is

essentially constant to the dielectric constant of silicon and can

be closely compensated by adding a correction term generated

in the same fashion as the proportional-to-temperature (PTAT)

term used to compensate bandgap references. The big advantage

over a bandgap reference is that the intrinsic temperature

coefficient is some thirty times lower (therefore requiring less

correction), resulting in much lower noise since most of the

noise of a bandgap reference comes from the temperature

compensation circuitry.

Figure 1 shows the basic topology of the ADR42x series. The

temperature correction term is provided by a current source with a

value designed to be proportional to absolute temperature. The

general equation is:

P

(1)

is

VGVRI

=× − ×()∆ 1

OUT P PTAT

where G is the gain of the reciprocal of the divider ratio, ∆V

the difference in pinch-off voltage between the two JFETs, and

I

is the positive temperature coefficient correction current.

PTAT

ADR42x are created by on-chip adjustment of R2 and R3 to

achieve 2.048 V or 2.500 V at the reference output respectively.

V

R2

R3

GND

IN

V

OUT

I

I

PTAT

1

*

*EXTRA CHANNEL IMPLANT

V

= G(VP – R1 I

OUT

I

1

V

P

R1

PTAT)

ADR42x

Figure 1. Simplified Schematic

Device Power Dissipation Considerations

The ADR42x family of references is guaranteed to deliver load

currents to 10 mA with an input voltage that ranges from 4.5 V

to 18 V. When these devices are used in applications at higher

current, users should account for the temperature effects due to

the power dissipation increases with the following equation:

TP T

=× +θ

DAAJJ

(2)

Basic Voltage Reference Connections

Voltage references, in general, require a bypass capacitor

connected from V

to GND. The circuit in Figure 2

OUT

illustrates the basic configuration for the ADR42x family of

references. Other than a 0.1 µF capacitor at the output to help

improve noise suppression, a large output capacitor at the

output is not required for circuit stability.

1

TP

V

IN

+

10F

0.1F

2

ADR42x

3

TOP VIEW

NIC

(Not to Scale)

4

NIC = NO INTERNAL CONNECTION

TP = TEST PIN

(DO NOT CONNECT)

8

7

6

5

TP

NIC

OUTPUT

TRIM

0.1F

Figure 2. Basic Voltage Reference Configuration

Noise Performance

The noise generated by the ADR42x family of references is

typi

cally less than 2 µV p-p over the 0.1 Hz to 10 Hz band

ADR420, ADR421, and ADR423. TPC 22 shows the 0.1

for

Hz to

10 Hz noise of the ADR421, which is only 1.75 µV p-p.

The noise

a

measurement is made with a bandpass filter made of

2-pole high-pass filter with a corner frequency at 0.1 Hz and

a 2-pole low-pass filter with a corner frequency at 10 Hz.

Turn-On Time

Upon application of power (cold start), the time required for the

output voltage to reach its final value within a specified error

band is defined as the turn-on settling time. Two components

normally associated with this are the time for the active circuits

to settle, and the time for the thermal gradients on the chip to

stabilize. TPC 29 through TPC 33, inclusive, show the turn-on

settling time for the ADR421.

APPLICATIONS SECTION

OUTPUT ADJUSTMENT

The ADR42x trim terminal can be used to adjust the output voltage

over a ±0.5% range. This feature allows the system designer to

trim system errors out by setting the reference to a voltage other

than the nominal. This is also helpful if the part is used in a system

at temperature to trim out any error. Adjustment of the output has

negligible effect on the temperature performance of the device.

To avoid degrading temperature coefficient, both the

potentiometer and the two resistors need to be low

trimming

temperature

coefficient types, preferably <100 ppm/°C.

INPUT

V

IN

V

ADR42x

TRIM

GND

O

R1

470k

OUTPUT

Rp

10k

10k (ADR420)

R2

15k (ADR421)

VO = 0.5%

where T

respectively, P

and TA are the junction and ambient temperatures,

J

is the device power dissipation, and θJA is the

D

device package thermal resistance.

–12–

Figure 3. Output Trim Adjustment

REV. B

Page 13

Reference for Converters in Optical Network Control Circuits

In the upcoming high-capacity, all-optical router network, Figure 4

employs arrays of micromirrors to direct and route optical

signals from fiber to fiber, without first converting them to

electrical form, which reduces the communication speed. The tiny

micromechanical mirrors are positioned so that each is illuminated

by a single wavelength that carries unique information and can be

passed to any desired input and output fiber. The mirrors are tilted

by the dual-axis actuators controlled by precision ADCs and

DACs within the system. Due to the microscopic movement of

the mirrors, not only is the precision of the converters important,

but the noise associated with these controlling converters is also

extremely critical, because total noise within the system can

be multiplied by the numbers of converters employed. As a result,

the ADR42x is necessary for this application for its exceptional

low noise to maintain the stability of the control loop.

SOURCE FIBER

LASER BEAM

ACT IVATO R

CONTROL

ELECTRONICS

GIMBAL + SENSOR

LEFT

DAC DACADC

MEMS MIRROR

PREAMPAMPL AMPL

DESTINATION

FIBER

ACT IVATO R

RIGHT

ADR421

ADR421

ADR421

ADR420/ADR421/ADR423/ADR425

+V

DD

2

V

IN

V

6

OUT

ADR42x

GND

4

A1

DD

A1 = OP777, OP193

–V

Figure 5. Negative Reference

High-Voltage Floating Current Source

The circuit of Figure 6 can be used to generate a floating current

source with minimal self-heating. This particular configuration

can operate on high supply voltages determined by the breakdown

voltage of the N-channel JFET.

V

IN

ADR42x

V

OUT

OP90

GND

–V

REF

+V

S

SST111

VISHAY

2N3904

R

L

2.10k

DSP

Figure 4. All-Optical Router Network

A Negative Precision Reference without Precision Resistors

In many current-output CMOS DAC applications, where the

output signal voltage must be of the same polarity as the reference

voltage, it is often required to reconfigure a current-switching

DAC into a voltage-switching DAC through the use of a 1.25 V

reference, an op amp, and a pair of resistors. Using a currentswitching DAC directly requires the need for an additional

operational amplifier at the output to reinvert the signal. A

negative voltage reference is then desirable from the point that

an additional operational amplifier is not required for either

reinversion (current-switching mode) or amplification (voltageswitching mode) of the DAC output voltage. In general, any

positive voltage reference can be converted into a negative voltage

reference through the use of an operational amplifier and a pair of

matched resistors in an inverting configuration. The disadvantage

to that approach is that the largest single source of error in the

circuit is the relative matching of the resistors used.

A negative reference can easily be generated by adding a precision

op amp and configuring as in Figure 5. V

is at virtual ground

OUT

and, therefore, the negative reference can be taken directly from

the output of the op amp. The op amp must be dual supply, low

offset, and have rail-to-rail capability if negative supply voltage

is close to the reference output.

–V

S

Figure 6. High-Voltage Floating Current Source

Kelvin Connections

In many portable instrumentation applications, where PC board

cost and area go hand-in-hand, circuit interconnects are very

often of dimensionally minimum width. These narrow lines can

cause large voltage drops if the voltage reference is required to

provide load currents to various functions. In fact, a circuit’s

interconnects can exhibit a typical line resistance of 0.45 mΩ/

square (1 oz. Cu, for example). Force and sense connections,

also referred to as Kelvin connections, offer a convenient method

of eliminating the effects of voltage drops in circuit wires. Load

currents flowing through wiring resistance produce an error

(V

= R × IL ) at the load. However, the Kelvin connection

ERROR

of Figure 7 overcomes the problem by including the wiring

resistance within the forcing loop of the op amp. Since the op

amp senses the load voltage, op amp loop control forces the

output to compensate for the wiring error and to produce the

correct voltage at the load.

V

IN

2

ADR42x

V

OUT

GND

4

6

R

LW

V

IN

R

A1

A1 = OP191

V

OUT

SENSE

LW

V

OUT

FORCE

R

L

REV. B

Figure 7. Advantage of Kelvin Connection

–13–

Page 14

A

DR420/ADR421/ADR423/ADR425

Dual Polarity References

V

IN

1F 0.1F

2

V

IN

ADR425

GND

4

V

6

OUT

R1

TRIM

5

10k

R3

5k

U1

+10V

V+

OP1177

U2

V–

–10V

10k

+5V

R2

–5V

Figure 8. +5 V and –5 V Reference Using ADR425

+2.5V

+10V

2

V

V

IN

ADR425

GND

4

6

OUT

5

5.6k

5.6k

R1

R2

–2.5V

V+

OP1177

U2

V–

–10V

U1

TRIM

Figure 9. +2.5 V and –2.5 V Reference Using ADR425

Dual polarity references can easily be made with an op amp and

a pair of resistors. In order not to defeat the accuracy obtained

by ADR42x, it is imperative to match the resistance tolerance as

well as the temperature coefficient of all the components.

Programmable Current Source

C1

10pF

V

DD

2

V

IN

ADR425

U1

GND

4

TRIM

V

OUT

5

AD5232

DIGITAL POT

6

U2

U2

A

BW

V

DD

V+

OP2177

A1

V–

V

SS

R1’

50k

C2

10pF

R1

50k

R2’

1k

V

DD

V+

OP2177

A2

V–

V

SS

R2

1k

VL

R2

B

10

A

LOAD

IL

Figure 10. Programmable Current Source

Together with a digital potentiometer and a Howland current

pump, ADR425 forms the reference source for a programmable

current as

RR

+×22

AB

R

I

L

1

R

2

B

V

W=

(3)

and

D

V

W

V

×

=

N

REF

2

(4)

where

D = Decimal Equivalent of the Input Code

N = Number of Bits

In addition, R1' and R2' must be equal to R1 and R2

respectively. R2

in theory can be made as small as needed to

B

achieve the current needed within A2 output current

+ R2B,

A

driving

capability. In this example, OP2177 is able to deliver a maximum of 10 mA. Since the current pump employs both

negative feedback, capacitors C1 and C2 are needed to

positive

and

ensure the

negative feedback prevails and, therefore, avoids oscillation.

This circuit also allows bidirectional current flow if the inputs

and VB of the digital potentiometer are supplied with the

V

A

dual polarity references as shown previously.

Programmable DAC Reference Voltage

With a multichannel DAC such as a Quad 12-bit voltage output

DAC AD7398, one of its internal DACs and an ADR42x voltage

reference can be served as a common programmable V

REFX

for the

rest of the DACs. The circuit configuration is shown in Figure 11.

The relationship of V

REFX

to V

depends upon the digital code

REF

and the ratio of R1 and R2 and is given by:

V

REFX

V

REF

=

1

×+

DR

+×

N

2

2

R

1

1

R

2

1

R

(5)

where

D = Decimal Equivalent of Input Code and

N = Number of Bits

= Applied External Reference

V

REF

= Reference Voltage for DAC A to D

V

REFX

–14–

REV. B

Page 15

ADR420/ADR421/ADR423/ADR425

AD8601

V

IN

V

O

R

L

25

N1

2U1

V

IN

GND

4

5

6

U2

2N7002

5V

V+

V–

ADR421

V

OUT

TRIM

Table III. V

R1, R2 Digital Code V

R1 = R2 0000 0000 0000 2 V

R1 = R2 1000 0000 0000 1.3 V

R1 = R2 1111 1111 1111 V

R1 = 3R2 0000 0000 0000 4 V

R1 = 3R2 1000 0000 0000 1.6 V

R1 = 3R2 1111 1111 1111 V

V

REFA

DACA

V

REFB

DACB

V

REFC

DACC

V

REFD

DACD

vs. R1 and R2

REFX

V

OUTA

V

IN

V

OUTB

V

OUTC

V

OUTD

R1

0.1%

ADR425

VOB = V

= V

V

OC

= V

V

OD

REF

REF

REF

REF

REF

R2

0.1%

V

REF

REFX

REFX

REFX

REF

REF

(DB)

(DC)

(DD)

AD7398

Figure 11. Programmable DAC Reference

Precision Voltage Reference for Data Converters

The ADR42x family has a number of features that make it ideal

for use with A/D and D/A converters. The exceptional low noise,

tight temperature coefficient, and high accuracy characteristics

make the ADR42x ideal for low noise applications such as cellular

base station applications.

Another example of ADC for which the ADR421 is also well-suited

is the AD7701. Figure 12 shows the ADR421 used as the precision

reference for this converter. The AD7701 is a 16-bit A/D converter

with on-chip digital filtering intended for the measurement of wide

dynamic range and low frequency signals such as those representing

chemical, physical, or biological processes. It contains a chargebalancing (sigma-delta) ADC, calibration microcontroller with on-chip

static RAM, a clock oscillator, and a serial communications port.

+5V

ANALOG

SUPPLY

RANGES

SELECT

CALIBRATE

ANALOG

INPUT

ANALOG

GROUND

–5V

ANALOG

SUPPLY

0.1F

0.1F

0.1F10F

10F

V

IN

V

ADR42x

GND

0.1F

OUT

AV

DD

V

REF

BP/UP

CAL

A

IN

AGND

AV

SS

AD7701

DV

SLEEP

MODE

DRDV

CS

SCLK

SDATA

CLKIN

CLKOUT

SC1

SC2

DGND

DV

DD

0.1F

DATA READY

READ (TRANSMIT)

SERIAL CLOCK

SERIAL CLOCK

0.1F

SS

Figure 12. Voltage Reference for 16-Bit A/D Converter

AD7701

Precision Boosted Output Regulator

A precision voltage output with boosted current capability can

be realized with the circuit shown in Figure 13. In this circuit,

U

forces VO to be equal to V

2

, therefore, the load current will be furnished by VIN. In this

N

1

configuration, a 50 mA load is achievable at V

by regulating the turn on of

REF

of 5 V. Moder-

IN

ate heat will be generated on the MOSFET and higher current

can be achieved with a replacement of the larger device. In

addition, for heavy capacitive load with step input, a buffer may

be added at the output to enhance the transient response.

Figure 13. Precision Boosted Output Regulator

REV. B

–15–

Page 16

ADR420/ADR421/ADR423/ADR425

Dimensions shown in inches and (mm).

0.1968 (5.00)

0.1890 (4.80)

PIN 1

SEATING

PLANE

85

1

0.0500 (1.27)

0.122 (3.10)

0.114 (2.90)

0.1574 (4.00)

0.1497 (3.80)

0.0098 (0.25)

0.0040 (0.10)

NOTES

1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS

2. ALL DIMENSIONS PER JEDEC STANDARDS MS-012 AA

OUTLINE DIMENSIONS

8-Lead Narrow Body SOIC

(R-8)

0.2440 (6.20)

0.2284 (5.80)

4

BSC

0.020 (0.51)

0.013 (0.33)

0.0688 (1.75)

0.0532 (1.35)

0.0098 (0.25)

0.0075 (0.19)

8

0

8-Lead Mini_SOIC

(RM-8)

0.0196 (0.50)

0.0099 (0.25)

0.050 (1.27)

0.016 (0.40)

45

C02432–0–3/02(B)

PIN 1

0.0256 (0.65) BSC

SEATING

PLANE

85

0.120 (3.05)

0.112 (2.84)

0.018 (0.46)

0.008 (0.20)

0.199 (5.05)

0.187 (4.75)

41

0.043 (1.09)

0.037 (0.94)

0.011 (0.28)

0.003 (0.08)

0.120 (3.05)

0.112 (2.84)

33

27

0.028 (0.71)

0.016 (0.41)

0.122 (3.10)

0.114 (2.90)

0.006 (0.15)

0.002 (0.05)

Revision History

Location Page

03/02—Data Sheet changed from REV. A to REV. B.

Edits to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Deletion of Precision Voltage Regulator section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Addition of Precision Boosted Output Regulator section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Addition of Figure 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Data Sheet changed from REV. 0 to REV. A.

Addition of ADR423 and ADR425 to ADR420/ADR421 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Universal

PRINTED IN U.S.A.

–16–

REV. B

Loading...

Loading...