Page 1

Precision Low Drift 2.048 V/2.500 V

a

FEATURES

Initial Accuracy: ⴞ6 mV Max

Low TCV

Load Regulation: 60 ppm/mA

Line Regulation: 25 ppm/V

Wide Operating Range:

2.4 V–18 V for ADR390

2.8 V–18 V for ADR391

Low Power: 120 A Max

Shutdown to Less than 3 A Max

High Output Current: 5 mA Min

Wide Temperature Range: ⴚ40ⴗC to +85ⴗC

Tiny SOT-23-5 Package

APPLICATIONS

Battery-Powered Instrumentation

Portable Medical Instruments

Data Acquisition Systems

Industrial and Process Control Systems

Hard Disk Drives

Automotive

: 25 ppm/ⴗC Max

O

SOT-23 Voltage References with Shutdown

ADR390/ADR391

PIN CONFIGURATION

5-Lead SOT-23

(RT Suffix)

1

SHDN

V

OUT(SENSE)

ADR390/

V

2

IN

ADR391

3

Table I.

Part Number Nominal Output Voltage (V)

ADR390 2.048

ADR391 2.500

5

GND

4

V

OUT(FORCE)

GENERAL DESCRIPTION

The ADR390 and ADR391 are precision 2.048 V and 2.5 V

bandgap voltage references featuring high accuracy and stability

and low power consumption in a tiny footprint. Patented temperature drift curvature correction techniques minimize nonlinearity of

the voltage change with temperature. The wide operating range

and low power consumption with additional shutdown capability

make them ideal for 3 V to 5 V battery-powered applications. The

Sense Pin enables greater accuracy by supporting full Kelvin

V

OUT

operation in systems using very fine or long circuit traces.

The ADR390 and ADR391 are micropower, Low Dropout Voltage

(LDV) devices that provide a stable output voltage from supplies as

low as 300 mV above the output voltage. They are specified over the

industrial (–40°C to +85°C) temperature range. Each is available

in the tiny 5-lead SOT-23 package.

The combination of V

sense and shutdown functions also

OUT

enables a number of unique applications combining precision

reference/regulation with fault decision and over-current protection. Details are provided in the applications section.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

Page 2

ADR390/ADR391

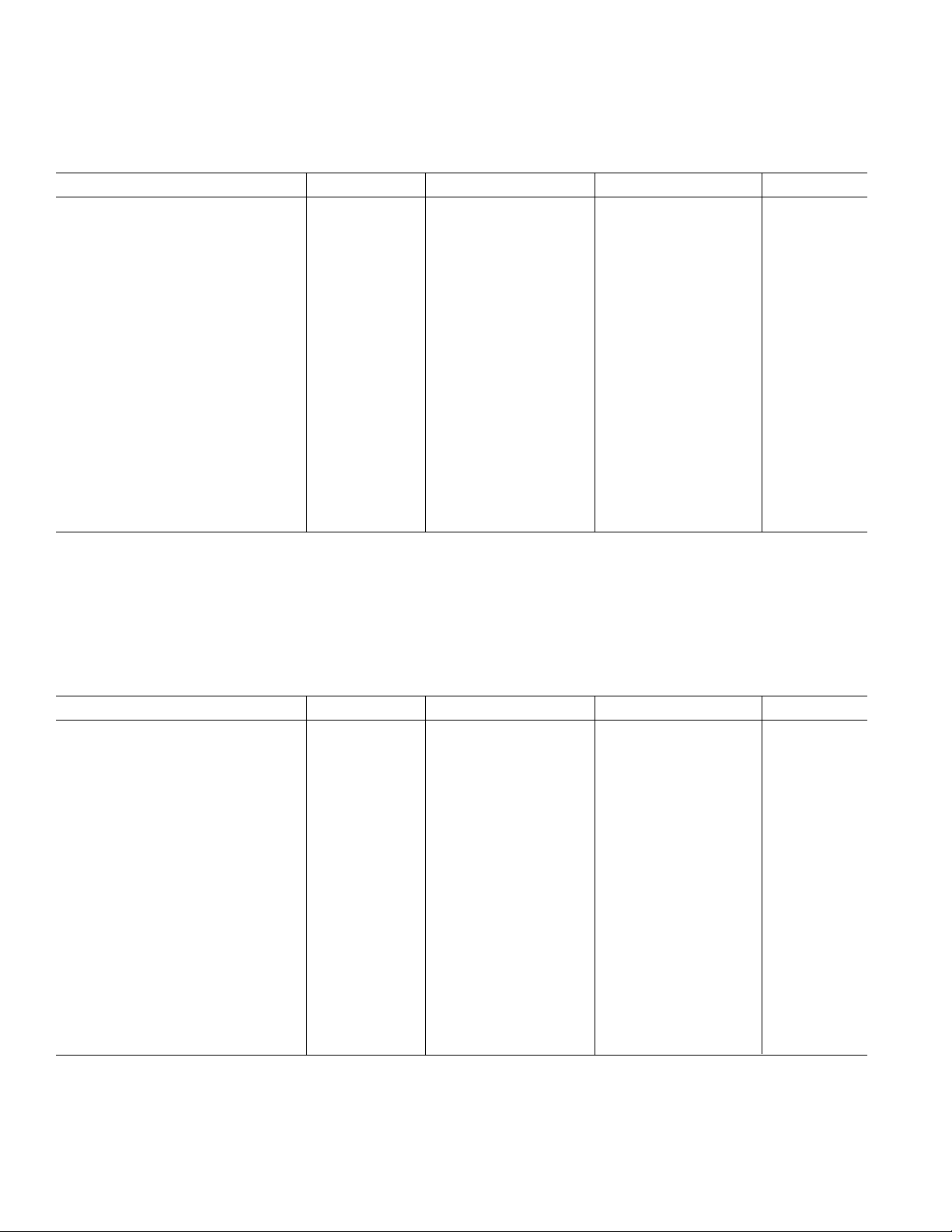

ADR390 SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(@ VIN = 5 V, TA = 25ⴗC unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Unit

Initial Accuracy V

Initial Accuracy Error V

Temperature Coefficient TCV

Minimum Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Turn-On Settling Time t

Long-Term Stability

Output Voltage Hysteresis

1

2

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

NOTES

1

Long-term stability, typical shift in value of output voltage at 25°C on a sample of parts subjected to operation life test of 1000 hours at 125°C. ∆VO = VO (t0) –V

(t

); VO (t0) = VO at 25°C at time 0; VO (t

1000

2

Output Voltage Hysteresis, is defined as the change in 25°C output voltage before and after the device is cycled through temperature. +25 °C to –40°C to +85°C to

+25°C. This is a typical value from a sample of parts put through such a cycle. Refer to Figures 11 and 12. V

at 25°C after temperature cycle at +25°C to –40°C to +85°C to +25°C; V

Specifications subject to change without notice.

1000

O

OERR

/°C –40°C < TA < +85°C 5 25 ppm/°C

O

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

N

R

∆V

O

V

OHYS

SC

SHDN

LOGIC

INL

INH

) = VO at 25°C after 1000 hours at 125°C; ∆VO = (VO (t0) – VO (t

VIN = 2.5 V to 15 V

–40°C < T

V

= 3 V,

IN

I

LOAD

–40°C < T

< +85°C 10 25 ppm/V

A

= 0 mA to 5 mA

< +85°C 60 ppm/mA

A

No Load 100 120 µA

–40°C < T

< +85°C 140 µA

A

0.1 Hz to 10 Hz 5 µV p-p

1,000 Hours 50 ppm

= 60 Hz 85 dB

IN

OHYS

= ((VO–V

)/VO) × 106 (in ppm).

OTC

2.042 2.048 2.054 V

0.29 0.29 %

300 mV

20 µs

40 ppm

30 mA

3 µA

500 nA

0.8 V

2.4 V

))/VO (t0) × 106 (in ppm).

1000

OHYS

= VO –V

; VO = VO at 25°C at time 0; V

OTC

OTC

O

= V

O

ELECTRICAL CHARACTERISTICS

(@ VIN = 15 V, TA = 25ⴗC unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Unit

Initial Accuracy V

Initial Accuracy Error V

Temperature Coefficient TCV

Minimum Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Turn-On Settling Time t

Long-Term Stability

Output Voltage Hysteresis

1

2

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

NOTES

1

Long-term stability, typical shift in value of output voltage at 25°C on a sample of parts subjected to operation life test of 1000 hours at 125°C. ∆VO = VO (t0) –V

(t

); VO (t0) = VO at 25°C at time 0; VO (t

1000

2

Output Voltage Hysteresis, is defined as the change in 25°C output voltage before and after the device is cycled through temperature. +25 °C to –40°C to +85°C to

+25°C. This is a typical value from a sample of parts put through such a cycle. Refer to Figures 11 and 12. V

at 25°C after temperature cycle at +25°C to –40°C to +85°C to +25°C; V

Specifications subject to change without notice.

1000

O

OERR

/°C –40°C < TA < +85°C 5 25 ppm/°C

O

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

N

R

∆V

O

V

OHYS

SC

SHDN

LOGIC

INL

INH

) = VO at 25°C after 1000 hours at 125°C; ∆VO = (VO (t0) – VO (t

VIN = 2.5 V to 15 V

–40°C < T

V

= 3 V,

IN

I

LOAD

–40°C < T

< +85°C 10 25 ppm/V

A

= 0 mA to 5 mA

< +85°C 60 ppm/mA

A

No Load 100 120 µA

–40°C < T

< +85°C 140 µA

A

0.1 Hz to 10 Hz 5 µV p-p

1,000 Hours 50 ppm

= 60 Hz 85 dB

IN

OHYS

= ((VO–V

)/VO) × 106 (in ppm).

OTC

2.042 2.048 2.054 V

0.29 0.29 %

300 mV

20 µs

40 ppm

30 mA

3 µA

500 nA

0.8 V

VIN – 1 V

))/VO (t0) × 106 (in ppm).

1000

OHYS

= VO –V

; VO = VO at 25°C at time 0; V

OTC

OTC

O

= V

O

–2–

REV. 0

Page 3

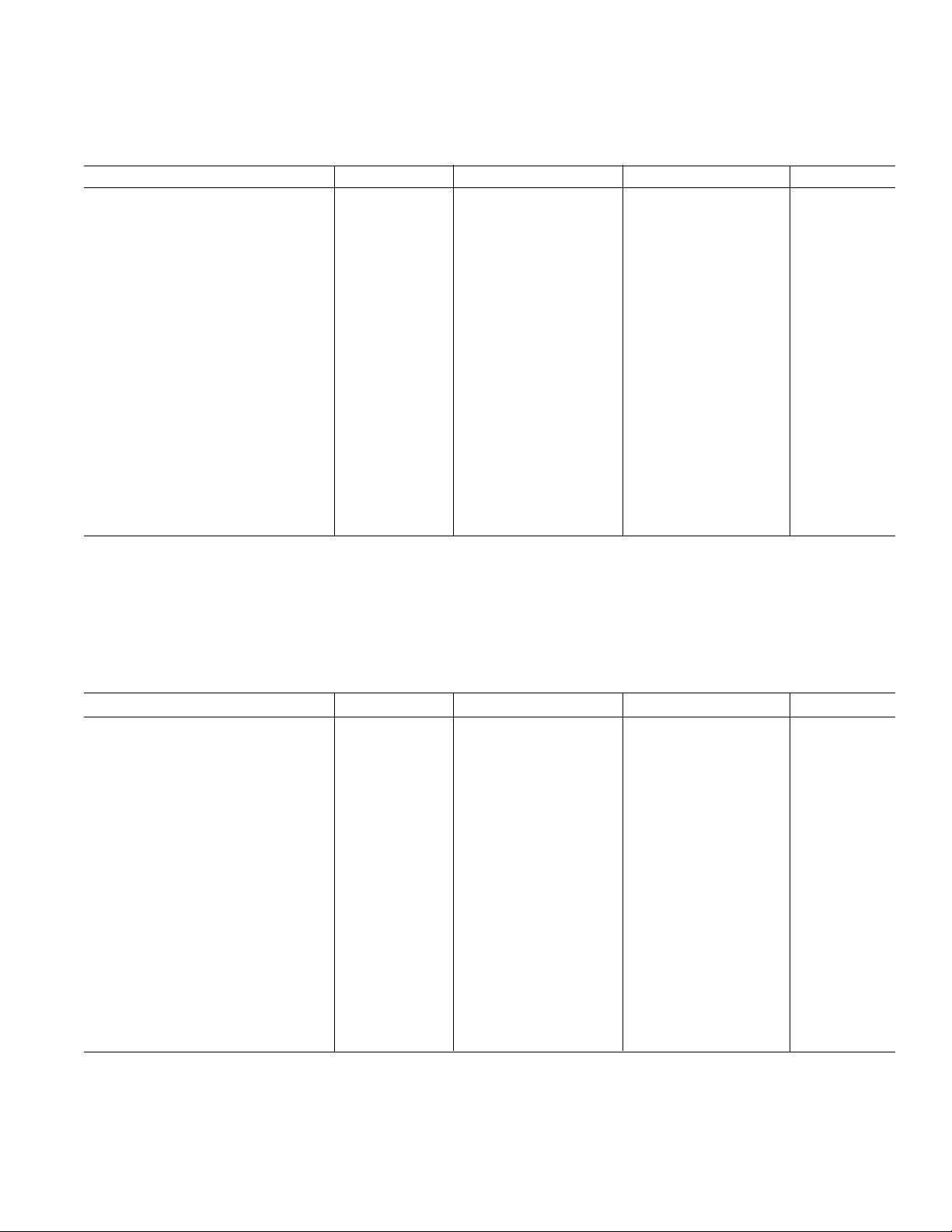

ADR391 SPECIFICATIONS

ADR390/ADR391

ELECTRICAL CHARACTERISTICS

(@ VIN = 5 V, TA = 25ⴗC unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Unit

Initial Accuracy V

Initial Accuracy Error V

Temperature Coefficient TCV

Minimum Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Turn-On Settling Time t

Long-Term Stability

Output Voltage Hysteresis

1

2

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

NOTES

1

Long-term stability, typical shift in value of output voltage at 25°C on a sample of parts subjected to operation life test of 1000 hours at 125°C. ∆VO = VO (t0) –V

(t

); VO (t0) = VO at 25°C at time 0; VO (t

1000

2

Output Voltage Hysteresis, is defined as the change in 25°C output voltage before and after the device is cycled through temperature. +25 °C to –40°C to +85°C to

+25°C. This is a typical value from a sample of parts put through such a cycle. Refer to Figures 11 and 12. V

at 25°C after temperature cycle at +25°C to –40°C to +85°C to +25°C; V

Specifications subject to change without notice.

1000

O

OERR

/°C –40°C < TA < +85°C 5 25 ppm/°C

O

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

N

R

∆V

O

V

OHYS

SC

SHDN

LOGIC

INL

INH

) = VO at 25°C after 1000 hours at 125°C; ∆VO = (VO (t0) – VO (t

VIN = 2.8 V to 15 V

–40°C < T

V

= 3.5 V,

IN

I

LOAD

–40°C < T

< +85°C 10 25 ppm/V

A

= 0 mA to 5 mA

< +85°C 60 ppm/mA

A

No Load 100 120 µA

–40°C < T

< +85°C 140 µA

A

0.1 Hz to 10 Hz 5 µV p-p

1,000 Hours 50 ppm

= 60 Hz 85 dB

IN

OHYS

= ((VO–V

)/VO) × 106 (in ppm).

OTC

2.494 2.5 2.506 V

0.24 0.24 %

300 mV

20 µs

75 ppm

25 mA

3 µA

500 nA

0.8 V

2.4 V

))/VO (t0) × 106 (in ppm).

1000

OHYS

= VO –V

; VO = VO at 25°C at time 0; V

OTC

OTC

O

= V

O

ELECTRICAL CHARACTERISTICS

(@ VIN = 15 V, TA = 25ⴗC unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Unit

Initial Accuracy V

Initial Accuracy Error V

Temperature Coefficient TCV

Minimum Supply Voltage Headroom V

Line Regulation ∆V

Load Regulation ∆V

Quiescent Current I

Voltage Noise e

Turn-On Settling Time t

Long-Term Stability

Output Voltage Hysteresis

1

2

Ripple Rejection Ratio RRR f

Short Circuit to GND I

Shutdown Supply Current I

Shutdown Logic Input Current I

Shutdown Logic Low V

Shutdown Logic High V

NOTES

1

Long-term stability, typical shift in value of output voltage at 25°C on a sample of parts subjected to operation life test of 1000 hours at 125°C. ∆VO = VO (t0) –V

(t

); VO (t0) = VO at 25°C at time 0; VO (t

1000

2

Output Voltage Hysteresis, is defined as the change in 25°C output voltage before and after the device is cycled through temperature. +25 °C to –40°C to +85°C to

+25°C. This is a typical value from a sample of parts put through such a cycle. Refer to Figures 11 and 12. V

at 25°C after temperature cycle at +25°C to –40°C to +85°C to +25°C; V

Specifications subject to change without notice.

1000

O

OERR

/°C –40°C < TA < +85°C 5 25 ppm/°C

O

– V

IN

O

/∆V

O

IN

/∆I

O

LOAD

IN

N

R

∆V

O

V

OHYS

SC

SHDN

LOGIC

INL

INH

) = VO at 25°C after 1000 hours at 125°C; ∆VO = (VO (t0) – VO (t

VIN = 2.8 V to 15 V

–40°C < T

V

= 3.5 V,

IN

I

LOAD

–40°C < T

< +85°C 10 25 ppm/V

A

= 0 mA to 5 mA

< +85°C 60 ppm/mA

A

No Load 100 120 µA

–40°C < T

< +85°C 140 µA

A

0.1 Hz to 10 Hz 5 µV p-p

1,000 Hours 50 ppm

= 60 Hz 85 dB

IN

OHYS

= ((VO–V

)/VO) × 106 (in ppm).

OTC

2.494 2.5 2.506 V

0.24 0.24 %

300 mV

20 µs

75 ppm

30 mA

3 µA

500 nA

0.8 V

VIN – 1 V

))/VO (t0) × 106 (in ppm).

1000

OHYS

= VO –V

; VO = VO at 25°C at time 0; V

OTC

OTC

O

= V

O

–3–REV. 0

Page 4

ADR390/ADR391

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V

Shutdown Logic Level . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V

Or Supply Voltage, Whichever is Lower . . . . . . . . . . . . 18 V

Output Short-Circuit Duration to GND Observe Derating Curves

Package Type JA*

JC

Unit

5-Lead SOT-23 (RT) 230 – °C/W

*θJA is specified for worst-case conditions, i.e., θ

socket for SOT packages.

is specified for device in

JA

Storage Temperature Range

RT Package . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

ADR390/ADR391 . . . . . . . . . . . . . . . . . . . –40°C to +85°C

Junction Temperature Range

RT Package . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . . 300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE

Temperature Package Package Top Output Number of

Model Range Description Option Mark Voltage Parts

ADR390ART–REEL7 –40⬚C to +85⬚C 5-Lead SOT RT-5 R0A 2.048 3,000

ADR390ART–REEL –40⬚C to +85⬚C 5-Lead SOT RT-5 R0A 2.048 10,000

ADR391ART–REEL7 –40⬚C to +85⬚C 5-Lead SOT RT-5 R1A 2.500 3,000

ADR391ART–REEL –40⬚C to +85⬚C 5-Lead SOT RT-5 R1A 2.500 10,000

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the ADR390/ADR391 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. 0

Page 5

Typical Performance Characteristics–

ADR390/ADR391

– V

OUT

V

2.054

2.052

2.050

2.048

2.046

2.044

2.042

SAMPLE 1

SAMPLE 2

SAMPLE 3

ⴚ40 ⴚ15

10 35 60 85

TEMPERATURE – ⴗC

Figure 1. ADR390 Output Voltage vs. Temperature

2.506

– V

OUT

V

2.504

2.502

2.500

2.498

2.496

SAMPLE 1

SAMPLE 2

SAMPLE 3

140

120

100

80

SUPPLY CURRENT – A

60

40

2.5 15.05.0

+85ⴗC

+25ⴗC

ⴚ40ⴗC

7.5 10.0 12.5

INPUT VOLTAGE – V

Figure 4. ADR391 Supply Current vs. Input Voltage

40

IL= 0mA TO 5mA

35

30

25

20

LOAD REGULATION – ppm/mA

15

VIN = 3.0V

VIN = 5.0V

2.494

ⴚ40 ⴚ15

10 35 60 85

TEMPERATURE – ⴗC

Figure 2. ADR391 Output Voltage vs. Temperature

140

120

100

80

SUPPLY CURRENT – A

60

40

2.5 15.05.0

+85ⴗC

+25ⴗC

ⴚ40ⴗC

7.5 10.0 12.5

INPUT VOLTAGE – V

Figure 3. ADR390 Supply Current vs. Input Voltage

10

ⴚ40 ⴚ15

10 35 60 85

TEMPERATURE – ⴗC

Figure 5. ADR390 Load Regulation vs. Temperature

40

IL= 0mA TO 5mA

35

30

25

20

LOAD REGULATION – ppm/mA

15

10

ⴚ40 ⴚ15

VIN = 3.5V

VIN = 5.0V

10 35 60 85

TEMPERATURE – ⴗC

Figure 6. ADR391 Load Regulation vs. Temperature

–5–REV. 0

Page 6

ADR390/ADR391

5

VIN = 2.5V TO 15V

4

3

2

LINE REGULATION – ppm/V

1

0

ⴚ40 ⴚ15

10 35 60 85

TEMPERATURE – ⴗC

Figure 7. ADR390 Line Regulation vs. Temperature

5

VIN = 2.8V TO 15V

4

3

2

LINE REGULATION – ppm/V

1

0.8

0.6

+85ⴗC

0.4

0.2

DIFFERENTIAL VOLTAGE – V

0

0

234

LOAD CURRENT – mA

+25ⴗC

ⴚ40ⴗC

51

Figure 10. ADR391 Minimum Input-Output Voltage

Differential vs. Load Current

60

TEMPERATURE: +25ⴗC ⴚ40ⴗC +85ⴗC +25ⴗC

50

40

30

FREQUENCY

20

10

0

ⴚ40 ⴚ15

10 35 60 85

TEMPERATURE – ⴗC

Figure 8. ADR391 Line Regulation vs. Temperature

0.8

0.6

0.4

0.2

DIFFERENTIAL VOLTAGE – V

0

0

ⴚ40ⴗC

+85ⴗC

+25ⴗC

234

LOAD CURRENT – mA

51

Figure 9. ADR390 Minimum Input-Output Voltage

Differential vs. Load Current

0

ⴚ0.24

Figure 11. ADR390 V

70

60

50

40

30

FREQUENCY

20

10

0

ⴚ0.56 ⴚ0.26

Figure 12. ADR391 V

ⴚ0.12

ⴚ0.18 ⴚ0.06

TEMPERATURE: +25ⴗC ⴚ40ⴗC +85ⴗC +25ⴗC

ⴚ0.41 ⴚ0.11

0 0.06 0.18

V

DEVIATION – mV

OUT

Hysteresis Distribution

OUT

V

DEVIATION – mV

OUT

Hysteresis Distribution

OUT

0.12 0.24

0.04 0.19

0.30

0.34

–6–

REV. 0

Page 7

ADR390/ADR391

VOLTAGE

TIME – 10s/DIV

0

0

0

0

0

0

0

0

0

C

BYPASS

= 0.1F

LINE

INTERRUPTION

V

OUT

0.5V/DIV

1V/DIV

VOLTAGE – 1V/DIV

TIME – 200s/DIV

0

0

0

0

0

0

0

0

0

CL = 0nF

V

LOAD

ON

V

OUT

LOAD OFF

1k

VIN = 5V

ADR391

ADR390

VOLTAGE NOISE DENSITY – nV/ Hz

100

10 10k100

FREQUENCY – Hz

1k

Figure 13. Voltage Noise Density vs. Frequency

0

0

0

0

0

0

0

0

LINE

INTERRUPTION

0

0

VOLTAGE

0

0

0

V

OUT

TIME – 10s/DIV

C

BYPASS

= 0F

0.5V/DIV

1V/DIV

Figure 16. ADR391 Line Transient Response

0

VOLTAGE – 100V/DIV

0

0

0

TIME – 10ms/DIV

Figure 14. ADR390 Voltage Noise 10 Hz to 10 kHz

0

0

0

0

0

0

VOLTAGE – 100V/DIV

0

0

0

Figure 15. ADR391 Voltage Noise 10 Hz to 10 kHz

TIME – 10ms/DIV

Figure 17. ADR391 Line Transient Response

Figure 18. ADR391 Load Transient Response

–7–REV. 0

Page 8

ADR390/ADR391

0

0

0

0

0

0

VOLTAGE – 1V/DIV

0

0

0

V

LOAD

V

OUT

LOAD OFF

ON

TIME – 200s/DIV

CL = 1nF

Figure 19. ADR391 Load Transient Response

0

0

0

0

0

0

VOLTAGE – 1V/DIV

0

V

LOAD

V

OUT

LOAD OFF

ON

CL = 100nF

0

V

= 15V

IN

0

0

0

0

VOLTAGE

V

0

0

0

0

V

IN

OUT

5V/DIV

2V/DIV

TIME – 40s/DIV

Figure 22. ADR391 Turn-Off Response at 15 V

0

C

= 0.1F

BYPASS

0

0

V

0

0

VOLTAGE

0

0

V

OUT

IN

2V/DIV

5V/DIV

0

0

TIME – 200s/DIV

Figure 20. ADR391 Load Transient Response

0

V

= 15V

IN

0

0

0

0

VOLTAGE

0

V

0

0

0

V

OUT

IN

5V/DIV

2V/DIV

TIME – 20s/DIV

Figure 21. ADR391 Turn-On Response Time at 15 V

0

0

TIME – 200s/DIV

Figure 23. ADR391 Turn-On/Turn-Off Response at 5 V

0

RL = 500⍀

0

0

V

0

0

VOLTAGE

0

0

0

0

V

OUT

IN

2V/DIV

5V/DIV

TIME – 200s/DIV

Figure 24. ADR391 Turn-On/Turn-Off Response at 5 V

–8–

REV. 0

Page 9

ADR390/ADR391

SHDN

FORCE

SENSE

V

IN

R59 R44

TESTPAD

R58

R53

R54

R49

TESTPAD

R48

GROUND

R61

R60

Q51

Q52

2RS

TESTPAD

0

RL = 500⍀

0

= 100nF

C

L

0

0

0

0

VOLTAGE – 5V/DIV

0

0

0

V

OUT

V

IN

2V/DIV

5V/DIV

TIME – 200s/DIV

Figure 25. ADR391 Turn-On/Turn-Off Response at 5 V

80

60

40

20

0

ⴚ20

ⴚ40

ⴚ60

RIPPLE REJECTION – dB

ⴚ80

ⴚ100

ⴚ120

10 1M100

1k 10k 100k

FREQUENCY – Hz

Figure 26. Ripple Rejection vs. Frequency

100

90

80

70

60

50

40

30

OUTPUT IMPEDANCE – ⍀

20

10

0

10 1M100

Figure 27. Output Impedance vs. Frequency

CL = 1F

1k 10k 100k

FREQUENCY – Hz

CL = 0F

CL = 0.1F

THEORY OF OPERATION

Bandgap references are the high-performance solution for low

supply voltage and low power voltage reference applications,

and the ADR390/ADR391 is no exception. But the uniqueness

of this product lies in its architecture. By observing Figure 28,

the zero TC bandgap voltage is referenced to the output, not to

ground. The bandgap cell consists of the pnp pair Q51 and Q52,

running at unequal current densities. The difference in V

BE

results in a voltage with a positive TC which is amplified up by

58

R

2

×

the ratio of

. This PTAT voltage, combined with VBE’s

54

R

of Q51 and Q52 produce the stable bandgap voltage.

Reduction in the bandgap curvature is performed by the ratio of

the two resistors R44 and R59. Precision laser trimming and

other patented circuit techniques are used to further enhance

the drift performance.

Figure 28. Simplified Schematic

Device Power Dissipation Considerations

The ADR390/ADR391 is capable of delivering load currents to

5 mA with an input voltage that ranges from 2.8 V (ADR391 only)

to 15 V. When this device is used in applications with large input

voltages, care should be taken to avoid exceeding the specified maximum power dissipation or junction temperature that could result in

premature device failure. The following formula should be used to

calculate a device’s maximum junction temperature or dissipation:

TT

−

J

P

=

D

A

θ

JA

In this equation, TJ and TA are, respectively, the junction and

ambient temperatures, P

θ

is the device package thermal resistance.

JA

is the device power dissipation, and

D

Shutdown Mode Operation

The ADR390/ADR391 includes a shutdown feature that is TTL/

CMOS level compatible. A logic LOW or a zero volt condition on

the SHDN pin is required to turn the device off. During shutdown,

the output of the reference becomes a high impedance state where

its potential would then be determined by external circuitry. If the

shutdown feature is not used, the SHDN pin should be connected

(Pin 2).

to V

IN

–9–REV. 0

Page 10

ADR390/ADR391

U1

ADR39x

R1

4.99k⍀

(SEE TEXT)

C1

0.1F

V

IN

VIN > V

OUT2

+0.15V

V

IN

COMMON

V

OUT

COMMON

1

2

4

5

V

OUT2

3.735V

VO (U1)

C2

1F

D1

AD589

VO (D1)

C3

1F

V

OUT1

1.235V

5V

APPLICATIONS

Membrane Switch Controlled Power Supply

The ADR390/ADR391 can operate as a low dropout power

supply in hand-held instrumentation. In the following circuit, a

membrane ON/OFF switch is used to control the operation of the

reference. During an initial power-on condition, the SHDN pin is

held to GND. Recall that this condition disables the output (read:

three-state). When the membrane ON switch is pressed, the SHDN

pin assumes and remains at the same potential as V

, via the 10 kΩ

IN

resistor thus enabling the output. When the membrane OFF switch

is pressed, the SHDN pin is momentarily connected to GND which

disables the ADR390/ADR391 output once again.

V

IN

10k⍀

ON

OFF

ADR39x

1F

TANT

V

OUT

Figure 29. Membrane Switch Controlled Power Supply

Stacking Reference ICs for Arbitrary Outputs

Some applications may require two reference voltage sources which

are a combined sum of standard outputs. The following circuit

shows how this “stacked output” reference can be implemented:

U2, either the external load of U1 or R1 must provide a path for

this current. If the U1 minimum load is not well defined, the

resistor R1 should be used, set to a value that will conservatively

pass 600 µA of current with the applicable V

across it. Note

OUT1

that the two U1 and U2 reference circuits are locally treated as

macrocells, each having its own bypasses at input and output for best

stability. Both U1 and U2 in this circuit can source dc currents up to

their full rating. The minimum input voltage, VS, is determined by

the sum of the outputs, V

, plus the dropout voltage of U2.

OUT2

A related variation on stacking two three-terminal references is

shown in the following figure where U1, an ADR391, is stacked

with a two-terminal reference diode such as the AD589. Similar

to the all three-terminal stacked references mentioned earlier,

the two individual terminal voltage outputs of D1 and U1 are

1.235 V and 2.5 V, respectively. Thus V

is the sum of D1 and

OUT2

U1, or 3.735 V. When using two-terminal reference diodes such

as D1, the rated minimum and maximum device currents must

be observed, and the maximum load current from V

be no greater than the current set up by R1 and V

OUT1

O(U1)

can

.

OUTPUT TABLE

VIN > V

COMMON

V

OUT2

IN

V

IN

+0.15V

0.1F

0.1F

U1/U2

ADR390/ADR390

ADR391/ADR391

C1

C3

U2

1

ADR39x

(SEE TABLE)

U1

1

ADR39x

(SEE TABLE)

2

4

VO (U2)

5

2

4

VO (U1)

5

C2

1F

C4

1F

V

OUT1

2.048

2.5

R1

3.9k⍀

(SEE TEXT)

Figure 30. Stacking Voltage References with the ADR390/

ADR391

Two reference ICs are used, fed from a common unregulated

input, V

in series which provides two output voltages V

V

OUT1

voltage and the terminal voltage of U2. U1 and U2 are simply

chosen for the two voltages that supply the required outputs (see

Output Table). For example, if both U1 and U2 are ADR391’s,

V

OUT1

While this concept is simple, a precaution is in order. Since the

lower reference circuit must sink a small bias current from U2,

plus the base current from the series PNP output transistor in

. The outputs of the individual ICs are simply connected

IN

is the terminal voltage of U1, while V

is 2.5 V and V

OUT2

is 5.0 V.

OUT2

and V

OUT1

is the sum of this

(V)

V

OUT2

4.096

5.0

V

OUT2

V

OUT1

V

OUT

COMMON

OUT2

(V)

Figure 31. Stacking Voltage References with the ADR390/

ADR391

A Negative Precision Reference without Precision Resistors

In many current-output CMOS DAC applications where the

output signal voltage must be of the same polarity as the reference

voltage, it is often required to reconfigure a current-switching

DAC into a voltage-switching DAC through the use of a 1.25 V

reference, an op amp, and a pair of resistors. Using a currentswitching DAC directly requires the need for an additional

operational amplifier at the output to reinvert the signal. A negative

voltage reference is then desirable from the point that an additional

operational amplifier is not required for either reinversion (currentswitching mode) or amplification (voltage switching mode) of the

DAC output voltage. In general, any positive voltage reference can

be converted into a negative voltage reference through the use of an

operational amplifier and a pair of matched resistors in an inverting

configuration. The disadvantage to this approach is that the largest

single source of error in the circuit is the relative matching of the

resistors used.

.

The following circuit avoids the need for tightly matched resistors with the use of an active integrator circuit. In this circuit,

the output of the voltage reference provides the input drive for

the integrator. The integrator, to maintain circuit equilibrium,

adjusts its output to establish the proper relationship between

the reference’s V

and GND. Thus, any negative output

OUT

voltage desired can be chosen by simply substituting for the

appropriate reference IC. The shutdown feature is maintained

in the circuit with the simple addition of a PNP transistor and

–10–

REV. 0

Page 11

ADR390/ADR391

a 10 kΩ resistor. A precaution should be noted with this approach:

although rail-to-rail output amplifiers work best in the application,

these operational amplifiers require a finite amount (mV) of headroom when required to provide any load current. The choice for

the circuit’s negative supply should take this issue into account.

V

IN

10k⍀

SHDN

TTL/CMOS

10k⍀

2N3906

1

SHDN

ADR39x

2

V

GND

5

V

OUT

S

V

OUT

100k⍀

1k⍀

4

1F

1F

+5V

A1

ⴚ5V

A1 = 1/2 OP295,

1/2 OP291

100⍀

ⴚV

REF

Figure 32. A Negative Precision Voltage Reference Uses

No Precision Resistors

Precision Current Source

Many times in low-power applications, the need arises for a precision current source that can operate on low supply voltages. As

shown in the following figure, the ADR390/ADR391 can be configured as a precision current source. The circuit configuration illustrated is a floating current source with a grounded load. The

reference’s output voltage is bootstrapped across R

, which sets

SET

the output current into the load. With this configuration, circuit

precision is maintained for load currents in the range from the

reference’s supply current, typically 90 µA to approximately 5 mA.

V

IN

SHDN

V

OUT

ADR39x

V

V

OUT

S

R

1

R

1

GND

1F

I

ADJUST

R

SY

I

OUT

}

P

1

SET

High-Power Performance with Current Limit

In some cases, the user may want higher output current delivered

to a load and still achieve better than 0.5% accuracy out of the

ADR390/ADR391. The accuracy for a reference is normally

specified on the data sheet with no load. However, the output

voltage changes with load current.

The circuit below provides high current without compromising

the accuracy of the ADR390/ADR391. The series pass transistor Q1 provides up to 1 A load current. The ADR390/ADR391

delivers only the base drive to Q1 through the force pin. The

sense pin of the ADR390/ADR391 is a regulated output and is

connected to the load.

R1

4.7k⍀

V

IN

U1

GND

SHDN

V

IN

V

OUT (FORCE)

V

OUT (SENSE)

ADR390/ADR391

Q2N2222

Q1

R

R

S

L

Q2N4921

I

L

Q2

Figure 34. ADR390/ADR391 for High-Power Performance

with Current Limit

A similar circuit function can also be achieved with the Darlington

transistor configuration, see Figure 35.

R1

4.7k⍀

V

IN

U1

GND

SHDN

V

IN

V

OUT (FORCE)

V

OUT (SENSE)

ADR390/ADR391

Q2N2222

R

Q1

Q2

Q2N4921

S

R

L

R

L

Figure 33. A Precision Current Source

Figure 35. ADR390/ADR391 High Output Current with

Darlington Drive Configuration

The transistor Q2 protects Q1 during short circuit limit faults by

robbing its base drive. The maximum current is I

≈ 0.6 V/RS.

LMAX

–11–REV. 0

Page 12

ADR390/ADR391

0.0669 (1.70)

0.0590 (1.50)

0.0512 (1.30)

0.0354 (0.90)

0.0059 (0.15)

0.0019 (0.05)

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

5-Lead SOT-23

(RT Suffix)

0.1181 (3.00)

0.1102 (2.80)

4 5

0.1181 (3.00)

0.1024 (2.60)

0.0374 (0.95) BSC

0.0571 (1.45)

0.0374 (0.95)

SEATING

PLANE

PIN 1

1 3

2

0.0748 (1.90)

BSC

0.0197 (0.50)

0.0138 (0.35)

10ⴗ

0ⴗ

C3863–8–4/00 (rev. 0) 00419

0.0079 (0.20)

0.0031 (0.08)

0.0217 (0.55)

0.0138 (0.35)

–12–

PRINTED IN U.S.A.

REV. 0

Loading...

Loading...