Page 1

Precision Low Power 2.048 V

SOT-23 Voltage Reference

FEATURES

Initial Accuracy: ⴞ4 mV Max

Initial Accuracy Error: ⴞ0.2%

Low TCVO: ⴞ50 ppm/ⴗC Max from –40ⴗC to +125ⴗC,

30 ppm/ⴗC Max from +25ⴗC to +70ⴗC

Load Regulation: 200 V/mA, 100 ppm/mA

Line Regulation: 25 V/V, 20 ppm/V

Wide Operating Range: V

Low Power: 72 A Max

High Output Sink/Source Current: ⴞ5 mA Min

Wide Temperature Range: –40ⴗC to +125ⴗC

Tiny 3-Lead SOT-23 Package with Standard Pinout

APPLICATIONS

Battery-Powered Instrumentation

Portable Medical Instruments

Data Acquisition Systems

Industrial Process Control Systems

Automotive

GENERAL DESCRIPTION

= 2.3 V to 15 V

IN

The ADR370 is a low cost, 3-terminal (series) band-gap voltage

reference featuring high accuracy, high stability, and low power

consumption packaged in a tiny 3-lead SOT-23 package. Precise

matching and thermal tracking of on-chip components, as well as

patented temperature drift curvature correction design techniques,

have been employed to ensure that the ADR370 provides an

accurate 2.048 V output.

This micropowered, low dropout voltage device will source or

sink up to 5 mA of load current while providing a stable 2.048 V

output. The compact footprint, high accuracy, and an operating

range of 2.3 V to 12 V make the ADR370 ideal for use in 3 V

and 5 V systems where there may be wide variations in supply

voltage and a need to minimize power dissipation.

The ADR370 is offered in A and B grades; all devices are specified

over the extended industrial range of –40°C to +125°C.

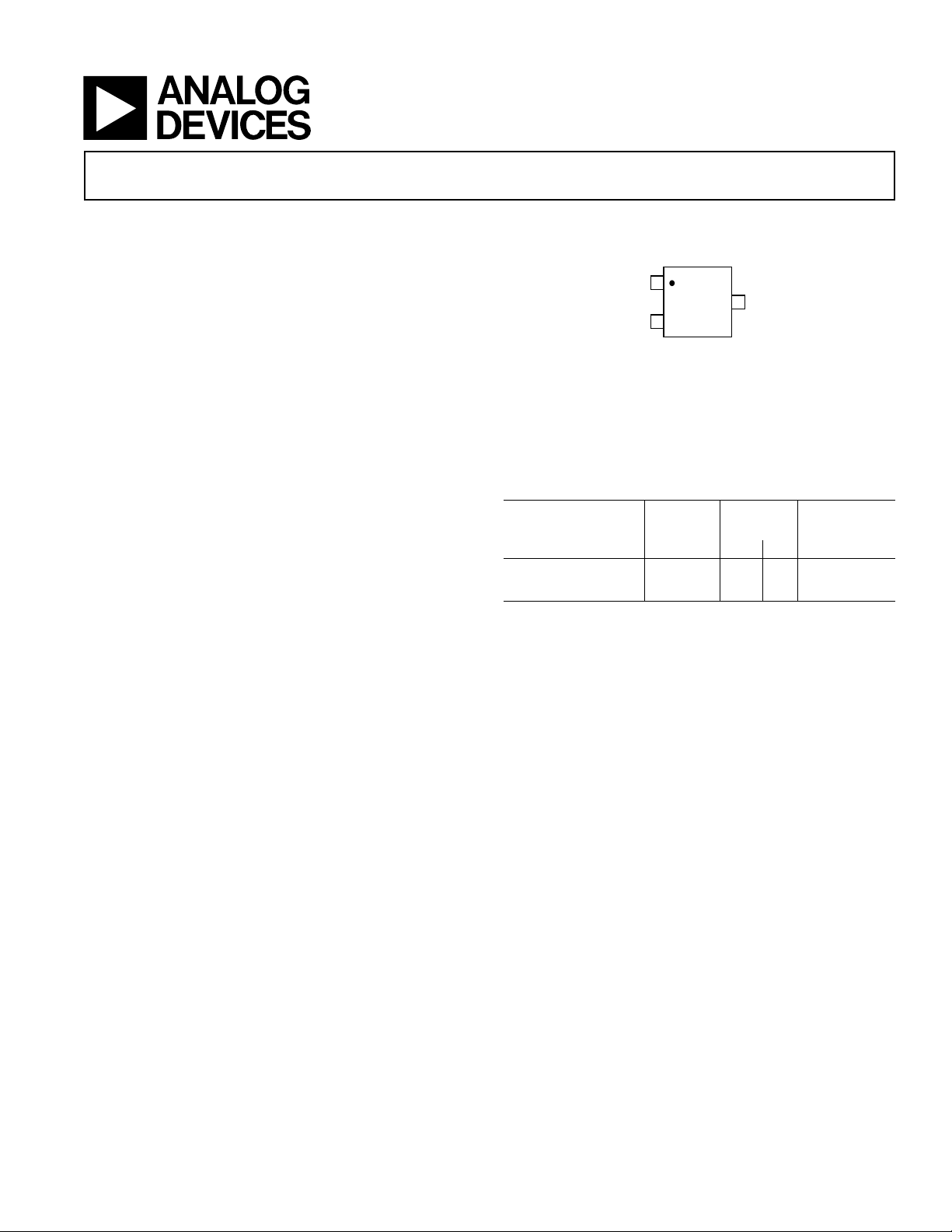

ADR370

PIN CONFIGURATION

3-Lead SOT-23

1

V

IN

3

ADR370

V

2

OUT

Table I. ADR370 Products

Output Initial Temperature

Voltage Accuracy Coefficent

Products (VO)

ADR370BRT-REEL7 2.048 4 0.2 50

ADR370ART-REEL7 2.048 10 0.5 100

GND

(mV)

(%) (ppm/°C)

*

*Protected by U.S.Patent No. 5,969,657; other patents pending.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

Page 2

ADR370–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(TA = T

MIN

to T

, VIN = 5 V, unless otherwise noted.)

MAX

Parameter Symbol Conditions Min Typ Max Unit

Output Voltage (@ 25°C) V

O

2.044 2.048 2.052 V

Initial Accuracy Error

A Grade V

B Grade V

V

V

OERR

OERR

OERR

OERR

–10 +10 mV

–0.5 +0.5 %

–4+4mV

–0.2 +0.2 %

Output Voltage Temperature Drift

A Grade TCV

B Grade TCV

TCV

Supply Headroom V

IN

O

O

O

– V

OUT

–40°C to +125°C 100 ppm/°C

–40°C to +125°C50ppm/°C

25°C to 70°C30ppm/°C

200 mV

Load Regulation

Line Regulation V

Ripple Rejection ∆V

/∆VINVIN = 5 V ± 100 mV (f = 120 Hz) 80 dB

OUT

0 mA < I

–3 mA < I

–0.1 mA < I

OUT

= 0 mA

I

OUT

< 5 mA @ 25°C –0.200 +0.200 mV/mA

OUT

< 0 mA @ 25°C –0.480 +0.480 mV/mA

OUT

< +0.1 mA –0.425 +0.425 mV/mA

OUT

200 mV < VIN < 15 V 20 ppm/V

Quiescent Current 72 µA

Short-Circuit Current to Ground 15 µA

Noise Voltage (@ 25°C) 0.1 Hz to 10 Hz 70 µV p-p

10 Hz to 10 kHz 50 µV rms

Turn-On Settling Time C

= 0.2 µF 100 µs

L

Long Term Stability 1,000 Hours @ 25°C 100 ppm/1,000 hrs

Output Voltage Hysteresis 115 ppm

Temperature Range –40 +125 °C

*Guaranteed by characterization.

Specifications subject to change without notice.

–2–

REV. A

Page 3

ADR370

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V

Storage Temperature Range

Package Type

JA

JC

Unit

3-SOT-23 (RT) 220 102 °C/W

RT Package . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +125°C

Operating Temperature Range . . . . . . . . . . .–40°C to +125°C

Lead Temperature Range

Soldering, 60 sec . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared, 15 sec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

*Absolute maximum ratings apply at 25°C, unless otherwise noted.

ORDERING GUIDE

Output Initial Temperature Number

Voltage Accuracy Coefficient Package Package of Parts Temperature

Model (VO)(mV) (%) (ppm/°C) Description Option Branding per Reel Range

ADR370BRT-R2 2.048 ±4 0.5 50 SOT-23 3-Lead RPB 250 –40°C to +125°C

ADR370BRT-REEL7 2.048 ±4 0.2 50 SOT-23 3-Lead RPB 3,000 –40°C to +125°C

ADR370ART-R2 2.048 ±10 0.5 100 SOT-23 3-Lead RPA 250 –40°C to +125°C

ADR370ART-REEL7 2.048 ±10 0.5 100 SOT-23 3-Lead RPA 3,000 –40°C to +125°C

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

ADR370 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. A

–3–

Page 4

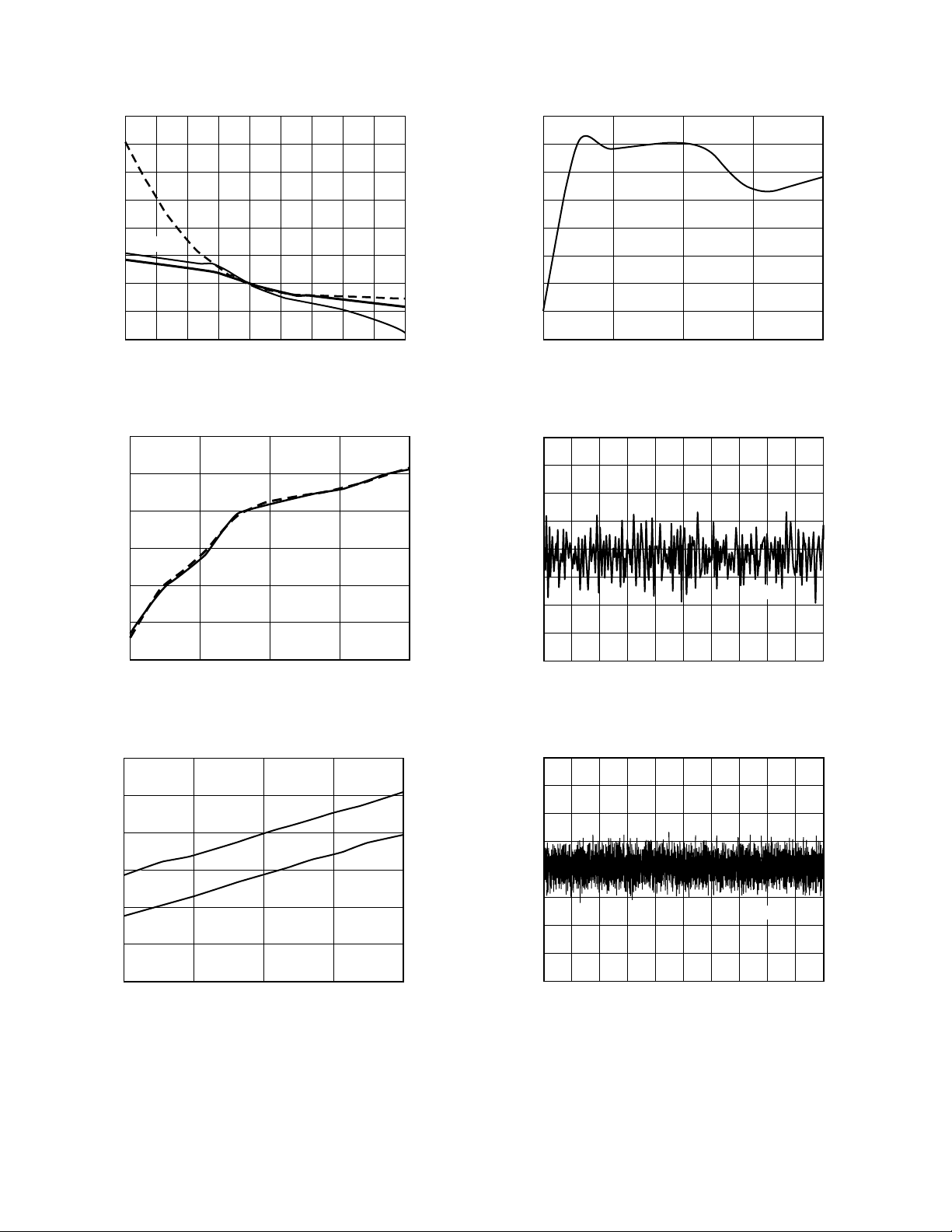

ADR370–Typical Performance Characteristics

12

10

8

–40ⴗC

6

4

O – mV

∆ V

+125ⴗC

2

+25ⴗC

0

–2

–4

–4 5–3

–2 –1 01234

LOAD – mA

TPC 1. Load Regulation vs. Load Current

2.048

2.046

2.044

2.042

VIN = 5V

VIN = 15V

6

4

2

0

–2

–4

–6

LINE REGULATION – ppm/V

–8

–10

–40

45 125

TEMPERATURE – ⴗC

V

TPC 4. Line Regulation vs. Temperature

0

0

0

0

0

5V TO 15V

IN

2.040

OUTPUT VOLTAGE – V

2.038

2.036

–40

45 125

TEMPERATURE – ⴗC

TPC 2. Output Voltage vs. Temperature

80

70

60

50

40

SUPPLY CURRENT – A

30

20

–40

TEMPERATURE – ⴗC

= 15V

V

IN

45 125

TPC 3. Supply Current vs. Temperature

0

VOLTA G E – 10V/DIV

0

0

0

000

00000000

TIME – 0.1s/DIV

TPC 5. Voltage Noise 0.1 Hz to 10 Hz

0

0

0

0

V

= 5V

IN

0

0

VOLTA G E – 200V/DIV

0

0

0

000

00000000

TIME – 0.1s/DIV

TPC 6. Voltage Noise 10 Hz to 100 kHz

–4–

REV. A

Page 5

ADR370

VOLTA G E – V

VOLTA G E – V

0

0

0

0

0

0

0

0

0

000

0

0

0

0

0

0

0

CBY = 0.1F

= 0.22F

C

LOAD

00000000

V

OUT

VIN = 5V/DIV

TIME – 100s/DIV

= 1V/DIV

TPC 7. Turn-On Response

R

= 1k⍀

LOAD

V

= 1V/DIV

OUT

VIN = 5V/DIV

0

CL = 0.1F

0

0

0

0

VOLTA G E – V

0

0

0

0

000

VIN = 1V/DIV

V

= 1V/DIV

OUT

00000000

TIME – 100s/DIV

TPC 9. Line Transient Response

0

CBY = 0.1F

0

0

0

0

VOLTA G E – V

0

0

C

LOAD

= 0.1F

VIN = 2V/DIV

V

OUT

= 20mV/DIV

0

0

000

00000000

TIME – 100s/DIV

TPC 8. Turn-Off Response

0

0

000

00000000

TIME – 100ms/DIV

TPC 10. Load Transient Response

REV. A

–5–

Page 6

ADR370

PARAMETER DEFINITIONS

Temperature Coefficient

Temperature coefficient is the change of output voltage with

respect to operating temperature changes, normalized by the

output voltage at 25°C. This parameter is expressed in ppm/°C

and can be determined with the following equation

TCV

ppm

O

°

C

VT VT

=

()−()

21

OO

°

×−

25

VCTT

()

O

()

21

6

10

×

(1)

where:

V

(25°C) = VO at 25°C.

O

V

) = VO at Temperature 1.

O (T1

V

) = VO at Temperature 2.

O (T2

Line Regulation

Line regulation is the change in output voltage due to a specified

change in input voltage. This parameter accounts for the effects

of self-heating. Line regulation is expressed in either percent per

volt, parts-per-million per volt, or microvolts per volt change in

input voltage.

Load Regulation

Load regulation is the change in output voltage due to a specified

change in load current. This parameter accounts for the effects

of self-heating. Load regulation is expressed in either microvolts

per milliampere, parts-per-million per milliampere, or ohms of

dc output resistance.

Long Term Stability

Long term stability is the typical shift of output voltage at 25°C

on a sample of parts subjected to a test of 1,000 hours at 25°C.

∆∆VVtVt

V ppm

where:

V

) = VO at 25°C at time 0.

O (T1

V

) = VO at 25°C after 1,000 hours operation at 25°C.

O (T2

=

OO O

O

()−()

01

Vt Vt

()−()

OO

=

[]

Vt

01

O

()

0

6

×

10

(2)

Thermal Hysteresis

Thermal hysteresis is defined as the change of output voltage after

the device is cycled through temperature from +25°C to –40°C

to +125°C and back to +25°C. This is a typical value from a sample

of parts put through such a cycle.

VVCV

O HYS O O TC

__

V ppm

O HYS

_

where:

V

(25°C) = VO at 25°C.

O

V

= VO at 25°C after temperature cycle at +25°C to –40°C

O_TC

25

=°

[]

−

()

25

VCV

()

OOTC

=

VC

°

−

_

25

°

()

O

6

10

×

(3)

to +125°C and back to +25°C.

THEORY OF OPERATION

The ADR370 uses the band-gap concept to produce a stable,

low temperature coefficient voltage reference suitable for high

accuracy data acquisition components and systems. This device

makes use of underlying temperature characteristics of a silicon

transistor’s base-emitter voltage (V

) in the forward biased

BE

operating region. Under this condition, all such transistors have

a –2 mV/°C temperature coefficient (TC) and a V

that, when

BE

extrapolated to absolute zero, 0 K, (with collector current proportional to absolute temperature) approximates the silicon

band-gap voltage. By summing a voltage that has an equal and

opposite temperature coefficient of 2 mV/°C with a V

BE

of a

forward biased transistor, an almost zero TC reference can be

developed. The simplified circuit diagram in Figure 1 shows how

a compensating voltage, V1, is achieved by driving two transistors

at different current densities and amplifying the resultant V

difference (∆VBE, which has a positive TC). The sum (VBG) of V

BE

BE

and V1 is then buffered and amplified to produce a stable reference

voltage of 2.048 V at the output.

V

R4

R3

R2

R1 V1

IN

V

OUT

R5

V

DS

R6

GND

Figure 1. Simplified Schematic

Applying the ADR370

In order to achieve the specified performance, two external

components should be used in conjunction with the ADR370,

a 4.7 µF capacitor and a 1 µF capacitor should be applied to the

input and output, respectively. Figure 2 shows the ADR370 with

both the input and output capacitors attached.

For further transient response optimization, an additional 0.1 µF

capacitor in parallel with the 4.7 µF input capacitor can be used.

A 1 µF output capacitor will provide stable performance for all

loading conditions. The ADR370 can, however, operate under

low (–100 µA < I

< +100 µA) current conditions with just a

OUT

0.2 µF output capacitor and a 1 µF input capacitor.

V

4.7F

C

IN

C

1F

OUT

IN

ADR370

V

OUT

GND

–6–

Figure 2. Typical Connection Diagram

REV. A

Page 7

ADR370

APPLICATIONS

Low Cost Negative Reference

A low cost negative reference can be obtained by leveraging the

current sinking capability of the ADR370. Simply tying the V

terminal to ground and adding a bias resistor, R

, to the GND

SET

OUT

pin of the device, a negative voltage reference can be obtained

as shown in Figure 3. R

should be chosen such that I

SET

SET

remains between 1 mA to 5 mA.

V

DD

ADR370

V

IN

V

OUT

GND

–VREF

R

I

SET

SET

V

SS

Figure 3. Low Cost Negative Reference

Precision Negative Reference

Without using any matching resistors, a precision negative reference

can be obtained using the configuration shown in Figure 4. The

voltage difference between V

2.048 V. Since V

is at virtual ground, U2 will close the loop by

OUT

and GND of the ADR370 is

OUT

forcing the GND pin to be the negative reference node. U2 should

be a low offset voltage precision op amp, such as the OP1177.

U1

2.3V TO 12V

–VREF

ADR370

V

IN

GND

V

OUT

OP1177

+15V

U2

–15V

VL + 2.5V < VDD < VL + 12V

ADR370

V

IN

GND

Iq = 65A

V

OUT

2.048V

I

= R

SET

SET

R

LIL

R

SET

V

L

Figure 5. Low Cost Current Source

Precision Current Source with Adjustable Output

A precision current source can be implemented with the circuit

shown in Figure 6. By adding a mechanical or digital potentiometer, this circuit becomes an adjustable current source. If a

digital potentiometer like the AD5201 is used, the load current

is simply the voltage across terminals B-to-W of the digital

potentiometer divided by R

VD

×

I

REF

=

L

R

× 256

SET

SET

.

(5)

where D is the decimal equivalent of the digital potentiometer

input code.

12V

ADR370

V

IN

GND

–2.048V TO V

V

OUT

L

0V TO (2.048V + VL)

AD5201

OP1177

+12V

–12V

B

W

A

R

SET

V

L

R

I

L

L

Figure 4. Precision Negative Reference

Low Cost Current Source

Figure 5 illustrates how a simple, low cost current source can be

configured using the ADR370. The load current, I

the sum of I

and the quiescent current, Iq. I

SET

reference voltage generated by the ADR370 divided by R

V

SET

2 048.

=

R

SET

I

, is simply

L

is simply the

SET

SET

.

(4)

The quiescent current, Iq, varies slightly with load. The variation

in I

limits the use of this circuit to general-purpose applications.

q

REV. A

–7–

Figure 6. Programmable 0 mA to 5 mA Current Source

To optimize the resolution of this circuit, dual supply op amps

should be used because the ground potential of ADR370 can

swing from –2.048 V at zero scale to V

at full scale of the

L

potentiometer setting.

Page 8

ADR370

12-Bit Precision Programmable Current Source

By replacing the potentiometer in Figure 6 with a 12-bit precision

DAC like the AD5322, a higher precision programmable current

source can be achieved. Figure 7 illustrates the implementation

of this circuit. The load current can be determined with the

following equation.

VD

I

=

L

R

−

()

REF

×14096

SET

(6)

The compliance voltage should be kept low so that the supply

voltage to U2, between V

U1

+5V

ADR370

V

IN

GND

V

+5V

OUT

and GND, does not fall below 2.5 V.

DD

IN

VREF (1 – D2/N)

V

O

1

OP1177

AD5322

+5V

U3

V+

V–

11

–5V

2

3

R

R

TOL ±0.05%

L

SET

V

L

I

L

U2

V

V

DD

GND

Figure 7. 12-Bit Programmable Current Source

Precision Boosted Output Regulator

A precision voltage output with boosted current can be realized

with the circuit shown in Figure 8. In this circuit, V

is maintained

O

by the ADR370 at 2.048 V.

The ADR370 sources a maximum of 5 mA if the load current,

I

, is more than 5 mA, current is furnished by the transistor, Q1,

L

and the input voltage supply V

10k⍀

4V TO 12V

R1

V

DD

DD

.

2N3906

Q1

ADR370

V

IN

GND

V

OUT

R

LIL

Figure 8. Precision Boosted Output Regulator

Q1 will be turned on to regulate current as needed. R1 is required

to bias the base of Q1 and must be large enough to comply with

the supply current requirements of the ADR370. The supply

voltage can be as low as 4 V.

The maximum current output of this circuit is limited by the

power dissipation of the bipolar transistor, Q1.

PV I

=−

()

DISS DD L

×2 048.

(7)

Using the 2N3906 PNP transistor shown in Figure 8 and a 4 V

power supply, R

should be chosen so that a maximum of 100 mA

L

is drawn from the circuit, which limits the power dissipation of

Q1 to ~200 mW.

–8–

REV. A

Page 9

ADR370

3.04

2.90

2.80

PIN 1

1.40

1.30

1.20

2.64

2.10

1.90 BSC

1

2

3

SEATING

PLANE

1.12

0.89

0.10

0.01

0.50

0.30

0.20

0.08

0.60

0.50

0.40

0.95 BSC

COMPLIANT TO JEDEC STANDARDS TO-236AB

1.55

1.50

1.50

8.30

8.00

7.70

DIRECTION OF UNREELING

7" REEL 100.00

13" REEL 330.00

20.20

MIN

TAPE AND REEL DIMENSIONS

Dimensions shown in millimeters.

OR

3.20

3.10

2.90

1.50 MIN

4.10

4.00

3.90

2.05

2.00

1.95

1.00 MIN

13.20

13.00

12.80

3.55

3.50

3.45

0.75 MIN

1.10

1.00

0.90

1.85

1.75

1.65

2.80

2.70

2.60

14.40 MAX

7" REEL 50.00 MIN

OR

13" REEL 100.00 MIN

0.35

0.30

0.25

OUTLINE DIMENSIONS

3-Lead Small Outline Transistor Package [SOT-23-3]

(RT-3)

Dimensions shown in millimeters.

REV. A

9.90

8.40

8.40

–9–

Page 10

ADR370

Revision History

Location Page

7/03—Data Sheet changed from REV. 0 to REV. A.

Updated FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Updated Table I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Updated ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Updated ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Updated ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Updated PARAMETER DEFINITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Updated OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

–10–

REV. A

Page 11

–11–

Page 12

C03432–0–7/03(A)

–12–

Loading...

Loading...