Page 1

Micropower, High Accuracy

Data Sheet

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

FEATURES

Maximum temperature coefficient: 5 ppm/°C (B grade)

Low long-term drift (LTD): 30 ppm (initial 1 khr typical)

Initial output voltage error: ±0.1% (maximum)

Operating temperature range: −40°C to +125°C

Output current: +10 mA source/−3 mA sink

Low quiescent current: 100 μA (maximum)

Low dropout voltage: 250 mV at 2 mA

Output voltage noise (0.1 Hz to 10 Hz): 29 μV p-p at

4.096 V (typical)

Qualified for automotive applications

APPLICATIONS

Automotive battery monitors

Portable instrumentation

Process transmitters

Remote sensors

Medical instrumentation

Voltage References

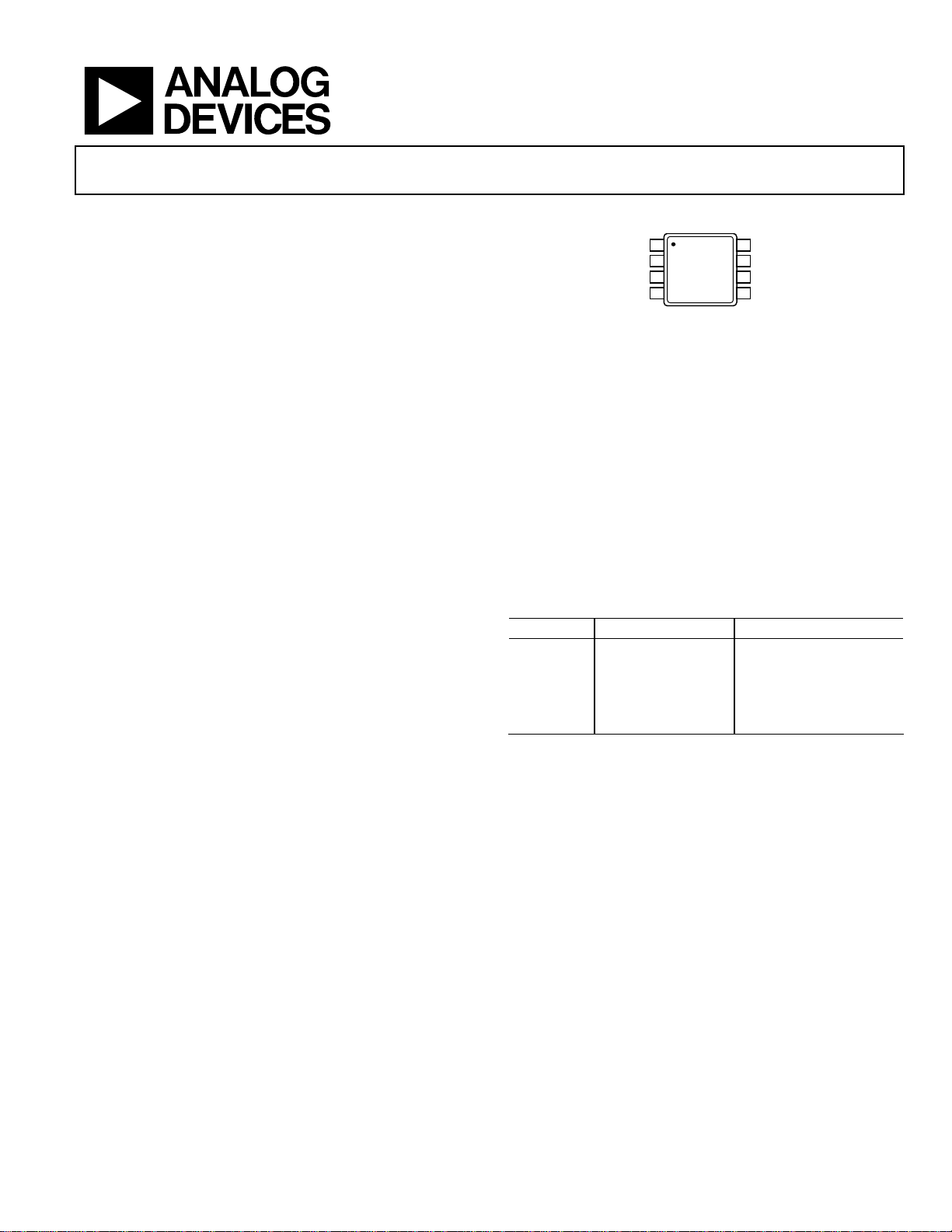

PIN CONFIGURATION

ENABLE

GND SENSE

GND FORCE

NOTES

1. NC = NO CONNECT. DO NOT

CONNECT TO THI S PIN.

1

ADR35xx

2

TOP VIEW

3

(Not to Scale)

4

NC

Figure 1. 8-Lead MSOP (RM-8 Suffix)

8

V

IN

V

SENSE

7

OUT

V

FORCE

6

OUT

5

NC

09594-001

GENERAL DESCRIPTION

The ADR3525W, ADR3530W, ADR3533W, ADR3540W, and

ADR3550W are low cost, low power, high precision CMOS

voltage references, featuring a maximum temperature coefficient (TC) of 5 ppm/°C (B grade), 8 ppm/°C (A grade), low

operating current, and low output noise in an 8-lead MSOP

package. For high accuracy, the output voltage and temperature

coefficient are trimmed digitally during final assembly using the

Analog Devices, Inc., patented DigiTrim® technology.

The low output voltage hysteresis and low long-term output

voltage drift improve lifetime system accuracy.

These CMOS references are available in five output voltages, all

of which are specified over the automotive temperature range of

−40°C to +125°C.

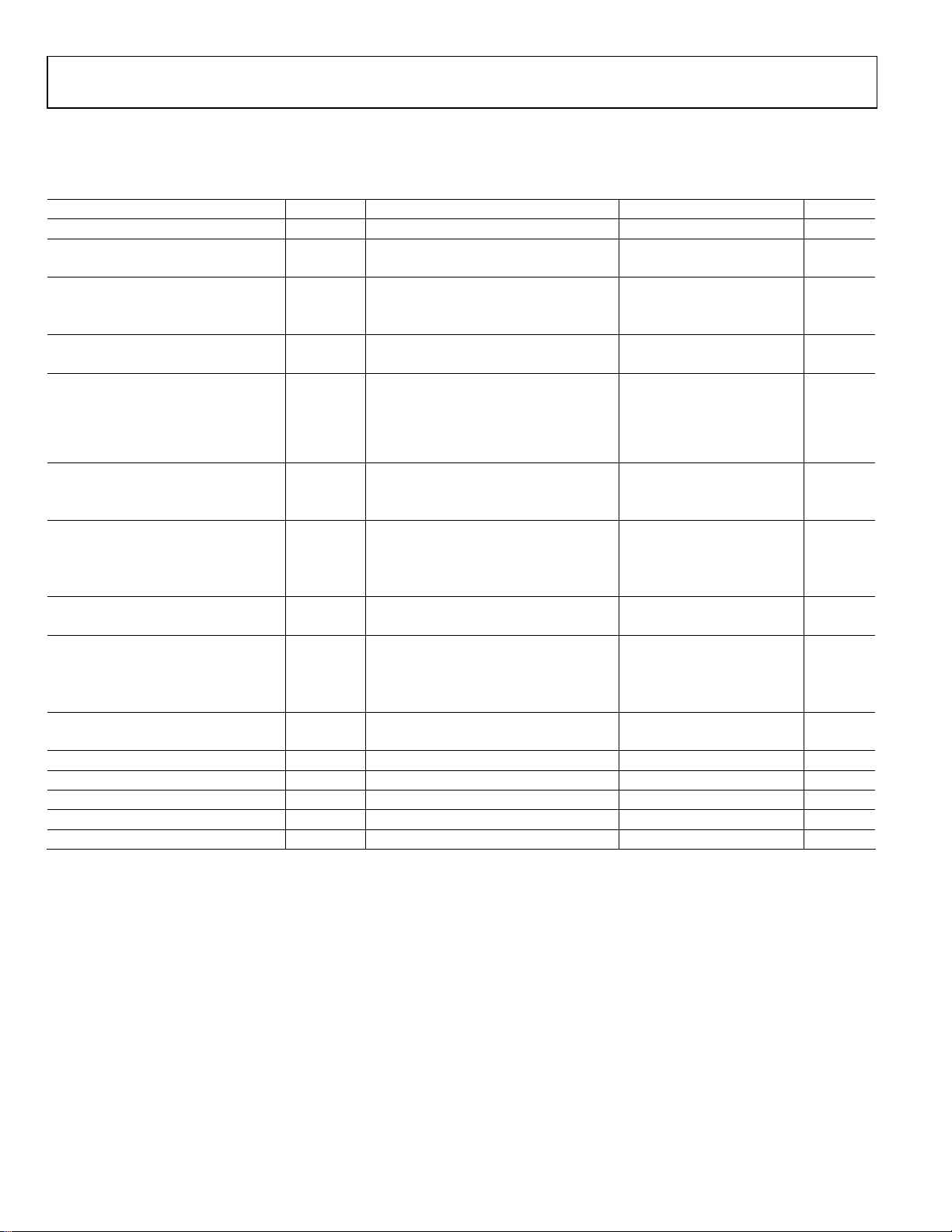

Table 1. Selection Guide

Model Output Voltage (V) Input Voltage Range ( V)

ADR3525W 2.500 2.7 to 5.5

ADR3530W 3.000 3.2 to 5.5

ADR3533W 3.300 3.5 to 5.5

ADR3540W 4.096 4.3 to 5.5

ADR3550W 5.000 5.2 to 5.5

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

Page 2

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Pin Configuration ............................................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

ADR3525 Electrical Characteristics .......................................... 3

ADR3530 Electrical Characteristics .......................................... 4

ADR3533 Electrical Characteristics .......................................... 5

ADR3540 Electrical Characteristics .......................................... 6

ADR3550 Electrical Characteristics .......................................... 7

Absolute Maximum Ratings ............................................................ 8

Thermal Resistance ...................................................................... 8

ESD Caution .................................................................................. 8

Pin Configuration and Function Descriptions ............................. 9

Typical Performance Characteristics ........................................... 10

Terminology .................................................................................... 16

Theory of Operation ...................................................................... 17

Long-Term Output Voltage Drift ............................................. 17

Power Dissipation....................................................................... 17

Applications Information .............................................................. 18

Basic Voltage Reference Connection ....................................... 18

Input and Output Capacitors .................................................... 18

4-Wire Kelvin Connections ...................................................... 18

VIN Slew Rate Considerations ................................................... 18

Shutdown/Enable Feature ......................................................... 18

Sample Applications ................................................................... 19

Outline Dimensions ....................................................................... 20

Ordering Guide .......................................................................... 20

Automotive Products ................................................................. 20

REVISION HISTORY

9/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 20

Page 3

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

SPECIFICATIONS

ADR3525 ELECTRICAL CHARACTERISTICS

VIN = 2.7 V to 5.5 V, IL = 0 mA, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

INITIAL OUTPUT VOLTAGE ERROR V

±2.5 mV

TEMPERATURE COEFFICIENT TCV

A Grade 2.5 8 ppm/°C

B Grade 2.5 5 ppm/°C

LINE REGULATION ∆V

V

LOAD REGULATION ∆V

Sourcing

Sinking

OUTPUT CURRENT CAPACITY IL

Sourcing VIN = 3.0 V to 5.5 V 10 mA

Sinking VIN = 3.0 V to 5.5 V −3 mA

QUIESCENT CURRENT IQ

Normal Operation ENABLE ≥ VIN × 0.85 85 A

ENABLE = VIN, −40°C ≤ TA ≤ +125°C 100 A

Shutdown ENABLE ≤ 0.7 V 5 A

DROPOUT VOLTAGE1 V

I

ENABLE PIN

Shutdown Voltage VL 0 0.7 V

ENABLE Voltage VH V

ENABLE Pin Leakage Current IEN ENABLE = VIN, TA = −40°C ≤ TA ≤ +125°C 1 3 A

OUTPUT VOLTAGE NOISE en p-p f = 0.1 Hz to 10 Hz 18 V p-p

f = 10 Hz to 10 kHz 42 V rms

OUTPUT VOLTAGE NOISE DENSITY en f = 1 kHz 1 µV/√Hz

OUTPUT VOLTAGE HYSTERESIS2 ∆V

RIPPLE REJECTION RATIO RRR fIN = 60 Hz −60 dB

LONG-TERM OUTPUT VOLTAGE DRIFT ∆V

TURN-ON SETTLING TIME tR C

1

Refers to the minimum difference between VIN and V

2

See the section. The part is placed through the temperature cycle in the order of temperatures shown.

Terminology

2.4975 2.500 2.5025 V

OUT

±0.1 %

OERR

−40°C ≤ TA ≤ +125°C

OUT

/∆VIN VIN = 2.7 V to 5.5 V 5 50 ppm/V

OUT

= 2.7 V to 5.5 V, −40°C ≤ TA ≤ +125°C 120 ppm/V

IN

/∆IL

OUT

= 0 mA to 10 mA,

I

L

= 3.0 V, −40°C ≤ TA ≤ +125°C

V

IN

= 0 mA to −3 mA,

I

L

V

= 3.0 V, −40°C ≤ TA ≤ +125°C

IN

I

DO

OUT_HYS

OUT_LTD

such that V

OUT

= 0 mA, TA = −40°C ≤ TA ≤ +125°C 50 200 mV

L

= 2 mA, TA = −40°C ≤ TA ≤ +125°C 75 250 mV

L

TA = +25°C to −40°C to +125°C to +25°C 70 ppm

1000 hours at 50°C 30 ppm

= 0.1 F, CL = 0.1 F, RL = 1 kΩ 600 s

IN

maintains a minimum accuracy of 0.1%. See the Termin section. ology

OUT

10 30 ppm/mA

10 50 ppm/mA

× 0.85 VIN V

IN

Rev. 0 | Page 3 of 20

Page 4

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

ADR3530 ELECTRICAL CHARACTERISTICS

VIN = 3.2 V to 5.5 V, IL = 0 mA, TA = 25°C, unless otherwise noted.

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

INITIAL OUTPUT VOLTAGE ERROR V

±3.0 mV

TEMPERATURE COEFFICIENT TCV

A Grade 2.5 8 ppm/°C

B Grade 2.5 5 ppm/°C

LINE REGULATION ∆V

V

LOAD REGULATION ∆V

Sourcing

Sinking

OUTPUT CURRENT CAPACITY IL

Sourcing VIN = 3.5 V to 5.5 V 10 mA

Sinking VIN = 3.5 V to 5.5 V −3 mA

QUIESCENT CURRENT IQ

Normal Operation ENABLE ≥ VIN × 0.85 85 A

ENABLE = VIN, −40°C ≤ TA ≤ +125°C 100 A

Shutdown ENABLE ≤ 0.7 V 5 A

DROPOUT VOLTAGE1 V

I

ENABLE PIN

Shutdown Voltage VL 0 0.7 V

ENABLE Voltage VH V

ENABLE Pin Leakage Current IEN ENABLE = VIN, TA = −40°C ≤ TA ≤ +125°C 0.85 3 A

OUTPUT VOLTAGE NOISE en p-p f = 0.1 Hz to 10 Hz 22 V p-p

f = 10 Hz to 10 kHz 45 V rms

OUTPUT VOLTAGE NOISE DENSITY en f = 1 kHz 1.1 µV/√Hz

OUTPUT VOLTAGE HYSTERESIS2 ∆V

RIPPLE REJECTION RATIO RRR fIN = 60 Hz −60 dB

LONG-TERM OUTPUT VOLTAGE DRIFT ∆V

TURN-ON SETTLING TIME tR C

1

Refers to the minimum difference between VIN and V

2

Terminology

See the section. The part is placed through the temperature cycle in the order of temperatures shown.

2.9970 3.0000 3.0030 V

OUT

±0.1 %

OERR

−40°C ≤ TA ≤ +125°C

OUT

/∆VIN VIN = 3.2 V to 5.5 V 5 50 ppm/V

OUT

= 3.2 V to 5.5 V, −40°C ≤ TA ≤ +125°C 120 ppm/V

IN

/∆IL

OUT

= 0 mA to 10 mA,

I

L

= 3.5 V, −40°C ≤ TA ≤ +125°C

V

IN

= 0 mA to −3 mA,

I

L

V

= 3.5 V, −40°C ≤ TA ≤ +125°C

IN

I

DO

OUT_HYS

OUT_LTD

such that V

OUT

= 0 mA, TA = −40°C ≤ TA ≤ +125°C 50 200 mV

L

= 2 mA, TA = −40°C ≤ TA ≤ +125°C 75 250 mV

L

TA = +25°C to −40°C to +125°C to +25°C 70 ppm

1000 hours at 50°C 30 ppm

= 0.1 F, CL = 0.1 F, RL = 1 kΩ 700 s

IN

maintains a minimum accuracy of 0.1%. See the Termin section. ology

OUT

9 30 ppm/mA

10 50 ppm/mA

× 0.85 VIN V

IN

Rev. 0 | Page 4 of 20

Page 5

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

ADR3533 ELECTRICAL CHARACTERISTICS

VIN = 3.5 V to 5.5 V, IL = 0 mA, TA = 25°C, unless otherwise noted.

Table 4.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

OUTPUT VOLTAGE V

INITIAL OUTPUT VOLTAGE ERROR V

±3.3 mV

TEMPERATURE COEFFICIENT TCV

A Grade 2.5 8 ppm/°C

B Grade 2.5 5 ppm/°C

LINE REGULATION ∆V

V

LOAD REGULATION ∆V

Sourcing

Sinking

OUTPUT CURRENT CAPACITY IL

Sourcing VIN = 3.8 V to 5.5 V 10 mA

Sinking VIN = 3.8 V to 5.5 V −3 mA

QUIESCENT CURRENT IQ

Normal Operation ENABLE ≥ VIN × 0.85 85 A

ENABLE = VIN, −40°C ≤ TA ≤ +125°C 100 A

Shutdown ENABLE ≤ 0.7 V 5 A

DROPOUT VOLTAGE1 V

I

ENABLE PIN

Shutdown Voltage VL 0 0.7 V

ENABLE Voltage VH V

ENABLE Pin Leakage Current IEN ENABLE = VIN, TA = −40°C ≤ TA ≤ +125°C 0.85 3 A

OUTPUT VOLTAGE NOISE en p-p f = 0.1 Hz to 10 Hz 25 V p-p

f = 10 Hz to 10 kHz 46 V rms

OUTPUT VOLTAGE NOISE DENSITY en f = 1 kHz 1.2 µV/√Hz

OUTPUT VOLTAGE HYSTERESIS2 ∆V

RIPPLE REJECTION RATIO RRR fIN = 60 Hz −60 dB

LONG-TERM OUTPUT VOLTAGE DRIFT ∆V

TURN-ON SETTLING TIME tR C

1

Refers to the minimum difference between VIN and V

2

Terminology

See the section. The part is placed through the temperature cycle in the order of temperatures shown.

3.2967 3.3000 3.3033 V

OUT

±0.1 %

OERR

−40°C ≤ TA ≤ +125°C

OUT

/∆VIN VIN = 3.5 V to 5.5 V 5 50 ppm/V

OUT

= 3.5 V to 5.5 V, −40°C ≤ TA ≤ +125°C 120 ppm/V

IN

/∆IL

OUT

= 0 mA to 10 mA,

I

L

= 3.8 V, −40°C ≤ TA ≤ +125°C

V

IN

= 0 mA to −3 mA,

I

L

V

= 3.8 V, −40°C ≤ TA ≤ +125°C

IN

I

DO

OUT_HYS

OUT_LTD

OUT

= 0 mA, TA = −40°C ≤ TA ≤ +125°C 50 200 mV

L

= 2 mA, TA = −40°C ≤ TA ≤ +125°C 75 250 mV

L

TA = +25°C to −40°C to +125°C to +25°C 70 ppm

1000 hours at 50°C 30 ppm

= 0.1 F, CL = 0.1 F, RL = 1 kΩ 750 s

IN

such that V

maintains a minimum accuracy of 0.1%. See the Termin section. ology

OUT

9 30 ppm/mA

10 50 ppm/mA

× 0.85 VIN V

IN

Rev. 0 | Page 5 of 20

Page 6

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

ADR3540 ELECTRICAL CHARACTERISTICS

VIN = 4.3 V to 5.5 V, IL = 0 mA, TA = 25°C, unless otherwise noted.

Table 5.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

OUTPUT VOLTAGE V

INITIAL OUTPUT VOLTAGE ERROR V

±4.096 mV

TEMPERATURE COEFFICIENT TCV

A Grade 2.5 8 ppm/°C

B Grade 2.5 5 ppm/°C

LINE REGULATION ∆V

V

LOAD REGULATION ∆V

Sourcing

Sinking

OUTPUT CURRENT CAPACITY IL

Sourcing VIN = 4.6 V to 5.5 V 10 mA

Sinking VIN = 4.6 V to 5.5 V −3 mA

QUIESCENT CURRENT IQ

Normal Operation ENABLE ≥ VIN × 0.85 85 A

ENABLE = VIN, −40°C ≤ TA ≤ +125°C 100 A

Shutdown ENABLE ≤ 0.7 V 5 A

DROPOUT VOLTAGE1 V

I

ENABLE PIN

Shutdown Voltage VL 0 0.7 V

ENABLE Voltage VH V

ENABLE Pin Leakage Current IEN ENABLE = VIN, TA = −40°C ≤ TA ≤ +125°C 0.85 3 A

OUTPUT VOLTAGE NOISE en p-p f = 0.1 Hz to 10 Hz 29 V p-p

f = 10 Hz to 10 kHz 53 V rms

OUTPUT VOLTAGE NOISE DENSITY en f = 1 kHz 1.4 µV/√Hz

OUTPUT VOLTAGE HYSTERESIS2 ∆V

RIPPLE REJECTION RATIO RRR fIN = 60 Hz −60 dB

LONG-TERM OUTPUT VOLTAGE DRIFT ∆V

TURN-ON SETTLING TIME tR C

1

Refers to the minimum difference between VIN and V

2

Terminology

See the section. The part is placed through the temperature cycle in the order of temperatures shown.

4.0919 4.0960 4.1000 V

OUT

±0.1 %

OERR

−40°C ≤ TA ≤ +125°C

OUT

/∆VIN VIN = 4.3 V to 5.5 V 3 50 ppm/V

OUT

= 4.3 V to 5.5 V, −40°C ≤ TA ≤ +125°C 120 ppm/V

IN

/∆IL

OUT

= 0 mA to 10 mA,

I

L

= 4.6 V, −40°C ≤ TA ≤ +125°C

V

IN

= 0 mA to −3 mA,

I

L

V

= 4.6 V, −40°C ≤ TA ≤ +125°C

IN

I

DO

OUT_HYS

OUT_LTD

such that V

OUT

= 0 mA, TA = −40°C ≤ TA ≤ +125°C 50 200 mV

L

= 2 mA, TA = −40°C ≤ TA ≤ +125°C 75 250 mV

L

TA = +25°C to −40°C to +125°C to +25°C 70 ppm

1000 hours at 50°C 30 ppm

= 0.1 F, CL = 0.1 F, RL = 1 kΩ 800 s

IN

maintains a minimum accuracy of 0.1%. See the Termin section. ology

OUT

6 30 ppm/mA

15 50 ppm/mA

× 0.85 VIN V

IN

Rev. 0 | Page 6 of 20

Page 7

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

ADR3550 ELECTRICAL CHARACTERISTICS

VIN = 5.2 V to 5.5 V, TA = 25°C, I

Table 6.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

OUTPUT VOLTAGE V

INITIAL OUTPUT VOLTAGE ERROR V

±5.0 mV

TEMPERATURE COEFFICIENT TCV

A Grade 2.5 8 ppm/°C

B Grade 2.5 5 ppm/°C

LINE REGULATION ∆V

V

LOAD REGULATION ∆V

Sourcing

Sinking

OUTPUT CURRENT CAPACITY I

Sourcing VIN = 5.5 V 10 mA

Sinking VIN = 5.5 V −3 mA

QUIESCENT CURRENT IQ

Normal Operation ENABLE > VIN × 0.85 85 A

ENABLE = VIN, −40°C ≤ TA ≤ +125°C 100 A

Shutdown ENABLE < 0.7 V 5 A

DROPOUT VOLTAGE1 V

I

ENABLE PIN

Shutdown Voltage VL 0 0.7 V

ENABLE Voltage VH V

ENABLE Pin Leakage Current IEN ENABLE = VIN, −40°C ≤ TA ≤ +125°C 0.85 3 A

OUTPUT VOLTAGE NOISE en p-p f = 0.1 Hz to 10 Hz 35 V p-p

f = 10 Hz to 10 kHz 60 V rms

OUTPUT VOLTAGE NOISE DENSITY en f = 1 kHz 1.5 V/√Hz

OUTPUT VOLTAGE HYSTERESIS2 ∆V

RIPPLE REJECTION RATIO RRR fIN = 60 Hz −58 dB

LONG-TERM OUTPUT VOLTAGE DRIFT ∆V

TURN-ON SETTLING TIME tR C

1

Refers to the minimum difference between VIN and V

2

Terminology

See the section. The part is placed through the temperature cycle in the order of temperatures shown.

= 0 mA, unless otherwise noted.

LOAD

4.995 5.000 5.005 V

OUT

±0.1 %

OERR

−40°C ≤ TA ≤ +125°C

OUT

/∆VIN VIN = 5.2 V to 5.5 V 3 50 ppm/V

OUT

= 5.2 V to 5.5 V, −40°C ≤ TA ≤ +125°C 120 ppm/V

IN

/∆IL

OUT

= 0 mA to 10 mA,

I

L

= 5.5 V, −40°C ≤ TA ≤ +125°C

V

IN

= 0 mA to −3 mA,

I

L

V

= 5.5 V, −40°C ≤ TA ≤ +125°C

IN

L

I

DO

OUT_HYS

OUT_LTD

OUT

= 0 mA, −40°C ≤ TA ≤ +125°C 50 200 mV

L

= 2 mA, −40°C ≤ TA ≤ +125°C 75 250 mV

L

TA = +25°C to −40°C to +125°C to +25°C 70 ppm

1000 hours at 50°C 30 ppm

= 0.1 F, CL = 0.1 F, RL = 1 kΩ 900 s

IN

such that V

maintains a minimum accuracy of 0.1%. See the Termin section. ology

OUT

3 30 ppm/mA

19 50 ppm/mA

× 0.85 VIN V

IN

Rev. 0 | Page 7 of 20

Page 8

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 7.

Parameter Rating

Supply Voltage 6 V

ENABLE to GND SENSE Voltage VIN

Operating Temperature Range −40°C to +125°C

Storage Temperature Range −65°C to +150°C

Junction Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 8. Thermal Resistance

Package Type θJA θ

8-Lead MSOP (RM-8 Suffix) 132.5 43.9 °C/W

Unit

JC

ESD CAUTION

Rev. 0 | Page 8 of 20

Page 9

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

ENABLE

GND SENSE

GND FORCE

NOTES

1. NC = NO CONNECT. DO NOT

CONNECT TO THI S PIN.

NC

1

ADR35xx

2

TOP VIEW

3

(Not to Scale)

4

Figure 2. Pin Configuration

Table 9. Pin Function Descriptions

Pin No. Mnemonic Description

1 ENABLE Enable Connection. Enables or disables the device.

2 GND SENSE Ground Voltage Sense Connection. Connect directly to the point of lowest potential in the application.

3 GND FORCE Ground Force Connection.

4 NC No Connect. Do not connect to this pin.

5 NC No Connect. Do not connect to this pin.

6 V

7 V

FORCE Reference Voltage Output.

OUT

SENSE Reference Voltage Output Sensing Connection. Connect directly to the voltage input of the load devices.

OUT

8 VIN Input Voltage Connection.

8

V

IN

V

SENSE

7

OUT

V

FORCE

6

OUT

5

NC

09594-002

Rev. 0 | Page 9 of 20

Page 10

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

A

A

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, unless otherwise noted.

2.5010

VIN = 5.5V

2.5008

2.5006

2.5004

2.5002

2.5000

2.4998

2.4996

OU T PU T VO LTAG E (V )

2.4994

2.4992

2.4990

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (º C)

Figure 3. ADR3525 Output Voltage vs. Temperature

40

35

30

25

20

15

NUMBER OF DEVICES

10

5

0

01234567891011

TEMPERATURE COEFFICIENT (ppm/° C)

Figure 4. ADR3525 Temperature Coefficient Distribution

24

ADR3525

22

ADR3530

ADR3533

20

ADR3540

ADR3550

18

16

14

TION (ppm/V)

12

10

8

6

LOAD REGUL

4

2

0

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

IL = 0mA TO 10mA

SOURCING

Figure 5. Load Regulation vs. Temperature (Sourcing)

09594-003

09594-004

09594-005

5.0025

VIN = 5.5V

5.0020

5.0015

5.0010

5.0005

5.0000

4.9995

4.9990

OUTPUT VOLTAGE (V)

4.9985

4.9980

4.9975

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (ºC)

Figure 6. ADR3550 Output Voltage vs. Temperature

45

40

35

30

25

20

15

NUMBER OF DEVI CES

10

5

0

01234567891011

TEMPERATURE COEFFICIENT (pp m/°C)

Figure 7. ADR3550 Temperature Coefficient Distribution

35

ADR3525

ADR3530

ADR3533

30

ADR3540

ADR3550

25

TION (ppm/V)

20

15

LOAD REGUL

10

5

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

IL = 0mA TO –3mA

SINKING

Figure 8. Load Regulation vs. Temperature (Sinking)

09594-006

09594-007

09594-008

Rev. 0 | Page 10 of 20

Page 11

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

A

A

A

400

–40°C

+25°C

350

+125°C

300

250

200

L VOLTAGE (mV)

150

100

DIFFERE NTI

50

0

–3 –2 –1 0 1 2 3 4 5 6 7 8 9 10

LOAD CURRENT (mA)

Figure 9. ADR3525 Dropout Voltage vs. Load Current

350

300

250

–40°C

+25°C

+125°C

09594-009

1

10µV/DIV

TIME = 1s/DIV

CH1 pk-pk = 18µV CH1 RMS = 3.14µV

Figure 12. ADR3525 Output Voltage Noise (0.1 Hz to 10 Hz)

09594-012

200

L VOLTAGE (mV)

150

100

DIFFERE NTI

50

0

–3 –2 –1 0 1 2 3 4 5 6 7 8 9 10

LOAD CURRENT (mA)

Figure 10. ADR3550 Dropout Voltage vs. Load Current

140

ADR3525

ADR3530

120

ADR3533

ADR3540

ADR3550

100

80

TION (ppm/V)

60

40

LINE REGUL

20

0

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

Figure 11. Line Regulation vs. Temperature

1

100µV/DIV

TIME = 1s/DIV

CH1 pk-pk = 300µV CH1 RMS = 42.0µV

09594-010

09594-013

Figure 13. ADR3525 Output Voltage Noise (10 Hz to 10 kHz)

12

10

8

6

4

NOISE DENSITY (µV p-p/ Hz)

2

0

0.1 1 10 100 1k 10k

09594-011

FREQUENC Y (Hz)

09594-014

Figure 14. ADR3525 Output Noise Spectral Density

Rev. 0 | Page 11 of 20

Page 12

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

R

A

0

CL = 1.1µF

)

–10

IN

/V

–20

OUT

–30

TIO (dB V

–40

–50

–60

–70

–80

RIPPLE REJECTIO N

–90

= 0.1µF

C

IN

10 100 1k 10k 100k

FREQUENC Y (Hz)

Figure 15. ADR3525 Ripple Rejection Ratio vs. Frequency

CIN = CL = 0.1µF

R

=

L

1

VIN = 2V/DIV

1

10µV/DIV

CH1 pk-pk = 33.4µV CH1 RMS = 5.68µV

09594-015

09594-018

Figure 18. ADR3550 Output Voltage Noise (0.1 Hz to 10 Hz)

1

2

V

= 1V/DIV

OUT

TIME = 200µs/DIV

Figure 16. ADR3525 Start-Up Response

ENABLE

1

2

V

= 1V/DIV

ENABLE

V

= 3.0V

IN

C

= CL = 0.1µF

IN

R

=

L

V

= 1V/DIV

OUT

TIME = 200µs/DIV

Figure 17. ADR3525 Restart Response from Shutdown

100µV/DIV

9594-016

CH1 pk-pk = 446µV CH1 RMS = 60. 3µV

09594-019

Figure 19. ADR3550 Output Voltage Noise (10 Hz to 10 kHz)

12

10

8

6

4

NOISE DENSITY (µV p-p/ Hz)

2

9594-017

0

0.1 1 10 100 1k 10k

FREQUENCY (Hz)

09594-020

Figure 20. ADR3550 Output Noise Spectral Density

Rev. 0 | Page 12 of 20

Page 13

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

A

V

0

CL = 1.1µF

)

C

= 0.1µF

IN

–10

IN

/V

–20

OUT

–30

TIO (dB

–40

–50

–60

–70

–80

RIPPLE REJECTION R

–90

10 100 1k 10k 100k

FREQUENC Y (Hz)

Figure 21. ADR3550 Ripple Rejection Ratio vs. Frequency

CIN = 0µF

C

= 0.1µF

L

R

=

V

IN

2V/DIV

1

L

09594-021

1

2

500mV/DIV

ENABLE

1V/DIV

CIN = CL = 0.1µF

V

= 3V

IN

R

= 1k

L

V

= 1V/DIV

OUT

TIME = 200µs/DIV

Figure 24. ADR3525 Shutdown Response

CIN = CL = 0.1µF

3.2V

2.7V

9594-024

V

OUT

2V/DIV

2

TIME = 200µs/DIV

Figure 22. ADR3550 Start-Up Response

ENABLE

1

2

V

= 2V/DIV

ENABLE

V

= 5.5V

IN

C

= CL = 0.1µF

IN

R

=

L

V

= 2V/DIV

OUT

TIME = 200µs/DIV

Figure 23. ADR3550 Restart Response from Shutdown

2

V

= 10mV/DIV

OUT

9594-022

1

TIME = 1ms/DIV

09594-025

Figure 25. ADR3525 Line Transient Response

V

OUT

SOURCING

= 20mV/DIV

SINKING

TIME = 1ms/ DIV

+10mA

–3mA

2.5V

9594-026

I

L

SINKING

CIN = 0.1µF

C

= 0.1µF

L

R

= 250

L

9594-023

Figure 26. ADR3525 Load Transient Response

Rev. 0 | Page 13 of 20

Page 14

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

100

VIN = 5.5 V

90

80

ENABLE

2V/DIV

1

V

2

VIN = 100mV/DIV

1

2

V

OUT

CIN = CL = 0.1µF

V

= 5V

IN

R

= 1k

L

= 2V/DIV

OUT

TIME = 200µs/DIV

Figure 27. ADR3550 Shutdown Response

CIN = CL = 0.1µF

= 5mV/DIV

TIME = 1ms/DIV

Figure 28. ADR3550 Line Transient Response

5.5V

5.2V

09594-027

09594-028

70

60

50

40

30

SUPPLY CURRENT (µA)

20

10

0

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

Figure 30. Supply Current vs. Temperature

2.0

–40°C

+25°C

1.8

+125°C

1.6

1.4

1.2

1.0

0.8

0.6

SUPPLY CURRENT (mA)

0.4

0.2

0

0

20 30 40 50 60 70 80 90 100

10

ENABLE VOLTAGE (% of VIN)

Figure 31. Supply Current vs. ENABLE Pin Voltage

10

CL = 0.1µF

= 1.1µF

C

L

09594-030

09594-031

I

L

SINKING

CIN = 0.1µF

C

= 0.1µF

L

R

= 500

L

V

OUT

SOURCING

= 20mV/DIV

TIME = 1ms/DIV

Figure 29. ADR3550 Load Transient Response

SINKING

+10mA

–3mA

5.0V

09594-029

Rev. 0 | Page 14 of 20

1

0.1

OUTPUT IMPEDANCE ( )

0.01

0.01 0.1 1 10 100 1k 10k

FREQUENCY (Hz)

Figure 32. ADR3550 Output Impedance vs. Frequency

09594-032

Page 15

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

9

8

7

6

5

4

3

NUMBER OF DEVICES

2

1

0

–0.008

–0.010

–0.006

0

0.002

–0.004

–0.002

RELATIVE SHIFT IN V

0.004

0.006

0.008

0.010

0.012

0.014

0.016

0.018

0.020

(%)

OUT

Figure 33. Output Voltage Drift Distribution After Reflow (SHR Drift)

8

TA = +25°C –40°C +125°C +25°C

7

6

09594-033

80

60

40

20

0

–20

–40

–60

LONG-T ERM OUTPUT VOLTAGE DRIFT (p pm)

–80

0 200 400 800600 1000

ELAPSED TIME (Hours)

Figure 35. ADR3550 Typical Long-Term Output Voltage Drift

(Four Devices, 1000 Hours)

09594-035

5

4

3

NUMBER OF DEVI CES

2

1

0

–90

–80

–70

–60

–50

–150

–140

–130

–120

–110

–100

OUTPUT VOLTAGE HYSTERESIS (ppm)

–40

0

102030

–30

–20

–10

40

Figure 34. ADR3550 Thermally Induced Output Voltage Hysteresis Distribution

09594-034

Rev. 0 | Page 15 of 20

Page 16

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

TERMINOLOGY

Dropout Voltage (VDO)

Dropout voltage, sometimes referred to as supply voltage

headroom or supply-output voltage differential, is defined as

the minimum voltage differential between the input and output

such that the output voltage is maintained to within 0.1%

accuracy.

V

= (VIN − V

DO

OUT)min

| IL = constant

Because the dropout voltage depends upon the current passing

through the device, it is always specified for a given load current.

In series-mode devices, dropout voltage typically increases

proportionally to load current (see Figure 9 and Figure 10).

Temperature Coefficient (TCV

OUT

)

The temperature coefficient relates the change in output voltage

to the change in ambient temperature of the device, as normalized

by the output voltage at 25°C. This parameter is expressed in

ppm/°C and can be determined by the following equations:

)},(min{)},(max{

TTTV

OUT

122

OUT

232

TTVTTV

21

)()(

)()(

×

)},(min{)},(max{

TTVTTV

32

×

TCV

TCV

OUT

OUT

−

=

1

=

2

OUT

6

OUT

6

21

TTTV

OUT

]/[10

Cppm

°

32

OUT

]/[10

Cppm

°

TCVTCVTCV =

−×

−

−×

},max{

(1)

2OUTOUT1OUT

where:

V

(T) is the output voltage at Temperature T.

OUT

= −40°C.

T

1

T

= +25°C.

2

= +125°C.

T

3

This three-point method ensures that TCV

accurately

OUT

portrays the maximum difference between any of the three

temperatures at which the output voltage of the part is

measured.

Thermally Induced Output Voltage Hysteresis (ΔV

OUT_HYS

)

Thermally induced output voltage hysteresis represents the

change in output voltage after the device is exposed to a

specified temperature cycle. This is expressed as either a shift in

voltage or a difference in ppm from the nominal output.

VCVV

)25( −°=Δ

)25(

−°

OUT

VCV

°

CV

V

=Δ

HYSOUT

_

[V]

TCOUTOUTHYSOUT

__

TCOUTOUT

_

)25(

6

[ppm]

10

×

where:

V

(25°C) is the output voltage at 25°C.

OUT

is the output voltage after temperature cycling.

V

OUT_TC

Long-Term Output Voltage Drift (ΔV

Long-term output voltage drift refers to the shift in output

voltage after 1000 hours of operation in a constant 50°C

environment. This is expressed as either a shift in voltage or a

difference in ppm from the nominal output.

)()(

tVtVV −=Δ

tV

OUT

OUT

0

0

)()(×−

tVtV

0

)(

_

V

=Δ

_

LTDOUT

OUTLTDOUT

OUT

1

1

OUT

where:

V

V

OUT(t0

OUT(t1

) is the V

) is the V

at 50°C at Time 0.

OUT

at 50°C after 1000 hours of operation

OUT

at 50°C.

Line Regulation

Line regulation refers to the change in output voltage in response

to a given change in input voltage and is expressed in percent

per volt, ppm per volt, or microvolts per volt change in input

voltage. This parameter accounts for the effects of self-heating.

Load Regulation

Load regulation refers to the change in output voltage in

response to a given change in load current and is expressed in

microvolts per mA, ppm per mA, or ohms of dc output

resistance. This parameter accounts for the effects of selfheating.

Solder Heat Resistance (SHR) Drift

SHR drift refers to the permanent shift in output voltage

induced by exposure to reflow soldering, expressed in units of

ppm. This is caused by changes in the stress exhibited upon the

die by the package materials when exposed to high temperatures. This effect is more pronounced in lead-free soldering

processes due to higher reflow temperatures.

OUT_LTD

[V]

6

10

)

[ppm]

Rev. 0 | Page 16 of 20

Page 17

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

V

THEORY OF OPERATION

IN

ENABLE

BAND GAP

VOLTAGE

REFERENCE

V

BG

GND FORCE

GND SENSE

Figure 36. Block Diagram

FORCE

V

OUT

V

SENSE

R

FB1

R

FB2

OUT

09594-036

The ADR3525W/ADR3530W/ADR3533W/ADR3540W/

ADR3550W use a patented voltage reference architecture to

achieve high accuracy, low temperature coefficient (TC), and

low noise in a CMOS process. Like all band gap references, the

references combine two voltages of opposite TCs to create an

output voltage that is nearly independent of ambient temperature. However, unlike traditional band gap voltage references, the

temperature-independent voltage of the references is arranged to

be the base-emitter voltage, V

temperature rather than the V

bipolar transistor at 0 K is approximately V

, of a bipolar transistor at room

BE

extrapolated to 0 K (the VBE of

BE

, the band gap

G0

voltage of silicon). A corresponding positive TC voltage is then

added to the V

voltage to compensate for its negative TC.

BE

The key benefit of this technique is that the trimming of the

initial accuracy and TC can be performed without interfering

with one another, thereby increasing overall accuracy across

temperature. Curvature correction techniques further reduce

the temperature variation.

The band gap voltage (V

) is then buffered and amplified to

BG

produce stable output voltages of 2.5 V and 5.0 V. The output

buffer can source up to 10 mA and sink up to −3 mA of load

current.

The ADR35xx references leverage Analog Devices patented

DigiTrim technology to achieve high initial accuracy and low

TC, and precision layout techniques lead to very low long-term

drift and thermal hysteresis.

LONG-TERM OUTPUT VOLTAGE DRIFT

One of the key parameters of the ADR35xx references is longterm output voltage drift. Independent of the output voltage

model and in a 50°C environment, these devices exhibit a

typical drift of approximately 30 ppm after 1000 hours of

continuous, unloaded operation.

It is important to understand that long-term output voltage drift

is not tested or guaranteed by design and that the output from

the device may shift beyond the typical 30 ppm specification.

Because most of the drift occurs in the first 200 hours of device

operation, burning in the system board with the reference

mounted can reduce subsequent output voltage drift over time.

See the AN-713 Application Note, The Effect of Long-Term Drift

on Voltage References, at www.analog.com for more information

regarding the effects of long-term drift and how it can be

minimized.

POWER DISSIPATION

The ADR35xx voltage references are capable of sourcing up to

10 mA of load current at room temperature across the rated

input voltage range. However, when used in applications subject

to high ambient temperatures, the input voltage and load current should be carefully monitored to ensure that the device

does not exceed its maximum power dissipation rating. The

maximum power dissipation of the device can be calculated via

the following equation:

TT

J

A

P

D

where:

P

is the device power dissipation.

D

is the device junction temperature.

T

J

T

is the ambient temperature.

A

is the package (junction-to-air) thermal resistance.

θ

JA

Because of this relationship, the acceptable load current in high

temperature conditions may be less than the maximum currentsourcing capability of the device. In no case should the part be

operated outside of its maximum power rating because doing so

can result in premature failure or permanent damage to the device.

][W

JA

Rev. 0 | Page 17 of 20

Page 18

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

V

V

APPLICATIONS INFORMATION

BASIC VOLTAGE REFERENCE CONNECTION

0.1µF

OUT

2.5V

V

2.7V TO

5.5V

IN

8

V

IN

1

ENABLE

AD3525/ADR3530/

0.1µF1µF

ARD3533/ADR3540/

FORCE

SENSE

6

7

V

OUT

V

OUT

ADR3550

GND SENSE

GND FORCE

2

3

Figure 37. Basic Reference Connection

The circuit shown in Figure 37 illustrates the basic configuration

for the ADR35xx references. Bypass capacitors should be

connected according to the following guidelines.

INPUT AND OUTPUT CAPACITORS

A 1 F to 10 F electrolytic or ceramic capacitor can be

connected to the input to improve transient response in

applications where the supply voltage may fluctuate. An

additional 0.1 F ceramic capacitor should be connected

in parallel to reduce high frequency supply noise.

A ceramic capacitor of at least a 0.1 F must be connected to

the output to improve stability and help filter out high frequency noise. An additional 1 F to 10 F electrolytic or

ceramic capacitor can be added in parallel to improve transient

performance in response to sudden changes in load current;

however, the designer should keep in mind that doing so

increases the turn-on time of the device.

Best performance and stability is attained with low ESR (for

example, less than 1 ), low inductance ceramic chip-type

output capacitors (X5R, X7R, or similar). If using an electrolytic

capacitor on the output, a 0.1 µF ceramic capacitor should be

placed in parallel to reduce overall ESR on the output.

4-WIRE KELVIN CONNECTIONS

Current flowing through a PCB trace produces an IR voltage

drop, and with longer traces, this drop can reach several

millivolts or more, introducing a considerable error into the

output voltage of the reference. A 1 inch long, 5 millimeter wide

trace of 1 ounce copper has a resistance of approximately

100 m at room temperature; at a load current of 10 mA, this

can introduce a full millivolt of error. In an ideal board layout,

the reference should be mounted as close to the load as possible

to minimize the length of the output traces, and, therefore, the

error introduced by voltage drop. However, in applications

where this is not possible or convenient, force and sense

connections (sometimes referred to as Kelvin sensing

connections) are provided as a means of minimizing the IR

drop and improving accuracy.

Kelvin connections work by providing a set of high impedance

voltage-sensing lines to the output and ground nodes. Because

very little current flows through these connections, the IR drop

across their traces is negligible, and the output and ground

09594-037

voltages can be sensed accurately. These voltages are fed back

into the internal amplifier and used to automatically correct for

the voltage drop across the current-carrying output and ground

lines, resulting in a highly accurate output voltage across the

load. To achieve the best performance, the sense connections

should be connected directly to the point in the load where the

output voltage should be the most accurate. See Figure 38 for an

example application.

OUTPUT CAPACITOR(S) SHOULD

BE MOUNTED AS CLOSE

FORCE PIN AS POSSIBLE.

TO V

OUT

0.1µF

8

IN

V

1

ENABLE

V

IN

OUT

V

OUT

AD3525/ADR3530/

ARD3533/ADR3540/

0.1µF

1µF

ADR3550

GND SENSE

GND FORCE

FORCE

SENSE

6

7

2

3

LOAD

SENSE CONNE CTIONS

SHOULD CONNECT AS

CLOSE TO LOAD

DEVICE AS POSSIBLE.

Figure 38. Application Showing Kelvin Connection

It is always advantageous to use Kelvin connections whenever

possible. However, in applications where the IR drop is negligible or an extra set of traces cannot be routed to the load, the

force and sense pins for both V

and GND can simply be

OUT

tied together, and the device can be used in the same way as a

normal 3-terminal reference (as shown in Figure 37).

VIN SLEW RATE CONSIDERATIONS

In applications with slow rising input voltage signals, the reference exhibits overshoot or other transient anomalies that appear

on the output. These phenomena also appear during shutdown

as the internal circuitry loses power.

To avoid such conditions, ensure that the input voltage waveform has both a rising and falling slew rate of at least 0.1 V/ms.

SHUTDOWN/ENABLE FEATURE

The ADR35xx references can be switched to a low power shutdown mode when a voltage of 0.7 V or lower is input to the

ENABLE pin. Likewise, the reference becomes operational for

ENABLE voltages of 0.85 × V

supply current drops to less than 5 A, useful in applications that

are sensitive to power consumption.

If using the shutdown feature, ensure that the ENABLE pin

voltage does not fall between 0.7 V and 0.85 × V

causes a large increase in the supply current of the device and

may keep the reference from starting up correctly (see Figure 31).

If not using the shutdown feature, however, the ENABLE pin

can simply be tied to the V

operational continuously.

or higher. During shutdown, the

IN

because this

IN

pin, and the reference remains

IN

09594-038

Rev. 0 | Page 18 of 20

Page 19

Data Sheet ADR3525/ADR3530/ADR3533/ADR3540/ADR3550

V

V

SAMPLE APPLICATIONS

Negative Reference

Figure 39 shows how to connect the ADR3550 and a standard

CMOS op amp, such as the AD8663, to provide a negative

reference voltage. This configuration provides two main

advantages: first, it requires only two devices and, therefore,

does not require excessive board space; second, and more

importantly, it does not require any external resistors, meaning

that the performance of this circuit does not rely on choosing

expensive parts with low temperature coefficients to ensure

accuracy.

+VDD

0.1µF1µF

8

1

V

IN

ENABLE

V

OUT

V

OUT

ADR3550

GND SENSE

GND FORCE

Figure 39. ADR3550 Negative Reference

In this configuration, the V

OUT

the reference sit at virtual ground, and the negative reference

voltage and load current are taken directly from the output of

the operational amplifier. Note that in applications where the

negative supply voltage is close to the reference output voltage,

a dual-supply, low offset, rail-to-rail output amplifier must be

used to ensure an accurate output voltage. The operational

amplifier must also be able to source or sink an appropriate

amount of current for the application.

Bipolar Output Reference

Figure 40 shows a bipolar reference configuration. By connecting

the output of the ADR3550 to the inverting terminal of an

operational amplifier, it is possible to obtain both positive and

negative reference voltages. R1 and R2 must be matched as

closely as possible to ensure minimal difference between the

negative and positive outputs. Resistors with low temperature

coefficients must also be used if the circuit is used in environments

with large temperature swings; otherwise, a voltage difference

develops between the two outputs as the ambient temperature

changes.

6

FORCE

7

SENSE

0.1µF

2

3

FORCE and V

AD8663

–VDD

SENSE pins of

OUT

–5V

0.1µF

IN

Boosted Output Current Reference

Figure 41 shows a configuration for obtaining higher current

drive capability from the ADR35xx references without

sacrificing accuracy. The op amp regulates the current flow

through the MOSFET until V

09594-039

the reference; current is then drawn directly from V

from the reference itself, allowing increased current drive

capability.

8

1

0.1µF1µF

Because the current-sourcing capability of this circuit depends

only on the I

can be adjusted to the application simply by choosing an

appropriate MOSFET. In all cases, the V

be tied directly to the load device to maintain maximum output

voltage accuracy.

8

1

0.1µF1µF

V

IN

ENABLE

ADR3550

V

OUT

V

OUT

GND SENSE

GND FORCE

FORCE

SENSE

6

7

0.1µF

2

3

ADA4000-1

R3

5k

R1

10k

R2

10k

+15V

–15V

Figure 40. ADR3550 Bipolar Output Reference

equals the output voltage of

OUT

instead of

IN

IN

0.1µF

+16V

R1

100

AD8663

2N7002

R

200

L

U6

V

IN

ENABLE

FORCE

V

OUT

SENSE

V

OUT

AD3525/ADR3530/

ARD3533/ADR3540/

ADR3550

GND SENSE

GND FORCE

6

7

2

3

Figure 41. Boosted Output Current Reference

rating of the MOSFET, the output drive capability

D

SENSE pin should

OUT

V

OUT

C

0.1µF

+5V

–5V

L

9594-040

09594-041

Rev. 0 | Page 19 of 20

Page 20

ADR3525/ADR3530/ADR3533/ADR3540/ADR3550 Data Sheet

OUTLINE DIMENSIONS

3.20

3.00

2.80

8

5

3.20

3.00

2.80

PIN 1

IDENTIFIER

0.95

0.85

0.75

0.15

0.05

COPLANARITY

1

0.65 BSC

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 42. 8-Lead Mini Small Outline Package [MSOP]

ORDERING GUIDE

1, 2

Model

ADR3525WARMZ-R7 2.500 −40°C to +125°C 8-Lead MSOP RM-8 1000 R3C

ADR3525WBRMZ-R7 2.500 −40°C to +125°C 8-Lead MSOP RM-8 1000 R2T

ADR3530WARMZ-R7 3.000 −40°C to +125°C 8-Lead MSOP RM-8 1000 R3D

ADR3530WBRMZ-R7 3.000 −40°C to +125°C 8-Lead MSOP RM-8 1000 R37

ADR3533WARMZ-R7 3.300 −40°C to +125°C 8-Lead MSOP RM-8 1000 R3E

ADR3533WBRMZ-R7 3.300 −40°C to +125°C 8-Lead MSOP RM-8 1000 R38

ADR3540WARMZ-R7 4.096 −40°C to +125°C 8-Lead MSOP RM-8 1000 R3F

ADR3540WBRMZ-R7 4.096 −40°C to +125°C 8-Lead MSOP RM-8 1000 R39

ADR3550WARMZ-R7 5.000 −40°C to +125°C 8-Lead MSOP RM-8 1000 R3G

ADR3550WBRMZ-R7 5.000 −40°C to +125°C 8-Lead MSOP RM-8 1000 R3B

1

Z = RoHS Compliant Part.

2

W = Qualified for Automotive Applications.

Output Voltage (V) Temperature Range Package Description Package Option

5.15

4.90

4.65

4

15° MAX

0.23

6°

0.09

0°

0.40

0.25

1.10 MAX

(RM-8)

Dimensions show in millimeters

0.80

0.55

0.40

10-07-2009-B

Ordering

Quantity Branding

AUTOMOTIVE PRODUCTS

The ADR3525W/ADR3530W/ADR3533W/ADR3540W/ADR3550W models are available with controlled manufacturing to support the

quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ

from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the

automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account

representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09594-0-9/11(0)

Rev. 0 | Page 20 of 20

Loading...

Loading...