Page 1

1.25 V Micropower, Precision Shunt

V

V

www.BDTIC.com/ADI

FEATURES

Wide operating range: 60 μA to 10 mA

Initial accuracy: ±0.12% maximum

Temperature drift: ±50 ppm/°C maximum

Output impedance: 0.5 Ω maximum

Wideband noise (10 Hz to 10 kHz): 20 μV rms

Operating temperature range: −40°C to +85°C

High ESD rating

4 kV human body model

400 V machine model

Compact, surface-mount SOT-23 package

APPLICATIONS

Portable, battery-powered equipment

Cellular phones, notebook computers, PDAs, GPSs,

and DMMs

Computer workstations

Suitable for use with a wide range of video RAMDACs

Smart industrial transmitters

PCMCIA cards

Automotive

3 V/5 V, 8-bit to 12-bit data converters

GENERAL DESCRIPTION

The ADR15811 is a low cost, 2-terminal (shunt), precision band

gap reference. It provides an accurate 1.250 V output for input

currents between 60 A and 10 mA.

The superior accuracy and stability of the ADR1581 is made

possible by the precise matching and thermal tracking of onchip components. Proprietary curvature correction design

techniques have been used to minimize the nonlinearities in

the voltage output temperature characteristics. The ADR1581

is stable with any value of capacitive load.

The low minimum operating current makes the ADR1581 ideal

fo

r use in battery-powered 3 V or 5 V systems. However, the wide

operating current range means that the ADR1581 is extremely

versatile and suitable for use in a wide variety of high current

applications.

The ADR1581 is available in two grades, A and B, both of which

re provided in the SOT-23 package. Both grades are specified

a

over the industrial temperature range of −40°C to +85°C.

1

Protected by U.S. Patent No. 5,969,657; other patents pending.

Voltage Reference

ADR1581

PIN CONFIGURATION

ADR1581

1

+

NC (OR V–)

3

–

2

TOP VIEW

NC = NO CONNECT

Figure 1. SOT-23

20

18

16

14

12

10

QUANTITY

8

6

4

2

0

–20 –10 0 10 20

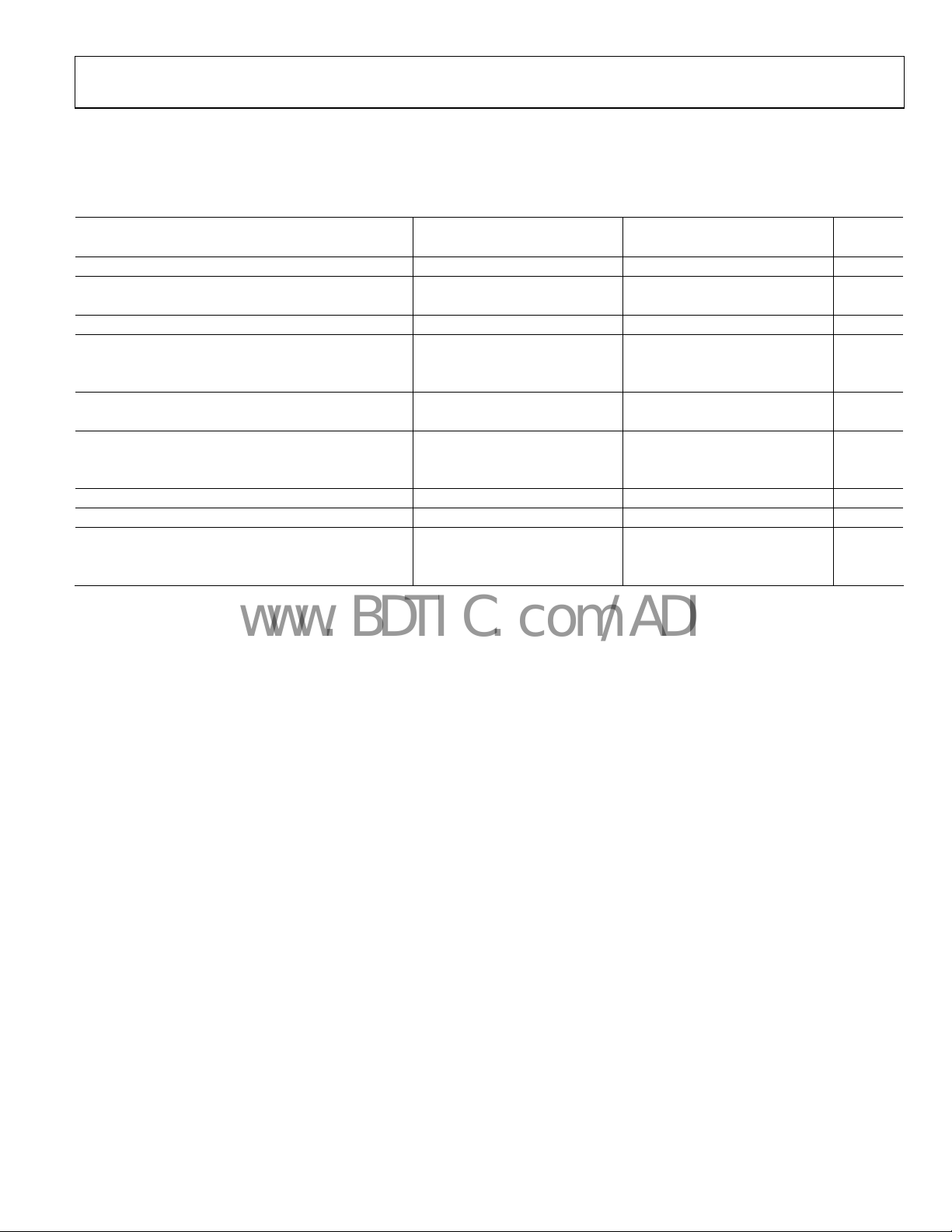

Figure 2. Reverse Voltage Temperature Drift Distribution

100

90

80

70

60

50

QUANTITY

40

30

20

10

0

–5 –4 –3 –2 –1 0 1 2 3 4 5

TEMPERATURE DRIFT (ppm/°C)

OUTPUT ERROR (mV)

Figure 3. Reverse Voltage Error Distribution

06672-001

06672-002

06672-003

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

Page 2

ADR1581

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Temperature Performance............................................................6

Applications....................................................................................... 1

General Description ......................................................................... 1

Pin Configuration............................................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Typical Performance Characteristics ............................................. 5

Theory of Operation ........................................................................ 6

Applying the ADR1581................................................................ 6

REVISION HISTORY

5/07—Revision 0: Initial Version

Voltage Output Nonlinearity vs. Temperature..........................7

Reverse Voltage Hysteresis...........................................................7

Output Impedance vs. Frequency ...............................................8

Noise Performance and Reduction .............................................8

Turn-On Time ...............................................................................8

Transient Response .......................................................................9

Precision Micropower Low Dropout Reference .......................9

Using the ADR1581 with 3 V Data Converters ..................... 10

Outline Dimensions....................................................................... 11

Ordering Guide .......................................................................... 12

Rev. 0 | Page 2 of 12

Page 3

ADR1581

www.BDTIC.com/ADI

SPECIFICATIONS

TA = 25°C, IIN = 100 µA, unless otherwise noted.

Table 1.

ADR1581A ADR1581B

Parameter Min Typ Max Min Typ Max Unit

REVERSE VOLTAGE OUTPUT (SOT-23) 1.240 1.250 1.260 1.2485 1.250 1.2515 V

REVERSE VOLTAGE TEMPERATURE DRIFT

−40°C to +85°C 100 50 ppm/°C

MINIMUM OPERATING CURRENT, T

MIN

to T

60 60 A

MAX

REVERSE VOLTAGE CHANGE WITH REVERSE CURRENT

60 A < IIN < 10 mA, T

60 A < IIN < 1 mA, T

MIN

MIN

to T

2.5 6 2.5 6 mV

MAX

to T

0.8 0.8 mV

MAX

DYNAMIC OUTPUT IMPEDANCE (VR/∆IR)

IIN = 1 mA ± 100 A (f = 120 Hz) 0.4 1 0.4 0.5 Ω

OUTPUT NOISE

RMS Noise Voltage: 10 Hz to 10 kHz 20 20 V rms

Low Frequency Noise Voltage: 0.1 Hz to 10 Hz 4.5 4.5 V p-p

TURN-ON SETTLING TIME TO 0.1%

OUTPUT VOLTAGE HYSTERESIS

1

2

5 5 µs

80 80 µV

TEMPERATURE RANGE

Specified Performance, T

Operating Range

1

Measured with a no load capacitor.

2

Output hysteresis is defined as the change in the +25°C output voltage after a temperature excursion to −40°C, then to +85°C, and back to +25°C.

3

The operating temperature range is defined as the temperature extremes at which the device continues to function. Parts may deviate from their specified

performance.

3

MIN

to T

−40 +85 −40 +85 °C

MAX

−55 +125 −55 +125 °C

Rev. 0 | Page 3 of 12

Page 4

ADR1581

www.BDTIC.com/ADI

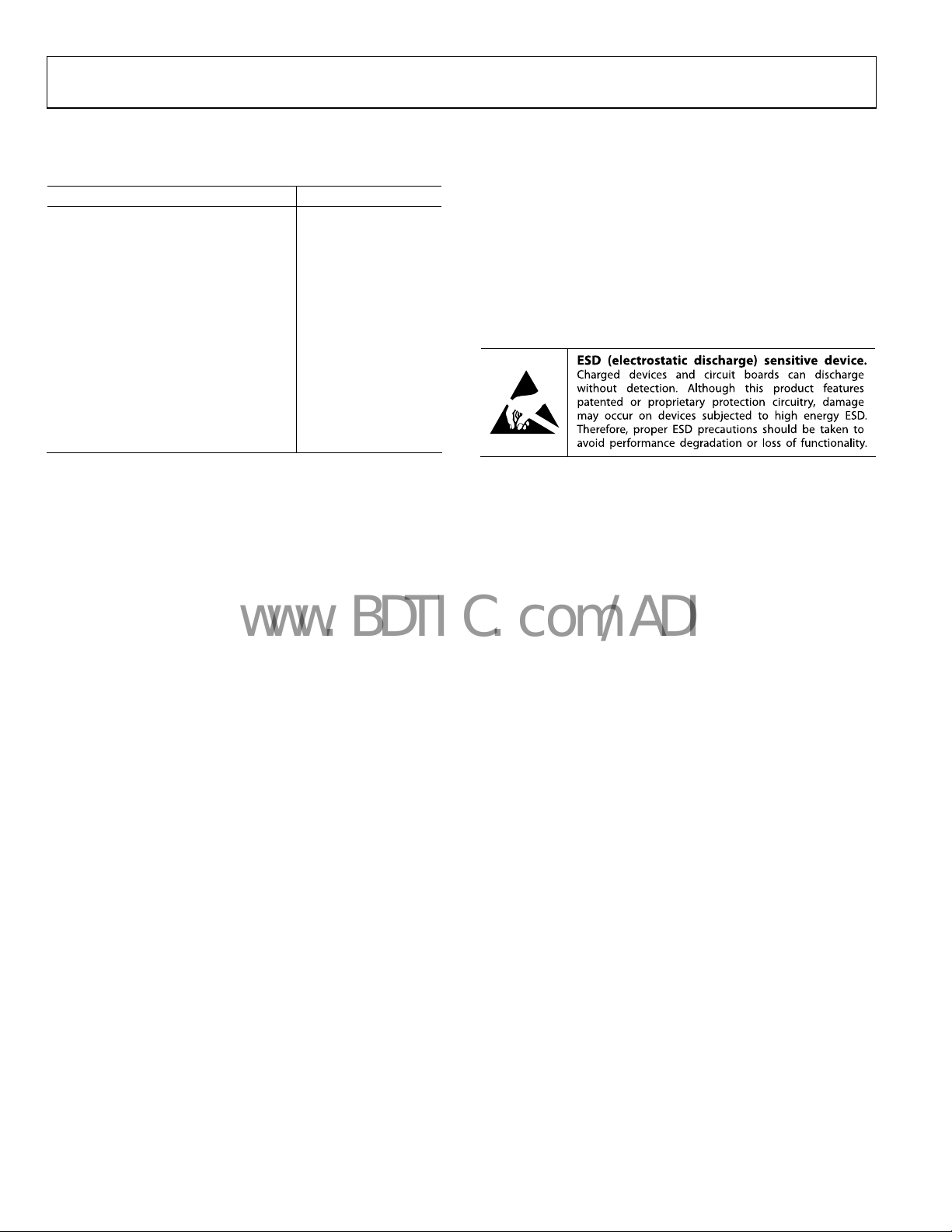

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Reverse Current 25 mA

Forward Current 20 mA

Internal Power Dissipation

SOT-23 (RT) 0.3 W

Storage Temperature Range −65°C to +150°C

Operating Temperature Range

ADR1581/RT −55°C to +125°C

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

ESD Susceptibility2

Human Body Model 4 kV

Machine Model 400 V

1

Specification is for device (SOT-23 package) in free air at 25°C: θJA = 300°C/W.

2

The human body model is a 100 pF capacitor discharged through 1.5 kΩ. For

the machine model, a 200 pF capacitor is discharged directly into the device.

1

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 4 of 12

Page 5

ADR1581

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

2000

100

1500

1000

500

0

–500

REVERSE VOLTAGE CHANGE (pp m)

–1000

–1500

–55 –35 –15 5 25 45 65 85 105 125

TEMPERATURE (°C)

20ppm/° C

5ppm/° C

Figure 4. Output Drift for Different Temperature Characteristics

7

6

5

4

3

2

1

REVERSE VOLTAGE CHANGE (mV)

0

+25°C

+85°C

–40°C

80

60

40

REVERSE CURRENT (µA)

20

0

06672-004

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

REVERSE VOLTAGE (V)

+25°C

+125°C

–40°C

06672-007

Figure 7. Reverse Current vs. Reverse Voltage

1

0.8

0.6

0.4

FORWARD VOLTAGE (µA)

0.2

+25°C

–40°C

+85°C

–1

0.01 0.10 1.00 10

REVERSE CURRENT (mA)

Figure 5. Output Voltage Error vs. Reverse Current

06672-005

0

0.01 0.1 1 10 100

FORWARD CURRENT (mA)

Figure 8. Forward Voltage vs. Forward Current

06672-008

600

400

200

NOISE VOLTAGE (nV/ Hz)

1.0 10 100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 6. Noise Spectral Density

06672-006

Rev. 0 | Page 5 of 12

Page 6

ADR1581

V

V

V

www.BDTIC.com/ADI

THEORY OF OPERATION

The ADR1581 uses the band gap concept to produce a stable,

low temperature coefficient voltage reference suitable for high

accuracy data acquisition components and systems. The device

makes use of the underlying physical nature of a silicon transistor

base emitter voltage in the forward-biased operating region. All

such transistors have an approximately −2 mV/°C temperature

coefficient, which is unsuitable for use directly as a low TC

reference; however, extrapolation of the temperature characteristic

of any one of these devices to absolute zero (with collector current

proportional to absolute temperature) reveals that its V

goes

BE

to approximately the silicon band gap voltage. Therefore, if a

voltage could be developed with an opposing temperature

coefficient to sum with V

The ADR1581 circuit in

, a zero TC reference would result.

BE

Figure 9 provides such a compensating

voltage, V1, by driving two transistors at different current densities

and amplifying the resultant V

positive TC. The sum of V

difference (∆VBE), which has a

BE

and V1 provides a stable voltage

BE

reference.

+

Figure 11 shows a typical connection of the ADR1581BRT

o

perating at a minimum of 100 µA. This connection can

provide ±1 mA to the load while accommodating ±10%

power supply variations.

S

IR + I

R

S

V

R

I

R

Figure 10. Typical Connection Diagram

+5V(+3V) ±10%

R

V

Figure 11. Typical Connection Diagram

S

R

I

L

2.94kΩ

(1.30kΩ)

L

V

OUT

6672-010

V

OUT

6672-011

V1

ΔV

BE

BE

Figure 9. Schema

tic Diagram

V–

APPLYING THE ADR1581

The ADR1581 is simple to use in virtually all applications.

To operate the ADR1581 as a conventional shunt regulator (see

Figure 10), an external series resistor is connected between the

supply

voltage and the ADR1581. For a given supply voltage, the

series resistor, R

the ADR1581. The value of R

the expected variations of the supply voltage (V

(I

), and the ADR1581 reverse voltage (VR) while maintaining an

L

acceptable reverse current (I

The minimum value for R

minimum and I

the minimum acceptable reverse current.

The value of R

when V

S

The equation for selecting R

= (VS − VR)/(IR + IL)

R

S

, determines the reverse current flowing through

S

must be chosen to accommodate

S

), load current

S

) through the ADR1581.

R

should be chosen when VS is at its

S

and VR are at their maximum while maintaining

L

should be large enough to limit IR to 10 mA

S

is at its maximum and IL and VR are at their minimum.

is as follows:

S

TEMPERATURE PERFORMANCE

The ADR1581 is designed for reference applications where stable

temperature performance is important. Extensive temperature

testing and characterization ensure that the device’s performance

is maintained over the specified temperature range.

Some confusion exists in the area of defining and specifying refere

nce voltage error over temperature. Historically, references have

06672-009

been characterized using a maximum deviation per degree Celsius,

for example, 50 ppm/°C. However, because of nonlinearities in

temperature characteristics that originated in standard Zener

references (such as S type characteristics), most manufacturers

now use a maximum limit error band approach to specify devices.

This technique involves the measurement of the output at three

or more temperatures to guarantee that the voltage falls within

the given error band. The proprietary curvature correction design

techniques used to minimize the ADR1581 nonlinearities allow

the temperature performance to be guaranteed using the maximum

deviation method. This method is more useful to a designer than

one that simply guarantees the maximum error band over the

entire temperature change.

Figure 12 shows a typical output voltage drift for the ADR1581

nd illustrates the methodology. The maximum slope of the two

a

diagonals drawn from the initial output value at +25°C to the

output values at +85°C and −40°C determines the performance

grade of the device. For a given grade of the ADR1581, the designer

can easily determine the maximum total error from the initial

tolerance plus the temperature variation.

Rev. 0 | Page 6 of 12

Page 7

ADR1581

www.BDTIC.com/ADI

1.2508

SLOPE = TC =

1.2506

1.2504

1.2502

1.2500

1.2498

1.2496

1.2494

OUTPUT VOLTAGE (V)

1.2492

1.2490

1.2488

–55 –35 –15 5 25 45 65 85 105 125

(+85°C – +25° C) × 1.250V × 10

SLOPE = TC =

V

MIN

TEMPERATURE ( °C)

Figure 12. Output Voltag

– VO)

(V

MAX

V

V

O

– VO)

(V

(–40°C – +25°C) × 1.250V × 10

MIN

e vs. Temperature

–6

MAX

–6

06672-012

600

500

400

300

200

RESIDUAL DRIFT ERROR (ppm)

100

0

–55 –35 –15 5 25 45 65 85 105 125

TEMPERATURE ( °C)

Figure 13. Residual Drift Error

06672-013

For example, the ADR1581BRT initial tolerance is ±1.5 mV;

a ±50 ppm/°C temperature coefficient corresponds to an error

band of ±4.1 mV (50 × 10

−6

× 1.250 V × 65°C). Therefore, the

unit is guaranteed to be 1.250 V ± 5.6 mV over the operating

temperature range.

Duplication of these results requires a combination of high

curacy and stable temperature control in a test system. Evaluation

ac

of the ADR1581 produces curves similar to those in

nd Figure 12.

a

Figure 4

VOLTAGE OUTPUT NONLINEARITY VS. TEMPERATURE

When a reference is used with data converters, it is important to

understand how temperature drift affects the overall converter

performance. The nonlinearity of the reference output drift

represents additional error that is not easily calibrated out of the

system. The usual way of showing the reference output drift is to

plot the reference voltage vs. temperature (see

al

ternative method is to draw a straight line between the

temperature endpoints and measure the deviation of the output

from the straight line. This shows the same data in a different

format. This characteristic (see

n

ormalizing the measured drift characteristic to the endpoint

Figure 13) is generated by

average drift. The residual drift error of approximately 500 ppm

shows that the ADR1581 is compatible with systems that require

10-bit accurate temperature performance.

Figure 12). An

REVERSE VOLTAGE HYSTERESIS

A major requirement for high performance industrial

uipment manufacturers is a consistent output voltage at

eq

nominal temperature following operation over the operating

temperature range. This characteristic is generated by measuring

the difference between the output voltage at +25°C after operating

at +85°C and the output voltage at +25°C after operating at −40°C.

Figure 14 displays the hysteresis associated with the ADR1581.

This ch

aracteristic exists in all references and has been minimized

in the ADR1581.

40

35

30

25

20

QUANTITY

15

10

5

0

–400 –300 –200 –100 0 100 200 300 400

Figure 14. Reverse Voltage Hyster

HYSTERESIS VOLTAGE (µV)

esis Distribution

06672-014

Rev. 0 | Page 7 of 12

Page 8

ADR1581

V

www.BDTIC.com/ADI

OUTPUT IMPEDANCE VS. FREQUENCY

Understanding the effect of the reverse dynamic output impedance

in a practical application is important to successfully applying the

ADR1581. A voltage divider is formed by the ADR1581 output

impedance and the external source impedance. When an external

source resistor of about 30 k (I

noise from a 100 kHz switching power supply is developed at

the output of the ADR1581.

pacitor connected directly across the ADR1581 reduces the

ca

effect of power supply noise to less than 0.01%.

1k

= 100 A) is used, 1% of the

R

Figure 15 shows how a 1 µF load

40µV/DIV 21µV rms

20µV/DIV

10µV/DIV

10ms/DIV

Figure 17. Total RMS Noise

6.5µV rms, t = 0.2ms

2.90µV rms, t = 960ms

(a)

(b)

(c)

06672-017

100

10

= 0.1I

ΔI

R

R

IR = 100µA

OUTPUT IMPEDANCE (Ω)

1

I

= 1mA

R

0.1

10 100 1k 10k 100k 1M

Figure 15. Output Imped

FREQUENCY (Hz)

ance vs. Frequency

CL = 0

C

= 1µF

L

06672-015

NOISE PERFORMANCE AND REDUCTION

The noise generated by the ADR1581 is typically less than

5 µV p-p over the 0.1 Hz to 10 Hz band.

0.1 H

z to 10 Hz noise of a typical ADR1581. Noise in a 10 Hz to

10 kHz bandwidth is approximately 20 V rms (see Figure 17a).

I

f further noise reduction is desired, a one-pole low-pass filter

can be added between the output pin and ground. A time constant

of 0.2 ms has a −3 dB point at about 800 Hz and reduces the high

frequency noise to about 6.5 V rms (see

constant of 960 ms has a −3 dB point at 165 Hz and reduces the

high frequency noise to about 2.9 V rms (see

Figure 16 shows the

Figure 17b). A time

Figure 17c).

4.48µV p-p

TURN-ON TIME

Many low power instrument manufacturers are becoming

increasingly concerned with the turn-on characteristics of the

components in their systems. Fast turn-on components often

enable the end user to keep power off when not needed, and yet

those components respond quickly when the power is turned

on for operation.

o

f the ADR1581.

Upon application of power (cold start), the time required for the

utput voltage to reach its final value within a specified error is

o

the turn-on settling time. Two components normally associated

with this are time for active circuits to settle and time for thermal

gradients on the chip to stabilize. This characteristic is generated

from cold start operation and represents the true turn-on waveform after power-up.

t

urn-on settling characteristics of the device; the total settling

time to within 1.0 mV is about 6 µs, and there is no long thermal

tail when the horizontal scale is expanded to 2 ms/div.

0V

Figure 18 displays the turn-on characteristics

Figure 20 shows both the coarse and fine

2.4V

V

IN

CL = 200pF

1µV/DIV

TIME (1s/DIV)

06672-016

Figure 16. 0.1 Hz to 10 Hz Voltage Noise

Rev. 0 | Page 8 of 12

250mV/DIV 5µs/DIV

Figure 18. Turn-On Response Time

RS= 11.5kΩ

+

IN

V

R

–

Figure 19. Turn-On, Settling, and Tra

R

L

CLV

nsient Test Circuit

OUT

06672-018

006672-010

Page 9

ADR1581

3

www.BDTIC.com/ADI

Output turn-on time is modified when an external noise-reduction

filter is used. When present, the time constant of the filter dominates the overall settling.

2.4V

V

0V

IN

OUTPUT ERROR

1mV/DIV, 2µs/DIV

Attempts to drive a large capacitive load (in excess of 1000 pF) may

r

esult in ringing, as shown in the step response (see Figure 22). This

ue to the additional poles formed by the load capacitance and

is d

the output impedance of the reference. A recommended method

of driving capacitive loads of this magnitude is shown in

Figure 19.

A resistor isolates the capacitive load from the output stage,

whereas the capacitor provides a single-pole low-pass filter

and lowers the output noise.

2.0V

OUTPUT

0.5mV/DIV, 2ms/DIV

Figure 20. Turn-On Settling

6672-020

TRANSIENT RESPONSE

Many ADCs and DACs present transient current loads to the

reference. Poor reference response can degrade the converter’s

performance.

Figure 21 displays both the coarse and fine settling characteristics

of the device to load transients of ±50 A.

20mV/DIV

20mV/DIV

1mV/DIV

IR = 150µA + 50µA STEP

IR = 150µA – 50µA ST EP

1µs/DIV1mV/DIV

Figure 21. Transient Settling

(a)

(b)

06672-021

1.8V

Figure 22. Transient Response with Capacitive Load

V

IN

CL = 0.01µF

50µs/DIV10mV/DIV

06672-022

PRECISION MICROPOWER LOW DROPOUT REFERENCE

The circuit in Figure 23 provides an ideal solution for creating

a stable voltage reference with low standby power consumption,

low input/output dropout capability, and minimum noise output.

The amplifier both buffers and optionally scales up the ADR1581

output voltage. Output voltages as high as 2.1 V can supply 1 mA of

load current. A one-pole filter connected between the ADR1581

and the OP193 input can be used to achieve low output noise. The

nominal quiescent power consumption is 250 µW.

V

28.7kΩ

205Ω

4.7µF

OP193

V

= 1.250V

OUT

OR

= 1.250 (1 + R2/ R3)

V

OUT

Figure 21a shows the settling characteristics of the device for an

increased reverse current of 50 A. Figure 21b shows the response

w

hen the reverse current is decreased by 50 µA. The transients

settle to 1 mV in about 3 µs.

Rev. 0 | Page 9 of 12

ADR1581

R2

R3

Figure 23. Micropower Buffered Reference

06672-023

Page 10

ADR1581

V

V

A

V

www.BDTIC.com/ADI

USING THE ADR1581 WITH 3 V DATA CONVERTERS

The ADR1581 low output drift (50 ppm/°C) and compact

sub

miniature SOT-23 package make it ideally suited for today’s

high performance converters in space-critical applications.

One family of ADCs for which the ADR1581 is well suited is the

AD7714-3 and AD7715-3. The AD7714/AD7715 are charge-

ncing (∑-∆) ADCs with on-chip digital filtering intended for

bala

the measurement of wide dynamic range, low frequency signals,

such as those representing chemical, physical, or biological

processes.

AD7714/AD7715 for 3 V operation.

Figure 24 shows the ADR1581 connected to the

3

28.7kΩ

REF IN(+)

DR1581

REF IN(–)

SWITCHING

FREQUENCY DEPENDS

ON

f

CLKIN

Figure 24. Reference Circuit for the AD7714-3/AD7715-3

AD7714-3/AD7715-3

R

SW

5kΩ (TYP)

C

REF

(3pF TO 8pF)

HIGH

IMPEDANCE

>1GΩ

06672-024

The ADR1581 is ideal for creating the reference level to use

with 12-bit multiplying DACs, such as the AD7943, AD7945,

and AD7948. In the single-supply bias mode (see Figure 25), the

im

pedance seen looking into the I

DAC code. If the ADR1581 drives I

terminal changes with

OUT2

and AGND directly, less

OUT2

than 0.2 LSBs of additional linearity error results. The buffer amp

eliminates linearity degradation resulting from variations in the

reference level.

3.3

R

DD

DGND

FB

DAC

3.3V

A1

SIGNAL G ROUND

I

OUT1

I

OUT2

AGND

C1

A1

Figure 25. Single-Supply System

A1: OP295

AD822

OP2283

V

OUT

06672-025

IN

V

REF

ADR1581

V

AD7943

29.4kΩ

Rev. 0 | Page 10 of 12

Page 11

ADR1581

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

3.04

2.90

1.40

1.30

1.20

PIN 1

0.10

0.01

Figure 26. 3-Lead Small Outline Transistor Package [SOT-23-3]

4.10

3.20

3.10

2.90

4.00

3.90

2.05

2.00

1.95

1.00 MIN

1.10

1.00

0.90

3.55

3.50

3.45

0.75 MIN

8.30

8.00

7.70

1.55

1.50

1.45

DIRECTION O F UNREELI NG

2.80

3

1

1.90 BSC

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS TO-236-AB

2

0.95 BSC

2.64

2.10

0.50

0.30

1.12

0.89

0.60

0.50

0.40

(RT-3)

Dim

ensions shown in millimeters

1.10

1.00

0.90

2.80

2.70

2.60

0.35

0.30

0.25

Figure 27. Tape and Reel Dime

7” REEL 100.00

13” REEL 330.00

20.20

MIN

nsions

(RT-3)

Dimensions shown in millimeters

OR

1.50 MIN

0.20

0.08

14.40 MIN

13.20

13.00

12.80

7” REEL 50.00 MIN

OR

13” REEL 100.00 MIN

9.90

8.40

6.90

053006-0

Rev. 0 | Page 11 of 12

Page 12

ADR1581

www.BDTIC.com/ADI

ORDERING GUIDE

Temperature

Range

ADR1581ARTZ-REEL7 −40°C to +85°C 10 mV 100 ppm/°C 3-Lead SOT-23-3 RT-3 R2M

ADR1581ARTZ-R2 −40°C to +85°C 10 mV 100 ppm/°C 3-Lead SOT-23-3 RT-3 R2M

ADR1581BRTZ-REEL7 −40°C to +85°C 1 mV 50 ppm/°C 3-Lead SOT-23-3 RT-3 R2K

ADR1581BRTZ-R2 −40°C to +85°C 1 mV 50 ppm/°C 3-Lead SOT-23-3 RT-3 R2K

1

Z = RoHS Compliant Part.

1

1

1

1

Initial Output

Error

Temperature

Coefficient

Package

Option Model Package Description Branding

©2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06672-0-5/07(0)

Rev. 0 | Page 12 of 12

Loading...

Loading...