Page 1

3 A, 1.2 MHz/600 kHz High Efficiency

Synchronous Step-Down DC-to-DC Regulator

FEATURES

3 A continuous output current

75 mΩ and 40 mΩ integrated FET

±1.5% output accuracy

Input voltage range from 2.3 V to 5.5 V

Output voltage from 0.6 V to V

600 kHz or 1.2 MHz fixed switching frequency

Synchronizable between 600 kHz and 1.4 MHz

Selectable synchronize phase shift: 0

Selectable PWM or PFM mode operation

Current mode architecture

Precision enable input

Power good output

Voltage tracking input

Integrated soft start

Internal compensation

Starts up into a precharged output

UVLO, OVP, OCP, and thermal shutdown

Available in 16-lead 4mm × 4mm LFCSP_WQ package

APPLICATIONS

Point of load conversion

Communications and networking equipments

Industrial and instrumentation

Consumer electronics

Medical appliances

IN

o

or 180o

ADP2118

GENERAL DESCRIPTION

The ADP2118 is a low quiescent current, synchronous, step-down,

dc-to-dc regulator in a compact 4mm × 4mm LFCSP_WQ

package. It uses a current mode, constant frequency pulse-width

modulation (PWM) control scheme for excellent stability and

transient response. Under light loads, the ADP2118 can be

configured to operate in pulse frequency modulation (PFM)

mode that reduces switching frequency to save power.

The ADP2118 runs from input voltages of 2.3 V to 5.5 V. The

output voltage of the ADP2118ACPZ-R7 is adjustable from

0.6 V to input voltage (V

available in preset output voltage options of 3.3 V, 2.5 V, 1.8 V,

1.5 V, 1.2 V, and 1.0 V. The ADP2118 requires minimal external

parts and provides a high efficiency solution with its integrated

power switch, synchronous rectifier, and internal compensation.

The IC draws less than 3 μA from the input source when it is

disabled. Other key features include undervoltage lockout

(UVLO), integrated soft start to limit inrush current at startup,

overvoltage protection (OVP), overcurrent protection (OCP),

and thermal shutdown (TSD).

), and the ADP2118ACPZ-x.x-R7 are

IN

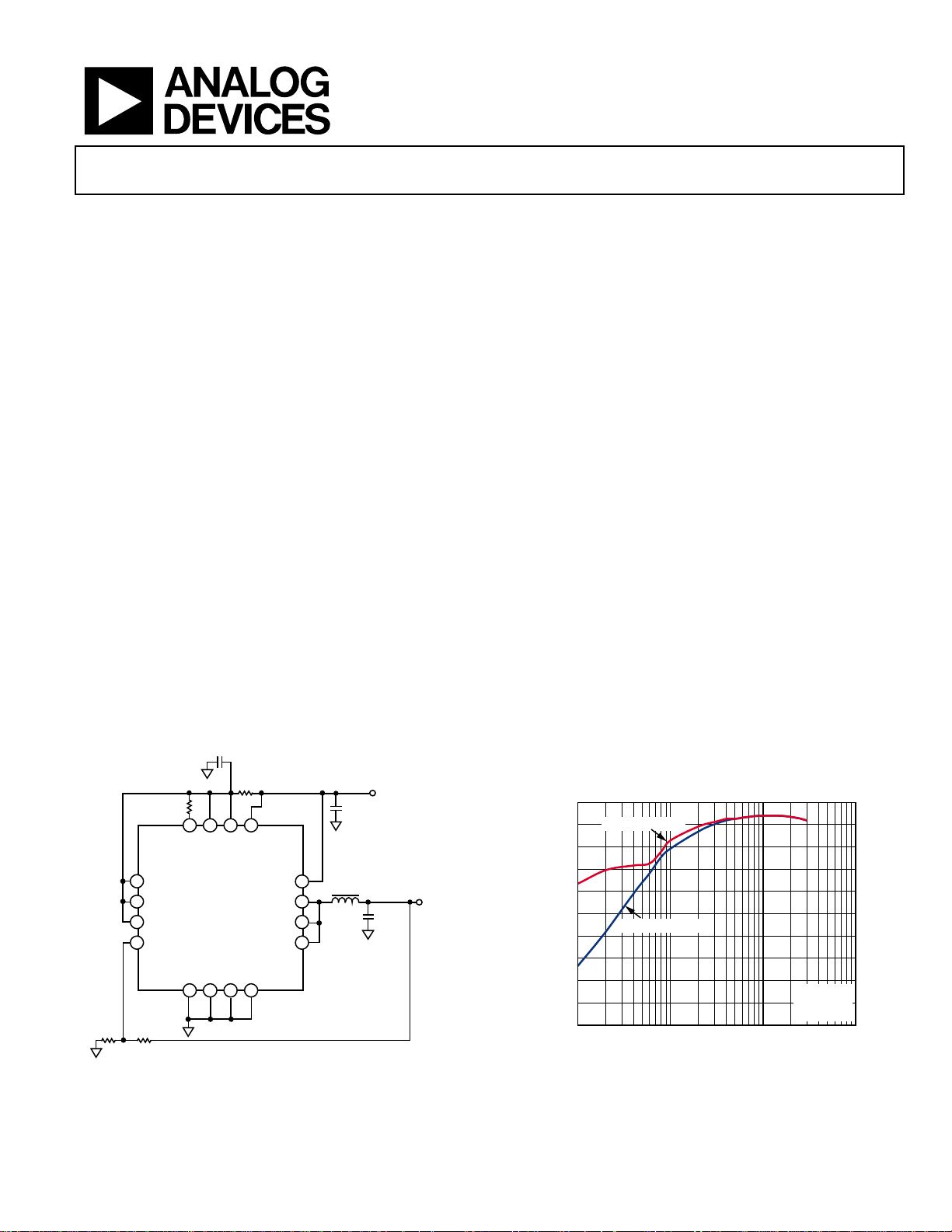

C1

0.1µF

R1

10Ω

R2

10kΩ

16 15 14 13

EN

VIN

VIN

P

12

PVIN

11

SW

10

SW

9

SW

PGND

PGND

PGND

R

BOT

2.21kΩ

1

SYNC/MODE

2

FREQ

3

TRK

4

FB

R

TOP

10kΩ

PGOOD

ADP2118

ND

G

5 6 7 8

Figure 1. Typical Applications Circuit

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

1µH

C

IN

100µF

X5R,

6.3V

L

V

IN

5V

C

OUT

100µF

X5R,

6.3V

V

OUT

3.3V

3A

08301-001

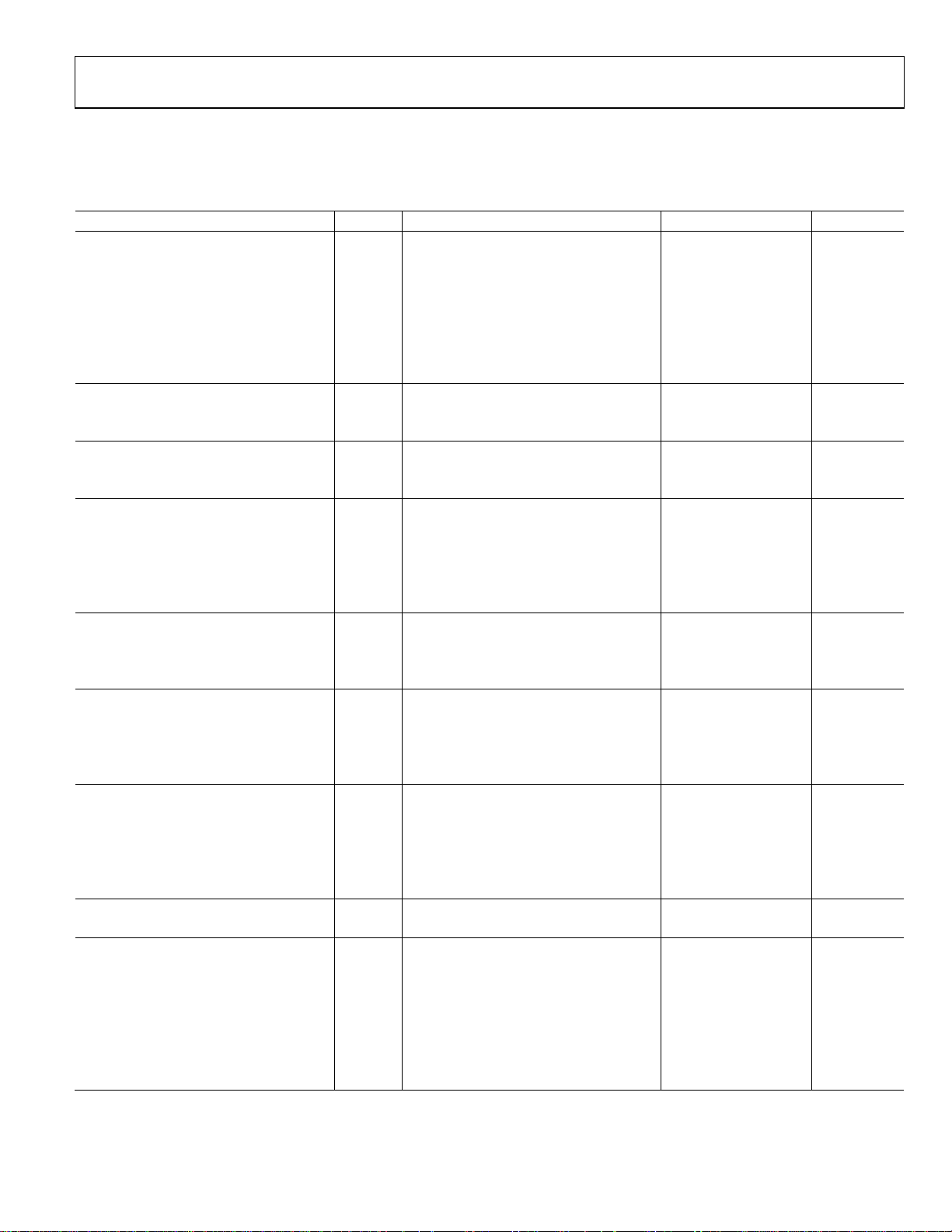

100

90

PFM OPERATION

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.01 0.1 1 10

FPWM OPE RAT I O N

OUTPUT CURRENT (A)

VIN = 5V

V

OUT

f

= 1.2MHz

S

Figure 2. Efficiency vs. Output Current

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

= 3.3V

08301-050

Page 2

ADP2118

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 5

Thermal Resistance ...................................................................... 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

Typical Performance Characteristics ............................................. 7

Functional Block Diagram ............................................................ 13

Theory of Operation ...................................................................... 14

Control Scheme .......................................................................... 14

PWM Mode Operation .............................................................. 14

PFM Mode Operation ................................................................ 14

Slope Compensation .................................................................. 14

Enable/Shutdown ....................................................................... 14

Integrated Soft Start ................................................................... 14

Tracking ....................................................................................... 14

Oscillator and Synchronization ................................................ 15

Current Limit and Short-Circuit Protection .......................... 15

Overvoltage Protection (OVP) ................................................. 15

Undervoltage Lockout (UVLO) ............................................... 15

Thermal Shutdown .................................................................... 15

Power Good ................................................................................ 15

Applications Information .............................................................. 16

Output Voltage Selection ........................................................... 16

Inductor Selection ...................................................................... 16

Output Capacitor Selection ....................................................... 16

Input Capacitor Selection .......................................................... 17

Voltage Tracking ......................................................................... 17

Typical Application Circuits ......................................................... 18

Outline Dimensions ....................................................................... 21

Ordering Guide .......................................................................... 21

REVISION HISTORY

10/09—Rev. 0 to Rev. A

Changed Converter to Regulator (Throughout) .......................... 1

Changes to Applications Section .................................................... 1

7/09—Revision 0: Initial Version

Rev. A | Page 2 of 24

Page 3

ADP2118

SPECIFICATIONS

VIN = PVIN = 3.3 V, EN = VIN, SYNC/MODE = high @ TJ = −40°C to +125°C, unless otherwise noted. Typical values are at TJ = 25oC.

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

VIN AND PVIN

VIN Voltage Range VIN 2.3 5.5 V

PVIN Voltage Range PVIN 2.3 5.5 V

Quiescent Current I

Shutdown Current I

VIN Undervoltage Lockout Threshold UVLO VIN rising 2.2 2.3 V

OUTPUT CHARACTERISTICS

Load Regulation1 I

Line Regulation1 I

FB

FB Regulation Voltage VFB VIN = 2.3 V to 5.5 V 0.591 0.6 0.609 V

FB Bias Current IFB 0.01 0.1 μA

SW

High-Side On Resistance2 VIN = PVIN = 3.3 V, ISW = 500 mA 75 110 mΩ

Low-Side On Resistance2 VIN = PVIN = 3.3 V, ISW = 500 mA 40 60 mΩ

SW Peak Current Limit High-side switch, VIN = PVIN = 3.3 V 4 5.2 6.4 A

SW Maximum Duty Cycle VIN = PVIN = 5.5 V, full frequency 100 %

SW Minimum On Time3 VIN = PVIN = 5.5 V, full frequency 100 ns

TRK

TRK Input Voltage Range 0 600 mV

TRK to FB Offset Voltage TRK = 0 mV to 500 mV −10 +10 mV

TRK Input Bias Current 100 nA

FREQUENCY

Oscillator Frequency FREQ = VIN 1.0 1.2 1.4 MHz

FREQ Input High Voltage 1.2 V

FREQ Input Low Voltage 0.4 V

SYNC/MODE

Synchronization Range 0.6 1.4 MHz

SYNC Minimum Pulse Width 100 ns

SYNC Minimum Off Time 100 ns

SYNC Input High Voltage 1.2 V

SYNC Input Low Voltage 0.4 V

INTEGRATED SOFT START

Soft Start Time All switching frequency 2048 Clock cycles

PGOOD

Power Good Range FB rising threshold 105 110 115 %

Power Good Deglitch Time From FB to PGOOD 16 Clock cycles

PGOOD Leakage Current V

PGOOD Output Low Voltage I

No switching, SYNC/MODE = GND 100 150 μA

VIN

Switching, no load, SYNC/MODE = high 680 900 μA

VIN = PVIN = 5.5 V, EN = GND 0.3 3 μA

SHDN

VIN falling 2 2.1 V

= 0 A to 3 A 0.08 %/A

o

= 1.5 A 0.05 %/V

o

FREQ = GND 500 600 700 kHz

FB rising hysteresis 2.5 %

FB falling threshold 85 90 94 %

FB falling hysteresis 2.5 %

= 5 V 0.1 1 μA

PGOOD

= 1 mA 140 200 mV

PGOOD

Rev. A | Page 3 of 24

Page 4

ADP2118

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

EN

EN Input Rising Threshold VIN = 2.3 V to 5.5 V 1.12 1.2 1.28 V

EN Input Hysteresis VIN = 2.3 V to 5.5 V 100 mV

EN Pull-Down Resistor 1 MΩ

THERMAL

Thermal Shutdown Threshold 140 °C

Thermal Shutdown Hysteresis 15

1

Specified by the circuit in . Figure 45

2

Pin-to-pin measurements.

3

Guaranteed by design.

°C

Rev. A | Page 4 of 24

Page 5

ADP2118

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VIN, PVIN −0.3 V to +6 V

SW −0.3 V to +6 V

FB, SYNC/MODE, EN, TRK, FREQ, PGOOD −0.3 V to +6 V

PGND to GND −0.3 V to +0.3 V

Operating Junction Temperature Range −40°C to +125°C

Storage Temperature Range −65°C to +150°C

Soldering Conditions JEDEC J-STD-020

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type

16-Lead LFCSP_WQ 38.3 °C/W

θ

JA

Unit

Boundary Conditions

θJA is measured using natural convection on a JEDEC 4-layer

board, and the exposed pad is soldered to the printed circuit

board with thermal vias.

ESD CAUTION

Rev. A | Page 5 of 24

Page 6

ADP2118

D

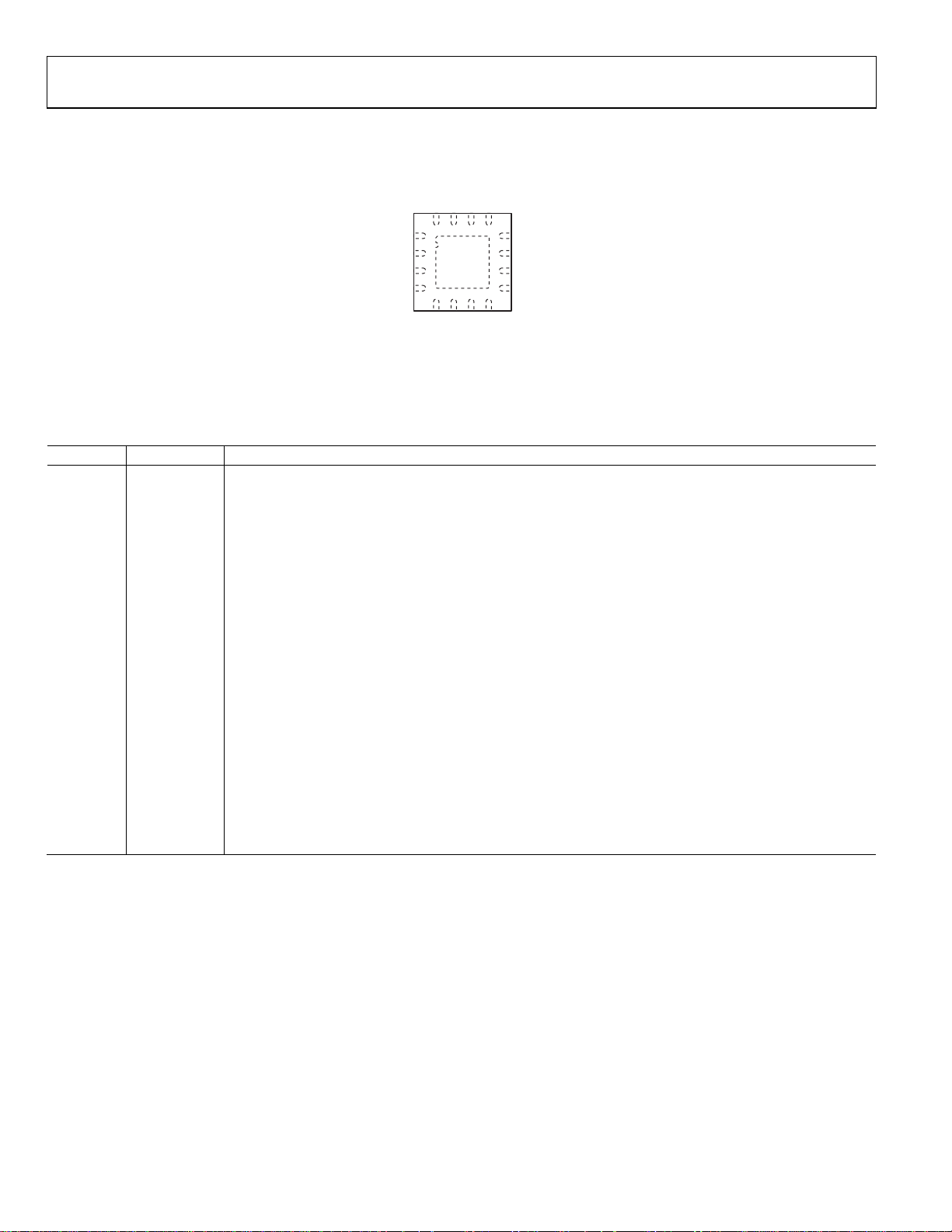

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

EN

VIN

16 PGOO

PVIN

13

15

14

FREQ

TRK

FB

1

2

ADP2118

5

GND

TOP

VIEW

6

PGND

3

4

SYNC/MODE

NOTES

1. THE EXPOSED PAD SHOULD BE SOLDERED TO

AN EXTERNAL GROUND PLANE UNDERNEATH

THE IC FOR THERMAL DISSIPATION.

12

PVIN

11

SW

10

SW

9

SW

8

7

PGND

PGND

08301-002

Figure 3. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 SYNC/MODE

Synchronization Input (SYNC). Connect this pin to an external clock between 600 kHz and 1.4 MHz to

synchronize the switching frequency to the external clock (see the Oscillator and Synchronization section for

details).

CCM/PFM Selection (MODE). When this pin is connected to VIN, PFM mode is disabled and the ADP2118 only

works in continuous conduction mode (CCM). When this pin is connected to ground, PFM mode is enabled

and becomes active at light loads.

2 FREQ Frequency Selection. Connect to GND to select 600 kHz and VIN for 1.2 MHz.

3 TRK

Tracking Input. To track a master voltage, drive TRK from a voltage divider from the master voltage. If the

tracking function is not used, connect TRK to VIN.

4 FB

Feedback Voltage Sense Input. Connect to a resistor divider from V

directly.

to V

OUT

. For the fixed output version, connect

OUT

5 GND Analog Ground. Connect to the ground plane.

6, 7, 8 PGND Power Ground. Connect to the ground plane and to the output return side of the output capacitor.

9, 10, 11 SW Switch Node Output. Connect to the output inductor.

12, 13 PVIN

Power Input Pin. Connect this pin to the input power source. Connect a bypass capacitor between this pin

and PGND.

14 VIN

Bias Voltage Input Pin. Connect a bypass capacitor between this pin and GND and a small (10 Ω) resistor

between this pin and PVIN.

15 EN

Precision Enable Pin. The external resistor divider can be used to set the turn-on threshold. To enable the part

automatically, connect the EN pin to VIN. This pin has a 1 MΩ pull-down resistor to GND.

16 PGOOD Power-Good Output (Open Drain). Connect to a resistor to any pull-up voltage <5.5 V.

17 (EPAD) Exposed Pad The exposed pad should be soldered to an external ground plane underneath the IC for thermal dissipation.

Rev. A | Page 6 of 24

Page 7

ADP2118

C

TYPICAL PERFORMANCE CHARACTERISTICS

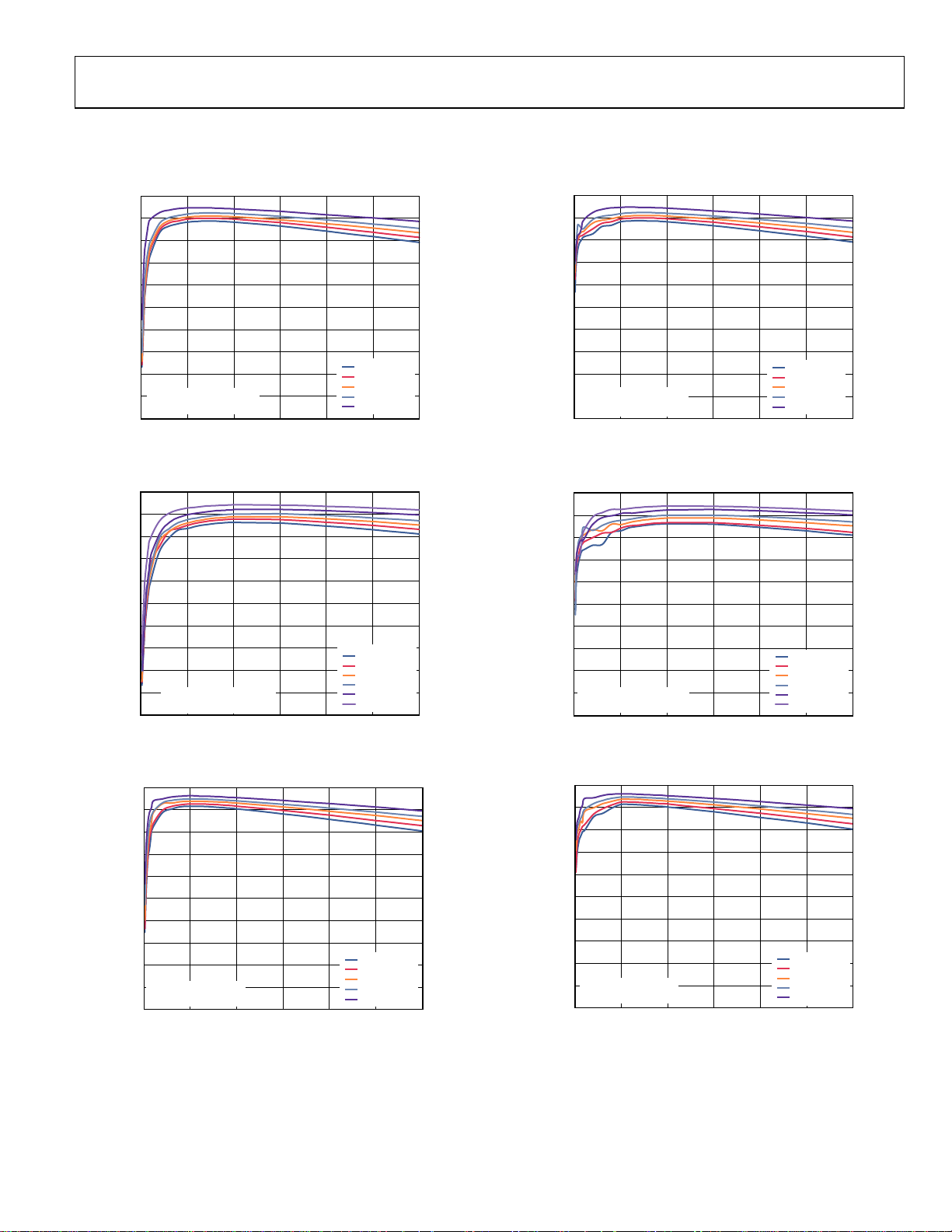

TA = 25°C, VIN = 5 V, V

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR COI LCRAFT

MSS1038-102NL

0

0 0.5 1.0 1.5 2.0 2.5 3.0

Figure 4. Efficiency (1.2 MHz, VIN = 3.3 V, FPWM) vs. Output Current

= 1.2 V, L = 1 μH, CIN = 100 μF, C

OUT

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

OUTPUT CURRENT (A)

= 100 μF, unless otherwise noted.

OUT

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR COI LCRAFT

MSS1038-102NL

0

0 0.5 1.0 1.5 2.0 2.5 3.0

08301-014

Figure 7. Efficiency (1.2 MHz, VIN = 3.3 V, PFM) vs. Output Current

OUTPUT CURRENT ( A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

08301-017

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR COI LCRAFT

MSS1038-102NL

0

0 0.5 1.0 1.5 2.0 2.5 3.0

OUTPUT CURRENT ( A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

Figure 5. Efficiency (1.2 MHz, VIN = 5 V, FPWM) vs. Output Current

100

90

80

70

60

50

40

EFFICIENCY (%)

30

V

= 1.0V

20

10

INDUCTOR SUMI DA

CDRH105R2R2NC

0

0 0.5 1.0 1.5 2.0 2.5 3.0

OUTPUT CURRENT (A)

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

Figure 6. Efficiency (600 kHz, VIN = 3.3 V, FPWM) vs. Output Current

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

INDUCTOR COI LCRAFT

MSS1038-102NL

0

0 0.5 1.0 1.5 2.0 2.5 3.0

08301-015

OUTPUT CURRENT ( A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

8301-018

Figure 8. Efficiency (1.2 MHz, VIN = 5 V, PFM) vs. Output Current

100

90

80

70

60

Y (%)

50

40

EFFICIEN

30

V

= 1.0V

20

10

INDUCTOR SUMIDA

CDRH105R2R2NC

0

0 0.5 1.0 1.5 2.0 2.5 3.0

08301-016

Figure 9. Efficiency (600 kHz, V

OUTPUT CURRENT ( A)

= 3.3 V, PFM) vs. Output Current

IN

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

8301-019

Rev. A | Page 7 of 24

Page 8

ADP2118

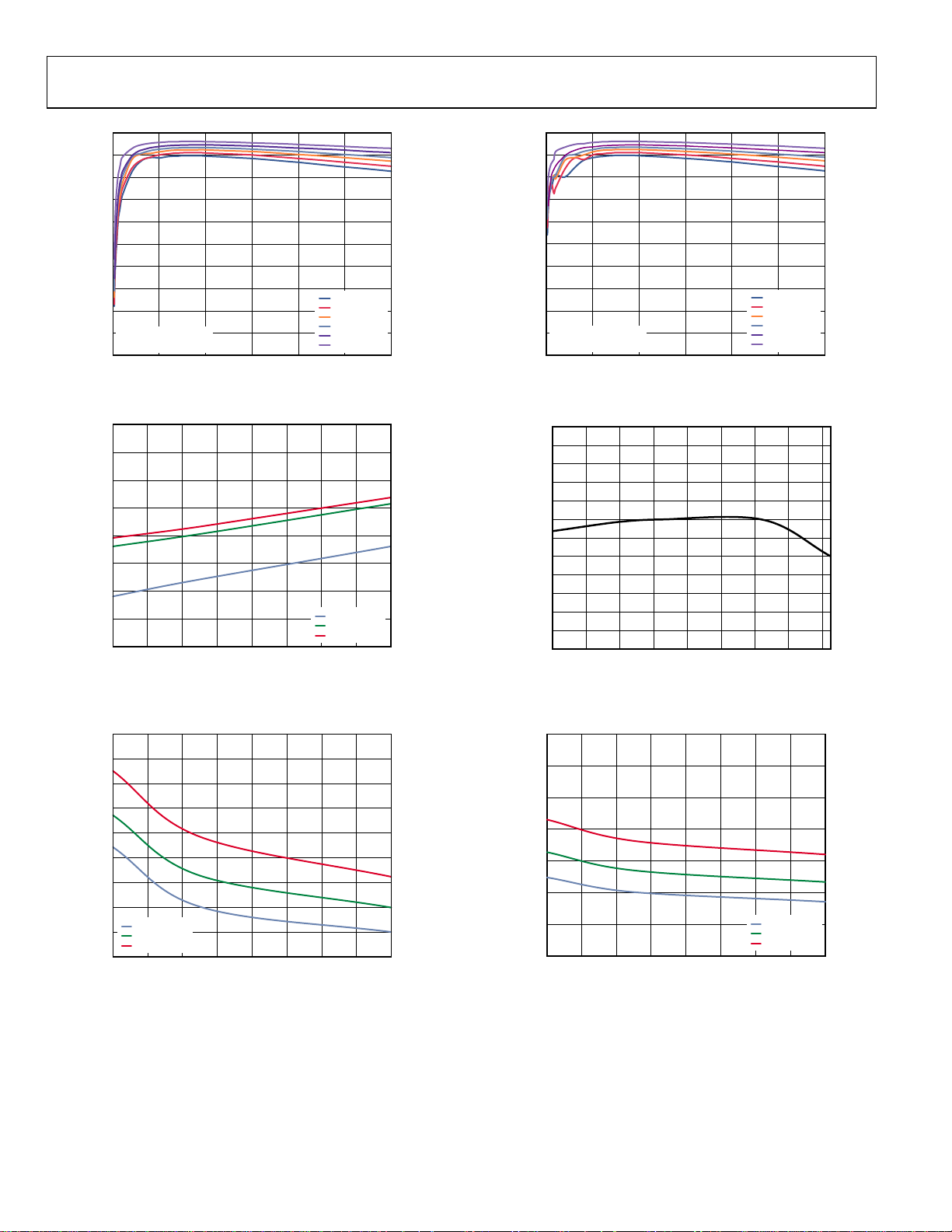

C

C

100

90

80

70

60

Y (%)

50

40

EFFICIEN

30

20

10

INDUCTOR SUMIDA

CDRH105R2R2NC

0

0 0.5 1.0 1.5 2.0 2.5 3.0

OUTPUT CURRENT( A)

V

OUT

V

OUT

V

OUT

V

OUT

V

OUT

V

OUT

Figure 10. Efficiency (600 kHz, VIN = 5 V, FPWM) vs. Output Current

120

115

110

105

100

95

90

QUIESCENT CURRENT (µA)

85

80

2.32.73.13.53.94.34.75.15.5

VIN (V)

Figure 11. Quiescent Current vs. V

TJ = –40°C

= +25°C

T

J

= +125°C

T

J

(No Switching)

IN

= 1.0V

= 1.2V

= 1.5V

= 1.8V

= 2.5V

= 3.3V

100

90

80

70

60

Y (%)

50

40

EFFICIEN

30

20

10

INDUCTOR SUMI DA

CDRH105R2R2NC

0

0 0.5 1.0 1.5 2.0 2.5 3.0

08301-020

OUTPUT CURRENT (A)

V

= 1.0V

OUT

V

= 1.2V

OUT

V

= 1.5V

OUT

V

= 1.8V

OUT

V

= 2.5V

OUT

V

= 3.3V

OUT

08301-023

Figure 13. Efficiency (600 kHz, VIN = 5 V, PFM) vs. Output Current

606

605

604

603

602

601

600

599

598

597

FEEDBACK VOLTAGE (mV)

596

595

594

–40 –20 0 20 40 60 80 100 120

08301-021

TEMPERATURE (°C )

8301-024

Figure 14. Feedback Voltage vs. Temperature (VIN = 3.3 V)

130

120

80

70

110

100

90

80

70

PFET RESISTOR (mΩ)

60

50

40

NFET RESISTOR (mΩ)

30

60

TJ = –40°C

50

T

= +25°C

J

T

= +125°C

J

40

2.3 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

(V)

V

IN

Figure 12. PFET Resistor vs. VIN (Pin-to-Pin Measurements)

20

10

2.3 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

08301-022

VIN (V)

Figure 15. NFET Resistor vs. VIN (Pin-to-Pin Measurements)

TJ = –40°C

T

= +25°C

J

T

= +125°C

J

08301-025

Rev. A | Page 8 of 24

Page 9

ADP2118

1350

1300

1250

1200

1150

1100

SWITCHI NG FREQUENCY (kHz)

1050

1000

2.3 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

V

(V)

IN

TJ = –40°C

T

J

T

J

Figure 16. Switching Frequency vs. VIN at 1.2 MHz

= +25°C

= +125°C

08301-026

660

640

620

600

580

560

540

SWITCHING F REQ UENCY (kHz)

520

500

2.3 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

V

(V)

IN

TJ = –40°C

T

J

T

J

Figure 19. Switching Frequency vs. VIN at 600 kHz

= +25°C

= +125° C

08301-029

1.30

1.28

1.26

1.24

1.22

1.20

1.18

1.16

1.14

1.12

1.10

1.08

ENABLE THRESHOLD (V)

1.06

1.04

1.02

1.00

–40 –20 0 20 40 60 80 100 120

RISING

FALLING

TEMPERATURE (°C)

Figure 17. EN Threshold vs. Temperature

5.5

5.4

5.3

5.2

5.1

5.0

4.9

PEAK CURRENT LIMI T (A)

4.8

4.7

4.6

–40 –20 0 20 40 60 80 100 120

TEMPERATURE (°C)

Figure 18. Peak Current Limit vs. Temperature (VIN = 3.3 V)

2.22

2.20

2.18

2.16

2.14

2.12

UVLO THRESHO LD (V)

2.10

2.08

2.06

–40 –20 0 20 40 60 80 100 120

8301-027

RISING

FALLING

TEMPERATURE (°C)

08301-030

Figure 20. UVLO Threshold vs. Temperature (VIN = 3.3 V)

5.5

5.4

5.3

5.2

5.1

5.0

4.9

PEAK CURRENT LI MIT (A)

4.8

4.7

4.6

2.3 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

08301-028

VIN (V)

08301-031

Figure 21. Peak Current Limit vs. VIN (TJ = 25°C)

Rev. A | Page 9 of 24

Page 10

ADP2118

EN

3

V

OUT

1

PGOOD

2

I

L

4

CH1 500mV CH2 5V

CH3 5V

CH4 2A Ω

M1ms A CH3 3.10V

T 20.40%

Figure 22. Soft Start with Full Load (1.2 MHz, VIN = 5 V)

V

(

A

C

)

O

U

T

1

I

O

4

CH1 50mV

CH4 2A Ω

M200µs A CH4 1.36A

T 30.40%

Figure 23. Load Transient (1.2 MHz, PFM, VIN = 5 V)

3

1

2

4

08301-032

08301-033

CH1 500mV CH2 5V

CH3 5V

1

4

CH1 50mV

EN

V

OUT

PGOOD

I

L

CH4 2A Ω

M1ms A CH3 3.10V

T 30.2%

Figure 25. Soft Start with Precharge (1.2 MHz, V

V

(AC)

OUT

I

O

CH4 2A Ω

M200µs A CH4 1.36A

T 30.40%

= 5 V)

IN

08301-035

08301-036

Figure 26. Load Transient (1.2 MHz, FPWM, VIN = 5 V)

2

3

SYNC

SW

CH3 2V

CH2 2V

M 400ns A CH2 2.88V

T –8ns

Figure 24. Synchronized to 1 MHz In Phase

08301-034

Rev. A | Page 10 of 24

SYNC

2

SW

3

CH3 2V

CH2 2V

M400ns A CH2 2.88V

T –8ns

Figure 27. Synchronized to 1 MHz 180° Out of Phase

08301-037

Page 11

ADP2118

V

OUT

V

OUT

1

SW

1

2

I

4

L

CH1 500mV CH2 5V

1

CH1 500mV

CH4 5A Ω

M2ms A CH1 670mV

T 29.60%

Figure 28. Output Short

TRK

FB

CH2 500mV

M4ms A CH2 640mV

T 59%

Figure 29. Tracking Function

SW

2

I

L

4

08301-038

CH1 500mV CH2 5V

CH4 5A Ω

M2ms A CH1 670mV

T 59.60%

08301-041

Figure 31. Output Short Recovery

1

4

2

08301-039

V

(AC)

OUT

I

L

SW

CH1 50mV CH2 5V

CH4 1A Ω

M4µs A CH4 1.72A

T 64.60%

08301-042

Figure 32. PFM Mode

V

(AC)

OUT

1

I

L

4

SW

2

CH1 10mV

CH2 5V

CH4 1A Ω

M 400ns A CH2 3.90V

T 57.80%

Figure 30. Discontinuous Conduction Mode (DCM)

V

(AC)

OUT

1

I

L

4

SW

2

08301-040

CH1 10mV CH2 5V

CH4 2A Ω

M400ns A CH2 3.1V

T 57.8%

08301-043

Figure 33. Continuous Conduction Mode (CCM)

Rev. A | Page 11 of 24

Page 12

ADP2118

60

48

36

24

12

0

–12

MAGNITUDE ( dB)

–24

–36

–48

CROSS FREQ UENCY: 102kHz

PHASE MARGIN: 50°

–60

100 1k 10k 100k 1M

Figure 34. Bode Plot at VIN = 5 V, V

60

48

36

24

12

0

–12

MAGNITUDE (dB)

–24

–36

–48

CROSS FREQUENCY: 81kHz

PHASE MARGIN: 63°

–60

100 1k 10k 100k 1M

Figure 35. Bode Plot at VIN = 5 V, V

60

48

36

24

12

0

–12

MAGNITUDE ( dB)

–24

–36

–48

CROSS FREQ UENCY : 52kHz

PHASE MARGIN: 76°

–60

100 1k 10k 100k 1M

Figure 36. Bode Plot at VIN = 5 V, V

FREQUENCY ( Hz )

OUT

FREQUENCY (Hz)

OUT

FREQUENCY (Hz)

OUT

= 1.0 V, IO = 3 A, fS = 1.2 MHz

12

= 1.5 V, IO = 3 A, fS = 1.2 MHz

12

= 2.5 V, IO = 3 A, fS = 1.2 MHz

12

200

160

120

80

40

0

–40

–80

–120

–160

–200

200

160

120

80

40

0

–40

–80

–120

–160

–200

200

160

120

80

40

0

–40

–80

–120

–160

–200

PHASE (Degrees)

PHASE (Degrees)

PHASE (Degrees)

60

48

36

24

12

0

–12

MAGNITUDE ( d B)

–24

–36

–48

CROSS FREQ UE NCY: 93kHz

PHASE MARGIN: 56°

–60

100 1k 10k 100k 1M

8301-044

FREQUENCY (Hz)

Figure 37. Bode Plot at VIN = 5 V, V

60

48

36

24

12

0

–12

MAGNITUDE ( d B)

–24

–36

–48

CROSS FREQ UE NCY: 69kHz

PHASE MARGIN: 69°

–60

100 1k 10k 100k 1M

8301-045

FREQUENCY (Hz)

Figure 38. Bode Plot at VIN = 5 V, V

60

48

36

24

12

0

–12

MAGNITUDE ( d B)

–24

–36

–48

CROSS FREQUE NCY: 46kHz

PHASE MARGIN: 79°

–60

100 1k 10k 100k 1M

8301-046

FREQUENCY (Hz)

Figure 39. Bode Plot at VIN = 5 V, V

12

= 1.2 V, IO = 3 A, fS = 1.2 MHz

OUT

12

= 1.8 V, IO = 3 A, fS = 1.2 MHz

OUT

12

= 3.3 V, IO = 3 A, fS = 1.2 MHz

OUT

200

160

120

80

40

0

–40

–80

–120

–160

–200

200

160

120

80

40

0

–40

–80

–120

–160

–200

200

160

120

80

40

0

–40

–80

–120

–160

–200

PHASE (Degrees)

8301-047

PHASE (Degrees)

8301-048

PHASE (Degrees)

8301-049

Rev. A | Page 12 of 24

Page 13

ADP2118

V

FUNCTIONAL BLOCK DIAGRAM

PVIN

ADP2118

Z

COMP

IN

UVLO

EN

PMOS CURRENT

SENSE AMP

TRK

PGOOD

GND

FB

0.6V

SOFT

START

0.66V

0.54V

ERRO AMP

Gm

SKIP MODE

THRESHOLD

SKIP

CMP

COMPENSATION

SYNC/MODE

LOGIC

CONTROL

SLOPE

OSCILLATOR

FREQ

CLK

NMOS

CURRENT

SENSE AMP

ZERO

CURRENT

CMP

PFET

NFET

SW

PGND

8301-003

Figure 40. Functional Block Diagram

Rev. A | Page 13 of 24

Page 14

ADP2118

THEORY OF OPERATION

The ADP2118 is a step-down, dc-to-dc regulator that uses fixed

frequency, peak current-mode architecture with an integrated

high-side switch and low-side synchronous rectifier. The high

switching frequency and tiny 16-lead, 4 mm × 4 mm LFCSP_WQ

package allow for a small step-down dc-to-dc regulator solution. The integrated high-side switch (P-channel MOSFET) and

synchronous rectifier (N-channel MOSFET) yield high efficiency

at medium-to-full loads, and light load efficiency is improved

by PFM mode.

The ADP2118 operates with an input voltage from 2.3 V to

5.5 V and regulates the output voltage down to 0.6 V. The

ADP2118 is also available with preset output voltage options

of 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V, and 1.0 V.

CONTROL SCHEME

The ADP2118 uses the fixed frequency, peak current mode

PWM control architecture and operates in PWM mode for

medium-to-full loads but shifts to PFM mode (if enabled) at

light loads to maintain high efficiency. When operating in fixed

frequency PWM mode, the duty cycle of the integrated switches

is adjusted to regulate the output voltage. When operating in

PFM mode at light loads, the switching frequency is adjusted to

regulate the output voltage.

The ADP2118 operates in PWM mode when the load current is

greater than the pulse-skipping threshold current. At load

currents below this value, the regulator smoothly transitions to

the PFM mode of operation.

PWM MODE OPERATION

In PWM mode, the ADP2118 operates at a fixed frequency set

by the FREQ pin. At the start of each oscillator cycle, the Pchannel MOSFET switch is turned on, putting a positive voltage

across the inductor. Current in the inductor increases until the

current sense signal crosses the peak inductor current level, turns

off the P-channel MOSFET switch, and turns on the N-channel

MOSFET synchronous rectifier. This puts a negative voltage

across the inductor, causing the inductor current to decrease.

The synchronous rectifier stays on for the rest of the cycle or

until the inductor current reaches zero, which causes the zerocrossing comparator to turn off the N-channel MOSFET as well.

The peak inductor current level is set by V

output of a transconductance error amplifier that compares the

feedback voltage with an internal 0.6 V reference.

COMP

. The V

COMP

is the

PFM MODE OPERATION

When PFM mode is enabled, the ADP2118 smoothly transitions to the variable frequency PFM mode of operation when

the load current decreases below the pulse-skipping threshold

current, switching only as necessary to maintain the output

voltage within regulation. When the output voltage drops below

regulation, the ADP2118 enters PWM mode for a few oscillator

cycles to increase the output voltage back to regulation. During the

wait time between bursts, both power switches are off, and the

Rev. A | Page 14 of 24

output capacitor supplies all the load current. Because the output

voltage dips and recovers occasionally, the output voltage ripple

in this mode is larger than the ripple in the PWM mode of

operation.

SLOPE COMPENSATION

Slope compensation stabilizes the internal current control loop

of the ADP2118 when operating close to and beyond 50% duty

cycle to prevent subharmonic oscillations. It is implemented by

summing an artificial voltage ramp to the current sense signal

during the on-time of the P-channel MOSFET switch. This

voltage ramp depends on the output voltage. When operating at

high output voltages, there is more slope compensation. The

slope compensation ramp value determines the minimum

inductor that can be used to prevent subharmonic oscillations.

ENABLE/SHUTDOWN

The EN pin is a precision analog input that enables the device

when the voltage exceeds 1.2 V (typical) and has 100 mV

hysteresis. When the enable voltage falls below 1.1 V (typical)

the part turns off. To force the ADP2118 to automatically start

when input power is applied, connect EN to VIN.

When the ADP2118 is shut down, the soft start capacitor is

discharged. This causes a new soft start cycle to begin when the

part is reenabled.

An internal pull-down resistor (1 MΩ) prevents an accidental

enable if EN is left floating.

INTEGRATED SOFT START

The ADP2118 has integrated soft start circuitry to limit the

output voltage rise time and reduce inrush current at startup.

The soft start time is fixed at 2048 clock cycles.

If the output voltage is precharged prior to turn-on, the

ADP2118 prevents a reverse inductor current (that would

discharge the output capacity) until the soft start voltage

exceeds the voltage on the FB pin.

TRACKING

The ADP2118 has a tracking input, TRK, that allows the output

voltage to track another voltage (master voltage). It is especially

useful in core and I/O voltage tracking for FPGAs, DSPs, and

ASICs.

The internal error amplifier includes three positive inputs: the

internal reference voltage, the soft start voltage, and the TRK

voltage. The error amplifier regulates the FB voltage to the

lowest of the three voltages. To track a master voltage, tie the

TRK pin to a resistor divider from the master voltage.

If the TRK function is not used, connect the TRK pin to VIN.

Page 15

ADP2118

OSCILLATOR AND SYNCHRONIZATION

The internal oscillator of ADP2118 can be set to 600 kHz or

1.2 MHz. Drive the FREQ pin low for 600 kHz; drive FREQ

pin high for 1.2 MHz.

To synchronize the ADP2118, drive an external clock at the

SYNC/MODE pin. The frequency of the external clock can be

in the range of 600 kHz to 1.4 MHz. During synchronization,

the regulator operates in CCM mode only.

If the FREQ pin is low, the switching frequency is in phase with

the external clock; if the FREQ pin is high, the switching

frequency is 180

o

out of phase with the external clock.

CURRENT LIMIT AND SHORT-CIRCUIT PROTECTION

The ADP2118 has a peak current limit protection circuit to

prevent current runaway. The peak current is limited at 5.2 A.

When the inductor peak current reaches the current limit value,

the high-side MOSFET turns off and the low-side MOSFET

turns on until the next cycle while the overcurrent counter

increments. If the overcurrent counter count exceeds 10, the

part enters hiccup mode. The high-side FET and low-side FET

are both turned off. The part remains in this mode for 4096

clock cycles and then attempts to restart from soft start. If the

current limit fault has cleared, the part resumes normal

operation. Otherwise, it reenters hiccup mode again after

counting 10 current-limit violations.

OVERVOLTAGE PROTECTION (OVP)

The output voltage is continuously monitored by a comparator

through the FB pin, which is at 0.6 V (typical) under normal

operation. This comparator is set to activate when the FB

voltage exceeds 0.66 V (typical), thus indicating an output

overvoltage condition. If the voltage remains above this

threshold for 16 clock cycles, the high-side MOSFET turns off

and the low-side MOSFET turns on until the current through it

reaches the limit (−0.9 A for forced continuous mode and 0 A

for PFM mode). Thereafter, both the MOSFETs are held in the

off state until FB falls below 0.54 V (typical), and then the part

restarts. The behavior of PGOOD under this condition is

described in the Power Good section.

UNDERVOLTAGE LOCKOUT (UVLO)

Undervoltage lockout circuitry is integrated on the ADP2118. If

the input voltage drops below 2.1 V, the ADP2118 shuts down,

and both the power switch and the synchronous rectifier turn

off. When the voltage rises again above 2.2 V, the soft start period

is initiated, and the part is enabled.

THERMAL SHUTDOWN

In the event that the ADP2118 junction temperature rises above

140°C, the thermal shutdown circuit turns off the regulator.

Extreme junction temperatures can be the result of high current

operation, poor circuit board design, and/or high ambient

temperature. A 15°C hysteresis is included so that when thermal

shutdown occurs, the ADP2118 does not return to operation

until the on-chip temperature drops below 125°C. When

coming out of thermal shutdown, soft start is initiated.

POWER GOOD

PGOOD is an active high, open-drain output and requires a

resistor to pull it up to a voltage. A high indicates that the

voltage on the FB pin (and therefore the output voltage) is

within 10% of the desired value. A low on this pin indicates that

the voltage on the FB pin is not within 10% of the desired value.

There is a 16 cycle waiting period after FB is detected as being

out of bounds. If FB returns to within the ±10% range, it is

ignored by PGOOD circuitry.

Rev. A | Page 15 of 24

Page 16

ADP2118

APPLICATIONS INFORMATION

This section describes the external components selection for the

ADP2118. The typical application circuit is shown in Figure 41.

C1

0.1µF

R1

R

BOT

10kΩ

10kΩ

1

SYNC/MODE

2

FREQ

3

TRK

4

FB

R

TOP

10kΩ

10Ω

R2

16 15 14 13

EN

OD

VIN

PGO

PVIN

PVIN

ADP2118

D

PGND

PGND

GND

5 6 7 8

Figure 41. Application Circuit

PGN

SW

SW

SW

12

11

10

9

1µH

C

100µF

X5R,

6.3V

L

V

IN

5V

IN

V

OUT

OUT

1.2V

3A

C

100µF

X5R,

6.3V

OUTPUT VOLTAGE SELECTION

The output voltage of the adjustable version of the ADP2118

can be set by an external resistive voltage divider by using the

following equation to set the voltage:

V 16.0

OUT

⎛

⎜

⎜

⎝

⎞

R

TOP

⎟

+×=

⎟

R

BOT

⎠

To limit output voltage accuracy degradation due to FB bias

current (0.1 μA maximum) to less than 0.5% (maximum),

ensure that R

is less than 30 kΩ.

BOT

INDUCTOR SELECTION

The inductor value is determined by the operating frequency,

input voltage, output voltage, and ripple current. Using a small

inductor leads to larger inductor current ripple and provides

fast transient response but degrades efficiency, whereas a large

inductor value leads to small current ripple and good efficiency

but slow transient response. As a guideline, the inductor current

ripple, ΔI

trade-off between the transient response and efficiency. The

inductor can be calculated using the following equation:

where:

V

IN

V

OUT

ΔI

D is the duty cyle.

, is typically set to 1/3 of the maximum load current

L

()

IN

=

L

×−

DVV

OUT

×Δ

L

fI

S

is the input voltage.

is the output voltage.

is the inductor current ripple.

L

V

OUT

D =

V

IN

Rev. A | Page 16 of 24

08301-004

The ADP2118 uses slope compensation in the current loop to

prevent subharmonic oscillations when the duty cycle is larger

than 50%. The internal slope compensation limits the minimum

inductor value.

The negative current limit (−0.9 A) also limits the minimum

inductor value. The inductor current ripple (ΔI

) calculated by

L

the selected inductor should not exceed 1.8 A.

The peak inductor current should be kept below the peak

current limit threshold value and can be calculated as

IIIΔ

L

+=

OPEAK

2

Ensure that the rms current of the selected inductor is greater

than the maximum load current and that its saturation current

is greater than the peak current limit of the regulator.

OUTPUT CAPACITOR SELECTION

The output voltage ripple, load step transient, and loop stability

determine the output capacitor selection.

The output ripple is determined by the ESR and the

capacitance.

⎛

⎜

+×Δ=Δ

ESRIV

OUT

L

⎜

⎝

8

OUT

The load transient response depends on the inductor, output

capacitor, and the control loop.

The ADP2118 has integrated loop compensation for simple

power design. Tab l e 5 and Ta b l e 6 show the typical recommended inductors and capacitors for the ADP2118. X5R or X7R

ceramic capacitors are highly recommended.

Table 5. Recommended L and C

VIN (V) V

(V) L (μH) C

OUT

OUT

3.3 1.0 1 100 + 47

3.3 1.2 1 100

3.3 1.5 1 100

3.3 1.8 1 100

3.3 2.5 1 100

5 1.0 1 100 + 47

5 1.2 1 100

5 1.5 1 100

5 1.8 1 100

5 2.5 1 100

5 3.3 1 100

⎞

1

⎟

⎟

××

fC

S

⎠

Value at fS = 1.2 MHz

(μF)

OUT

Page 17

ADP2118

V

Table 6. Recommended L and C

VIN (V) V

(V) L (μH) C

OUT

Value at fS = 600 kHz

OUT

(μF)

OUT

3.3 1.0 1.5 100 + 47

3.3 1.2 1.5 100

3.3 1.5 1.5 100

3.3 1.8 1.5 100

3.3 2.5 1.5 100

5 1.0 1.5 100 + 47

5 1.2 1.5 100

5 1.5 2.2 100

5 1.8 2.2 100

5 2.5 2.2 100

5 3.3 2.2 100

Higher or lower inductors and output capacitors can be used in

the regulator, but the system stability and load transient

performance need to be checked.

The minimum output capacitor can be 47 μF. If f

the inductor range is 0.8 μH to 3.3 μH. If f

= 1.2 MHz,

S

= 600 kHz, the

S

inductor range is 1.5 μH to 3.3 μH.

Table 7. Recommended Inductors

Manufacturer Part Number

Coilcraft MSS1038, MSS1048, MSS1260

Sumida CDRH103R, CDRH104R, CDRH105R

Table 8. Recommended Capacitors

Manufacturer Part Number Description

Murata GRM32ER60J107ME20 100 μF, 6.3 V, X5R, 1210

Murata GRM32ER60J476ME20 47 μF, 6.3 V, X5R, 1210

TDK C3225X5R0J107M 100 μF, 6.3 V, X5R, 1210

TDK C3225X5R0J476M 47 μF, 6.3 V, X5R, 1210

INPUT CAPACITOR SELECTION

The input capacitor reduces the input voltage ripple caused by

the switch current on PVIN. Place the input capacitor as close

as possible to the PVIN pin. A 22 μF or 47 μF ceramic capacitor

is recommended. The rms current rating of the input capacitor

should be larger than the following equation:

()

DDII

ORMS

−××= 1

VOLTAGE TRACKING

The ADP2118 includes a tracking feature that allows the

ADP2118 output (slave voltage) to be configured to track an

external voltage (master voltage), as shown in Figure 42.

A common application is coincident tracking, shown in Figure 43.

Coincident tracking limits the slave output voltage to be the

same as the master voltage until it reaches regulation. Connect

the TRK pin to a resistor divider from the master voltage. For

coincident tracking, set R

TRKT

= R

TOP

and R

TRKB

= R

BOT

.

Ratiometric tracking is shown in Figure 44. The slave output is

limited to a fraction of the master voltage. In this application,

the slave and master voltages reach the final value at the same

time. The ratio of the slave output voltage to the master voltage

is a function of the two dividers.

R

TOP

+

1

V

V

MASTER

R

TRKT

R

TRKB

SLAVE

MASTER

R

BOT

=

VOLTAGE

VOLTAGE

+

1

R

TRKT

R

TRKB

ADP2118

TRK

FB

Figure 42. Voltage Tracking

TIME

Figure 43. Coincident Tracking

TIME

Figure 44. Ratiometric Tracking

V

MASTER

V

SLAVE

V

MASTER

V

SLAVE

V

SLAVE

R

TOP

R

BOT

08301-005

08301-006

08301-007

Rev. A | Page 17 of 24

Page 18

ADP2118

TYPICAL APPLICATION CIRCUITS

C1

0.1µF

R1

10kΩ

1

SYNC/MODE

2

FREQ

3

TRK

4

FB

R2

16 15 14 13

EN

PGOOD

ADP2118

GND

PGND

5 6 7 8

10Ω

VIN

PGND

PVIN

12

PVIN

11

SW

10

SW

9

SW

PGND

1µH

C

100µF

X5R,

6.3V

L

V

IN

3.3V

IN

V

OUT

OUT

1.2V

3A

C

100µF

X5R,

6.3V

R

BOT

10kΩ

R

TOP

10kΩ

L: MSS1038-102NL COILCRAFT

C

,

C

: C3225X5R0J107M TDK

IN

OUT

08301-008

Figure 45. 1.2 V, 3 A, 1.2 MHz Step-Down Regulator,

Force Continuous Conduction Mode

C1

0.1µF

R1

10Ω

R2

10kΩ

16 15 14 13

EN

VIN

PVIN

PGOOD

R

BOT

15kΩ

1

SYNC/MODE

2

FREQ

3

TRK

4

FB

R

TOP

47.5kΩ

ADP2118

PGND

GND

5 6 7 8

PGND

12

PVIN

11

SW

10

SW

9

SW

PGND

L: MSS1038-102NL COILCRAFT

C

: C3225X5R0J107M TDK

IN

C

: GRM32ER61A476KE20 MURATA

OUT

Figure 46. 2.5 V, 3 A, 1.2 MHz Step-Down Regulator, Enable PFM Mode

1µH

C

100µF

X5R,

6.3V

L

V

IN

5V

IN

V

OUT

OUT

2.5V

3A

8301-009

C

47µF

X5R,

10V

Rev. A | Page 18 of 24

Page 19

ADP2118

10kΩ

1MHz

EXT

CLOCK

R

BOT

10kΩ

1

SYNC/MODE

2

FREQ

3

TRK

4

FB

R

TOP

20kΩ

0.1µF

R2

16 15 14 13

PGOOD

ADP2118

PGND

GND

5 6 7 8

C1

R1

10Ω

EN

VIN

PVIN

12

PVIN

11

SW

10

SW

9

SW

PGND

PGND

L: MSS1038-102NL COILCRAFT

C

, C

: C3225X5R0J107M TDK

IN

OUT

1µH

L

C

IN

100µF

X5R,

6.3V

V

IN

5V

C

OUT

100µF

X5R,

6.3V

V

1.8V

3A

OUT

08301-010

Figure 47. 1.8 V, 3 A Step-Down Regulator,

Synchronized to 1 MHz In Phase with the External Clock

C1

0.1µF

R1

1MHz

EXT

CLOCK

10kΩ

1

SYNC/MODE

2

FREQ

3

TRK

4

FB

R2

16 15 14 13

EN

PGOOD

ADP2118

10Ω

VIN

PVIN

12

PVIN

11

SW

10

SW

9

SW

1µH

C

IN

100µF

X5R,

6.3V

L

V

IN

5V

C

OUT

100µF

X5R,

6.3V

V

OUT

1.5V

3A

PGND

GND

PGND

PGND

L: MSS1038-102NL COILCRAFT

C

, C

: C3225X5R0J107M TDK

IN

OUT

08301-011

R

BOT

10kΩ

R

TOP

15kΩ

5 6 7 8

Figure 48. 1.5 V, 3 A Step-Down Regulator, Synchronized to 1 MHz,

180° Out of Phase with the External Clock

Rev. A | Page 19 of 24

Page 20

ADP2118

10kΩ

1

SYNC/MODE

V

MASTER

R

TRKT

10kΩ

R

TRKB

2.21kΩ

R

BOT

2.21kΩ

2

3

4

R

TOP

10kΩ

FREQ

TRK

FB

0.1µF

R2

16 15 14 13

PGOOD

ADP2118

ND

G

5 6 7 8

C1

R1

10Ω

EN

VIN

PVIN

12

PVIN

11

SW

10

SW

9

SW

PGND

PGND

PGND

L: MSS1038-102NL COILCRAFT

C

, C

: C3225X5R0J107M TDK

IN

OUT

1µH

L

C

IN

100µF

X5R,

6.3V

V

IN

5V

C

OUT

100µF

X5R,

6.3V

V

OUT

3.3V

3A

08301-012

Figure 49. 3.3 V, 3 A, 1.2 MHz Step-Down Regulator, Tracking Mode

Rev. A | Page 20 of 24

Page 21

ADP2118

OUTLINE DIMENSIONS

PIN 1

INDICATOR

0.80

0.75

0.70

SEATING

PLANE

4.10

4.00 SQ

3.90

0.65

BSC

0.50

0.40

0.30

0.05 MAX

0.02 NOM

0.20 REF

0.35

0.30

0.25

13

12

9

8

BOTTOM VIEWTOP VIEW

COPLANARITY

0.08

N

1

P

I

D

C

I

A

N

I

16

1

EXPOSED

PAD

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

2.60

2.50 SQ

2.40

4

5

R

O

T

COMPLIANTTOJEDEC STANDARDS MO-220-WGGC.

042709-A

Figure 50. 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

4 mm × 4 mm Body, Very Very Thin Quad

(CP-16-26)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Output Voltage Package Description Package Option

ADP2118ACPZ-R71 −40°C to +125°C Adjustable 16-Lead LFCSP_WQ CP-16-26

ADP2118ACPZ-1.0-R71 −40°C to +125°C 1.0 V 16-Lead LFCSP_WQ CP-16-26

ADP2118ACPZ-1.2-R71 −40°C to +125°C 1.2 V 16-Lead LFCSP_WQ CP-16-26

ADP2118ACPZ-1.5-R71 −40°C to +125°C 1.5 V 16-Lead LFCSP_WQ CP-16-26

ADP2118ACPZ-1.8-R71 −40°C to +125°C 1.8 V 16-Lead LFCSP_WQ CP-16-26

ADP2118ACPZ-2.5-R71 −40°C to +125°C 2.5 V 16-Lead LFCSP_WQ CP-16-26

ADP2118ACPZ-3.3-R71 −40°C to +125°C 3.3 V 16-Lead LFCSP_WQ CP-16-26

ADP2118-EVALZ Evaluation Board

1

Z = RoHS Compliant Part.

Rev. A | Page 21 of 24

Page 22

ADP2118

NOTES

Rev. A | Page 22 of 24

Page 23

ADP2118

NOTES

Rev. A | Page 23 of 24

Page 24

ADP2118

NOTES

©2009 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D08301-0-10/09(A)

Rev. A | Page 24 of 24

Loading...

Loading...