Page 1

PWM, Step-Down DC-to-DC Controller

www.BDTIC.com/ADI

FEATURES

Wide power input voltage range: 1 V to 24 V

Chip supply voltage range: 3.7 V to 5.5 V

Wide output voltage range: 0.6 V to 85% of input voltage

1% accuracy, 0.6 V reference voltage

Output voltage margining control

Output voltage tracking

All N-channel MOSFET

300 kHz, 600 kHz, or up to 1.2 MHz synchronized frequency

No current sense resistor required

Power-good output

Programmable soft start with reverse current protection

Current-limit protection

Thermal overload protection

Overvoltage protection

Undervoltage lockout

1 μA shutdown supply current

Small, 24-lead QSOP package

APPLICATIONS

Telecommunications and networking systems

High performance servers

Medical imaging systems

DSP core power supplies

Microprocessor core power supplies

Mobile communication base stations

Distributed power

GENERAL DESCRIPTION

The ADP1822 is a versatile and inexpensive synchronous voltagemode PWM step-down controller. It drives an all N-channel power

stage to regulate an output voltage as low as 0.6 V.

BIAS INP UT

5V

15pF

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

1µF

80.6kΩ

309pF

10Ω

1µF

100nF

PVCC

BST

VCC

ADP1822

SHDN

FREQ

SYNC

PWGD

MAR

MSEL

COMP

SS

AGND DG ND

PGND

TRKP

TRKN

MDN

MUP

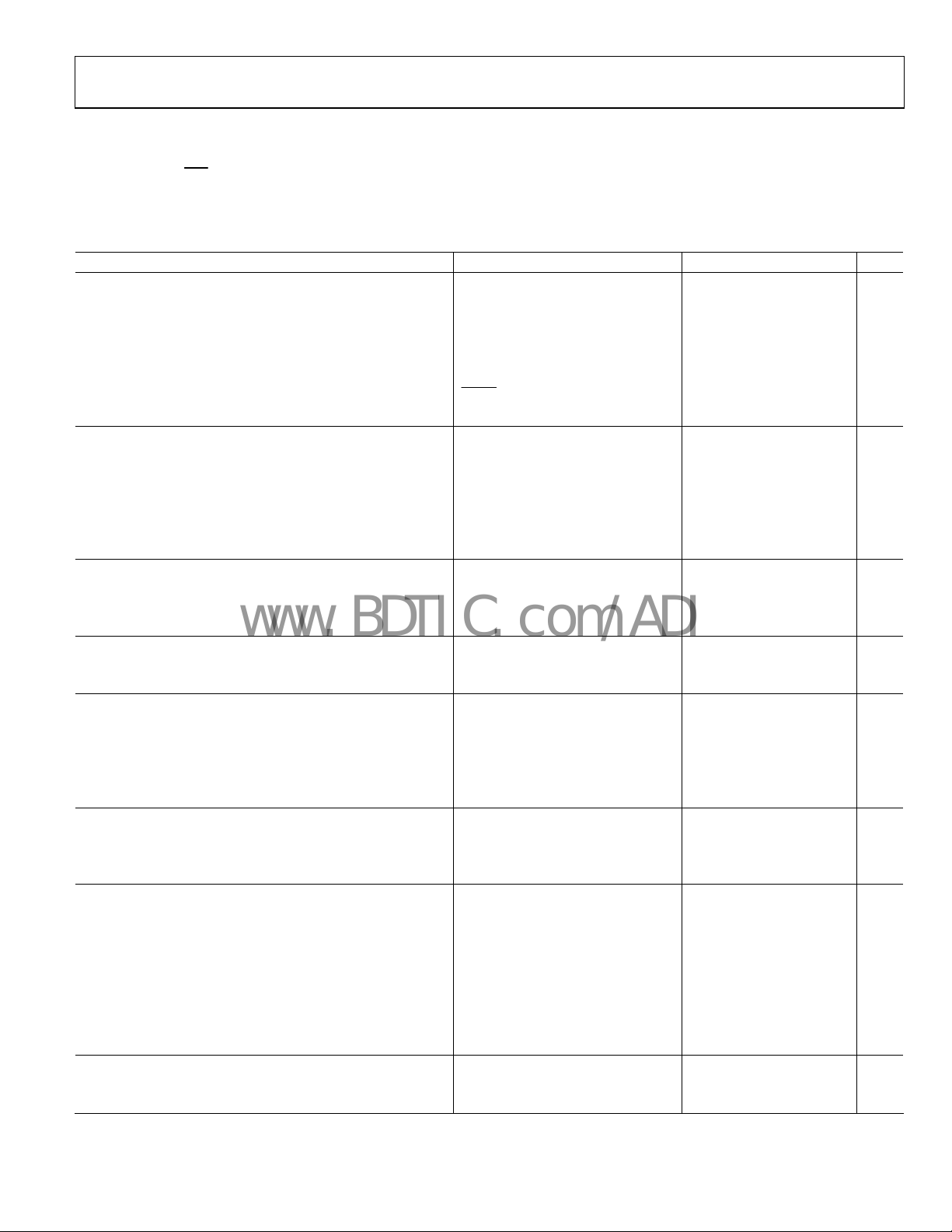

Figure 2. Typical Operating Circuit

DH

SW

CSL

DL

FB

with Margining and Tracking

ADP1822

The ADP1822 regulated output can track another power supply

and can be dynamically adjusted up or down with the controller’s

margining-control inputs, making it ideal for high reliability

applications. It is well suited for a wide range of high power

applications, such as DSP power and processor core power in

telecommunications, medical imaging, high performance

servers, and industrial applications. It operates from a 3.7 V to

5.5 V supply with power input voltage ranging from 1.0 V to 24 V.

The ADP1822 can operate at any frequency between 300 kHz

and 1.2 MHz, either by synchronizing with an external source

or an internally generated, logic-controlled clock of 300 kHz or

600 kHz. It includes an adjustable soft start to allow sequencing

and quick power-up while preventing input inrush current. Output

reverse-current protection at startup prevents excessive output

voltage excursions. The adjustable, virtually lossless currentlimit scheme reduces external part count and improves efficiency.

The ADP1822 operates over the −40°C to +125°C junction

temperature range and is available in a 24-lead QSOP package.

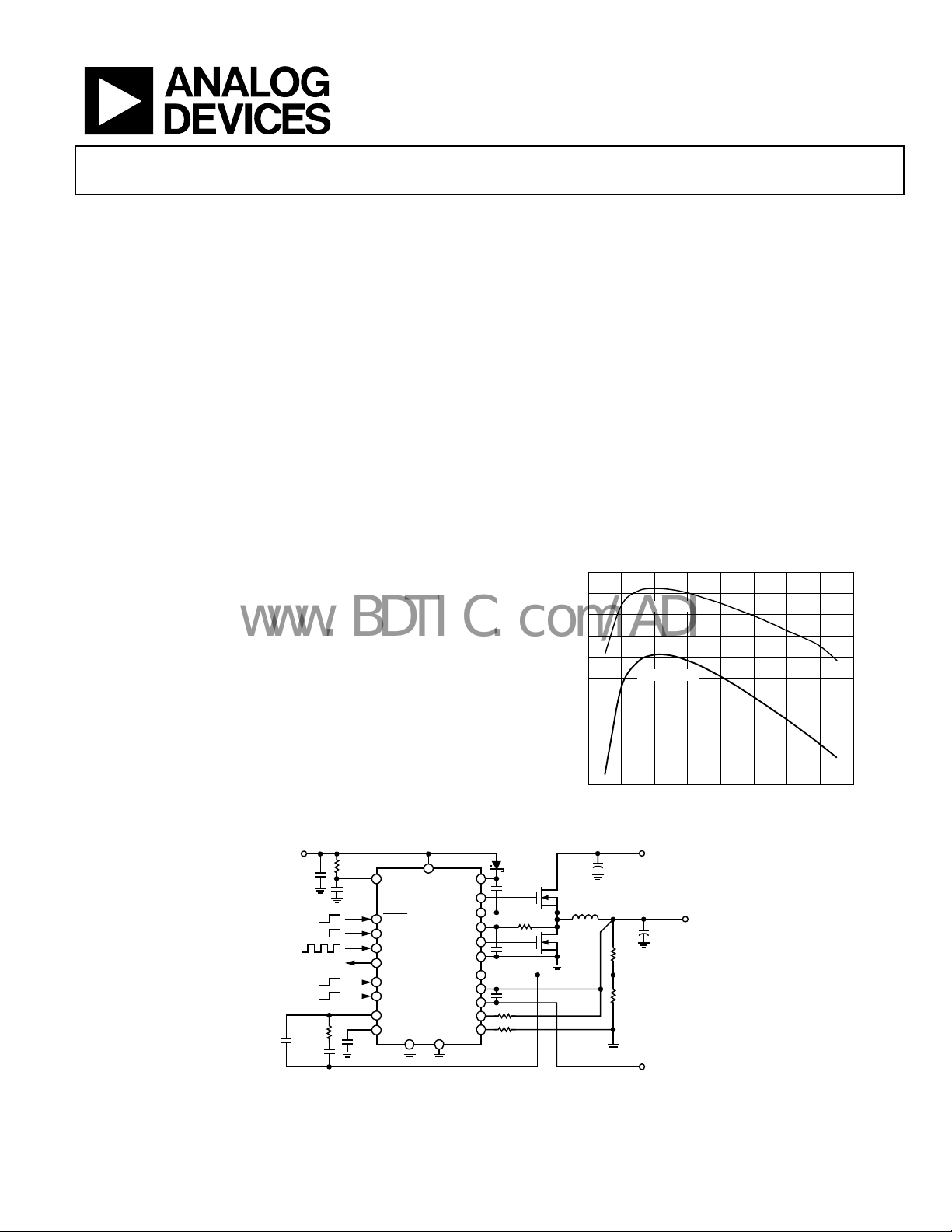

97

96

95

94

93

92

91

EFFICIENCY (%)

90

89

88

87

01

CMOSH-3

0.1µF

6.18kΩ

2.2pF

1nF

158kΩ

316kΩ

IRF3711

1µH

IRF3711

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006–2007 Analog Devices, Inc. All rights reserved.

3.3V OUTPUT

1.8V OUTPUT

2 4 6 8 10 12 14

LOAD CURRENT (A)

Figure 1. Efficiency vs. Load Current, 5 V Input

POWER INPUT

2.25V TO 24V

180µF

20V

OUTPUT

1.8V, 15A

1000µF

4V

20kΩ

10kΩ

TRACKING

SIGNAL INPUT

05311-001

05311-006

6

Page 2

ADP1822

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Simplified Block Diagram ............................................................... 6

Pin Configuration and Function Descriptions............................. 7

Typical Performance Characteristics ............................................. 9

Theory of Operation ...................................................................... 12

Current-Limit Scheme............................................................... 12

Output Voltage Margining ........................................................ 12

Output Voltage Tracking ...........................................................12

Soft Start ...................................................................................... 12

High-Side Driver (BST and DH).............................................. 13

Low-Side Driver (DL)................................................................ 13

Input Voltage Range................................................................... 13

Setting the Output Voltage ........................................................ 13

Switching Frequency Control................................................... 13

Compensation............................................................................. 13

Power-Good Indicator............................................................... 13

Shutdown Control...................................................................... 13

Application Information................................................................ 14

Selecting the Input Capacitor................................................... 14

Output LC Filter......................................................................... 14

Selecting the MOSFETS ............................................................ 15

Setting the Current Limit.......................................................... 15

Feedback Voltage Divider ......................................................... 16

Setting the Voltage Margin........................................................ 16

Compensating the Regulator.................................................... 16

Setting the Soft Start Period...................................................... 18

Synchronizing the Converter.................................................... 19

Setting the Output Voltage Tracking ....................................... 19

Application Circuits ....................................................................... 20

Outline Dimensions....................................................................... 21

Ordering Guide .......................................................................... 21

REVISION HISTORY

5/07—Rev. B to Rev. C

Changes to Features.......................................................................... 1

Changes to General Description .................................................... 1

Changes to Specifications Section.................................................. 3

Changes to Table 2............................................................................ 5

Changes to Theory of Operation Section.................................... 12

Changes to Current Limit Scheme Section................................. 12

Changes to Setting the Current Limit Section............................ 15

Changes to Ordering Guide.......................................................... 21

8/06—Rev. A to Rev. B

Change to Title.................................................................................. 1

C

hange to General Description...................................................... 1

Changes to Figure 6.......................................................................... 9

Changes to Output Voltage Margining Section.......................... 12

Changes to Table 4.......................................................................... 12

1/06—Rev. 0 to Rev. A

Changes to Figure 1...........................................................................1

hanges to Table 1.............................................................................3

C

Changes to Input Voltage Range Section .................................... 13

Changes to Selecting the Input Capacitor Section..................... 14

Added Equation 1; Renumbered Sequentially ........................... 14

Changes to Equation 7 and Equation 8 ....................................... 15

Changes to Selecting the MOSFETS Section.............................. 15

Added Equation 9; Renumbered Sequentially ........................... 15

Changes to Equation 10................................................................. 15

Changes to Equation 22................................................................. 17

Changes to Compensating the Regulator Section...................... 17

Changes to Figure 19 and Figure 20............................................. 17

Changes to Equation 27................................................................. 17

Changes to Equation 34................................................................. 18

7/05—Revision 0: Initial Version

Rev. C | Page 2 of 24

Page 3

ADP1822

www.BDTIC.com/ADI

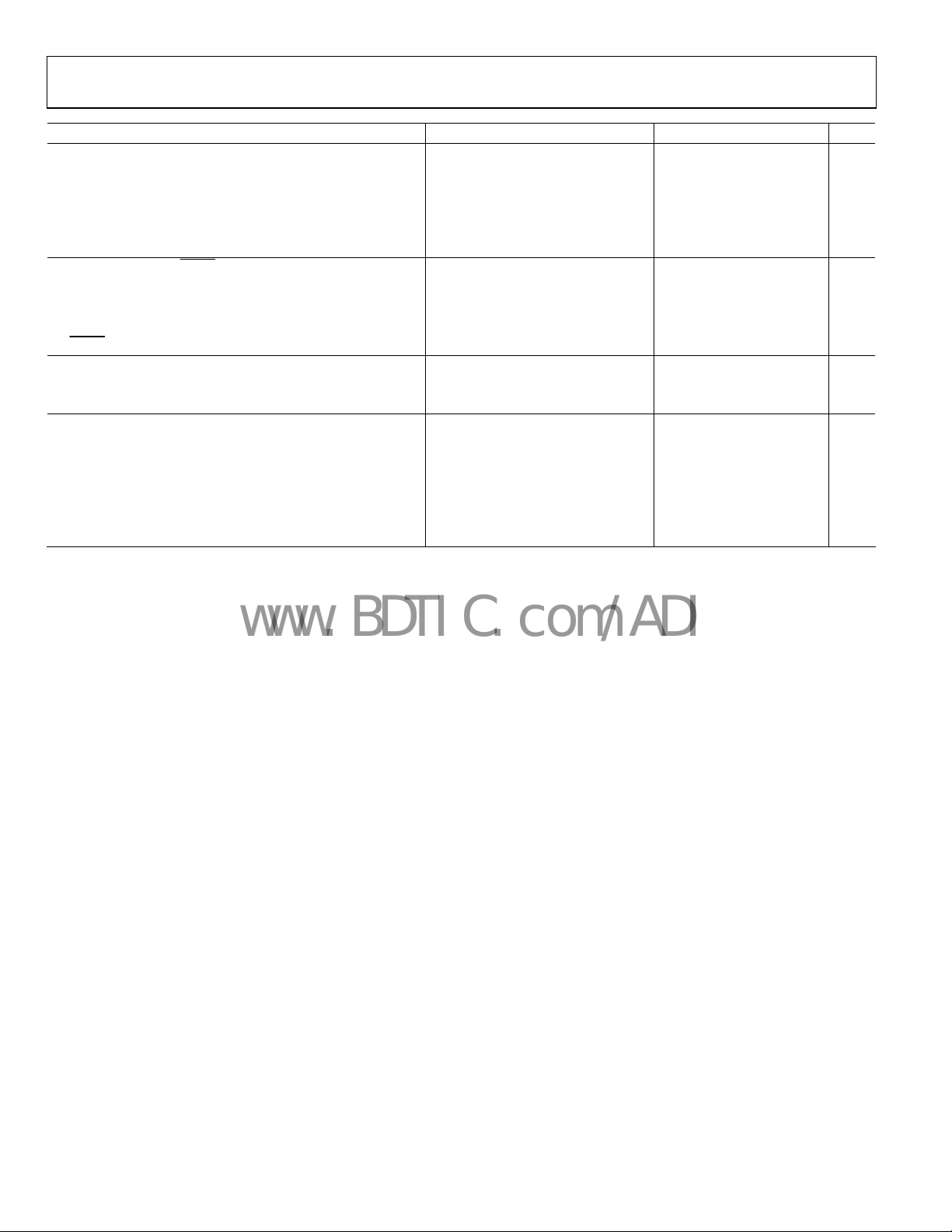

SPECIFICATIONS

V

= V

VCC

correlation using standard statistical quality control (SQC). T

T

= 25°C.

A

Table 1.

Parameter Conditions Min Typ Max Unit

POWER SUPPLY

Input Voltage 3.7 5.5 V

Undervoltage Lockout Threshold V

V

Undervoltage Lockout Hysteresis V

Quiescent Current I

Shutdown Current

Power Stage Supply Voltage 1.0 24 V

ERROR AMPLIFER

FB Regulation Voltage TJ = −40°C to +85°C 594 600 606 mV

T

FB Input Bias Current –100 +1 +100 nA

Error Amplifier Open-Loop Voltage Gain 70 dB

COMP Output Sink Current 600 μA

COMP Output Source Current 110 μA

PWM CONTROLLER

PWM Peak Ramp Voltage 1.25 V

DL Minimum On Time FREQ = VCC (300 kHz) 120 170 220 ns

FREQ = VCC (300 kHz), TA=25°C 140 170 200 ns

SOFT START

SS Pull-Up Resistance SS = GND 95 kΩ

SS Pull-Down Resistance VSS = 0.6 V 1.65 2.5 4.2 kΩ

OSCILLATOR

Oscillator Frequency FREQ = GND 250 310 375 kHz

FREQ = VCC 470 570 720 kHz

Synchronization Range FREQ = GND 300 600 kHz

FREQ = VCC 600 1200 kHz

SYNC Minimum Pulse Width 80 ns

CURRENT SENSE

CSL Threshold Voltage Relative to PGND −30 0 +30 mV

CSL Output Current V

Current Sense Blanking Period 160 ns

GATE DRIVERS

DH Rise Time C

DH Fall Time C

DL Rise Time C

DL Fall Time C

Driver RON, Sourcing Current 1 A, 0.7 μs pulse 2 Ω

Driver RON, Sinking Current 1 A, 0.7 μs pulse 1.5 Ω

DL Low to DH High Dead Time 33 ns

DH Low to DL High Dead Time 42 ns

VOLTAGE MARGINING

High Output Voltage Margin Resistance MUP to FB, V

Low Output Voltage Margin Resistance MDN to FB, V

PVCC

= V

SHDN

= V

FREQ

= V

= 5 V, SYNC = MAR = MSEL = GND. All limits at temperature extremes are guaranteed via

TRKN

= −40°C to +125°C, unless otherwise specified. Typical values are at

J

rising, TJ = −40°C to +125°C 2.4 2.7 3.0 V

VCC

rising, TA = 25°C 2.5 2.7 2.9 V

VCC

0.1 V

VCC

+ I

, not switching 1 2 mA

VCC

VCC

= GND

SHDN

= −40°C to +125°C 588 600 606 mV

J

= 0 V 42 50 54 μA

CSL

= 3 nF, VDH = VIN, V

GATE

= 3 nF, VDH = VIN, V

GATE

= 3 nF, VDL = VIN 19 ns

GATE

= 3 nF, VDL = 0 V 13 ns

GATE

= V

MAR

= 5 V, V

MAR

− VSW = 5 V 16 ns

BST

− VSW = 5 V 12 ns

BST

= 5 V 20 Ω

MSEL

= 0 V 20 Ω

MSEL

10 μA

Rev. C | Page 3 of 24

Page 4

ADP1822

www.BDTIC.com/ADI

Parameter Conditions Min Typ Max Unit

TRACKING

Tracking Comparator Input Offset –200 +200 mV

Tracking Comparator Delay 100 ns

Tracking Comparator Common-Mode Input Voltage Range 0 V

TRKP Pull-Up Resistance Pull-up to VCC 200 kΩ

TRKN Pull-Down Resistance 200 kΩ

LOGIC THRESHOLDS (SHDN, SYNC, FREQ, MAR, MSEL)

Input High Voltage V

Input Low Voltage V

SYNC, FREQ Input Leakage Current SYNC = FREQ = GND 0.1 1 μA

SHDN, MAR, MSEL Pull-Down Resistance

THERMAL SHUTDOWN

Thermal Shutdown Threshold 145 °C

Thermal Shutdown Hysteresis 10 °C

PWGD OUTPUT

FB Overvoltage Threshold VFB rising 750 mV

FB Overvoltage Hysteresis 35 mV

FB Undervoltage Threshold VFB rising 550 mV

FB Undervoltage Hysteresis 35 mV

PWGD Off Current V

PWGD Low Voltage I

= 3.7 V to 5.5 V 2.0 V

VCC

= 3.7 V to 5.5 V 0.8 V

VCC

100 kΩ

= 5 V 1 μA

PWGD

= 10 mA 150 500 mV

PWGD

V

VCC

Rev. C | Page 4 of 24

Page 5

ADP1822

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VCC, SHDN

TRKP

MDN to GND; PVCC to PGND; BST to SW

BST to GND −0.3 V to +30 V

CSL to GND −1 V to +30 V

DH to GND

DL to PGND

SW to GND −2 V to +30 V

PGND to GND

θJA, 2-Layer (SEMI Standard Board) 122°C/W

θJA, 4-Layer (JEDEC Standard Board) 82°C/W

Operating Ambient Temperature Range −40°C to +85°C

Operating Junction Temperature Range −55°C to +125°C

Storage Temperature Range −65°C to +150°C

Maximum Soldering Lead Temperature 260°C

, SYNC, FREQ, COMP, SS, FB,

, TRKN, MAR, MSEL, MUP, and

−0.3 V to +6 V

− 0.3 V) to

(V

SW

+ 0.3 V)

(V

BST

−0.3 V to

(V

+ 0.3 V)

PVCC

±2 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Absolute maximum ratings apply individually only, not in

combination. Unless otherwise specified, all other voltages are

referenced to GND.

ESD CAUTION

Rev. C | Page 5 of 24

Page 6

ADP1822

www.BDTIC.com/ADI

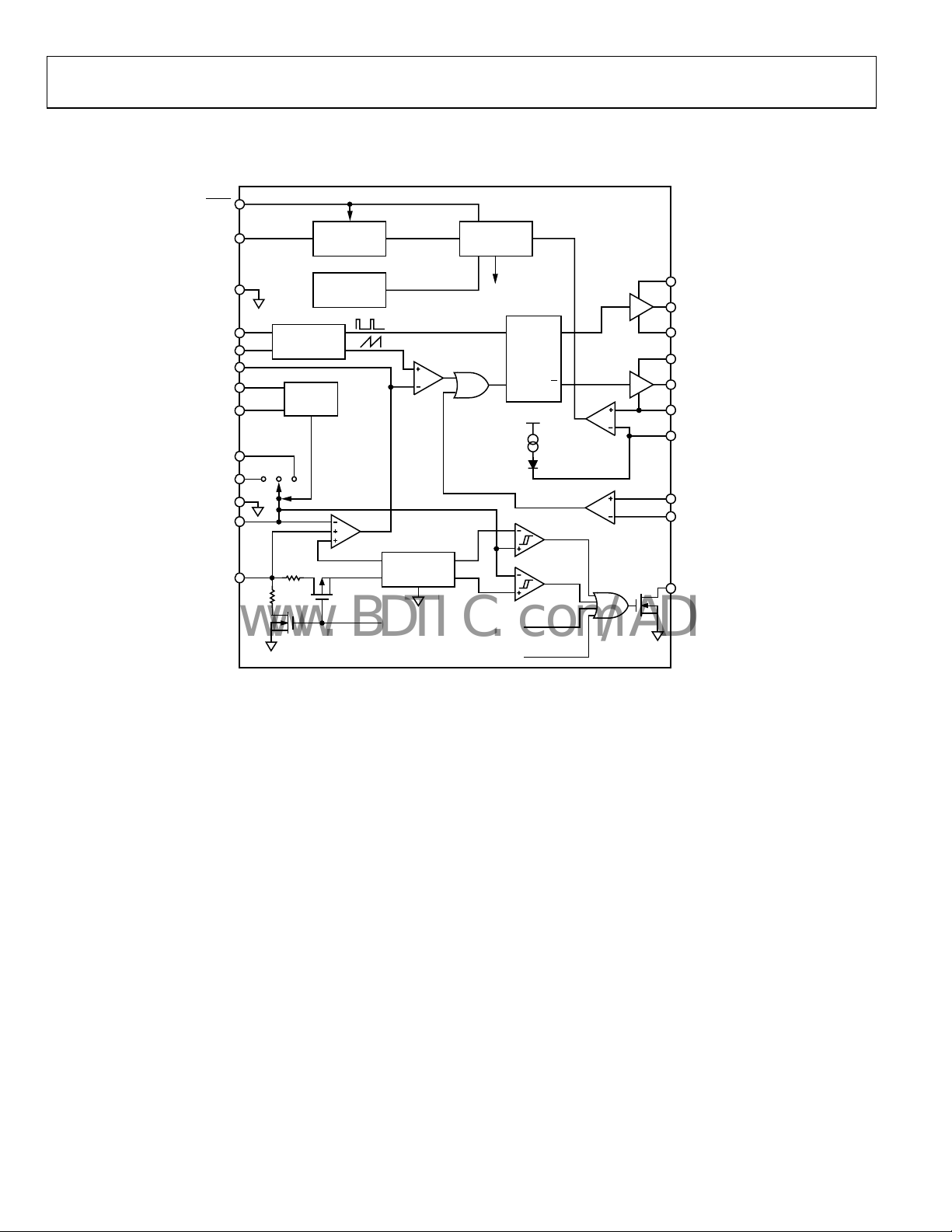

SIMPLIFIED BLOCK DIAGRAM

SHDN

VCC

GND

FREQ

SYNC

COMP

MAR

MSEL

MUP

MDN

DGND

FB

SS

2.5kΩ

SHUTDOWN

OSCILLATOR

DECODE

100kΩ

THERMAL

V

FAULT

REF

REFERENCE

OV

UV0.8V

LOGICUVLO

FAU LT

S

Q

PWM

R

Q

VCC

UVLO

THSD

ADP1822

BST

DH

SW

PVCC

DL

PGND

CSL

TRKP

TRKN

PWGD

05311-002

Figure 3. Simplified Block Diagram

Rev. C | Page 6 of 24

Page 7

ADP1822

www.BDTIC.com/ADI

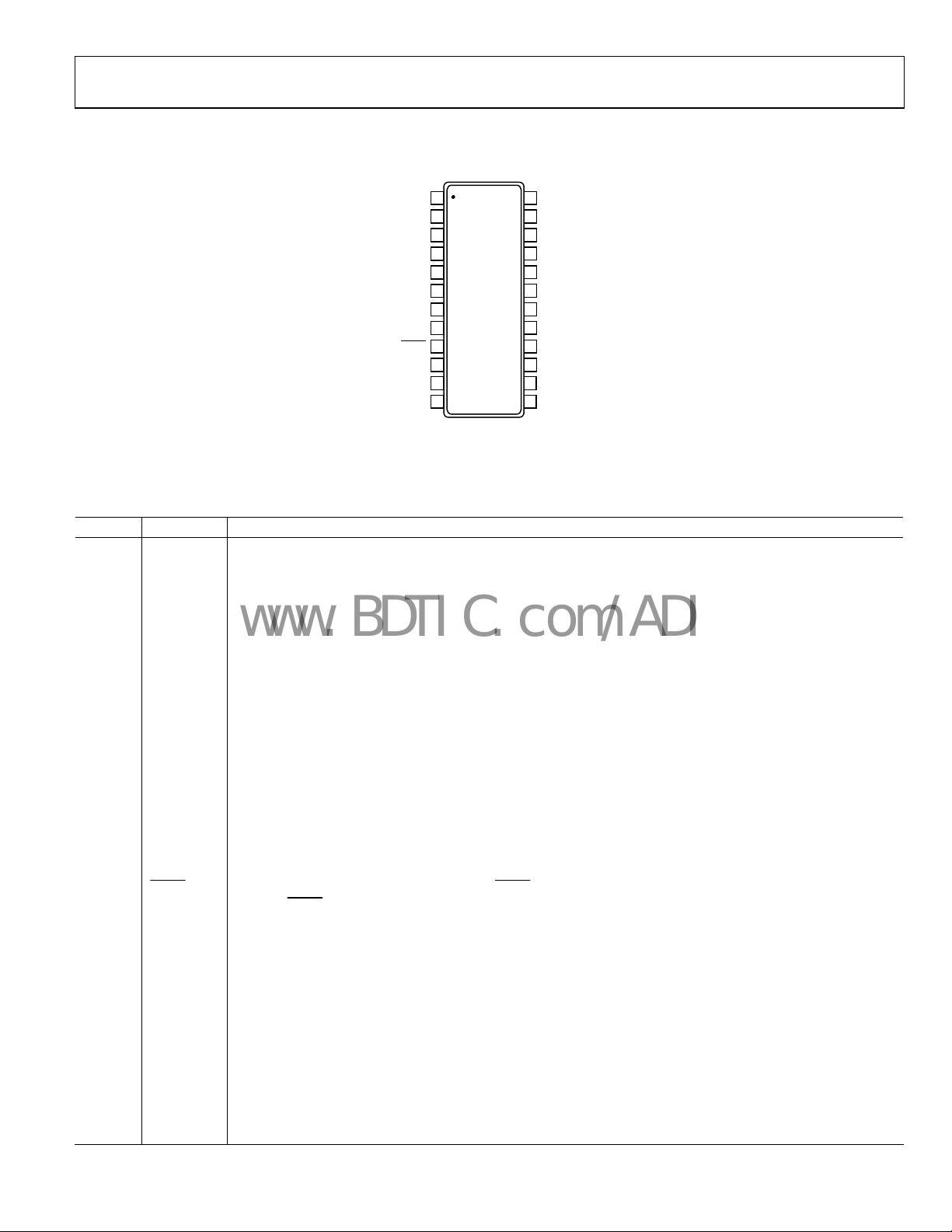

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 BST

High-Side Gate Driver Boost Capacitor Input. A capacitor between SW and BST powers the high-side gate driver

The capacitor is charged through a diode from PVCC when the low-side MOSFET is on. Connect a 0.1 μF or

DH.

greater ceramic capacitor from BST to SW and a Schottky diode from PVCC to BST to power the high-side gate

driver.

2 DH

High-Side Gate Driver Output. Connect DH to the gate of the external high-side N-channel MOSFET switch.

DH is powered from the capacitor between SW and BST and its voltage swings between V

3 SW

Power Switch Node. SW is the power switching node. Connect the source of the high-side N-channel MOSFET

switch and the drain of the low-side N-channel MOSFET synchronous rectifier to SW. SW powers the output

through the output LC filter.

4 SYNC

Frequency Synchronization Input. Drive SYNC with an external 300 kHz to 1.2 MHz signal to synchronize the

converter switching frequency to the applied signal. The maximum SYNC frequency is limited to 2× the nominal

internal frequency selected by FREQ. Do not leave SYNC unconnected; when not used, connect SYNC to GND.

5 FREQ

Frequency Select Input. FREQ selects the converter switching frequency. Drive FREQ low to select 300 kHz, or

high to select 600 kHz. Do not leave FREQ unconnected.

6 MAR

Margin Control Input. MAR is used with MSEL to control output voltage margining. MAR chooses between

high voltage and low voltage margining when MSEL is driven high. If not used, connect MAR to GND.

7 TRKN

Tracking Comparator Negative Input. Drive TRKN from the voltage that the ADP1822 output voltage tracks.

TRKN voltage is limited to VCC. See the Output Voltage Tracking section.

8 TRKP

Tracking Comparator Positive Input. Drive TRKP from the output voltage. TRKP voltage is limited to VCC.

See the Output Voltage Tracking section.

9

SHDN

Active Low DC-to-DC Shutdown Input. Drive SHDN high to turn on the converter. Drive it low to turn it off.

Connect SHDN

10 PWGD

Open-Drain Power-Good Output. PWGD sinks current to GND when the output voltage is above or below

the regulation voltage. Connect a pull-up resistor from PWGD to VDD for a logical power-good indicator.

11 DGND

12 GND

13 SS

Digital Ground. Connect DGND to GND at a single point as close as possible to the IC.

Analog Ground. Connect GND to PGND at a single point as close as possible to the IC.

Soft Start Control Input. A capacitor from SS to GND controls the soft start period. When the output is overloaded,

SS is discharged to prevent excessive input current while the output recovers. Connect a 1 nF to 1 μF capacitor

from SS to GND to set the soft start period. See the

14 FB

Voltage Feedback Input. Connect to a resistive voltage divider from the output to FB to set the output voltage.

See the Setting the Output Voltage section.

15 COMP

Compensation Node. Connect a resistor-capacitor network from COMP to FB to compensate the regulation

control system. See the Compensation section.

16 MSEL

Margin Select Input. Drive MSEL high to activate the voltage margining feature. Drive MSEL low to regulate

the output v

BST

DH

SW

SYNC

FREQ

MAR

TRKN

TRKP

SHDN

PWGD

DGND

GND

1

2

3

4

5

ADP1822

6

TOP VIEW

(Not to Scale)

7

8

9

10

11

12

NC = NO CONNECT

24

NC

23

PVCC

22

DL

21

PGND

20

CSL

19

VCC

18

MUP

17

MDN

16

MSEL

15

COMP

14

FB

13

SS

05311-005

Figure 4. ADP1822 Pin Configuration

to VCC for automatic startup.

Soft Start section.

oltage to the nominal value. If not used, connect MSEL to GND.

and V

SW

BST

.

Rev. C | Page 7 of 24

Page 8

ADP1822

www.BDTIC.com/ADI

Pin No. Mnemonic Description

17 MDN

18 MUP

19 VCC

20 CSL

21 PGND Power Ground. Connect GND to PGND at a single point as close as possible to the IC.

22 DL

23 PVCC

24 NC No Connection. Not internally connected.

Margin Down Input. Connect a resistor from MDN to the output

See the Setting the Voltage Margin section.

Margin Up Input. Connect a resistor from MUP to GND to set the high margining voltage. See the Setting the

ltage Margin section.

Vo

Internal Power Supply Input. VCC powers the in

connected as close as possible to the IC.

Low-Side Current Sense Input. Connect CSL to SW thr

urrent Limit section.

C

Low-Side Gate Driver Output. Connect DL to the gate of the low

The DL voltage swings between PGND and PVCC.

Internal Gate Driver Power Supply Input. PVCC powers the low-side gate driver DL. Bypass PVCC to PGND with 1

eater capacitor connected as close as possible to the IC.

μF or gr

ternal circuitry. Bypass VCC to GND with 0.1 μF or greater capacitor

ough a resistor to set the current limit. See the Setting the

voltage to set the low margining voltage.

-side N-channel MOSFET synchronous rectifier.

Rev. C | Page 8 of 24

Page 9

ADP1822

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

97

96

95

94

93

92

91

EFFICIENCY (%)

90

89

88

87

01

Figure 5. Efficiency vs. Load Current, V

3.

3V OUTPUT

1.8V OUTPUT

2 4 6 8 10 12 14

LOAD CURRENT (A)

= 5 V, V

IN

= 3.3 V, 1.8 V

OUT

05311-106

6

0.6003

0.6002

0.6001

0.6000

0.5999

0.5998

FEEDBACK VOLTAGE (V)

0.5997

0.5996

–50 110

–30 –10 10 30 50 70 90

TEMPERATURE (°C)

Figure 8. FB Regulation Voltage vs. Temperature

05311-009

94

92

90

88

86

EFFICIENCY (%)

84

82

80

01

2 4 6 8 10 12 14

Figure 6. Efficiency vs. Load Current, V

1400

1200

1000

800

600

VCC CURRENT (µA)

400

200

3.3V OUTPUT

1.8V OUTPUT

LOAD CURRENT (A)

= 12 V, V

IN

05311-007

6

= 3.3 V, 1.8 V Figure 9. Switching Frequency vs. Temperature

OUT

700

600

500

400

300

200

SWITCHI NG FREQUE NCY (kHz)

100

0

–50 100

600kHz

300kHz

050

TEMPERATURE (°C)

OUTPUT VOLTAGE

(20mV/DIV)

LOAD CURRENT

(5A/DIV)

05311-010

0

06

12345

VCC VOLTAGE (V)

05311-008

Figure 7. VCC Supply Current vs. Voltage

Rev. C | Page 9 of 24

05311-011

Figure 10. Load Transient Response, 1.5 A to 15 A

Page 10

ADP1822

www.BDTIC.com/ADI

SHDN (5V/DIV)

PWGD (5V/DIV)

OUTPUT VOLTAGE

(1V/DIV)

05311-012

OUTPUT VOLTAGE

(50mV/DIV)

INPUT VOLTAGE

(5V/DIV)

Figure 11. Power-On Response Figure 14. Line Transient Response, 10 V to 16 V

OUTPUT VOLTAGE

(1V/DIV)

SHDN (5V/DIV)

PWGD (5V/DIV)

OUTPUT VOLTAGE (100mV/DIV)

MAR VOLTAGE (5V/DIV)

05311-015

05311-013

Figure 12. Power-On Response, Prebiased Output Figure 15. Output Voltage Margin-Down Response

OUTPUT VOLTAGE (100mV/DIV)

OUTPUT VOLTAGE

(1V/DIV)

LOAD CURRENT

(10A/DIV)

MAR VOLTAGE (5V/DIV)

05311-014

Figure 13. Output Short-Circui

t Response and Recovery Figure 16. Output Voltage Margin-Up Response

05311-016

05311-017

Rev. C | Page 10 of 24

Page 11

ADP1822

www.BDTIC.com/ADI

TRACKING VOLTAGE (1V/DIV)

OUTPUT VOLTAGE (1V/DIV)

05311-018

Figure 17. Output Voltage Tracking Response

Rev. C | Page 11 of 24

Page 12

ADP1822

www.BDTIC.com/ADI

THEORY OF OPERATION

The ADP1822 is a versatile, economical, synchronous-rectified,

fixed frequency, voltage-mode, pulse-width modulated (PWM)

step-down controller capable of generating an output voltage as

low as 0.6 V. It is ideal for a wide range of high power applications,

such as DSP and processor core power in telecommunications,

medical imaging, and industrial applications. The ADP1822

controller runs from 3.7 V to 5.5 V and accepts a power input

voltage between 1.0 V and 24 V.

The ADP1822 includes circuitry to implement output voltage

ma

rgining and can track an external voltage, making it ideal for

high reliability applications with multiple dc-to-dc converters. It

operates at a fixed, internally set 300 kHz or 600 kHz switching

frequency that is controlled by the state of the FREQ input. The

high frequency reduces external component size and cost while

maintaining high efficiency. For noise sensitive applications

where the switching frequency needs to be more tightly controlled, synchronize the ADP1822 to an external signal whose

frequency is between 300 kHz and 1.2 MHz.

The ADP1822 includes adjustable soft start with output reverse-

urrent protection, and a unique, adjustable, lossless current

c

limit. It operates over the −40°C to +125°C junction temperature range and is available in a space-saving, 24-lead QSOP

package.

CURRENT-LIMIT SCHEME

The ADP1822 employs a unique, programmable cycle-by-cycle

lossless current-sensing scheme that uses an inexpensive

resistor to set the current limit. A 50 µA current source is forced

out of CSL to a programming resistor connected to SW. The

resulting voltage across the current sense resistor sets the

current-limit threshold. When on-state voltage of the low-side

MOSFET synchronous rectifier exceeds the programmed

threshold, the low-side MOSFET remains on, preventing

another on cycle and reducing the inductor current. Once the

MOSFET voltage, and thus the inductor current, is below the

current-sense threshold, the synchronous rectifier is allowed to

turn off, and another cycle begins.

When the ADP1822 senses an overcurrent condition, SS sinks

current from the soft start capacitor through an internal 2.5 kΩ

resistor, reducing the voltage at SS and thus reducing the regulated

output voltage. The output behaves like a constant current source

around the preset current limit in the event of an overcurrent

condition. The ADP1822 remains in this mode for as long as

the overcurrent condition persists. When the overcurrent

condition is removed, operation resumes in soft start mode.

This ensures that when the overload condition is removed, the

output voltage smoothly transitions back to regulation while

providing protection for overload and short-circuit conditions.

The ADP1822 also offers a technique for implementing a

c

urrent limit foldback in the event of a short circuit with the use

of an additional resistor. See the Setting the Current Limit

ection for more information.

s

OUTPUT VOLTAGE MARGINING

The ADP1822 features output voltage margining. MAR enables

voltage margining, and MSEL controls whether the voltage is

margined up or down.

The voltage is margined by switching a resistor from FB to

ND (for the high margin) or from FB to the output voltage

G

(for the low margin). The switches from FB are internal to the

ADP1822 through the MUP and MDN terminals.

he states of MAR and MSEL and the resulting voltage margin

t

setting. See the

rmation.

info

Table 4. Voltage Margining Control

MSEL MAR Voltage Margin

X L None (FB not changed)

H H High margin (FB connected to MUP)

L H Low margin (FB connected to MDN)

Setting the Voltage Margin section for more

Tabl e 4 shows

OUTPUT VOLTAGE TRACKING

The ADP1822 features an internal comparator that forces the

output voltage to track an external voltage at startup, which

prevents the output voltage from exceeding the tracking voltage.

The comparator turns off the high-side switch if the positive

cking (TRKP) input voltage exceeds the negative tracking

tra

(TRKN) input voltage. Connect TRKP to the output voltage and

drive TRKN with the voltage to be tracked. If the voltage at

TRKN is below the regulation voltage, the output voltage is

limited to the voltage at TRKN. If the voltage at TRKN is above

the regulation voltage, the output voltage regulates the desired

voltage set by the voltage divider. For more information, see the

Setting the Output Voltage Tracking section.

SOFT START

When powering up or resuming operation after shutdown,

overload, or short-circuit conditions, the ADP1822 employs an

adjustable soft start feature that reduces input current transients

and prevents output voltage overshoot at start-up and overload

conditions. The soft start period is set by the value of the soft

start capacitor, C

When starting the ADP1822, C

enabled by either driving

above the undervoltage lockout threshold, and C

charging to 0.8 V through an internal 100 kΩ resistor. As C

charges, the regulation voltage at FB is limited to the lesser of

either the voltage at SS or the internal 0.6 V reference voltage.

As the voltage at SS rises, the output voltage rises proportionally

until the voltage at SS exceeds 0.6 V. At this time, the output

voltage is regulated to the desired voltage.

, between SS and GND.

SS

is initially discharged. It is

SS

SHDN

high or by bringing VCC

begins

SS

SS

Rev. C | Page 12 of 24

Page 13

ADP1822

www.BDTIC.com/ADI

If the output voltage is precharged prior to turn-on, the

ADP1822 prevents reverse inductor current that would discharge

the output voltage. Once the voltage at SS exceeds the 0.6 V

regulation voltage, the reverse current is re-enabled to allow the

output voltage regulation to be independent of load current.

To override the soft start feature, leave SS unconnected. This

al

lows the output voltage to rise as quickly as possible and

eliminates the soft start period.

HIGH-SIDE DRIVER (BST AND DH)

Gate drive for the high-side power MOSFET is generated by a

flying capacitor boost circuit. This circuit allows the high-side

N-channel MOSFET gate to be driven above the input voltage,

allowing full enhancement of and a low voltage drop across the

MOSFET. The circuit is powered from a flying capacitor from

SW to BST that in turn is powered from the PVCC gate driver

voltage. When the low-side switch is turned on, SW is driven to

PGND, and the flying capacitor is charged from PVCC through

an external Schottky rectifier. The capacitor stores sufficient

charge to power BST to drive DH high and to fully enhance the

high-side N-channel MOSFET. Use a flying capacitor value

greater than 100× the high-side MOSFET input capacitance.

LOW-SIDE DRIVER (DL)

DL is the gate drive for the low-side power MOSFET synchronous

rectifier. Synchronous rectification reduces conduction losses

developed by a conventional rectifier by replacing it with a

low resistance MOSFET switch. DL turns on the synchronous

rectifier by driving the gate voltage to PVCC. The MOSFET is

turned off by driving the gate voltage to PGND.

An active dead time reduction circuit reduces the break-beforemak

e time of the switching to limit the losses due to current

flowing through the synchronous rectifier body diode or

external Schottky rectifier.

INPUT VOLTAGE RANGE

The ADP1822 takes its internal power from the VCC and

PVCC inputs. PVCC powers the low-side MOSFET gate drive

(DL), and VCC powers the internal control circuitry. Both of

these inputs are limited to between 3.7 V and 5.5 V. Bypass

PVCC to PGND with a 1 µF or greater capacitor. Bypass VCC

to GND with a 0.1 µF or greater capacitor.

The power input to the dc-to-dc converter can range between

1.2× th

e output voltage up to 24 V. Bypass the power input to

PGND with a suitably large capacitor. See the Selecting the

Inp

ut Capacitor section.

SETTING THE OUTPUT VOLTAGE

The output voltage is set using a resistive voltage divider from

the output to FB. The voltage divider drops the output voltage

to the 0.6 V FB regulation voltage to set the regulation output

voltage. The output voltage is set to voltages as low as 0.6 V and

as high as 85% of the minimum power input voltage (see the

Feedback Voltage Divider section).

SWITCHING FREQUENCY CONTROL

The ADP1822 has a logic-controlled frequency select input,

FREQ, which sets the switching frequency to 300 kHz or

600 kHz. Drive FREQ low for 300 kHz and drive it high for

600 kHz.

The SYNC input is used to synchronize the converter switching

f

requency to an external signal. The synchronization range is

300 kHz to 1.2 MHz. The acceptable synchronization frequency

range is limited to twice the nominal switching frequency set by

FREQ. For lower frequency synchronization, between 300 kHz

and 600 kHz, connect FREQ to GND. For higher frequency

synchronization, between 480 kHz and 1.2 MHz, connect FREQ

to VCC (see the

rmation).

info

Synchronizing the Converter section for more

COMPENSATION

The control loop is compensated by an external series RC

network from COMP to FB and sometimes requires a series RC

in parallel with the top voltage divider resistor. COMP is the

output of the internal error amplifier.

The internal error amplifier compares the voltage at FB to the

in

ternal 0.6 V reference voltage. The difference between the two

(the feedback voltage error) is amplified by the error amplifier.

To optimize the ADP1822 for stability and transient response

for a given set of external components and input/output voltage

conditions, choose the compensation components. For more

information on choosing the compensation components, see

the

Compensating the Regulator section.

POWER-GOOD INDICATOR

The ADP1822 features an open-drain power-good output,

PWGD, that sinks current when the output voltage drops

8.3% below or 25% above the nominal regulation voltage. Two

comparators measure the voltage at FB to set these thresholds.

The PWGD output also sinks current if overtemperature or

input undervoltage conditions are detected. It is operational

with V

Use this output as a simple power-good signal by connecting a

pu

voltage as low as 1.0 V.

CC

ll-up resistor from PWGD to an appropriate supply voltage.

SHUTDOWN CONTROL

The ADP1822 dc-to-dc converter features a low power shutdown mode that reduces quiescent supply current to 1 µA. To

shut down the ADP1822, drive

SHDN

high. For automatic startup, connect

SHDN

low. To turn it on, drive

SHDN

to VCC.

Rev. C | Page 13 of 24

Page 14

ADP1822

≅

I

www.BDTIC.com/ADI

APPLICATION INFORMATION

SELECTING THE INPUT CAPACITOR

The input capacitor absorbs the switched input current of the

-dc converter, allowing the input source to deliver smooth

dc-to

dc current. Choose an input capacitor whose impedance at the

switching frequency is lower than the input source impedance.

Use low equivalent series resistance (ESR) capacitors, such as

low ESR tantalum, ceramic, or organic electrolyte (such as

Sanyo OS-CON) types. For all types of capacitors, make sure

that the current rating of the capacitor is greater than the input

rms ripple current, which is approximately

V

II

LOADIN_RMS

V

OUT

IN

V

IN

1

−××≅

V

OUT

(1)

OUTPUT LC FILTER

The output LC filter smoothes the switched voltage at SW,

making the output an almost dc voltage. Choose the output LC

filter to achieve the desired output ripple voltage. Since the

output LC filter is part of the regulator negative-feedback

control loop, the choice of the output LC filter components

affects the regulation control-loop stability.

Choose an inductor value such that the inductor ripple current

is approximately 1/3 of the maximum dc output load current.

Using a larger value inductor results in a physical size larger

than required, and using a smaller value results in increased

losses in the inductor and/or MOSFET switches.

Choose the inductor value by

⎡

V

⎢

OUT

))((

L

⎣

SW

1

If

L 1

where:

L is the inductor value.

f

is the switching frequency.

SW

is the output voltage.

V

OUT

V

is the input voltage.

IN

ΔI

is the inductor ripple current, typically 1/3 of the maximum

L

dc load current.

Choose the output capacitor to set the desired output voltage

ripple. The ADP1822 functions with output capacitors that have

both high and low ESR. For high ESR capacitors, such as tantalum

or electrolytic types, many parallel connected capacitors may be

required to achieve the desired output ripple voltage. When

choosing an output capacitor, consider ripple current rating,

capacitance, and ESR. Make sure that the ripple current rating is

higher than the maximum inductor ripple current (I

⎤

V

OUT

−=

(2)

⎥

V

IN

⎦

).

L

The output ripple voltage is a function of the inductor ripple

current and the capacitor impedance at the switching frequency.

For high ESR capacitors, the impedance is dominated by the

ESR, while for low ESR capacitors, the impedance is dominated

by the capacitance. Determine if the capacitor is high ESR or

low ESR by comparing the zero frequency formed by the

capacitance and the ESR to the switching frequency:

f

ESRZ

=

1

()

()

OUT

ESRCπ

2

(3)

where:

f

is the frequency of the output capacitor ESR zero.

ESRZ

C

is the output capacitance.

OUT

ESR is the equivalent series resistance of the capacitor.

If f

is much less than the switching frequency, then the capacitor

ESRZ

is high ESR, and the ESR dominates the impedance at the switching

frequency. If f

is much greater than the switching frequency, the

ESRZ

capacitor is low ESR, and the impedance is dominated by the

capacitance at the switching frequency.

When using capacitors whose impedance is dominated by ESR

at the switching frequency (such as tantalum or aluminum

electrolytic capacitors), approximate the output voltage ripple

current by

)( ESRIV

OUT

L

(4)

where:

is the output ripple voltage.

ΔV

OUT

ΔI

is the inductor ripple current.

L

ESR is the total equivalent series resistance of the output

capacitor (or the parallel combination of ESR of all parallelconnected output capacitors).

Make sure that the ripple current rating of the output capacitor(s) is

greater than the maximum inductor ripple current.

For output capacitors whose ESR is much lower than the

pacitive impedance at the switching frequency, the capacitive

ca

impedance dominates the output ripple current. In this case,

determine the ripple voltage by

Δ

VΔ

≅

OUT

L

()

8

OUT

(5)

()

fC

SW

where:

is the switching frequency.

f

SW

C

is the output capacitance.

OUT

Rev. C | Page 14 of 24

Page 15

ADP1822

()()(

)

()()(

)

(

(

)

(

www.BDTIC.com/ADI

When f

is approximately the same as the switching frequency,

ESRZ

the square-root sum of the squares of the two ripples applies, or

2

[]

OUT

2

)(

ESRIV

L

⎡

+≅

⎢

()

8

OUT

⎣

⎤

I

L

⎥

()

fC

SW

⎦

(6)

SELECTING THE MOSFETS

The choice of MOSFET directly affects the dc-to-dc converter

performance. The MOSFET must have low on resistance to

reduce I

In addition, the MOSFET must have low thermal resistance to

ensure that the power dissipated in the MOSFET does not result

in excessive MOSFET die temperature.

The high-side MOSFET carries the load current during on time

a

the lower the MOSFET on resistance, the higher the gate charge

and vice versa. Therefore, it is important to choose a high-side

MOSFET that balances the two losses. The conduction loss of

the high-side MOSFET is determined by

where:

P

R

The gate-charging loss is approximated by

where:

P

V

Q

f

The high-side MOSFET transition loss is approximated by

where:

P

t

t

The total power dissipation of the high-side MOSFET is the

s

where P

The low-side MOSFET does not carry the transition losses but

do

off. For high input and low output voltages, the low-side

MOSFET carries the current most of the time, and therefore to

achieve high efficiency, it is critical to optimize the low-side

MOSFET for low on resistance. In some cases, where the power

2

R losses and low gate charge to reduce transition losses.

nd carries all the transitions losses of the converter. Typically,

⎞

⎛

2

()()

≅

is the conduction power loss.

C

is the MOSFET on resistance.

ON

T

is the gate-charging loss power.

T

is the gate driver supply voltage.

PVCC

is the MOSFET total gate charge.

G

is the converter switching frequency.

SW

SW

IN

=

P

is the high-side MOSFET switching loss power.

SW

is the MOSFET rise time.

R

is the MOSFET fall time.

F

V

OUT

⎟

⎜

RIP

ONLOADC

⎜

⎝

fQVP ≅ (8)

SWGPVCC

LOAD

(7)

⎟

V

IN

⎠

()

2

fttIV

×+××

FR

SW

(9)

um of all the previous losses, or

PPPP ++≅ (10)

CHS

is the total high-side MOSFET power loss.

HS

SW

T

es carry the inductor current when the high-side MOSFET is

loss exceeds the MOSFET rating, or lower resistance is required

than is available in a single MOSFET, connect multiple low-side

MOSFETs in parallel. The equation for low-side MOSFET

power loss is

()()

RIP

1

⎢

ONLOADLS

⎣

⎡

2

⎤

V

OUT

−≅

(11)

⎥

V

IN

⎦

where:

P

is the low-side MOSFET on resistance.

LS

R

is the total on resistance of the low-side MOSFET(s).

ON

If multiple low-side MOSFETs are used in parallel, use the

arallel combination of the on resistances for determining R

p

ON

to solve this equation.

SETTING THE CURRENT LIMIT

The internal current-limit circuit measures the voltage across

the low-side MOSFET to determine the load current. When the

low-side MOSFET current exceeds the current limit, the highside MOSFET is not allowed to turn on until the current drops

below the current-limit.

The current limit is set through the current-limit resistor, R

The current-sense pin, CSL, sources 50 µA through R

creates an offset voltage of resistance of R

multiplied by the

CL

50 µA CSL current. When the low-side MOSFET voltage is

equal to or greater than the offset voltage, the ADP1822 is in

current limit mode and prevents additional on-time cycles.

Choose the current-limit resistor by the equation

)

RI

LPK

R =

CL

ONWC

(12)

A42

where:

is the peak inductor current.

I

LPK

R

is the worst-case (maximum) low-side MOSFET on

ONWC

resistance.

The worst-case, low-side MOSFET on resistance can be found

he MOSFET data sheet. Note that MOSFETs typically

in t

increase on resistance with increasing die temperature. To

determine the worst-case MOSFET on resistance, calculate the

worst-case MOSFET temperature (based on the MOSFET

power loss) and multiply by the ratio between the typical on

resistance at that temperature and the on resistance at 25°C as

listed in the MOSFET data sheet.

In addition, the ADP1822 offers a technique for implementing a

urrent-limit foldback in the event of a short circuit with the

c

use of an additional resistor, as shown in

is largely responsible for setting the foldback current limit

R

LO

during a short circuit, and R

up the normal current limit. R

is mainly responsible for setting

HI

is lower than RHI.

LO

Figure 18. The resistor

These current-limit sense resistors can be calculated as

)( )

RI

R = (13)

LO

ONWCPKFOLDBACK

A42

. This

CL

.

CL

Rev. C | Page 15 of 24

Page 16

ADP1822

V

()(

M

MUP

www.BDTIC.com/ADI

V

R

=

HI

I

LPK

R

OUT

ONWC

R

LO

(14)

A42−

where:

I

PKFOLDBACK

is the desired short-circuit peak inductor current

limit.

I

is the peak inductor current limit during normal operation

LPK

and is also used in Equation 12.

IN

ADP1822

DH

DL

CSL

Figure 18. Short-Circuit Current Foldback Scheme

M1

M2

R

LO

LV

OUT

+

C

R

HI

OUT

05311-118

FEEDBACK VOLTAGE DIVIDER

The output regulation voltage is set through the feedback

voltage divider. The output voltage is reduced through the

voltage divider and drives the FB feedback input. The regulation

threshold at FB is 0.6 V. For the low-side resistor of the voltage

divider, R

results in a reduction in output voltage accuracy. Choose R

, use 10 kΩ. A larger value resistor can be used but

BOT

TOP

to

set the output voltage by

⎛

OUT

⎜

RR

=

BOTTOP

⎜

⎝

⎞

VV

−

FB

⎟

(15)

⎟

V

FB

⎠

where:

R

is the high-side voltage divider resistance.

TOP

R

is the low-side voltage divider resistance.

BOT

V

is the regulated output voltage.

OUT

V

is the feedback regulation threshold, 0.6 V.

FB

SETTING THE VOLTAGE MARGIN

The output voltage is margined by connecting a resistor from

FB to GND (for the high margin voltage) or FB to the output

voltage (for low margin voltage). The switches for margining are

supplied inside the ADP1822 and are controlled by the MAR

and MSEL inputs (see

Choose the high margin resistor by

⎡

()()

⎢

⎣

R

=

UP

where:

R

is the up-margin resistor from MUP to GND.

UP

R

is the bottom voltage divider resistor from FB to GND.

BOT

R

is the top voltage divider resistor from FB to the output

TOP

voltage.

K

is the high voltage margin as a ratio of the output voltage

MUP

(for example, margining 4% up would be K

K

RR

+

RR

Tabl e 1 ).

⎤

BOTTOP

⎥

BOTTOP

⎦

(16)

= 0.04).

MUP

Choose the low margin resistor by the equation

R 1

DN

⎥

⎢

K

MDN

⎦

⎣

⎤

⎡

R

TOP

=

⎡

V

FB

⎢

⎣

−−

V

OUT

⎤

K

(17)

⎥

MDN

⎦

where:

R

is the down-margin resistor.

DN

R

is the top voltage divider resistor from FB to the output

TOP

voltage.

V

is the 0.6 V feedback voltage.

FB

V

is the nominal output voltage setting.

OUT

K

is the down-margin as a ratio of the nominal output voltage

MDN

(for example, margining 4% down would be K

MDN

= 0.04).

For example, for an output voltage of 1.0 V and a ±5% margin,

choose

R

= 10 kΩ (18)

BOT

Thus,

⎡

OUT

RR

=

⎢

BOTTOP

⎣

⎤

VV

−

FB

⎥

V

FB

⎦

(19)

k67.6=

and

⎡

⎢

⎢

⎣

R

=

UP

K

⎤

)

RR

BOTTOP

⎥

RR

+

⎥

BOTTOP

⎦

UP

(20)

kΩ

80=

and

MDN

⎤

(21)

kΩK

7.461 =

⎥

⎥

⎦

⎡

=

R

⎢

DN

⎢

⎣

⎡

⎤

R

TOP

K

MDN

V

FB

⎢

⎥

⎥

⎢

⎦

⎣

−−

V

OUT

COMPENSATING THE REGULATOR

The output of the error amplifier at COMP is used to compensate

the regulation control system. Connect a resistor capacitor (RC)

network from COMP to FB to compensate the regulator.

The first step of selecting the compensation components is

determining the desired regulation-control crossover frequency,

f

. Choose a crossover frequency approximately 1/10 of the

CO

switching frequency, or

f

SW

f =

CO

The characteristics of the output capacitor affect the compensation

required to stabilize the regulator. The output capacitor acts

with its ESR to form a zero. Calculate the ESR zero frequency by

f

ESRZ

Note that as similar capacitors are placed in parallel, the ESR

zero frequency remains the same.

≤ fCO/2, use the ESR zero to stabilize the regulator (see the

If f

ESRZ

Compensation Using the ESR Zero section). If f

feed-forward network to stabilize the regulator (see the

(22)

10

=

1

()

()

OUT

ESRC

π2

(23)

≥ 2fCO, use a

ESRZ

/2 < f

section). If f

CO

ESRZ

< 2fCO, Compensation Using Feed-Forward

Rev. C | Page 16 of 24

Page 17

ADP1822

(

)

()(

)

(

)

N

(

(

(

www.BDTIC.com/ADI

then use both the ESR zero and feed-forward zeros to stabilize

the regulator (see the Compensation Using Both the ESR and

F

eed-Forward Zeros section).

In all three cases, it is sometimes beneficial, although not required,

o add an additional compensation capacitor, C

t

, from COMP

C2

to FB to reduce high frequency noise. This capacitor forms an

extra pole in the loop response. Choose this capacitor such that

the pole occurs at approximately 1/2 of the switching frequency, or

f

PC

2

Assuming C

=

2

C

f

SW

==

2

COMP

()()

>> CC2, then solving for CC2,

2

()( )

RfCπ2

COMPSW

1

RCCπ

//2

2

(24)

COMPCCOMP

(25)

Compensation Using the ESR Zero

C

C2

C

R

COMP

COMP

TO

PWM

INTERNAL ERROR AMPLIFIER

Figure 19. Compensation Using the ESR Zero

COMP

FB

0.6V

V

OUT

R

TOP

R

BOT

05311-003

If the output capacitor ESR zero is sufficiently low (less than or

equal to 1/2 of the crossover frequency), use the ESR to stabilize

the regulator. In this case, use the circuit shown in

hoose the compensation resistor to set the desired crossover

C

Figure 19.

frequency, typically 1/10 of the switching frequency or

R =

COMP

()

TOP

()

RAMP

ESRZ

2

()

fV

IN

LC

()

ffVR

CO

(26)

where:

R

is the compensation resistor.

COMP

is the internal ramp peak voltage, 1.25 V.

V

RAMP

f

and fCO are the ESR zero and crossover frequencies.

ESRZ

is the dc input voltage.

V

IN

f

is the characteristic frequency of the output LC filter, or

LC

1

f

=

LC

(27)

LC

π2

using known constants

≅

COMP

Choose the compensation capacitor

, to the lesser of 1/4 of the crossover frequency or 1/2 of

zero, f

ZC

ESRZTOP

V

I

to set the compensation

(28)

()

CLffRR9.4

()

SW

the LC resonant frequency, or

ff

f

ZC

SWCO

===

404

1

()()

π2

(29)

RC

COMPCOMP

or

f

ZC

Solving for C

COMP

f

LC

==

2

,

COMP

=

()( )

1

()()

π2

RC

4

RfCπ2

COMPCO

(30)

COMPCOMP

(31)

In terms of the switching frequency and combining the constants,

C

COMP

≅

37.6

()( )

(32)

Rf

COMPSW

or

COMP

=

2

()( )

RfCπ2

(33)

COMPLC

or whichever is greater.

Compensation Using Feed-Forward

C

C2

C

R

COMP

COMP

TO

PWM

INTERNAL ERROR AMPLIFIER

Figure 20. Compensation Using Feed-Forward

COMP

FB

0.6V

V

OUT

C

TOP

BOT

FF

R

FF

05311-004

R

R

If the ESR zero is at too high a frequency to be useful in

stabilizing the regulator, add a series RC network, as shown in

Figure 20, in parallel with the top side voltage divider resistor,

R

. This adds an additional zero and pole pair that is used to

TOP

increase the phase at crossover, thus improving stability.

Choose the feed-forward zero frequency for 1/7 of the crossover

requency, and the feed-forward pole at 7× the crossover

f

frequency. This sets the ratio of pole-to-zero frequency of

approximately 50:1 for optimum stability.

Choose the compensation resistor, R

, to set the crossover

COMP

frequency by

)

)( )( )

ffVR

R =

where f

RAMP

COMP

ZFF

TOP

()

fV

IN

LC

is the feed-forward zero frequency and is 1/7 of the

ZFF

CO

2

(34)

crossover frequency. Simplify the following equation:

2

)

R

COMP

0705.0≅ (35)

V

()

TOP

SW

()

CLfR

()

IN

Rev. C | Page 17 of 24

Page 18

ADP1822

(

()(

(

(

f

www.BDTIC.com/ADI

Choose the compensation capacitor to set the compensation

zero, f

, to the lesser of 1/4 of the crossover frequency or 1/2 of

ZC

the LC resonant frequency, or

ff

f

ZC

SWCO

===

404

1

()()

π2

RC

(36)

COMPCOMP

or

f

ZC

Solving for C

COMP

f

LC

==

2

,

COMP

=

()( )

1

()()

π2

4

RfCπ2

COMPCO

(37)

RC

COMPCOMP

(38)

In terms of the switching frequency and combining the constants,

C

COMP

≅

37.6

()( )

(39)

Rf

COMPSW

or

COMP

=

2

()( )

(40)

RfCπ2

COMPLC

or whichever is greater.

Choose the feed-forward capacitor, C

, to set the feed-forward

FF

zero at 1/7 of the crossover frequency

CO

f =

ZFF

(41)

7

or

=

CO

Simplifying and solving for C

C

=

FF

Choose the feed-forward resistor, R

=

CO

Simplifying and solving for R

R

=

FF

7

()

()

CRfπ2

FF

TOP

14.11

()

TOP

(43)

()

fR

SW

1

()

()()

CRfπ27

FFFF

227.0

()

SW

(45)

()

Cf

FF

(42)

,

FF

, to set the condition

FF

(44)

,

FF

Compensation Using Both the ESR and Feed-Forward Zeros

If the output capacitor ESR zero frequency falls between 1/2 of

the crossover frequency to 2× the crossover frequency, use the

circuit shown in Figure 19, such that the ESR zero, along with a

eed-forward network, stabilizes the regulator. In this case, the

f

feed-forward zero is set to 1/7 of the crossover frequency, and

the feed-forward pole is set to the same frequency as the ESR zero.

Choose the compensation resistor, R

, to set the crossover

COMP

frequency by

R =

COMP

where f

is the feed-forward zero frequency and is 1/7 of the

ZFF

crossover frequency. Simplify the following equation:

R

COMP

Choose the compensation capacitor to set the compensation

zero, f

, to 1/2 of the LC resonant frequency, or

ZC

f

ZC

Solving for C

COMP

Choose the feed-forward capacitor, C

zero at 1/7 of the crossover frequency

f =

ZFF

or

=

CO

Simplifying and solving for C

C

=

FF

()

Choose the feed-forward resistor, R

=

CO

Simplifying and solving for R

R

=

FF

()

SETTING THE SOFT START PERIOD

The ADP1822 uses an adjustable soft start to limit the output

voltage ramp-up period, limiting the input inrush current. The

soft start is set by selecting the capacitor, C

The ADP1822 charges C

The voltage on C

CSS

where R is the in

is achieved when V

)

RAMP

TOP

IN

TOP

0705.0≅ (47)

f

LC

==

()()

π2

2

,

COMP

=

f

2

()( )

RfCπ2

COMPLC

CO

(50)

7

7

()

()

CRfπ2

FF

TOP

14.11

(52)

()

fR

SW

TOP

1

()

()()

CRfπ27

FFFF

227.0

(54)

()

Cf

FF

SW

SS

while it is charging is

SS

⎛

⎜

−=

eV

1V8.0

⎜

⎝

ternal 100 kΩ resistor. The soft start period, t

= 0.6 V, or

CSS

⎛

⎜

−=

1V8.0V6.0

e

⎜

⎝

)( )

ffVR

CO

ZFF

2

()

fV

LC

)

SW

V

IN

1

RC

COMPCOMP

(46)

2

)

()

CLfR

()

(48)

(49)

, to set the feed-forward

FF

(51)

,

FF

, to set the condition

FF

(53)

,

FF

, from SS to GND.

SS

to 0.8 V through an internal resistor.

1

⎞

RC

⎟

SS

(55)

⎟

⎠

SS

t

SS

⎞

)k100

C

⎟

SS

(56)

⎟

⎠

,

Rev. C | Page 18 of 24

Page 19

ADP1822

www.BDTIC.com/ADI

or

t

SS

()

C

kΩ100

SS

Solving for C

C

SS

and combining constants,

SS

= (7.213 × 10−6)tSS (58)

⎛

⎜

−−=

1ln

⎜

⎝

⎞

V6.0

⎟

=

⎟

V8.0

⎠

(57)

386.1

SYNCHRONIZING THE CONVERTER

The dc-to-dc converter switching can be synchronized to an

external signal. This allows multiple ADP1822 converters to be

operated at the same frequency to prevent frequency beating or

other interactions.

To synchronize the ADP1822 switching to an external signal,

drive the SYNC input with the synchronizing signal. The ADP1822

can only synchronize up to 2× the nominal oscillator frequency.

If the frequency is set to 300 kHz (FREQ connected to GND), it

can synchronize up to 600 kHz. If the frequency is set to 600 kHz

(FREQ connected to VCC), it can synchronize to 1.2 MHz.

The high-side MOSFET turn-on follows the rising edge of

the SYNC input by approximately 320 ns. To prevent erratic

switching frequency, make sure that the falling edge of the

SYNC input signal does not coincide with the falling edge of

the dc-to-dc converter switching, or

V

()

[]

()

f D +≠ ns320

SWSYNC

OUT

(59)

V

IN

where D

Make sure that in all combinations of frequency, input, and

output voltages, the SYNC input fall time does not align with

the dc-to-dc converter fall time.

SETTING THE OUTPUT VOLTAGE TRACKING

The ADP1822 provides a tracking function that limits the

output voltage to or below an external tracking voltage. This is

useful in systems where multiple dc-to-dc converters are used to

power different sections of a circuit, such as a microcontroller or a

DSP that has separate I/O and core voltages. In similar circuits,

if the nominally lower of the two voltages exceeds the nominally

higher voltage at startup or shutdown, the circuit powered may

experience problems. To prevent this, use the tracking feature of

the ADP1822 to limit the output voltage to or below the tracking

voltage at all times.

To use the tracking feature, connect TRKP to the output voltage

and drive TRKN with the tracking voltage. To ensure that noise

does not cause unstable operation, connect a 1 nF capacitor

between TRKN and TRKP as close to the ADP1822 as possible.

If either the ADP1822 output voltage or the tracking voltage at

any time exceeds the voltage at VCC, use equal voltage dividers

from the output voltage to TRKP and from the tracking voltage

to TRKN to prevent overstress on the TRKP and TRKN inputs.

is the duty cycle of the synchronization waveform.

SYNC

Rev. C | Page 19 of 24

Page 20

ADP1822

www.BDTIC.com/ADI

APPLICATION CIRCUITS

15pF

1µF

80.6kΩ

309pF

10Ω

1µF

100nF

VCC

ADP1822

SHDN

FREQ

SYNC

PWGD

MAR

MSEL

COMP

SS

AGND DGND

PVCC

BST

DH

SW

CSL

PGND

TRKP

TRKN

MDN

MUP

CMOSH-3

DL

FB

0.1µF

2.2pF

1nF

158kΩ

316kΩ

10Ω

3.01kΩ

3×

IRF3711

1µH

2×

180µF

20V

Figure 21. Typical Application Circuit, 5 V Input

4× 1000µF, 4V

20kΩ

10kΩ

INPUT

5V

TRACKING

SIGNAL INPUT

OUTPUT

1.8V, 15A

05311-019

0.1µF

2.2pF

1nF

316kΩ

CMOZ5V6

3.01kΩ

158kΩ

1.2kΩ

Q1

IRF3711

1µH

2×

IRF3711

2×

180µF

20V

4× 1000µF, 4V

20kΩ

10kΩ

INPUT

12V

TRACKING

SIGNAL INPUT

OUTPUT

1.8V, 15A

05311-020

15pF

1µF

80.6kΩ

309pF

10Ω

1µF

100nF

VCC

ADP1822

SHDN

FREQ

SYNC

PWGD

MAR

MSEL

COMP

SS

AGND DGND

PVCC

CMST2222A

CMOSH-3

BST

DH

SW

CSL

DL

PGND

FB

TRKP

TRKN

MDN

MUP

Figure 22. Typical Application Circuit, 12 V Input

Rev. C | Page 20 of 24

Page 21

ADP1822

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

0.345

0.341

0.337

PIN 1

0.010

0.004

COPLANARITY

0.004

24 13

1

0.065

0.049

0.025

BSC

COMPLIANT TO JEDEC STANDARDS MO-137AE

0.012

0.008

0.069

0.053

12

0.158

0.154

0.150

SEATING

PLANE

0.244

0.236

0.228

0.010

0.006

8°

0°

0.050

0.016

Figure 23. 24-Lead Shrink Small Outline Package [QSOP]

Q-24)

(R

Dimensions shown in inches

ORDERING GUIDE

Model Temperature Range Package Description Package Option

ADP1822ARQZ-R7 −40°C to +85°C 24-Lead Shrink Small Outline Package [QSOP] RQ-24

2

ADP1822-EVAL Evaluation Board

1

Operating junction temperature is –40°C to +125°C.

2

Z = RoHS Compliant Part.

1

Rev. C | Page 21 of 24

Page 22

ADP1822

www.BDTIC.com/ADI

NOTES

Rev. C | Page 22 of 24

Page 23

ADP1822

www.BDTIC.com/ADI

NOTES

Rev. C | Page 23 of 24

Page 24

ADP1822

www.BDTIC.com/ADI

NOTES

©2006–2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05311-0-5/07(C)

Rev. C | Page 24 of 24

Loading...

Loading...