Page 1

3.3 V Dual-Loop 50 Mbps to 3.3 Gbps

Data Sheet

FEATURES

50 Mbps to 3.3 Gbps operation

Single 3.3 V operation

Typical rise/fall time: 80 ps

Bias current range: 2 mA to 100 mA

Modulation current range: 5 mA to 80 mA

Monitor photodiode current: 50 μA to 1200 μA

Dual MPD functionality for DWDM

50 mA supply current at 3.3 V

Closed-loop control of power and extinction ratio

Full current parameter monitoring

Laser fail and laser degrade alarms

Automatic laser shutdown (ALS)

Optional clocked data

Supports FEC rates

48-lead (7 mm × 7 mm) LFCSP package

32-lead (5 mm × 5 mm) LFCSP package

Laser Diode Driver

ADN2847

APPLICATIONS

SONET OC-1/3/12/48

SDH STM-0/1/4/16

Fibre Channel

Gigabit Ethernet

DWDM dual MPD wavelength control

GENERAL DESCRIPTION

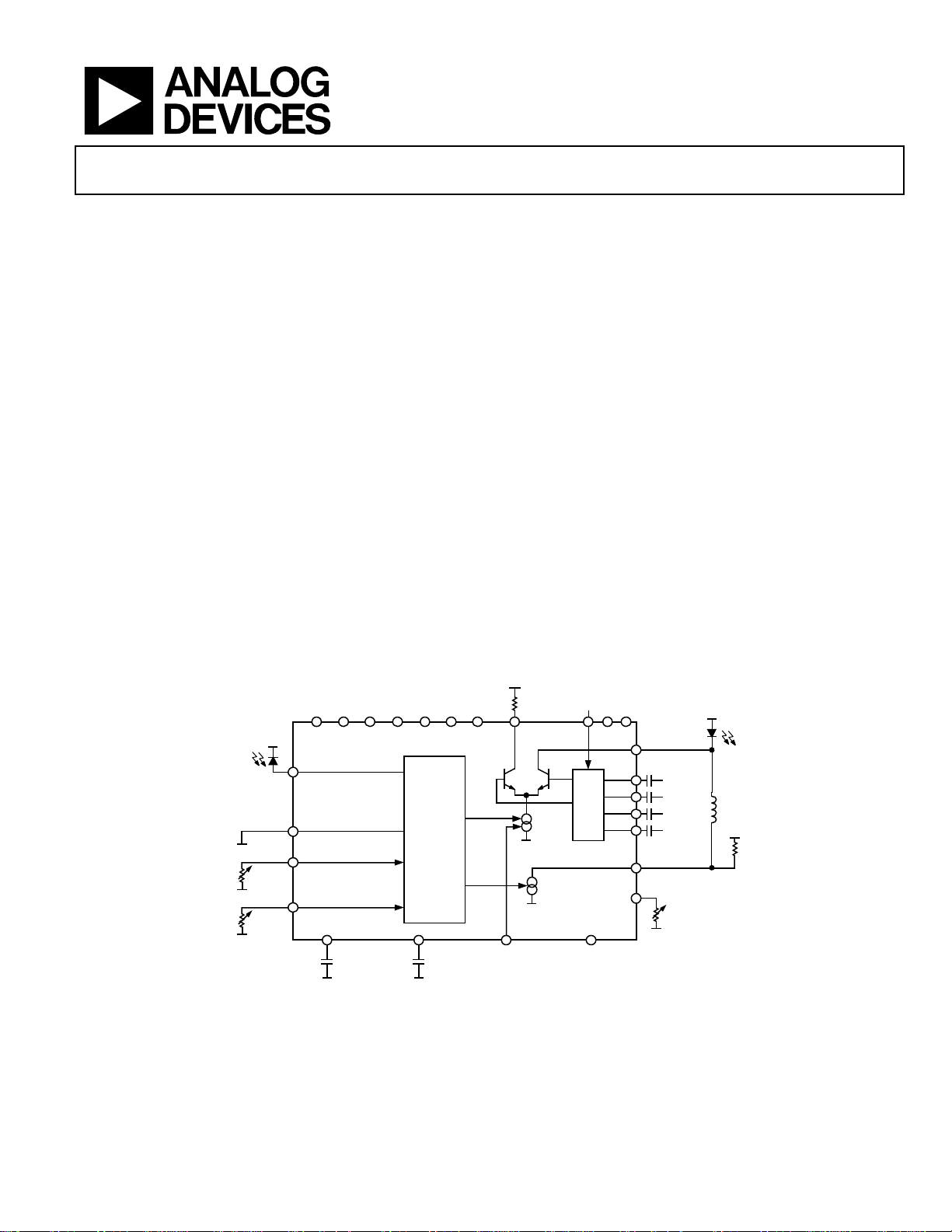

The ADN2847 uses a unique control algorithm to control both

average power and extinction ratio of the laser diode (LD) after

initial factory setup. External component count and PCB area

are low, as both power and extinction ratio control are fully

integrated. Programmable alarms are provided for laser fail

(end of life) and laser degrade (impending fail).

Optional dual MPD current monitoring is designed into the

ADN2847 specifically for DWDM wavelength control.

The ADN2847 is specified for the −40°C to +85°C temperature

range and is available in a 48-lead LFCSP package and a 32-lead

LFCSP package.

FUNCTIONAL BLOCK DIAGRAM

V

CC

CLKSEL

MPD

GND

GND

GND

V

CC

IMPD

IMPD2

PSET

ERSET

IBMON

IMMON

IMPDMON

IMPDMON2

CONTROL

PAV C A PERCAP

GNDGND

CC

ALS

FAI L

DEGRADE

IMODN

I

MOD

I

BIAS

V

GND

IMODP

I

BIAS

ASET

ADN2847

GND

LBWSETIDTONE

Figure 1.

DATAP

DATAN

CLKP

CLKN

LD

V

CC

V

CC

R

Z

02745-001

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2003–2012 Analog Devices, Inc. All rights reserved.

Page 2

ADN2847 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Diagrams.......................................................................... 4

Absolute Maximum Ratings............................................................ 5

Thermal Resistance ...................................................................... 5

ESD Caution.................................................................................. 5

Die Pad Coordinates ........................................................................ 6

Pin Configurations and Function Descriptions ........................... 7

Theory of Operation ........................................................................ 9

Control........................................................................................... 9

Loop Bandwidth Selection .......................................................... 9

Alarms.............................................................................................9

Monitor Currents ....................................................................... 10

Dual MPD DWDM Function (48-Lead LFCSP Only) ......... 10

IDTONE (48-Lead LFCSP Only)............................................. 10

Data and Clock Inputs............................................................... 10

CCBIAS........................................................................................ 10

I

................................................................................................ 10

BIAS

Automatic Laser Shutdown....................................................... 10

Alarm Interfaces......................................................................... 11

Power Consumption .................................................................. 11

Laser Diode Interfacing............................................................. 11

Optical Supervisor...................................................................... 11

Outline Dimensions....................................................................... 14

Ordering Guide .......................................................................... 15

REVISION HISTORY

3/12—Rev. A to Rev. B

Added EPAD Notation .................................................................... 7

Updated Outline Dimensions....................................................... 14

Changes to Ordering Guide.......................................................... 15

10/06—Rev. 0 to Rev. A

Updated Format..................................................................Universal

Change to Data Sheet Title.............................................................. 1

Changes to Figure 1.......................................................................... 1

Changes to Specifications................................................................ 3

Added I

Changes to Laser Diode Interfacing Section............................... 11

Changes to Figure 14...................................................................... 12

Changes to Figure 15...................................................................... 13

Changes to Ordering Guide.......................................................... 15

1/03—Revision 0: Initial Version

Section ......................................................................... 10

BIAS

Rev. B | Page 2 of 16

Page 3

Data Sheet ADN2847

SPECIFICATIONS

VCC = 3.0 V to 3.6 V. Temperature range: −40°C to +85°C. All specifications T

at T

= 25°C.

A

Table 1.

Parameter Min Typ Max Unit Conditions/Comments

LASER BIAS CURRENT (I

Output Current I

I

when ALS is asserted 0.1 mA

BIAS

, ALS)

BIAS

2 100 mA

BIAS

ALS Assertion Time 5 μs I

I

Compliance Voltage 1.2 VCC V

BIAS

CCBIAS Compliance Voltage 1.2 VCC V

MODULATION CURRENT (IMODP, IMODN)1

Output Current I

5 80 mA

MOD

Compliance Voltage 1.5 VCC V

I

when ALS is Asserted 0.1 mA

MOD

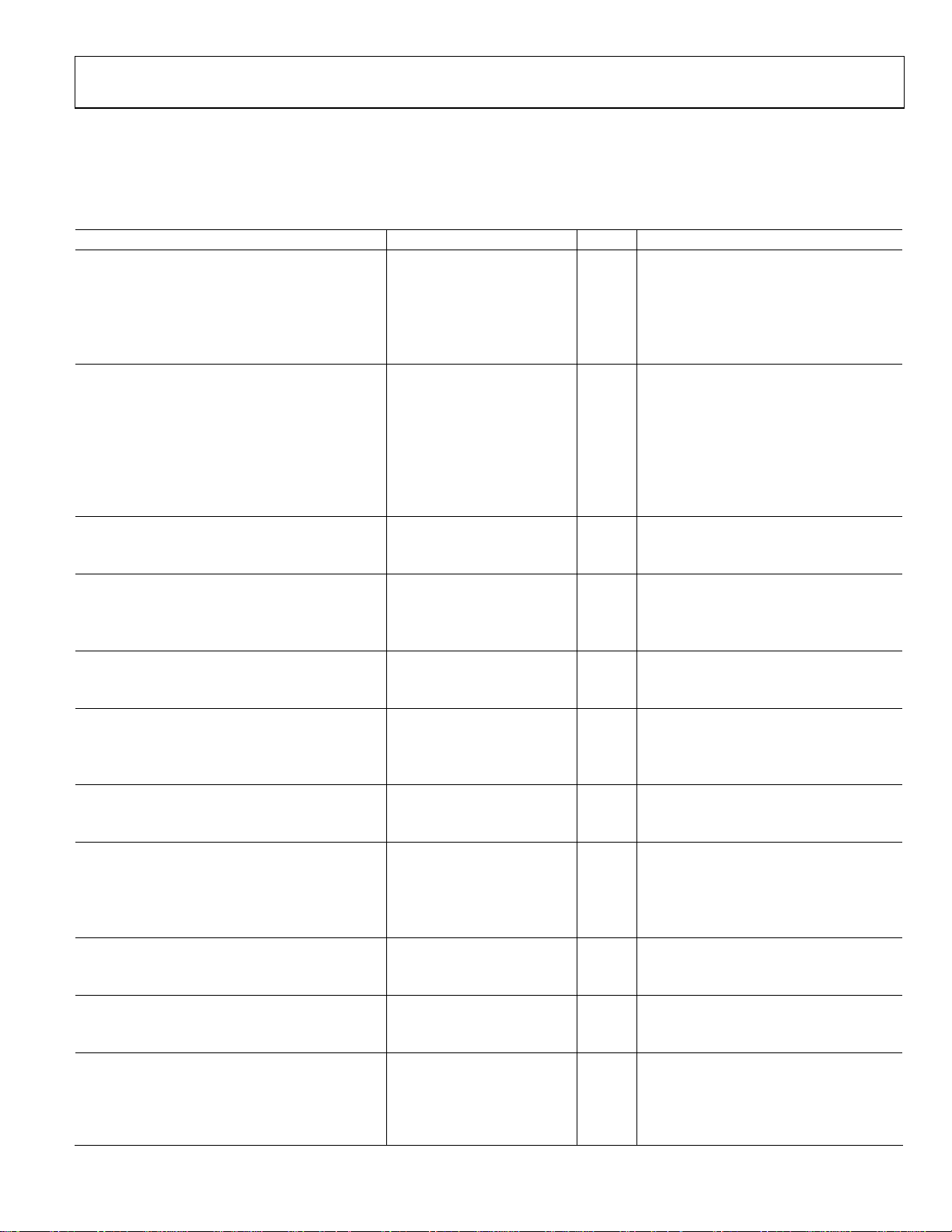

Rise Time2 80 120 ps See Figure 3 for device rise time histogram

Fall Time2 80 120 ps See Figure 4 for device fall time histogram

Random Jitter2 1 1.5 ps RMS

Pulse Width Distortion2 15 ps I

MONITOR PD (MPD, MPD2)

Current 50 1200 μA Average current

Compliance Voltage 1.65 V

POWER SET INPUT (PSET)

Capacitance 80 pF

Monitor Photodiode Current into RPSET Resistor 50 1200 μA Average current

Voltage 1.1 1.2 1.3 V

EXTINCTION RATIO SET INPUT (ERSET)

Allowable Resistance Range 1.2 25 kΩ

Voltage 1.1 1.2 1.3 V

ALARM SET (ASET)

Allowable Resistance Range 1.2 25 kΩ

Voltage 1.1 1.2 1.3 V

Hysteresis 5 %

CONTROL LOOP Low Loop Bandwidth selection

Time Constant 0.22 sec LBWSET = GND

2.25 sec LBWSET = VCC

DATA INPUTS (DATAP, DATAN, CLKP, CLKN)3

V p-p (Single-Ended, Peak-to-Peak) 100 500 mV Data and clock inputs are ac-coupled

Input Impedance (Single-Ended) 50 Ω

4

t

50 ps See Figure 2

SETUP

4

t

100 ps See Figure 2

HOLD

LOGIC INPUTS (ALS, LBWSET, CLKSEL)

VIH 2.4 V

VIL 0.8 V

ALARM OUTPUTS (FAIL, DEGRADE) Internal 30 kΩ Pull-Up

V

2.4 V

OH

VOL 0.8 V

IDTONE

Compliance Voltage VCC − 1.5 V

I

Ratio 2

OUT/IIN

5

f

0.01 1 MHz

IN

MIN

to T

, unless otherwise noted. Typical values specified

MAX

< 10% of nominal

BIAS

= 40 mA

MOD

User to supply current sink in the range of

50 μA to 4 mA

Rev. B | Page 3 of 16

Page 4

ADN2847 Data Sheet

Parameter Min Typ Max Unit Conditions/Comments

IBMON, IMMON, IMPDMON, IMPDMON2

IBMON, IMMON Division Ratio 100 A/A

IMPDMON, IMPDMON2 1 A/A

IMPDMON to IMPDMON2 Matching 2 % I

Compliance Voltage 0 VCC −1.2 V

SUPPLY

6

I

50 mA I

CC

7

V

3.0 3.3 3.6 V

CC

1

The high speed performance for the die version of ADN2847 can be achieved when using the bonding diagram shown in Figure 6.

2

Measured into a 25 Ω load using a 11110000 pattern at 2.5 Gbps.

3

When the voltage on DATAP is greater than the voltage on DATAN, the modulation current flows in the IMODP pin.

4

Guaranteed by design and characterization. Not production tested.

5

IDTONE can cause eye distortion.

6

I

for power calculation in the P section is the typical ICC given. ower Consumption

CCMIN

7

All VCC pins should be shorted together.

TIMING DIAGRAMS

= 1200 μA

MPD

= I

BIAS

MOD

= 0

DA TAP/ D ATAN

CLKP

40

30

20

COUNT (%)

10

0

76

78 82 84 86 88 90 92 94 96 98 10080

RISE TIME (ps)

Figure 3. Rise Time Distribution Under Worst-Case Operating Conditions

SETUP

t

S

Figure 2. Setup and Hold Time

40

30

20

COUNT (%)

10

2745-007

Figure 4. Fall Time Distribution Under Worst-Case Operating Conditions

HOLD

t

H

0

80

82 86 88 90 92 94 96 98 100 102 10484

02745-002

FAL L TI ME ( p s )

02745-008

Rev. B | Page 4 of 16

Page 5

Data Sheet ADN2847

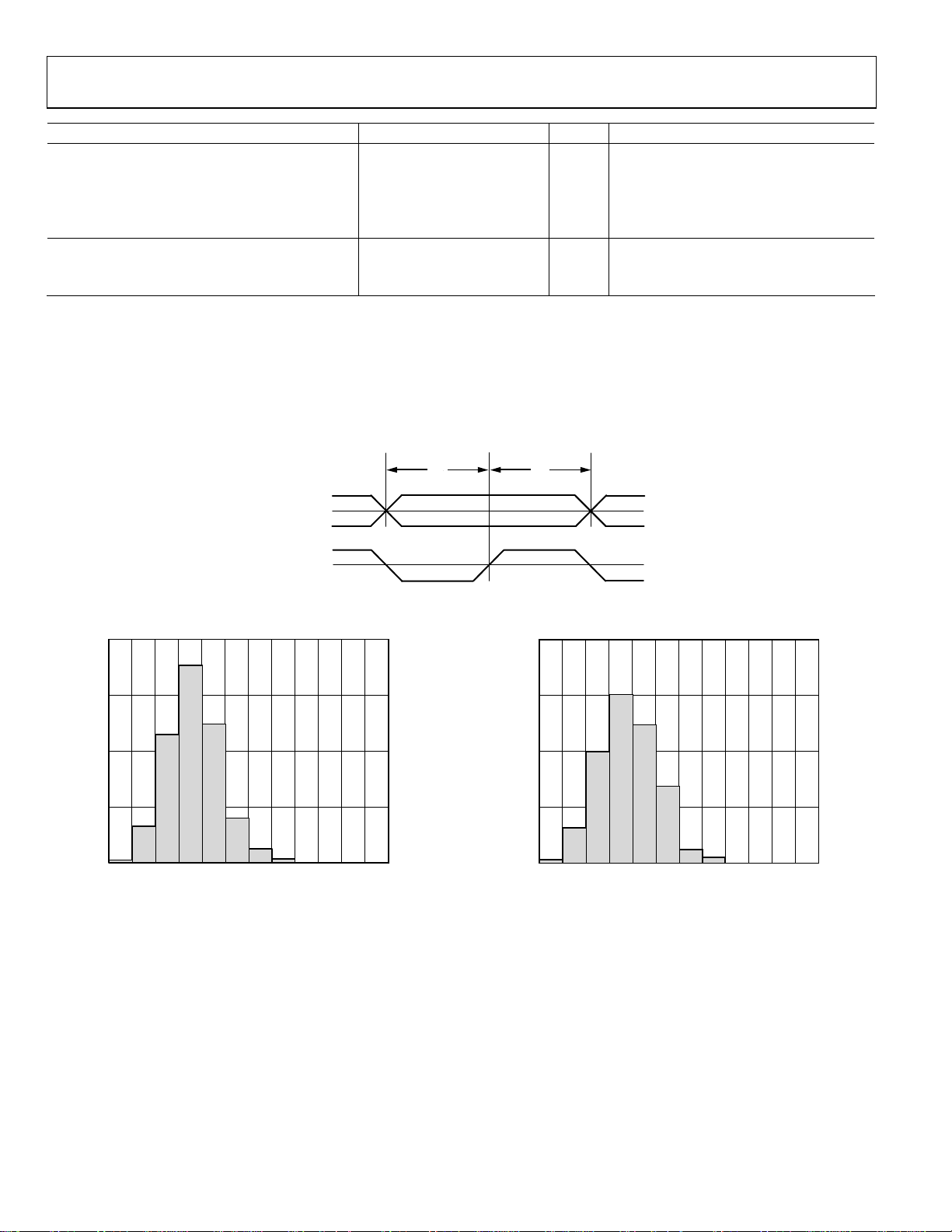

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 2.

Parameter Rating

VCC to GND 4.2 V

Digital Inputs (ALS, LBWSET, CLKSEL) −0.3 V to VCC + 0.3 V

IMODN, IMODP V

Operating Temperature Range Industrial −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Junction Temperature (TJ max) 150°C

Power Dissipation1 (W)

Lead Temperature (Soldering 10 sec) 300°C

1

Power consumption formulae are provided in the Power Consumption

section.

+ 1.2 V

CC

(TJ max − TA)/ θJA

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type θJA Unit

48-lead LFCSP 25 °C/W

32-lead LFCSP 32 °C/W

ESD CAUTION

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. B | Page 5 of 16

Page 6

ADN2847 Data Sheet

m

m

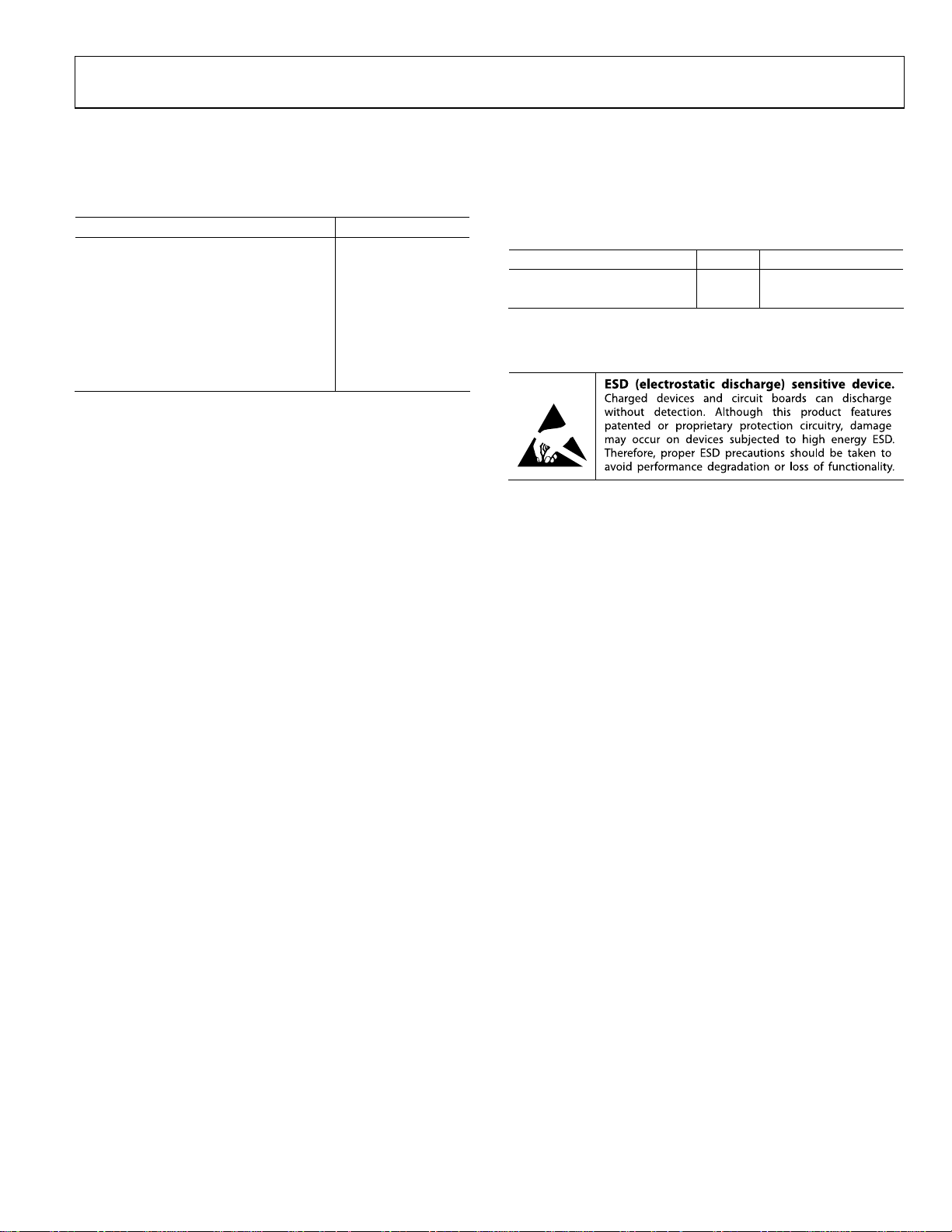

DIE PAD COORDINATES

2280µm

2620µ

2280µ

GND2

GND2

IBMON

GND2

V

2

CC

IMODN

IMODN

GND2

IMODP

IMODP

GND2

GND2

I

BIAS

I

BIAS

CCBIAS

ASET

GND GND4

LBWSET

ERSET

IMMON

PSET

V

3GNDCLKSEL

CC

IMPD

GND

FAIL

ALS

IMPDMON2

DEGRADEIDTONE

GNDGND3

GND

CLKN

CLKP

GND1

DATAP

DATAN

GND1

V

1

CC

GND

PAVC AP

ERCAP

4IMPD2IMPDMON

V

CC

Figure 5. Metallization Photograph

Table 4. Die Pad Coordinates

1

Pad Number Pad Name x[μm] y[μm]

1 TP1 (GND) −996 1026

2 LBWSET −996 853

3 ASET −996 679

4 ERSET −996 506

5 PSET −996 332

6 TP2 (GND) −996 159

7 IMPD −996 −15

8 IMPDMON −996 506

9 IMPDMON2 −996 −361

10 IMPD2 −996 −534

11 GND4 −996 −724

12 VCC4 −995 −964

13 ERCAP −925 −1191

14 PAVCAP −777 −1191

15 TP3 (GND) −606 −1191

16 VCC1 −389 −1191

17 GND1 −200 −1191

18 DATAN −70 −1191

19 DATAP 83 −1191

20 GND1 263 −1191

21 CLKP 442 −1191

22 CLKN 596 −1191

23 TP4 (GND) 762 −1191

24 TP5 (GND) 996 −1109

1

With the origin in the center of the die (see Figure 5).

DIE ROTATED 90° IN PACKAGE

LEFT RIGHT

1

BOTTOM

02745-003

TOP

2620µm

02745-004

Figure 6. Bonding Diagram

Pad Number Pad Name x[μm] y[μm]

25 TP6 (GND) 996 −935

26 CLKSEL 996 −762

27 DEGRADE 996 −589

28 FAIL 996 −415

29 ALS 996 −242

30 VCC3 996 −19

31 GND3 996 251

32 IMMON 996 441

33 IBMON 996 614

34 GND2 996 804

35 IDTONE 995 993

36 GND2 995 1133

37 GND2 867 1191

38 VCC2 713 1191

39 IMODN 500 1191

40 IMODN 396 1191

41 GND2 242 1191

42 IMODP 88 1191

43 IMODP −16 1191

44 GND2 −239 1191

45 GND2 −443 1191

46 I

47 I

−633 1191

BIAS

−772 1191

BIAS

48 CCBIAS −912 1191

Rev. B | Page 6 of 16

Page 7

Data Sheet ADN2847

6

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

BIAS

BIAS

48 CCBIAS

47 I

46 I

45 GND2

44 GND2

43 IMODP

42 IMODP

41 GND2

40 IMODN

TP1 1

LBWSET 2

ASET 3

ERSET 4

PSET 5

TP2 6

IMPD 7

IMPDMON 8

IMPDMON2 9

IMPD2 10

GND4 11

V

4 12

CC

NOTES

1. THE EXPOSED PAD ON THE BOTTOM OF THE

PACKAGE MUST BE CONNECTED TO V

THE GND PL ANE.

PIN 1

INDICATOR

(Not to Scale)

TP3 15

ERCAP 13

PAVCAP 14

ADN2847

TOP VIEW

1 16

CC

V

GND1 17

DATAP 19

DATAN 18

CLKP 21

GND1 20

Figure 7. 48-Lead LFCSP

2

CC

39 IMODN

38 V

TP4 23

CLKN 22

37 GND2

TP5 24

CC

36 GND2

35 IDTONE

34 GND2

33 IBMON

32 IMMON

31 GND3

30 V

3

CC

29 ALS

28 FAIL

27 DEGRADE

26 CLKSEL

25 TP6

OR

BIAS

30 GND2

32 CCBIAS

31 I

LBWSET 1

ASET 2

ERSET 3

PSET 4

IMPD 5

IMPDMON

GND4 7

V

4 8

CC

NOTES

1. THE EXPOSED PAD ON THE BOTTOM OF THE

PACKAGE MUST BE CONNECTED TO V

THE GND PLANE.

02745-005

PIN 1

INDICATOR

ADN2847

TOP VIEW

1 11

CC

V

ERCAP 9

PAVCAP 10

Figure 8. 32-Lead LFCSP

29 GND2

DATAN 12

28 IMODP

DATAP 13

27 GND2

26 IMODN

CLKP 15

GND1 14

2

CC

25 V

CLKN 16

Table 5. Pin Function Descriptions

Pin Number

48-Lead 32-Lead Mnemonic Description

1 N/A TP1 Test Pin. In normal operation, TP1 = GND.

2 1 LBWSET Select Low Loop Bandwidth.

3 2 ASET Alarm Current Threshold Setting Pin.

4 3 ERSET Extinction Ratio Set Pin.

5 4 PSET Average Optical Power Set Pin.

6 N/A TP2 Test Pin. In normal operation, TP2 = GND.

7 5 IMPD Monitor Photodiode Input.

8 6 IMPDMON Mirrored Current from Monitor Photodiode.

9 N/A IMPDMON2 Mirrored Current from Monitor Photodiode 2. (For use with two MPDs).

10 N/A IMPD2 Monitor Photodiode Input 2. (For use with two MPDs).

11 7 GND4 Supply Ground.

12 8 VCC4 Supply Voltage.

13 9 ERCAP Extinction Ratio Loop Capacitor.

14 10 PAVCAP Average Power Loop Capacitor.

15 N/A TP3 Test Pin. In normal operation, TP3 = GND.

16 11 VCC1 Supply Voltage.

17 N/A GND1 Supply Ground.

18 12 DATAN Data, Negative Differential Terminal.

19 13 DATAP Data, Positive Differential Terminal.

20 14 GND1 Supply Ground.

21 15 CLKP Data Clock Positive Differential Terminal. Used if CLKSEL = VCC.

22 16 CLKN Data Clock Negative Differential Terminal. Used if CLKSEL = VCC.

23 N/A TP4 Test Pin. In normal operation, TP4 = GND.

24 N/A TP5 Test Pin. In normal operation, TP5 = GND.

25 N/A TP6 Test Pin. In normal operation, TP6 = GND.

26 17 CLKSEL Clock Select. Active = VCC. Used if data is clocked into chip.

27 18 DEGRADE Degrade Alarm Output.

28 19 FAIL Fail Alarm Output.

29 20 ALS Automatic Laser Shutdown.

24 IBMON

23 IMMO N

22 GND3

3

21 V

CC

20 ALS

19 FAIL

18 DEGRADE

17 CLKSEL

OR

CC

02745-006

Rev. B | Page 7 of 16

Page 8

ADN2847 Data Sheet

Pin Number

48-Lead 32-Lead Mnemonic Description

30 21 VCC3 Supply Voltage.

31 22 GND3 Supply Ground.

32 23 IMMON Modulation Current Mirror Output.

33 24 IBMON Bias Current Mirror Output.

34 N/A GND2 Supply Ground.

35 N/A IDTONE IDTONE. Requires external current sink to ground.

36 N/A GND2 Supply Ground.

37 N/A GND2 Supply Ground.

38 25 VCC2 Supply Voltage.

39 26 IMODN Modulation Current Negative Output. Connect via a matching resistor to VCC.

40 N/A IMODN Modulation Current Negative Output. Connect via a matching resistor to VCC.

41 27 GND2 Supply Ground.

42 28 IMODP Modulation Current Positive Output. Connect to laser diode.

43 N/A IMODP Modulation Current Positive Output. Connect to laser diode.

44 29 GND2 Supply Ground.

45 30 GND2 Supply Ground.

46 31 I

47 N/A I

48 32 CCBIAS

EP EP EPAD

Laser Diode Bias Current.

BIAS

Laser Diode Bias Current.

BIAS

Extra Laser Diode Bias. (Connected to Vcc when dc-coupled to laser diode. Connected to I

when ac-coupled to laser diode).

Exposed Pad. The exposed pad on the bottom of the package must be connected to V

the GND plane.

BIAS

or

CC

Rev. B | Page 8 of 16

Page 9

Data Sheet ADN2847

=

THEORY OF OPERATION

Laser diodes have current-in to light-out transfer functions, as

shown in Figure 9. Two key characteristics of this transfer

function are the threshold current, I

, and the slope in the

TH

linear region beyond the threshold current, referred to as slope

efficiency (LI).

P1

ER =

P0

P1 + P0

=

P

AV

P1

P

AV

OPTICAL P OWER

P0

Figure 9. Laser Transfer Function

2

∆P

∆P

LI =

CURRENT

∆I

02745-009

∆I

I

TH

CONTROL

A monitor photodiode (MPD) is required to control the LD. The

MPD current is fed into the ADN2847 to control the power and

extinction ratio, continuously adjusting the bias current and

modulation current in response to the changing threshold

current and light-to-current slope efficiency of the laser.

The ADN2847 uses automatic power control (APC) to maintain

a constant average power over time and temperature.

The ADN2847 uses closed-loop extinction ratio control to allow

optimum setting of the extinction ratio for every device. Thus,

SONET/SDH interface standards can be met over device variation,

temperature, and laser aging. Closed-loop modulation control

eliminates the need to either overmodulate the LD or include

external components for temperature compensation. This

reduces research and development time and second sourcing

issues caused by characterizing LDs.

Average power and extinction ratio are set using the PSET pin

and the ERSET pin, respectively. Potentiometers are connected

between these pins and ground. The potentiometer R

to change the average power. The potentiometer R

to adjust the extinction ratio. Both PSET and ERSET are kept

1.2 V above GND.

The R

PSET

and R

potentiometers can be calculated using the

ERSET

following formulas:

V2.1

R =

PSET

R

=

ERSET

()

I

AV

V2.1

I

_

CWMPD

×

P

CW

ER

ER

1

−

1

+

()

P

×

AV

ERSET

is used

PSET

is used

where:

I

is the average MPD current.

AV

P

is the dc optical power specified on the laser data sheet.

CW

I

is the MPD current at that specified PCW.

MPD_CW

P

is the average power required.

AV

ER is the desired extinction ratio (ER = P1/P0).

Note that I

ERSET

and I

changes from device to device; however,

PSET

the control loops determines actual values. It is not required to

know exact values for LI or MPD optical coupling.

LOOP BANDWIDTH SELECTION

For continuous operation, the user should hardwire the LBWSET

pin high and use 1 F capacitors to set the actual loop bandwidth.

These capacitors are placed between the PAVCAP pin and the

ERCAP pin and ground. It is important that these capacitors are

low leakage multilayer ceramics with an insulation resistance

greater than 100 G or a time constant of 1000 seconds,

whichever is less.

Table 6.

Operation

Mode LBWSET

Continuous

High 1 μF 1 μF

Recommended

PAVCAP

Recommended

ERCAP

50 Mbps to

3.3 Gbps

Optimized for

Low 22 nF 22 nF

2.5 Gbps to

3.3 Gbps

Setting LBSET low and using 22 nF capacitors results in a

shorter loop time constant (a 10× reduction over using 1 F

capacitors and keeping LBWSET high.)

ALARMS

The ADN2847 is designed to allow interface compliance to

ITUT-G958 (11/94) section 10.3.1.1.2 (transmitter fail) and

section 10.3.1.1.3 (transmitter degrade). The ADN2847 has two

active high alarms, DEGRADE and FAIL. A resistor between

ground and the ASET pin is used to set the current at which

these alarms are raised. The current through the ASET resistor

is a ratio of 100:1 to the FAIL alarm threshold. The DEGRADE

alarm is raised at 90% of this level.

Example:

II

DEGRADEFAIL

I

R

ASET

ASET

I

FAIL

100

I

ASET

mA50

100

V2.1

2.1

A500

where the smallest valid value for

corresponds to the I

maximum of 100 mA.

BIAS

mA45somA50 =

A500

===

k4.2

===

R

is 1.2 k, because this

ASET

Rev. B | Page 9 of 16

Page 10

ADN2847 Data Sheet

The laser degrade alarm, DEGRADE, is provided to give a

warning of imminent laser failure if the laser diode degrades

further or environmental conditions continue to stress the LD,

such as increasing temperature.

The laser fail alarm, FAIL, is activated when the transmitter can

no longer be guaranteed to be SONET/SDH compliant. This

occurs when one of the following conditions arises:

• The ASET threshold is reached.

• The ALS pin is set high. This shuts off the modulation and

bias currents to the LD, resulting in the MPD current

dropping to zero. This gives closed-loop feedback to the

system that ALS has been enabled.

DEGRADE is raised only when the bias current exceeds 90% of

ASET current.

MONITOR CURRENTS

IBMON, IMMON, IMPDMON, and IMPDMON2 are current

controlled current sources from V

. They mirror the bias,

CC

modulation, and MPD current for increased monitoring

functionality. An external resistor to GND gives a voltage

proportional to the current monitored.

If the monitoring functions IMPDMON and IMPDMON2 are

not required, the IMPD pin and the IMPD2 pin must be

grounded and the monitor photodiode output must be

connected directly to the PSET pin.

DUAL MPD DWDM FUNCTION (48-LEAD LFCSP ONLY)

The ADN2847 has circuitry for a second monitor photodiode,

MPD2. The second photodiode current is mirrored to

IMPDMON2 for wavelength control purposes and is summed

internally with the first monitor photodiode current for the

power control loop. For single MPD circuits, the MPD2 pin is

tied to GND.

This enables the system designer to use the two currents to

control the wavelength of the laser diode using various optical

filtering techniques inside the laser module.

If the monitor current functions IMPDMON and IMPDMON2

are not required, then the IMPD pin and IMPD2 pin can be

grounded and the monitor photodiode output can be connected

directly to PSET.

IDTONE (48-LEAD LFCSP ONLY)

The IDTONE pin is supplied for fiber identification/supervisory

channels or control purposes in WDM. This pin modulates the

optical one level over a possible range of 2% of minimum I

to 10% of maximum I

. The level of modulation is set by con-

MOD

necting an external current sink between the IDTONE pin and

ground. There is a gain of two from this pin to the I

MOD

Figure 12 shows how the AD9850/AD9851 or the AD9834 can

be used with the ADN2847 to allow fiber identification.

MOD

current.

If the ID_TONE function is not used, the IDTONE pin should

be tied to V

. Note that using IDTONE during transmission

CC

can cause optical eye degradation.

DATA AND CLOCK INPUTS

Data and clock inputs are ac-coupled (10 nF capacitors are

recommended) and terminated via a 100 internal resistor

between DATAP and DATAN, and also between the CLKP pin

and the CLKN pin. There is a high impedance circuit to set the

common-mode voltage that is designed to allow for maximum

input voltage headroom over temperature. It is necessary that ac

coupling is used to eliminate the need for matching between

common-mode voltages.

ADN2847

DATA P

DATA N

Figure 10. AC Coupling of Data Inputs

50Ω 50Ω

V

(TO FLIP-FLOPS)

REG

R

R = 2.5kΩ, DATA

R = 3kΩ, CLK

400µA TYP

02745-010

For input signals that exceed 500 mV p-p single-ended, it is

necessary to insert an attenuation circuit as shown in Figure 11.

R1

R2

NOTES

1. R

IN

IMPEDANCE OF THE ADN2847.

DATA P/CLK P

R3

DATAN/CLKN

= 100Ω = THE DI FFERENTI AL INPUT

Figure 11. Attenuation Circuit

ADN2847

R

IN

02745-011

CCBIAS

When the laser is used in ac-coupled mode, the CCBIAS pin

and the I

coupled mode, CCBIAS should be tied to V

I

BIAS

pin should be tied together (Figure 15). In dc-

BIAS

.

CC

To achieve optimum eye quality, one pull-up resistor (RZ) is

necessary, as shown in both circuits in Figure 14 and Figure 15.

The recommended resistor R

value is approximately

Z

200 Ω ~ 500 Ω.

AUTOMATIC LASER SHUTDOWN

The ADN2847 ALS allows compliance to ITU-T-G958 (11/94),

section 9.7. When ALS is logic high, both bias and modulation

currents are turned off. Correct operation of ALS can be confirmed

if the FAIL alarm is raised when ALS is asserted. Note that this

is the only time DEGRADE is low while FAIL is high.

Rev. B | Page 10 of 16

Page 11

Data Sheet ADN2847

V

REF CLOCK

20MHz TO 180MHz

CLKIN

AD9850/AD9851

AD9834

R

CONTROLL ER

9

DDS

SET

1.25mA TO 20mA

21

20

I

12

OUT

37.5µA TO 600µA

I

OUT

50Ω

50Ω

LP FILTER

(DC-COUPLED)

Figure 12. Application Circuit to Allow Fiber Identification Using the AD9850/AD9851

ALARM INTERFACES

The FAIL and DEGRADE outputs have an internal pull-up

resistor of 30 k, used to pull the digital high value to V

.

CC

However, the alarm can be overdriven with an external resistor

allowing alarm interfacing to non-V

output levels must be below the V

levels. Non-VCC alarm

CC

used for the ADN2847.

CC

POWER CONSUMPTION

The ADN2847 die temperature must be kept below 125°C. Both

LFCSP packages have an exposed paddle that should be connected

in such a manner that is at the same potential as the ADN2847

ground pins. The θ

for both packages is specified in the

JA

Absolute Maximum Ratings section. Power consumption can be

calculated using

I

= I

CC

P = V

T

DIE

Thus, the maximum combination of I

CCMIN

× ICC + (I

CC

= T

+ 0.3 I

AMBIENT

MOD

× V

BIAS

+θJA × P

BIAS_PIN

) + I

MOD

BIAS

(V

+ I

MODP_PIN

must be

MOD

+ V

MODN_PIN

)/2

calculated, where:

I

= 50 mA (typical value of ICC provided in the

CCMIN

Specifications section)

I

= I

BIAS

T

DIE

T

AMBIENT

V

BIAS_PIN

V

MODP_PIN

V

MODN_PIN

= 0

MOD

= die temperature

= ambient temperature

= voltage at I

BIAS

pin

= average voltage at IMODP pin

= average voltage at IMODN pin

LASER DIODE INTERFACING

Many laser diodes designed for 2.5 Gbps operation are packaged

with an internal resistor to bring the effective impedance up to

25 to minimize transmission line effects. In high current

applications, the voltage drop across this resistor combined

with the laser diode forward voltage makes direct connection

between the laser and the driver impractical in a 3 V system.

10kHz TO 1MHz

1/2

AD8602

0.125mA TO 2mA

BC550

35

IDTONE

ADN2847

500Ω

BC550

AD8602

1.3kΩ

1/2

50µA TO 800µ A

1kΩ

32

IMMON

02745-012

AC coupling the driver to the laser diode removes this

headroom constraint.

Caution must be taken when choosing component values for

ac coupling (see Figure 15) to ensure that the time constants

(L/R and RC) are sufficiently long for the data rate and expected

number of consecutive identical digits (CIDs). Failure to do this

can lead to pattern dependent jitter and vertical eye closure.

For designs with low series resistance, or where external

components become impractical, the ADN2847 supports direct

connection to the laser diode (see Figure 14). In this case, care

must be taken to ensure that the voltage drop across the laser

diode does not violate the minimum compliance voltage on the

IMODP pin.

OPTICAL SUPERVISOR

The PSET and ERSET potentiometers can be replaced with a

dual-digital potentiometer, the ADN2850 (see Figure 13). The

ADN2850 provides an accurate digital control for the average

optical power and extinction ratio and ensures excellent

stability over temperature.

CC

V

V

CC

IMPD

ADN2847

Tx

Rx

CLK

CS

ADN2850

SDI

SDO

CLK

CS

DAC1

DAC2

PSET

ERSET

DATA P

DATA N

IDTONE

DATA P

IMODP

I

BIAS

DATA N

IDTONE

Figure 13. Application Using the ADN2850 a Dual 10-Bit Digital

Potentiometer with an Extremely Low Temperature Coefficient

as an Optical Supervisor

CC

V

CC

R

Z

02745-013

Rev. B | Page 11 of 16

Page 12

ADN2847 Data Sheet

MPD LD

FAI L

10nF

10nF

10nF

10nF

DEGRADE

CLKN

CLKP

DATA P

DATA N

ALS

V

CC

36

GND2

37

GND2

V

2

48

CC

IMODN

IMODN

GND2

IMODP

IMODP

GND2

GND2

I

BIAS

I

BIAS

CCBIAS

1

V

CC

10µH

LD = LASER DIODE

MPD = MONITOR PHOTODIODE

*

V

CC

*

*

*

V

CC

R

Z

V

CC

GND2

IBMON

IDTONE

ERSET

ASET

LBWSET

GND

** **

1kΩ

1.5kΩ1.5kΩ

GND3

IMMON

ADN2847

GND

PSET

25

3

CC

ALS

FAI L

V

IMPDMON2

IMPDMON

IMPD

1.5kΩ

100nF 100nF 100nF 100nF 10µF

GND

24

GND

CLKSEL

DEGRADE

IMPD2

GND4

GND

CLKN

CLKP

GND1

DATA P

DATA N

GND1

V

CC

GND

PAV C A P

ERCAP

4

CC

V

12

V

CC

1

22nF

22nF

13

VCCs SHOULD HAVE BYPAS S CAPACITORS AS

CLOSE AS POS SIBLE TO T HE ACTUAL SUPPLY PI NS

ON THE ADN2847 AND THE L ASER DIODE US ED.

CONSERVATIVE DECOUPLING WOULD I NCLUDE

100pF CAPACIT ORS IN PARAL LEL WI TH 10nF

CAPACITORS.

GND

NOTES

* DESIGNATES COMPONENTS THAT NEED TO BE OPTIMIZED FOR THE TYPE OF LASER USED.

** FOR DIGITAL PROGRAMMING, THE ADN2850 OR THE ADN2860 OPTICAL SUPERVIS OR CAN BE USED.

GND

02745-014

Figure 14. DC-Coupled 3.3 Gbps Test Circuit, Data Not Clocked

Rev. B | Page 12 of 16

Page 13

Data Sheet ADN2847

MPD LD

FAI L

10nF

10nF

10nF

10nF

DEGRADE

CLKN

CLKP

DATAP

DATAN

10µF

ALS

V

CC

*

*

*

V

CC

*

1µH

LD = LASER DIODE

MPD = MONIT OR PHOTO DIODE

*

*

*

37

*

*

*

V

CC

R

Z

48

36

GND2

V

2

CC

IMODN

IMODN

GND2

IMODP

IMODP

GND2

GND2

I

BIAS

I

BIAS

CCBIAS

1

GND2

GND

V

CC

1.5kΩ

GND2

IBMON

IDTONE

ERSET

ASET

LBWSET

** **

1kΩ

1.5kΩ

GND3

IMMON

ADN2847

GND

PSET

25

3

CC

ALS

FAI L

V

IMPDMON2

IMPDMON

IMPD

1.5kΩ

100nF 100nF 100n F 100nF

DEGRADE

IMPD2

CLKSEL

GND4

GND

GND

GND

CLKN

CLKP

GND1

DATA P

DATA N

GND1

V

CC

GND

PAVCAP

ERCAP

4

CC

V

12

V

CC

1

24

GND

1µF

1µF

13

VCCs SHOULD HAVE BYPASS CAPACITORS AS

CLOSE AS POSSIBLE TO THE ACTUAL SUPPLY PINS

ON THE ADN2847 AND THE L ASER DIODE USED.

CONSERVATIV E DECOUPLING WOULD INCL UDE

100pF CAPACIT ORS IN PARAL LEL W ITH 10nF

CAPACITORS.

NOTES

* DES IGNATES CO MPONENTS THAT NEED TO BE OPTI MIZED FO R THE TYPE OF LASER US ED.

** FOR DIG ITAL PROGRAMMI NG, THE ADN2850 OR THE ADN2860 OPTICAL SUPE RVISOR CAN BE USED.

Figure 15. AC-Coupled 50 Mbps to 3.3 Gbps Test Circuit, Data Not Clocked

02745-016

Figure 16. 2.5 Gbps Optical Eye at 25°C. Average Power = 0 dBm,

Extinction Ratio = 10 dB, PRBS 31 Pattern. Eye Obtained Using a DFB Laser.

Extinction Ratio = 10 dB, PRBS 31 Pattern. Eye Obtained Using a DFB Laser.

Rev. B | Page 13 of 16

GND

02745-017

Figure 17. 2.5 Gbps Optical Eye at 85°C. Average Power = 0 dBm,

02745-015

Page 14

ADN2847 Data Sheet

C

S

C

S

OUTLINE DIMENSIONS

INDI

EATING

PLANE

PIN 1

ATO R

0.80

0.75

0.70

5.10

5.00 SQ

4.90

0.05 MAX

0.02 NOM

0.20 REF

0.50

BSC

0.50

0.40

0.30

COPLANARIT Y

0.08

0.30

0.25

0.18

25

N

1

P

32

24

EXPOSED

PAD

17

BOTTOM VIEWTOP VIEW

1

8

916

FOR PROP ER CONNECTI ON OF

THE EXPOSED PAD, REFER TO

THE PIN CO NFIGURAT ION AND

FUNCTIO N DESCRIPTIONS

SECTION OF THIS DATA SHEET.

I

N

I

D

I

3.25

3.10 SQ

2.95

0.25 MIN

R

C

A

O

T

COMPLI ANT TO JEDE C STANDARDS MO- 220-WHHD.

112408-A

Figure 18. 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

5 mm × 5 mm Body, Very Very Thin Quad

(CP-32-7)

Dimensions shown in millimeters

INDI

EATING

PLANE

PIN 1

ATO R

0.80

0.75

0.70

7.00

BSC SQ

0.50

BSC

TOP VIEW

COMPLI ANT TO JE DEC STANDARDS MO -220-WKKD.

0.45

0.40

0.35

0.20 REF

Figure 19. 48-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

7 mm × 7 mm Body, Very Very Thin Quad

(CP-48-4)

Dimensions shown in millimeters

0.30

0.23

0.18

37

36

25

24

0.05 MAX

0.02 NOM

COPLANARIT Y

0.08

48

1

EXPOSED

PAD

12

BOTTOM VIEW

13

FOR PROP ER CONNECTI ON OF

THE EXPOSED PAD, REFER TO

THE PIN CO NFIGURAT ION AND

FUNCTIO N DESCRIPTIONS

SECTION OF THIS DATA SHEET.

P

N

I

5.20

5.10 SQ

5.00

0.25 MIN

N

1

I

R

O

C

I

A

T

D

112408-B

Rev. B | Page 14 of 16

Page 15

Data Sheet ADN2847

ORDERING GUIDE

Model1 Temperature Range Package Description Package Option

ADN2847ACPZ-32 −40°C to +85°C 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-32-7

ADN2847ACPZ-32-RL −40°C to +85°C 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-32-7

ADN2847ACPZ-32-RL7 −40°C to +85°C 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-32-7

ADN2847ACPZ-48 −40°C to +85°C 48-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-48-4

1

Z = RoHS Compliant Part.

Rev. B | Page 15 of 16

Page 16

ADN2847 Data Sheet

NOTES

©2003–2012 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D02745-0-3/12(B)

Rev. B | Page 16 of 16

Loading...

Loading...