Page 1

Low Voltage, High Accuracy, Triple/Quad

V

www.BDTIC.com/ADI

Voltage Microprocessor Supervisory Circuit

FEATURES

Accurate monitoring of up to four power supply voltages

5 factory-set threshold options: 1.8 V, 2.5 V, 3.0 V, 3.3 V, 5 V

Adjustable input threshold voltage = 0.62 V (1.5% accuracy)

200 ms typical reset timeout

Open-drain

Reset output stage: active low, valid to IN

Low power consumption (35 μA)

Power supply glitch immunity

Specified from −40°C to +85°C

6-lead SOT-23 package

APPLICATIONS

Telecommunications

Microprocessor systems

Desktop and notebook computers

Data storage equipment

Servers/workstations

GENERAL DESCRIPTION

The ADM6710 is a low voltage, high accuracy supervisory

circuit. The device monitors up to four system supply voltages.

The ADM6710 incorporates a variety of internally pretrimmed

u

ndervoltage threshold options for monitoring 1.8 V, 2.5 V,

3.0 V, 3.3 V and 5.0 V supply voltages. The ADM6710Q offers

three adjustable thresholds for monitoring voltages down to

0.62 V. See the

o

f all available options.

If a monitored power supply voltage falls below the minimum

v

oltage threshold, a single active low output asserts, triggering a

system reset. The output is open drain with a weak internal

pull-up to the monitored IN

RESET

output (10 μA internal pull-up)

= 1 V or IN2 = 1 V

1

Ordering Guide section for a list and description

supply (or to VCC in the case of the

2

ADM6710

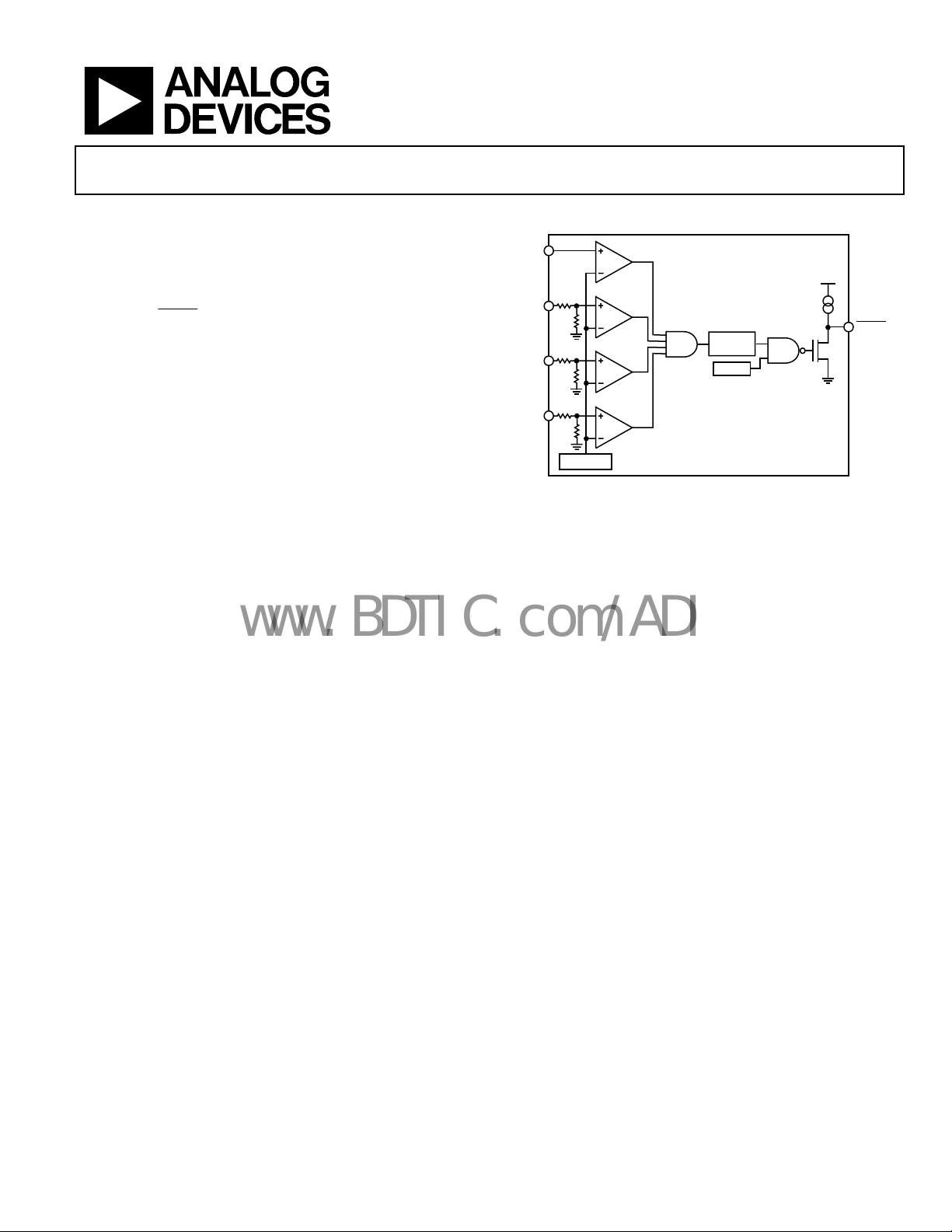

FUNCTIONAL BLOCK DIAGRAM

IN

1

IN2,

CC

IN

3

IN

4

0.62V REF

ADM6710Q) of typically 10 μA. Once all voltages rise above the

selected threshold level, the reset signal remains low for the

reset timeout period (200 ms typical).

The ADM6710 output remains valid as long as IN

exceeds 1 V, whereas for the ADM6710Q, the output remains

valid as long as V

exceeds 2 V.

CC

Unused monitored inputs should not be allowed to float or to

grounded, instead they should be connected to a supply

be

voltage greater than their specified threshold voltages.

The ADM6710 is available in a 6-lead SOT-23 package. The

de

vice operates over the extended temperature range of −40°C

to +85°C.

ADM6710

TIMEOUT

Figure 1.

200ms

UVLO

IN2, V

or IN2

1

CC

RESET

06626-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

Page 2

ADM6710

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configurations and Function Descriptions ........................... 5

REVISION HISTORY

6/07—Revision 0: Initial Version

Typical Performance Characteristics..............................................6

Theory of Operation .........................................................................8

Input Configuration......................................................................8

RESET

Output Configuration .....................................................8

Addition Of Manual Reset ...........................................................8

Outline Dimensions..........................................................................9

Ordering Guide .............................................................................9

Rev. 0 | Page 2 of 12

Page 3

ADM6710

www.BDTIC.com/ADI

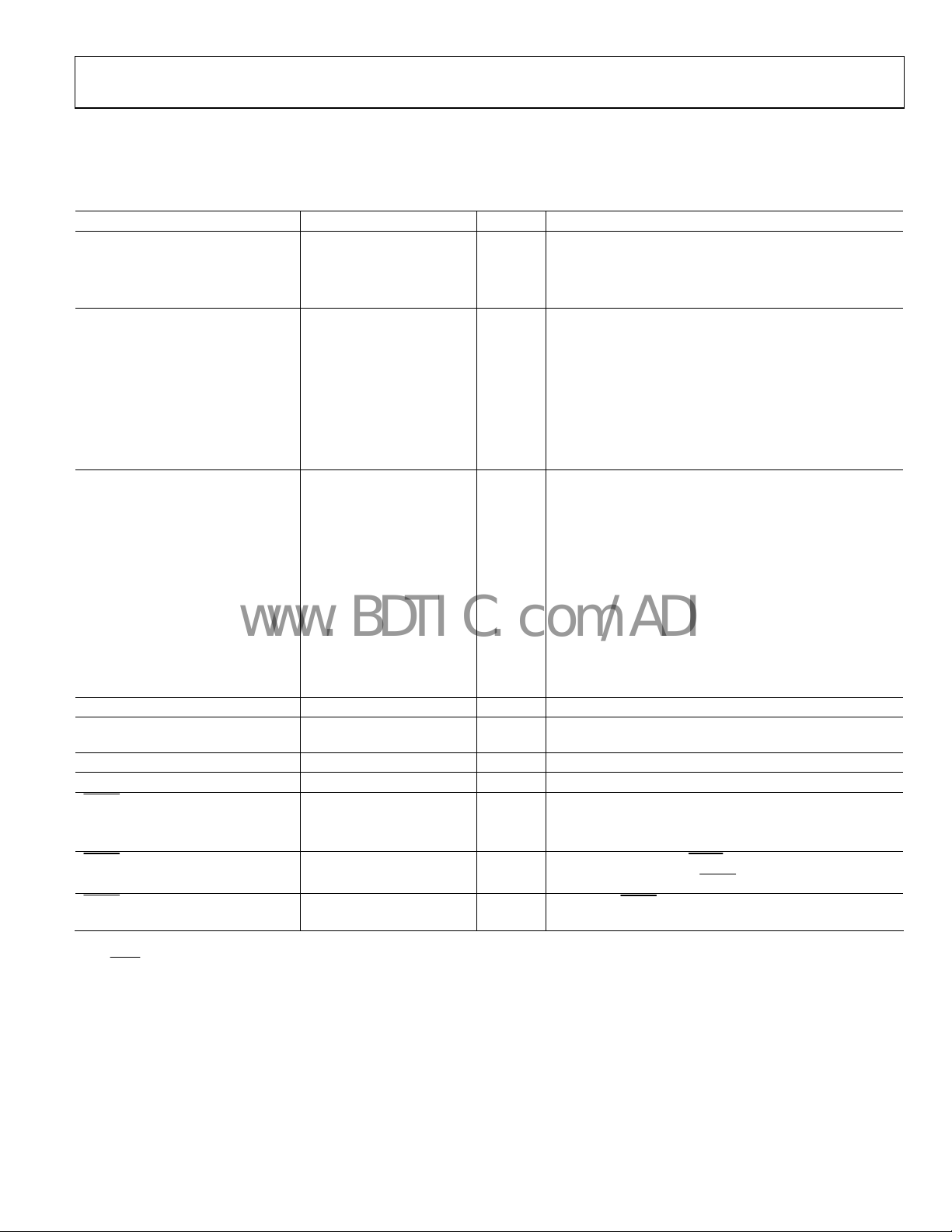

SPECIFICATIONS

V

= 1 V to 5.5 V, TA = −40°C to +85°C, unless otherwise noted. Typical values are V

IN2

Table 1.

Parameter Min Typ Max Units Test Conditions/Comments

OPERATING VOLTAGE RANGE

1

V

CC

2

V

IN2

2.0 5.5 V ADM6710Q only

1.0 5.5 V All devices except ADM6710Q; TA = 0°C to +85°C

1.2 5.5 V All devices except ADM6710Q; TA = −40°C to +85°C

INPUT CURRENT

INx Input Current

25 40 μA

IN

supplies)

55 115 μA

IN

The supply splits into 25 μA for the resistor divider and

30 μA for other circuits.

0.4 μA V

0.2 μA V

ICC Input Current

35 50 μA ADM6710Q only; VCC = 5.5 V

THRESHOLD VOLTAGE

Threshold Voltage (VTH) 4.50 4.63 4.75 V INX decreasing; 5 V (−5%)

4.25 4.38 4.50 V INX decreasing; 5 V (−10%)

3.00 3.08 3.15 V INX decreasing; 3.3 V (−5%)

2.85 2.93 3.00 V INX decreasing; 3.3 V (−10%)

2.70 2.78 2.85 V INX decreasing; 3.0 V (−5%)

2.55 2.63 2.70 V INX decreasing; 3.0 V (−10%)

2.25 2.32 2.38 V INX decreasing; 2.5 V (−5%)

2.13 2.19 2.25 V INX decreasing; 2.5 V (−10%)

1.62 1.67 1.71 V INX decreasing; 1.8 V (−5%)

1.53 1.58 1.62 V INX decreasing; 1.8 V (−10%)

Adjustable Threshold (VTH) 0.611 0.620 0.629 V INX decreasing

RESET THRESHOLD HYSTERESIS ( V

RESET THRESHOLD TEMPERATURE

COEFFICIENT (TCV

)

TH

) 0.3 %VTH INX increasing relative to INX decreasing

HYST

60 ppm/°C

INX to RESET DELAY (tRP) 30 μs VIN falling at 10 mV/μs from VTH to VTH − 50 mV

RESET TIMEOUT PERIOD (tRP) 140 200 280 ms

RESET OUTPUT LOW (VOL)

0.3 V

V

0.4 V V

RESET OUTPUT HIGH (VOH)

0.8 × V

RESET OUTPUT HIGH SOURCE

CURRENT (I

1

Note that the ADM6710Q is powered from VCC.

2

RESET

The

)

OH

output is guaranteed to be in the correct state for IN1 or IN2 down to 1 V.

0.3 V V

0.8 × V

V

CC

V

IN2

10 μA

V

V

V

= 3.0 V to 3.3 V, TA = 25°C.

IN2

= Nominal input voltage (for 1.8 V, 2.5 V and 5.0 V

X

= Nominal input voltage (for 3.0 V and 3.3 V supplies).

2

= 0 V to 0.85 V (for adjustable thresholds)

IN1

, V

= 0 V to 0.85 V (for adjustable thresholds)

IN3

IN4

, V

= 5 V, I

IN2

CC

, VCC = 2.5 V, I

IN2

= 1.0 , I

IN2

≥ 2.0 V, I

CC

≥ 2.0 V, I

IN2

≥ 2.0 V,

IN2

= 2 mA

SINK

= 1.2 mA

SINK

= 20 μA, TA = 0°C to +85°C

SINK

RESET

SOURCE

SOURCE

RESET

= 4 μA,

= 4 μA,

deasserted

deasserted (ADM6710Q only)

RESET

deasserted

Rev. 0 | Page 3 of 12

Page 4

ADM6710

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

RESET

VCC, INX,

Continuous

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature (10 sec) 300°C

Junction Temperature 135°C

Table 3. Thermal Resistance

Package Type θJA Unit

6-lead SOT-23 169.5 °C/W

to GND

RESET

Current

−0.3 V to +6 V

20 mA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 4 of 12

Page 5

ADM6710

V

www.BDTIC.com/ADI

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

IN

IN

IN

1

1

2

2

3

3

ADM6710

TOP VIEW

(Not to Scale)

6

5

4

RESET

GND

IN

4

06626-002

Figure 2. ADM6710 Pin Configuration Fig

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 IN1 Input Voltage 1.

IN2 Input Voltage 2. IN2 is the power supply input for the ADM6710. 2

V

V

CC

is the power supply input for the ADM6710Q. It is not a monitored input.

CC

3 IN3 Input Voltage 3.

4 IN4 Input Voltage 4.

5 GND Ground.

6

RESET

Active Low RESET Output. RESET goes low when an input drops below the specified threshold. Once all inputs

rise above the threshold voltage, RESET

with a weak internal pull-up to IN

IN

1

CC

IN

3

1

ADM6710Q

2

TOP VIEW

(Not to Scale)

3

6

5

4

RESET

GND

IN

4

06626-003

ure 3. ADM6710Q Pin Configuration

remains low for 200 ms (typical) before going high. RESET is open drain

or, in the case of the ADM6710Q, to VCC, typically 10 μA.

2

Rev. 0 | Page 5 of 12

Page 6

ADM6710

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

V

= VCC = 3.0V, TA = 25°C, unless otherwise noted.

IN2

60

58

56

54

52

50

48

INPUT CURRENT (µ A)

2

46

IN

44

42

40

–40 85

–15 10 35 60

TEMPERATURE (ºC)

Figure 4. IN

Input Current vs. Temperature

2

120

100

80

60

40

INPUT CURRENT (µ A)

2

IN

20

0

05

.5 11.522.533.544.55

IN2 VOLTAGE (V)

Figure 5. IN

Input Current vs. IN2 Voltage

2

VIN2 = 3.3V

2 = 3V

V

IN

06626-008

06626-009

.5

100

90

80

70

60

50

40

TRANSIENT DURATI ON (µs)

X

30

20

10

MAXIMUM IN

0

01

100 200 300 400 500 600 700 800 900

Figure 7. Maximum IN

100

90

80

70

60

50

40

RESET DELAY (µs)

30

20

10

0

01000

100 200 300 400 500 600 700 800 900

RESET

Figure 8.

Delay vs. Reset Threshold Overdrive (INx Decreasing)

RESET ASSERTED ABOVE THIS LI NE

000

RESET THRESHO LD OVERDRI VE (mV)

Transient Duration vs. Reset Threshold Overdrive

x

RESET THRESHO LD OVERDRI VE (mV)

06626-011

06626-012

0.05

0

–0.05

–0.1

–0.15

–0.2

–0.25

–0.3

NORMALIZE D THERSHOLD ERROR (%)

–0.35

–40 85

–15 10 35 60

TEMPERATURE ( ºC)

VTH = 1.8V

= 3.3V

V

IN2

06626-010

Figure 6. Normalized Threshold Error vs. Temperature

Rev. 0 | Page 6 of 12

214

212

210

208

206

RESET TIMEOUT DELAY (mS)

204

202

–40 85

–15103560

TEMPERATURE ( ºC)

Figure 9. Reset Timeout D

elay vs. Temperature

06626-013

Page 7

ADM6710

www.BDTIC.com/ADI

C3

C2

C2 DC1M

BwL C3 DC1M

–6.000V offset

Figure 10.

INx

RESET

2.00V/div

RESET

BwL Timebase 0. 0µs

1.00V/div

2.040V offset

10.0 µs/div

2.0 GS/s200kS

Pull-Up and Pull-Down Response (10 μs/div)

Trigger 0.0µs

–520mVSTOP

NEGATIVEEDGE

C3

C2

06626-014

INx

RESET

C2 DC1 M

BwL C3

2.00V/div

–6.000V offset

Figure 11.

BwL

DC1M –101ms C3Timebase

2.00V/div

2.000V offset

RESET

Timeout Delay (50 ms/div)

50.0 ms/div

1.0 MS/s500kS

Trigger DC

680mVNormal

PositiveEdge

06626-015

Rev. 0 | Page 7 of 12

Page 8

ADM6710

V

V

V

www.BDTIC.com/ADI

THEORY OF OPERATION

The ADM6710 is a compact, low power supervisory circuit

capable of monitoring up to four voltages in a multisupply

application.

The device includes several factory-set voltage threshold

ptions for monitoring 1.8 V, 2.5 V, 3.0 V, 3.3 V and 5.0 V

o

supplies. It also provides up to three adjustable thresholds for

monitoring voltages down to 0.62 V. See the

s

ection for a list and description of all available options.

The ADM6710Q has three adjustable voltage inputs and is

po

wered by V

, which is not a monitored voltage. All other

CC

ADM6710 devices are powered by IN

voltage, and therefore monitors up to four voltages. If a

monitored voltage drops below its associated threshold, the

active low reset output asserts low and remains low while either

IN

or IN2 remains above 1.0 V.

1

ADM6710

IN

1

MONITORED

SUPPLIES

IN

2

RESET

IN

3

IN

4

GND

Figure 12. Typical Applications Circuit

INPUT CONFIGURATION

The ADM6710 provides numerous monitor choices with

adjustable reset thresholds. Typically, the threshold voltage at

each adjustable IN

than 0.62 V, connect a resistor divider network to the circuit as

depicted in

INTH

The internal comparators each typically have a hysteresis of

0.3% with respect to the reset threshold. This built-in hysteresis

improves the device’s immunity to ambient noise without

noticeably reducing the threshold accuracy. The ADM6710 is

unaffected by short input transients.

The ADM6710 is powered from the monitored IN

the case of the ADM6710Q. Monitored inputs are resistant to

short power supply glitches.

tch immunity data. To increase noise immunity in noisy

gli

applications, place a 0.1 μF capacitor between the IN

input is 0.62 V. To monitor a voltage greater

x

Figure 13, where

⎛

=

⎜

62.0

VV

⎜

⎝

Figure 13. Setting the Adjustable Monitor

⎞

+

RR

21

⎟

⎟

R

2

⎠

INTH

R1

R2

V

= 0.62V

REF

Figure 7 depicts the ADM6710

Ordering Guide

, which is a monitored

2

MICROPROCESSOR

06626-004

06626-006

, or VCC in

2

input and

2

ground. Adding capacitance to IN

, IN3, and IN4 also improves

1

noise immunity.

Do not allow unused monitor inputs to float or to be grounded.

C

onnect these inputs to a supply voltage greater than their

specified threshold voltages. In the case of unused IN

adjustable

x

inputs, limit the bias current by connecting a 1 MΩ series

resistor between the unused input and IN

(or VCC in the case

2

of the ADM6710Q).

RESET OUTPUT CONFIGURATION

RESET

The

output asserts low if a monitored INx voltage drops

below its voltage threshold. Once all voltages rise above the

selected threshold level, the reset signal remains low for the

reset timeout period (200 ms typical). The reset output is open

drain with a weak internal pull-up to the monitored IN

or VCC

2

supply, typically 10 μA.

Many applications that interface with other logic devices do not

r

equire an external pull-up resistor. However, if an external

pull-up resistor is required and it is connected to a voltage

ranging from 0 V to 5.5 V, it will overdrive the internal pull-up.

Reverse current flow from the external pull-up voltage to IN

2

is

prevented by the internal circuitry.

V

RESET

5

CC

06626-005

IN2=3.3

ADM6710

Figure 14. Interface with a Different Logic Supply Voltage

100kΩ

RESET

ADDITION OF MANUAL RESET

Use the circuit shown in Figure 15 to add manual reset to any of

the ADM6710 adjustable inputs. When the switch is closed, the

ADM6710

IN

1

IN

2

RESET

IN

3

IN

4

GND

RESET

output commences.

06626-007

is an Adjustable Input)

4

analog input shorts to ground and a

The switch must remain open for a minimum of 140 ms for the

RESET

output to deassert.

V

IN4

R1

R2

Figure 15. Addition of Manual Reset (IN

Rev. 0 | Page 8 of 12

Page 9

ADM6710

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

2.90 BSC

1.90

BSC

0.50

0.30

45

2.80 BSC

2

0.95 BSC

1.45 MAX

SEATING

PLANE

0.22

0.08

10°

0.60

4°

0.45

0°

0.30

1.60 BSC

PIN 1

INDICATOR

1.30

1.15

0.90

0.15 MAX

6

1 3

COMPLIANT TO JEDEC STANDARDS MO-178-AB

Figure 16. 6-Lead Small Outline Transistor Package [SOT-23]

(RJ-6)

Dim

ensions shown in millimeters

ORDERING GUIDE

Nominal Input Voltage

Model

ADM6710AARJZ-REEL7

ADM6710BARJZ-REEL7

ADM6710CARJZ-REEL7

ADM6710DARJZ-REEL7

ADM6710EARJZ-REEL7

ADM6710FARJZ-REEL7

ADM6710GARJZ-REEL7

ADM6710HARJZ-REEL7

ADM6710IARJZ-REEL7

ADM6710JARJZ-REEL7

ADM6710KARJZ-REEL7

ADM6710LARJZ-REEL7

1

1

1

1

1

1

1

1

1

1

1

1

ADM6710MARJZ-REEL7

ADM6710NARJZ-REEL7

ADM6710OARJZ-REEL7

ADM6710PARJZ-REEL7

ADM6710QARJZ-REEL7

1

Z = RoHS Compliant Part.

2

Adjustable voltage based on 0.62 V internal threshold. The external threshold voltage can be set using an external resistor divider.

1

1

1

1

IN2 IN3 IN4

IN

1

5 3.3 2.5 Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MA9

5 3.3 2.5 Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAH

5 3.3 1.8 Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAJ

5 3.3 1.8 Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAK

Adj.23.3 2.5 1.8 10 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAX

Adj.23.3 2.5 1.8 5 −40°C to +85°C 6-Lead SOT-23 RJ-6 MA4

5 3.3 Adj.2Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAL

5 3.3 Adj.2Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAM

Adj.23.3 2.5 Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAN

Adj.23.3 2.5 Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAP

Adj.23.3 1.8 Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAQ

Adj.23.3 1.8 Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAR

1

Adj.23 2.5 Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAS

Adj.23 2.5 Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAT

Adj.23 1.8 Adj.210 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAU

Adj.23 1.8 Adj.25 −40°C to +85°C 6-Lead SOT-23 RJ-6 MAV

Adj.2VCC Adj.2Adj.2N/A −40°C to +85°C 6-Lead SOT-23 RJ-6 MAW

Supply

olerance (%)

T

Temperature

Range

Package

Description

Package

Option

Branding

Rev. 0 | Page 9 of 12

Page 10

ADM6710

www.BDTIC.com/ADI

NOTES

Rev. 0 | Page 10 of 12

Page 11

ADM6710

www.BDTIC.com/ADI

NOTES

Rev. 0 | Page 11 of 12

Page 12

ADM6710

www.BDTIC.com/ADI

NOTES

©2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06626-0-6/07(0)

Rev. 0 | Page 12 of 12

Loading...

Loading...