Page 1

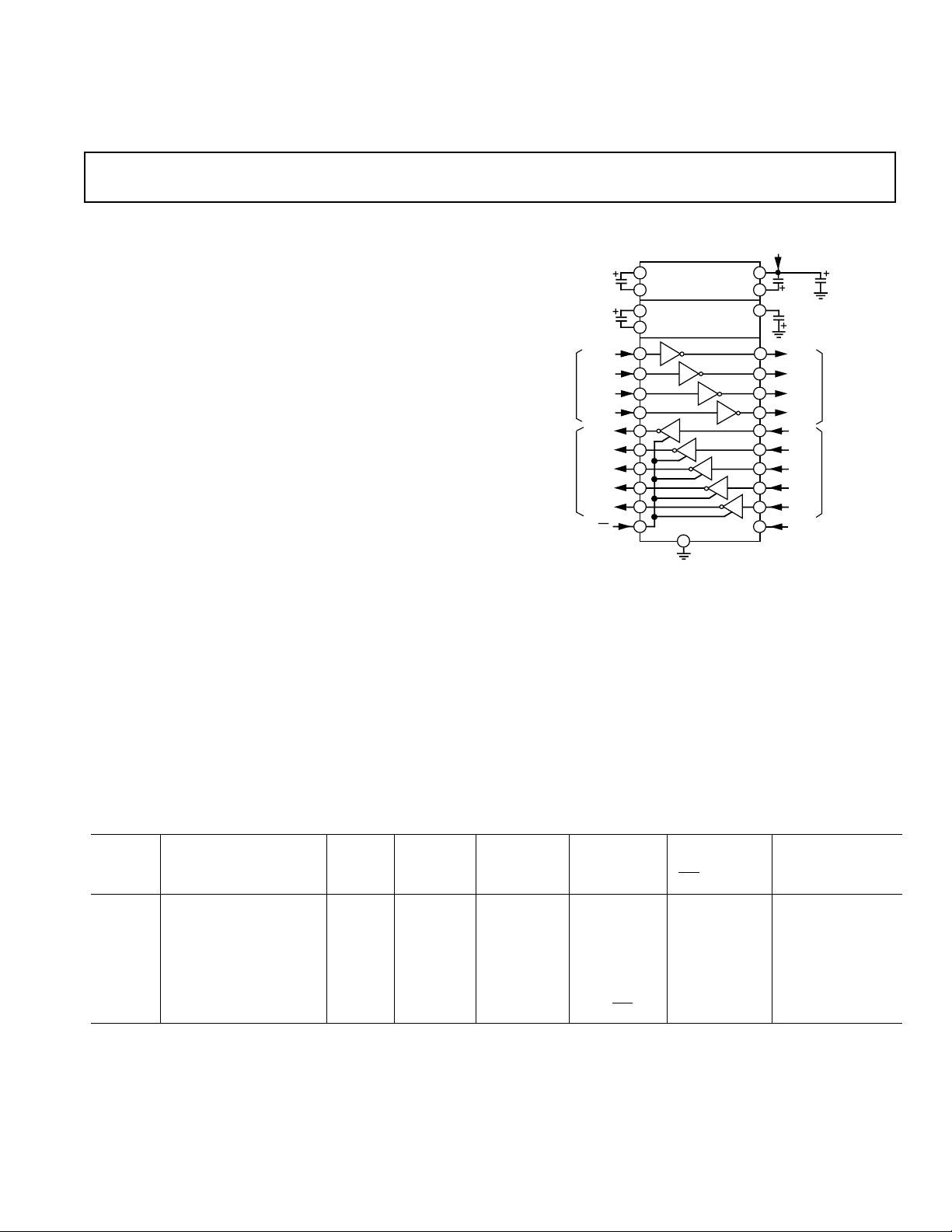

ADM211

SD

GND

10

25

RS-232

INPUTS**

*INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

T1

IN

RS-232

OUTPUTS

TTL/CMOS

INPUTS*

T1

OUT

T2

I

N

T4

I

N

T2

OUT

T4

OUT

7

6 3

2

T2

T1

+5V TO +10V

VOLTAGE

DOUBLER

+10V TO –10V

VOLTAGE

INVERTER

17

0.1µF

16V

13

0.1µF

6.3V

+5V INPUT

V

CC

V+

V–

C1+

C1–

C2+

C2–

0.1µF

16V

11

0.1µF

14

12

0.1µF

16V

16

15

T3

IN

T3

OUT

20 1T3

21

28

T4

TTL/CMOS

OUTPUTS

R3

IN

R4

IN

R3

OUT

R4

OUT

R4

R3

24

EN

27

23

22

26

R1

IN

R2

IN

R1

OUT

R2

OUT

R2

R1 9

45

8

R5

IN

R5

OUT

R5

1819

0.1 mF, +5 V Powered

a

FEATURES

0.1 mF to 10 mF Capacitors

120 kB/s Data Rate

2 Receivers Active in Shutdown (ADM213)

On-Board DC-DC Converters

69 V Output Swing with +5 V Supply

Low Power (15 mW)

Low Power Shutdown ≤5 mW

630 V Receiver Input Levels

Latch-Up FREE

Plug-In Upgrade for MAX205-211/213

APPLICATIONS

Computers

Peripherals

Modems

Printers

Instruments

CMOS RS-232 Drivers/Receivers

ADM205–ADM211/ADM213

TYPICAL OPERATING CIRCUIT

GENERAL DESCRIPTION

The ADM2xx family of line drivers/receivers is intended for all

EIA-232-E and V.28 communications interfaces, especially in

applications where ±12 V is not available. The ADM205,

ADM206, ADM211 and ADM213 feature a low power shutdown mode which reduces power dissipation to less than 5 µW

making them ideally suited for battery powered equipment. The

ADM205 does not require any external components and is particularly useful in applications where printed circuit board space

is critical. The ADM213 has an active-low shutdown and an

active-high receiver enable control. Two receivers of the

ADM213 remain active during shutdown. This feature is useful

for ring indicator monitoring.

All members of the ADM2xx family, except the ADM209, include two internal charge pump voltage converters which allow

operation from a single +5 V supply. These converters convert

the +5 V input power to the ±10 V required for RS-232 output

levels. The ADM209 is designed to operate from +5 V and

+12 V supplies. An internal +12 V to –12 V charge pump voltage converter generates the –12 V supply.

Table I. Selection Table

No. of No. of Low Power TTL No. of Receivers

Part Power RS-232 RS-232 External Shutdown Three-State Active in

Number Supply Voltage Drivers Receivers Capacitors (SD) EN Shutdown

ADM205 +5 V 5 5 None Yes Yes 0

ADM206 +5 V 4 3 4 Yes Yes 0

ADM207 +5 V 5 3 4 No No 0

ADM208 +5 V 4 4 4 No No 0

ADM209 +5 V & +9 V to +13.2 V 3 5 2 No Yes 0

ADM211 +5 V 4 5 4 Yes Yes 0

ADM213 +5 V 4 5 4 Yes (SD) Yes (EN) 2

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

© Analog Devices, Inc., 1994

Tel: 617/329-4700 Fax: 617/326-8703

Page 2

(VCC = +5 V 6 10% (206, 207, 208, 2O9,

ADM205–ADM211/ADM213–SPECIFICATIONS

V+ = +9 V to +13.2 V (ADM209); C1–C4 = 0.1 mF Ceramic. All Specifications T

MIN

to T

unless otherwise noted.)

MAX

211, 213); VCC = +5 V 6 5% (ADM205);

Parameter Min Typ Max Units Test Conditions/Comments

Output Voltage Swing ±5 ±9 Volts All Transmitter Outputs Loaded with 3 kΩ to

Ground

V

Power Supply Current 3 7 mA No Load, ADM206, ADM211, ADM213

CC

5 9 mA No Load, ADM205, ADM207, ADM208

0.4 1 mA No Load, ADM209

V+ Power Supply Current 3.5 5 mA No Load, V+ = 12 V ADM209 Only

Shutdown Supply Current 1 5 µA

Input Logic Threshold Low, V

Input Logic Threshold High, V

INL

INH

2.0 V TIN, EN, SD, EN, SD

Logic Pull-Up Current 10 25 µAT

0.8 V TIN, EN, SD, EN, SD

= 0 V

IN

RS-232 Input Voltage Range –30 +30 V

RS-232 Input Threshold Low 0.8 1.2 V

RS-232 Input Threshold High 1.7 2.4 V

RS-232 Input Hysteresis 0.2 0.5 1.0 V

RS-232 Input Resistance 357kΩ

TTL/CMOS Output Voltage Low, V

TTL/CMOS Output Voltage High, V

OL

OH

3.5 V I

TTL/CMOS Output Leakage Current 0.05 ±5 µA

0.4 V I

= 1.6 mA

OUT

= –1.0 mA

OUT

EN = V

, EN = 0 V, 0 V ≤ R

CC

OUT

≤ V

CC

Output Enable Time (TEN) 115 ns ADM205, ADM206, ADM209, ADM211

(Figure 25. C

Output Disable Time (T

) 165 ns ADM205, ADM206, ADM209, ADM211

DIS

(Figure 25. R

Propagation Delay 0.5 5 µs RS-232 to TTL

Instantaneous Slew Rate

Transition Region Slew Rate 3 6 V/µsR

l

25 30 V/µsC

= 10 pF, R

L

= 3 kΩ, C

L

= 150 pF)

L

= 1 kΩ)

L

= 3-7 kΩ, TA = +25°C

L

= 2500 pF

L

Measured from +3 V to –3 V or –3 V to +3 V

Output Resistance 300 Ω V

= V+ = V– = 0 V, V

CC

OUT

= ±2 V

RS-232 Output Short Circuit Current ±12 ±60 mA

NOTE

1

Sample tested to ensure compliance.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS*

(T

= +25°C unless otherwise noted)

A

V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

CC

V+ . . . . . . . . . . . . . . . . . . . . . . . . . . . . (V

– 0.3 V) to +14 V

CC

V– . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –14 V

Input Voltages

T

. . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to (VCC + 0.3 V)

IN

R

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±30 V

IN

Output Voltages

T

. . . . . . . . . . . . . . . . . . . (V+, + 0.3 V) to (V–, –0.3 V)

OUT

R

. . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to (VCC + 0.3 V)

OUT

Short Circuit Duration

T

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Continuous

OUT

Power Dissipation

N-24 DIP (Derate 13.5 mW/°C above +70°C) . . . 1000 mW

N-24A DIP (Derate 13.5 mW/°C above +70°C) . . 500 mW

R-24 SOIC (Derate 12 mW/°C above +70°C) . . . . .850 mW

R-28 SOIC (Derate 12.5 mW/°C above +70°C) . . 900 mW

RS-28 SSOP (Derate 10 mW/°C above +70°C) . . . .900 mW

Q-24 Cerdip (Derate 12.5 mW/°C above +70°C) . 1000 mW

D-24 Ceramic (Derate 20 mW/°C above +70°C) . .1000 mW

Thermal Impedance, θ

JA

N-24 DIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120°C/W

N-24A DIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110°C/W

R-24 SOIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85°C/W

R-28 SOIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80°C/W

RS-28 SSOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100°C/W

Q-14 Cerdip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105°C/W

Q-16 Cerdip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100°C/W

Q-20 Cerdip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100°C/W

Q-24 Cerdip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55°C/W

D-24 Ceramic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50°C/W

Operating Temperature Range

Industrial (A Version) . . . . . . . . . . . . . . . . . -40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . .–65°C to +150°C

Lead Temperature, Soldering . . . . . . . . . . . . . . . . . . . +300°C

Vapour Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

ESD Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . > 2000 V

*This is a stress rating only and functional operation of the device at these or any

other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended

periods of time may affect reliability.

–2–

REV. 0

Page 3

ADM205–ADM211/ADM213

ADM205

0.1µF

T1

IN

SD

RS-232

OUTPUTS

TTL/CMOS

INPUTS

*

T1

OUT

GND

11

T2

IN

T3

IN

T4

IN

T5

IN

T2

OUT

T3

OUT

T4

OUT

T5

OUT

T3

22

16

7

8

15

21

19

4

2

3

1

T4

T2

T1

T5

RS-232

INPUTS

**

TTL/CMOS

OUTPUTS

R1

OUT

R1

IN

R2

IN

R3

IN

R4

IN

R5

IN

R2

OUT

R3

OUT

R4

OUT

R5

OUT

R1

R5

R4

R3

R2

20

*

INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

EN

13

5

24

10

18

14

17

6

9

23

12

+5V INPUT

V

CC

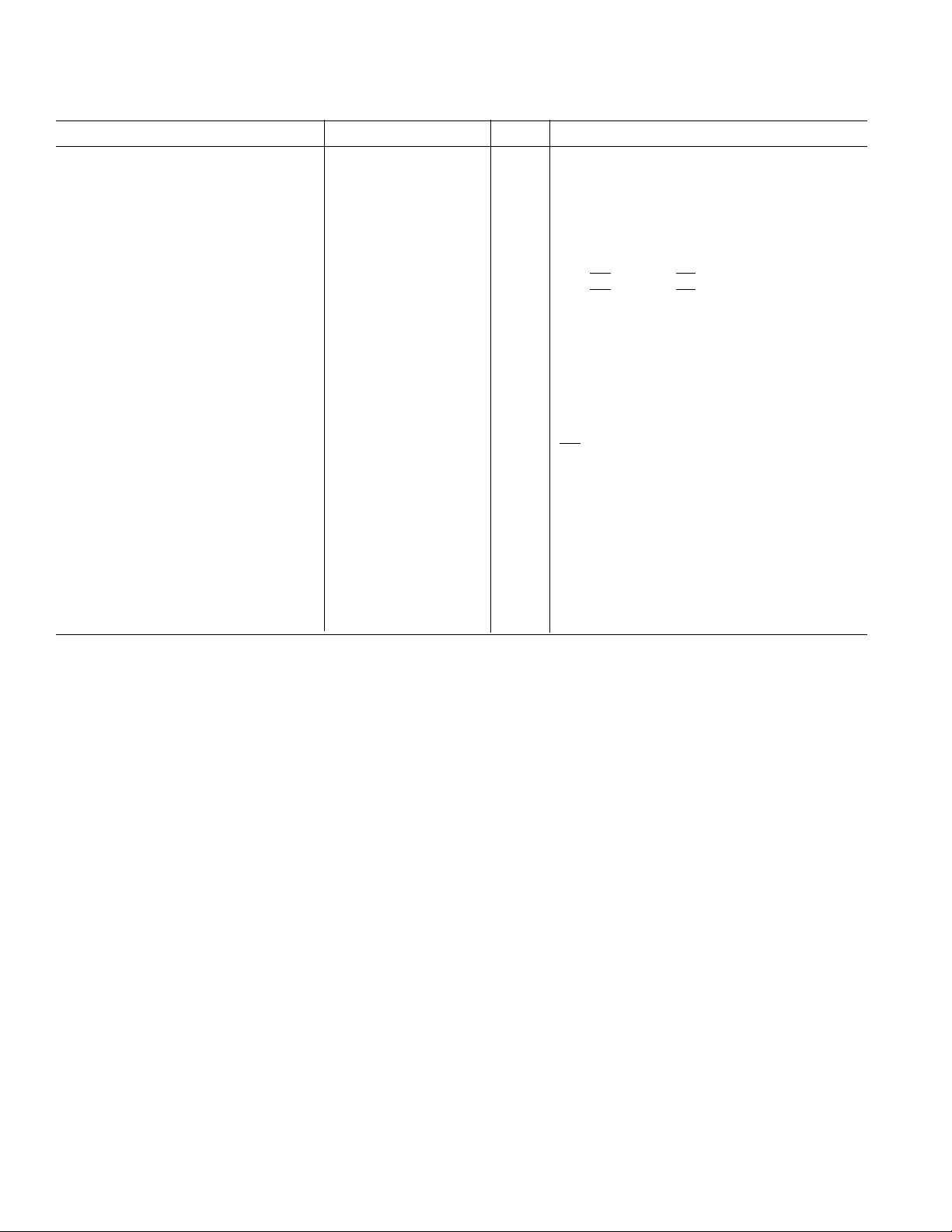

ORDERING GUIDE

Temperature Package Temperature Package Temperature Package

Model Range Option* Model Range Option* Model Range Option*

ADM205 ADM206 ADM207

ADM205AN –40°C to +85°C N-24A ADM206AN –40°C to +85°C N-24 ADM207AN –40°C to +85°C N-24

ADM206AR –40°C to +85°C R-24 ADM207AR –40°C to +85°C R-24

ADM206ARS –40°C to +85°C RS-24 ADM207ARS –40°C to +85°C RS-24

ADM208 ADM209 ADM211

ADM208AN –40°C to +85°C N-24 ADM209AN –40°C to +85°C N-24 ADM211AR –40°C to +85°C R-28

ADM208AR –40°C to +85°C R-24 ADM209AR –40°C to +85°C R-24 ADM211ARS –40°C to +85°C RS-28

ADM208ARS –40°C to +85°C RS-24 ADM209ARS –40°C to +85°C RS-24

ADM213

ADM213AR –40°C to +85°C R-28

ADM213ARS –40°C to +85°C RS-28

*N = Plastic DIP; R = Small Outline IC (SOIC); RS = Small Shrink Outline Package (SSOP).

1

T4

OUT

2

T3

OUT

3

T1

OUT

4

T2

OUT

5

R2

IN

6

IN

7

8

9

10

11

12

ADM205

Top View

(Not to Scale)

R2

OUT

T2

IN

T1

IN

R1

OUT

R1

GND

V

CC

Figure 1. ADM205 DIP Pin Configuration

24

R3

IN

23

R3

OUT

22

T5

IN

21

SD

20

EN

19

T5

OUT

18

R4

IN

17

R4

OUT

16

T4

IN

15

T3

IN

14

R5

OUT

13

R5

IN

Figure 2. ADM205 Typical Operating Circuit

REV. 0

–3–

Page 4

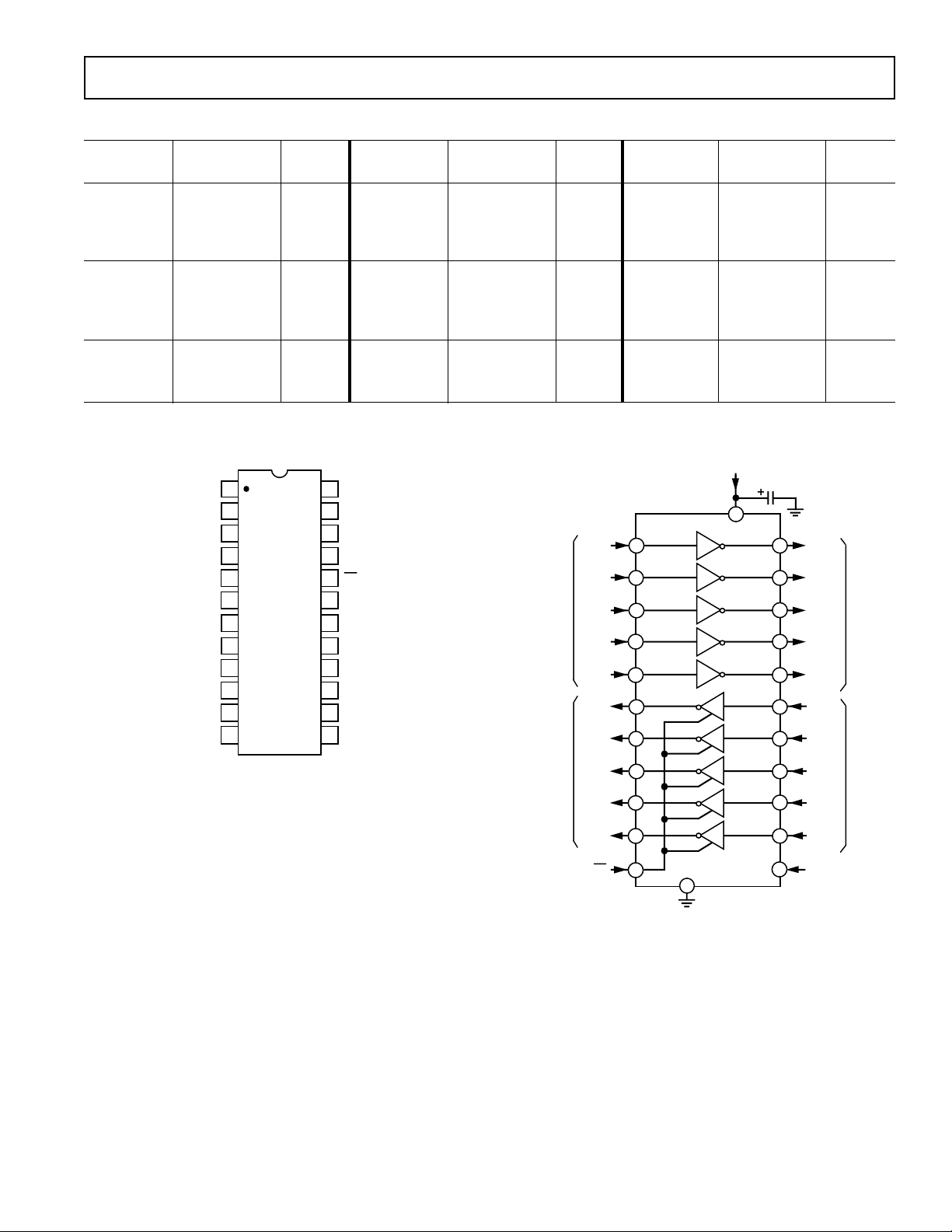

ADM205–ADM211/ADM213

1

2

3

7

24

23

22

18

8

9

10

17

16

15

11

12

14

13

4

5

21

20

619

Top View

(Not to Scale)

ADM207

T1

IN

T2

IN

T1

OUT

T2

OUT

T3

OUT

V

CC

GND

R3

IN

R1

IN

R2

IN

R2

OUT

R1

OUT

R3

OUT

T3

IN

T4

IN

T4

OUT

V+

V–C1+

C1– C2+

C2–

T5

IN

T5

OUT

T1

IN

ADM207

RS-232

OUTPUTS

TTL/CMOS

INPUTS*

T1

OUT

GND

8

T2

IN

T3

IN

T4

IN

T2

OUT

T3

OUT

T4

OUT

T3

19

6

7

18

3

1

2

24

T4

T2

T1

RS-232

INPUTS**

TTL/CMOS

OUTPUTS

R1

IN

R2

IN

R3

IN

R1

OUT

R2

OUT

R3

OUT

R3

R2

R1

*INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

16

4

23

17

22

5

+5V TO +10V

VOLTAGE

DOUBLER

+10V TO –10V

VOLTAGE

INVERTER

14

13

12

10

15

0.1µF

16V

11

0.1µF

6.3V

+5V INPUT

V

CC

V+

V–

C1+

C1–

C2+

C2–

0.1µF

6.3V

0.1µF

16V

T5

IN

T5

OUT

21

20

T5

9

0.1µF

1

T3

OUT

2

T1

OUT

3

T2

OUT

4

R1

IN

5

R1

OUT

T2

6

7

8

9

10

11

12

ADM206

Top View

(Not to Scale)

T1

GND

V

C1+

C1–

IN

IN

CC

V+

24

T4

OUT

23

R2

IN

22

R2

OUT

21

SD

20

EN

19

T4

IN

T3

18

IN

17

R3

OUT

16

R3

IN

15

V–

14

C2–

C2+

13

Figure 3. ADM206 DIP/SOIC/SSOP Pin Configuration

+5V INPUT

0.1µF

6.3V

10

C1+

+5V TO +10V

C1–

VOLTAGE

DOUBLER

12

9

V

CC

V+

0.1µF

6.3V

11

0.1µF

Figure 5. ADM207 DIP/SOIC/SSOP Pin Configuration

C2+

TTL/CMOS

INPUTS

TTL/CMOS

OUTPUTS

*

0.1µF

16V

R1

R2

R3

T1

T2

T3

T4

IN

IN

IN

IN

OUT

OUT

OUT

EN

13

14

18

19

22

17

20

7

6

5

C2–

+10V TO –10V

VOLTAGE

INVERTER

T1

T2

T3

T4

GND

8

*

INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

Figure 4. ADM206 Typical Operating Circuit

R1

R2

R3

ADM206

V–

15

2

3

1

24

4

23

16

21

T1

T2

T3

T4

0.1µF

16V

R1

R2

R3

SD

OUT

OUT

OUT

OUT

IN

IN

IN

RS-232

OUTPUTS

RS-232

INPUTS

**

Figure 6. ADM207 Typical Operating Circuit

–4–

REV. 0

Page 5

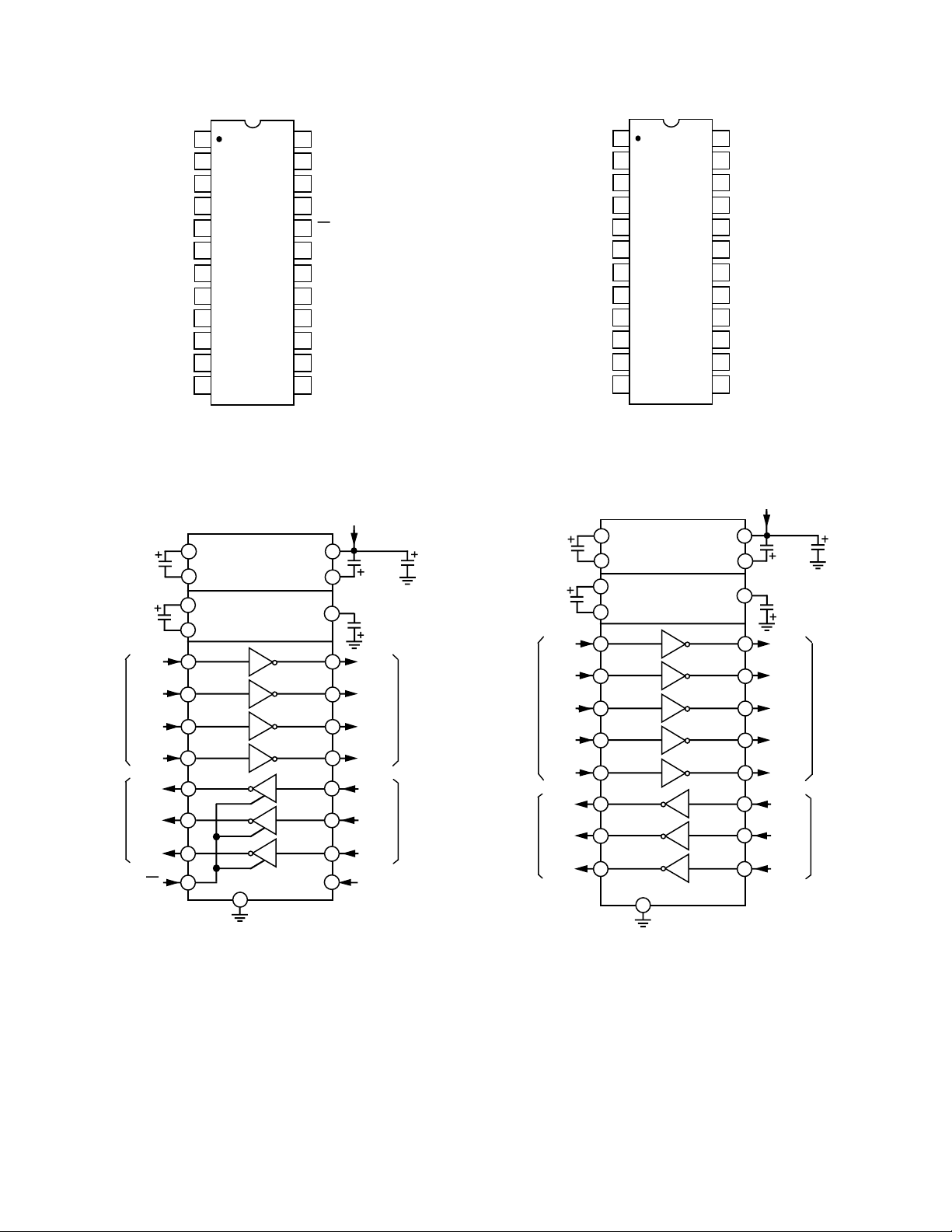

ADM205–ADM211/ADM213

1

2

3

7

24

23

22

18

8

9

10

17

16

15

11

12

14

13

4

5

21

20

619

Top View

(Not to Scale)

ADM209

R4

IN

R5

IN

R1

IN

R4

OUT

R1

OUT

V

CC

GND

T3

IN

T2

IN

R2

OUT

R5

OUT

R3

OUT

R3

IN

T1

OUT

T1

IN

V+

NC

C+

C–

T3

OUT

R2

IN

T2

OUT

V–

EN

NC = NO CONNECT

24

T3

OUT

23

R3

IN

22

R3

OUT

21

T4

IN

20

T4

OUT

19

T3

IN

T2

18

IN

17

R4

OUT

16

R4

IN

15

V–

14

C2–

C2+

13

R2

R1

T2

T1

OUT

OUT

R2

OUT

T1

OUT

R1

GND

V

C1+

C1–

IN

IN

IN

CC

V+

1

2

3

4

5

6

7

8

9

10

11

12

ADM208

Top View

(Not to Scale)

Figure 7. ADM208 DIP/SOIC/SSOP Pin Configuration

+5V INPUT

TTL/CMOS

INPUTS

TTL/CMOS

OUTPUTS

*

0.1µF

6.3V

0.1µF

16V

R1

R2

R3

R4

10

C1+

+5V TO +10V

12

C1–

C2+

13

14

T1

IN

18 1

T2

IN

T3

IN

T4

IN

OUT

OUT

22

OUT

OUT

5

21

6

4

C2–

+10V TO –10V

INVERTER

GND

8

VOLTAGE

DOUBLER

VOLTAGE

T1

T2

T319

T4

R1

R2

R3

R3 1617

ADM208

V

9

CC

V+

V–

0.1µF

6.3V

11

15

0.1µF

16V

T1

2

OUT

T2

OUT

RS-232

24

20

7

3

23

OUTPUTS

T3

OUT

T4

OUT

R1

IN

R2

IN

RS-232

INPUTS

R3

IN

R4

IN

0.1µF

Figure 9. ADM209 DIP/SOIC/SSOP Pin Configuration

+5V INPUT

0.1µF

V

4

0.1µF

16V

TTL/CMOS

INPUTS

*

R1

R2

TTL/CMOS

OUTPUTS

**

R3

R4

R5

6

7

T1

24

IN

T2

23

IN

T3

16

IN

1

OUT

22

OUT

17

OUT

11

OUT

10

OUT

14

EN

C1+

C1–

+12V TO –12V

VOLTAGE

INVERTER

T1

T2

T3

R1

R2

R3

R4

R5

GND

ADM209

3

CC

+9V TO +13.2V

5

V+

8

V–

19

20

13

2

21

18

12

9

15

0.1µF

16V

INPUT

T1

OUT

RS-232

T2

OUT

OUTPUTS

T3

OUT

R1

IN

R2

IN

RS-232

R3

IN

INPUTS

**

R4

IN

R5

IN

NC

*

INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

REV. 0

Figure 8. ADM208 Typical Operating Circuit

*

INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

Figure 10. ADM209 Typical Operating Circuit

–5–

Page 6

ADM205–ADM211/ADM213

1

2

3

7

28

27

26

22

8

9

10

21

20

19

11

12

18

17

4

5

25

24

623

Top View

(Not to Scale)

13

14

16

15

ADM213

R2

OUT

R2

IN

R5IN*

T4

IN

R3

IN

T1

OUT

T2

OUT

T3

OUT

T4

OUT

R5

OUT

*

V+

V–

V

CC

C1+

C1– C2+

C2–

GND

SD

R3

OUT

EN

T3

IN

R4IN*

R4

OUT

*

R1

IN

R1

OUT

T1

IN

T2

IN

* ACTIVE IN SHUTDOWN

ADM213

GND

10

SD

25

RS-232

INPUTS

**

TTL/CMOS

OUTPUTS

24

*

INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

** INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

*** ACTIVE IN SHUTDOWN

EN

R5

IN

***

R5

OUT

***

R5

18

19

R4

IN

***

R4

OUT

***

R4

23

22

R1

IN

R1

OUT

R1

R3

IN

R3

OUT

R3

27

26

9

R2

IN

R2

OUT

R2

4

5

8

T1

IN

RS-232

OUTPUTS

TTL/CMOS

INPUTS

*

T1

OUT

T3

IN

T3

OUT

T320

7

2

1

T1

+5V TO +10V

VOLTAGE

DOUBLER

+10V TO –10V

VOLTAGE

INVERTER

16

15

14

12

17

0.1µF

16V

13

0.1µF

6.3V

+5V INPUT

V

CC

V+

V–

C1+

C1–

C2+

C2–

0.1µF

16V

0.1µF

16V

T4

IN

T4

OUT

T4

21 28

11

0.1µF

T2

IN

T2

OUT

6

3

T2

1

T3

OUT

2

T1

OUT

3

T2

OUT

R2

4

IN

5

R2

OUT

623

T2

IN

7

T1

IN

R1

OUT

R1

GND

V

CC

C1+

V+

C1– C2+

IN

8

9

10

11

12

13

14

ADM211

Top View

(Not to Scale)

T4

28

OUT

R3

27

IN

R3

26

OUT

SD

25

24

EN

R4

IN

22

R4

OUT

21

T4

IN

T3

20

IN

R5

19

OUT

18

R5

IN

17

V–

16

C2–

15

Figure 11. ADM211 SOIC/SSOP Pin Configuration

+5V INPUT

0.1µF

16V

0.1µF

16V

12

C1+

+5V TO +10V

C1–

C2+

C2–

VOLTAGE

DOUBLER

+10V TO –10V

VOLTAGE

INVERTER

14

15

16

11

V

CC

V+

V–

0.1µF

13

6.3V

17

0.1µF

16V

0.1µF

Figure 13. ADM213 SOIC/SSOP Pin Configuration

GND

10

T1

T2

T320

T4

T1

7

IN

T2

6

TTL/CMOS

INPUTS

TTL/CMOS

OUTPUTS

IN

*

T3

IN

21 28

T4

IN

R1

R2

R3

R4

R5

*INTERNAL 400kΩ PULL-UP RESISTOR ON EACH TTL/CMOS INPUT

**INTERNAL 5kΩ PULL-DOWN RESISTOR ON EACH RS-232 INPUT

Figure 12. ADM211 Typical Operating Circuit

OUT

OUT

OUT

OUT

OUT

EN

8

5

26

22

19

24

R1

R2

R3

R4

R5

ADM211

2

3

1

9

4

27

23

18

25

T1

OUT

T2

OUT

T3

OUT

T4

OUT

R1

R2

R3

R4

R5

SD

IN

IN

IN

IN

IN

RS-232

OUTPUTS

RS-232

INPUTS

**

Figure 14. ADM213 Typical Operating Circuit

–6–

REV. 0

Page 7

Mnemonic Function

ADM205–ADM211/ADM213

PIN FUNCTION DESCRIPTION

V

CC

Power Supply Input 5 V ± 10% (+5 V ± 5% ADM205).

V+ Internally generated positive supply (+10 V nominal) on all parts except ADM209.

ADM209 requires external 9 V to 13.2 V supply.

V– Internally generated negative supply (–10 V nominal).

GND Ground pin. Must be connected to 0 V.

C+ (ADM209 only) External capacitor (+ terminal) is connected to this pin.

C– (ADM209 only) External capacitor (– terminal) is connected to this pin.

C1+ (ADM206, ADM207, ADM208, ADM211, ADM213) External capacitor (+ terminal) is connected to this pin.

C1– (ADM206, ADM207, ADM208, ADM211, ADM213) External capacitor (– terminal) is connected to this pin.

C2+ (ADM206, ADM207, ADM208, ADM211, ADM213) External capacitor (+ terminal) is connected to this pin.

C2– (ADM206, ADM207, ADM208, ADM211, ADM213) External capacitor (– terminal) is connected to this pin.

T

IN

Transmitter (Driver) Inputs. These inputs accept TTL/CMOS levels. An internal 400 kΩ pull-up resistor to Vcc is

connected on each input.

T

R

OUT

IN

Transmitter (Driver) Outputs. These are RS-232 levels (typically ±10 V).

Receiver Inputs. These inputs accept RS-232 signal levels. An internal 5 kΩ pull-down resistor to GND is con-

nected on each input.

R

OUT

Receiver Outputs. These are TTL/CMOS levels.

EN/EN Enable Input. Active low on ADM205, ADM206, ADM209, ADM211. Active high on ADM213. This input is

used to enable/disable the receiver outputs. With

abled. With

EN =High (EN = low ADM213), the outputs are placed in a high impedance state. This facility is

EN = Low (EN = High ADM213), the receiver outputs are en-

useful for connecting to microprocessor systems.

SD Shutdown Input. Active high on ADM205, ADM206, ADM211. Active low on ADM213. With SD = high on the

SD/

ADM205, ADM206, ADM211, the charge pump is disabled, the receiver outputs are placed in a high impedance

state and the driver outputs are turned off. With

SD low on the ADM213, the charge pump is disabled, the driver

outputs are turned off and all receivers except R4 and R5 are placed in a high impedance state. In shutdown, the

power consumption reduces to 5 µW.

NC No Connect. No connections are required to this pin.

Table II. ADM205, ADM206, ADM211 Truth Table

SD EN Status Transmitters T1–T5 Receivers R1–R5

0 0 Normal Operation Enabled Enabled

0 1 Normal Operation Enabled Disabled

1 0 Shutdown Disabled Disabled

Table III. ADM213 Truth Table

SD EN Status Transmitters T1-T4 Receivers R1-R3 Receivers R4, R5

0 0 Shutdown Disabled Disabled Disabled

0 1 Shutdown Disabled Disabled Enabled

1 0 Normal Operation Enabled Disabled Disabled

1 1 Normal Operation Enabled Enabled Enabled

REV. 0

–7–

Page 8

12

0

8

2

0

6

4

8

10

642

T

OUT

– V

T

OUT

HIGH

T

OUT

LOW

I

OUT

– mA

ADM205–ADM211/ADM213–Typical Performance Characteristics

10

— mA

V+

| V– |

302010

8

6

— Volts

OUT

V

4

2

0

0

I

OUT

Figure 15. Charge Pump V+, V– vs. Current

18

16

14

12

10

SLEW RATE – V/µs

8

10

V

(1 O/P LOADED)

8

– V

OUT

V

6

40

4

3.0

Figure 17. Transmitter Output Voltage vs. V

OUT

4.0

V

(ALL O/Ps LOADED)

OUT

V

– V

CC

5.0

CC

6

4

0

CAPACITIVE LOAD – pF

200015001000500

Figure 16. Transmitter Slew Rate vs. Load Capacitance

300

200

100

V+, V– IMPEDANCE – Ω

0

Figure 19. Charge Pump Impedance vs. V

2500

Figure 18. Transmitter Output Voltage vs. Current

V– (UNLOADED)

V– (LOADED)

V+ (UNLOADED)

V+ (LOADED)

3

4

V

– V

CC

5

CC

–8–

REV. 0

Page 9

0.8 VA3

S1 S3

V+ = 2V

CC

S2 S4

INTERNAL

OSCILLATOR

C1 C3

V

CC

GND

V

CC

S1 S3

S2 S4

INTERNAL

OSCILLATOR

C2 C4

V– = – (V+)

GND

V+

GND

FROM

VOLTAGE

DOUBLER

100

90

10

0%

B

5

5V

w

5V

L

1Ms

H

O

Figure 20. Charge Pump, V+, V– Exiting Shutdown

0.8 VA3

100

90

10

0%

B

5

5V

w

L

H

5µs

O

Figure 21. Transmitter Output Loaded Slew Rate

0.8 VA3

100

90

ADM205–ADM211/ADM213

The ADM205, ADM206, ADM211, and ADM213 are particularly useful in battery powered systems as they feature a low

power shutdown mode which reduces power dissipation to less

than 5 µW.

The ADM205 is designed for applications where space saving is

important as the charge pump capacitors are molded into the

package.

The ADM209 includes only a negative charge pump converter

and are intended for applications where a positive 12 V is available.

To facilitate sharing a common line or for connection to a microprocessor data bus the ADM205, ADM206, ADM209,

ADM211 and ADM213 feature an enable (

disabled, the receiver outputs are placed in a high impedance

state.

CIRCUIT DESCRIPTION

The internal circuitry in the ADM205-ADM211 and ADM213

consists of three main sections. These are:

(a) A charge pump voltage converter

(b) RS-232 to TTL/CMOS receivers

(c) TTL/CMOS to RS-232 transmitters

Charge Pump DC-DC Voltage Converter

The charge pump voltage converter consists of an oscillator and

a switching matrix. The converter generates a ± 10 V supply

from the input 5 V level. This is done in two stages using a

switched capacitor technique as illustrated in Figures 23 and 24.

First, the 5 V input supply is doubled to 10 V using capacitor

C1 as the charge storage element. The 10 V level is then inverted to generate –10 V using C2 as the storage element.

EN) function. When

10

0%

B

5

5V

w

L

H

1µs

O

Figure 22. Transmitter Output Unloaded Slew Rate

GENERAL INFORMATION

The ADM205-ADM211 and ADM213 family of RS-232 drivers/receivers are designed to solve interface problems by meeting

the EIA-232-E specifications while using a single digital +5 V

supply. The EIA-232-E standard requires transmitters which

will deliver ±5 V minimum on the transmission channel and receivers which can accept signal levels down to ± 3 V. The

ADM205-ADM211 and ADM213 meet these requirements by

integrating step up voltage converters and level shifting transmitters and receivers onto the same chip. CMOS technology is

used to keep the power dissipation to an absolute minimum. A

comprehensive range of transmitter/receiver combinations is

available to cover most communications needs. The ADM205–

ADM211 and ADM213 are modifications, enhancements and

improvements to the AD230–AD241 family and derivatives

thereof. They are essentially plug-in compatible and do not have

materially different applications.

Figure 23. Charge-Pump Voltage Doubler

Figure 24. Charge-Pump Voltage Inverter

Capacitors C3 and C4 are used to reduce the output ripple.

Their values are not critical and can be reduced if higher levels

of ripple are acceptable. The charge pump capacitors C1 and

C2 may also be reduced at the expense of higher output impedance on the V+ and V– supplies.

The V+ and V– supplies may also be used to power external circuitry if the current requirements are small.

REV. 0

–9–

Page 10

ADM205–ADM211/ADM213

T

EN

T

DIS

3V

0V

R

OUT

3.5V

0.8V

V

OH

– 0.1V

V

VOL

+ 0.1V

EN

*

* POLARITY OF EN IS REVERSED FOR ADM213

Transmitter (Driver) Section

The drivers convert TTL/CMOS input levels into EIA-232-E

output levels. With V

= +5 V and driving a typical EIA-232-E

CC

load, the output voltage swing is ±9 V. Even under worst case

conditions the drivers are guaranteed to meet the ±5 V EIA-232-E

minimum requirement.

The input threshold levels are both TTL and CMOS compatible with the switching threshold set at V

V

= 5 V the switching threshold is 1.25 V typical. Unused in-

CC

/4. With a nominal

CC

puts may be left unconnected, as an internal 400 kΩ pull-up resistor pulls them high forcing the outputs into a low state.

As required by the EIA-232-E standard, the slew rate is limited

to less than 30 V/µs without the need for an external slew limit-

ing capacitor and the output impedance in the power-off state is

greater than 300 Ω.

Receiver Section

The receivers are inverting level shifters which accept EIA-232-E

input levels (±5 V to ±15 V) and translate them into 5 V TTL/

CMOS levels. The inputs have internal 5 kΩ pull-down resistors

to ground and are also protected against overvoltages of up to

±30 V. The guaranteed switching thresholds are 0.8 V minimum and 2.4 V maximum which are well within the ± 3 V

EIA-232-E requirement. The low level threshold is deliberately

positive as it ensures that an unconnected input will be interpreted as a low level.

The receivers have Schmitt trigger inputs with a hysteresis level

of 0.5 V. This ensures error-free reception for both noisy inputs

and for inputs with slow transition times.

Shutdown (SD)

The ADM205, ADM206, ADM211 and ADM213 feature a

control input which may be used to disable the part and reduce

the power consumption to less than 5 µW. This is very useful in

battery operated systems. During shutdown the charge pump is

turned off, the transmitters are disabled and all receivers except

R4 and R5 on the ADM213 are put into a high-impedance disabled state. Receivers R4 and R5 on the ADM213 remain enabled during shutdown. This feature allows monitoring external

activity such as ring indicator monitoring while the device is in a

low power shutdown mode. The shutdown control input is active high on all parts except the ADM213 where it is active low.

Refer to Tables II and III.

Enable Input

The ADM205, ADM209, ADM211, and ADM213 feature an

enable input used to enable or disable the receiver outputs. The

enable input is active low on the ADM205, ADM209, ADM211

and active-high on the ADM213. Refer to Tables II and III.

When disabled, all receiver outputs are placed in a high impedance state. This function allows the outputs to be connected directly to a microprocessor data bus. It can also be used to allow

receivers from different devices to share a common data line.

The timing diagram for the enable function is shown in Figure

25.

Figure 25. Enable Timing

APPLICATION HINTS

Driving Long Cables

In accordance with the EIA-232-E standard, long cables are

permissible provided that the total load capacitance does not exceed 2500 pF. For longer cables which do exceed this, then it is

possible to trade off baud rate vs. cable length. Large load capacitances cause a reduction in slew rate, and hence the maximum

transmission baud rate is decreased. The ADM205–ADM211 and

ADM213 are designed so that the slew rate reduction with increasing load capacitance is minimized.

For the receivers, it is important that a high level of noise immunity be inbuilt so that slow rise and fall times do not cause multiple output transitions as the signal passes slowly through the

transition region. The ADM205–ADM211 and ADM213 have

0.5 V of hysteresis to guard against this. This ensures that, even

in noisy environments, error-free reception can be achieved.

High Baud Rate Operation

The ADM205–ADM211 and ADM213 feature high slew rates

permitting data transmission at rates well in excess of the

EIA-232-E specification. The drivers maintain ± 5 V signal

levels at data rates up to 120-kB/s under worst-case loading

conditions.

–10–

REV. 0

Page 11

OUTLINE DIMENSIONS

0.013 (0.32)

0.009 (0.23)

0.042 (1.067)

0.018 (0.447)

6

°

0

°

0.03 (0.76)

0.02 (0.51)

PIN 1

0.299 (7.6)

0.291 (7.39)

0.414 (10.52)

0.398 (10.10)

13

12

1

24

1. LEAD NO. 1 IDENTIFIED BY A DOT.

2. SOIC LEADS WILL BE EITHER TIN PLATED OR SOLDER DIPPED

IN ACCORDANCE WITH MIL-M-38510 REQUIREMENTS

0.019 (0.49)

0.014 (0.35)

0.05 (1.27)

BSC

0.096 (2.44)

0.089 (2.26)

0.608 (15.45)

0.596 (15.13)

0.01 (0.254)

0.006 (0.15)

Dimensions shown in inches and (mm).

ADM205–ADM211/ADM213

24-Lead Plastic DIP (N-24)

0.07 (1.78)

0.05 (1.27)

13

12

(6.61 ± 0.03)

0.130 (3.30)

0.128 (3.25)

SEATING

PLANE

24

PIN 1 0.260 ± 0.001

1

1.228 (31.19)

1.226 (31.14)

0.02 (0.5)

0.016 (0.41)

0.11 (2.79)

0.09 (2.28)

NOTES

1. LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH

2. PLASTIC LEADS WILL BE EITHER SOLDER DIPPED OR TIN PLATED

IN ACCORDANCE WITH MIL-M-38510 REQUIREMENTS.

24-Lead Plastic DIP (N-24A)

0.065 (1.66)

0.045 (1.15)

13

12

0.55 (13.97)

0.53 (13.47)

0.16 (4.07)

0.14 (3.56)

SEATING

PLANE

PIN 1

0.2

(5.08)

MAX

0.175 (4.45)

0.12 (3.05)

24

1

0.02 (0.508)

0.015 (0.381)

1.25 (31.75)

1.24 (31.5)

0.105 (2.67)

0.095 (2.42)

0.32 (8.128)

0.30 (7.62)

15

°

0

0.606 (15.4)

0.594 (15.09)

15

°

0

°

0.011 (0.28)

0.009 (0.23)

0.012 (0.305)

0.008 (0.203)

0.225

(5.715)

MAX

(3.175)

PIN 1

0.125

MIN

24-Lead Cerdip (Q-24)

13

TYP

13

0.295 (7.493)

MAX

12

12

0.070 (1.778)

0.020 (0.508)

SEATING

PLANE

24

24

1

1

1.290 (32.77) MAX

0.021 (0.533)

0.015 (0.381)

0.110 (2.794)

0.090 (2.286)

TYP

1. LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH.

2. CERDIP LEADS WILL BE EITHER TIN PLATED OR SOLDER DIPPED

IN ACCORDANCE WITH MIL-M-38510 REQUIREMENTS.

TYP

0.065 (1.651)

0.055 (1.397)

28-Lead SOIC (R-28)

0.180

(4.572)

MAX

0.320 (8.128)

0.290 (7.366)

15

°

0

°

0.012 (0.305)

0.008 (0.203)

TYP

REV. 0

PIN 1

0.008 (0.203)

0.002 (0.050)

28-Lead SSOP (RS-28)

24

1

0.328 (8.33)

0.318 (8.08)

0.0256 (0.65)

BSC

1. LEAD NO. 1 IDENTIFIED BY A DOT.

2. LEADS WILL BE EITHER TIN PLATED OR SOLDER DIPPED

IN ACCORDANCE WITH MIL-M-38510 REQUIREMENTS

13

12

0.009 (0.229)

0.005 (0.127)

–11–

0.212 (5.38)

0.205 (5.207)

0.311 (7.9)

0.301 (7.64)

0.07 (1.78)

0.066 (1.67)

8°

0°

0.037 (0.94)

0.022 (0.559)

Page 12

ADM205–ADM211/ADM213

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

PIN 1

0.01 (0.254)

0.006 (0.15)

28-Lead SOIC (R-28)

28

1

0.708 (18.02)

0.696 (17.67)

0.05 (1.27)

BSC

1. LEAD NO. IDENTIFIED BY A DOT.

2. SOICLEADS WILL BE EITHER TIN PLATED OR SOLDER DIPPED

IN ACCORDANCE WITH MIL-M-38510 REQUIREMENTS.

0.019 (0.49)

0.014 (0.35)

15

14

0.299 (7.6)

0.291 (7.39)

0.096 (2.44)

0.089 (2.26)

0.013 (0.32)

0.009 (0.23)

0.414 (10.52)

0.398 (10.10)

6

°

0

°

0.03 (0.76)

0.02 (0.51)

0.042 (1.067)

0.018 (0.457)

28

PIN 1

0.008 (0.203)

0.002 (0.050)

28-Lead SSOP (RS-28)

15

0.212 (5.38)

0.205 (5.207)

0.311 (7.9)

0.301 (7.64)

141

0.407 (10.34)

0.397 (10.08)

0.0256 (0.65)

BSC

1. LEAD NO. 1 IDENTIFIED BY A DOT.

2. LEADS WILL BE EITHER TIN PLATED OR SOLDER DIPPED

IN ACCORDANCE WITH MIL-M-38510 REQUIREMENTS

0.07 (1.78)

0.066 (1.67)

0.009 (0.229)

0.005 (0.127)

8°

0°

0.037 (0.94)

0.022 (0.559)

C1897–18–4/94

–12–

PRINTED IN U.S.A.

REV. 0

Loading...

Loading...