Page 1

50 MHz to 4.0 GHz

FEATURES

Fixed gain of 20 dB

Operation from 50 MHz to 4.0 GHz

Highest dynamic range gain block

Input/output internally matched to 50 Ω

Integrated bias control circuit

OIP3 of 42.0 dBm at 2.0 GHz

P1dB of 19.3 dBm at 2.0 GHz

Noise figure of 3.3 dB at 2.0 GHz

Single 5 V power supply

Low quiescent current of 89 mA

Thermally efficient SOT-89 package

ESD rating of ±1.5 kV (Class 1C)

GENERAL DESCRIPTION

The ADL5602 is a broadband 20 dB linear amplifier that operates

at frequencies up to 4 GHz. The device can be used in a wide

variety of cellular, CATV, military, and instrumentation equipment.

The ADL5602 provides the highest dynamic range available

from an internally matched gain block. This is accomplished

by providing extremely low noise figures and very high OIP3

specifications simultaneously, across the entire 4 GHz

frequency range.

The ADL5602 provides a gain of 20 dB, which is stable over

frequency, temperature, power supply, and from device to

device. The device is internally matched to 50 Ω at the input

and output, making the ADL5602 very easy to implement in a

wide variety of applications. Only input/output ac coupling

capacitors, power supply decoupling capacitors, and an external

inductor are required for operation.

RF/IF Gain Block

ADL5602

FUNCTIONAL BLOCK DIAGRAM

GND

(2)

ADL5602

BIAS

1 2

RFIN GND RFOUT

Figure 1.

The ADL5602 is fabricated on an InGaP HBT process and has

an ESD rating of ±1.5 kV (Class 1C). The device is available in a

thermally efficient SOT-89 package.

The ADL5602 consumes 89 mA on a single 5 V supply and is

fully specified for operation from −40°C to +85°C.

A fully populated RoHS-compliant evaluation board is available.

3

8190-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

Page 2

ADL5602

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Typical Scattering Parameters (S Parameters) .......................... 5

Absolute Maximum Ratings ............................................................ 7

ESD Caution .................................................................................. 7

Pin Configuration and Function Descriptions ............................. 8

Typical Performance Characteristics ............................................. 9

REVISION HISTORY

6/09—Revision 0: Initial Version

Basic Connections .......................................................................... 11

Soldering Information and Recommended

PCB Land Pattern ....................................................................... 11

W-CDMA ACPR Performance .................................................... 12

Evaluation Board ............................................................................ 13

Outline Dimensions ....................................................................... 14

Ordering Guide .......................................................................... 14

Rev. 0 | Page 2 of 16

Page 3

ADL5602

SPECIFICATIONS

VCC = 5 V and TA = 25°C, unless otherwise noted.

Table 1.

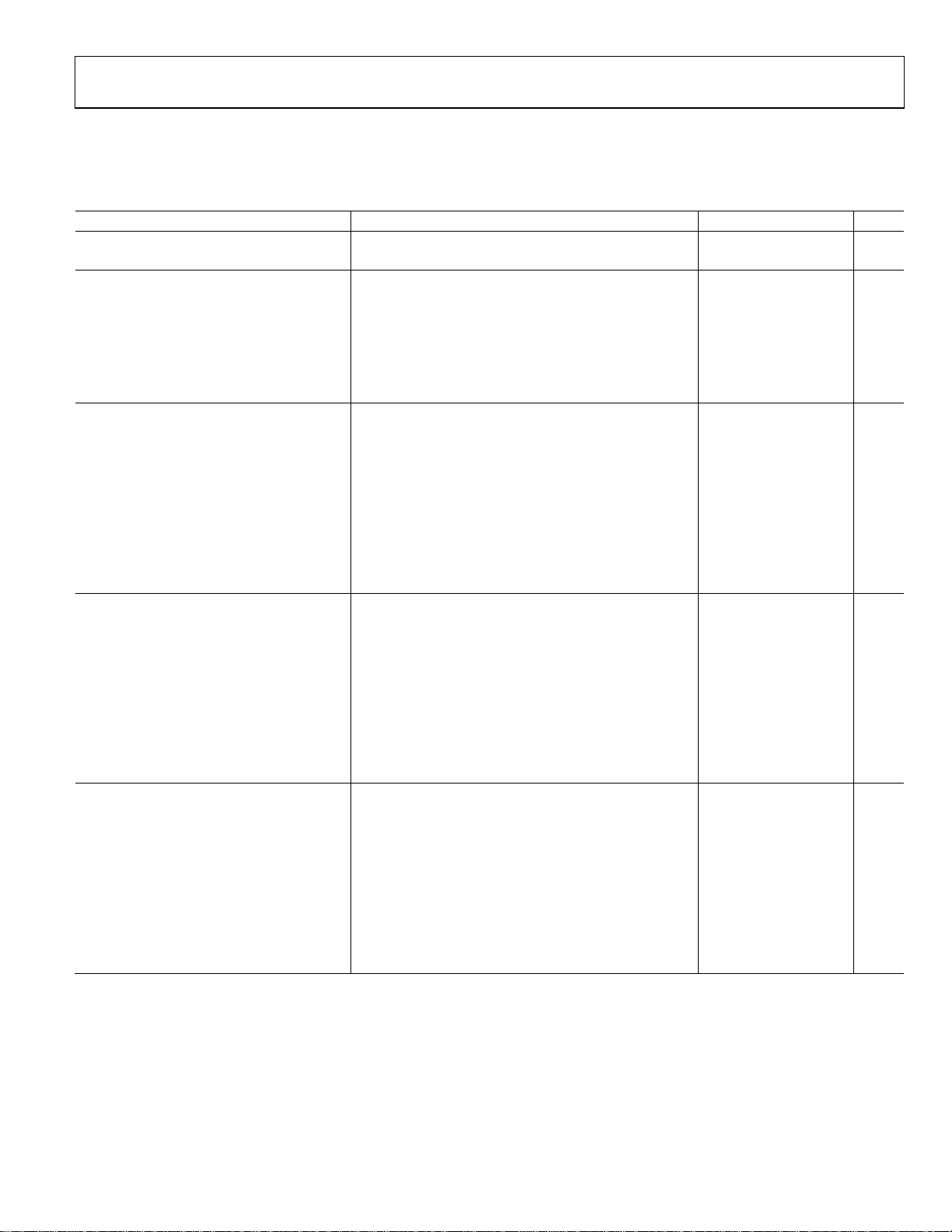

Parameter Conditions Min Typ Max Unit

OVERALL FUNCTION

Frequency Range 50 4000 MHz

FREQUENCY = 50 MHz

Gain 18.3 dB

Output 1 dB Compression Point (P1dB) 18.0 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −40.5 dBc

OUT

= 0 dBm −46.1 dBc

OUT

Noise Figure 2.9 dB

FREQUENCY = 140 MHz

Gain 17.0 dB

vs. Frequency ±50 MHz ±1.2 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.03 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.04 dB

Output 1 dB Compression Point (P1dB) 18.3 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −45.1 dBc

OUT

= 0 dBm −55.1 dBc

OUT

Noise Figure 2.9 dB

FREQUENCY = 350 MHz

Gain 19.7 dB

vs. Frequency ±50 MHz ±0.20 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.31 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.01 dB

Output 1 dB Compression Point (P1dB) 20.0 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −49.9 dBc

OUT

= 0 dBm −83.7 dBc

OUT

Noise Figure 3.0 dB

FREQUENCY = 700 MHz

Gain 19.0 20.2 21.0 dB

vs. Frequency ±50 MHz ±0.01 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.28 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.01 dB

Output 1 dB Compression Point (P1dB) 19.0 20.1 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −50.3 dBc

OUT

= 0 dBm −78.4 dBc

OUT

Noise Figure 3.0 dB

) = 0 dBm per tone 27.5 dBm

OUT

) = 0 dBm per tone 25.0 dBm

OUT

) = 0 dBm per tone 36.5 dBm

OUT

) = 0 dBm per tone 38.5 dBm

OUT

Rev. 0 | Page 3 of 16

Page 4

ADL5602

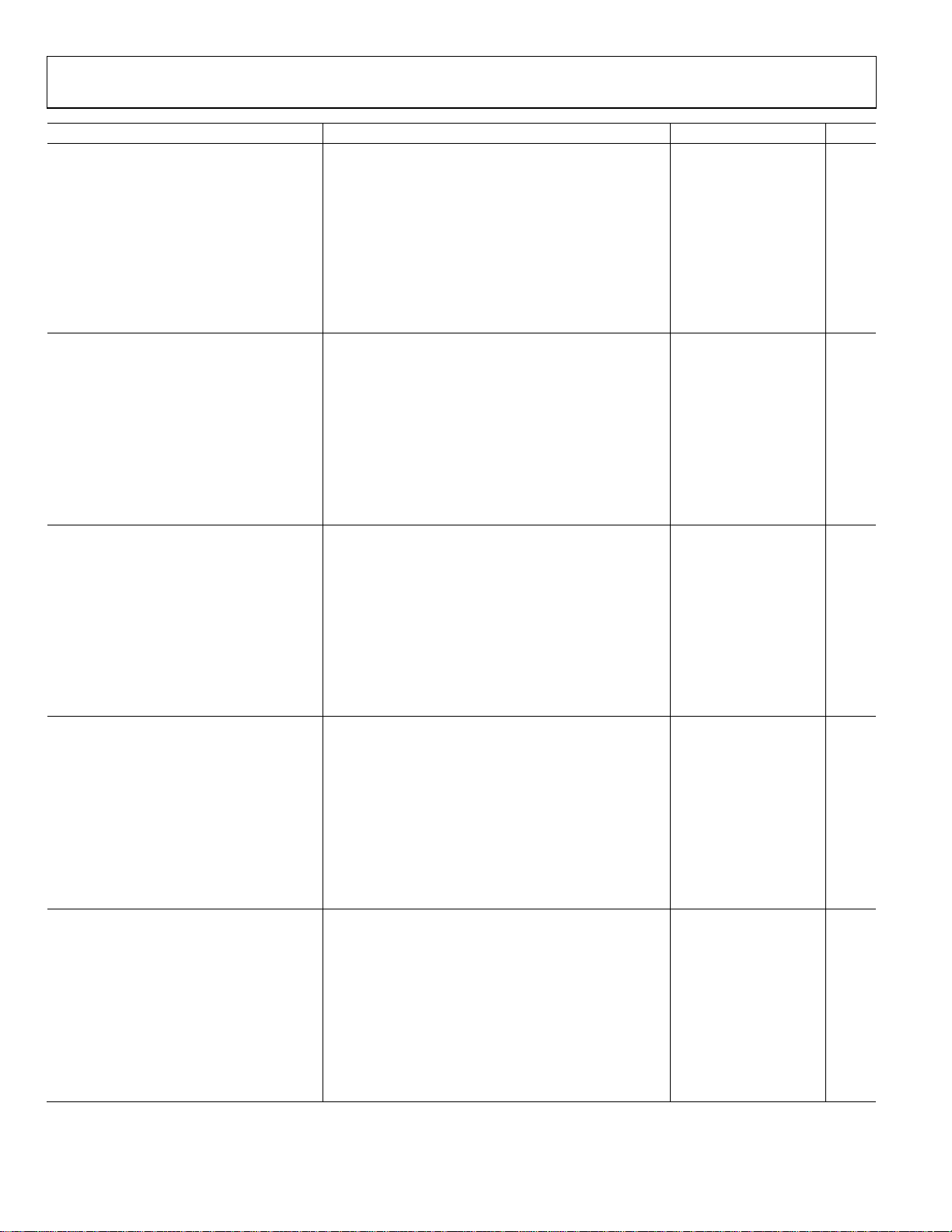

Parameter Conditions Min Typ Max Unit

FREQUENCY = 900 MHz

Gain 19.0 20.2 21.0 dB

vs. Frequency ±50 MHz ±0.01 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.28 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.01 dB

Output 1 dB Compression Point (P1dB) 19.0 20.1 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −59.4 dBc

OUT

= 0 dBm −77.3 dBc

OUT

Noise Figure 2.9 dB

FREQUENCY = 2000 MHz

Gain 19.5 dB

vs. Frequency ±50 MHz ±0.04 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.35 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.04 dB

Output 1 dB Compression Point (P1dB) 19.3 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −53.1 dBc

OUT

= 0 dBm −60.7 dBc

OUT

Noise Figure 3.3 dB

FREQUENCY = 2600 MHz

Gain 19.2 dB

vs. Frequency ±50 MHz ±0.01 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.28 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.05 dB

Output 1 dB Compression Point (P1dB) 18.7 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −52.8 dBc

OUT

= 0 dBm −67.4 dBc

OUT

Noise Figure 3.4 dB

FREQUENCY = 3500 MHz

Gain 19.3 dB

vs. Frequency ±50 MHz ±0.03 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.37 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.07 dB

Output 1 dB Compression Point (P1dB) 17.4 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −42.9 dBc

OUT

= 0 dBm −66.4 dBc

OUT

Noise Figure 3.8 dB

FREQUENCY = 4000 MHz

Gain 18.5 dB

vs. Frequency ±50 MHz ±0.19 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.73 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.08 dB

Output 1 dB Compression Point (P1dB) 15.2 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −44.1 dBc

OUT

= 0 dBm −64.0 dBc

OUT

Noise Figure 4.2 dB

) = 0 dBm per tone 40.0 dBm

OUT

) = 0 dBm per tone 42.0 dBm

OUT

) = 0 dBm per tone 36.5 dBm

OUT

) = 0 dBm per tone 31.5 dBm

OUT

) = 0 dBm per tone 28.0 dBm

OUT

Rev. 0 | Page 4 of 16

Page 5

ADL5602

Parameter Conditions Min Typ Max Unit

POWER INTERFACE VCC

Supply Voltage (VCC) 4.5 5 5.5 V

Supply Current 89 106 mA

vs. Temperature −40°C ≤ TA ≤ +85°C ±3 mA

Power Dissipation VCC = 5 V 0.45 W

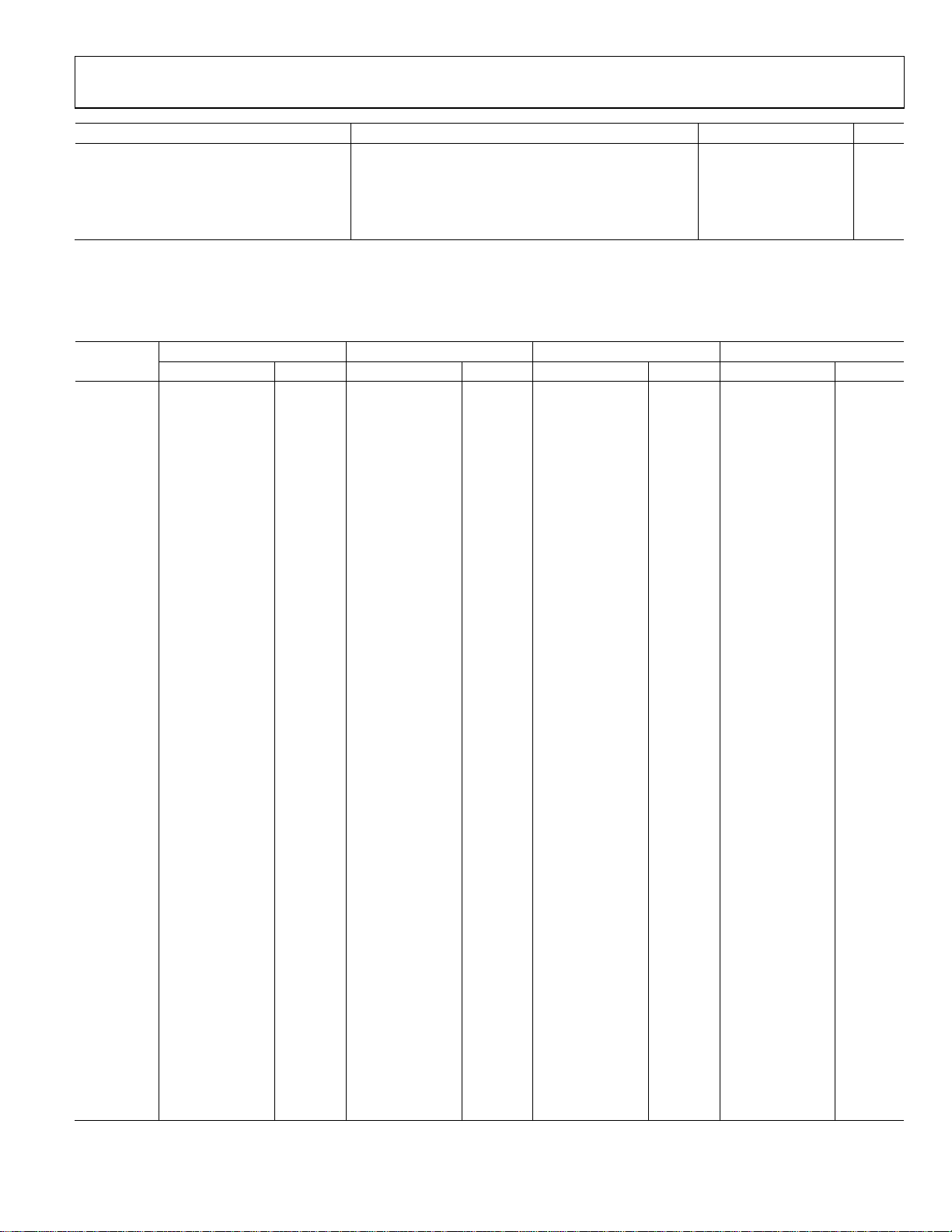

TYPICAL SCATTERING PARAMETERS (S PARAMETERS)

VCC = 5 V and TA = 25°C, the effects of the test fixture have been de-embedded up to the pins of the device.

Table 2.

Frequency

(MHz)

50 −12.75 +32.81 18.14 +163.00 −25.27 −9.54 −8.96 −145.86

100 −8.98 −7.00 15.77 −179.92 −27.59 +4.56 −7.07 −178.96

150 −10.11 −34.04 17.27 −169.01 −26.11 +16.05 −7.89 +159.89

200 −11.97 −50.46 18.50 −168.73 −24.84 +16.55 −9.33 +147.22

250 −13.85 −62.42 19.21 −171.01 −24.14 +14.79 −10.87 +140.02

300 −15.69 −72.90 19.64 −173.77 −23.70 +12.89 −12.23 +136.16

350 −17.40 −81.30 19.90 −176.45 −23.43 +11.02 −13.56 +134.03

400 −19.17 −88.48 20.07 −178.86 −23.26 +9.65 −14.79 +132.79

450 −20.86 −97.45 20.18 +178.79 −23.14 +8.07 −15.99 +132.72

500 −22.52 −107.32 20.25 +176.86 −23.08 +7.11 −17.02 +133.33

550 −24.32 −112.89 20.32 +174.84 −23.00 +6.15 −18.21 +133.04

600 −26.07 −120.03 20.35 +173.09 −22.97 +5.24 −19.45 +135.06

650 −27.89 −128.79 20.39 +171.35 −22.93 +4.35 −20.73 +136.29

700 −30.79 −133.19 20.42 +169.67 −22.91 +3.72 −22.22 +136.96

750 −34.53 −136.03 20.42 +167.93 −22.91 +2.93 −23.91 +135.39

800 −42.59 −130.76 20.46 +166.48 −22.88 +2.30 −26.35 +136.07

850 −46.49 −2.93 20.47 +164.85 −22.88 +1.67 −29.40 +132.08

900 −34.26 +15.99 20.47 +163.17 −22.86 +0.98 −34.27 +116.48

950 −29.55 +9.83 20.48 +161.77 −22.86 +0.39 −40.86 +41.72

1000 −25.87 +5.52 20.48 +160.25 −22.86 −0.21 −31.44 −10.36

1050 −23.03 +1.85 20.47 +158.65 −22.89 −0.84 −26.19 −18.99

1100 −21.25 +0.10 20.45 +157.18 −22.90 −1.43 −23.27 −22.34

1150 −19.31 −1.89 20.45 +155.50 −22.92 −2.06 −20.70 −22.26

1200 −17.72 −4.09 20.40 +153.93 −22.96 −2.72 −18.67 −24.44

1250 −16.13 −6.53 20.35 +152.44 −23.04 −3.38 −16.92 −24.75

1300 −14.81 −8.71 20.31 +150.88 −23.07 −4.04 −15.44 −25.79

1350 −13.65 −10.01 20.24 +149.35 −23.16 −4.60 −14.14 −25.36

1400 −12.68 −11.33 20.18 +147.91 −23.22 −5.06 −13.12 −25.73

1450 −11.72 −12.65 20.11 +146.40 −23.32 −5.76 −12.04 −25.59

1500 −10.92 −13.56 20.04 +145.13 −23.39 −6.16 −11.20 −25.40

1550 −10.21 −14.37 19.97 +143.86 −23.49 −6.54 −10.49 −25.60

1600 −9.58 −15.37 19.88 +142.58 −23.57 −6.93 −9.77 −25.59

1650 −9.05 −15.74 19.80 +141.40 −23.69 −7.16 −9.21 −25.31

1700 −8.52 −16.73 19.72 +140.23 −23.76 −7.45 −8.66 −25.42

1750 −8.13 −17.13 19.64 +139.13 −23.87 −7.60 −8.26 −25.32

1800 −7.76 −17.59 19.57 +138.12 −23.94 −7.80 −7.91 −24.96

1850 −7.46 −17.76 19.50 +137.16 −24.05 −7.88 −7.56 −24.77

1900 −7.19 −17.92 19.43 +136.25 −24.13 −7.91 −7.35 −24.46

1950 −6.98 −17.84 19.39 +135.31 −24.18 −7.94 −7.13 −23.92

Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°)

S11 S21 S12 S22

Rev. 0 | Page 5 of 16

Page 6

ADL5602

Frequency

(MHz)

2000 −6.85 −18.00 19.35 +134.44 −24.26 −7.99 −6.96 −23.55

2050 −6.74 −17.93 19.31 +133.61 −24.29 −7.91 −6.86 −22.70

2100 −6.63 −17.57 19.29 +132.74 −24.37 −7.81 −6.75 −22.45

2150 −6.66 −17.34 19.25 +132.06 −24.42 −7.58 −6.76 −22.01

2200 −6.65 −17.26 19.29 +131.19 −24.40 −7.63 −6.78 −21.42

2250 −6.69 −17.10 19.30 +130.47 −24.41 −7.59 −6.82 −20.82

2300 −6.77 −16.90 19.33 +129.54 −24.42 −7.40 −6.87 −20.25

2350 −6.87 −16.65 19.36 +128.72 −24.40 −7.46 −7.04 −19.57

2400 −7.05 −16.25 19.42 +127.81 −24.38 −7.50 −7.20 −18.85

2450 −7.22 −16.11 19.49 +126.89 −24.35 −7.46 −7.42 −18.17

2500 −7.45 −16.00 19.53 +125.82 −24.31 −7.75 −7.66 −17.76

2550 −7.64 −15.84 19.58 +124.74 −24.31 −7.86 −7.91 −17.18

2600 −7.95 −15.66 19.66 +123.61 −24.25 −8.20 −8.29 −16.64

2650 −8.29 −15.64 19.74 +122.46 −24.19 −8.54 −8.66 −16.15

2700 −8.62 −15.95 19.81 +121.20 −24.17 −8.90 −8.97 −15.97

2750 −8.95 −15.92 19.89 +119.91 −24.13 −9.35 −9.41 −15.67

2800 −9.31 −16.23 19.94 +118.47 −24.08 −9.95 −9.87 −15.96

2850 −9.67 −16.74 20.03 +117.02 −24.05 −10.55 −10.34 −16.17

2900 −9.99 −17.33 20.07 +115.47 −24.07 −11.17 −10.83 −16.68

2950 −10.28 −18.00 20.14 +113.95 −24.02 −11.71 −11.28 −17.66

3000 −10.53 −19.16 20.18 +112.28 −24.03 −12.51 −11.69 −19.15

3050 −10.69 −20.29 20.21 +110.53 −24.10 −13.72 −12.17 −21.42

3100 −10.86 −21.94 20.25 +108.77 −24.04 −14.66 −12.54 −24.24

3150 −10.91 −23.61 20.27 +107.15 −24.09 −15.23 −12.83 −27.07

3200 −10.70 −25.42 20.28 +105.16 −24.18 −16.23 −12.92 −32.00

3250 −10.57 −27.33 20.28 +103.09 −24.17 −17.39 −13.04 −36.71

3300 −10.38 −29.60 20.26 +101.20 −24.22 −18.24 −12.99 −42.66

3350 −9.92 −31.76 20.21 +99.05 −24.39 −20.06 −12.57 −48.16

3400 −9.48 −34.25 20.15 +96.98 −24.49 −20.74 −12.19 −54.36

3450 −8.98 −36.47 20.08 +94.93 −24.61 −21.69 −11.64 −59.44

3500 −8.44 −38.18 20.00 +92.80 −24.72 −23.44 −11.00 −64.07

3550 −7.92 −40.32 19.90 +90.88 −24.88 −24.35 −10.34 −68.43

3600 −7.34 −42.20 19.74 +88.69 −25.15 −25.31 −9.59 −72.77

3650 −6.79 −43.72 19.57 +86.66 −25.35 −26.95 −8.90 −76.09

3700 −6.29 −45.15 19.41 +84.80 −25.56 −27.76 −8.29 −79.17

3750 −5.82 −46.51 19.23 +82.83 −25.90 −28.90 −7.69 −81.76

3800 −5.37 −47.51 19.00 +81.05 −26.16 −29.05 −7.12 −84.30

3850 −4.93 −48.36 18.78 +79.53 −26.46 −30.35 −6.65 −86.42

3900 −4.56 −48.94 18.55 +78.02 −26.81 −29.93 −6.20 −88.14

3950 −4.23 −49.33 18.32 +76.71 −27.08 −31.04 −5.83 −89.69

4000 −3.97 −49.71 18.08 +75.39 −27.50 −30.65 −5.50 −91.14

Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°)

S11 S21 S12 S22

Rev. 0 | Page 6 of 16

Page 7

ADL5602

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage, VCC 6.5 V

Input Power (re: 50 Ω) 16 dBm

Internal Power Dissipation (Paddle Soldered) 600 mW

θ

(Junction to Air) 30.7°C/W

JA

θ

(Junction to Paddle) 5.0°C/W

JC

Maximum Junction Temperature 150°C

Lead Temperature (Soldering, 60 sec) 240°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 7 of 16

Page 8

ADL5602

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

RFIN

ADL5602

2

GND

RFOUT

TOP VIEW

(Not to Scale)

3

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 RFIN RF Input. This pin requires a dc blocking capacitor.

2 GND Ground. Connect this pin to a low impedance ground plane.

3 RFOUT

RF Output and Supply Voltage. DC bias is provided to this pin through an inductor that is connected to

the external power supply. The RF path requires a dc blocking capacitor.

(2) Exposed Paddle Exposed Paddle. Internally connected to GND. Solder to a low impedance ground plane.

(2)

GND

08190-002

Rev. 0 | Page 8 of 16

Page 9

ADL5602

TYPICAL PERFORMANCE CHARACTERISTICS

45

40

35

30

25

20

15

10

NF, GAIN, P1dB, OIP3 (dB, dBm)

5

0

0 0.4 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.0

FREQUENCY (GHz)

OIP3

GAIN

P1dB

NF

Figure 3. Noise Figure, Gain, P1dB, and OIP3 vs. Frequency

21.0

20.5

20.0

19.5

19.0

18.5

GAIN (dB)

18.0

17.5

17.0

16.5

0 0.4 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.0

+25°C

FREQUENCY (GHz)

–40°C

+85°C

Figure 4. Gain vs. Frequency and Temperature

30

28

26

24

22

20

P1dB (dBm)

18

16

14

12

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

08190-003

FREQUENCY (GHz)

+25°C

+85°C

–40°C

+25°C

+85°C

Figure 6. P1dB and OIP3 vs. Frequency and Temperature

44

2600MHz

140MHz

900MHz

700MHz

4000MHz

P

PER TONE (d Bm)

OUT

350MHz

2000MHz

3500MHz

) and Frequency

OUT

42

40

38

36

34

32

30

OIP3 (dBm)

28

26

24

22

50MHz

20

–5–3–11357911131517

08190-004

Figure 7. OIP3 vs. Output Power (P

–40°C

45

40

35

30

25

20

OIP3 (dBm)

15

10

5

0

08190-006

8190-007

0

–5

–10

–15

–20

–25

–30

S-PARAMETERS (dB)

–35

–40

–45

–50

0 0.4 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.0

S11

S12

S22

FREQUENCY (GHz)

Figure 5. Input Return Loss (S11), Output Return Loss (S22), and

Reverse Isolation (S12) vs. Frequency

08190-005

Rev. 0 | Page 9 of 16

5.6

5.2

4.8

4.4

4.0

3.6

3.2

NOISE FIGURE (dB)

2.8

2.4

2.0

0 0.4 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.0

FREQUENCY (GHz)

+85°C

+25°C

–40°C

Figure 8. Noise Figure vs. Frequency and Temperature

08190-008

Page 10

ADL5602

–

30

–40

–50

–60

–70

HARMONICS (d Bc)

–80

–90

0.50 1.0 1.5 2.0 2.5 3.0 3.5 4.0

FREQUENCY ( GHz)

Figure 9. Single Tone Harmonics vs. Frequency , P

H2

H3

OUT

08190-009

= 0 dBm

45

40

35

30

25

20

15

PERCENTAGE (%)

10

5

0

32 34 36 38 40 42 44 46 48 50

OIP3 (dBm)

Figure 12. OIP3 Distribution at 2000 MHz, P

= 0 dBm

OUT

08190-020

30

25

20

15

10

PERCENTAGE (%)

5

0

18.8 19.0 19.2 19.4 19.6 19.8 20.0

GAIN (dB)

Figure 10. Gain Distribution at 2000 MHz

30

25

20

15

10

PERCENTAGE (%)

5

0

18.5 18.7 18.9 19.1 19.3 19.5 19.7 19.9

P1dB (dBm)

Figure 11. P1dB Distribution at 2000 MHz

80

70

60

50

40

30

PERCENTAGE (%)

20

10

0

2.6 2.8 3.0 3.2 3.4 3.6 3.8 4.0

8190-010

NOISE FIGURE (dB)

08190-021

Figure 13. Noise Figure Distribution at 2000 MHz

98

96

94

92

90

88

86

SUPPLY CURRENT (mA)

84

82

80

–40–30–20–100 102030405060708090

8190-011

5.25V

5V

4.75V

TEMPERATURE (°C)

8190-014

Figure 14. Supply Current vs. Temperature

Rev. 0 | Page 10 of 16

Page 11

ADL5602

VCC

BASIC CONNECTIONS

The basic connections for operating the ADL5602 are shown in

Figure 15. Recommended components are listed in Tabl e 5. The

input and output should be ac-coupled with appropriately sized

capacitors (device characterization was performed with 0.1 F

capacitors). A 5 V dc bias is supplied to the amplifier through

the bias inductor connected to RFOUT (Pin 3). The bias voltage

should be decoupled using a 1 µF capacitor, a 1.2 nF capacitor,

and a 68 pF capacitor.

RFIN

C1

0.1µF

GND

GND

(2)

ADL5602

2

1

RFIN

3

GND

RFOUT

Figure 15. Basic Connections

C6

1µF

C5

1.2nF

C4

68pF

L1

470nH

C2

0.1µF

RFOUT

08190-015

SOLDERING INFORMATION AND RECOMMENDED PCB LAND PATTERN

Figure 16 shows the recommended land pattern for the ADL5602.

To minimize thermal impedance, the exposed paddle on the

package underside should be soldered down to a ground plane

along with Pin 2. If multiple ground layers exist, they should be

stitched together using vias. For more information on land

pattern design and layout, refer to AN-772 Application Note, A

Design and Manufacturing Guide for the Lead Frame Chip Scale

Package (LFCSP).

1.80mm

3.48mm

5.56mm

0.20mm

0.86mm

0.62mm

1.27mm

1.50mm

3.00mm

08190-016

Figure 16. Recommended Land Pattern

Table 5. Recommended Components for Basic Connections

Frequency (MHz) C1 C2 L1 C4 C5 C6

50 to 4000 0.1 µF 0.1 µF 470 nH (Coilcraft 0603LS-NX or equivalent) 68 pF 1.2 nF 1 µF

Rev. 0 | Page 11 of 16

Page 12

ADL5602

–

A

W-CDMA ACPR PERFORMANCE

Figure 17 shows a plot of adjacent channel power ratio (ACPR)

vs. P

for the ADL5602. The signal type being used is a single

OUT

W-CDMA carrier (Test Model 1-64) at 2140 MHz. This signal is

generated by a very low ACPR source. ACPR is measured at the

output by a high dynamic range spectrum analyzer, which

incorporates an instrument noise correction function.

The ADL5602 achieves an ACPR of −75 dBc at −5 dBm output,

at which point device noise and not distortion is beginning to

dominate the power in the adjacent channels. At an output

power of +5 dBm, ACPR is still very low at −61 dBc, making

the device particularly suitable for PA driver applications.

40

–45

–50

–55

–60

–65

T 5MHz CARRIER O FFSET ( dBc)

–70

–75

ACPR

–80

–20 –15 –10 –5 0 5 10

Figure 17. ACPR vs. P

P

(dBm)

OUT

, Single Carrier W-CDMA (Test Model 1-64) at

OUT

2140 MHz Evaluation Board

08190-017

Rev. 0 | Page 12 of 16

Page 13

ADL5602

V

EVALUATION BOARD

GND

Figure 19 shows the schematic for the ADL5602 evaluation

board. The board is powered by a single 5 V supply.

The components used on the board are listed in Tab le 6 .

Power can be applied to the board through clip-on leads

GND

(2)

(VCC and GND).

ADL5602

RFIN

C1

0.1µF

1

RFIN

3

GND

RFOUT

2

Figure 19. Evaluation Board Schematic

08190-018

Figure 18. Evaluation Board Layout (Top)

Table 6. Evaluation Board Configuration Options

Component Description Default Value

C1, C2 AC-coupling capacitors 0.1 F, 0402

L1 DC bias inductor 470 nH, 0603 (Coilcraft 0603LS-NX or equivalent)

VCC and GND Clip-on terminals for power supply

C4, C5, C6 Power supply decoupling capacitors C4 = 68 pF, 0603; C5 = 1.2 nF, 0603; C6 = 1 F, 1206

CC

1.2nF

C6

1µF

C5

C4

68pF

L1

470nH

C2

0.1µF

RFOUT

8190-019

Rev. 0 | Page 13 of 16

Page 14

ADL5602

OUTLINE DIMENSIONS

*

1.75

1.55

4.25

3.94

1.50 TYP

(2)

12

3.00 TYP

4.60

4.40

*

0.56

0.36

*

COMPLIANT TO JEDEC S TANDARDS TO-243 W ITH

EXCEPTIO N TO DIMENSIONS INDICATED BY AN ASTERIS K.

2.60

2.30

3

1.20

0.75

2.29

2.14

0.44

0.35

*

0.52

0.32

END VIEW

1.60

1.40

121808-B

Figure 20. 3-Lead Small Outline Transistor Package [SOT-89]

(RK-3)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

ADL5602ARKZ-R71 −40°C to +85°C 3-Lead SOT-89, 7“ Tape and Reel RK-3

ADL5602-EVALZ1 Evaluation Board

1

Z = RoHS Compliant Part.

Rev. 0 | Page 14 of 16

Page 15

ADL5602

NOTES

Rev. 0 | Page 15 of 16

Page 16

ADL5602

NOTES

©2009 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D08190-0-6/09(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...