Page 1

3.3 GHz Ultralow Distortion

V

V

V

FEATURES

−3 dB bandwidth of 3.3 GHz (AV = 6 dB)

Pin-strappable gain adjust: 6 dB, 12 dB, 15.5 dB

Differential or single-ended input to differential output

Low noise input stage: 2.1 nV/√Hz RTI @ A

Low broadband distortion (Av = 6 dB)

10 MHz: −91 dBc HD2, −98 dBc HD3

70 MHz: −102 dBc HD2, −90 dBc HD3

140 MHz: −104 dBc HD2, −87 dBc HD3

250 MHz: −80 dBc HD2, −94 dBc HD3

IMD3s of −94 dBc at 250 MHz center

Slew rate: 9.8 V/ns

Fast settling of 2 ns and overdrive recovery of 3 ns

Single-supply operation: 3 V to 3.6 V

Power-down control

Fabricated using the high speed XFCB3 SiGe process

APPLICATIONS

Differential ADC drivers

Single-ended to differential conversion

RF/IF gain blocks

SAW filter interfacing

= 12 dB

V

RF/IF Differential Amplifier

ADL5562

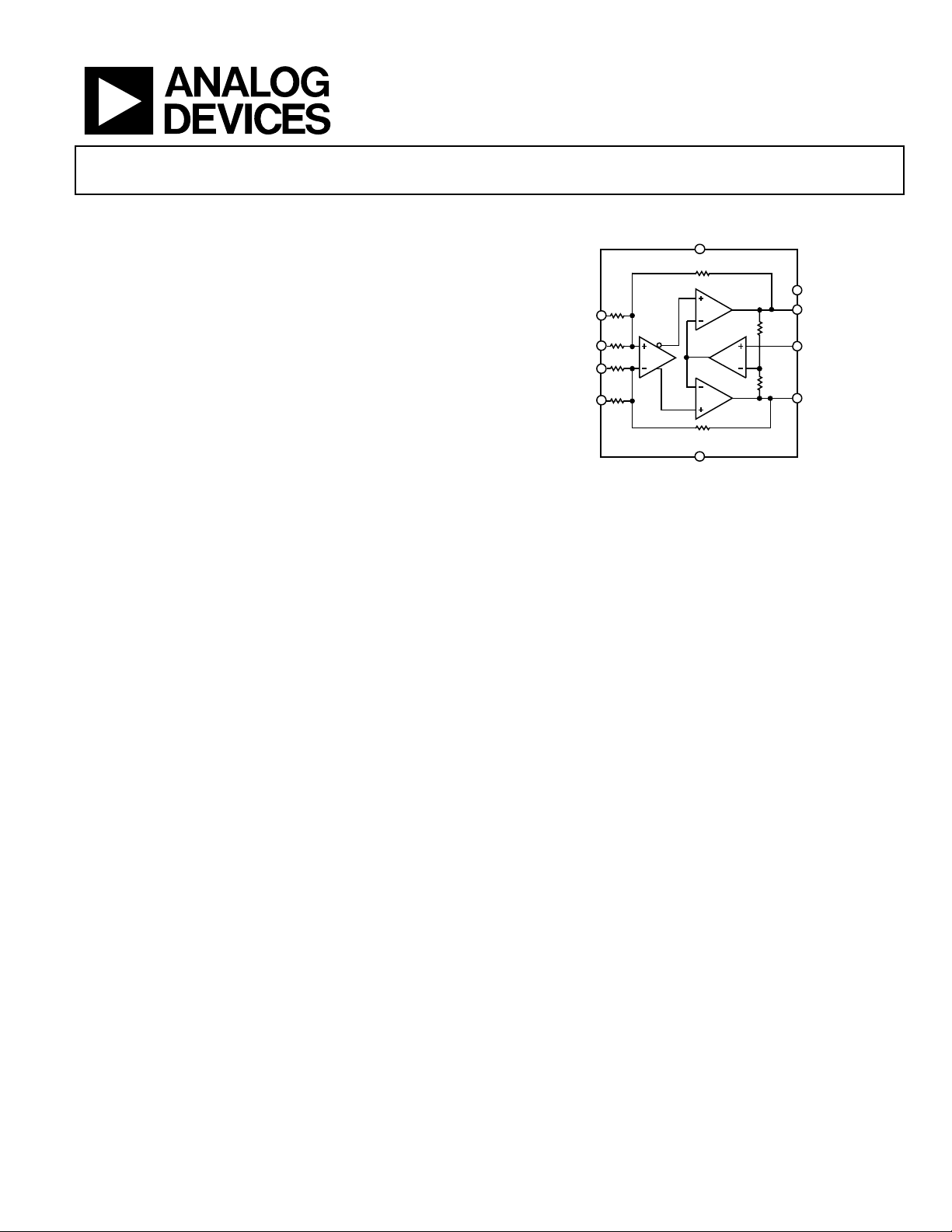

FUNCTIONAL BLOCK DIAGRAM

CC

R

F

ENBL

VON

VCOM

VOP

08003-001

VIP2

VIP1

IN1

IN2

R

G2

R

G1

R

G1

R

G2

R

F

ADL5562

GND

Figure 1.

GENERAL DESCRIPTION

The ADL5562 is a high performance differential amplifier

optimized for RF and IF applications. The amplifier offers low

noise of 2.1 nV/√Hz and excellent distortion performance over

a wide frequency range, making it an ideal driver for high speed

8-bit to 16-bit ADCs.

The ADL5562 provides three gain levels of 6 dB, 12 dB, and

15.5 dB through a pin-strappable configuration. For the singleended input configuration, the gains are reduced to 5.6 dB,

11.1 dB, and 14.1 dB. Using an external series input resistor

expands the amplifier gain flexibility and allows for any gain

selection from 0 dB to 15.5 dB.

The quiescent current of the ADL5562 is typically 80 mA and,

when disabled, consumes less than 3 mA, offering excellent

input-to-output isolation.

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The device is optimized for wideband, low distortion performance.

These attributes, together with its adjustable gain capability,

make this device the amplifier of choice for general-purpose IF

and broadband applications where low distortion, noise, and power

are critical. This device is optimized for the best combination of

slew speed, bandwidth, and broadband distortion. These attributes

allow it to drive a wide variety of ADCs and make it ideally suited

for driving mixers, pin diode attenuators, SAW filters, and multielement discrete devices.

Fabricated on an Analog Devices, Inc., high speed SiGe process,

the ADL5562 is supplied in a compact 3 mm × 3 mm, 16-lead

LFCSP package and operates over the temperature range of

−40°C to + 85°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2011 Analog Devices, Inc. All rights reserved.

Page 2

ADL5562

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 6

ESD Caution .................................................................................. 6

Pin Configuration and Function Descriptions ............................. 7

Typical Performance Characteristics ............................................. 8

Circuit Description ......................................................................... 13

Basic Structure ............................................................................ 13

REVISION HISTORY

7/11—Rev. B to Rev. C

Changes to Figure 28 and Figure 29 ............................................. 12

Added Figure 30 and Figure 31; Renumbered Sequentially ..... 12

Changes to Ordering Guide .......................................................... 21

3/10—Rev. A to Rev. B

Changes to Figure 43 ...................................................................... 19

Updated Outline Dimensions ....................................................... 21

Changes to Ordering Guide .......................................................... 21

9/09—Rev. 0 to Rev. A

Changes to Features Section............................................................ 1

Changes to Table 1 ............................................................................ 3

Changes to Figure 5 .......................................................................... 8

Changes to Figure 9 and Figure 10 ................................................. 9

Changes to Figure 32, Equation 1, and Figure 34 ...................... 15

Changes to Equation 2 ................................................................... 16

Changes to Figure 38, Figure 39, Figure 40, and Table 9 ........... 17

Changes to Figure 43 ...................................................................... 19

Moved Table 14 to........................................................................... 19

5/09—Revision 0: Initial Version

Applications Information .............................................................. 14

Basic Connections ...................................................................... 14

Input and Output Interfacing ................................................... 15

Gain Adjustment and Interfacing ............................................ 16

ADC Interfacing ......................................................................... 16

Layout Considerations ............................................................... 18

Soldering Information ............................................................... 19

Evaluation Board ........................................................................ 19

Outline Dimensions ....................................................................... 21

Ordering Guide .......................................................................... 21

Rev. C | Page 2 of 24

Page 3

ADL5562

AV = 15.5 dB, V

≤ 1.0 V p-p

270 MHz

Maximum Output Voltage Swing

1 dB compressed

4.9 V p-p

SPECIFICATIONS

VCC = 3.3 V, VCOM = 1.65 V, RL = 200 Ω differential, AV = 6 dB, CL = 1 pF differential, f = 140 MHz, TA = 25°C.

Table 1.

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Bandwidth AV = 6 dB, V

AV = 12 dB, V

AV = 15.5 dB, V

Bandwidth for 0.1 dB Flatness AV = 6 dB, V

AV = 12 dB, V

Gain Accuracy AV = 6 dB, RL = open 0.17 dB

AV = 12 dB, RL = open 0.05 dB

AV = 15.5 dB, RL = open 0.06 dB

Gain Supply Sensitivity VCC ± 5% −0.005 dB/V

Gain Temperature Sensitivity −40°C to +85°C, AV = 15.5 dB 0.32 mdB/°C

Slew Rate Rise, AV = 15.5 dB, RL = 200 Ω, V

Fall, AV = 15.5 dB, RL = 200 Ω, V

Settling Time 2 V step to 1% 2 ns

Overdrive Recovery Time VIN = 4 V to 0 V step, V

Reverse Isolation (S12) 60 dB

INPUT/OUTPUT CHARACTERISTICS

Output Common Mode VCC/2 V

Voltage Adjustment Range 1.4 to 1.8 V

≤ 1.0 V p-p 3300 MHz

OUT

≤ 1.0 V p-p 3900 MHz

OUT

≤ 1.0 V p-p 1900 MHz

OUT

≤ 1.0 V p-p 220 MHz

OUT

≤ 1.0 V p-p 270 MHz

OUT

OUT

= 2 V step 9.8 V/ns

OUT

= 2 V step 10.1 V/ns

OUT

≤ ±10 mV 3 ns

OUT

Output Common-Mode Offset Referenced to VCC/2 60 mV

Output Common-Mode Drift −40°C to +85°C 285 µV/°C

Output Differential Offset Voltage 1 mV

CMRR 65 dB

Output Differential Offset Drift −40°C to +85°C 15 µV/°C

Input Bias Current 3 µA

Input Resistance (Differential) AV = 6 dB 400 Ω

AV = 12 dB 200 Ω

AV = 15.5 dB 133 Ω

Input Resistance (Single-Ended)1 AV = 5.6 dB, RS = 50 Ω 307 Ω

AV = 11.1 dB, RS = 50 Ω 179 Ω

AV = 14.1 dB, RS = 50 Ω 132 Ω

Input Capacitance (Single-Ended) 0.3 pF

Output Resistance (Differential) 12 Ω

POWER INTERFACE

Supply Voltage 3 3.3 3.6 V

ENBL Threshold Device disabled, ENBL low 0.6 V

Device enabled, ENBL high 1.3 V

ENBL Input Bias Current ENBL high −27 µA

ENBL low −300 µA

Quiescent Current ENBL high 75.5 80 84.5 mA

ENBL low 3.5 mA

Rev. C | Page 3 of 24

Page 4

ADL5562

Output Third-Order Intercept/Third-Order

AV = 6 dB, RL = 200 Ω, V

= 2 V p-p composite

+42/−97

dBm/dBc

Second/Third Harmonic Distortion

AV = 6 dB, RL = 200 Ω, V

= 2 V p-p

−102/−90

dBc

AV = 15.5 dB

18.1 dBm

Parameter Conditions Min Typ Max Unit

10 MHz NOISE/HARMONIC PERFORMANCE

Second/Third Harmonic Distortion AV = 6 dB, RL = 200 Ω, V

AV = 12 dB, RL = 200 Ω, V

AV = 15.5 dB, RL = 200 Ω, V

Intermodulation Distortion

(2 MHz spacing)

AV = 12 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 15.5 dB, RL = 200 Ω, V

(2 MHz spacing)

Noise Spectral Density (RTI) AV = 6 dB 3 nV/√Hz

AV = 12 dB 2.1 nV/√Hz

AV = 15.5 dB 1.6 nV/√Hz

1 dB Compression Point (RTO) AV = 6 dB 19.7 dBm

AV = 12 dB 19.6 dBm

AV = 15.5 dB 18.2 dBm

70 MHz NOISE/HARMONIC PERFORMANCE

AV = 12 dB, RL = 200 Ω, V

AV = 15.5 dB, RL = 200 Ω, V

Output Third-Order Intercept/Third-Order

Intermodulation Distortion

AV = 6 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 12 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 15.5 dB, RL = 200 Ω, V

(2 MHz spacing)

Noise Spectral Density (RTI) AV = 6 dB 3 nV/√Hz

AV = 12 dB 2.1 nV/√Hz

AV = 15.5 dB 1.6 nV/√Hz

1 dB Compression Point (RTO) AV = 6 dB 19.6 dBm

AV = 12 dB 19.6 dBm

AV = 15.5 dB 18.2 dBm

140 MHz NOISE/HARMONIC PERFORMANCE

Second/Third Harmonic Distortion AV = 6 dB, RL = 200 Ω, V

AV = 12 dB, RL = 200 Ω, V

AV = 15.5 dB, RL = 200 Ω, V

Output Third-Order Intercept/Third-Order

Intermodulation Distortion

AV = 6 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 12 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 15.5 dB, RL = 200 Ω, V

(2 MHz spacing)

Noise Spectral Density (RTI) AV = 6 dB 3 nV/√Hz

AV = 12 dB 2.1 nV/√Hz

AV = 15.5 dB 1.6 nV/√Hz

1 dB Compression Point (RTO) AV = 6 dB 19.6 dBm

AV = 12 dB 19.4 dBm

= 2 V p-p −91/−98 dBc

OUT

= 2 V p-p −95/−98 dBc

OUT

= 2 V p-p −96/−92 dBc

OUT

OUT

= 2 V p-p composite

OUT

= 2 V p-p composite

OUT

OUT

= 2 V p-p −97/−85 dBc

OUT

= 2 V p-p −93/−83 dBc

OUT

= 2 V p-p composite

OUT

= 2 V p-p composite

OUT

= 2 V p-p composite

OUT

= 2 V p-p −104/−87 dBc

OUT

= 2 V p-p −82/−81 dBc

OUT

= 2 V p-p −80/−80 dBc

OUT

= 2 V p-p composite

OUT

= 2 V p-p composite

OUT

= 2 V p-p composite

OUT

+43/−93 dBm/dBc

+43/−91 dBm/dBc

+46/−96 dBm/dBc

+44/−93 dBm/dBc

+43/−91 dBm/dBc

+47/−100 dBm/dBc

+45/−95 dBm/dBc

+43/−92 dBm/dBc

Rev. C | Page 4 of 24

Page 5

ADL5562

Output Third-Order Intercept/Third-Order

AV = 6 dB, RL = 200 Ω, V

= 2 V p-p composite

+43/−94

dBm/dBc

AV = 12 dB, RL = 200 Ω, V

= 1 V p-p

−69/−73

dBc

AV = 12 dB, RL = 200 Ω, V

= 1 V p-p composite

+24/−66

dBm/dBc

Parameter Conditions Min Typ Max Unit

250 MHz NOISE/HARMONIC PERFORMANCE

Second/Third Harmonic Distortion AV = 6 dB, RL = 200 Ω, V

AV = 12 dB, RL = 200 Ω, V

AV = 15.5 dB, RL = 200 Ω, V

Intermodulation Distortion

(2 MHz spacing)

AV = 12 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 15.5 dB, RL = 200 Ω, V

(2 MHz spacing)

Noise Spectral Density (RTI) AV = 6 dB 3.2 nV/√Hz

AV = 12 dB 2.2 nV/√Hz

AV = 15.5 dB 1.6 nV/√Hz

1 dB Compression Point (RTO) AV = 6 dB 19.8 dBm

AV = 12 dB 19.3 dBm

AV = 15.5 dB 19.1 dBm

500 MHz NOISE/HARMONIC PERFORMANCE

Second/Third Harmonic Distortion AV = 6 dB, RL = 200 Ω, V

AV = 15.5 dB, RL = 200 Ω, V

Output Third-Order Intercept/Third-Order

Intermodulation Distortion

AV = 6 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 12 dB, RL = 200 Ω, V

(2 MHz spacing)

AV = 15.5 dB, RL = 200 Ω, V

(2 MHz spacing)

Noise Spectral Density (RTI) AV = 6 dB 3.7 nV/√Hz

AV = 12 dB 2.2 nV/√Hz

AV = 15.5 dB 1.6 nV/√Hz

1 dB Compression Point (RTO) AV = 6 dB 18.1 dBm

AV = 12 dB 18.1 dBm

AV = 15.5 dB 18.1 dBm

1000 MHz NOISE/HARMONIC PERFORMANCE

Second/Third Harmonic Distortion AV = 6 dB, RL = 200 Ω, V

AV = 12 dB, RL = 200 Ω, V

AV = 15.5 dB, RL = 200 Ω, V

Output Third-Order Intercept/Third-Order

Intermodulation Distortion

AV = 6 dB, RL = 200 Ω, V

(2 MHz spacing)

(2 MHz spacing)

AV = 15.5 dB, RL = 200 Ω, V

(2 MHz spacing)

Noise Spectral Density (RTI) AV = 6 dB 4.7 nV/√Hz

AV = 12 dB 2.2 nV/√Hz

AV = 15.5 dB 1.6 nV/√Hz

1 dB Compression Point (RTO) AV = 6 dB 15 dBm

AV = 12 dB 15.1 dBm

AV = 15.5 dB 15.1 dBm

1

See the Applications Information section for a discussion of single-ended input, dc-coupled operation.

= 2 V p-p −80/−94 dBc

OUT

= 2 V p-p −74/−86 dBc

OUT

= 2 V p-p −74/−84 dBc

OUT

OUT

= 2 V p-p composite

OUT

= 2 V p-p composite

OUT

= 1 V p-p −75/−69 dBc

OUT

OUT

= 1 V p-p −72/−75 dBc

OUT

= 1 V p-p composite

OUT

= 1 V p-p composite

OUT

= 1 V p-p composite

OUT

= 1 V p-p −70/−60 dBc

OUT

= 1 V p-p −69/−61 dBc

OUT

= 1 V p-p −66/−59 dBc

OUT

= 1 V p-p composite

OUT

OUT

= 1 V p-p composite

OUT

+41/−87 dBm/dBc

+40/−86 dBm/dBc

+40/−98 dBm/dBc

+39/−97 dBm/dBc

+38/−93 dBm/dBc

+24/−65 dBm/dBc

+25/−66 dBm/dBc

Rev. C | Page 5 of 24

Page 6

ADL5562

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage (VCC) 3.6 V

VIP1, VIP2, VIN1, VIN2 VCC + 0.5 V

Internal Power Dissipation 310 mW

θJA 98.3°C/W

Maximum Junction Temperature 125°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. C | Page 6 of 24

Page 7

ADL5562

PIN 1

INDICATOR

1VIP2

2VIP1

3VIN1

4VIN2

11 VOP

12 ENBL

10 VON

9 VCOM

5VCC

6VCC

7VCC

8VCC

15

GND

16

GND

14

GND

13

GND

TOP VIEW

(Not to S cale)

ADL5562

08003-031

NOTES

1. EXPOS E D P ADDLE. CONNECT TO A LOW

IMPEDANCE T HE RM AL AND ELECTRI CAL

GROUND PLANE .

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 VIP2 Balanced Differential Input. Biased to VCOM, typically ac-coupled. Input for AV = 12 dB gain, strapped to

VIP1 for A

= 15.5 dB.

V

2 VIP1 Balanced Differential Input. Biased to VCOM, typically ac-coupled. Input for AV = 6 dB gain, strapped to

VIP2 for A

= 15.5 dB.

V

3 VIN1 Balanced Differential Input. Biased to VCOM, typically ac-coupled. Input for AV = 6 dB gain, strapped to

VIN2 for A

= 15.5 dB.

V

4 VIN2 Balanced Differential Input. Biased to VCOM, typically ac-coupled. Input for AV = 12 dB gain, strapped to

VIN1 for A

= 15.5 dB.

V

5, 6, 7, 8 VCC Positive Supply.

9 VCOM Common-Mode Voltage. A voltage applied to this pin sets the common-mode voltage of the input and

output. Typically decoupled to ground with a 0.1 μF capacitor. With no reference applied, input and

output common mode floats to midsupply (VCC/2).

10 VON Balanced Differential Output. Biased to VCOM, typically ac-coupled.

11 VOP Balanced Differential Output. Biased to VCOM, typically ac-coupled.

12 ENBL Enable. Apply positive voltage (1.0 V < ENBL < VCC) to activate device.

13, 14, 15, 16 GND Ground. Connect to low impedance ground.

EP Exposed Pad. Connect to a low impedance thermal and electrical ground plane.

Rev. C | Page 7 of 24

Page 8

ADL5562

A

√

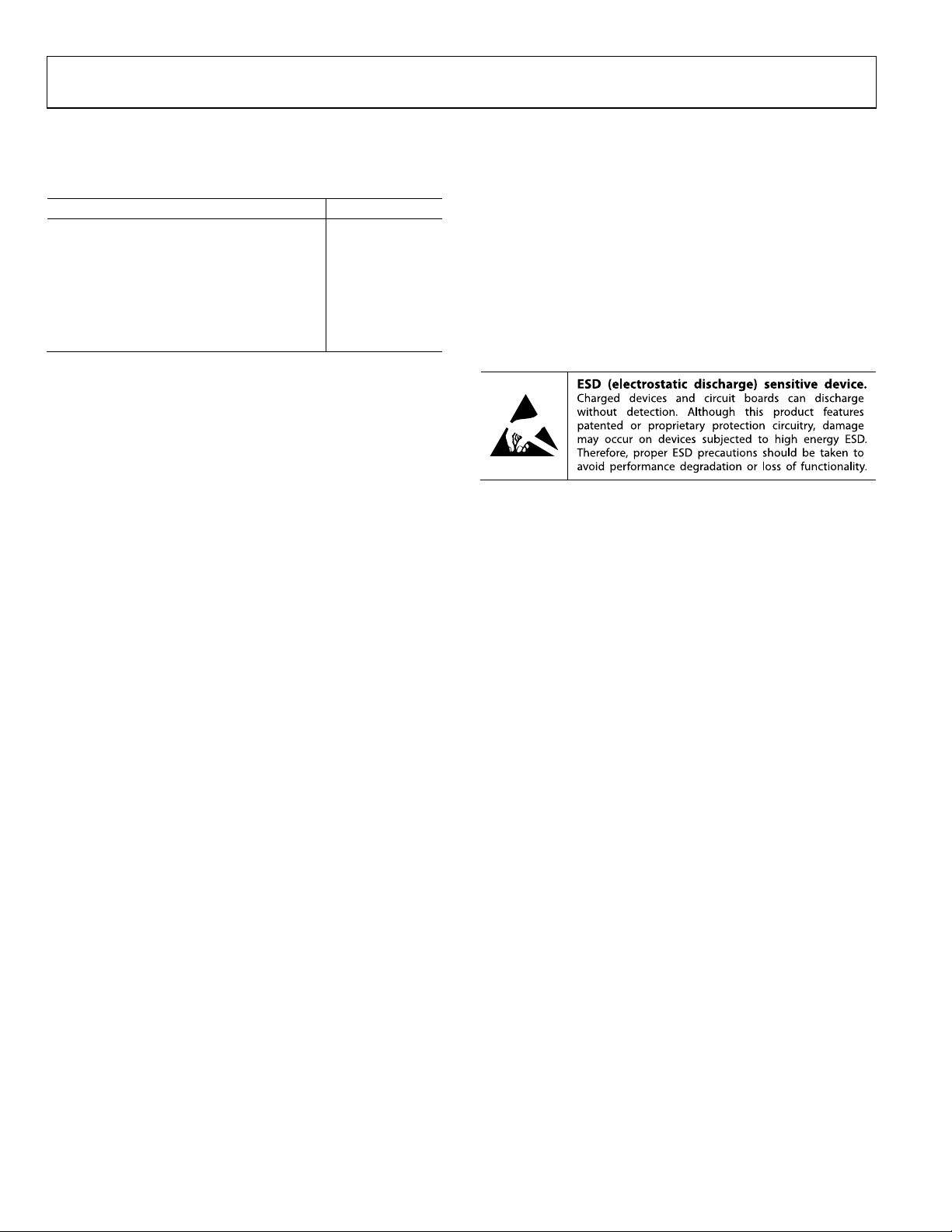

TYPICAL PERFORMANCE CHARACTERISTICS

VCC = 3.3 V, VCOM = 1.65 V, RL = 200 Ω differential, AV = 6 dB, CL = 1 pF differential, f = 140 MHz, T = 25°C.

16

MAXIMUM GAIN

14

12

MID GAIN

–40°C

+25°C

+85°C

25

RL = 200Ω

20

10

GAIN (dB)

8

MINIMUM GAIN

6

4

10M 100M 1G 10G

FREQUENCY (Hz)

Figure 3. Gain vs. Frequency Response for 200 Ω Differential Load,

= 6 dB, AV = 12 dB, and AV = 15.5 dB over Temperature

A

V

20

–40°C

+25°C

+85°C

18

MAXIMUM GAIN

16

14

MID GAIN

12

GAIN (dB)

10

8

MINIMUM GAIN

6

4

10M 100M 1G 10G

FREQUENCY ( Hz)

Figure 4. Gain vs. Frequency Response for 1 kΩ Differential Load,

= 6 dB, AV = 12 dB, and AV = 15.5 dB over Temperature

A

V

16

AV MAXIMUM

A

MID

V

A

MINIMUM

14

V

12

15

OP1dB (dBm)

MIN GAIN +85°C

MIN GAIN +25°C

MIN GAIN –40°C

10

MID GAIN +85°C

MID GAIN +25°C

MID GAIN –40°C

MAX GAIN +85°C

MAX GAIN +25°C

MAX GAIN –40°C

5

0 100 200 300 400 500 600 700 800 900 1000

08003-002

FREQEUNCY (MHz)

8003-016

Figure 6. Output P1dB (OP1dB) vs. Frequency at AV = 6 dB, AV = 12 dB, and

= 15.5 dB over Temperature, 200 Ω Differential Load

A

V

25

20

15

OP1dB (dBm)

10

5

0 100 200 300 400 500 600 700 800 900 1000

08003-003

FREQUENCY (MHz)

RL = 1kΩ

MIN GAIN +85°C

MIN GAIN +25°C

MIN GAIN –40°C

MID GAIN +85°C

MID GAIN +25°C

MID GAIN –40°C

MAX GAIN +85°C

MAX GAIN +25°C

MAX GAIN –40°C

08003-017

Figure 7. Output P1dB (OP1dB) vs. Frequency at AV = 6 dB, AV = 12 dB, and

= 15.5 dB over Temperature, 1 kΩ Differential Load

A

V

8

AV MAXIMUM

A

MID

V

7

A

MINIMUM

Hz)

V

6

10

8

6

NOISE FI GURE (dB)

4

2

0

10 100 1000

FREQUENCY ( MHz)

Figure 5. Noise Figure vs. Frequency at

= 6 dB, AV = 12 dB, and AV = 15.5 dB

A

V

08003-004

5

4

L DENSITY ( nV/

3

2

NOISE SPECTR

1

0

10M 100M 1G

FREQUENCY ( Hz)

Figure 8. Noise Spectral Density vs. Frequency

at A

= 6 dB, AV = 12 dB, and AV = 15.5 dB

V

08003-005

Rev. C | Page 8 of 24

Page 9

ADL5562

10

15

20

25

30

35

40

45

50

55

60

0 50 100 150 200 250

OIP3 (d Bm)

FREQUENCY (MHz)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-018

0

10

20

30

40

50

60

0 50 100 150 200 250

OIP3 (d Bm)

FREQUENCY (MHz)

+85°C

+25°C

–40°C

08003-019

30

35

40

45

50

55

60

0 50 100 150 200 250

OIP3 (d Bm)

FREQUENCY (MHz)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-006

–120

–100

–80

–60

–40

–20

0

–160

–140

–120

–100

–80

–60

–40

0 50 100

150 200 250

IMD3, R

L

= 1kΩ (dBc)

IMD3, R

L

= 200Ω (dBc)

FREQUENCY (MHz)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-020

08003-028

0

5

10

15

20

25

30

35

40

45

50

–2 –1 0 1 2 3 4 5

OIP3 (d Bm)

P

OUT

/TONE (dBm)

–110

–105

–100

–95

–90

–85

–80

–75

–70

0 50 100 150 200 250

IMD (dBc)

FREQUENCY (MHz)

A

V

MAXIMUM

AV MID

AV MINIMUM

08003-007

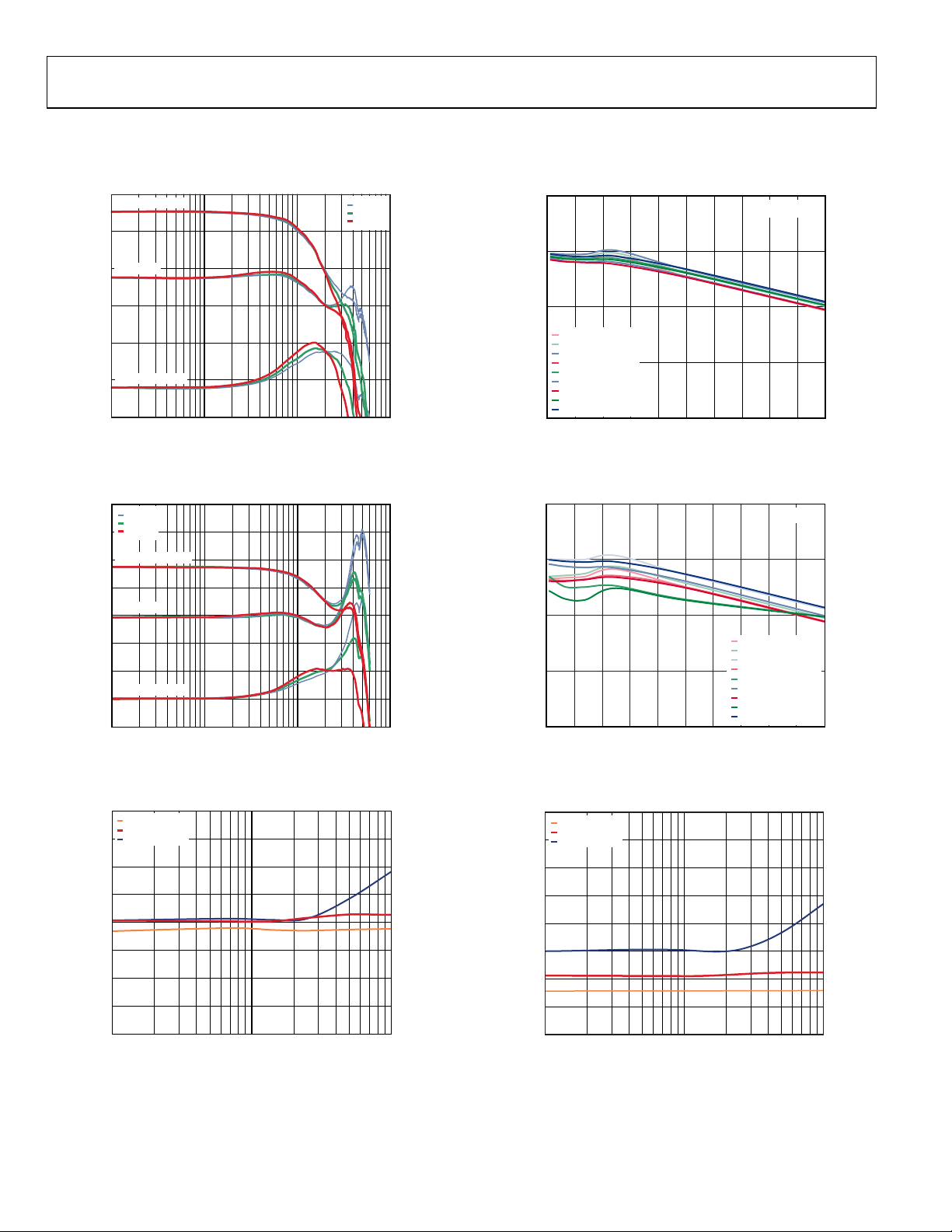

Figure 9. Output Third-Order Intercept at Three Gains, Output Level at 2 V p-p

Composite, R

= 200 Ω

L

Figure 10. Output Third-Order Intercept vs. Frequency, Over Temperature,

Output Level at 2 V p-p Composite, R

= 200 Ω

L

Figure 12. Two-Tone Output IMD vs. Frequency, Output Level

at 2 V p-p Composite, R

Figure 13. Output Third-Order Intercept (OIP3) vs. Power (P

Frequency 140 MHz, A

= 200 Ω and RL = 1 kΩ

L

= 15.5 dB

V

OUT

),

Figure 11. OIP3 vs. Frequency (Single-Ended Input)

Figure 14. IMD vs. Frequency (Single-Ended Input)

Rev. C | Page 9 of 24

Page 10

ADL5562

–120

–100

–80

–60

–40

–20

0

–160

–140

–120

–100

–80

–60

–40

0 50 100 150 200 250

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

FREQUENCY (MHz)

A

V

MAXIMUM

A

V

MID

AV MINIMUM

08003-021

–120

–100

–80

–60

–40

–20

0

–160

–140

–120

–100

–80

–60

–40

0 50 100 150 200 250

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

08003-022

FREQUENCY (MHz)

+85°C

+25°C

–40°C

08003-023

–120

–100

–80

–60

–40

–20

0

–160

–140

–120

–100

–80

–60

–40

0 50 100 150

200 250

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

FREQUENCY (MHz)

+85°C

+25°C

–40°C

–120

–100

–80

–60

–40

–20

0

–160

–140

–120

–100

–80

–60

–40

0 50 100 150 200 250

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

FREQUENCY (MHz)

AV MAXIMUM

A

V

MID

AV MINIMUM

08003-024

08003-029

–100

–90

–80

–70

–60

–50

–40

–30

–20

–2 –1 0 1 2 3 4 5

HARMONIC DISTORTION (dBc)

HD2

HD3

P

OUT

(dBm)

–100

–95

–90

–85

–80

–75

–70

–65

–60

–55

–50

–110

–105

–100

–95

–90

–85

–80

–75

–70

–65

–60

0 50 100 150 200 250

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

FREQUENCY (MHz)

AV MAXIMUM

A

V

MID

A

V

MINIMUM

08003-008

Figure 15. Harmonic Distortion (HD2/HD3) vs. Frequency at AV = 6 dB,

A

= 12 dB, and AV = 15.5 dB, Output Level at 2 V p-p, RL = 200 Ω

V

Figure 16. Harmonic Distortion (HD2/HD3) vs. Frequency,

Three Temperatures, Output Level at 2 V p-p, R

= 200 Ω

L

Figure 18. Harmonic Distortion (HD2/HD3) vs. Frequency at Av = 6 dB,

A

= 12 dB, and Av = 15.5 dB, Output Level at 2 V p-p, RL = 1 kΩ

v

Figure 19. Harmonic Distortion (HD2/HD3) vs. Power (P

Frequency 140 MHz, A

= 15.5 dB

V

OUT

),

Figure 17. Harmonic Distortion (HD2/HD3) vs. Frequency, Over Temperature,

Output Level at 2 V p-p, R

= 1 kΩ

L

Figure 20. Harmonic Distortion (HD2/HD3) vs. Frequency (Sin gle-Ended Input)

Rev. C | Page 10 of 24

Page 11

ADL5562

–130

–120

–110

–100

–90

–80

–70

–60

–100

–90

–80

–70

–60

–50

–40

–30

0 100 200 300 400 500 600 700

800 900 1000

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

R

LOAD

(Ω)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-009

08003-030

TIME (2.5ns/DIV)

VOLTAGE (V)

08003-036

TIME (2.5ns/DIV)

VOLTAGE (V)

2V p-p OUTPUT

–110

–105

–100

–95

–90

–85

–80

–75

–70

–65

–60

–105

–100

–95

–90

–85

–80

–75

–70

–65

–60

–55

1.1 1.2 1.3 1.4 1.5 1.6 1.7 1.8

1.9

HARMONIC DISTORTIO N HD3 ( dBc)

HARMONIC DISTORTIO N HD2 ( dBc)

VCOM (V)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-010

–180

–160

–140

–120

–100

–80

–60

–40

–20

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

0 100 200 300 400 500 600 700 800 900 1000

PHASE (Degrees)

GROUP DELAY (ns)

FREQUENCY (MHz)

A

V

MAXIMUM

AV MID

A

V

MINIMUM

08003-011

0

10

20

30

40

50

60

70

80

30

40

50

60

70

80

90

100

110

10M 100M 1G

CMRR (dB)

CMRR (dB)

FREQUENCY (Hz)

AV MAXIMUM

A

V

MID

AV MINIMUM

RL = 200Ω

RL = 1kΩ

08003-012

Figure 21. Harmonic Distortion (HD2/HD3) vs. R

Figure 22. ENBL Time Domain Response

LOAD

Figure 24. Harmonic Distortion (HD2/HD3) vs. VCOM

Figure 25. Group Delay and Phase vs. Frequency

Figure 23. Large Signal Pulse Response, A

= 15.5 dB

V

Figure 26. Common-Mode Rejection Ratio (CMRR) vs. Frequency

Rev. C | Page 11 of 24

Page 12

ADL5562

–70

–60

–50

–40

–30

–20

–10

0

0 0.5 1.0 1.5 2.0 2.5 3.0

S12 (dB)

FREQUENCY (GHz)

DISABLED

ENABLED

08003-013

1000

900

800

700

600

500

400

300

200

100

0

20

10

0

–10

–20

–30

–40

–50

–60

–70

–80

FREQUENCY (Hz)

10M 100M 1G

IMPEDANCE MAGNITUDE (Ω)

PHASE (Degrees)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-014

IMPEDANCE MAGNITUDE ( Ω)

16

14

12

10

8

6

4

2

0

40

35

30

25

20

15

10

5

0

FREQUENC

Y (Hz)

10M 100M 1G

PHASE (Degrees)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-015

800

700

600

500

400

300

200

100

0

8

7

6

5

4

3

2

1

0

FREQUENCY (Hz)

10M 100M 1G

RESISTANCE (Ω)

CAPACITANCE (pF)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-051

16

10

10M 100M 1G 2G

RESISTANCE (Ω)

INDUCTANCE (n H)

A

V

MAXIMUM

A

V

MID

A

V

MINIMUM

08003-052

Figure 27. Reverse Isolation (S12) vs. Frequency

Figure 30. Input Resistance and Capacitance vs. Frequency

14

12

8

Figure 28. Input Impedance vs. Frequency

Figure 29. Output Impedance vs. Frequency

10

8

6

4

2

0

FREQUENCY (Hz)

6

4

2

0

Figure 31. Output Resistance and Inductance vs. Frequency

Rev. C | Page 12 of 24

Page 13

ADL5562

CIRCUIT DESCRIPTION

BASIC STRUCTURE

The ADL5562 is a low noise, fully differential amplifier/ADC

driver that uses a 3.3 V supply. It provides three gain options

(6 dB, 12 dB, and 15.5 dB) without the need for external resistors

and has wide bandwidths of 2.6 GHz for 6 dB, 2.3 GHz for 12 dB,

and 2.1 GHz for 15.5 dB. Differential input impedance is 400 Ω

for 6 dB, 200 Ω for 12 dB, and 133 Ω for 15.5 dB. It has a

differential output impedance of 10 Ω and a common-mode

adjust voltage of 1.25 V to 1.85 V.

0.1µF

1

/2 R

S

AC

1

/2 R

S

++

0.1µF

100ΩVIP2

200Ω

VIP1

200Ω

VIN1

100Ω

VIN2

Figure 32. Basic Structure

400Ω

400Ω

5Ω

R

L

5Ω

08003-032

The ADL5562 is composed of a fully differential amplifier with

on-chip feedback and feed-forward resistors. The two feed-forward

resistors on each input set this pin-strappable amplifier in three

different gain configurations of 6 dB, 12 dB, and 15.5 dB. The

amplifier is designed to provide high differential open-loop gain

and an output common-mode circuit that enables the user to

change the common-mode voltage from a VCOM pin. The

amplifier is designed to provide superior low distortion at

frequencies up to and beyond 300 MHz with low noise and

low power consumption. The low distortion and noise are

realized with a 3.3 V power supply at 80 mA.

The ADL5562 is very flexible in terms of I/O coupling. It can

be ac-coupled or dc-coupled at the inputs and/or the outputs

within the specified input and output common-mode levels.

The input of the device can be configured as single-ended or

differential with similar distortion performance. Due to the

internal connections between the inputs and outputs, keep the

output common-mode voltage between 1.25 V and 1.85 V for

the best distortion. For a dc-coupled input, the input common

mode should be between 1 V and 2.3 V for the best distortion.

The device has been characterized using 2 V p-p into 200 Ω. If

the inputs are ac-coupled, the input and output common-mode

voltages are set by VCC/2 when no external circuitry is used.

The ADL5562 provides an output common-mode voltage set by

VCOM, which allows driving an ADC directly without external

components, such as a transformer or ac coupling capacitors,

provided the VCOM of the amplifier is within the VCOM of the

ADC. For dc-coupled requirements, the input VCM must be set

by the VCOM pin in all three gain settings.

Rev. C | Page 13 of 24

Page 14

ADL5562

APPLICATIONS INFORMATION

BASIC CONNECTIONS

Figure 33 shows the basic connections for operating the ADL5562.

VCC should be 3.3 V with each supply pin decoupled with at least

one low inductance surface-mount ceramic capacitor of 0.1 μF

placed as close as possible to the device. The VCOM pin (Pin 9)

should also be decoupled using a 0.1 μF capacitor.

The gain of the part is determined by the pin-strappable input

configuration. When Input A is applied to VIP1 and Input B is

applied to VIN1, the gain is 6 dB (minimum gain, see Equation 1

and Equation 2). When Input A is applied to VIP2 and Input B

is applied to VIN2, the gain is 12 dB (middle gain). When

Input A is applied to VIP1 and VIP2 and Input B is applied to

VIN1 and VIN2, the gain is 15.5 dB (maximum gain).

Pin 1 to Pin 4, Pin 10, and Pin 11 are biased at 1/2 VCC above

ground and can be dc-coupled (if within the specified input or

output common-mode voltage levels) or ac-coupled as shown

in Figure 33.

To enable the ADL5562, the ENBL pin must be pulled high.

Pulling the ENBL pin low puts the ADL5562 in sleep mode,

reducing the current consumption to 3 mA at ambient.

ND

VOP

VON

8

VCC

12

11

10

9

R

0.1µF

BALANCED

L

LOAD

8003-033

BALANCED

SOURCE

RS/2

R

S

13

16

ND

G

1

A

0.1µF

C

A

B

/2

0.1µF

VCC

VIP2

2

VIP1

3

VIN1

4

VIN2

VCC

5

10µF

14

15

ND

ND

G

G

ADL5562

VCC

VCC

7

6

0.1µF

G

ENBL

VCOM

VCC

Figure 33. Basic Connections

Rev. C | Page 14 of 24

Page 15

ADL5562

V

V

A

2

A

3

A

A

INPUT AND OUTPUT INTERFACING

The ADL5562 can be configured as a differential-input to

differential-output driver, as shown in Figure 34. The differential

broadband input is provided by the ETC1-1-13 balun transformer,

and the two 34.8 resistors provide a 50 input match for the

three input impedances that change with the variable gain

strapping. The input and output 0.1 µF capacitors isolate the VCC/2

bias from the source and balanced load. The load should equal 200 Ω

to provide the expected ac performance (see the Specifications

section and the Typical Performance Characteristics section).

3.3

ETC1-1-13

50Ω

AC

NOTES

1. FOR 6d B GAIN (A

2. FOR 12d B GAIN (A

3. FOR 15.5dB GAIN (A

AND INPUT B TO BOTH VIN1 AND VI N2.

0.1µF

+

R2

0.1µF

R1

= 2), CONNECT INPUT A TO VIP1 AND INPUT B TO VIN1.

V

= 4), CONNECT INPUT A TO VIP2 AND INPUT B TO VIN2.

V

= 6), CONNECT INPUT A TO BOTH VIP1 AND VIP2

V

VIP2

A

VIP1

VIN1

B

+

VIN2

Figure 34. Differential-Input to Differential-Output Configuration

Table 4. Differential Termination Values for Figure 34

Gain (dB) R1 (Ω) R2 (Ω)

6 28.7 28.7

12 33.2 33.2

15.5 40.2 40.2

The differential gain of the ADL5562 is dependent on the

source impedance and load, as shown in Figure 35.

1

1

/2 R

/2 R

0.1µF

+

S

AC

S

0.1µF

+

VIP1

VIN1

VIN2

100ΩVIP2

200Ω

200Ω

100Ω

Figure 35. Differential Input Loading Circuit

400Ω

400Ω

The differential gain can be determined using the following

formula. The values of R

for each gain configuration are

IN

shown in Table 5.

400

A

V

R

R

L

(1)

R

10

IN

L

Table 5. Values of RIN for Differential Gain

Gain (dB) RIN (Ω)

6 200

12 100

15.5 66.7

0.1µF

R

L

2

R

++

0.1µF

0.1µF

L

2

08003-043

R

L

2

R

L

2

++

8003-044

0.1µF

5Ω

5Ω

Single-Ended Input to Differential Output

The ADL5562 can also be configured in a single-ended input

to differential output driver, as shown in Figure 36. In this

configuration, the gain of the part is reduced due to the application

of the signal to only one side of the amplifier. The strappable

gain values are listed in Table 6 with the required terminations

to match to a 50 Ω source using R1 and R2. Note that R1 must

equal the parallel value of the source and R2. The input and

output 0.1 µF capacitors isolate the VCC/2 bias from the source

and the balanced load. The performance for this configuration

is shown in Figure 11, Figure 14, and Figure 20.

3.3

0.1µF

+

50ΩACR2

R1

NOTES

1. FOR 5.6dB GAIN (

AND INPUT B TO VIN1.

. FOR 11.1dB GAIN (

AND INPUT B TO VIN2.

. FOR 14.1dB GAIN (

VIP1 AND VIP2 AND INPUT B TO BOTH VIN1 AND VIN2.

VIP2

A

VIP1

VIN1

B

VIN2

+

0.1µF

= 1.9), CONNECT INPUT A T O VIP1

V

= 3.6), CONNECT INPUT A TO VIP2

V

= 5.1), CO NNECT INPUT A TO BOT H

V

0.1µF

0.1µF

R

L

2

R

L

2

++

08003-045

Figure 36. Single-Ended Input to Differential Output Configuration

Table 6. Single-Ended Termination Values for Figure 36

Gain (dB) R1 (Ω) R2 (Ω)

5.6 27 60

11.1 29 69

14.1 30 77

The single-ended gain configuration of the ADL5562 is dependent

on the source impedance and load, as shown in Figure 37.

400Ω

0.1µF

5Ω

R

L

2

R

L

0.1µF

5Ω

2

++

VIP1

VIN1

VIN2

100ΩVIP2

200Ω

200Ω

100Ω

400Ω

0.1µF

+

R

R2

S

C

+

0.1µF

R1

Figure 37. Single-Ended Input Loading Circuit

8003-046

Rev. C | Page 15 of 24

Page 16

ADL5562

L

L

X

S

X

S

S

S

IN

V

R

R

R

RR

RR

R

RR

RR

R

A

+

×

+

×

+

×

+

×

+

=

102

2

2

2

400

1

0.1µF

08003-037

1

/

2 RSHUNT

1

/2 R

S

1

/

2

R

S

AC

0.1

µF

1

/2R

SERIES

VIP1

VIN2

VIN1

VIP2

1

/

2RSERIES

1

/

2

R

SHUNT

ADL5562

+

=

IN

SERIES

IN

RR

R

dBIl log20)(

IN

SERIESS

SHUNT

RRR

R

+

−

=

11

1

2

400

50

105

54.9

0.1µF

08003-038

34.8Ω

50Ω

AC

0.1

µF

3.3V

ETC1-1-13

VIN1

VIP1

VIP2

A

B

VIN2

34.8Ω

ADL5562

++

0.1µF

0.1

µF

33Ω

VOP

VON

33Ω

+

+

AD9445

14-BIT ADC

14

VIN+

VIN–

The single-ended gain can be determined using the following

formula. The values of R

are shown in Table 7.

Table 7. Values of R

Gain (dB) RIN (Ω) RX (Ω)

5.6 200 R2 || 3071

11.1 100 R2 || 1791

14.1 66.7 R2 || 1321

1

These values based on a 50 Ω input match.

GAIN ADJUSTMENT AND INTERFACING

The effective gain of the ADL5562 can be reduced using a number

of techniques. A matched attenuator network can reduce the

effective gain; however, this requires the addition of a separate

component that can be prohibitive in size and cost. Instead, a

simple voltage divider can be implemented using the combination

of additional series resistors at the amplifier input and the input

impedance of the ADL5562, as shown in Figure 38. A shunt

resistor is used to match to the impedance of the previous stage.

and RX for each gain configuration

IN

and RX for Single-Ended Gain

IN

(2)

The necessary shunt component, R

impedance, R

, can be expressed as

S

, to match to the source

SHUNT

(4)

The insertion loss and the resultant power gain for multiple

shunt resistor values are summarized in Table 8. The source

resistance and input impedance need careful attention when using

Equation 3 and Equation 4. The reactance of the input impedance

of the ADL5562 and the ac coupling capacitors must be considered

before assuming that they make a negligible contribution.

Table 8. Gain Adjustment Using Series Resistor

Il (dB) RIN (Ω) RS (Ω) R

(Ω) R

SERIES

SHUNT

(Ω)

2 400 50 105 54.9

4 400 50 232 54.9

2 200 50 51.1 61.9

4 200 50 115 59

2 133 50 34.8 71.5

2 400 200 102 332

4 400 200 232 294

2 200 200 51.1 976

4 200 200 115 549

Figure 38. Gain Adjustment Using a Series Resistor

Figure 38 shows a typical implementation of the divider concept

that effectively reduces the gain by adding attenuation at the input.

For frequencies less than 100 MHz, the input impedance of

the ADL5562 can be modeled as a real 133 Ω, 200 Ω, or 400 Ω

resistance (differential) for maximum, middle, and minimum

gains, respectively. Assuming that the frequency is low enough

to ignore the shunt reactance of the input and high enough so

that the reactance of moderately sized ac coupling capacitors

can be considered negligible, the insertion loss, Il, due to the

shunt divider can be expressed as

(3)

4 400 50 232 54.9

2 200 50 51.1 61.9

ADC INTERFACING

The ADL5562 is a high output linearity amplifier that is optimized

for ADC interfacing. There are several options available to the

designer when using the ADL5562. Figure 39 shows a simplified

wideband interface with the ADL5562 driving the AD9445. The

AD9445 is a 14-bit, 125 MSPS ADC with a buffered wideband input.

For optimum performance, the ADL5562 should be driven

differentially using an input balun. Figure 39 uses a wideband 1:1

transmission line balun followed by two 34.8 Ω resistors in parallel

with the three input impedances (which change with the gain

selection of the AD55L62) to provide a 50 Ω differential input

impedance. This provides a wideband match to a 50 Ω source.

The ADL5562 is ac-coupled from the AD9445 to avoid commonmode dc loading. The 33 Ω series resistors help to improve the

isolation between the ADL5562 and any switching currents present at

the analog-to-digital sample-and-hold input circuitry. The AD9445

input presents a 2 kΩ differential load impedance and requires a

2 V p-p differential input swing to reach full scale (VREF = 1 V).

Figure 39. Wideband ADC Interfacing Example Featuring the AD9445

Rev. C | Page 16 of 24

Page 17

ADL5562

08003-026

0 6.25 12.50 18.75 25.00 31.25 37.50 43.75 50.00 56.25 62.50

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

–140

–150

(dBFS)

FREQUENCY (MHz)

ADL5562 DRIVING THE AD9445 14-BIT ADC

GAIN = 6dB

INPUT = 140MHz

SNR = 66.25dBc

SFDR = 87.44dBc

NOISE FLOOR = –109.5dB

FUND = –1.081dBF S

SECOND = –84.54d Bc

THIRD = –84.54d Bc

08003-025

FREQUENCY (MHz)

FIRST POINT = –1.02dBFS

END POINT = –5.69dBFS

MID POI NT = –1.09dBFS

MIN = –5.69dBFS

MAX = –0.88dBF S

0

–1

–2

–3

–4

–5

–6

–7

–8

–9

–10

2.00

81.90 241.70 401.50 561.30 721.10

161.80 321.60 481.40 641.20 801.00

(dBFS)

08003-039

105Ω

L5

105Ω

AD9246

AD9640

AD6655

1nF

L1C2L3

1nF

L1 L3

C4

CML

ADL5562

4Ω

4Ω

140

33

3.3

47

27

33

120

This circuit provides variable gain, isolation, and source matching

for the AD9445. Using this circuit with the ADL5562 in a gain

of 6 dB, an SFDR performance of 87 dBc is achieved at 140 MHz,

and a −3 dB bandwidth of 760 MHz, as indicated in Figure 40

and Figure 41.

Figure 40. Measured Single-Tone Performance of the

Circuit in Figure 39 for a 100 MHz Input Signal

The wideband frequency response is an advantage in broadband applications, such as predistortion receiver designs and

instrumentation applications. However, by designing for a wide

analog input frequency range, the cascaded SNR performance is

somewhat degraded due to high frequency noise aliasing into

the wanted Nyquist zone.

An alternative narrow-band approach is presented in Figure 42.

By designing a narrow band-pass antialiasing filter between the

ADL5562 and the target ADC, the output noise of the ADL5562

outside of the intended Nyquist zone can be attenuated, helping

to preserve the available SNR of the ADC. In general, the SNR

improves several decibels when including a reasonable order antialiasing filter. In this example, a low loss 1:1 input transformer is

used to match the ADL5562 balanced input to a 50 Ω unbalanced

source, resulting in minimum insertion loss at the input.

Figure 42 is optimized for driving some of the Analog Devices

popular unbuffered ADCs, such as the AD9246, AD9640,

and AD6655. Table 9 includes antialiasing filter component

recommendations for popular IF sampling center frequencies.

Inductor L5 works in parallel with the on-chip ADC input

capacitance and a portion of the capacitance presented by C4 to

form a resonant tank circuit. The resonant tank helps to ensure

that the ADC input looks like a real resistance at the target center

frequency. The L5 inductor shorts the ADC inputs at dc, which

introduces a zero into the transfer function. In addition, the ac

coupling capacitors introduce additional zeros into the transfer

function. The final overall frequency response takes on a bandpass characteristic, helping to reject noise outside of the intended

Nyquist zone. Table 9 provides initial suggestions for prototyping

purposes. Some empirical optimization may be needed to help

compensate for actual PCB parasitics.

Figure 41. Measured Frequency Response of the Wideband

ADC Interface Depicted in Figure 39

Table 9. Interface Filter Recommendations for Various IF Sampling Frequencies

Center Frequency (MHz) 1 dB Bandwidth (MHz) L1 (nH) C2 (pF) L3 (nH) C4 (pF) L5 (nH)

96 30 3.3 47 27 75 100

170 32 3.3 56 27 22 110

211 33 3.3 47 27 18 56

Figure 42. Narrow-Band IF Sampling Solution for an Unbuffered ADC Application

Rev. C | Page 17 of 24

Page 18

ADL5562

0.1µF

0.1µF

0.1µF

0.1µF

ADL5562

VIP2

VIP1

VIN1

VOP

VON

VIN2

R6

R5

R4

R3

R2

R1

R8

R7

R10

R9

ETC1-1-13

ETC1-1-13

SPECTRUM

ANALYZER

08003-034

15.5

40.2

40.2 0 0 0 0

RL (Ω)

R7 (Ω)

R8 (Ω)

R9 (Ω)

R10 (Ω)

ADL5562

VIP2

VIP1

VIN1

VOP

VON

VIN2

R6

R5

R4

R3

R2

R1

R8

R7

R10

R9

PORT 1

PORT 3

PORT 2

PORT 4

08003-035

LAYOUT CONSIDERATIONS

High-Q inductive drives and loads, as well as stray transmission

line capacitance in combination with package parasitics, can

potentially form a resonant circuit at high frequencies, resulting

in excessive gain peaking or possible oscillation. If RF transmission

lines connecting the input or output are used, they should be

designed such that stray capacitance at the input/output pins is

minimized. In many board designs, the signal trace widths

should be minimal where the driver/receiver is more than oneeighth of the wavelength from the amplifier. This nontransmission

line configuration requires that underlying and adjacent ground

and low impedance planes be dropped from the signal lines

Figure 43. General Purpose Characterization Circuit

Table 10. Gain Setting and Input Termination Components for Figure 43

AV (dB) R1 (Ω) R2 (Ω) R3 (Ω) R4 (Ω) R5 (Ω) R6 (Ω)

6 29 29 Open 0 0 Open

12 33 33 0 Open Open 0

Table 11. Output Matching Network for Figure 43

200 84.5 84.5 34.8 34.8

1 k 487 487 25 25

Figure 44. Differential Characterization Circuit Using Agilent E8357A 4-Port PNA

Table 12. Gain Setting and Input Termination Components for Figure 44

AV (dB) R1 (Ω) R2 (Ω) R3 (Ω) R4 (Ω) R5 (Ω) R6 (Ω)

6 67 67 Open 0 0 Open

12 100 100 0 Open Open 0

15.5 200 200 0 0 0 0

Table 13. Output Matching Network for Figure 44

RL (Ω) R7 (Ω) R8 (Ω) R9 (Ω) R10 (Ω)

200 50 50 Open Open

1 k 475 475 61.9 61.9

Rev. C | Page 18 of 24

Page 19

ADL5562

C3

10µFC40.1µF

C5

0.1µFC60.1µFC70.1µF

C8

0.1µF

C13

0.1µF

C11

0.1µF

VPOS

08003-040

R9

34.8Ω

R11

OPEN

J3

R10

34.8Ω

R8

84.5Ω

C10

0.01µF

C9

0.01µF

P1

T2

J2

AGND

VPOS

GND

R7

84.5Ω

ENBL

ADL5562

9

10

11

12

4

3

2

1

16 15 14 13

5 6 7 8

GND GND GND GND

VCC

VIN1

VIN2

VIP2

VIP1

VON

VOCM

ENBL

VOP

VCC VCC VCC

C12

0.1µF

J1

T1

R1

40.2Ω

R2

40.2Ω

R4

0Ω

R3

0Ω

R5

0Ω

R6

0Ω

C1

0.01µF

C2

0.01µF

VPOS, GND

Ground and supply vector pins.

VPOS, GND = installed

SOLDERING INFORMATION

On the underside of the chip scale package, there is an exposed

compressed paddle. This paddle is internally connected to the

ground of the chip. Solder the paddle to the low impedance

ground plane on the PCB to ensure the specified electrical

performance and to provide thermal relief. To further reduce

thermal impedance, it is recommended that the ground planes

on all layers under the paddle be stitched together with vias.

EVALUATION BOARD

Figure 45 shows the schematic of the ADL5562 evaluation board.

The board is powered by a single supply in the 3 V to 3.6 V range.

The power supply is decoupled by 10 µF and 0.1 µF capacitors.

Table 14 details the various configuration options of the evaluation

board. Figure 46 and Figure 47 show the component and circuit

layouts of the evaluation board.

To realize the minimum gain (6 dB into a 200 Ω load), Input 1

(VIN1 and VIP1) must be used by installing 0 Ω resistors at R3

and R4, leaving R5 and R6 open. R1 and R2 must be 33 Ω for a

50 Ω input impedance.

Likewise, driving Input 2 (VIN2 and VIP2) realizes the middle

gain (12 dB into a 200 Ω load) by installing 0 Ω at R5 and R6

and leaving R3 and R4 open. R1 and R2 must be 29 Ω for a

50 Ω input impedance.

For the maximum gain (15.5 dB into a 200 Ω load), both inputs

are driven by installing 0 Ω resistors at R3, R4, R5, and R6. R1

and R2 must be 40.2 Ω for a 50 Ω input impedance.

The balanced input and output interfaces are converted to

single ended with a pair of baluns (M/A-COM ETC1-1-13).

The balun at the input, T1, provides a 50 Ω single-ended-todifferential transformation. The output balun, T2, and the

matching components are configured to provide a 200 Ω to 50 Ω

impedance transformation with an insertion loss of about 17 dB.

Table 14. Evaluation Board Configuration Options

Component Description Default Condition

C3, C4, C5,

C6, C7, C11

J1, R1, R2, R3,

R4, R5, R6, C1,

C2, C12, T1

J3, R7, R8, R9,

R10, R11, C9,

C10, C13, T2

ENBL, P1, C8 Device enable. C8 is a bypass capacitor. When the P1 jumper is set toward the VPOS label,

Figure 45. Evaluation Board Schematic

Power supply decoupling. The supply decoupling consists of a 10 µF capacitor (C3)

to ground. C4 to C7 are bypass capacitors. C11 ac couples VREF to ground.

Input interface. The SMA labeled J1 is the input. T1 is a 1-to-1 impedance ratio balun

to transform a single-ended input into a balanced differential signal. C1 and C2

provide ac coupling. C12 is a bypass capacitor. R1 and R2 provide a differential 50 Ω

input termination. R3 to R6 are used to select the input for the pin-strappable gain.

Maximum gain: R3, R4, R5, R6 = 0 Ω; and R1, R2 = 40.2 Ω. Middle gain: R5, R6 = 0 Ω; and R3,

R4 = open; R1, R2 = 33 Ω. Minimum gain: R3, R4 = 0 Ω; and R5, R6 = open; R1, R2 = 29 Ω.

Output interface. The SMA labeled J3 is the output. T2 is a 1-to-1 impedance ratio

balun to transform a balanced differential signal to a single-ended signal. C13 is a

bypass capacitor. R7, R8, R9, and R10 are provided for generic placement of matching

components. The evaluation board is configured to provide a 200 Ω to 50 Ω impedance

transformation with an insertion loss of 17 dB. C9 and C10 provide ac coupling.

the ENBL pin is connected to the supply, enabling the device. In the opposite direction,

toward the GND label, the ENBL pin is grounded, putting the device in power-down mode.

Rev. C | Page 19 of 24

C3 = 10 µF (Size D),

C4, C5, C6, C7, C11 = 0.1 µF (Size 0402)

J1 = installed,

R1, R2 = 40.2 Ω (Size 0402),

R3, R4, R5, R6 = 0 Ω (Size 0402),

C1, C2 = 0.01 µF (Size 0402),

C12 = 0.1 µF (Size 0402)

T1 = ETC1-1-13 (M/A-COM)

J3 = installed,

R7, R8 = 84.5 Ω (Size 0402),

R9, R10 = 34.8 Ω (Size 0402),

R11 = open (Size 0402),

C9, C10 = 0.01 µF (Size 0402),

C13 = 0.1 µF (Size 0402)

T2 = ETC1-1-13 (M/A-COM)

ENBL, P1= installed,

C8 = 0.1 µF (Size 0402)

Page 20

ADL5562

08003-041

08003-042

Figure 46. Layout of Evaluation Board, Component Side

Figure 47. Layout of Evaluation Board, Circuit Side

Rev. C | Page 20 of 24

Page 21

ADL5562

1

0.50

BSC

0.60 MAX

PIN 1

INDICATOR

1.50 REF

0.50

0.40

0.30

0.25 MIN

0.45

2.75

BSC SQ

TOP

VIEW

12° MAX

0.80 MAX

0.65 TYP

SEATING

PLANE

PIN 1

INDICATOR

1.00

0.85

0.80

0.30

0.23

0.18

0.05 MAX

0.02 NOM

0.20 REF

3.00

BSC SQ

*

1.45

1.30 SQ

1.15

EXPOSED

PAD

16

5

13

8

9

12

4

(BOTTOM VIEW)

*

COMPLIANT

TO

JEDEC STANDARDS MO-220-VEED-2

EXCEPT FOR EXPOSED PAD DIMENSION.

072208-A

FOR PROP E R CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CO NFIGURATI ON AND

FUNCTIO N DE S CRIPTIONS

SECTION OF THIS DATA SHEET.

ADL5562-EVALZ

Evaluation Board

OUTLINE DIMENSIONS

Figure 48. 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

3 mm × 3 mm Body, Very Thin Quad

(CP-16-2)

Dimensions shown in millimeters

ORDERING GUIDE

Model1

Range Package Description

ADL5562ACPZ-R7 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ], 7” Tape and Reel CP-16-2 Q1Q 1,500

ADL5562ACPZ-WP −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ], Waffle Pack CP-16-2 Q1Q 50

Temperature

1

Z = RoHS Compliant Part.

Package

Option Branding

Ordering

Quantity

Rev. C | Page 21 of 24

Page 22

ADL5562

NOTES

Rev. C | Page 22 of 24

Page 23

ADL5562

NOTES

Rev. C | Page 23 of 24

Page 24

ADL5562

©2009–2011 Analog Devices, Inc. All rights reserved. Trademarks and

NOTES

registered trademarks are the property of their respective owners.

D08003-0-7/11(C)

Rev. C | Page 24 of 24

Loading...

Loading...