Page 1

20 MHz to 1.0 GHz IF Gain Block

FEATURES

Fixed gain of 16 dB

Operation from 20 MHz to 1.0 GHz

Input and output internally matched to 50 Ω

Integrated bias control circuit

OIP3

45.5 dBm at 190 MHz

45.5 dBm at 380 MHz

Noise figure

3.2 dB at 190 MHz

3.3 dB at 380 MHz

P1dB of 18.9 dBm at 190 MHz

Single 5 V power supply

Low quiescent current of 97 mA

MSL-1 rated SOT-89 package

ESD rating of ±2 kV (Class 2)

Pin-compatible with the 20 dB gain

GENERAL DESCRIPTION

The ADL5535 is a 16 dB linear amplifier that operates at

frequencies up to 1 GHz. The device can be used in a wide

variety of cellular, CATV, military, and instrumentation

equipment.

The ADL5535 provides the highest dynamic range available

from an internally matched IF gain block. This is accomplished

by providing extremely low noise figures and very high OIP3

specifications simultaneously across the entire 1 GHz frequency

range. The ADL5535 also provides extremely flat gain and P1dB

over frequency, which are stable over temperature, power supply,

and from device to device.

The device is internally matched to 50 at the input and output,

making the ADL5535 very easy to implement in a wide variety

of applications. Only input/output ac coupling capacitors, power

supply decoupling capacitors, and an external inductor are

required for operation.

ADL5536

ADL5535

FUNCTIONAL BLOCK DIAGRAM

GND

(2)

ADL5535

BIAS

1 2

RFIN GND RFOUT

Figure 1.

The ADL5535 is fabricated on a GaAs HBT process and has an

ESD rating of ±2 kV (Class 2). The device is assembled in an

MSL-1 rated SOT-89 package that uses an exposed paddle for

excellent thermal impedance.

The ADL5535 consumes only 97 mA on a single 5 V supply and

is fully specified for operation from −40°C to +85°C.

The ADL5535 is also pin-compatible with the 20 dB gain

ADL5536. Fully populated evaluation boards are available

for each amplifier.

3

08674-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

Page 2

ADL5535

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Typical Scattering Parameters (S-Parameters) ......................... 5

Absolute Maximum Ratings ............................................................ 6

ESD Caution .................................................................................. 6

Pin Configuration and Function Descriptions ............................. 7

Typical Performance Characteristics ............................................. 8

REVISION HISTORY

4/10—Revision 0: Initial Version

Basic Connections .......................................................................... 10

Soldering Information and Recommended PCB

Land Pattern ................................................................................ 10

ACPR Performance ........................................................................ 11

Error Vector Magnitude (EVM) Performance ........................... 11

ADC Driving Application ............................................................. 12

Evaluation Board ............................................................................ 13

Outline Dimensions ....................................................................... 14

Ordering Guide .......................................................................... 14

Rev. 0 | Page 2 of 16

Page 3

ADL5535

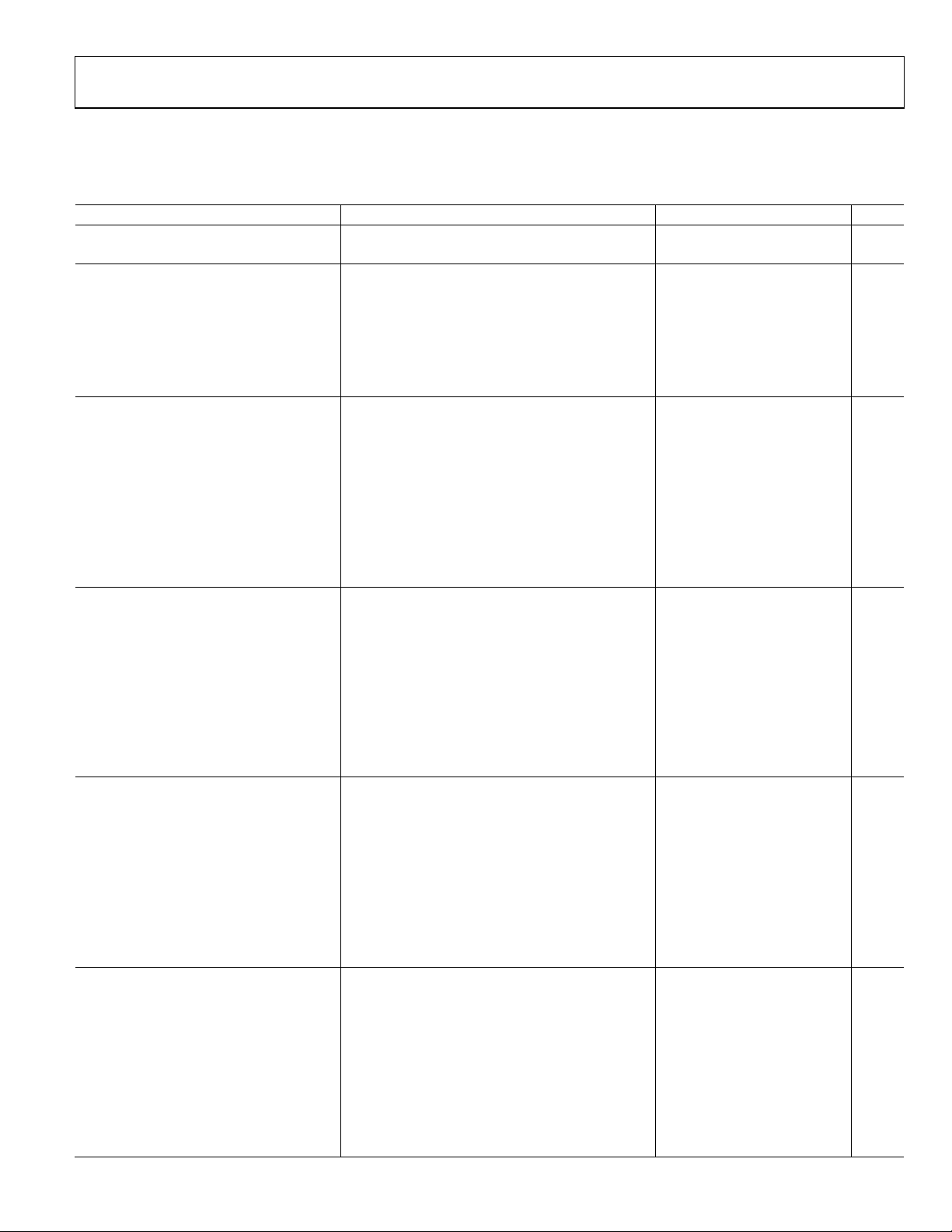

SPECIFICATIONS

VCC = 5 V and TA = 25°C, unless otherwise noted.

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

OVERALL FUNCTION

Frequency Range 20 1000 MHz

FREQUENCY = 20 MHz

Gain 16.7 dB

Output 1 dB Compression Point (P1dB) 17.7 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −59.5 dBc

OUT

= 0 dBm −93 dBc

OUT

Noise Figure 3.0 dB

FREQUENCY = 70 MHz

Gain 16.5 dB

vs. Frequency ±50 MHz ±0.33 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.16 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.04 dB

Output 1 dB Compression Point (P1dB) 18.9 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −64 dBc

OUT

= 0 dBm −93 dBc

OUT

Noise Figure 3.0 dB

FREQUENCY = 190 MHz

Gain 15.2 16.1 17.0 dB

vs. Frequency ±50 MHz ±0.06 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.17 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.04 dB

Output 1 dB Compression Point (P1dB) 17.8 18.9 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −60.2 dBc

OUT

= 0 dBm −84.3 dBc

OUT

Noise Figure 3.2 dB

FREQUENCY = 380 MHz

Gain 15.0 15.8 16.5 dB

vs. Frequency ±50 MHz ±0.08 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.17 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.05 dB

Output 1 dB Compression Point (P1dB) 17.8 18.9 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −61.9 dBc

OUT

= 0 dBm −75 dBc

OUT

Noise Figure 3.3 dB

FREQUENCY = 748 MHz

Gain 15.2 dB

vs. Frequency ±50 MHz ±0.10 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.20 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.06 dB

Output 1 dB Compression Point (P1dB) 18.9 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −52.6 dBc

OUT

= 0 dBm −68 dBc

OUT

Noise Figure 3.2 dB

Rev. 0 | Page 3 of 16

) = 3 dBm per tone 41.5 dBm

OUT

) = 3 dBm per tone 43.5 dBm

OUT

) = 3 dBm per tone 45.5 dBm

OUT

) = 3 dBm per tone 45.5 dBm

OUT

) = 3 dBm per tone 42.0 dBm

OUT

Page 4

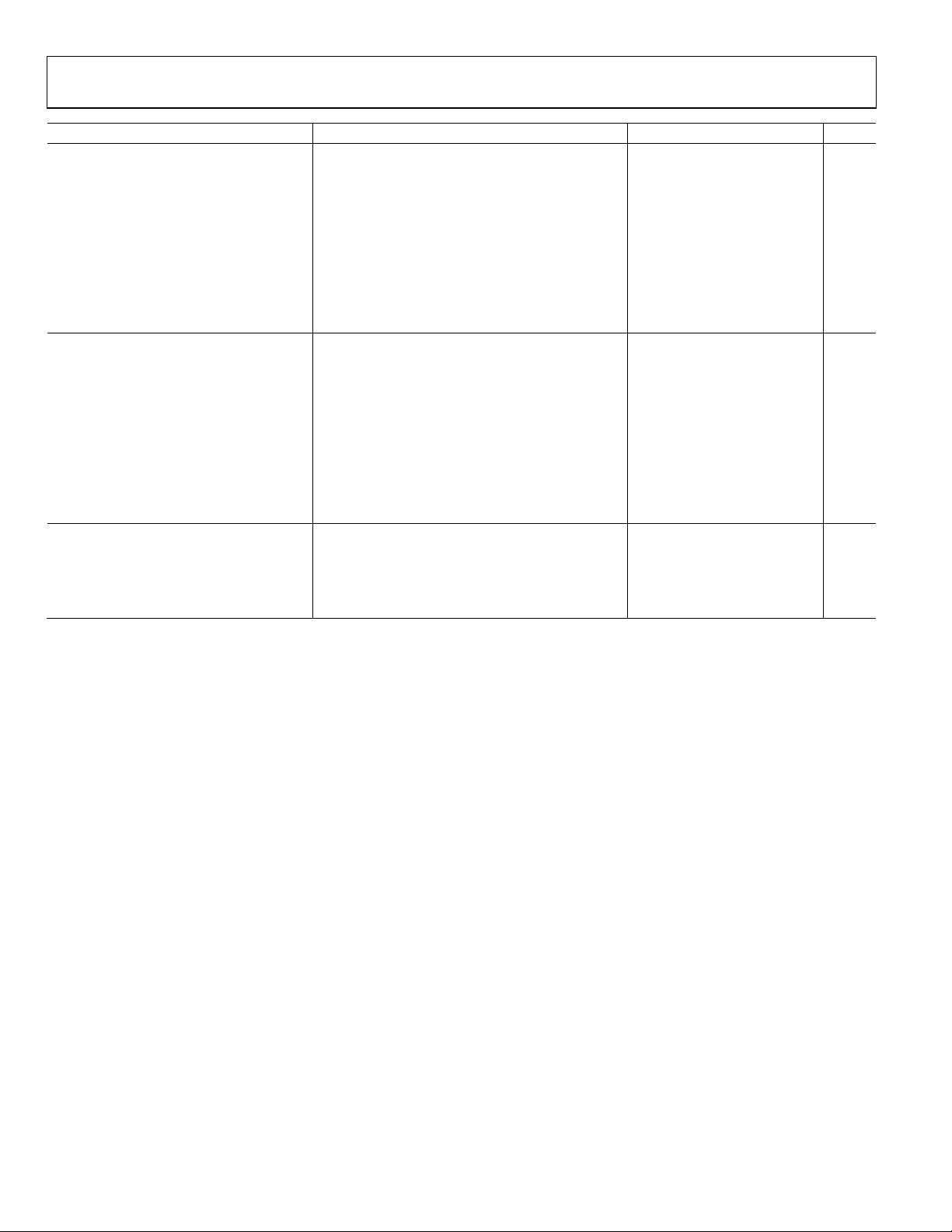

ADL5535

Parameter Test Conditions/Comments Min Typ Max Unit

FREQUENCY = 900 MHz

Gain 15.1 dB

vs. Frequency ±50 MHz ±0.11 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.20 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.06 dB

Output 1 dB Compression Point (P1dB) 19.0 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −59.3 dBc

OUT

= 0 dBm −64.6 dBc

OUT

Noise Figure 3.2 dB

FREQUENCY = 1000 MHz

Gain 14.9 dB

vs. Frequency ±50 MHz ±0.11 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.21 dB

vs. Supply Voltage 4.75 V to 5.25 V ±0.07 dB

Output 1 dB Compression Point (P1dB) 18.9 dBm

Output Third-Order Intercept (OIP3) ∆f = 1 MHz, output power (P

Second Harmonic P

Third Harmonic P

= 0 dBm −51.4 dBc

OUT

= 0 dBm −63.1 dBc

OUT

Noise Figure 3.3 dB

POWER INTERFACE

Supply Voltage (VCC) 4.5 5.0 5.5 V

Supply Current 97 115 mA

vs. Temperature −40°C ≤ TA ≤ +85°C ±2.0 mA

Power Dissipation VCC = 5 V 0.5 W

) = 3 dBm per tone 40.0 dBm

OUT

) = 3 dBm per tone 39.5 dBm

OUT

Rev. 0 | Page 4 of 16

Page 5

ADL5535

TYPICAL SCATTERING PARAMETERS (S-PARAMETERS)

VCC = 5 V, TA = 25°C, and the effects of the test fixture have been de-embedded up to the pins of the device.

Table 2.

Frequency

(MHz)

20 −13.03 −112.72 17.11 167.18 −19.70 +10.45 −14.78 −125.49

70 −18.32 −152.93 16.33 171.17 −19.67 +0.77 −15.85 −161.12

120 −19.04 −161.05 16.22 169.68 −19.66 −1.99 −15.99 −166.87

190 −19.31 −163.81 16.16 166.09 −19.65 −4.89 −15.97 −168.23

240 −19.35 −163.54 16.10 163.36 −19.65 −6.74 −15.91 −167.75

290 −19.26 −162.62 16.08 160.44 −19.65 −8.54 −15.81 −166.89

340 −19.24 −161.59 16.01 157.37 −19.66 −10.20 −15.70 −166.07

390 −19.12 −158.71 15.94 154.60 −19.65 −11.99 −15.53 −164.46

440 −18.88 −157.70 15.91 151.65 −19.65 −13.65 −15.28 −163.07

490 −18.58 −157.00 15.84 148.72 −19.69 −15.34 −15.02 −162.82

540 −18.35 −156.08 15.80 145.67 −19.71 −16.97 −14.80 −162.40

590 −18.12 −154.28 15.71 142.80 −19.70 −18.60 −14.58 −161.54

640 −17.82 −153.50 15.67 139.94 −19.71 −20.26 −14.31 −161.17

690 −17.57 −152.78 15.59 136.89 −19.73 −21.87 −14.07 −160.95

740 −17.30 −151.90 15.51 134.11 −19.74 −23.49 −13.82 −160.76

790 −17.04 −151.31 15.44 131.17 −19.75 −25.11 −13.58 −160.71

840 −16.76 −150.77 15.35 128.31 −19.77 −26.74 −13.34 −160.76

900 −16.41 −150.20 15.26 125.01 −19.79 −28.65 −13.05 −160.99

950 −16.15 −149.94 15.17 122.08 −19.80 −30.29 −12.82 −161.31

1000 −15.87 −149.69 15.08 119.42 −19.82 −31.88 −12.59 −161.67

1050 −15.60 −149.72 15.00 116.58 −19.84 −33.51 −12.38 −162.13

1100 −15.35 −149.61 14.89 113.89 −19.86 −35.10 −12.17 −162.71

1150 −15.08 −149.74 14.81 111.22 −19.88 −36.69 −11.97 −163.25

1200 −14.86 −149.84 14.70 108.43 −19.90 −38.29 −11.79 −163.86

1250 −14.58 −149.97 14.61 105.97 −19.92 −39.90 −11.59 −164.52

1300 −14.35 −150.33 14.52 103.20 −19.94 −41.52 −11.41 −165.22

1350 −14.11 −150.67 14.41 100.66 −19.96 −43.13 −11.25 −166.05

1400 −13.90 −151.10 14.32 98.10 −19.99 −44.68 −11.08 −166.79

1450 −13.69 −151.43 14.21 95.51 −20.02 −46.23 −10.93 −167.47

1500 −13.46 −151.86 14.11 93.03 −20.04 −47.82 −10.78 −168.33

1550 −13.26 −152.41 14.02 90.50 −20.06 −49.37 −10.63 −169.12

Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°)

S11 S21 S12 S22

Rev. 0 | Page 5 of 16

Page 6

ADL5535

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage, VCC 6.5 V

Input Power (Referred to 50 Ω) 20 dBm

Internal Power Dissipation (Paddle Soldered) 650 mW

θ

(Junction to Air) 30.7°C/W

JA

θ

(Junction to Paddle) 5.0°C/W

JC

Maximum Junction Temperature 150°C

Lead Temperature (Soldering, 60 sec) 240°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 6 of 16

Page 7

ADL5535

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

RFIN

1

GND

RFOUT

NOTES

1. THE EXPOSED PADDLE I S

INTERNALL Y CONNECTED TO GND

AND MUST BE SOLDERED TO A LOW

IMPEDANCE GRO UND PLANE.

ADL5535

2

TOP VIEW

(Not to S cale)

3

(2)

GND

08674-002

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 RFIN RF Input. This pin requires a dc blocking capacitor.

2 GND Ground. Connect this pin to a low impedance ground plane.

3 RFOUT

RF Output and Supply Voltage. A dc bias is provided to this pin through an inductor that is connected to the

external power supply. The RF path requires a dc blocking capacitor.

(2) Exposed Paddle

Exposed Paddle. The exposed paddle is internally connected to GND and must be soldered to a low impedance

ground plane.

Rev. 0 | Page 7 of 16

Page 8

ADL5535

–

TYPICAL PERFORMANCE CHARACTERISTICS

50

45

40

35

30

25

20

15

10

NF, GAIN, P1dB, OIP3 (dB, dBm)

5

0

0 100 200 300 400 500 600 700 800 900 1000

OIP3

P1dB

GAIN

NF

FREQUENCY (MHz)

Figure 3. Noise Figure, Gain, P1dB, and OIP3 vs. Frequency

19.2

19.0

18.8

18.6

18.4

18.2

18.0

P1dB (dBm)

17.8

17.6

17.4

17.2

17.0

0 100 200 300 400 500 600 700 800 900 1000

8674-003

+25°C

FREQUENCY ( M Hz )

–40°C

+85°C

+25°C

–40°C

+85°C

Figure 6. P1dB and OIP3 vs. Frequency and Temperature

54

52

50

48

46

44

42

OIP3 (dBm)

40

38

36

34

32

8674-006

17.0

16.5

16.0

15.5

GAIN (dB)

15.0

14.5

14.0

0 100 200 300 400 500 600 700 800 900 1000

–40°C

+25°C

+85°C

FREQUENCY ( MHz)

Figure 4. Gain vs. Frequency and Temperature

4

–6

–8

–10

–12

–14

–16

–18

S-PARAMETERS (dB)

–20

–22

–24

0 100 200 300 400 500 600 700 800 900 1000

S11

FREQUENCY (M Hz )

S22

S12

Figure 5. Input Return Loss (S11), Output Return Loss (S22), and

Reverse Isolation (S12) vs. Frequency

48

46

20MHz

70MHz

44

190MHz

380MHz

42

40

38

36

OIP3 (dBm)

34

32

30

28

–8 –6 –4 –2 0 2 4 6 8 10 12 14

08674-004

Figure 7. OIP3 vs. Output Power (P

4.8

4.6

4.4

4.2

4.0

3.8

3.6

3.4

3.2

3.0

NOISE FI GURE (dB)

2.8

2.6

2.4

2.2

2.0

08674-005

+25°C

0 100 200 300 400 500 600 700 800 900 1000

748MHz

900MHz

1000MHz

P

PER TONE (d Bm)

OUT

+85°C

FREQUENCY (M Hz )

) and Frequency

OUT

–40°C

08674-007

08674-023

Figure 8. Noise Figure vs. Frequency and Temperature

Rev. 0 | Page 8 of 16

Page 9

ADL5535

–

30

40

–40

–50

SECOND HARMONIC

–60

–70

–80

–90

SECOND AND THIRD HARMO NICS (dBc)

–100

0 100 200 300 400 500 600 700 800 900 1000

THIRD HARMONIC

FREQUENCY (MHz)

Figure 9. Single-Tone Harmonics vs. Frequency, P

100

90

80

70

60

50

40

PERCENTAGE (%)

30

20

10

0

15.5 15.7 15.9 16.1 16.3 16.5 16.7

GAIN (dB)

Figure 10. Gain Distribution at 190 MHz

= 0 dBm

OUT

35

30

25

20

15

PERCENTAGE (%)

10

5

0

8674-009

08674-010

40 41 42 43 44 45 46 47 48 49 50 51 52

OIP3 (dBm)

Figure 12. OIP3 Distribution at 190 MHz, P

70

60

50

40

30

PERCENTAGE (%)

20

10

0

2.5 2.7 2.9 3.1 3.3 3.5 3.7 3.9

NOISE FI GURE (dB)

= 3 dBm

OUT

08674-012

08674-013

Figure 13. Noise Figure Distribution at 190 MHz

30

25

20

15

10

PERCENTAGE (%)

5

0

18.3 18.5 18.7 18.9 19.1 19.3 19.5

P1dB (dBm)

Figure 11. P1dB Distribution at 190 MHz

8674-011

115

110

105

100

95

90

85

SUPPLY CURRENT (mA)

80

75

70

–40 –30 –20 –10 0

Figure 14. Supply Current vs. Temperature

5.25V

5.00V

4.75V

10

30

20

40

TEMPERATURE (°C)

50 60

80 90

70

08674-014

Rev. 0 | Page 9 of 16

Page 10

ADL5535

VCC

BASIC CONNECTIONS

The basic connections for operating the ADL5535 are shown in

Figure 15. Recommended components are listed in Tabl e 5. The

input and output should be ac-coupled with appropriately sized

capacitors (device characterization was performed with 0.1 F

capacitors). A 5 V dc bias is supplied to the amplifier through

the bias inductor connected to RFOUT (Pin 3). The bias voltage

should be decoupled using a 1 µF capacitor, a 1.2 nF capacitor,

and a 68 pF capacitor.

RFIN

0.1µF

GND

(2)

GND

ADL5535

2

1

RFIN

3

GND

RFOUT

Figure 15. Basic Connections

C6

1µF

C5

1.2nF

C4

68pF

L1

470nH

C2C1

0.1µF

RFOUT

08674-015

SOLDERING INFORMATION AND RECOMMENDED PCB LAND PATTERN

Figure 16 shows the recommended land pattern for the ADL5535.

To minimize thermal impedance, the exposed paddle on the

package underside, along with Pin 2, should be soldered to a

ground plane. If multiple ground layers exist, they should be

stitched together using vias. For more information about land

pattern design and layout, refer to the AN-772 Application

Note, A Design and Manufacturing Guide for the Lead Frame

Chip Scale Package (LFCSP).

1.80mm

3.48mm

5.56mm

0.20mm

0.86mm

0.62mm

1.27mm

1.50mm

3.00mm

08674-016

Figure 16. Recommended Land Pattern

Table 5. Recommended Components for Basic Connections

Frequency C1 C2 L1 C4 C5 C6

20 MHz to 1000 MHz 0.1 µF 0.1 µF 470 nH (Coilcraft 0603LS-NX or equivalent) 68 pF 1.2 nF 1 µF

Rev. 0 | Page 10 of 16

Page 11

ADL5535

–

–

ACPR PERFORMANCE

Figure 17 shows a plot of the adjacent channel power ratio

(ACPR) vs. P

for the ADL5535. The signal type used is a

OUT

single wideband code division multiple access (W-CDMA)

carrier (Test Model 1-64). This signal is generated by a very

low ACPR source. ACPR is measured at the output by a high

dynamic range spectrum analyzer that incorporates an instrument noise-correction function. At an output power level of

+8 dBm, ACPR is still very low at −65 dBc, making the device

suitable for use in driver applications.

35

–40

–45

–50

–55

–60

190MHz SOURCE POWER

OUTPUT REFERRED

–65

ACPR (dBc)

–70

–75

–80

380MHz SOURCE POW E R OUT P UT REF E RRED

–85

–5–3–1135791113

P

(dBm)

OUT

Figure 17. ACPR vs. P

, Single W-CDMA Carrier (Test Model 1-64)

OUT

at 190 MHz and 380 MHz

380MHz

190MHz

08674-024

ERROR VECTOR MAGNITUDE (EVM) PERFORMANCE

Error vector magnitude (EVM) is a measure used to quantify the

performance of a digital radio transmitter or receiver. A signal

received by a receiver has all constellation points at their ideal

locations; however, various imperfections in the implementation

(such as magnitude imbalance, noise floor, and phase imbalance)

cause the actual constellation points to deviate from their ideal

locations. The ADL5535 shows excellent performance when used

with higher-order modulation schemes, such as a 16 QAM.

Figure 18 illustrates the EVM performance of the ADL5535 when

driven with a 16 QAM 10 Msym/s signal. Degradation of the EVM

performance starts to occur at an output power of +12 dBm.

20

–25

–30

190MHz SOURCE PO WER

EVM (dB)

–35

–40

–45

4 6 8 10 12 14 16 18

OUTPUT REFE RRED

380MHz SOURCE POW E R OUT P UT REF E RRED

Figure 18. EVM Performance vs. P

P

(dBm)

OUT

with a 16 QAM, 10 Msym/s Signal

OUT

380MHz

190MHz

08674-025

Rev. 0 | Page 11 of 16

Page 12

ADL5535

V

ADC DRIVING APPLICATION

The ADL5535 is a high linearity, fixed gain IF amplifier suitable

for use as an ADC driver. Figure 22 shows the schematic of the

ADL5535 driving the AD9268 16-bit analog-to-digital converter

(ADC). The ADL5535 has a single-ended input and output impedance of 50 Ω. A 1:1 impedance transformer, along with termination

resistors and series ferrite beads, are used to present a 50 Ω load

for the antialiasing filter interface. The filter interface between the

ADL5535 and the AD9268 is a sixth-order Butterworth low-pass

filter. The interface provides a 50 MHz, 1 dB bandwidth centered

around 175 MHz. Following the sixth-order filter, a shunt LC tank

circuit was inserted to further reduce the low frequency response

of the filter, giving more of a band-pass response to the filter.

The normalized wideband response is shown in Figure 19.

5

0

–5

–10

–15

–20

–25

–30

–35

NORMALIZED RESPONSE (d BFS)

–40

–45

50

0

100 150 200 250 300 350 400

FREQUENCY (MHz)

08674-021

Figure 19. Normalized Response of the ADC Interface Shown

in Figure 22

5

470nH

100pF

22nH

50Ω

68nH

22pF

56nH

27pF

8pF

ADL5535

Figure 22. Schematic of the ADL5535 Driving the AD9268 16-Bit ADC

72nH

MABA-007159-000000

8.2pF

SAMPLE FREQUENCY = 122.88MHz

0

SNRFS = 75.877dB

INPUT FREQUENCY = 1 70MHz

–15

FUNDAMENTAL POWER = –1.044dBFS

SECOND HARMONIC POWER = –75.499dBc

–30

THIRD HARMONIC POWER = –80.003dBc

NOISE FLOOR = –153.762dBFS/√Hz

–45

–60

AMPLITUDE (dBFS)

–75

–90

–105

–120

–135

5

2

3

FREQUENCY ( M Hz )

6

+

4

60544842363024181206

Figure 20. Measured Single-Tone Performance of the Circuit Shown

in Figure 22

FUNDAMENTAL1 = –7.161dBFS

0

FUNDAMENTAL2 = –7.116dBFS

IMD (2f1 – f2) = –66. 07dBc

–15

IMD (2f2 – f1) = –67. 588dBc

NOISE FLOOR = –150.84dBFS/√Hz

–30

–45

AMPLITUDE (dBFS)

–105

–120

–135

–60

–75

–90

f1 + f2

f2 – f1

FREQUENCY (M Hz )

2f1 – f2

2f2 – f1

60544842363024181206

Figure 21. Measured Two-Tone Performance of the Circuit Shown

in Figure 22

VCM

FERRITE BEAD

33Ω

VCM

10Ω AT 100MHz

FERRITE BEAD

33Ω

10Ω AT 100MHz

66Ω

66Ω

VIN+A

AD9268

VIN–A

08674-022

1

0.1µF

0.1µF

08674-019

08674-020

Rev. 0 | Page 12 of 16

Page 13

ADL5535

VCC

EVALUATION BOARD

GND

RFOUT

GND

C6

1µF

C5

1.2nF

C4

68pF

L1

3

470nH

C2

0.1µF

RFOUT

Figure 23 shows the evaluation board layout, and Figure 24

shows the schematic for the ADL5535 evaluation board. The

board is powered by a single 5 V supply.

The components used on the board are listed in Tab le 6 .

(2)

Power can be applied to the board through clip-on leads

(VCC and GND).

Figure 23. Evaluation Board Layout (Top)

RFIN

C1

0.1µF

8674-018

ADL5535

2

1

GND

RFIN

Figure 24. Evaluation Board Schematic

Table 6. Evaluation Board Components

Component Description Default Value

C1, C2 AC coupling capacitors 0.1 F, 0402

L1 DC bias inductor 470 nH, 0603 (Coilcraft 0603LS-NX or equivalent)

VCC, GND Clip-on terminals for power supply

C4 Power supply decoupling capacitor 68 pF, 0603

C5 Power supply decoupling capacitor 1.2 nF, 0603

C6 Power supply decoupling capacitor 1 F, 1206

08674-015

Rev. 0 | Page 13 of 16

Page 14

ADL5535

OUTLINE DIMENSIONS

*

1.75

1.55

4.25

3.94

1.50 TYP

(2)

12

3.00 TYP

4.60

4.40

*

0.56

0.36

*

COMPLIANT TO JEDEC STANDARDS TO-243 WITH THE

EXCEPTION OF DIMENSIONS INDICATED BY AN ASTERISK.

2.60

2.30

3

1.20

0.75

2.29

2.14

0.44

0.35

*

0.52

0.32

END VIEW

1.60

1.40

12-18-2008-B

Figure 25. 3-Lead Small Outline Transistor Package [SOT-89]

(RK-3)

Dimensions shown in millimeters

ORDERING GUIDE

1

Model

ADL5535ARKZ-R7 −40°C to +85°C 3-Lead SOT-89, 7” Tape and Reel RK-3

ADL5535-EVALZ Evaluation Board

1

Z = RoHS Compliant Part.

Temperature Range Package Description Package Option

Rev. 0 | Page 14 of 16

Page 15

ADL5535

NOTES

Rev. 0 | Page 15 of 16

Page 16

ADL5535

NOTES

©2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D08674-0-4/10(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...