Page 1

20 MHz to 500 MHz

FEATURES

Fixed gain of 20 dB

Operation up to 500 MHz

Input/output internally matched to 50 Ω

Integrated bias control circuit

OIP3 of 40 dBm at 70 MHz

P1dB of 20.4 dBm at 70 MHz

Noise figure of 2.5 dB at 70 MHz

Temperature and power supply stable

Single 5 V power supply

GENERAL DESCRIPTION

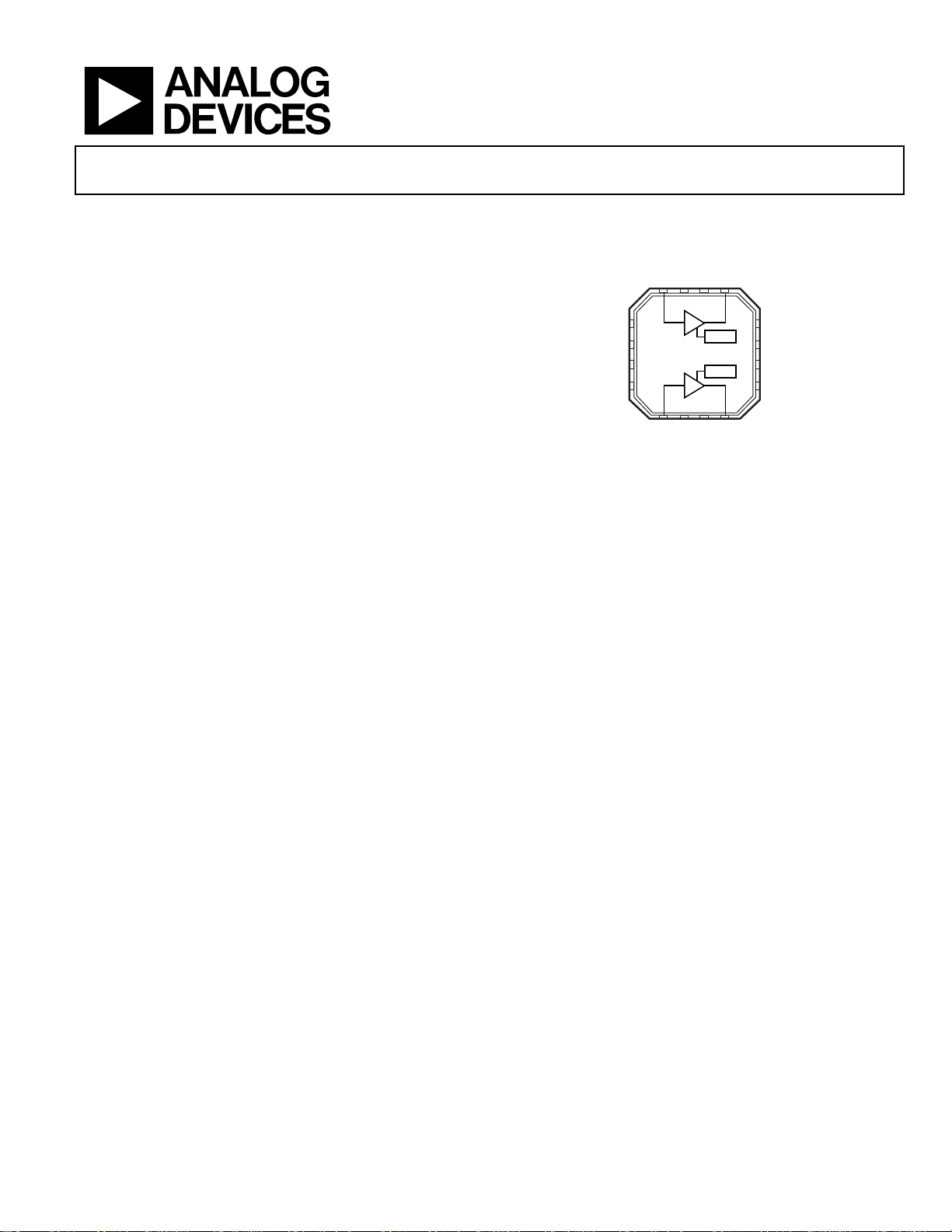

The ADL5534 contains two broadband, fixed-gain, linear

amplifiers and operates at frequencies up to 500 MHz. The

device can be used in a wide variety of equipment, including

cellular, satellite, broadband, and instrumentation equipment.

The ADL5534 has a fixed gain of 20 dB, which is stable over

frequency, temperature, power supply, and from device-todevice. The amplifiers are single-ended and internally matched

to 50 Ω. Only input/output ac-coupling capacitors, power supply

decoupling capacitors, and an external bias inductor are

required for operation of each amplifier.

Dual IF Amplifier

ADL5534

FUNCTIONAL BLOCK DIAGRAM

15 NC

14 NC

BIAS

BIAS

NC 6

CLIN2 7

Figure 1.

13 RFOUT1

12 CLIN1

11 NC

10 NC

9 NC

RFOUT2 8

06836-001

16 RFI N1

NC 1

NC 2

NC 3

NC

NC = NO CONNECT

ADL5534

4

RFIN2 5

The ADL5534 is fabricated on a GaAs HBT process. The

device is packaged in a 16-lead 5 mm × 5 mm LFCSP that

uses an exposed paddle for excellent thermal impedance.

The ADL5534 consumes 98 mA of current per amplifier on

a single 5 V supply, and is fully specified for operation from

−40°C to +85°C.

A similar amplifier, ADL5531 (available from Analog Devices,

Inc.) is the 20 dB gain single-channel version. Fully populated

evaluation boards for both the ADL5531 and ADL5534 are

available.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

Page 2

ADL5534

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Typical Scattering Parameters ..................................................... 4

Absolute Maximum Ratings ............................................................ 5

ESD Caution .................................................................................. 5

Pin Configuration and Function Descriptions ............................. 6

Typical Performance Characteristics ............................................. 7

REVISION HISTORY

6/08—Revision 0: Initial Version

Basic Connections .............................................................................9

Using Baluns to Combine Both Amplifiers Into a Single

Amplifier ..................................................................................... 10

ADC Driving Application ......................................................... 11

Soldering Information and Recommended PCB Land

Pattern .......................................................................................... 12

Evaluation Board ............................................................................ 13

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 15

Rev. 0 | Page 2 of 16

Page 3

ADL5534

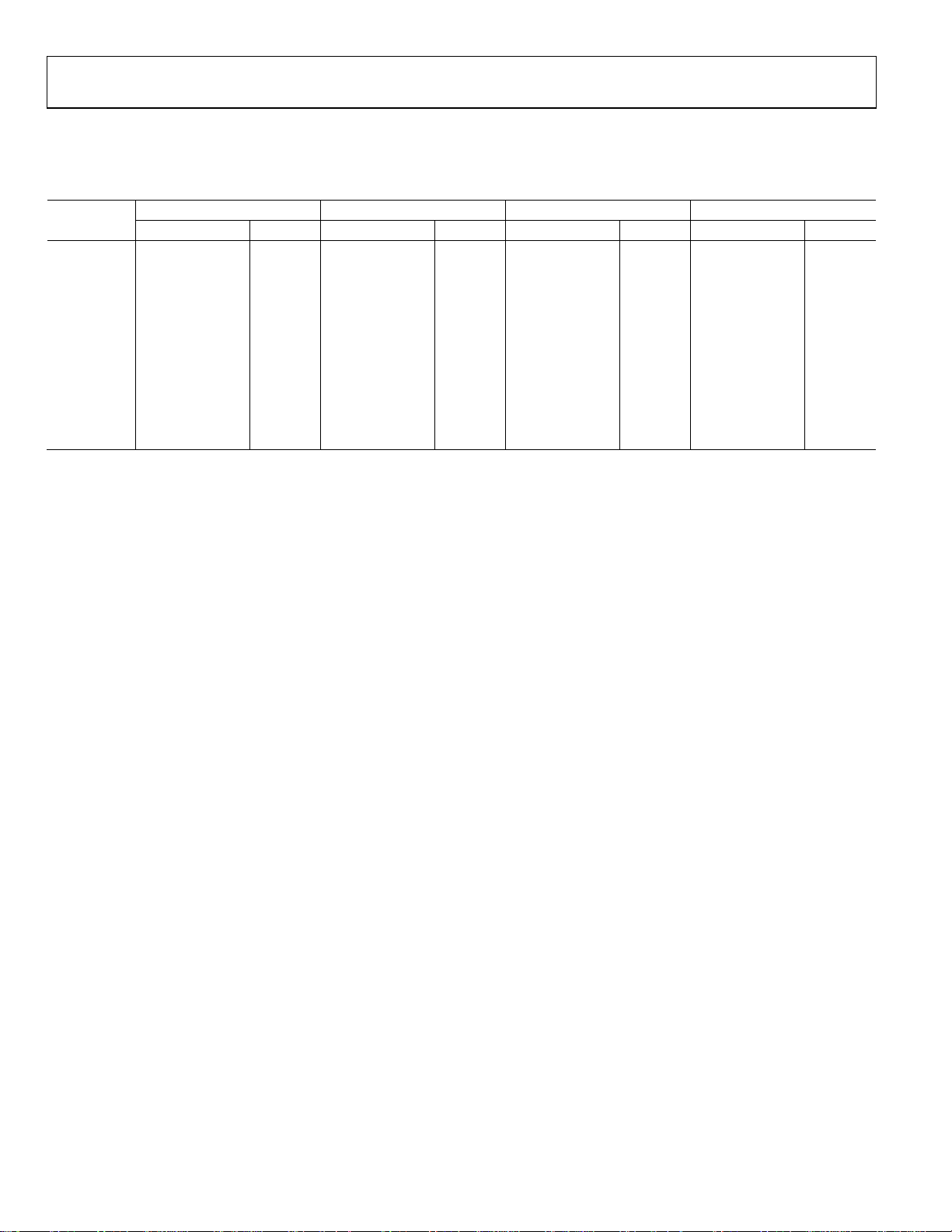

SPECIFICATIONS

VPOS = 5 V and TA = 25°C, unless otherwise noted.

Table 1.

Parameter Conditions Min Typ Max Unit

OVERALL FUNCTION

Frequency Range 20 500 MHz

Gain (S21) 190 MHz 20.4 dB

Input Return Loss (S11) 190 MHz −18.0 dB

Output Return Loss (S22) 190 MHz −29.0 dB

Reverse Isolation (S12) 190 MHz −23.0 dB

FREQUENCY = 70 MHz

Gain 21.0 dB

vs. Frequency ±5 MHz ±0.04 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.20 dB

vs. Supply 4.75 V to 5.25 V ±0.20 dB

Output 1 dB Compression Point 20.4 dBm

Output Third-Order Intercept f = 1 MHz, output power (P

Noise Figure 2.5 dB

Device-to-Device Isolation Measured at output with input applied to alternate device −46.0 dB

FREQUENCY = 190 MHz

Gain 19.5 20.4 21 dB

vs. Frequency ±50 MHz ±0.15 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.20 dB

vs. Supply 4.75 V to 5.25 V ±0.17 dB

Output 1 dB Compression Point 20.6 dBm

Output Third-Order Intercept f = 1 MHz, output power (P

Noise Figure 2.7 dB

Device-to-Device Isolation Measured at output with input applied to an alternate device −38.0 dB

FREQUENCY = 380 MHz

Gain 19.0 19.8 20.5 dB

vs. Frequency ±50 MHz ±0.18 dB

vs. Temperature −40°C ≤ TA ≤ +85°C ±0.22 dB

vs. Supply 4.75 V to 5.25 V ±0.16 dB

Output 1 dB Compression Point 20.4 dBm

Output Third-Order Intercept f = 1 MHz, output power (P

Noise Figure 3.0 dB

Device-to-Device Isolation Measured at output with input applied to an alternate device −34.0 dB

POWER INTERFACE RFOUT1, RFOUT2 pins

Supply Voltage 4.75 5 5.25 V

Supply Current Per amplifier 98 110 mA

vs. Temperature −40°C ≤ TA ≤ +85°C ±15 mA

Power Dissipation 0.5 W

) = 0 dBm per tone 40.0 dBm

OUT

) = 0 dBm per tone 39.0 dBm

OUT

) = 0 dBm per tone 36.0 dBm

OUT

Rev. 0 | Page 3 of 16

Page 4

ADL5534

TYPICAL SCATTERING PARAMETERS

VPOS = 5 V and TA = 25°C; the effects of the test fixture have been de-embedded up to the pins of the device.

Table 2.

S11 S21 S12 S22

Freq. (MHz)

20 −22.72 −102.04 21.79 174.78 −24.08 5.82 −18.56 −42.21

50 −20.40 −138.34 21.07 171.81 −23.40 6.92 −21.33 −71.17

100 −19.83 −160.87 20.66 169.90 −23.11 7.81 −25.56 −90.45

150 −19.95 −170.03 20.51 167.16 −23.01 9.36 −27.64 −95.94

200 −20.29 −174.24 20.39 164.06 −22.93 11.42 −27.78 −94.45

250 −20.72 −176.35 20.27 160.68 −22.85 13.45 −26.69 −91.22

300 −20.93 −175.04 20.16 157.31 −22.77 15.66 −24.58 −89.94

350 −21.06 −174.10 20.01 153.74 −22.69 17.74 −22.78 −90.89

400 −21.43 −171.87 19.85 150.30 −22.61 20.07 −20.76 −91.14

450 −21.58 −168.25 19.68 146.82 −22.51 22.24 −18.97 −92.39

500 −21.75 −163.79 19.45 142.72 −22.36 24.88 −17.10 −92.91

Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°) Magnitude (dB) Angle (°)

Rev. 0 | Page 4 of 16

Page 5

ADL5534

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage on RFOUT1, RFOUT2 5.5 V

Input Power on RFIN1, RFIN2 10 dBm

Internal Power Dissipation (Paddle Soldered) 900 mW

θJA (Junction-to-Air) 54°C/W

Maximum Junction Temperature 150°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 16

Page 6

ADL5534

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

15 NC

14 NC

16 RFI N1

PIN 1

NC 1

NC 2

NC 3

NC 4

INDICATOR

ADL5534

TOP VIEW

(Not to Scale)

RFIN2 5

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1, 2, 3, 4, 6, 9,

NC No Connect.

10, 11, 14, 15

5, 16 RFIN2, RFIN1 RF Input. Requires a dc blocking capacitor. Use a 10 nF capacitor for normal operation.

7, 12 CLIN2, CLIN1

A 1 nF capacitor connected from Pin 7 to ground and Pin12 to ground provides decoupling

for the on-board linearizer.

8, 13 RFOUT2, RFOUT1

RF Output and Bias. DC bias is provided to this pin through an inductor. A 470 nH inductor is

recommended for normal operation. The RF path requires a dc blocking capacitor. Use a 10 nF

capacitor for normal operation.

Exposed Paddle GND. Solder this paddle to a low impedance ground plane.

13 RFOUT1

12 CLIN1

11 NC

10 NC

9 NC

NC 6

CLIN2 7

RFOUT2 8

06836-002

Rev. 0 | Page 6 of 16

Page 7

ADL5534

–

TYPICAL PERFORMANCE CHARACTERISTICS

22

20

18

16

14

12

10

8

6

NOISE FI GURE AND GAIN (d B)

4

2

0

0 50 100 150 200 250 300 350 400 450 500

FREQUENCY (MHz)

GAIN

OIP3

P1dB

NOISE FIGURE

Figure 3. Noise Figure, Gain, P1dB, and OIP3 vs. Frequency

21.4

21.2

21.0

20.8

20.6

20.4

20.2

20.0

GAIN (dB)

19.8

19.6

19.4

19.2

19.0

0 50 100 150 200 250 300 350 400 450 500

+25°C

FREQUENCY (MHz)

–40°C

+85°C

Figure 4. Gain vs. Frequency and Temperature

45

42

39

36

33

30

27

24

P1dB AND OIP3 (d Bm)

21

18

15

12

06836-003

23.0

22.5

22.0

21.5

21.0

P1dB (dBm)

20.5

20.0

19.5

19.0

+85°C

+85°C

0 50 100 150 200 250 300 350 400 450 500

–40°C

+25°C

–40°C

FREQUENCY (MHz)

+25°C

42

40

38

36

34

OIP3 (dBm)

32

30

28

26

06836-006

Figure 6. P1dB and OIP3 vs. Frequency and Temperature

42

190MHz

40

38

36

500MHz

34

32

OIP3 (dBm)

30

28

26

24

6836-004

380MHz

–4–2024681012141618–6 20

P

(dBm)

OUT

70MHz

20MHz

06836-007

Figure 7. OIP3 vs. Output Power and Frequency

5

–10

–15

–20

–25

S–PARAMETERS (d B)

–30

–35

60 100 140 180 220 260 300 340 380 420 460

20 500

FREQUENCY (MHz)

S11

S12

S22

Figure 5. Input Return Loss (S11), Output Return Loss (S22), and Reverse

06836-005

5.0

4.5

4.0

3.5

3.0

2.5

NOISE FIGURE (dB)

2.0

1.5

1.0

0 50 100 150 200 250 300 350 400 450 500

+85°C

+25°C

–40°C

FREQUENCY (MHz)

Figure 8. Noise Figure vs. Frequency and Temperature

06836-008

Isolation (S12) vs. Frequency

Rev. 0 | Page 7 of 16

Page 8

ADL5534

–

60

25

50

40

30

20

PERCENTAGE (%)

10

0

36.6

37.4

38.2

39.0

39.8

37.0

37.8

38.6

OIP3 (dBm)

39.4

40.2

40.6

Figure 9. OIP3 Distribution at 190 MHz

100

90

80

70

60

50

40

PERCENTAGE (%)

30

20

10

0

19.0 19. 4 19. 8 20. 2 20.6 21.0 21.4 21 .8

P1dB (dBm)

Figure 10. P1dB Distribution at 190 MHz

41.0

41.4

41.8

–30

–35

–40

–45

–50

INPUT TO ALTERNATE O UTPUT ISO LATIO N (dB)

–55

60 100 140 180 220 260 3 00 340 380 420 46020 500

06836-009

FREQUENCY (MHz)

06836-011

Figure 12. Device-to-Device Isolation vs. Frequency

4.0

3.8

3.6

3.4

3.2

3.0

2.8

NOISE FI GURE (dB)

2.6

2.4

2.2

2.0

0 50 100 150 200 250 300 350 400 450 500

6836-010

FREQUENCY (MHz)

06836-013

Figure 13. Noise Figure vs. Frequency at 25°C, Multiple Devices Shown

70

60

50

40

30

PERCENTAGE (%)

20

10

0

19.7

19.9

20.1

20.3

20.5

20.7

19.8

20.0

20.2

20.4

GAIN (dB)

20.6

20.8

20.9

21.0

06836-012

Figure 11. Gain Distribution at 190 MHz

150

140

130

120

110

100

90

80

SUPPLY CURRENT (mA)

70

60

50

–40–30–20–100 102030405060708090

5.25V

5V

4.75V

TEMPERATURE ( °C)

Figure 14. Supply Current vs. Temperature and Supply Voltage

06836-014

Rev. 0 | Page 8 of 16

Page 9

ADL5534

V

BASIC CONNECTIONS

470nH

L1

C7

10nF

C9

1µF

POS

GND

RFIN1

RFIN2

C1

10nF

C3

10nF

15

14

1nF

13

NC

NC

RFOUT1

CLIN1

Z1

NC

C6

NC

NC

NC

RFOUT2

CLIN2

867

L2

470nH

C5

12

1nF

11

10

9

C8

10nF

16

1

RFIN1

NC

2

NC

3

ADL5534

NC

4

NC

RFIN2

5

C2

10nF

C4

10nF

C10

1µF

RFOUT1

RFOUT2

VPOS1

GND1

06836-015

Figure 15. Basic Connections

Table 5. Recommended Components for Basic Connections

Frequency C1, C2, C3, C4, C7, C8 L1, L2 C5, C6 C9, C10

20 MHz to 500 MHz 10 nF 470 nH 1 nF 1 F

The basic connections for operating the ADL5534 are shown in

Figure 15. Recommended components are listed in Tabl e 5. The

inputs and outputs should be ac-coupled with appropriately

sized capacitors (device characterization was performed with

10 nF capacitors). DC bias is provided to the amplifier via the

L1 and L2 inductors connected to the RFOUT1 and RFOUT2

pins. The recommended inductors for L1 and L2 are Coilcraft,

1008CS-471XJLC or equivalent. The bias voltage should be

decoupled using 10 nF and 1 μF capacitors. A bias voltage

of 5 V is required.

Rev. 0 | Page 9 of 16

Page 10

ADL5534

V

1

NC

2

NC

3

NC

4

NC

RFIN

ADT2-1T-1P+

1

T1

C15

10nF

Figure 16. Connections for Operating as a Balanced Amplifier

USING BALUNS TO COMBINE BOTH AMPLIFIERS INTO A SINGLE AMPLIFIER

The ADL5534 is ideal for use in a balanced amplifier configuration. To accomplish this, flux-coupled RF transformers

with a 2:1 impedance ratio can be used for wide band

operation. Alternatively, a balun can be constructed using

lumped element components for operation over a narrow

frequency range. Figure 16 shows the necessary connections

for configuring the ADL5534 for operation as a balanced

amplifier. Figure 17 shows the performance of the ADL5534

operating in a balanced configuration.

15

16

NC

RFIN1

Z1

ADL5534

NC

RFIN2

5

C6

1nF

POS

C10

1µF

C9

1µF

W2

GAIN

W1

GND

RFOUT

T2

ADT2-1T-1P+

1

VPOS1

GND1

OIP2

P1dB

NOISE FI GURE

FREQUENCY (MHz)

06836-016

OIP3

90

80

70

60

50

40

OIP2 (dBm)

30

20

10

0

06836-017

L1

470nH

14

13

NC

RFOUT1

NC

NC

NC

RFOUT2

CLIN2

867

L2

470nH

GAIN, NOISE FIGURE, P1dB, OIP3 (dB, dBm)

C7

10nF

C5

12

CLIN1

1nF

11

10

C16

9

10nF

C8

10nF

45

40

35

30

25

20

15

10

5

0

0 50 100 150 200 250 300 350 400 450 500

Figure 17. Performance of the ADL5534 Operating in Balanced

Configuration

Rev. 0 | Page 10 of 16

Page 11

ADL5534

V

470nH

15

14

1nF

NC

Z1

NC

NC

CLIN2

13

867

RFOUT1

NC

NC

NC

RFOUT2

470nH

CLIN1

RFIN

10nF

16

1

RFIN1

NC

2

NC

3

ADL5534

NC

4

NC

RFIN2

5

Figure 18. Narrow-Band IF Sampling Solution for Unbuffered ADC

ADC DRIVING APPLICATION

The ADL5534 is a high linearity, fixed gain IF amplifier suitable

for use as an ADC driver. The ADL5534 has a differential input

and output impedance of 100 Ω. A flux-coupled RF transformer

with a 2:1 impedance ratio was used to perform the single-endedto-differential conversion at the input of the ADL5534. The

interface between the ADL5534 and the AD9640 is a thirdorder low pass filter presenting a 100 Ω differential impedance

to the source and load. The ADL5534 must be ac-coupled to

prevent dc bias from entering the inputs of the ADC. Capacitors

of 100 pF were chosen to reduce any low frequency noise coming

from the ADL5534 and provide dc blocking. The measured

results for this interface shows 0.5 dB insertion loss for a 20 MHz

bandwidth centered around 92 MHz. The wideband response for

the interface is shown in Figure 19. The single-tone results in

Figure 20 show an SNR of 69.3 dB and an SFDR of 82 dBc. The

two-tone results in Figure 21 show an IMD3 of −80.5 dBc and

an SFDR of 78 dBc.

5

0

–5

–10

–15

–20

–25

–30

NORMALIZ ED LOSS (d B)

–35

–40

–45

50 100 150 200 250 300 350 400

FREQUENCY (MHz)

Figure 19. Measured Frequency Response of ADC interface

in Figure 18

06836-019

10nF

1nF

12

11

10

9

10nF 1µF

POS

1µF

GND

120nH

16pF

CML

120nH

SNR = 69.334dBc

0

SFDR = 82.267d Bc

NOISE F LOOR = –109.519dB

FUND = –1.05dBF s

SECOND = –82.262d Bc

THIRD = –88.688d Bc

60 121824303642485460

49.9Ω

49.9Ω

33Ω

4.7pF

33Ω

FREQUENCY (MHz )

AD9640

06836-018

100pF

100pF

120nH

120nH

VPOS1

GND1

–15

–30

–45

–60

–75

(dBFS)

–90

–105

–120

–135

Figure 20. Measured Single-Tone Performance of the Circuit in Figure 18

SFDR = 78.267dBc

0

NOISE FLOOR = –110.131dB

FUND 1 = –7.181dBFs

–15

FUND 2 = –7.191dBFs

IMD (2F1 – F2) = –80.538dBc

–30

IMD (2F2 – F1) = –82.086dBc

–45

–60

–75

(dBFS)

–90

–105

–120

–135

60 121824303642485460

FREQUENCY (MHz )

Figure 21. Measured Two-Tone Performance of the Circuit in Figure 18

06836-020

06836-021

Rev. 0 | Page 11 of 16

Page 12

ADL5534

SOLDERING INFORMATION AND RECOMMENDED PCB LAND PATTERN

Figure 22 shows the recommended land pattern for ADL5534.

To minimize thermal impedance, the exposed paddle on the

package underside should be soldered down to a ground plane.

If multiple ground layers exist, they should be stitched together

using vias. Pin 1 to Pin 4, Pin 6, Pin 9 to Pin 11, and Pin 14 to

Pin 15 can be left unconnected, or can be connected to ground.

Connecting these pins to ground improves device-to-device

isolation and slightly enhances thermal impedance. For more

information on land pattern design and layout, refer to the

AN-772 Application Note , A Desig

for the Lead Frame Chip Scale Package (LFCSP).

n and Manufacturing Guide

3.1mm

4.8mm

0.2mm

0.8mm

2.4mm

Figure 22. Recommended Land Pattern

06836-022

Rev. 0 | Page 12 of 16

Page 13

ADL5534

V

EVALUATION BOARD

Figure 23 shows the schematic for the ADL5534 evaluation

board. The board is powered by a single 5 V supply. The

components used on the board are listed in Tabl e 6.

Transformers (T1 and T2) are provided so the ADL5534

can be configured as a balanced amplifier. Applying 5 V to

R1

ADT2-1T-1P+

R3

C1

10nF

C3

10nF

C11

OPEN

1

T1

C15

OPEN

C12

OPEN

V

POS

1

NC

2

NC

3

NC

4

NC

W3

Figure 23. Evaluation Board Schematic

RFIN1

RFIN2

R5

OPEN

R7

OPEN

OPEN

OPEN

15

16

NC

RFIN1

ADL5534

NC

RFIN2

5

C6

1nF

V

Z1

VPOS biases the amplifier corresponding to RFIN1 and

RFOUT1. Applying 5 V to VPOS1 biases the amplifier

corresponding to RFIN2 and RFOUT2. To bias both amplifiers

from a single supply, connect 5 V to VPOS or VPOS1 and

attach a jumper across W3.

POS

C10

1µF

C9

1µF

C13

OPEN

C14

OPEN

VPOS1

W2

GND1

W1

GND

C2

10nF

OPEN

T2

ADT2-1T-1P+

1

OPEN

C4

10nF

RFOUT1

R2

R6

OPEN

R8

OPEN

R4

RFOUT2

14

POS1

NC

CLIN2

470nH

13

867

470nH

L1

RFOUT1

NC

NC

NC

RFOUT2

L2

C7

10nF

C5

12

CLIN1

1nF

11

10

C16

OPEN

9

C8

10nF

06836-023

Table 6. Evaluation Board Configuration Options

Component Description Default Condition

C1, C2, C3, C4 AC coupling capacitors 10 nF, Size 0402

C5, C6 Provides decoupling for the on-board linearizer 1 nF, Size 0603

C11, C12, C13, C14,

C15, C16

Optional components used for configuring ADL5534 as a balanced amplifier

Open, Size 0402

C9, C10 Power-supply decoupling capacitors 1 µF, Size 0603

C7, C8 Power-supply decoupling capacitors 10 nF, Size 0603

R1, R2, R3, R4, R5,

Optional components used for configuring ADL5534 as a balanced amplifier Open, Size 0603

R6, R7, R8

T1, T2

T1 and T2 are 50 Ω to100 Ω impedance transformers used to configure the ADL5534

as a balanced amplifier; T1 and T2 are used to present a 100 Ω differential impedance

Installed (Mini-Circuits®

ADT2-1T-1P+)

to the ADL5534

L1, L2 DC bias inductor 470 nH, Size 1008

VPOS, GND,

VPOS1, GND1

Clip-on terminals for power supply

VPOS, VPOS1; red

GND, GND1; black

W1, W2 2-pin jumper for connection of ground and supply via cable W1, W2

W3 2-pin jumper used to connect VPOS to VPOS1 W3

Rev. 0 | Page 13 of 16

Page 14

ADL5534

Figure 24. Evaluation Board Layout (Top)

06836-024

Figure 25. Evaluation Board Layout (Bottom)

06836-025

Rev. 0 | Page 14 of 16

Page 15

ADL5534

C

OUTLINE DIMENSIONS

5.00

INDI

PIN 1

ATO R

1.00

0.85

0.80

12° MAX

SEATING

PLANE

BSC SQ

TOP

VIEW

0.80 MAX

0.65 TYP

COMPLIANT TO JEDEC STANDARDS MO-220-VHHB

0.35

0.30

0.25

4.75

BSC SQ

0.20 REF

0.60 MAX

0.80 BSC

0.05 MAX

0.02 NOM

COPLANARITY

0.75

0.60

0.50

0.08

Figure 26. 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

5 mm × 5 mm Body, Very Thin Quad

CP-16-6

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option Ordering Quantity

ADL5534ACPZ-R7

ADL5534ACPZ-R2

ADL5534-EVALZ

1

Z = RoHS Compliant Part.

1

−40°C to +85°C 16-Lead LFCSP_VQ, 7” Tape and Reel CP-16-6 1500

1

−40°C to +85°C 16-Lead LFCSP_VQ, 7” Tape and Reel CP-16-6 250

1

Evaluation Board 1

0.60 MAX

13

12

EXPOSED

(BOTTOM VIEW)

9

8

PA D

16

1

4

5

2.40 BSC

PIN 1

INDICATOR

3.25

3.10 SQ

2.95

0.25 MIN

010606-0

Rev. 0 | Page 15 of 16

Page 16

ADL5534

NOTES

©2008 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06836-0-6/08(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...