Page 1

FEATURES

Matched pair of multiplying VGAs

Broad frequency range 20 MHz to 2.4 GHz

Continuous magnitude control from +5 dB to −30 dB

Output third-order intercept 24 dBm

Output 1 dB compression point 11 dBm

Output noise floor −148 dBm/Hz

Adjustable modulation bandwidth up to 230 MHz

Fast output power disable

Single-supply voltage 4.75 V to 5.25 V

APPLICATIONS

PA linearization and predistortion

Amplitude and phase modulation

Variable matched attenuator and/or phase shifter

Cellular base stations

Radio links

Fixed wireless access

Broadband/CATV

RF/IF analog multiplexer

RF/IF Vector Multiplier

ADL5390

FUNCTIONAL BLOCK DIAGRAM

VPRF

INMQ

INPQ

CMRF

INPI

INMI

CMOP

Figure 1.

VPS2OBBMQBBP

RFOP

RFOM

DSOPIBBMIBBP

04954-001

GENERAL DESCRIPTION

The ADL5390 vector multiplier consists of a matched pair of

broadband variable gain amplifiers whose outputs are summed.

The separate gain controls for each amplifier are linear-inmagnitude. If the two input RF signals are in quadrature, the

vector multiplier can be configured as a vector modulator or as

a variable attenuator/phase shifter by using the gain control pins

as Cartesian variables. In this case, the output amplitude can be

controlled from a maximum of +5 dB to less than –30 dB, and

the phase can be shifted continuously over the entire 360°

range. Since the signal paths are linear, the original modulation

on the inputs is preserved. If the two signals are independent,

then the vector multiplier can function as a 2:1 multiplexer or

can provide fading from one channel to another.

The ADL5390 operates over a wide frequency range of 20 MHz

to 2400 MHz. For a maximum gain setting on one channel at

380 MHz, the ADL5390 delivers an OP1dB of 11 dBm, an OIP3

of 24 dBm, and an output noise floor of −148 dBm/Hz. The gain

and phase matching between the two VGAs is better than 0.5 dB

and 1°, respectively, over most of the operating range.

The gain control inputs are dc-coupled with a +/−500 mV differential full-scale range centered about a 500 mV common

mode. The maximum modulation bandwidth is 230 MHz,

which can be reduced by adding external capacitors to limit the

noise bandwidth on the control lines.

Both the RF inputs and outputs can be used differentially or

single-ended and must be ac-coupled. The impedance of each

VGA RF input is 250 Ω to ground, and the differential output

impedance is nominally 50 Ω over the operating frequency

range. The DSOP pin allows the output stage to be disabled

quickly to protect subsequent stages from overdrive. The

ADL5390 operates off supply voltages from 4.75 V to 5.25 V

while consuming 135 mA.

The ADL5390 is fabricated on Analog Devices’ proprietary,

high performance 25 GHz SOI complementary bipolar IC

process. It is available in a 24-lead, Pb-free CSP package and

operates over a −40°C to +85°C temperature range. Evaluation

boards are available.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

ADL5390

TABLE OF CONTENTS

Specifications..................................................................................... 3

RF Output and Matching .......................................................... 13

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics............................................. 7

General Structure ........................................................................... 11

Theory of Operation ..................................................................11

Noise and Distortion.................................................................. 11

Applications..................................................................................... 12

Using the ADL5390.................................................................... 12

RF Input and Matching.............................................................. 12

REVISION HISTORY

10/04—Revision 0: Initial Version

Driving the I-Q Baseband Gain Controls............................... 13

Interfacing to High Speed DACs.............................................. 14

Generalized Modulator ............................................................. 15

Vec t or Mo d ul a t or ....................................................................... 15

Vector Modulator Example—CDMA2000 ............................. 15

Quadrature Modulator.............................................................. 17

RF Multiplexer............................................................................ 18

Evaluation Board ............................................................................ 19

Outline Dimensions ....................................................................... 23

Ordering Guide .......................................................................... 23

Rev. 0 | Page 2 of 24

Page 3

ADL5390

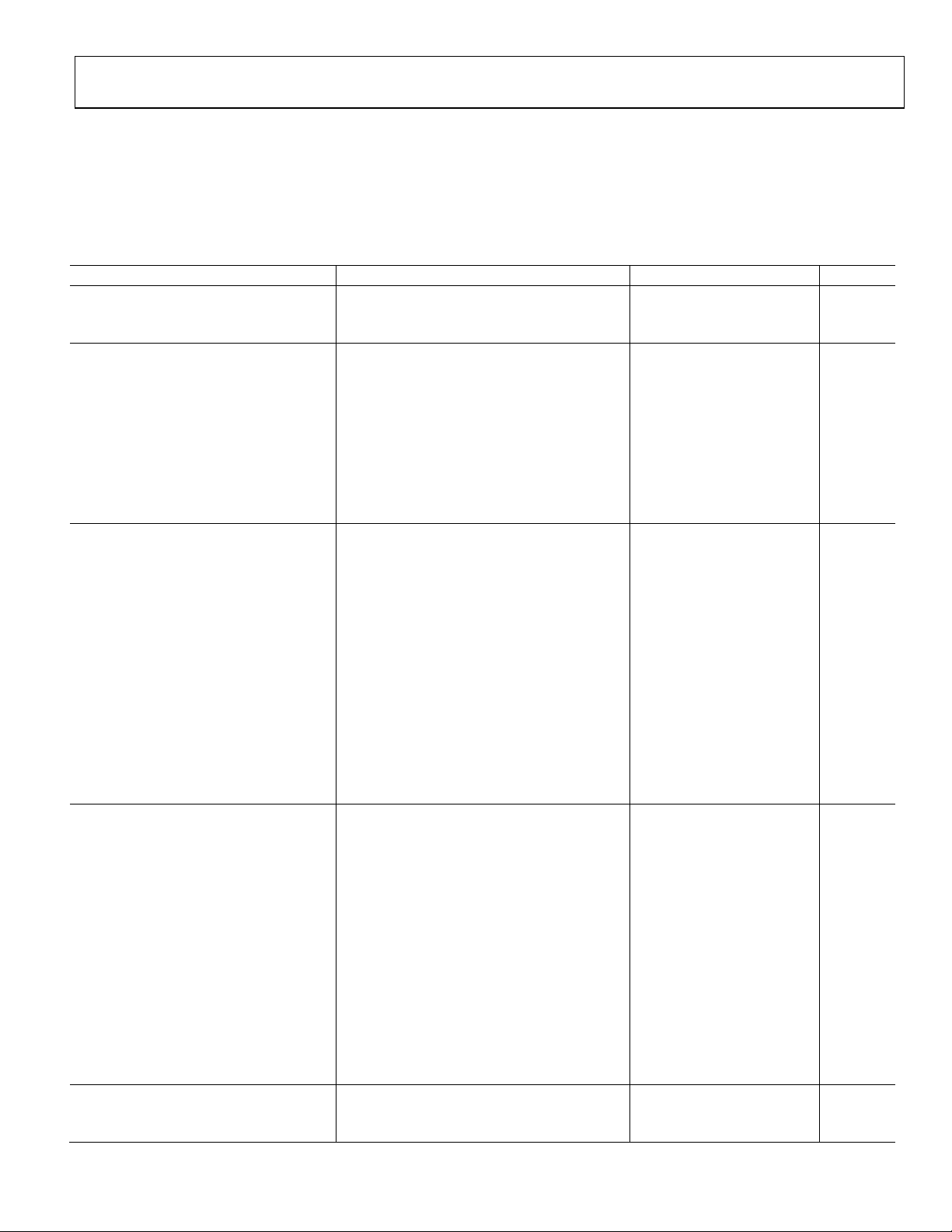

SPECIFICATIONS

VS = 5 V, TA = 25°C, ZO = 50 Ω, FRF = 380 MHz, single-ended source drive to INPI and INPQ, and INMI and INMQ are ac-coupled to

common, unless otherwise noted. 66.5 Ω termination resistors before ac-coupling capacitors on INPI and INPQ. The specifications refer

to one active channel with the other channel input terminated in 50 Ω. The common-mode level for the gain control inputs is 0.5 V. A

maximum gain setpoint of 1.0 refers to a differential gain control voltage of 0.5 V.

Table 1.

Parameter Conditions Min Typ Max Unit

OVERALL FUNCTION

Frequency Range

Gain Control Range Relative to maximum gain 35 dB

GAIN CONTROL INTERFACE (I and Q) QBBP, QBBM, IBBM, IBBP (Pins 4, 5, 14, 15)

Gain Scaling 3.5 1/V

Modulation Bandwidth

Second Harmonic Distortion

Third Harmonic Distortion

Step Response For gain from −15 dB to +5 dB 45 ns

For gain from +5 dB to −15 dB 47 ns

FRF = 70 MHz

Maximum Gain Maximum gain setpoint 4.6 dB

Gain Conformance Over gain setpoint of 0.2 to 1.0 0.25 dB

Output Noise Floor Maximum gain setpoint, no RF input −149 dBm/Hz

RF PIN = −5 dBm, frequency offset = 20 MHz −146 dBm/Hz

Output IP3

Output 1 dB Compression Point Maximum gain setpoint 10.7 dBm

Input 1 dB Compression Point Gain setpoint = 0.1 6.7 dBm

Gain Flatness Over any 60 MHz bandwidth 0.25 dB

Gain Matching At maximum gain setpoint 0.5 dB

Phase Matching At maximum gain setpoint ±0.25 Degrees

Input Impedance INPI, INMI, INMQ, INMP (Pins 20, 21, 22, 23)

Output Return Loss

FRF = 140 MHz

Maximum Gain Maximum gain setpoint 4.5 dB

Gain Conformance Over gain setpoint of 0.2 to 1.0 0.25 dB

Output Noise Floor Maximum gain setpoint, no RF input −144 dBm/Hz

RF PIN = −5 dBm, frequency offset = 20 MHz −145 dBm/Hz

Output IP3

Output 1 dB Compression Point Maximum gain setpoint 11 dBm

Input 1 dB Compression Point Gain setpoint = 0.1 7.1 dBm

Gain Flatness Over any 60 MHz bandwidth 0.25 dB

Gain Matching At maximum gain setpoint 0.5 dB

Phase Matching At maximum gain setpoint ±0.25 Degrees

Input Impedance INPI, INMI, INMQ, INMP (Pins 20, 21, 22, 23)

Output Return Loss

FRF = 380 MHz

Maximum Gain Maximum gain setpoint 4.1 dB

Gain Conformance Over gain setpoint of 0.2 to 1.0 0.25 dB

20 2400 MHz

500 mV p-p, sinusoidal baseband input single-

230 MHz

ended

500 mV p-p, 1 MHz, sinusoidal baseband input

45 dBc

differential

500 mV p-p, 1 MHz, sinusoidal baseband input

55 dBc

differential

= 70 MHz, F

F

RF1

= 72.5 MHz, maximum gain

RF2

23 dBm

setpoint

Ohms||pF

RFOP, RFOM (Pins 9, 10) measured through

250||1

9.7 dB

balun

= 140 MHz, F

F

RF1

= 142.5 MHz, maximum

RF2

24.4 dBm

gain setpoint

Ohms||pF

RFOP, RFOM (Pins 9, 10) measured through

250||1

9.6 dB

balun

Rev. 0 | Page 3 of 24

Page 4

ADL5390

Parameter Conditions Min Typ Max Unit

Output Noise Floor Maximum gain setpoint, no RF input −147.5 dBm/Hz

RF PIN = −5 dBm, frequency offset = 20 MHz −146 dBm/Hz

Output IP3

= 380 MHz, F

F

RF1

= 382.5 MHz, maximum

RF2

gain setpoint

Output 1 dB Compression Point Maximum gain setpoint 11.3 dBm

Input 1 dB Compression Point Gain setpoint = 0.1 8.3 dBm

Gain Flatness Over any 60 MHz bandwidth 0.25 dB

Gain Matching At maximum gain setpoint 0.5 dB

Phase Matching At maximum gain setpoint ±0.5 Degrees

Input Impedance INPI, INMI, INMQ, INMP (Pins 20, 21, 22, 23)

Output Return Loss

RFOP, RFOM (Pins 9, 10) measured through

balun

FRF = 900 MHz

Maximum Gain Maximum gain setpoint 4.5 dB

Gain Conformance Over gain setpoint of 0.2 to 1.0 0.4 dB

Output Noise Floor Maximum gain setpoint, no RF input −149.5 dBm/Hz

RF PIN = −5 dBm, frequency offset = 20 MHz −148 dBm/Hz

Output IP3

= 900 MHz, F

F

RF1

= 902.5 MHz, maximum

RF2

gain setpoint

Output 1 dB Compression Point Maximum gain setpoint 11.5 dBm

Input 1 dB Compression Point Gain setpoint = 0.1 8.5 dBm

Gain Flatness Over any 60 MHz bandwidth 0.25 dB

Gain Matching At maximum gain setpoint 0.6 dB

Phase Matching At maximum gain setpoint ±1 Degrees

Input Impedance INPI, INMI, INMQ, INMP (Pins 20, 21, 22, 23)

Output Return Loss

RFOP, RFOM (Pins 9, 10) measured through

balun

FRF = 2400 MHz

Maximum Gain Maximum gain setpoint 7.0 dB

Gain Conformance Over gain setpoint of 0.2 to 1.0 0.5 dB

Output Noise Floor Maximum gain setpoint, no RF input −147 dBm/Hz

RF PIN = −5 dBm, frequency offset = 20 MHz −144 dBm/Hz

Output IP3

= 2400 MHz, F

F

RF1

= 2402.5 MHz, maximum

RF2

gain setpoint

Output 1 dB Compression Point Maximum gain setpoint 9.6 dBm

Input 1 dB Compression Point Gain setpoint = 0.1 4.3 dBm

Gain Flatness Over any 60 MHz bandwidth 0.25 dB

Gain Matching At maximum gain setpoint 0.8 dB

Phase Matching At maximum gain setpoint ±2.5 Degrees

Input Impedance INPI, INMI, INMQ, INMP (Pins 20, 21, 22, 23)

Output Return Loss

RFOP, RFOM (Pins 9, 10) measured through

balun

POWER SUPPLY VPRF, VPS2 (Pin 1, 18, 6); RFOP, RFOM (Pins 9, 10)

Positive Supply Voltage 4.75 5 5.25 V

Total Supply Current Includes load current 135 mA

OUTPUT DISABLE DSOP (Pin 13)

Disable Threshold 2.5 V

Maximum Attenuation DSOP = 5 V 40 dB

Enable Response Time

Delay following high-to-low transition until

device meets full specifications

Disable Response Time

Delay following low-to-high transition until

device produces full attenuation

24.2 dBm

200||1

Ohms||pF

8.5 dB

23.3 dBm

180||0.6

Ohms||pF

6.8 dB

18.7 dBm

140||0.5

Ohms||pF

13.5 dB

15 ns

10 ns

Rev. 0 | Page 4 of 24

Page 5

ADL5390

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameters Rating

Supply Voltage VPRF, VPS2 5.5 V

DSOP 5.5 V

IBBP, IBBM, QBBP, QBBM 2.5 V

RFOP, RFOM 5.5 V

RF Input Power at Maximum Gain 10 dBm for 50 Ω

(INPI or INPQ, Single-Ended Drive)

Equivalent Voltage 2.0 V p-p

Internal Power Dissipation 825 mW

θJA (With Pad Soldered to Board) 59°C/W

Maximum Junction Temperature 125°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 5 of 24

Page 6

ADL5390

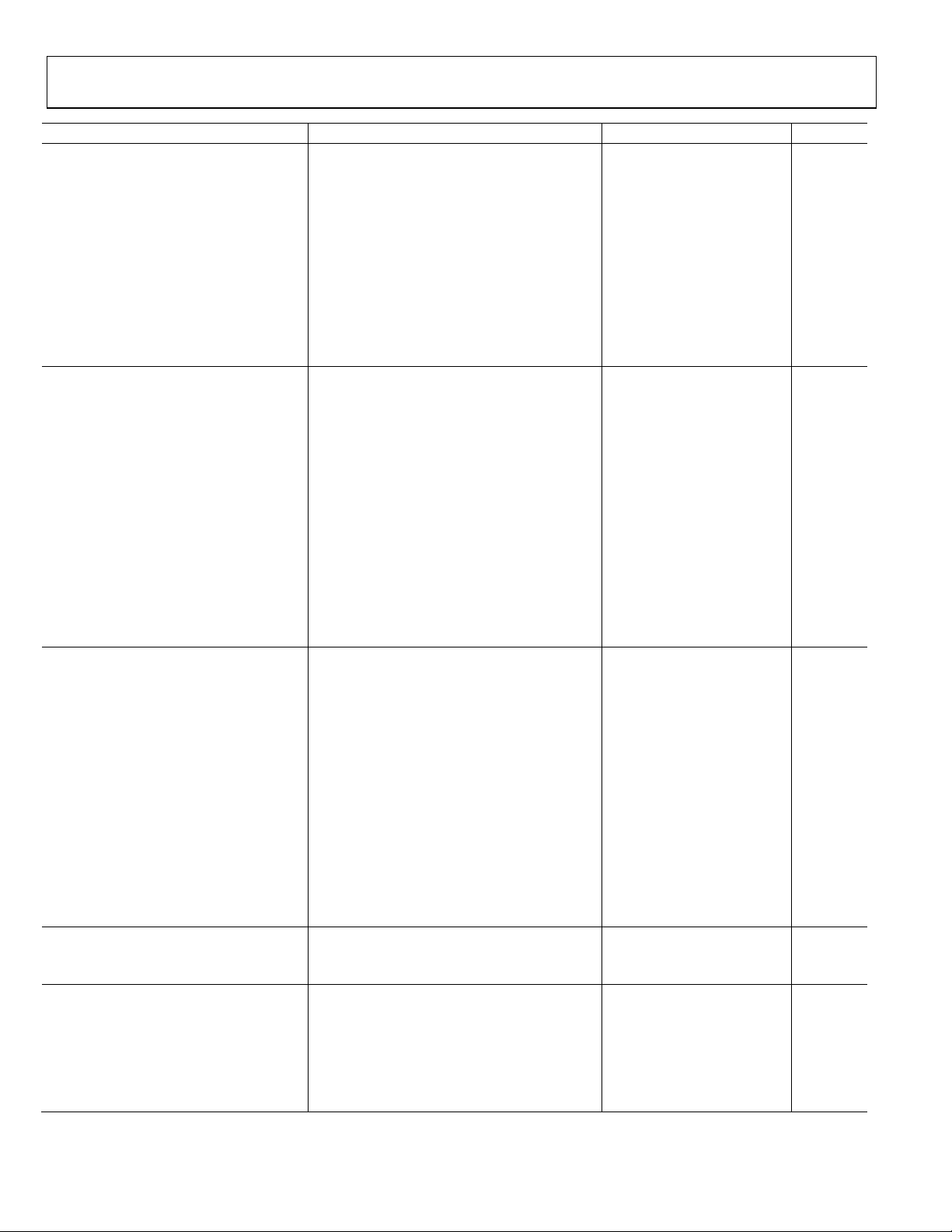

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

CMRF

INPQ

INMQ

INMI

INPI

24

23 22 21 20 19

CMRF

VPRF

QFLP

QFLM

QBBP

QBBM

VPS2

1

2

3

4

5

6

ADL5390

TOP VIEW

(Not to Scale)

7 8 9 101112

RFOP

CMOP

CMOP

RFOM

CMOP

CMOP

18

VPRF

17

IFLP

16

IFLM

15

IBBP

14

IBBM

13

DSOP

04954-002

Figure 2. LFCSP Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

2, 3 QFLP, QFLM

Q Baseband Input Filter Pins. Connect optional capacitor to reduce Q baseband gain control channel low-

pass corner frequency.

4, 5 QBBP, QBBM Q Channel Differential Baseband Gain Control Inputs. Typical common-mode bias level of 0.5 V.

6, 1, 18 VPS2, VPRF Positive Supply Voltage. VP of 4.75 V to 5.25 V.

7, 8, 11, 12,

CMOP, CMRF Device Common. Connect via lowest possible impedance to external circuit common.

19, 24

9, 10 RFOP, RFOM

Differential RF Outputs. Must be ac-coupled. Differential impedance 50 Ω nominal.

13 DSOP Output Disable. Pull high to disable output stage. Connect to common for normal operation.

14, 15 IBBM, IBBP I Channel Differential Baseband Gain Control Inputs. Typical common-mode bias level of 0.5 V.

16, 17 IFLM, IFLP

I Baseband Input Filter Pins. Connect optional capacitor to reduce I baseband gain control channel lowpass corner frequency.

20, 21 INPI, INMI

I Channel Differential RF Inputs. Must be ac-coupled. 250 Ω impedance to common on each pin. These

inputs can be driven single-ended without any performance degradation.

22, 23 INMQ, INPQ

Q Channel Differential RF Inputs. Must be ac-coupled. 250 Ω impedance to common on each pin. These

inputs can be driven single-ended without any performance degradation.

Exposed

Paddle

GND

The exposed paddle on the underside of the package should be soldered to a low thermal and electrical

impedance ground plane.

Rev. 0 | Page 6 of 24

Page 7

ADL5390

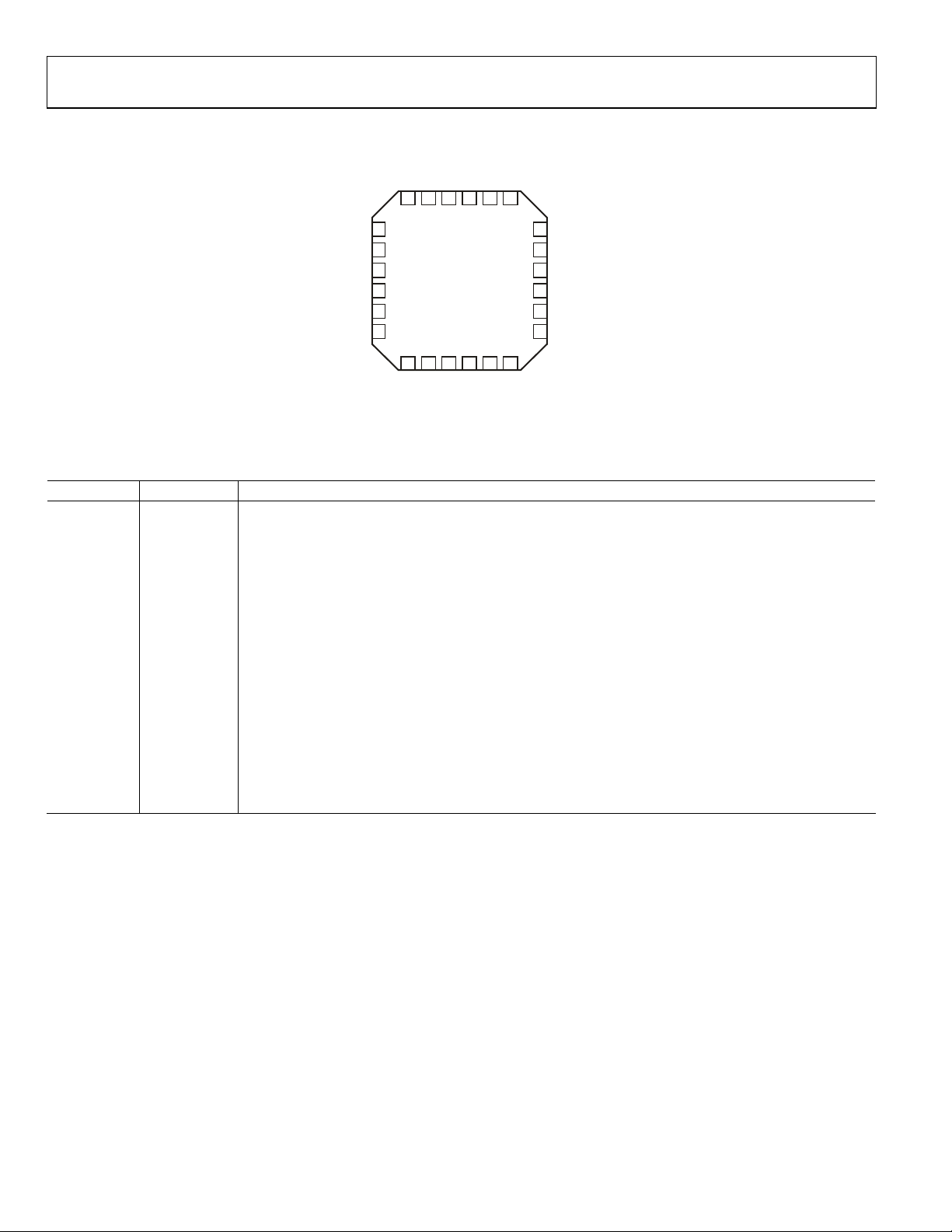

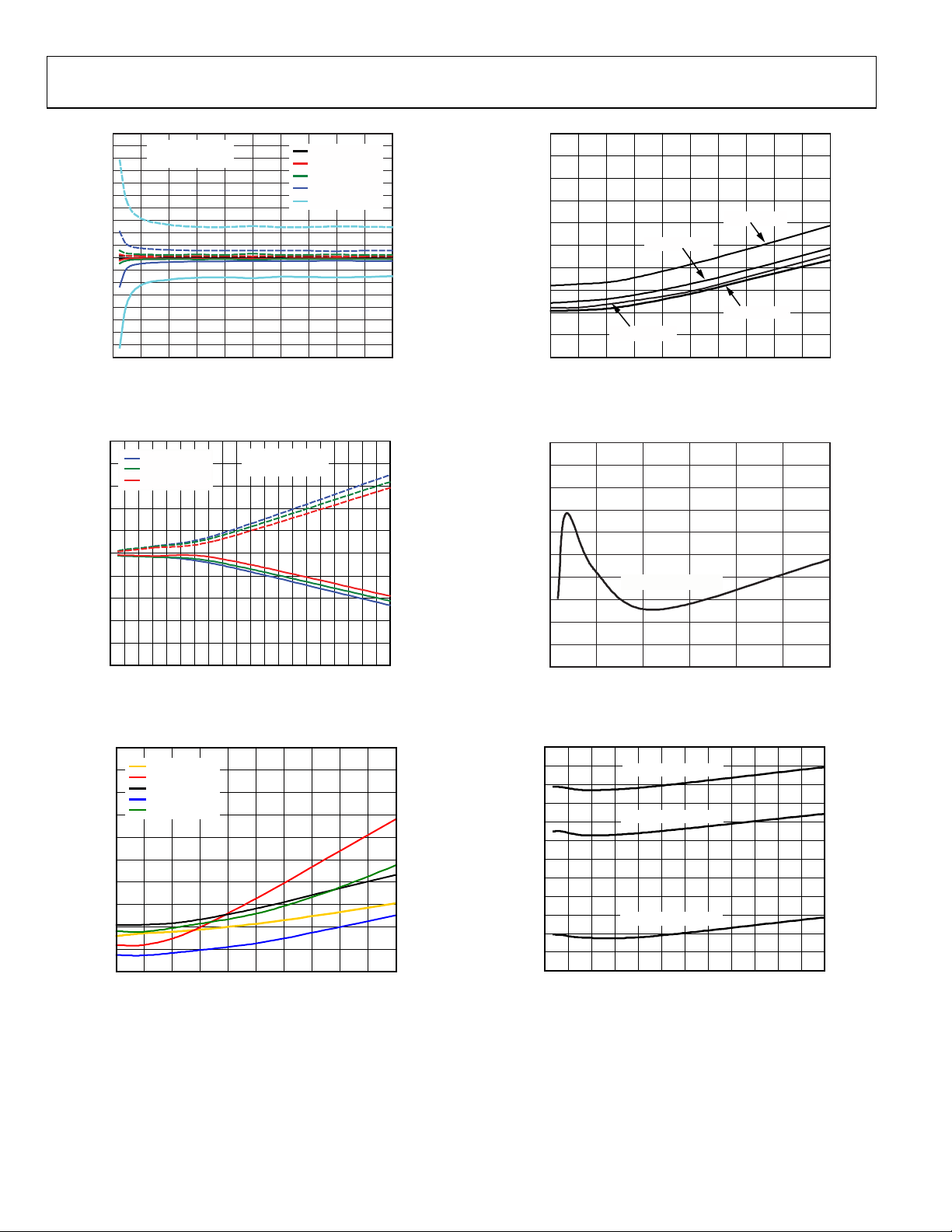

TYPICAL PERFORMANCE CHARACTERISTICS

10

5

0

–5

–10

GAIN (dB)

–15

–20

–25

–30

0.250

0.50

GAIN SETPOINT

FRF = 70MHz

= 140MHz

F

RF

= 380MHz

F

RF

= 900MHz

F

RF

= 2400MHz

F

RF

0.75 1.00

04954-003

5

4

3

2

1

0

–1

–2

CHANNEL GAIN MATCH (dB)

–3

–4

–5

0 300 600 900 1200 1500 1800 2100 2400

+3

σ

–3

σ

FREQUENCY (MHz)

04954-006

Figure 3. Gain Magnitude vs. Gain Setpoint, RF Frequency = 70 MHz,

140 MHz, 380 MHz, 900 MHz, 2400 MHz (Channel I or Channel Q)

10

–5

–10

GAIN (dB)

–15

–20

–25

–30

TEMP = –40°C

TEMP = +25°C

5

TEMP = +85°C

0

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

GAIN SETPOINT

04954-004

Figure 4. Gain Magnitude vs. Gain Setpoint, Temp = +85°C, +25°C, −40°C,

RF Frequency = 380 MHz (Channel I or Channel Q)

4

+3σ= DASH LINE

σ

= SOLID LINE

–3

3

2

1

0

–1

GAIN ERROR (dB)

–2

–3

–4

0 0.25 0.50 0.75 1.0

GAIN SETPOINT

FRF = 70MHz

FRF = 140MHz

F

= 380MHz

RF

= 900MHz

F

RF

F

= 2400MHz

RF

04954-005

Figure 5. Gain Conformance Error vs. Gain Setpoint, RF Frequency = 70 MHz,

140 MHz, 380 MHz, 900 MHz, 2400 MHz

Figure 6. Channel Gain Matching (I to Q) vs. RF Frequency,

Gain Setpoint = 1.0

9

8

7

6

5

4

GAIN (dB)

3

2

1

0

0 300 600 900 1200 1500 1800 2100 2400

FREQUENCY (MHz)

TEMP = –40°C

TEMP = +25°C

TEMP = +85°C

04954-007

Figure 7. Channel Gain vs. RF Frequency, Temp = +85°C, +25°C, −40°C,

Gain Setpoint = 1.0

5

+3σ= DASH LINE

σ

= SOLID LINE

–3

0

–5

–10

PHASE ERROR (Degrees)

–15

–20

0 0.25 0.50 0.75 1.0

GAIN SETPOINT

FRF = 70MHz

= 140MHz

F

RF

F

= 380MHz

RF

= 900MHz

F

RF

= 2400MHz

F

RF

04954-008

Figure 8. Single-Channel Phase Deviation vs. Gain Setpoint, Normalized to

Gain Setpoint = 1.0, RF Frequency = 70 MHz, 140 MHz, 380 MHz,

900 MHz, 2400 MHz

Rev. 0 | Page 7 of 24

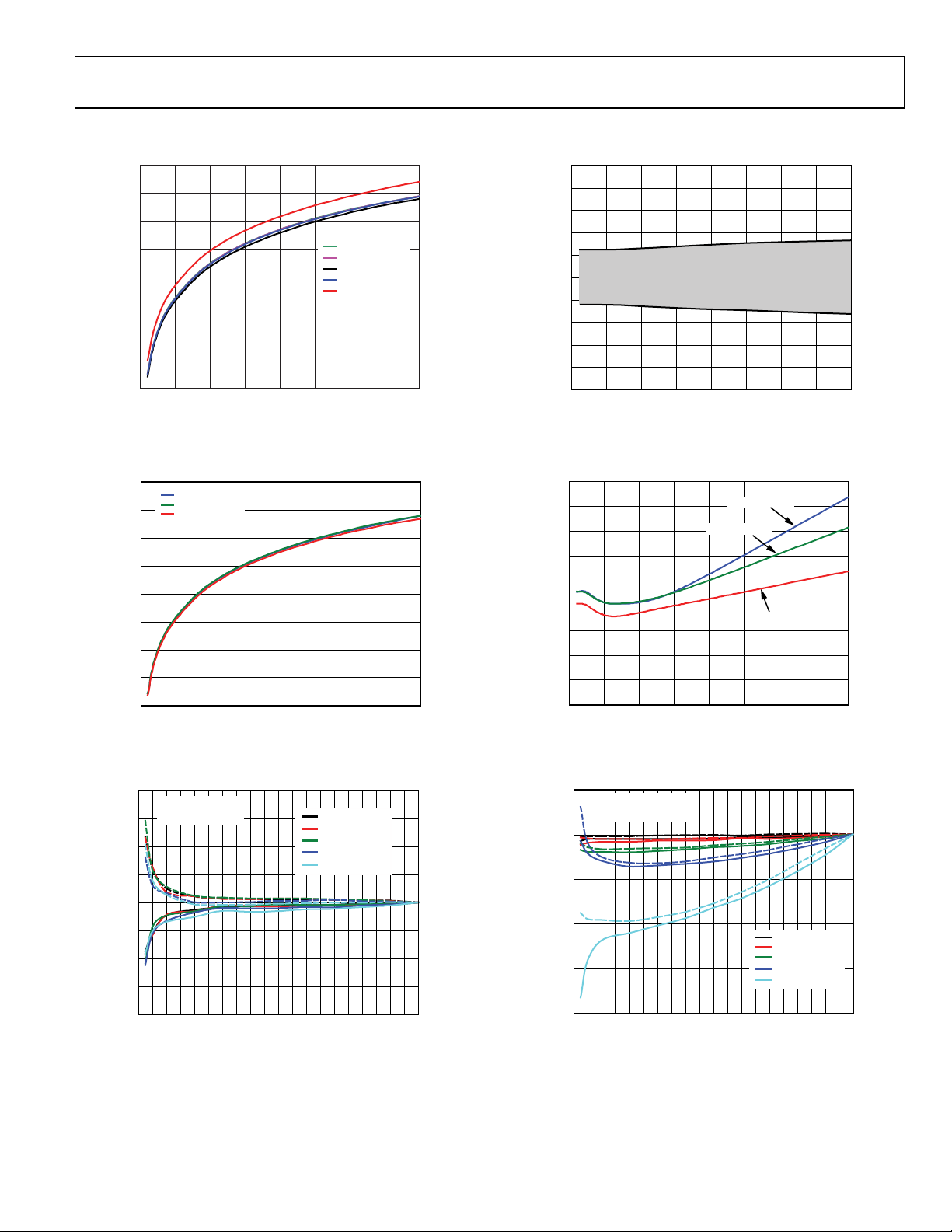

Page 8

ADL5390

25

20

15

10

–5

–10

PHASE DIFFERRENCE (Degrees)

–15

–20

Figure 9. Channel-to-Channel Phase Matching vs. Gain Setpoint,

RF Frequency = 70 MHz, 140 MHz, 380 MHz, 900 MHz, 2400 MHz

10

8

6

4

2

0

–2

–4

PHASE DIFFERENCE (Degrees)

–6

–8

–10

Figure 10. Channel-to-Channel Phase Matching vs. RF Frequency, Temp =

–142

–143

–144

–145

–146

–147

–148

NOISE (dBm/Hz)

–149

–150

–151

–152

Figure 11. Output Noise Floor vs. Gain Setpoint, No RF Carrier,

RF Frequency = 70 MHz, 140 MHz, 380 MHz, 900 MHz, 2400 MHz

+3σ= DASH LINE

–3

σ

= SOLID LINE

5

0

0 0.2 0.4 0.6 0.8 1.0

TEMP = –40°C

TEMP = +25°C

TEMP = +85°C

0 600 1200 1800 2400

GAIN SETPOINT

+3σ= DASH LINE

–3

σ

FREQUENCY (MHz)

FRF= 70MHz

F

F

F

F

= SOLID LINE

=140MHz

RF

=380MHz

RF

= 900MHz

RF

= 2400MHz

RF

+85°C, +25°C, −40°C, Gain Setpoint = 1.0

FRF = 70MHz

F

= 140MHz

RF

F

= 380MHz

RF

F

= 900MHz

RF

F

= 2400MHz

RF

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

GAIN SETPOINT

04954-009

04954-010

04954-011

–142

–143

–144

–145

–146

–147

–148

NOISE (dBm/Hz)

–149

–150

–151

–152

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

PIN=–10dBm

PIN=–15dBm

GAIN SETPOINT

PIN= –5dBm

NO CARRIER

Figure 12. Output Noise Floor vs. Gain Setpoint, No Carrier, with Carrier

(20 MHz Offset), RF P

–142

–143

–144

–145

–146

–147

–148

NOISE (dBm/Hz)

–149

–150

–151

–152

0 400 800 1200 1600 2000 2400

= −5, −10, −15, No Carrier, RF Frequency = 380 MHz

IN

GAIN SETPOINT = 1.0

FREQUENCY (MHz)

Figure 13. Output Noise Floor vs. RF Frequency, Gain Setpoint = 1.0,

No RF Carrier

10

5

0

–5

GAIN (dB)

–10

–15

–20

0 400 800 1200 1600 2000 2400

GAIN SETPOINT = 1.0

GAIN SETPOINT = 0.5

GAIN SETPOINT = 0.1

FREQUENCY (MHz)

Figure 14. Gain vs. RF Frequency, Gain Setpoint = 1.0, 0.5, 0.1

04954-012

04954-013

04954-014

Rev. 0 | Page 8 of 24

Page 9

ADL5390

0

–10

–20

–30

–40

–50

–60

–70

–80

RF OUTPUT SIDEBAND POWER (dBm)

–90

–100

0 100 200 300 400 500 600 700 800 900 1000

DIFF. BASEBAND INPUT LEVEL (mV p-p)

FUNDAMENTAL

2ND HARMONIC

3RD HARMONIC

04954-015

Figure 15. Baseband Harmonic Distortion, (Channel I and Channel Q),

RF P

= −5 dBm, (Balun and Cable Losses Not Included)

IN

12

11

10

9

OP1dB (dBm)

8

7

6

0

400 800 1200 1600 2000 2400

FREQUENCY (MHz)

TEMP = –40°C

TEMP = +25°C

TEMP = +85°C

04954-016

0

–5

–10

–15

–20

–25

SIDEBAND POWER (dBm)

–30

–35

0 50 100 150 200 250 300 350 400

1V p-p BASEBAND INPUT

500mV p-p BASEBAND INPUT

250mV p-p BASEBAND INPUT

BB FREQUENCY (MHz)

Figure 18. IQ Modulation Bandwidth vs. Baseband Magnitude

15

10

5

0

–5

OP1dB (dBm)

–10

–15

–20

–25

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

GAIN SETPOINT

FRF = 70MHz

= 140MHz

F

RF

= 380MHz

F

RF

= 900MHz

F

RF

= 2400MHz

F

RF

04954-018

04954-019

Figure 16. Output 1 dB Compression Point vs. RF Frequency,

Temp = +85°C, +25°C, −40°C, Gain Setpoint = 1.0

30

28

TEMP = –40°C

26

24

22

20

OIP3 (dBm)

18

16

14

12

10

0

TEMP = +85°C

400 800 1200 1600 2000 2400

FREQUENCY (MHz)

TEMP = +25°C

04954-017

Figure 17. Output IP3 vs. RF Frequency, Temp = +85°C, +25°C, −40°C,

Gain Setpoint = 1.0

Rev. 0 | Page 9 of 24

Figure 19. Output 1 dB Compression vs. Gain Setpoint, RF Frequency =

70 MHz, 140 MHz, 380 MHz, 900 MHz, 2400 MHz

30

25

20

15

10

5

OIP3 (dBm)

0

–5

–10

–15

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

GAIN SETPOINT

FRF = 70MHz

= 140MHz

F

RF

F

= 380MHz

RF

= 900MHz

F

RF

F

= 2400MHz

RF

04954-020

Figure 20. Output IP3 vs. Gain Setpoint, RF Frequency = 70 MHz, 140 MHz,

380 MHz, 900 MHz, 2400 MHz

Page 10

ADL5390

300

250

200

150

100

INPUT SHUNT RESISTANCE (Ω)

50

20 220 420 620 820 1020 12201420 16201820 2020 2220

Figure 21. S11 of RF Input (Shunt R/C Representation)

SHUNT CAPACITANCE (pF)

SHUNT RESISTANCE (Ω)

F

(MHz)

RF

1.25

1.00

0.75

0.50

0.25

0

INPUT SHUNT CAPACITANCE (pF)

04954-021

0

–5

–10

–15

–20

–25

–30

–35

–40

–45

–50

RF OUTPUT POWER (dBm)

–55

–60

–65

–70

–75

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

DSOP VOLTAGE (V)

Figure 24. Power Shutdown Attenuation, RF = 380 MHz

04954-024

ADL5390 SDD22

90

60

30

330

300

)

I

150

→

|GRIDZ|

S

11TERMANG

I

210

IMPEDANCE CIRCLE

SDD22 NOM WFR DUT 1

S22 NOM WFR

120

240

10MHz

ARG(

GRIDZ

2.7GHz

10MHz

270

), RADS(S

3GHz

11

TERMANG

Figure 22. S22 of RF Output (Differential and Single-Ended through Balun)

139

138

Vp = 5.25

1

0

0180

04954-022

TEK RUN ENVELOPE 12 AUG 04 16:48:01

1

CH1 500mV Ω

CH3 2.0V Ω D

S

M 10.0ns 5.0GS/s ET 200ps/pt

A CH3 760mV

04954-025

Figure 25. Power Shutdown Response Time, RF = 380 MHz

137

136

135

134

SUPPLY CURRENT (mA)

133

132

–40 –25 –10 5 20 35 50 65 80

Vp = 5

Vp = 4.75

TEMPERATURE (°C)

Figure 23. Supply Current vs. Temperature

04954-023

Rev. 0 | Page 10 of 24

Page 11

ADL5390

GENERAL STRUCTURE

THEORY OF OPERATION

The simplified block diagram given in Figure 26 shows a

matched pair of variable gain channels whose outputs are

summed and presented to the final output. The RF/IF signals

propagate from the left to the right, while the baseband gain

controls are placed above and below. The proprietary linearresponding variable attenuators offer excellent linearity, low

noise, and greater immunity from mismatches than other

commonly used methods.

Since the two independent RF/IF inputs can be combined in

arbitrary proportions, the overall function can be termed

“vector multiplication” as expressed by

= V

V

OUT

IRF

× (V

where:

V

V

IRF

IBB

and V

and V

are the RF/IF input vectors.

QRF

are the baseband input scalars.

QBB

VO is the built-in normalization factor, which is designed to be

0.285 V (1/3.5 V).

The overall voltage gain, in linear terms, of the I and Q channels

is proportional to its control voltage and scaled by the normalization factor, i.e., a full-scale gain of 1.75 (5 dB) for V

500 mV. A full-scale voltage gain of 1.75 defines a gain setpoint

of 1.0.

Due to its versatile functional form and wide signal dynamic

range, the ADL5390 can form the core of a variety of useful

functions such as quadrature modulators, gain and phase adjusters, and multiplexers. At maximum gain on one channel, the

output 1 dB compression point and noise floor referenced to

50 Ω are 11 dBm and −148 dBm/Hz, respectively. The broad

frequency response of the RF/IF and gain control ports allows

the ADL5390 to be used in a variety of applications at different

frequencies. The bandwidth for the RF/IF signal path extends

from approximately 20 MHz to beyond 2.4 GHz, while the gain

controls signals allow for modulation rates greater than 200 MHz.

IBB/VO

) + V

QRF

× (V

QBB/VO

)

of

I (Q)BB

,

V

IRF

I CHANNEL

SINGLE-ENDED

OR DIFFERENTIAL

V

,

QRF

Q CHANNEL

SINGLE-ENDED

OR DIFFERENTIAL

Figure 26. Simplified Architecture of the ADL5390

NOISE AND DISTORTION

The signal path for a particular channel of the ADL5390 consists basically of a preamplifier followed by a variable attenuator

and then an output driver. Each subblock contributes some level

of noise and distortion to the desired signal. As the channel gain

is varied, these relative contributions change. The overall effect

is a dependence of output noise floor and output distortion

levels on the gain setpoint.

For the ADL5390, the distortion is always determined by the

preamplifier. At the highest gain setpoint, the signal capacity, as

described by the 1 dB compression point (P1dB) and the thirdorder intercept (OIP3), are at the highest levels. As the gain is

reduced, the P1dB and OIP3 are reduced in exact proportion.

At the higher gain setpoints, the output noise is dominated by

the preamplifier as well. At lower gains, the contribution from

the preamplifier is correspondingly reduced and eventually a

noise floor, set by the output driver, is reached. As Figure 27

illustrates, the overall dynamic range defined as a ratio of OIP3

to output noise floor remains constant for the higher gain

setpoints. At some gain level, the noise floor levels off and the

dynamic range degrades commensurate with the gain reduction.

175

DYNAMIC RANGE = OIP3 – (OUTPUT NOISE

FLOOR (NO CARRIER))

170

BASEBAND INPUT

V-I

ATTENUATOR

V-I

ATTENUATOR

BASEBAND INPUT

I CHANNEL

V

IBB

LINEAR

LINEAR

V

QBB

Q CHANNEL

I-V

OUTPUT

DISABLE

SINGLE-ENDED

OR DIFFERENTIAL

50Ω OUTPUT

04954-026

Matching between the two gain channels is ensured by careful

layout and design. Since they are monolithic and arranged

symmetrically on the die, thermal and process gradients are

minimized. Typical gain and phase mismatch at maximum gain

are <0.5 dB and <0.5°.

Rev. 0 | Page 11 of 24

165

Hz)

×

160

155

150

DYNAMIC RANGE (dB

145

140

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

GAIN SETPOINT

Figure 27. Dynamic Range Variation with Gain Setpoint

04954-027

Page 12

ADL5390

APPLICATIONS

USING THE ADL5390

The ADL5390 is designed to operate in a 50 Ω impedance system.

Figure 29 illustrates an example where the RF/IF inputs are

driven in a single-ended fashion, while the differential RF output is converted to a single-ended output with a RF balun. The

baseband gain controls for the I and Q channels are typically

driven from differential DAC outputs. The power supplies,

VPRF and VPS2, should be bypassed appropriately with 0.1 µF

and 100 pF capacitors. Low inductance grounding of the CMOP

and CMRF common pins is essential to prevent unintentional

peaking of the gain. The exposed paddle on the underside of the

package should be soldered to a low thermal and electrical

impedance ground plane.

RF INPUT AND MATCHING

The RF/IF inputs present 250 Ω resistive terminations to

ground. In general, the input signals should be ac-coupled

through dc-blocking capacitors. The inputs may be driven differentially or single-ended, in which case the unused inputs are

connected to common via the dc-blocking capacitors. The

ADL5390’s performance is not degraded by driving these inputs

single-ended. The input impedance can be reduced by placing

external shunt termination resistors to common on the source

side of the dc-blocking capacitors so that the quiescent dc-bias

RFIN_I

RFIN_Q

66.5Ω

R22

66.5Ω

C7

VP

R2

C2

10nF

C5

10nF

0.1µF

L1

0Ω

L2

0Ω

VP

C4

0.1µF

C1

10nF

C6

10nF

100pF

C8

100pF

C3

VPRF

CMRF

INPI

INMI

IPMQ

INPQ

CMRF

VPRF

C12

(SEE TEXT)

IFLP

IFLM

ADL5390

P

L

F

QFLM

Q

C11

(SEE TEXT)

QBBP QBBM

Figure 29. Basic Connections

IBBMIBBP

IBBP

QBBP

IBBM

level of the ADL5390 inputs is not affected, as shown in Figure

29. Capacitive reactance at the RF inputs can be compensated

for with series inductance. In fact, the customer evaluation

board has high impedance line traces between the shunt termination pads and the device input pins, which provides series inductance and improves the return loss at 1.9 GHz to better than

−15 dB with the shunt termination removed, as shown in Figure

28.

0

876.8

C18

972.0

1067.2

1162.4

(M/A-COM)

S11 MATCH WITHOUT

66.5Ω TERMINATION

1448.0

1352.8

T1

1543.2

4

1733.6

1638.4

1828.8

1924.0

1257.6

15

3

ETC1-1-13

2114.4

2019.2

2209.6

RFOP

–5

–10

–15

dB

–20

400.8

591.2

496.0

S11 MATCH WITH

TERMINATION

686.4

781.6

FREQUENCY (MHz)

–25

–30

–35

20.0

115.2

210.4

305.6

Figure 28. ADL5390 Customer Evaluation Board RF Input Return Loss.

VP

B

SW1

DSOP

CMOP

CMOP

RFOM

RFOP

CMOP

CMOP

VPS2

QBBM

C10

100pFC90.1µF

R8

10kΩ

120nH

C14

0.1µF

L4

A

L3

120nH

VP

10nF

C17

10nF

2400.0

2304.8

04954-029

04954-028

Rev. 0 | Page 12 of 24

Page 13

ADL5390

±

RF OUTPUT AND MATCHING

The RF/IF outputs of the ADL5390, RFOP and RFOM, are open

collectors of a transimpedance amplifier that need to be pulled

up to the positive supply, preferably with RF chokes, as shown

in Figure 30. The nominal output impedance looking into each

individual output pin is 25 Ω. Consequently, the differential

output impedance is 50 Ω.

V

P

0.1µF

RFOP

120nH

10pF

10pF

50Ω

DIFFERENTIAL

1:1

RF

OUTPUT

04954-030

R

T

RFOM

I

G

SIG

Figure 30. RF Output Interface to the ADL5390 Showing

M

R

T

Coupling Capacitors, Pull-Up RF Chokes, and Balun

Since the output dc levels are at the positive supply, ac-coupling

capacitors are usually needed between the ADL5390 outputs

and the next stage in the system.

The RF output signal can be disabled by raising the DSOP pin

to the positive supply. The output disable function provides

>40 dB attenuation of the input signal, even at full gain. The

interface to DSOP is high impedance and the output disable

and output enable response times are <100 ns. If the output

disable function is not needed, the DSOP should be tied to

ground.

10

8

6

4

2

GAIN (dB)

0

–2

–4

RL = 50Ω

–10

10 100 1000 10000

Figure 31. Gain of the ADL5390 Using a Single-Ended Output with Different

Dummy Loads, R

on the Unused Output, Gain Setpoint = 1.0

L2

RL2 = OPEN

R

L2

R

L2

FREQUENCY (MHz)

= 50Ω

= SHORT

04954-043

A 1:1 RF broadband output balun, such as the ETC1-1-13 (M/ACOM), converts the differential output of the ADL5390 into a

single-ended signal. Note that the loss and balance of the balun

directly impact the apparent output power, noise floor, and gain/

phase errors of the ADL5390. In critical applications, narrow-band

baluns with low loss and superior balance are recommended.

If the output is taken in a single-ended fashion directly into a 50 Ω

load through a coupling capacitor, there will be an impedance

mismatch. This can be resolved with a 1:2 balun to convert the

single-ended 25 Ω output impedance to 50 Ω. If loss of signal

swing is not critical, a 25 Ω back termination in series with the

output pin can also be used. The unused output pin must still be

pulled up to the positive supply. The user may load it through a

coupling capacitor with a dummy load to preserve balance. The

mismatched gain of the ADL5390 when the output is singleended varies slightly with dummy load value, as shown in Figure

31.

DRIVING THE I-Q BASEBAND GAIN CONTROLS

The I and Q gain control inputs to the ADL5390 set the gain for

each channel. These inputs are differential and should normally

have a common-mode level of 0.5 V. However, when differentially driven, the common mode can vary from 250 mV to

750 mV while still allowing full gain control. Each input pair

has a nominal input swing of ±0.5 V differential around the

common-mode level. The maximum gain is achieved if the

differential voltage is equal to +500 mV or −500 mV. So with a

common-mode level of 500 mV, IBBP and IBBM will each

swing between 250 mV and 750 mV.

The I and Q gain control inputs can also be driven with a singleended signal. In this case, one side of each input should be tied

to a low noise 0.5 V voltage source (a 0.1 µF decoupling capacitor located close to the pin is recommended), while the other

input swings from 0 V to 1 V. Low speed, single-ended drive can

easily be achieved using 12-bit voltage output DACs such as

AD8303 (serial SPI® interface) or AD8582 (parallel interface)

DACs. A reference voltage should also be supplied. Differential

drive generally offers superior even-order distortion and lower

noise than single-ended drive.

The bandwidth of the baseband controls exceeds 200 MHz even

at full-scale baseband drive. This allows for very fast gain modulation of the RF input signal. In cases where lower modulation

bandwidths are acceptable or desired, external filter capacitors

can be connected across Pins IFLP to IFLM and Pins QFLP to

QFLM to reduce the ingress of baseband noise and spurious

signal into the control path.

Rev. 0 | Page 13 of 24

Page 14

ADL5390

The 3 dB bandwidth is set by choosing C

following equation:

nF10kHz45

external

×

pF0.5

+

≈

f

dB3

C

This equation has been verified for values of C

0.1 µF (bandwidth settings of approximately 4.5 kHz to 43 MHz).

INTERFACING TO HIGH SPEED DACs

The AD977x family of dual DACs is well suited to driving the I

and Q gain controls of the ADL5390 with fast modulating signals. While these inputs can in general be driven by any DAC,

the differential outputs and bias level of the ADI TxDAC® family allows for a direct connection between DAC and modulator.

The AD977x family of dual DACs has differential current outputs. The full-scale current is user programmable and is usually

set to 20 mA, that is each output swings from 0 mA to 20 mA.

The basic interface between the AD9777 DAC outputs and the

ADL5390 I and Q gain control inputs is shown in Figure 32.

Resistors R1 and R2 (R1 = R2) set the dc bias level according to

the following equation:

Bias Level = Average Output Current × R1

For example, if the full-scale current from each output is 20 mA,

each output will have an average current of 10 mA. Therefore,

to set the bias level to the recommended 0.5 V, R1 and R2

should be set to 50 Ω each. R1 and R2 should always be equal.

If R3 is omitted, this will result in an available swing from the

DAC of 2 V p-p differential, which is twice the maximum voltage

range required by the ADL5390. DAC resolution can be maximized by adding R3, which scales down this voltage according

to the following equation:

=SwingScaleFull

according to the

FLT

from 10 pF to

FLT

AD9777 ADL5390

I

OUTA1

I

OUTB1

I

OUTA2

I

OUTB2

R1

R2

R1

R2

OPTIONAL

LOW-PASS

FILTER

OPTIONAL

LOW-PASS

FILTER

R3

R3

IBBP

IBBM

QBBP

QBBM

Figure 32. Basic AD9777-to-ADL5390 Interface

1.15

1.13

1.10

1.08

1.05

1.02

1.00

0.97

0.95

0.92

0.90

0.88

0.85

0.82

0.80

0.77

0.75

0.72

DIFFERENTIAL PEAK-PEAK SWING (R3) (V p-p)

0.70

R3 (Ω)

13050 55 60 65 70 75 80 85 90 100105 115 120110 12595

04954-033

Figure 33. Peak-Peak DAC Output Swing vs.

Swing Scaling Resistor R3 (R1 = R2 = 50 Ω)

Figure 33 shows the relationship between the value of R3 and

the peak baseband voltage with R1 and R2 equal to 50 Ω. As

shown in Figure 33, a value of 100 Ω for R3 will provide a

peak-peak swing of 1 V p-p differential into the ADL5390’s

I and Q inputs.

04954-032

MAX

R2

+

⎤

⎥

R3R2

⎥

⎦

()()

⎡

1||2

R3R2R1I

−×+×

⎢

⎢

⎣

When using a DAC, low-pass image reject filters are typically

used to eliminate the Nyquist images produced by the DAC.

They also provide the added benefit of eliminating broadband

noise that might feed into the modulator from the DAC.

Rev. 0 | Page 14 of 24

Page 15

ADL5390

(

[

(

)

=

GENERALIZED MODULATOR

The ADL5390 can be configured as a traditional IQ quadrature

modulator or as a linear vector modulator by applying signals

that are in quadrature to the RF/IF input channels. Since the

quadrature generation is performed externally, its accuracy and

bandwidth are determined by the user. The user-defined bandwidth is attractive for multioctave or lower IF applications

where on-chip, high accuracy quadrature generation is traditionally difficult or impractical. The gain control pins (I

and Q

) become the in-phase (I) and quadrature (Q) base-

BBP/M

BBP/M

band inputs for the quadrature modulator and the gain/phase

control for the vector modulator. The wide modulation bandwidths of the gain control interface allow for high fidelity baseband signals to be generated for the quadrature modulator and

for high speed gain and phase adjustments to be generated for

the vector modulator.

RF/IF signals can be introduce to the ADL5390 in quadrature

by using a two-way 90

o

power splitter such as the Mini-Circuits

QCN-12. Each output of an ideal 90o power splitter is 3 dB

smaller than the input and has a 90o phase difference from the

other output. In reality, the 90

o

power splitter will have its own

insertion loss, which can be different for each output, causing a

magnitude imbalance. Furthermore, quadrature output will not

be maintained over a large frequency range, introducing a phase

imbalance. The type of 90

o

power splitter that should be used

for a particular application will be determined by the frequency,

bandwidth, and accuracy needed. In some applications minor

magnitude and phase imbalances can be adjusted for in the

I/Q gain control inputs.

VECTOR MODULATOR

V

q

MAX GAIN = 5dB

+0.5

|A|

A

θ

V

i

+0.5–0.5

inputs V

IBB

and V

the vector gain, which can also be expressed as a magnitude and

phase. By applying different combinations of baseband inputs,

any vector gain within the unit circle can be programmed. The

magnitude and phase (with respect to 90

power splitter will directly affect this representation and could

be seen as an offset and skew of the circle.

A change in sign of V

sign of the gain or as a 180° phase change. The outermost circle

represents the maximum gain magnitude. The circle origin

implies, in theory, a gain of 0. In practice, circuit mismatches

and unavoidable signal feedthrough limit the minimum gain to

approximately −30 dB. The phase angle between the resultant

gain vector and the positive x-axis is defined as the phase shift.

Note that there is a nominal, systematic insertion phase through

the ADL5390 to which the phase shift is added. In the following

discussions, the systematic insertion phase is normalized to 0°.

The correspondence between the desired gain and phase and

the Cartesian inputs V

metric identities

where:

V

is the baseband scaling constant (285 mV).

O

V

and V

IBB

QBB

centered around 500 mV, respectively (V

V

= V

QBB

QBBP

Note that when evaluating the arctangent function, the proper

phase quadrant must be selected. For example, if the principal

value of the arctangent (known as arctangent(x)) is used, quadrants 2 and 3 would be interpreted mistakenly as quadrants 4

and 1, respectively. In general, both V

concert to modulate the gain and the phase.

. The resultant of their vector sum represents

QBB

o

) accuracy of the 90o

or V

IBB

IBB

IBB

QBB

can be viewed as a change in

QBB

and V

)

is given by simple trigono-

QBB

22

//

VVVVGain +=

OQBBO

]

()

VVarctanPhase /

IBB

are the differential I and Q baseband voltages

= V

− V

IBBP

IBBM

are needed in

QBB

− V

QBBM

).

and V

IBB

IBB

;

Pure amplitude modulation is represented by radial movement

of the gain vector tip at a fixed angle, while pure phase modula-

MIN GAIN < –30dB

–0.5

Figure 34. Vector Gain Representation

04954-034

The ADL5390 can be used as a vector modulator by driving the

RF I and Q inputs single-ended through a 90

o

power splitter. By

controlling the relative amounts of I and Q components that are

summed, continuous magnitude and phase control of the gain

is possible. Consider the vector gain representation of the

ADL5390 expressed in polar form in Figure 34. The attenuation

factors for the RF I and Q signal components are represented on

the x-axis and y-axis, respectively, by the baseband gain control

tion is represented by rotation of the tip around the circle at a

fixed radius. Unlike traditional I-Q modulators, the ADL5390 is

designed to have a linear RF signal path from input to output.

Traditional I-Q modulators provide a limited LO carrier path

through which any amplitude information is removed.

VECTOR MODULATOR EXAMPLE—CDMA2000

The ADL5390 can be used as a vector modulator by driving the

RF I and Q inputs (INPI and INPQ) single-ended through a 90

power splitter and controlling the magnitude and phase using

the gain control inputs. To demonstrate operation as a vector

modulator, an 880 MHz single-carrier CDMA2000 test model

o

signal (forward pilot, sync, paging, and six traffic as per

Rev. 0 | Page 15 of 24

Page 16

ADL5390

–

3GPP2 C.S0010-B, Table 6.5.2.1) was applied to the ADL5390.

A cavity-tuned filter was used to reduce noise from the signal

source being applied to the device. The 4.6 MHz pass band of

this filter is apparent in the subsequent spectral plots.

Figure 35 shows the output signal spectrum for a programmed

gain and phase of 5 dB and 45

V

= V

IBB

V

IBBM

= 0.353 V (centered around 500 mV), i.e., V

QBB

= V

QBBP

− V

= 0.353 V. Adjacent channel power is

QBBM

measured in 30 kHz resolution bandwidth at 750 kHz and

1.98 MHz carrier offset. Noise floor is measured at ±4 MHz

carrier offset in a 1 MHz resolution bandwidth.

REF LVL

5dBm

0.7dB OFFSET

0

–10

–20

–30

1AVG

–40

–50

–60

–70

Cl2

–80

–90

100

CENTER 880MHz 500kHz/ SPAN 5MHz

Figure 35. Output Spectrum, Single-Carrier CDMA2000 Test Model at −5 dBm,

= VQ = 0.353 V, ACP Measured at 750 kHz and 1.98 MHz Carrier Offset,

V

I

Input Signal–Filtered Using a Cavity-Tuned Filter (Pass Band = 4.6 MHz)

Cl2

MARKER 1 [T1]

–14.38dBm

880.00755511MHz

Holding the I and Q gain control voltages steady at 0.353 V,

input power was swept. Figure 36 shows the resulting output

power, noise floor, and adjacent channel power ratio. The noise

floor is presented as noise in a 1 MHz bandwidth as defined by

the 3GPP2 specification.

–30

–40

o

. P

is equal to 0 dBm and

OUT

−

IBBP

RBW 30kHz

VWB 300kHz

SWT 2s

1

C0

Cl1

Cl1

RF ATT 20dB

MIXER –10dBm

UNIT dB

1 [T1] –14.38dBm

880.00755511MHz

CH PWR

1 [T1] –14.38dBm

880.00755511MHz

CH PWR 0.13dBm

ACP UP –62.00dB

ACP LOW –61.98dB

ALT1 UP –87.02dB

ALT1 LOW –87.04dB

C0

CU1

CU1

CU2

A

1RM

EXT

CU2

04954-035

–30

–40

ACP is still in compliance with the standard (<−45 dBc @

750 kHz and <−60 dBc @ 1.98 MHz) even with output powers

greater than +3 dBm. At low output power levels, ACP at

1.98 MHz carrier offset degrades as the noise floor of the

ADL5390 becomes the dominant contributor to measured ACP.

Measured noise at 4 MHz carrier offset begins to increase

sharply above 2 dBm output power. This increase is not due to

noise, but results from increased carrier-induced distortion. As

output power drops below 2 dBm, the noise floor drops towards

−90 dBm.

With a fixed input power of 2.16 dBm, the output power was

again swept by changing V

and V

IBB

from 0 V to 500 mV.

QBB

The resulting output power, ACP, and noise floor are shown in

Figure 37.

5

–2

–9

–16

–23

–30

RF OUTPUT POWER (dBm)

–37

–44

0 0.1 0.2 0.3 0.4 0.5

ACP: 1.98MHz OFFSET, 30kHz RBW

NOISE: 4MHz OFFSET, 1MHz RBW

V

vs. V

OUT

IBB/VQBB

ACP: 750kHz OFFSET, 30kHz RBW

V

I(Q)BB

Figure 37. Output Power, Noise, and ACP vs. I and Q Control Voltages,

CDMA2000 Test Model, V

= VQ, ACP Measured in 30 kHz RBW at ±750 MHz

I

and ±1.98 MHz Carrier Offset, Noise Measured at ±4 MHz Carrier Offset

–30

–40

–50

–60

–70

–80

–90

–100

ACP (dBc)

NOISE (dBm @ 4MHz Carrier Offset)

04954-045

In contrast to Figure 36, Figure 37 shows that for a fixed input

power, ACP remains fairly constant as gain and phase are

changed (this is not true for very high RF input powers) until

the noise floor of the ADL5390 becomes the dominant contributor to the measured ACP.

–50

–60

–70

ACP (dBc)

–80

–90

–100

–30 –25 –20 –15 –10 –5 0 5

ACP: 1.98MHz OFFSET, 30kHz RBW

NOISE: 4MHz OFFSET, 1MHz RBW

ACP: 750kHz OFFSET, 30kHz RBW

OUTPUT POWER (dBm)

–50

–60

–70

–80

–90

–100

NOISE (dBm @ 4MHz Carrier Offset)

04954-044

Figure 36. Noise and ACP vs. Output Power, Single-Carrier CDMA2000 Test

Model, VI = VQ = 0.353, ACP Measured in 30 kHz RBW at ±750 kHz and

±1.98 MHz Carrier Offset, Noise Measured at ±4 MHz Carrier Offset

Rev. 0 | Page 16 of 24

Page 17

ADL5390

1

234

QUADRATURE MODULATOR

The ADL5390 can be used as a quadrature modulator by driving

the RF I and Q inputs (INPI and INPQ) single-ended through a

o

90

phase splitter to serve as the LO input. I/Q modulation is

applied to the baseband I and Q gain control inputs (IBBP/IBBM

and QBBP/QBBM). A simplified schematic is shown in Figure

38.

I DATA

LO IN

50Ω

SUM

PORT

QCN-12

TERM

PORT

90° PHASE

SPLITTER

PORT 1

PORT 2

10nF

66.5Ω

10nF

66.5Ω

INPI

INPQ

Figure 38. Quadrature Modulator Application

Single sideband performance of a quadrature modulator is

determined by the magnitude and phase balance (compared to

o

a 90

offset) at the summation point of the I and Q signals.

Because the ADL5390 has matched amplifiers and mixers in

the I and Q channel, most of the single sideband performance

will be determined by the external 90

single sideband performance can be achieved by choosing a

well-balanced 90

o

phase splitter. However, phase and magnitude

differences in the 90o phase splitter can be corrected by adjusting

the magnitude and phase of the I and Q data. Figure 39 shows

the performance of the ADL5390 used in conjunction with MiniCircuits QCN-12 90

o

power splitter. Figure 40 shows the single

sideband improvement as the I and Q data is adjusted in magnitude

and phase to achieve better single sideband performance.

IBBP

IBBM

RFOM

ADL5390

Q DATA

RFOP

QBBP

QBBM

o

phase splitter. Good

10nF

10nF

(M/A-COM)

15

34

ETC1-1-13

ROFP

*

RBW 3kHz

VWB 10kHz

SWT 780ms

A

1

4

04954-039

1 AP

CLRWR

REF 7dBm ATT 35dB

DESIRED SIDEBAND

–16.20dBm

0

900.998397436MHz

UNDESIRED SIDEBAND

–10

–23.27dB

–1.996794872MHz

–20

THIRD BASEBAND HARMONIC

–37.38dB

–30

–4.004807692MHz

LO FEEDTHROUGH

–40

–41.27dB

–998.397435897kHz

–50

3

–60

–70

-80

-

CENTER 900MHz 700kHz/ SPAN 7MHz

2

Figure 39. SSB Quadrature Modulator Result Us ing External 90° Phase Splitter,

= −15 dBm, VIBB = VQBB = 0.5 V

RF P

IN

(With Reference to a Common-Mode Voltage of 0.5 V )

*

RBW 3kHz

REF 7dBm ATT 35dB

DESIRED SIDEBAND

0

04954-038

1 AP

CLRWR

–16.78dBm

900.998397436MHz

UNDESIRED SIDEBAND

–10

–51.81dB

–1.996794872MHz

–20

THIRD BASEBAND HARMONIC

–38.45dB

–30

–4.004807692MHz

LO FEEDTHROUGH

–40

–41.49dB

–998.397435897kHz

–50

–60

–70

–80

–90

CENTER 900MHz 700kHz/ SPAN 7MHz

VWB 10kHz

SWT 780ms

A

04954-046

Figure 40. SSB Modulator Applications with Gain and Phase Errors Corrected,

RF Pin = −15 dBm, VIBB = VQBB = 0.5 V (With Reference to a Common-Mode

Voltage of 0.5 V), I/Q Phase O ffset by 3

o

, and Magnitude Offset by 0.5 V

For maximum dynamic range, the ADL5390 should be driven

as close to the output 1 dB compression point as possible. The

output power of the ADL5390 increases linearly with the RF

(LO) input power and baseband gain control input voltage until

the ADL5390 reaches compression. At the 1 dB compression

point, the lower sideband starts to increase. Figure 41 demonstrates the output spectrum of a 3-carrier CDMA2000 signal

applied to the I/Q baseband gain control inputs. As the RF (LO)

power is increased, the relative amount of noise is reduced until

the ADL5390 goes into compression. At this point, the relative

noise increases, as shown in Figure 42.

Analog Devices has several quadrature/vector modulators that

have highly accurate integrated 90

o

phase splitters—AD8340,

AD8341, AD8345, AD8346, AD8349—that cover a variety of

frequency bands.

Rev. 0 | Page 17 of 24

Page 18

ADL5390

RBW 10kHz

*

VBW 300kHz

REF –26.6dBm

1 RM

AVG

*

–100

–110

–120

–30

–40

–50

–60

–70

–80

–90

POS –26.623dBm

CENTER 880MHz 1.29MHz/ SPAN 12.9MHz

STANDARD: CDMA IS95C CLASS 0 FWD

Tx CHANNELS

CH1 (REF)

CH2

CH3

TOTAL

ATT 5dB

*

–22.93dBm

–22.83dBm

–22.95dBm

–18.13dBm

*

SWT 4s

*

ADJACENT CHANNEL

LOWER –59.25dB

UPPER –59.43dB

ALTERNATE CHANNEL

LOWER –62.79dB

UPPER –63.11dB

2ND ALTERNATE CHANNEL

LOWER –60.71dB

UPPER –60.32dB

A

NOR

Figure 41. ADL5390 as a Quadrature Modulator with the Use of an External

90° Phase Splitter, RF/LO Power = −1 dBm and Gain Control Inputs Driven

Differentially with 0.353 V

–69

–70

–71

–72

–73

–74

–75

NOISE (dBC) (1MHz RBW)

–76

–77

–78

–25 –20 –15 –10 –5 0

NOISE (dBc) - 8MHz OFFSET - 1MHz RBW

, 3-Carrier CDMA2000 I/Q Data

P-P

OUTPUT POWER (dBm)

04954-031

Figure 42. Noise vs. Output Power

04954-037

RF MULTIPLEXER

The ADL5390 may also be used as an RF multiplexer. In this

application, two RF signals are applied to the INPI and INPQ

inputs, and the baseband voltages control which of the two RF

signals appears at the output. Figure 43 illustrates this application and shows that with V

ence to a common-mode voltage of 0.5 V). The INPI signal is

presented to the output. Then, when V

0.0 and V

Lastly, as V

the output. With V

remains equal to zero, there is no RF output.

QBB

transitions to 0.5 V, the INPQ signal appears at

QBB

= 0.0 and V

IBB

output is typically >40 dB at 380 MHz.

TEK STOPPED 200 Acqs 24 AUG 04 11:08:40

CH2

2

CH3

CH1

3

1

CH1 200mV Ω CH2 500mV Ω D

CH3 500mV Ω D

S

Figure 43. ADL5390 in RF Multiplexer Application

= 0.5 and V

IBB

= 0.0, the isolation to the

QBB

V

IBB

V

QBB

RF OUTPUT

M 40.0ns 1.25GS/s 800ps/pt

S

A CH2 780mV

= 0.0 (with refer-

QBB

transitions to V

IBB

IBB

04954-047

=

Rev. 0 | Page 18 of 24

Page 19

ADL5390

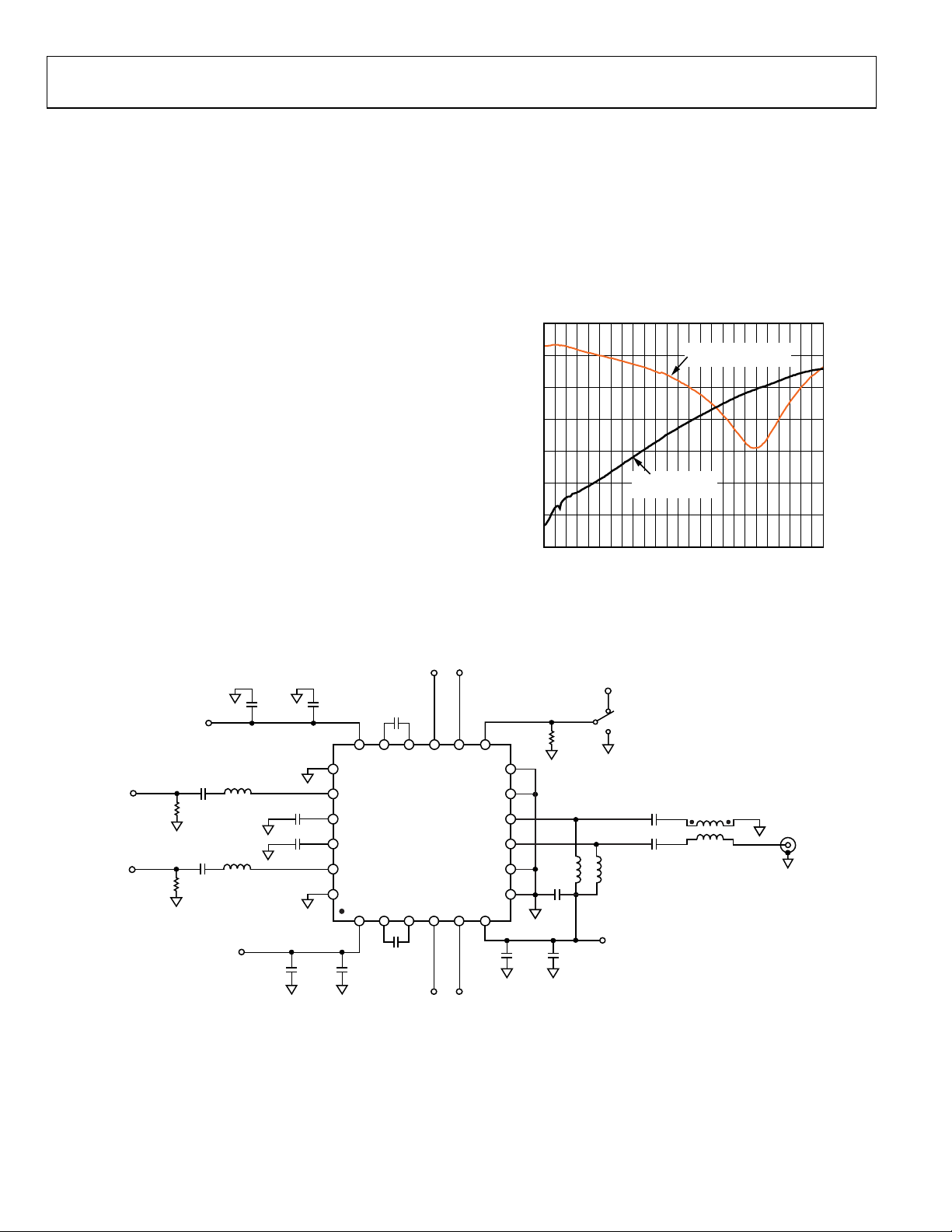

EVALUATION BOARD

The evaluation board circuit schematic for the ADL5390 is

shown in Figure 44.

The evaluation board is configured to be driven from a

single-ended 50 Ω source. Although the input of the ADL5390

is differential, it may be driven single-ended with no loss of

performance.

The low-pass corner frequency of the baseband I and Q channels can be reduced by installing capacitors in the C11 and C12

positions. The low-pass corner frequency for either channel is

approximated by

nF10kHz45

external

×

pF0.5

+

f

≈

dB3

C

On this evaluation board, the I and Q baseband circuits are

identical to each other, so the following description applies to

each. The connections and circuit configuration for the I/Q

baseband inputs are described in Table 4.

The baseband input of the ADL5390 requires a differential voltage drive. The evaluation board is set up to allow such a drive

by connecting the differential voltage source to QBBP and

QBBM. The common-mode voltage should be maintained at

approximately 0.5 V. For this configuration, Jumpers W1 to W4

should be removed.

The baseband input of the evaluation board may also be driven

with a single-ended voltage. In this case, a bias level is provided

to the unused input from Potentiometer R10 by installing either

W1 or W2.

Setting SW1 in Position B disables the ADL5390 output amplifier.

With SW1 set to Position A, the output amplifier is enabled. With

SW1 set to Position A, an external voltage signal, such as a pulse,

can be applied to the DSOP SMA connector to exercise the

output amplifier enable/disable function.

Rev. 0 | Page 19 of 24

Page 20

ADL5390

Table 4. Evaluation Board Configuration Options

Component Function Default Conditions

R7, R9, R11, R14,

R15, R19, R20,

R21, C15, C19,

W3, W4

R1, R3, R10, R12,

R13, R16, R17,

R18, C16, C20,

W1, W2

C11, C12

T1, C17, C18, L3,

L4

C2, C1, R2

C5, C6, R22

R4, R6, R5, C4, C7

C9, C3, C8, C10

R8, SW1

I Channel Baseband Interface. Resistors R7 and R9 may be installed to

accommodate a baseband source that requires a specific terminating

impedance. Capacitors C15 and C19 are bypass capacitors. For single-ended

baseband drive, the Potentiometer R11 can be used to provide a bias level to

the unused input (install either W3 or W4).

Q Channel Baseband Interface. See the I Channel Baseband Interface section.

Baseband Low-Pass Filtering. By adding capacitor C11 between QFLP and

QFLM, and capacitor C12 between IFLP and IFLM, the 3 dB low-pass corner

frequency of the baseband interface can be reduced from 230 MHz (nominal)

as given by the equation in the Evaluation Board section.

Output Interface. The 1:1 balun transformer, T1, converts the 50 Ω differential

output to 50 Ω single-ended. C17 and C18 are dc blocks. L3 and L4 provide dc

bias for the output.

I and Q Channel RF Input Interface. The single-ended impedance to the

ADL5390 RF inputs is 200 Ω. Shunt terminations R2 and R22 of 66.5 Ω bring the

impedances to 50 Ω. C2 and C5 are dc blocks. C1 and C6 are used to ac-couple

the unused side of the differential inputs to common.

Power Supply Decoupling.

Output Disable Interface. The output stage of the ADL5390 is disabled by

applying a high voltage to the DSOP pin by moving SW1 to Position B. The

output stage is enabled moving SW1 to Position A. The output disable

function can also be exercised by applying an external high or low voltage to

the DSOP SMA connector with SW1 in Position A.

R7, R9 = not installed

R11 = potentiometer, 2 kΩ, 10 turn

(Bourns)

R14 = 4 kΩ (size 0603)

R15 = 44 kΩ (size 0603)

R19, R20, R21 = 0 Ω (size 0603)

C15, C19 = 0.1 µF

(Size 0603)

W3 = jumper (installed)

W4 = jumper (open)

R1, R3 = not installed

R10 = potentiometer, 2 kΩ, 10 turn

(Bourns)

R12 = 4 kΩ (size 0603)

R13 = 44 kΩ (size 0603)

R16, R17, R18 = 0 Ω

(size 0603)

C16, C20 = 0.1 µF (size 0603)

W1 = jumper (installed)

W2 = jumper (open)

C11, C12 = not installed

C17, C18 = 10 nF (size 0603)

T1 = ETC1-1-13 (M/A-COM)

L3, L4 = 120 nH (size 0603)

C2 = C1 = 10 nF (size 0603)

R2 = 66.5 Ω 10 (size 0603)

C5 = C6 = 10 nF (size 0603)

R22 = 66.5 Ω 10 (size 0603)

R4, R6, R5 = 0 Ω (size 0603)

C4, C7 C9 = 0.1uF (size 0603)

C3, C8, C10 = 100 pF (size 0603)

R8 = 10 kΩ (size 0603)

SW1 = SPDT (Position A, output

enabled)

Rev. 0 | Page 20 of 24

Page 21

ADL5390

RFIN_I

RFIN_Q

VP

66.5Ω

R22

66.5Ω

R8

10kΩ

L4

VP

TEST POINT

B

SW1

A

L3

120nH

VP

IBBMIBBP

W4

0.1µF

R14

4kΩ

IFLM

QFLM

C15

R19

0Ω

R11

2kΩ

IBBP

QBBP

C19

0.1µF

W3

IBBM

QBBM

R15

44kΩ

DSOP

CMOP

CMOP

RFOM

RFOP

CMOP

CMOP

VPS2

100pF

R7

(OPEN)

R20

0Ω

C10

VP

120nH

C14

0.1µF

R6

0Ω

C9

0.1µF

R9

(OPEN)

R21

0Ω

C1

10nF

C6

10nF

R4

0Ω

100pF

C8

100pF

C3

VPRF

CMRF

INPI

INMI

IPMQ

INPQ

CMRF

VPRF

C12

(OPEN)

IFLP

ADL5390

P

L

F

Q

C11

(OPEN)

C7

R5

0.1µF

0Ω

L1

0Ω

R2

C2

10nF

L2

0Ω

C5

10nF

VP

C4

0.1µF

C18

10nF

C17

10nF

GND

TEST POINT

15

3

T1

ETC1-1-13

(M/A-COM)

DSOP

4

RFOP

R12

R10

2kΩ

R16

0Ω

C20

0.1µF

R13

44kΩ

W1

VP

R18

0Ω

R3

(OPEN)

QBBM

04954-040

QBBP

R17

0Ω

R1

(OPEN)

4kΩ

C16

0.1µF

W2

Figure 44. Evaluation Board Schematic

Rev. 0 | Page 21 of 24

Page 22

ADL5390

04954-041

04954-042

Figure 45. Component Side Layout

Figure 46. Component Side Silkscreen

Rev. 0 | Page 22 of 24

Page 23

ADL5390

OUTLINE DIMENSIONS

0.60 MAX

19

18

EXPOSED

(BOTTOMVIEW)

13

12

PA D

24

6

7

1

2.50 REF

PIN 1

INDICATOR

2.45

2.30 SQ

2.15

0.23 MIN

*

PIN 1

INDICATOR

1.00

0.85

0.80

SEATING

PLANE

12° MAX

4.00

BSC SQ

TOP

VIEW

0.80 MAX

0.65 TYP

*

COMPLIANT TO JEDEC STANDARDS MO-220-VGGD-2

EXCEPT FOR EXPOSED PAD DIMENSION

0.30

0.23

0.18

3.75

BSC SQ

0.20 REF

0.05 MAX

0.02 NOM

COPLANARITY

0.60 MAX

0.50

BSC

0.50

0.40

0.30

0.08

Figure 47. 24-Lead Lead Frame Chip Scale Package [LFCSP]

4 × 4 mm Body

(CP-24-2)

Dimensions shown in millimeters

ORDERING GUIDE

Models Temperature Range Package Description Package Option Order Multiple

ADL5390ACPZ-WP

ADL5390ACPZ-REEL71 −40°C to +85°C 24-Lead Lead Frame Chip Scale Package (LFCSP) CP-24-2 1,500

ADL5390-EVAL Evaluation Board 1

1

Z = Pb-free part.

2

WP = waffle pack.

1, 2

−40°C to +85°C 24-Lead Lead Frame Chip Scale Package (LFCSP) CP-24-2 64

Rev. 0 | Page 23 of 24

Page 24

ADL5390

NOTES

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

D04954–0–10/04(0)

Rev. 0 | Page 24 of 24

Loading...

Loading...